**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>6</sup>

G06F 3/00

(45) 공고일자 1996년03월04일

(11) 공고번호 특 1996-0003064

---

|           |                |           |                |

|-----------|----------------|-----------|----------------|

| (21) 출원번호 | 특 1988-0005244 | (65) 공개번호 | 특 1988-0014452 |

| (22) 출원일자 | 1988년05월06일    | (43) 공개일자 | 1988년12월23일    |

---

(30) 우선권주장 37 14 998.9 1987년05월06일 독일(DE)

(71) 출원인 로베르트 보쉬 게엠베하 클라우스 보스, 빌프리에드 빌트

1996년03월04일

(72) 발명자

컨테르 카이저

독일연방공화국, 데-7000 슈튜트가르트 40, 슈바인푸르츠스트라쎄 10

빈프리드 클뢰츠너

독일연방공화국, 데-7133 마울브론 2, 하우프스트라쎄 8

임마누엘 크라우터

독일연방공화국, 데-7151 에르브스테텐, 하우프스트라쎄 26

에드먼드 제니커

독일연방공화국, 데-7141 쉬비에베르딘겐, 슈튜트가르터 스트라쎄 102

이병호, 최달용

**심사관 : 홍순우 (책자공보 제4360호)**

**(54) 마이크로 프로세서용 입·출력 회로장치**

---

**요약**

내용 없음.

**대표도**

**도1**

**명세서**

[발명의 명칭]

마이크로 프로세서용 입·출력 회로장치

[도면의 간단한 설명]

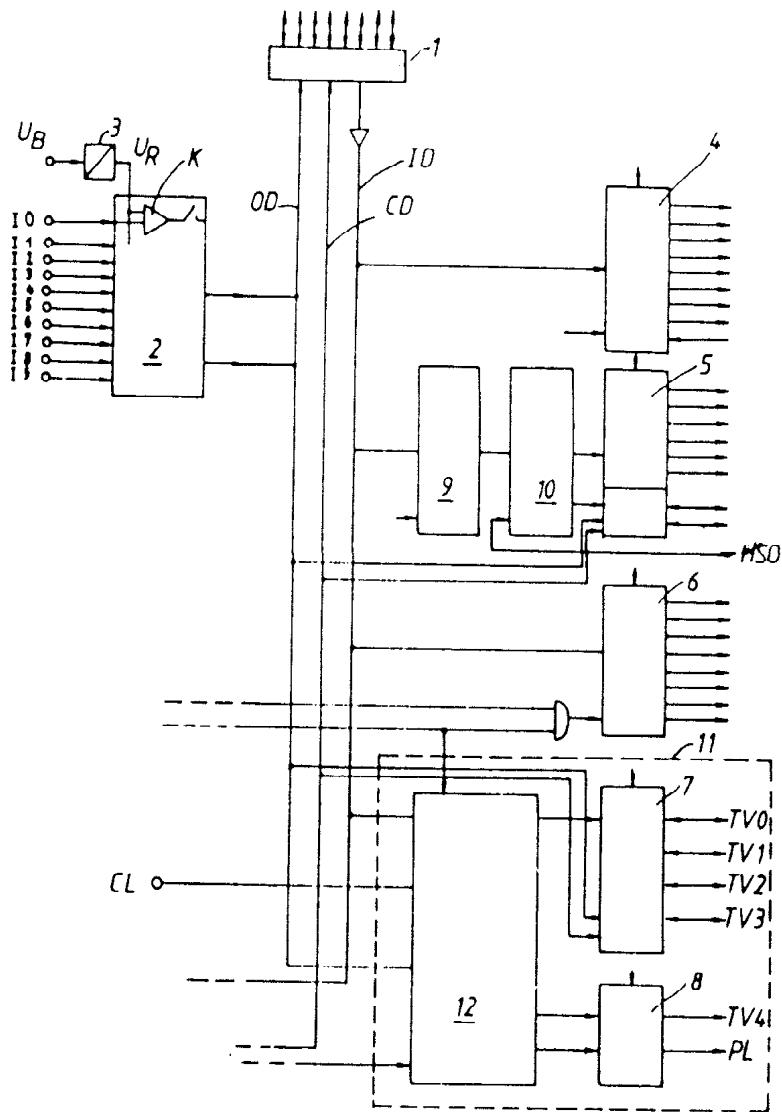

제1도는 본 발명의 입·출력 회로장치의 실시예의 블록 접속도.

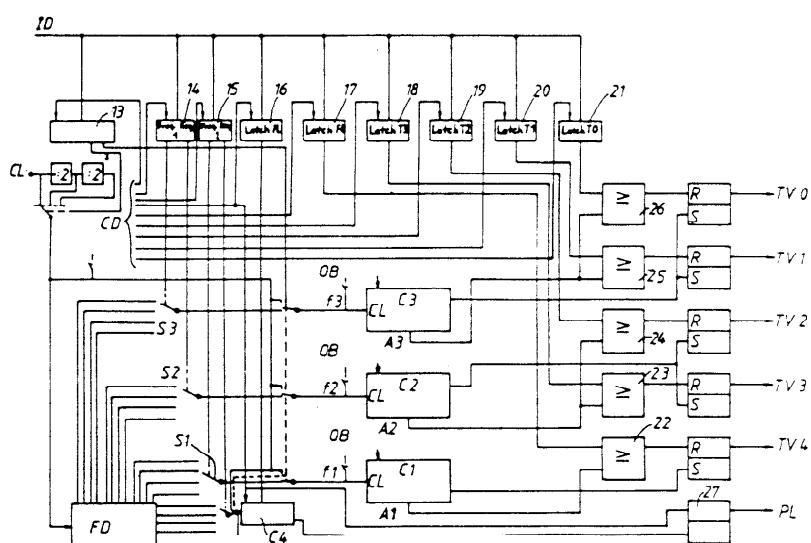

제2도는 제1도의 회로 장치에 설치되어 있는 상이한 키잉비의 조종을 위한 장치의 상세 접속도.

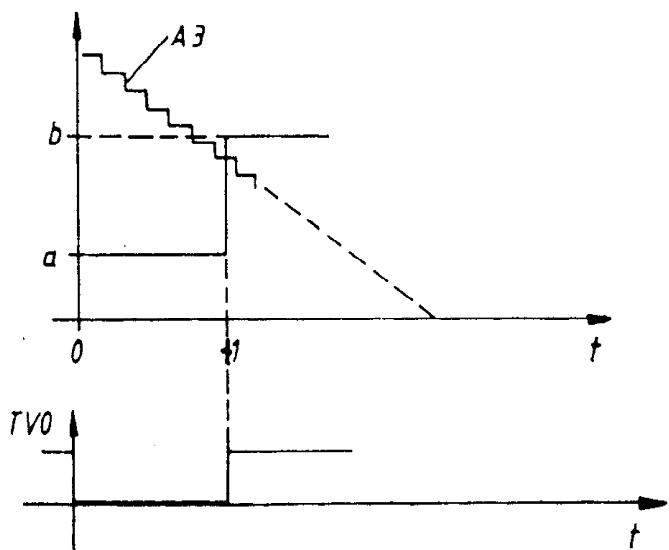

제3도는 제2도의 블록 접속도의 구성에서 생기는 신호의 파형도.

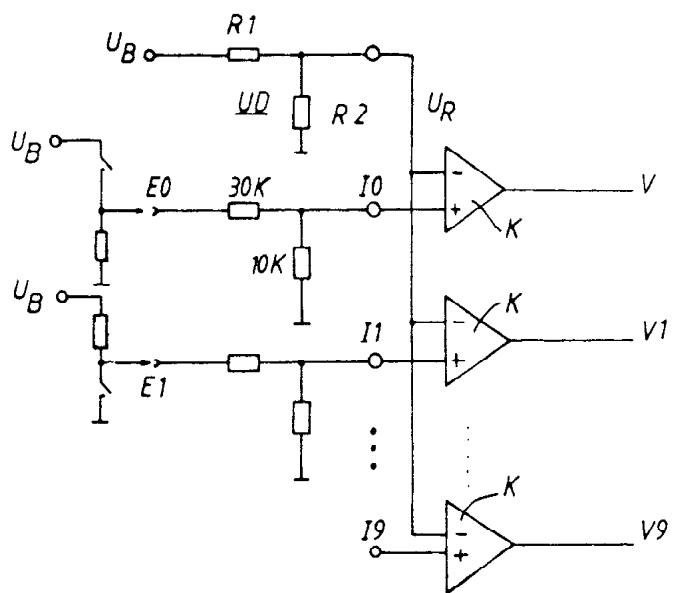

제4도는 기준전압의 전지전압에 의존하는 콤퍼레이터의 구성도.

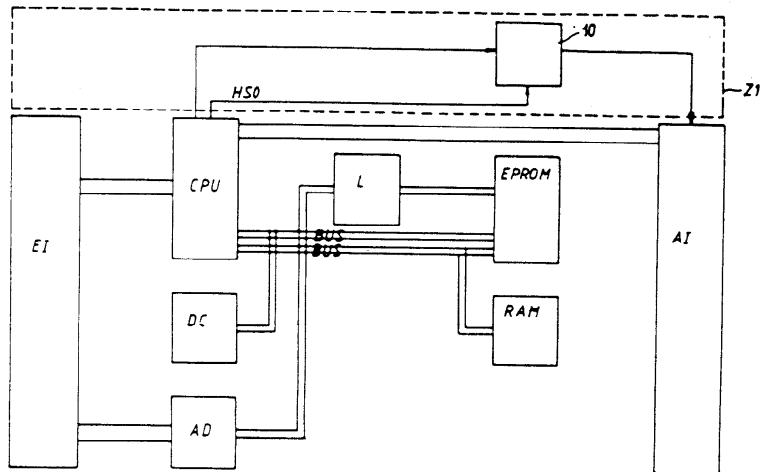

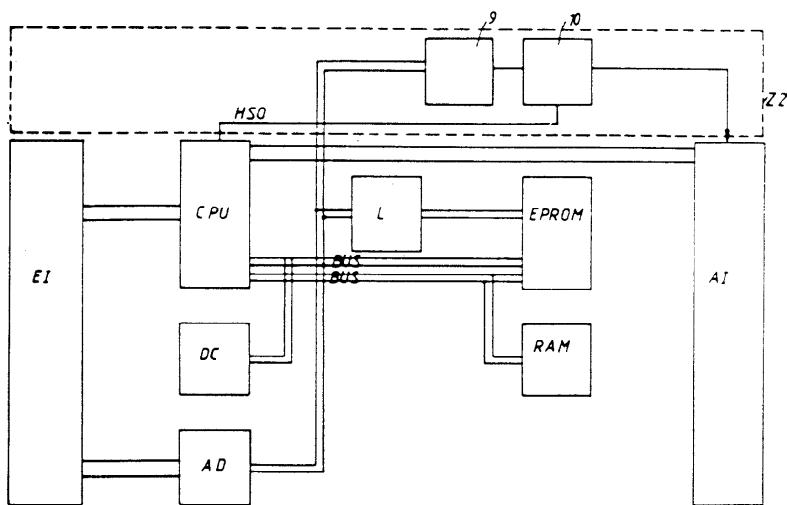

제5도 및 제6도는 HSO 포트의 확대를 위해 부가적 레지스터를 가지는 구성의 블록접속도.

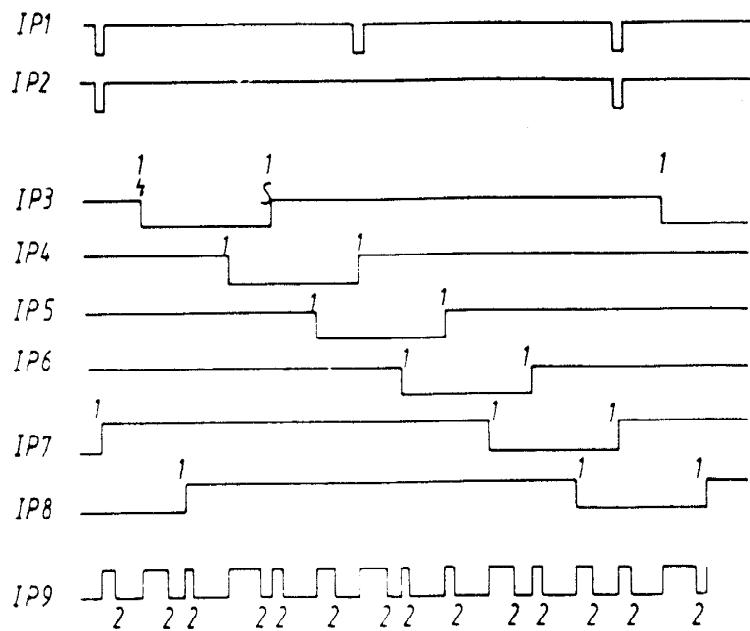

제7도는 6기통 기관에서 생기는 여러가지 신호의 펄스 파형도.

\* 도면의 주요부분에 대한 부호의 설명

1 : 인터페이스 2 : 콤퍼레이터장치

3 : 전압변환기 4 내지 8 : 인터페이스

[발명의 상세한 설명]

본 발명은 특허청구범위 제1항의 상위개념에 의한 마이크로세서용 입·출력 회로장치에 관한다.

특히 자동차에 쓰이는 것 같은 제어장치의 전기신호의 검출, 처리를 위해 입·출력 회로(장치)에서는 아나로그동작을 하는 콤퍼레이터가 쓰이며, 이들 콤퍼레이터는 아나로그 입력신호를 한계값이 조합해서 감시한다. 컴퓨터 프로그램과 제어되어야 할 기관의 작동상태에 의존해서 입·출력 회로 장치

로 프로그래밍 가능한 반복주파수로 가변 키잉비 내지 듀티레이시오가 발생되어져서 출력측 제어신호가 예컨대, 변화된 기관회전수에 적합 되어진다. 특히, 자동차-제어장치에서 적용할때, 예컨대 가솔린 분사상태를 최적 제어할 수 있으려면 다수의 출력신호가 매우 정확한 시점에서 송출되도록 할 것이 필요하다.

종래의 입·출력 회로장치에서는 여러가지 신호 처리기능 및 제어기능 역할을 할 수 있으려면 여러 가지 다른 전자부품, 소자가 상호 합성 접속되어야 한다.

본 발명의 과제 내지 목적으로 하는 바는 종래기술에서의 첫머리에 말한 형식의 회로장치로 개량을 하여 최적 제어를 위한 정확한 신호생성을 할 수 있는 회로장치를 제공하는데 있다.

상기 과제는 본 발명에 의하면 특허청구범위 제1항의 구성요건으로 해결된다.

변동 내지 슬라이드 하는 기준 전압은 유리하게 전자전압과 접지간에 설치된 2개의 저항으로 되는 분압기를 거쳐서 발생되어진다. 그 경우, 해당 텁으로 전자전압과 더불어 변화하는 소망의 기준전압이 끄집어내어져 형성된다. 복수의 컴퓨터에 대해서 기준전압형성을 위한 1개의 분압기가 사용될 수 있으며 그것에 의해서 구성소자, 부품이 두드러진 절감이 달성된다.

변화하는 한계값에 대한 되도록 신속한 응답, 응동을 가능하게 하기 위해서 비교기가 설치되며 이 비교기는 그 입력측에 가해지는 디지털값이 상등한지여부, 또, “>”(한계값이 해당 실제값보다 크다)의 조건의 발생여부에 대해 점검하고 이 조건의 발생시 출력신호를 송출한다. 이것은 다만 상등한지 여부만을 체크하는 종래의 디지털 비교기에 비해서 다음같은 이점 즉 변화하는 한계값에 비해서 다음 같은 이점, 즉 변화하는 한계값에 대해서 비교기의 가일층 신속한 응답, 응동이 행해진다는 이점을 가진다. 이것은 특히 다음과 같은 경우 유리하다. 즉, 한계값이 다운카운터의 값과 비교되며 그것으로 비교기의 출력신호의 소정의 키잉비가 정해지는 경우 특히 유리하다. 한계값이 변화되면 본 발명의 비교기에서는 종래의 비교기의 경우에서보다 조기 시점에서 키잉비 내지 듀티레이시오가 변화한다.

하나의 다운카운터 출력측에는 복수의 비교기의 한쪽의 입력측의 접속되어져서 그것으로 상이한 한계값의 인가로 상이한 키잉비 내지 듀티레이시오가 얻어지며 그때, 복수의 다운카운터가 필요치 않은 것 같이 할 수 있다.

종래의 접적화 출입회로장치에서는 다만 한정된 수의 고속도 출력측(HSO-보트) 밖에 존재하지 않으며 이들 수의 출력측은 특히 자동차로 제어기능, 역할에 대해서는 그수의 점에서 때때로 불충분한 것이다. 이것들의 소위 HSO 포트는 입·출력 회로장치에서 다음같이 해서 확대될 수 있는, 즉 출력인터페이스와 내부 데이터 선로 사이에서 부가적 출력 레지스터(출력 래치)가 삽입 접속되며 이 출력 레지스터는 그 이네블(준비) 입력측에서 중앙 프로세서 유닛의 HSO-포트와 접속되어 있는것 같아 하는 것이다. 이같은 출력 레지스터에는 부가적인 이네블(준비) 레지스터가 전자 접속되고, 그것으로 HSO-신호발생때 출력 레지스터는 그내용을 순간에 출력 인터페이스에 송출하고 이네블 레지스터의 내용을 동시에 인수할 수 있도록 할 수 있다. 이같이해서 비교적 큰규모, 범위에서의 제어정보의 시간적으로 정확한 처리 및 전송이 가능해진다.

상술의 수단으로, 입·출력 회로장치로 높은 접적도를 달성하는 것이 가능하며 그때, 모든 기능이 하나의 칩상에 접적된다.

다음에 도시하는 실시예를 써서 본 발명을 상술한다.

제1도의 블록접속도에 도시하는 장치구성은 양방향 인터페이스(1)를 가지며 이 인터페이스에는 데이터 선로 OD, CD, ID가 접속되어 있다. 데이터 선로 OD는 다른 데이터 선로와 마찬가지로 8종으로 구성될 수 있으며 송신 데이터버스를 이룬다. 데이터 선로 ID는 인터페이스(1)를 거쳐서 도래하는데 이타에 대한 데이터버스를 형성하며 한편, CD는 제어데이터버스를 형성한다. 복수의 컴퓨터 K를 가지는 컴퓨터 장치(2)에 있어서 입력측 아나로그신호(10) 내지 (19)가 기준전압 U<sub>R</sub>과

비교된다. 기준전압 U<sub>R</sub>은 전압변환기(3)(이것은 분압기로서 구성될 수 있다)를 거쳐서 전자전압 U<sub>B</sub>로부터 도출될 수 있다. 컴퓨터 회로(2)의 구성을 제4도를 써서 상술한다.

제1도의 블록접속에서는 다른 인터페이스(4) 내지 (8)이 도시되어 있으며, 이것들의 인터페이스는 출력측의 방향을 나타내는 화살표로 나타내는 바와 같이 제어신호를 송출, 수신한다. 이것들의 인터페이스는 플립플롭으로 실현될 수 있는 레지스터(래치)로서 구성되어 있다. 인터페이스(5)에는 이네블(준비) 레지스터(9)와 출력 레지스터(10)가 전자 접속되어 있다. 이 경우 출력 레지스터(10)의 이네블(준비) 입력측은 HSO 포트의 고속도 트리거 신호단자와 접속되어 있다. 데이터버스 ID를 거쳐서 도래하는 데이터는 우선 준비 레지스터(9)에 중간 기억되며 HSO 트리거 신호 발생시 출력 레지스터(10)중에 전송된다. 그와 동시에 출력 레지스터(10)중에 이미 기억된 정보는 인터페이스(5)로 전송된다. 준비, 출력 레지스터(9), (10)의 이 이상의 설명은 제5도, 제6도를 써서 한다.

제1도에는 인터페이스(7), (8)의 출력측에서 여러가지 상이한 키잉비 내지 듀티레이오시를 형성하기 위해 쓰이는 장치(11)가 도시되어 있다. 이 목적을 위해서 디지털 카운터 비교기 유닛(12)이 설치되어 있으며, 이것에 대해서는 제2도를 써서 설명한다.

제2도에 있어서 데이터버스 ID는 복수의 레지스터(13) 내지 (21)에 접속되어 있으며 그것들중에서 레지스터(래치)(17) 내지 (21)은 출력측이 비교기(22) 내지 (26)과 접속되어 있다. 비교기 (22) 내지 (26)의 다른 출력측은 카운터 C<sub>1</sub> 내지 C<sub>3</sub>과 접속되어 있다. 비교기(22) 내지 (26)은 레지스터(17) 내지 (21)내에 파일된 디지털 한계값을 카운터 C<sub>1</sub> 내지 C<sub>3</sub>(이것은 다음 카운터로서 구성되어 있다)의 그때마다 실제의 카운터 상태와 비교한다. 상기 한계값이 대응하는 카운터 상태와 같던가 그 이상의 경우, 상응하는 비교기는 출력측에서 신호를 그것에 후지 접속된 R<sub>s</sub> 플립플롭에 송출한다. 그것에 의해서 출력측 TV0 내지 TV4에서 상이한 키잉비(내지 듀티레이시오)를 가지는 제어신호가 나타난다.

그때 그 상이한 키잉비는 더우기 그때마다 조정 설정되는 디지털 한계값에도 의존한다.

카운터 C<sub>1</sub> 내지 C<sub>3</sub>는 그 클록입력측에서 분주기 FD 형성되는 소정 주파수의 공급을 받는다. 스위치 S1 내지 S3을 거쳐서 상이한 주파수 f<sub>1</sub> 내지 f<sub>301</sub> 선택된다.

분주기 FD의 입력측에 공급되는 입력측 클록신호 CL은 상이한 주파수로 변환되며, 이 주파수로 또한 다운카운터 C4와 플립플롭(27)을 거쳐서 다른 출력신호 PL가 발생되어진다.

제3도에는 같은시간 눈금을 가지는 2개의 다이어그램이 도시되어 있으며 한쪽의 다이어그램은 카운터 C3의 출력 신호 A3을 나타내며 그 아래쪽에 있는 다이어그램은 출력신호 TV0를 나타낸다. 시점(t1)에서 원래의 한계값 a(이것은 디지털로 레지스터(21)에 파일되어 있다)는 값 B로 절환된다. 이 값 B는 상기 시점에서 출력측 A3으로 나타나는 카운터 상태를 웃돈다. 비교기(제2도)는 마찬가지로 시점(t1)에서 한계치 b쪽이 실제의 카운터 상태를 웃돌고 있음을 검출하고 따라서 출력신호를 송출하고 그것에 의해서 출력측 TV0에서의 신호가 “1”로 절환된다. 마찬가지로 해서 다른 비교기(22) 내지 (26)은 카운터(C<sub>1</sub>) 내지 (C<sub>3</sub>)과 공동하며 그 결과 출력측에서 상이한 키잉비 또는 듀티리시오가 있는 신호가 얻어진다.

제4도에는 입력측(10) 내지 (19)를 가지는 콤퍼레이터 회로 (2)가 부분적으로 비교적 상세하게 도시되어 있다. 기준전압 U<sub>B</sub>는 분압기 U<sub>D</sub> (이것은 2개의 저항 R<sub>1</sub>, R<sub>2</sub>로 된다)를 써서 기준전압 U<sub>R</sub>로 저감된다. 기준 전압 U<sub>R</sub>는 복수 콤퍼레이터 K의 부입력측에 가해지며 그것의 다른쪽의 입력측에는 측정신호라던가 절환신호등이 가해지며 이것들의 신호도 마찬가지로 분압기를 써서 비교적으로 낮은 값으로 저감되어 있다. 입력신호 E<sub>0</sub>는 예컨대 기관의 스타터리레이의 전압에 상응하며 한편, 입력신호(E1)은 자동차의 브레이크 등에 가해지는 전압에 상응한다. 이같이해서 자동차의 다수의 전기장치를 그 기능성의 정상이상 또는 그때마다의 작동상태에 대해서 감시할 수 있다. 콤퍼레이터 K의 입력측에 가해지는 상호 비교되어야할 전압은 마찬가지로 전지 전압에 의존하며 따라서 생기는 전지전압 변동을 받는다. 출력측(V<sub>0</sub>-V<sub>g</sub>)로부터 상태표시 특성신호가 데이터 선로 OD(제1도)로 송출된다.

제5도에 도시하는 블록접속도에는 특히 부가적 출력 레지스터(10)의 장치구성이 도시되어 있으며 제6도의 블록접속도에는 특히 부가적 준비 레지스터(9)의 장치구성이 도시되어 있다. 출력 레지스터(10)(출력래치)의 준비 입력측(래치 이네블)은 중앙 프로세서 유닛 CPU의 HSO 포트에 접속되어 있으며 이 CPU는 데이터 전송과 데이터를 출력포트를 거쳐서 제어한다. 부가회로(Z1)(제5도) 또는 확대된 부가회로 (Z2)(제6도)에 의해서 신속한 신호처리 및 전송을 가능하게 하는 HSO-출력측의 확대가 가능하다.

제5도 및 제6도의 회로장치의 기타의 장치 부분은 입력 인터페이스 E1, A-D 변환기 AD, 데코더 DC, 레지스터 L(래치), EPROM, RAM, 출력 레지스터(A1)로 된다. 그것들의 여러가지의 장치 부분은 복수의 데이터 선로 및 제어선로를 거쳐서 상호 접속되어 있다. 제7도에 도시하는 펄스다이어그램(IF1 내지 IF9)은 하기를 의미한다.

IP1 : 크랭크축 신호

IP2 : 캠축 신호

IP3 내지 IP8 : 6기통 기관의 6개의 점화선로상에 생기는 점화신호

IF9 : HSO 트리거 신호(하이스피드(고속) 출력 포트의 신호)

HS0 신호는 크랭크축에 동기 또는 기타의 형식으로 실시간신호를 이루는 트리거신호이다.

(1)로 도시하는 시점마다에 HSO-트리거신호(IP9)는 다음같이 변화한다. 즉 그 값이 (0)에서 (1)로 바뀌듯이 신호변화한다. 그것으로 출력 레지스터(10)의 출력측에는 이네블 레지스터(9)중에 비교적 조기에 써 넣어진 시점(1)에서의 점화선로(IP3 내지 IP8)의 상태를 나타내는 데이터가 나타난다. 이 과정은 CPU의 다른 양태의 인터럽트(끼어들기) 부하에 의해서 영향을 받지 않으며 이것으로써 정확하게 소정의 시점에서 행해진다. HSO 포트의 전위변화에 의해서는 마찬가지로 낮은 우선도의 인터럽트(끼어들기)가 트리거되며 그것으로 시점(1)로 행해지는 다른 인터럽트는 그 시퀀스로 저해되지 않도록 된다. 이 HSO-인터럽트는 시점(2)로부터 CPU에 의해 처리 된다. 이 시점에서 우선 출력리지스터(10)의 이네블 입력측(래치 이네블)의 전위가 (1)로부터 (0)으로 리셋되며 이어서 다른 점화시점을 나타내는 데이터가 준비 레지스터(9)중에 써 넣어진다. 이같은 준비 레지스터(9)로의 써 넣기가 실시간 프로그램의 실행에 있어서 경우에 따라 가일층 유리한 비교적 보다 뒤의 시점에서 행해질 수 있다. 단, 이 써 넣기는 출력 레지스터(10)의 래치 이네블 입력측에서 (0)에서 (1)로의 다음의 전위 변화전에 종료되어 있어야 한다.

이같이해서 복수의 결과의 정확한 출력이 오직 1개의 HSO 포트를 써서 가능해지며 그때, 제어 프로그램의 실시간 사이퀀스가 방해되는 일은 없다.

본 발명의 특허청구 범위 제 2 항 상위 개념에 의한 입·출력 회로장치에 있어서 변동 내지 슬라이드하는 기준전압을 사용함으로서 자동차에서 작동상태 및 온도에 의존해서 생기는 것같은 두드러지 작동전압변동이 있어도 입력측 아나로그 신호의 정확한 감시상 불리한 영향을 끼치지 않는다는 이점이 얻어진다. 기준전압은 발생하는 전지전압 변동, 변화에 따라서 더불어 변동 내지 슬라이드하고 그 결과 전지 전압이 설정값의 반분으로 저하되었을때에도 마찬가지로 그 전압값에 관해서 감시되어야 할 저하된 입력신호가 콤퍼레이터로 감시될 수 있다. 이것은 일정의 기준전압을 써서 종래 콤퍼레이터로는 불가능하다.

#### (57) 청구의 범위

**청구항 1**

규칙적으로 반복되는 문제를 취급개정하고, 다수의 제어출구를 갖고 있으며, 데이터 선로를 통하여 컴퓨터와 연결된 인터페이스를 갖고 있고, 상기 인터페이스에 접속되어 있는 출력 레지스터가 딸려 있는 마이크로세서용, 특히 자동차 제어 장치용 출력회로에 있어서, 상기 출력회로 (10)에 하나의 이네블레지스터(9)가 접속되어 있고, 상기 이네블레지스터(9)에는 마이크로세서(CPU)에 의해서 데이터들이 모아질수 있으며, 상기 이네블레지스터(9)에 파일된 상기 데이터들은 컴퓨터(CPU)에 의해 주어지는 신호(HSO-신호)를 바탕으로 상기 출력레지스터(10)로 전달될 수 있고, 상기 인터페이스(5)에서 없앨수 있으며, 상기 HSO-신호는 규칙적으로 반복되는 문제와 관련있는 것을 특징으로 하는 마이크로세서용 입·출력 회로장치.

**청구항 2**

제1항에 있어서, 상기 컴퓨터에 의해서 주어진 신호는 트리거 신호를 제공하며, 상기 트리거 신호를 크랭크축과 동시적으로 주어지는 것을 특징으로 하는 마이크로세서용 입·출력 회로 장치.

**청구항 3**

규칙적으로 반복되는 문제를 취급개정하고, 다수의 제어 출구를 갖고 있으며, 데이터 선로를 통하여 컴퓨터와 연결된 인터페이스를 갖고 있고, 상기 인터페이스에 접속되어 있는 출력 레지스터가 딸려 있는 마이크로세서용, 특히 자동차 제어 장치용 출력 회로에 있어서, 상기 출력레지스터에 이네블레지스터(17 내지 21)들이 접속되어 있고, 상기 이네블레지스터에는 마이크로세서(CPU)에 의해 데이터들이 모아질 수 있으며, 카운터(C1 내지 C3)의 계산상태가 상기 이네블레지스터에 입력된 수치와 같거나 또는 그 수치보다 크거나 작을 경우에는 상기 출력 레지스터는 접속이 바뀌게 되는 것을 특징으로 하는 마이크로세서용 입·출력 회로 장치.

**청구항 4**

제3항에 있어서, 하나의 카운터는 다수의 비교기에 연결되어 있으며, 상기 카운터(C1 내지 C3)의 클럭신호(CL)는 다양한 것을 특징으로 하는 마이크로세서용 입·출력 회로 장치.

**도면**

도면1

도면2

도면3

도면4

도면5

도면6

## 도면7