(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2019-0045909

(43) 공개일자 2019년05월03일

(51) 국제특허분류(Int. Cl.)

*H01L 27/12* (2006.01) *H01L 21/762* (2006.01)

*H01L 23/48* (2006.01) *H01L 23/522* (2006.01)

*H01L 23/66* (2006.01) *H01L 29/06* (2006.01)

*H01L 29/66* (2006.01) *H01L 29/78* (2006.01)

*H01L 29/786* (2006.01) *H01Q 1/24* (2006.01)

*H01Q 1/38* (2015.01)

(52) CPC특허분류

*H01L 27/1211* (2013.01)

*H01L 21/76251* (2013.01)

(21) 출원번호 10-2019-7006280

(22) 출원일자(국제) 2017년08월03일

심사청구일자 없음

(85) 번역문제출일자 2019년02월28일

(86) 국제출원번호 PCT/US2017/045349

(87) 국제공개번호 WO 2018/048529

국제공개일자 2018년03월15일

(30) 우선권주장

15/257,823 2016년09월06일 미국(US)

전체 청구항 수 : 총 25 항

(54) 발명의 명칭 백사이드 바디 콘택트를 갖는 딥 트렌치 능동 디바이스

### (57) 요 약

집적 회로는 게이트 평거들을 갖는 게이트를 포함할 수 있다. 집적 회로는 또한 게이트의 게이트 평거들과 서로 맞물리는 반도체 기둥들을 갖는 바디를 포함할 수 있다. 집적 회로는 또한 바디에 커플링된 백사이드 콘택트(들)를 포함할 수 있다. 집적 회로는 백사이드 금속배선을 더 포함할 수 있다. 백사이드 금속배선은 백사이드 콘택트(들)를 통해 바디에 커플링될 수 있다.

### 대 표 도

(52) CPC특허분류

*H01L 23/481* (2013.01)

*H01L 23/5223* (2013.01)

*H01L 23/66* (2013.01)

*H01L 29/0649* (2013.01)

*H01L 29/66795* (2013.01)

*H01L 29/7851* (2013.01)

*H01L 29/78615* (2013.01)

*H01Q 1/241* (2013.01)

*H01Q 1/38* (2018.05)

---

## 명세서

### 청구범위

#### 청구항 1

복수의 게이트 핑거들을 포함하는 게이트;

상기 복수의 게이트 핑거들과 서로 맞물리는 복수의 반도체 기둥들을 포함하는 바디;

상기 바디에 커플링된 적어도 하나의 백사이드 콘택트; 및

상기 적어도 하나의 백사이드 콘택트를 통해 상기 바디에 커플링된 백사이드 금속배선을 포함하는, 집적 회로.

#### 청구항 2

제1 항에 있어서,

상기 복수의 게이트 핑거들은 폴리실리콘 재료를 포함하는, 집적 회로.

#### 청구항 3

제1 항에 있어서,

상기 복수의 게이트 핑거들과 상기 복수의 반도체 기둥들 사이에 게이트 유전체를 더 포함하는, 집적 회로.

#### 청구항 4

제3 항에 있어서,

제1 플레이트로서 상기 복수의 게이트 핑거들, 제2 플레이트로서 상기 복수의 반도체 기둥들, 및 커패시터 유전체로서 상기 게이트 유전체를 포함하는 커패시터를 더 포함하는, 집적 회로.

#### 청구항 5

제1 항에 있어서,

상기 백사이드 콘택트는, 상기 바디와 상기 백사이드 금속배선 사이에 각각 커플링된 복수의 콘택트 플러그들을 포함하고, 상기 백사이드 금속배선은 상기 복수의 콘택트 플러그들에 직접 커플링되는, 집적 회로.

#### 청구항 6

제1 항에 있어서,

상기 백사이드 콘택트와 상기 바디 사이에 직접 백사이드 실리사이드를 더 포함하는, 집적 회로.

#### 청구항 7

제6 항에 있어서,

상기 백사이드 실리사이드는 상기 바디 상에 직접 복수의 이산적 엘리먼트들을 포함하거나, 또는 상기 백사이드 실리사이드는 상기 바디 상에 연속적 층을 포함하는, 집적 회로.

#### 청구항 8

제1 항에 있어서,

상기 게이트의 제1 사이드에 근접한 상기 바디의 제1 도핑된 영역; 및

상기 게이트의 상기 제1 사이드에 대향하는 제2 사이드에 근접한 상기 바디의 제2 도핑된 영역을 더 포함하는, 집적 회로.

#### 청구항 9

제8 항에 있어서,

상기 제1 도핑된 영역은 소스 영역이고 상기 제2 도핑된 영역은 드레인 영역인, 집적 회로.

#### 청구항 10

제1 항에 있어서,

매립된 산화물(BOX) 층; 및

상기 매립된 산화물 층을 지지하는 백사이드 유전체 층을 더 포함하고, 상기 바디는 상기 매립된 산화물 층을 통해 확장되고 상기 백사이드 유전체 층에 의해 지지되며, 상기 백사이드 콘택트 및 상기 백사이드 금속배선은 상기 백사이드 유전체 층에 있는, 집적 회로.

#### 청구항 11

제1 항에 있어서,

매립된 산화물(BOX) 층; 및

상기 매립된 산화물 층을 지지하는 백사이드 유전체 층을 더 포함하고, 상기 바디는 상기 매립된 산화물까지 확장되고, 상기 백사이드 콘택트는 상기 바디 및 상기 백사이드 금속배선에 커플링하도록 상기 매립된 산화물 층까지 확장되는, 집적 회로.

#### 청구항 12

제1 항에 있어서,

매립된 산화물 층 – 이를 통해 상기 게이트의 제1 부분이 확장되고, 상기 제1 부분은 상기 복수의 게이트 평거들에 커플링됨 –; 및

상기 매립된 산화물 층을 지지하는 백사이드 유전체 층을 더 포함하는, 집적 회로.

#### 청구항 13

제1 항에 있어서,

RF(radio frequency) 프론트 엔드 모듈에 통합되며, 상기 RF 프론트 엔드 모듈은 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 내비게이션 디바이스, 통신 디바이스, PDA(personal digital assistant), 고정 위치 데이터 유닛, 모바일 폰 및 휴대용 컴퓨터 중 적어도 하나에 통합되는, 집적 회로.

#### 청구항 14

복수의 반도체 기둥들을 포함하는 바디를 형성하기 위해 절연 층 내의 반도체 층을 에칭하는 단계;

상기 절연 층의 프론트-사이드 표면 상에 및 상기 복수의 반도체 기둥들의 표면 상에 유전체 재료 층을 증착하는 단계;

복수의 게이트 평거들을 포함하는 게이트를 형성하기 위해 상기 유전체 재료 층 상에 및 상기 복수의 반도체 기둥들을 분리하는 복수의 트렌치들에 반도체 재료를 증착하는 단계 – 상기 복수의 게이트 평거들은 상기 복수의 반도체 기둥들과 서로 맞물림 –;

상기 절연 층의 상기 프론트-사이드 표면 상의 프론트-사이드 유전체 층에 핸들 기판을 본딩하는 단계; 및

상기 절연 층의 백사이드 표면을 지지하는 백사이드 유전체 층에 백사이드 금속배선을 제조하는 단계를 포함하고, 상기 백사이드 금속배선은 적어도 하나의 백사이드 콘택트를 통해 상기 바디에 커플링되는, 집적 회로를 구성하는 방법.

#### 청구항 15

제14 항에 있어서,

상기 반도체 재료를 증착하는 단계는, 상기 복수의 게이트 평거들을 포함하는 게이트를 형성하기 위해 상기 유

전체 재료 층 상에 및 상기 복수의 반도체 기동들을 분리하는 상기 복수의 트렌치들에 폴리실리콘 재료를 증착하는 단계를 포함하는, 집적 회로를 구성하는 방법.

### 청구항 16

제14 항에 있어서,

상기 백사이드 콘택트와 상기 바디 사이에 직접 백사이드 실리사이드를 증착하는 단계를 더 포함하는, 집적 회로를 구성하는 방법.

### 청구항 17

제16 항에 있어서,

상기 백사이드 실리사이드를 복수의 이산적 엘리먼트들로서, 상기 바디 상에 직접 또는 상기 바디 상에 연속적 층으로서 증착하는 단계를 더 포함하는, 집적 회로를 구성하는 방법.

### 청구항 18

제14 항에 있어서,

상기 게이트의 제1 사이드에 근접한 상기 바디의 제1 도핑된 영역을 도핑하는 단계; 및

상기 게이트의 상기 제1 사이드에 대향하는 제2 사이드에 근접한 상기 바디의 제2 도핑된 영역을 도핑하는 단계를 더 포함하는, 집적 회로를 구성하는 방법.

### 청구항 19

제14 항에 있어서,

상기 반도체 재료를 증착하는 단계는 매립된 산화물 층을 통해 확장되는 상기 게이트의 제1 부분을 증착하는 단계를 더 포함하고, 상기 게이트의 제1 부분은 상기 복수의 게이트 핑거들에 커플링되는, 집적 회로를 구성하는 방법.

### 청구항 20

제14 항에 있어서,

상기 집적 회로를 RF(radio frequency) 프론트 엔드 모듈에 집적하는 단계를 더 포함하고, 상기 RF 프론트 엔드 모듈은 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 내비게이션 디바이스, 통신 디바이스, PDA(personal digital assistant), 고정 위치 데이터 유닛, 모바일 폰 및 휴대용 컴퓨터 중 적어도 하나에 통합되는, 집적 회로를 구성하는 방법.

### 청구항 21

복수의 게이트 핑거들을 포함하는 게이트;

상기 복수의 게이트 핑거들과 서로 맞물리는 복수의 반도체 기동들을 포함하는 바디;

상기 바디에 커플링된 적어도 하나의 백사이드 콘택트; 및

상기 적어도 하나의 백사이드 콘택트를 통해 상기 바디를 연결하기 위한 수단을 포함하는, 집적 회로.

### 청구항 22

제21 항에 있어서,

상기 게이트의 제1 사이드에 근접한 상기 바디의 제1 도핑된 영역; 및

상기 게이트의 상기 제1 사이드에 대향하는 제2 사이드에 근접한 상기 바디의 제2 도핑된 영역을 더 포함하는, 집적 회로.

### 청구항 23

제21 항에 있어서,

RF(radio frequency) 프론트 엔드 모듈에 통합되며, 상기 RF 프론트 엔드 모듈은 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 내비게이션 디바이스, 통신 디바이스, PDA(personal digital assistant), 고정 위치 데이터 유닛, 모바일 폰 및 휴대용 컴퓨터 중 적어도 하나에 통합되는, 집적 회로.

#### 청구항 24

복수의 게이트 평거들을 포함하는 게이트 및 상기 복수의 게이트 평거들과 서로 맞물리는 복수의 반도체 기둥들을 포함하는 바디를 포함하는 딥 트렌치 스위치 트랜지스터, 상기 바디에 커플링되는 적어도 하나의 백사이드 콘택트, 및 상기 적어도 하나의 백사이드 콘택트를 통해 상기 바디에 커플링되는 백사이드 금속배선을 포함하는 집적 RF(radio frequency) 회로; 및

상기 스위치 트랜지스터의 출력에 커플링되는 안테나를 포함하는, RF 프론트 엔드 모듈.

#### 청구항 25

제24 항에 있어서,

뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 내비게이션 디바이스, 통신 디바이스, PDA(personal digital assistant), 고정 위치 데이터 유닛, 모바일 폰 및 휴대용 컴퓨터 중 적어도 하나에 통합되는, RF 프론트 엔드 모듈.

### 발명의 설명

#### 기술 분야

[0001]

[0001] 본 개시는 일반적으로 IC(integrated circuit)들에 관한 것이다. 더 구체적으로, 본 개시는 백사이드 바디 콘택트를 갖는 딥 트렌치(deep trench) 능동 디바이스에 관한 것이다.

#### 배경 기술

[0002]

[0002] 고성능 디아플렉서(diplexer)들을 포함하는 모바일 RF(radio frequency) 칩 설계들(예를 들어, 모바일 RF 트랜시버들)은 비용 및 전력 소비 고려사항들로 인해 딥 서브-마이크론(deep sub-micron) 프로세스 노드로 이동해왔다. 이러한 모바일 RF 트랜시버들의 설계는 이러한 딥 서브-마이크론 프로세스 노드에서 복잡해진다. 이러한 모바일 RF 트랜시버들의 설계 복잡도는 캐리어 어그리게이션과 같은 통신 향상들을 지원하기 위해 추가된 회로 기능들에 의해 추가로 복잡하게 된다. 모바일 RF 트랜시버들에 대한 추가적인 설계 난제들은 매스매치, 잡음 및 다른 성능 고려사항들과 같은 아날로그/RF 성능 고려사항들을 포함한다. 이러한 모바일 RF 트랜시버들의 설계는 예를 들어, 공진을 억제하고 그리고/또는 필터링, 우회 및 커플링을 수행하기 위해, 추가적인 수동 디바이스들의 사용을 포함한다.

[0003]

[0003] 이러한 모바일 RF 트랜시버들의 설계는 SOI(silicon on insulator) 기술의 사용을 포함할 수 있다. SOI 기술은 기생 디바이스 커패시턴스를 감소시키고 성능을 개선하기 위해 종래의 실리콘 기판들을 계층화된 실리콘-절연체-실리콘 기판으로 대체한다. SOI-기반 디바이스들은 종래의 실리콘-구축 디바이스들과 상이한데, 이는 실리콘 접합이 통상적으로 BOX(buried oxide) 층인 전기 절연체 위에 있기 때문이다. 그러나, 감소된 두께의 BOX 층은 BOX 층을 지지하는 기판과 실리콘 층 상의 능동 디바이스의 근접도에 의해 초래되는 기생 커패시턴스를 충분히 감소시키지 않을 수 있다.

[0004]

[0004] 불행하게도, SOI 기술을 사용하여 제조된 트랜지스터는 일반적으로 플로팅 바디(floating body) 효과를 겪고, 여기서 트랜지스터의 바디는 절연된 기판에 대해 커패시터를 형성한다. 이러한 어레인지먼트에서, 커패시터 상에 누적된 전하는 악영향들, 예를 들어, 구조에서의 기생 트랜지스터들 및 오프-상태 누설 뿐만 아니라 이의 이전 상태들에 대한 트랜지스터의 임계 전압의 의존도를 초래한다. 플로팅 바디 효과는 특히 아날로그 디바이스들에서 극심한데, 여기서 임계 전압 제어 및 바디 충전 제어는 플로팅 바디 효과에 의해 방지된다. 플로팅 바디 효과를 방지하기 위해 바디 콘택트가 사용될 수 있다. 불행하게도, 바디 콘택트의 사용은 영역 패널티를 초래한다.

### 발명의 내용

[0005] [0005] 집적 회로는 게이트 평거들을 갖는 게이트를 포함할 수 있다. 집적 회로는 또한 게이트의 게이트 평거들과 서로 맞물리는 반도체 기둥들을 갖는 바디를 포함할 수 있다. 집적 회로는 또한 바디에 커플링된 백사이드 콘택트(들)를 포함할 수 있다. 집적 회로는 백사이드 금속배선을 더 포함할 수 있다. 백사이드 금속배선은 백사이드 콘택트(들)를 통해 바디에 커플링될 수 있다.

[0006] [0006] 집적 회로를 구성하는 방법은 반도체 기둥들을 포함하는 바디를 형성하기 위해 절연 층 내의 반도체 층을 에칭하는 단계를 포함할 수 있다. 방법은 또한 절연 층의 프론트-사이드 표면 상에 및 반도체 기둥들의 표면 상에 유전체 재료 층을 증착하는 단계를 포함할 수 있다. 방법은 반도체 기둥들과 서로 맞물리는 게이트 평거들을 포함하는 게이트를 형성하기 위해, 유전체 재료 층 상에 및 반도체 기둥들을 분리하는 트렌치를 내에 반도체 재료를 증착하는 단계를 더 포함할 수 있다. 방법은 또한 절연 층의 프론트-사이드 유전체 층에 핸들 기판을 본딩하는 단계를 포함할 수 있다. 방법은 절연 층의 백사이드 표면을 지지하는 백사이드 유전체 층에 백사이드 금속배선을 제조하는 단계를 더 포함할 수 있다. 백사이드 금속배선은 백사이드 콘택트(들)를 통해 바디에 커플링될 수 있다.

[0007] [0007] 집적 회로는 게이트 평거들을 갖는 게이트를 포함할 수 있다. 집적 회로는 또한 게이트의 게이트 평거들과 서로 맞물리는 반도체 기둥들을 갖는 바디를 포함할 수 있다. 집적 회로는 또한 바디에 커플링된 백사이드 콘택트(들)를 포함할 수 있다. 집적 회로는 백사이드 콘택트(들)를 통해 바디를 연결하기 위한 수단을 더 포함할 수 있다.

[0008] [0008] RF(radio frequency) 프론트 엔드 모듈은 집적 RF 회로를 포함할 수 있다. 집적 RF 회로는 게이트 평거들을 포함하는 게이트를 갖는 딥 트렌치 스위치 트랜지스터를 포함할 수 있다. 집적 RF 회로는 또한 게이트 평거들과 서로 맞물리는 반도체 기둥들을 갖는 바디를 포함할 수 있다. 집적 RF 회로는 바디에 커플링된 백사이드 콘택트(들) 및 백사이드 콘택트(들)를 통해 바디에 커플링된 백사이드 금속배선을 더 포함할 수 있다. RF 프론트 엔드 모듈은 또한 스위치 트랜지스터의 출력에 커플링된 안테나를 포함할 수 있다.

[0009] [0009] 이것은, 후속하는 상세한 설명이 더 양호하게 이해될 수 있게 하기 위해, 본 개시의 특성들 및 기술적 이점들을 다소 광범위하게 약술하였다. 본 개시의 부가적인 특성들 및 이점들은 후술될 것이다. 본 개시가 본 개시의 동일한 목적들을 수행하기 위해 다른 구조들을 변경 또는 설계하기 위한 기반으로서 용이하게 이용될 수 있다는 것이 당업자들에 의해 인식되어야 한다. 또한, 그러한 등가 구성들이 첨부된 청구항들에 기재된 바와 같은 본 개시의 교시를 벗어나지 않는다는 것이 당업자들에 의해 인식되어야 한다. 추가적인 목적들 및 이점들과 함께, 본 개시의 구성 및 동작 방법 둘 모두에 대해 본 개시의 특징인 것으로 믿어지는 신규한 특성들은, 첨부한 도면들과 관련하여 고려될 경우 다음의 설명으로부터 더 양호하게 이해될 것이다. 그러나, 각각의 도면들은 오직 예시 및 설명의 목적으로 제공되며, 제시된 개시들의 제한들에 대한 정의로 의도되지 않음을 명시적으로 이해해야 한다.

## 도면의 간단한 설명

[0010] [0010] 본 개시의 더 철저한 이해를 위해, 이제 첨부된 도면들과 함께 취해지는 하기 설명이 참조된다.

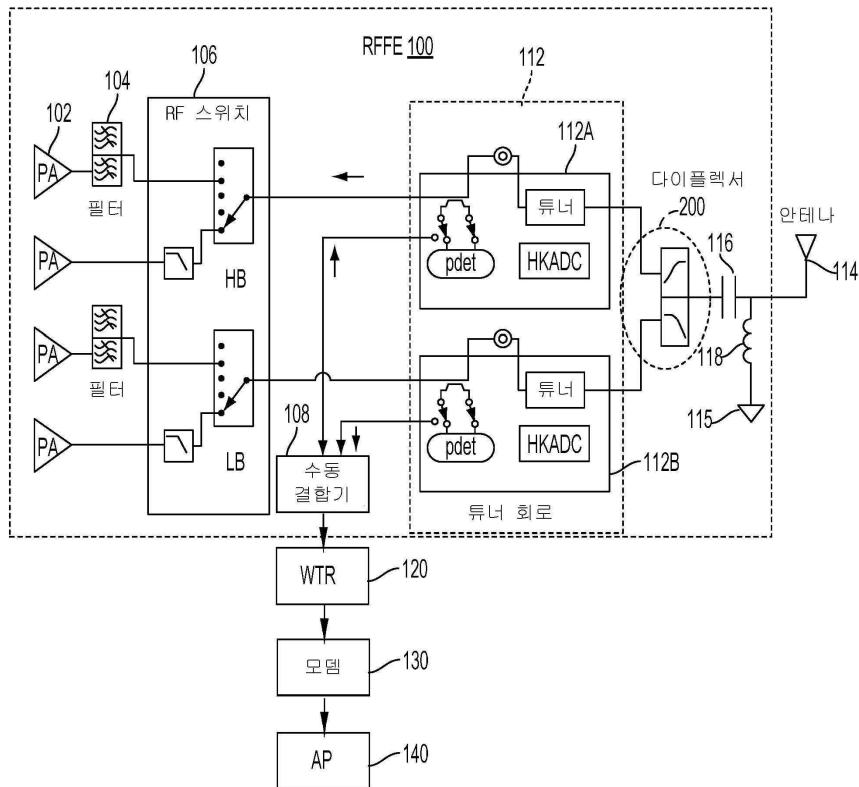

[0011] 도 1a는 본 개시의 양상에 따른 다이플렉서를 이용하는 RF FE(radio frequency (RF) front end) 모듈의 개략도이다.

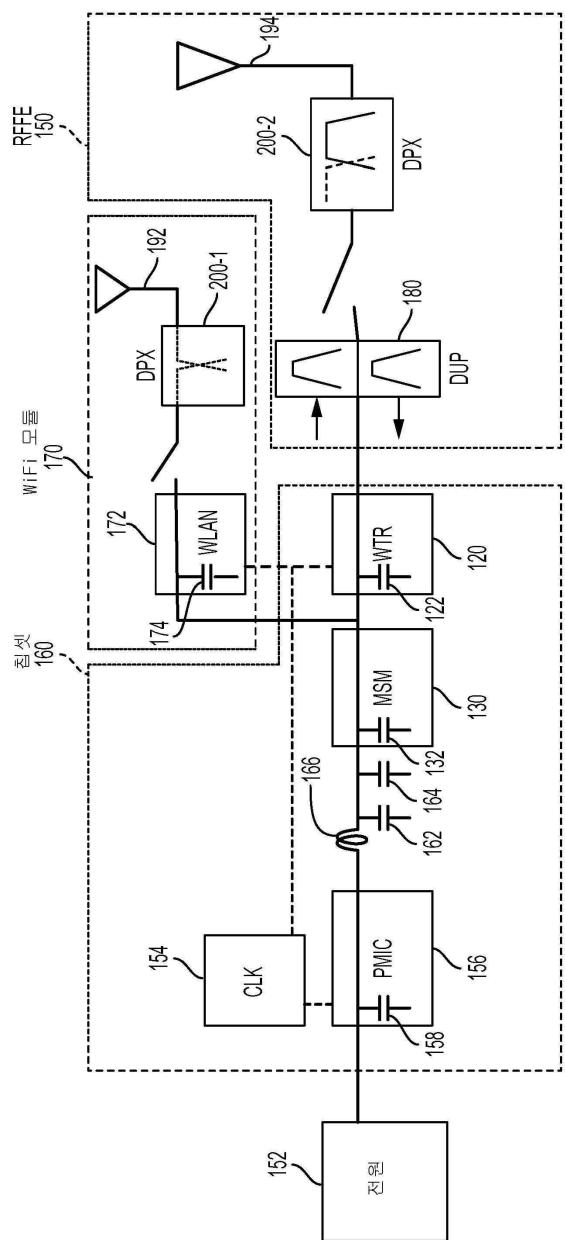

[0012] 도 1b는 본 개시의 양상들에 따른 캐리어 어그리게이션을 제공하기 위한 칩셋에 대해 다이플렉서들을 이용하는 RF FE(radio frequency (RF) front end) 모듈의 개략도이다.

[0013] 도 2a는 본 개시의 양상에 따른 다이플렉서 설계의 도면이다.

[0014] 도 2b는 본 개시의 양상에 따른 RF(radio frequency) 프론트 엔드 모듈의 도면이다.

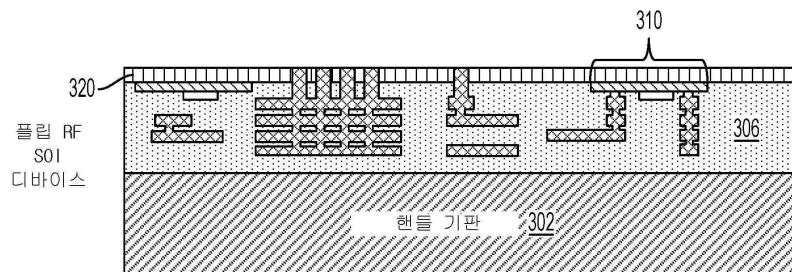

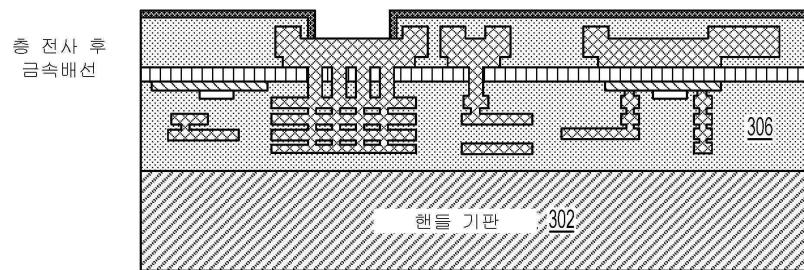

[0015] 도 3a 내지 도 3e는 본 개시의 양상들에 따른 총 전자 프로세스 동안 집적 RF(radio frequency) 회로 구조의 단면도들을 도시한다.

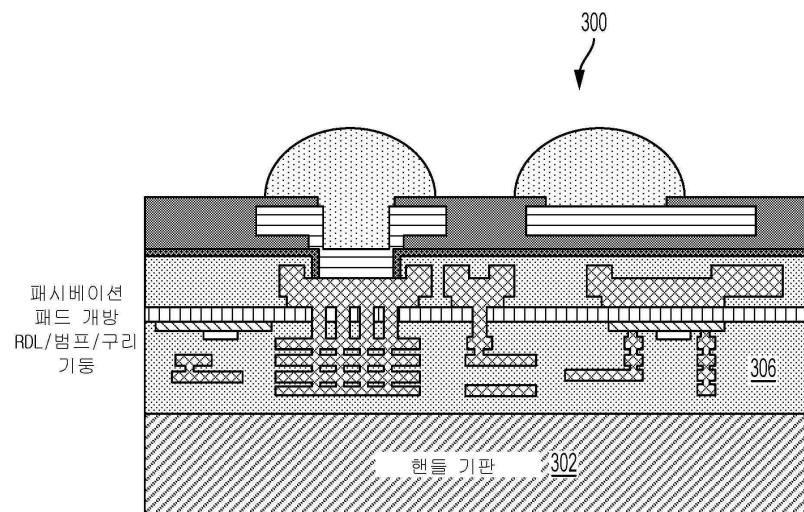

[0016] 도 4는 본 개시의 양상들에 따른 총 전자 프로세스를 사용하여 제조된 집적 RF(radio frequency) 회로 구조의 단면도이다.

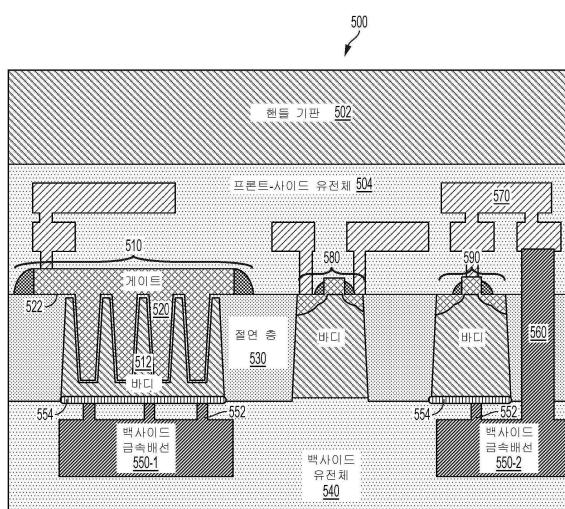

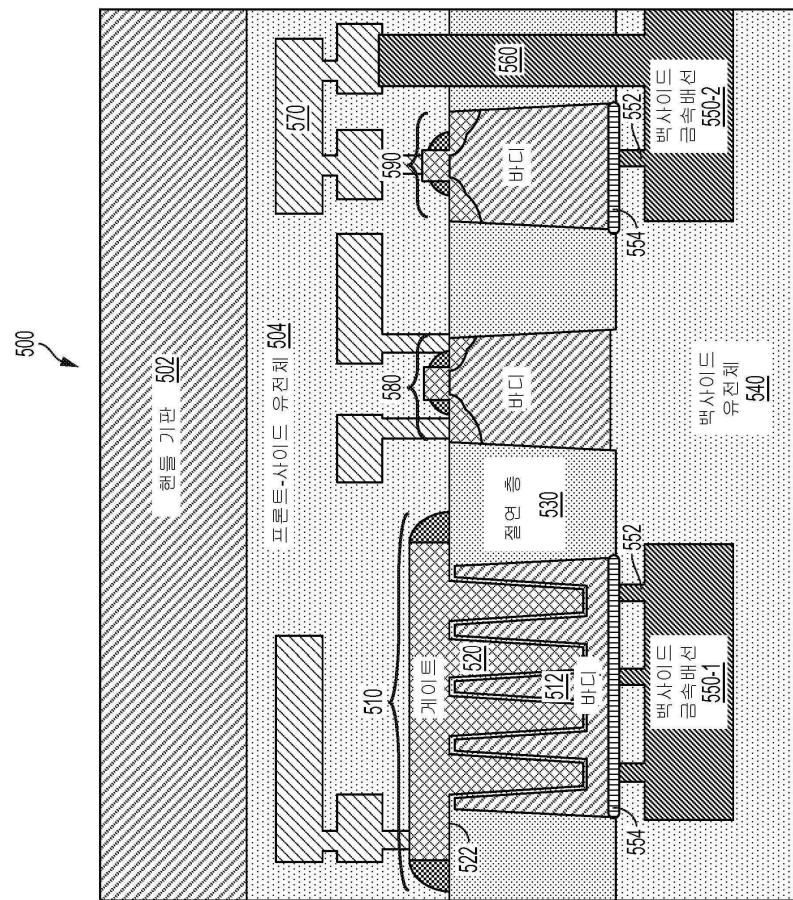

[0017] 도 5는 본 개시의 양상에 따른 백사이드 바디 콘택트를 갖는 딥 트렌치 능동 디바이스를 포함하는 집적 회로 구조의 단면도이다.

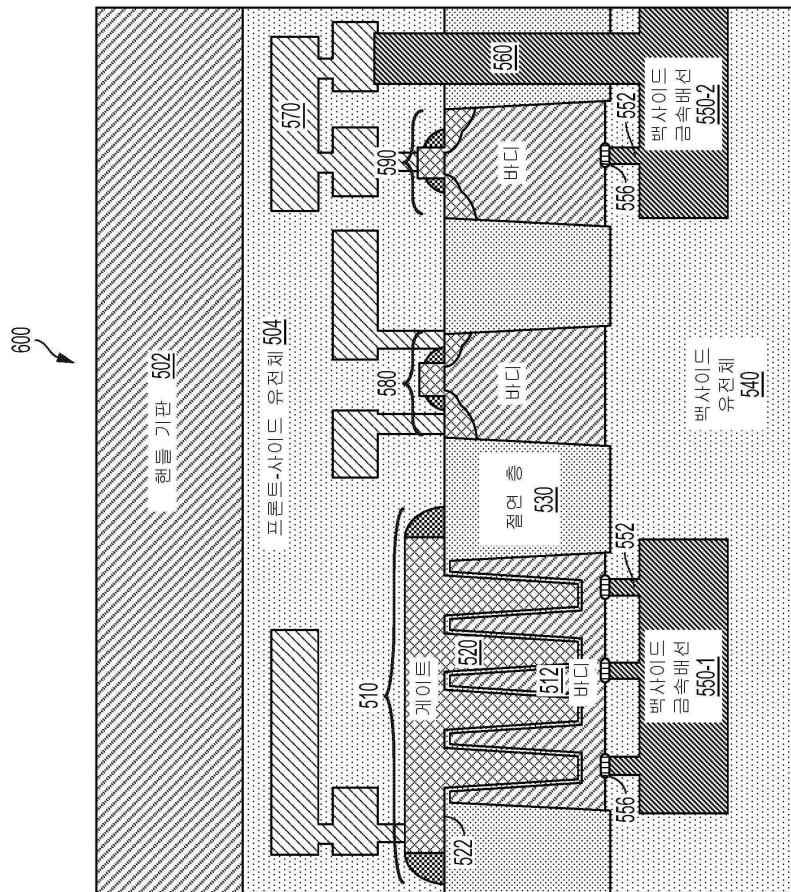

[0018] 도 6은 본 개시의 다른 양상에 따른 백사이드 바디 콘택트를 갖는 딥 트렌치 능동 디바이스를 포함하는 집적 회로 구조의 단면도이다.

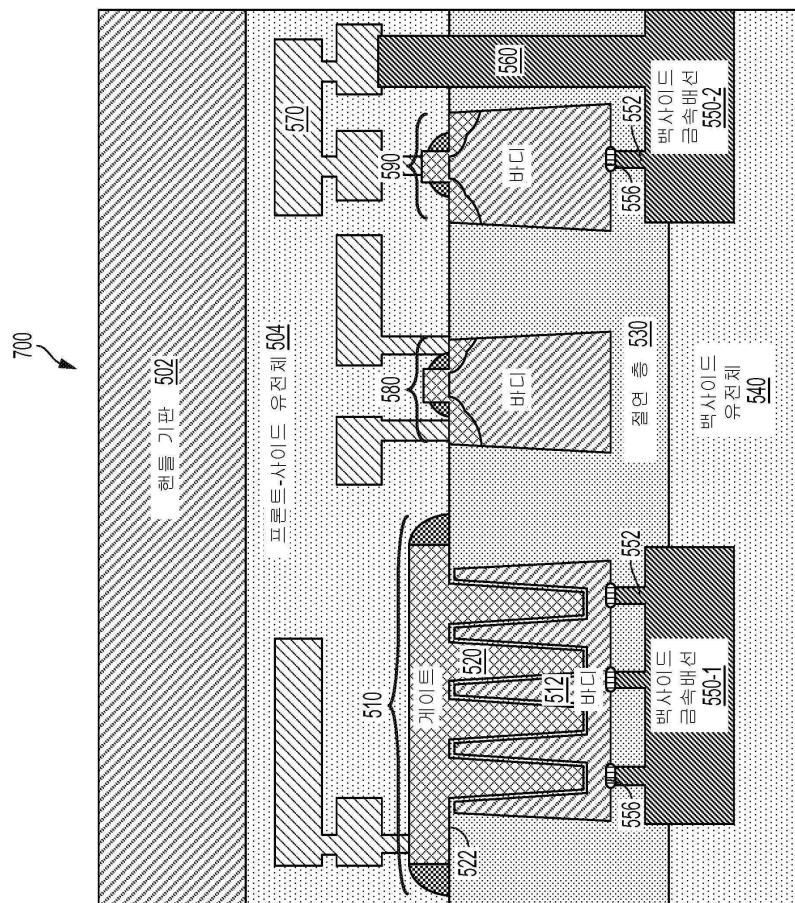

[0019] 도 7은 본 개시의 추가적 양상에 따른 백사이드 바디 콘택트를 갖는 딥 트렌치 능동 디바이스를 포함하는 집적 회로 구조의 단면도이다.

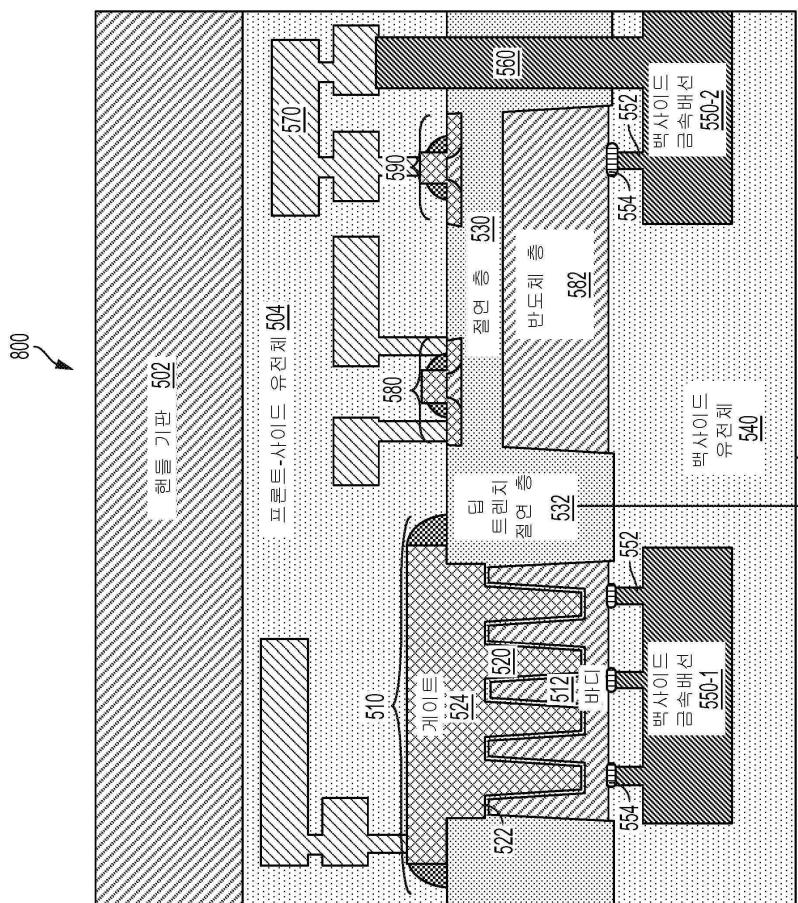

[0020] 도 8은 본 개시의 다른 양상에 따른 백사이드 바디 콘택트를 갖는 딥 트렌치 능동 디바이스를 포함하는 집적 회로 구조의 단면도이다.

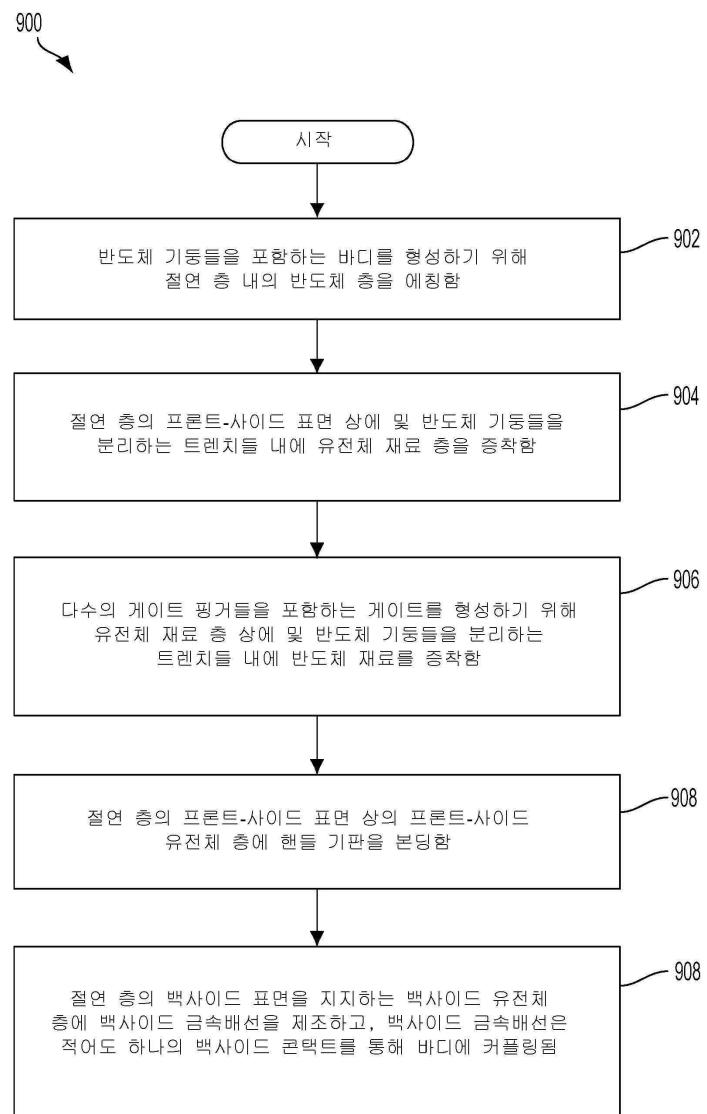

[0021] 도 9는 본 개시의 양상에 따른 백사이드 바디 콘택트를 갖는 딥 트렌치 능동 디바이스를 포함하는 집적 회로 구조를 구성하는 방법을 예시하는 프로세스 흐름도이다.

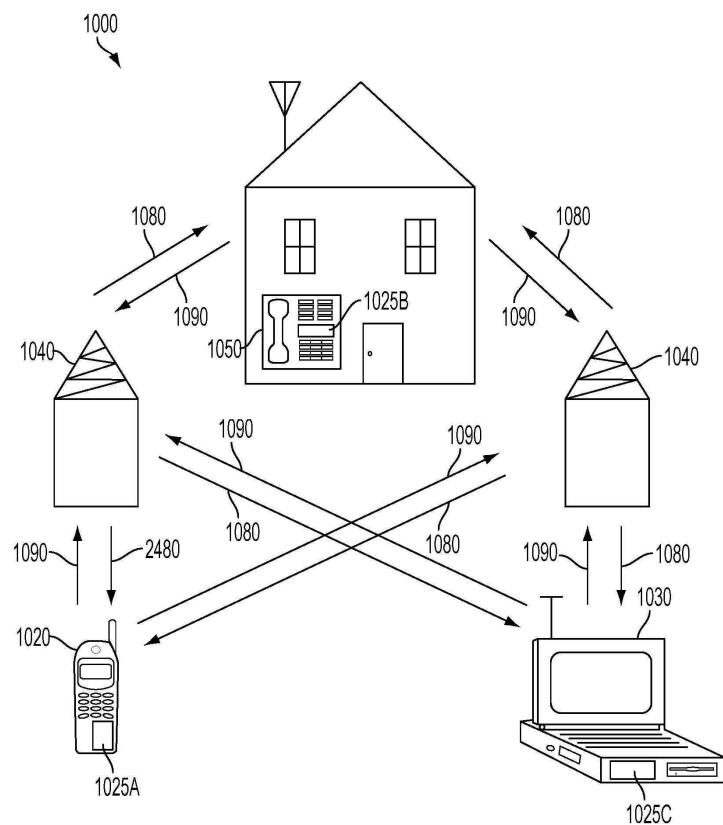

[0022] 도 10은 본 개시의 구성이 유리하게 이용될 수 있는 예시적인 무선 통신 시스템을 도시하는 블록도이다.

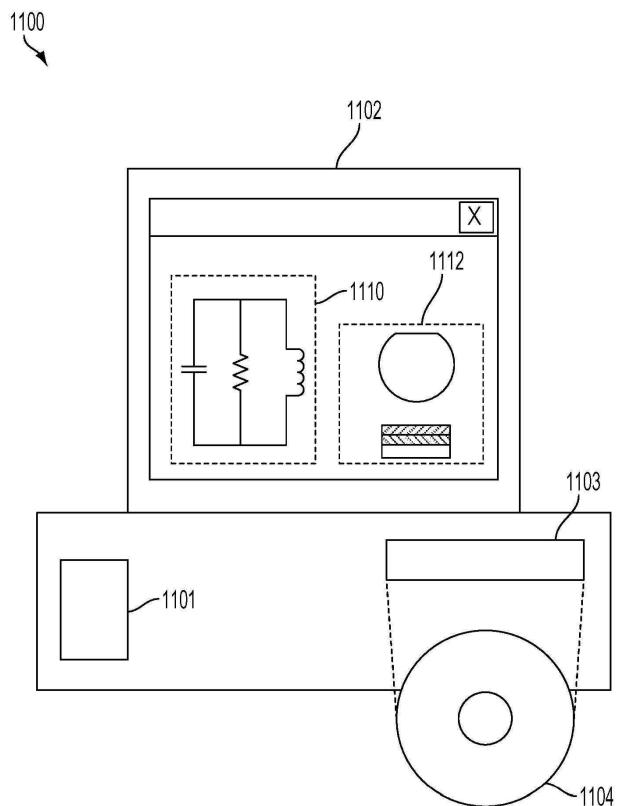

[0023] 도 11은 일 구성에 따른 반도체 컴포넌트의 회로, 레이아웃 및 로직 설계에 사용되는 설계 워크스테이션을 예시하는 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0011] [0024] 첨부 도면들과 관련하여 아래에 기술되는 상세한 설명은 다양한 구성들의 설명으로 의도되며, 본 명세서에서 설명된 개념들이 실시될 수 있는 유일한 구성들을 표현하도록 의도되는 것은 아니다. 상세한 설명은 다양한 개념들의 철저한 이해를 제공할 목적으로 특정 세부사항들을 포함한다. 그러나, 이러한 특정 세부사항들 없이도 이러한 개념들이 실시될 수 있음을 당업자들에게 자명할 것이다. 일부 예들에서, 이러한 개념들을 불명료하게 하는 것을 피하기 위해, 잘 알려진 구조들 및 컴포넌트들은 블록도 형태로 도시된다. 본 명세서에 설명된 바와 같이, "및/또는"이라는 용어의 사용은 "포함적 논리합(inclusive OR)"을 표현하도록 의도되고, "또는"이라는 용어의 사용은 "배타적 논리합(exclusive OR)"을 표현하도록 의도된다.

[0012] [0025] 모바일 RF(radio frequency) 칩 설계들(예를 들어, 모바일 RF 트랜시버들)은 비용 및 전력 소비 고려사항들로 인해 딥 서브-마이크론 프로세스 노드로 이동해왔다. 모바일 RF 트랜시버들의 설계 복잡도는 캐리어 어그리게이션과 같은 통신 향상들을 지원하기 위해 추가된 회로 기능들에 의해 추가로 복잡하게 된다.

[0013] [0026] 이러한 모바일 RF 트랜시버들의 설계는 SOI(silicon on insulator) 기술의 사용을 포함할 수 있다. SOI 기술은 기생 디바이스 커패시턴스를 감소시키고 성능을 개선하기 위해 종래의 실리콘 기판들을 계층화된 실리콘-절연체-실리콘 기판으로 대체한다. SOI-기반 디바이스들은 종래의 실리콘-구축 디바이스들과 상이한데, 이는 실리콘 접합이 통상적으로 BOX(buried oxide) 층인 전기 절연체 위에 있기 때문이며, 여기서 BOX 층의 두께는 감소될 수 있다. 그러나, 감소된 두께의 BOX 층은 BOX 층을 지지하는 기판과 실리콘 층 상의 능동 디바이스의 근접도에 의해 초래되는 기생 커패시턴스를 충분히 감소시키지 않을 수 있다.

[0014] [0027] SOI 기술을 사용하여 제조된 트랜지스터는 일반적으로 플로팅 바디(floating body) 효과를 겪고, 여기서 트랜지스터의 바디는 절연된 기판에 대해 커패시터를 형성한다. 이러한 어레인지먼트에서, 커패시터 상에 누적된 전하는 악영향들, 예를 들어, 구조에서의 기생 트랜지스터들 및 오프-상태 누설 뿐만 아니라 이의 이전 상태들에 대한 트랜지스터의 임계 전압의 의존도를 초래한다. 플로팅 바디 효과는 특히 아날로그 디바이스들에서 극심한데, 여기서 임계 전압 제어 및 바디 충전 제어는 플로팅 바디 효과에 의해 방지된다. 플로팅 바디 효과를 방지하기 위해 바디 콘택트가 사용될 수 있다. 불행하게도, 바디 콘택트의 사용은 영역 패널티를 초래한다. 그 결과, 본 개시의 양상들은 딥 트렌치 능동 디바이스에 대한 백사이드 바디 연결의 형성을 가능하게 하는 충전사 후 프로세스(post-layer transfer process)를 포함한다.

[0015] [0028] 집적 회로 구조의 반도체 제조에 대한 프로세스 흐름은 FEOL(front-end-of-line) 프로세스들, MOL(middle-of-line)(또한, MEOL(middle-end-of-line)로 지칭됨) 프로세스들 및 BEOL(back-end-of-line) 프로세스들을 포함할 수 있다. FEOL 프로세스는 이온 주입, 어닐링, 산화, CVD(chemical vapor deposition) 또는 ALD(atomic layer deposition) 예칭, CMP(chemical mechanical polishing), 에피택시를 포함한다. MOL 프로세스들은 BEOL 상호연결부들에 대한 트랜지스터들의 연결을 가능하게 하는 프로세스 단계들의 세트를 포함할 수 있다. 이러한 단계들은 실리시레이션(silicidation) 및 콘택트 형성 뿐만 아니라 응력 도입을 포함한다. BEOL 프로세스들은 독립적 트랜지스터들을 연결하고 회로들을 형성하는 상호연결부를 형성하는 프로세스 단계들의 세트를 포함할 수 있다.

[0016] [0029] 본 개시의 양상들은 고품질(Q)-팩터 RF(radio frequency) 애플리케이션들에 대한 집적 RF 회로 구조들에

서 안테나 스위치 트랜지스터로서 사용될 수 있는 백사이드 바디 콘택트를 갖는 딥 트렌치 스위치 트랜지스터를 설명한다. 일 구성에서, 층 전사 전 프로세스(pre-layer transfer process)가 딥 트렌치 트랜지스터를 형성한다. 또한, 층 전사 후 프로세스는 딥 트렌치 스위치 트랜지스터의 바디를 연결하는 백사이드 바디 콘택트를 형성한다. 백사이드 바디 연결을 형성하는 층 전사 후 프로세스는 종래의 바디 콘택트들과 연관된 영역 패널티 또는 원치 않는 저항 경로들을 회피하면서 딥 스위치 트랜지스터의 바디가 부동하는 것을 방지함으로써 SOI 디바이스들과 연관된 플로팅 바디 효과 문제를 해결한다.

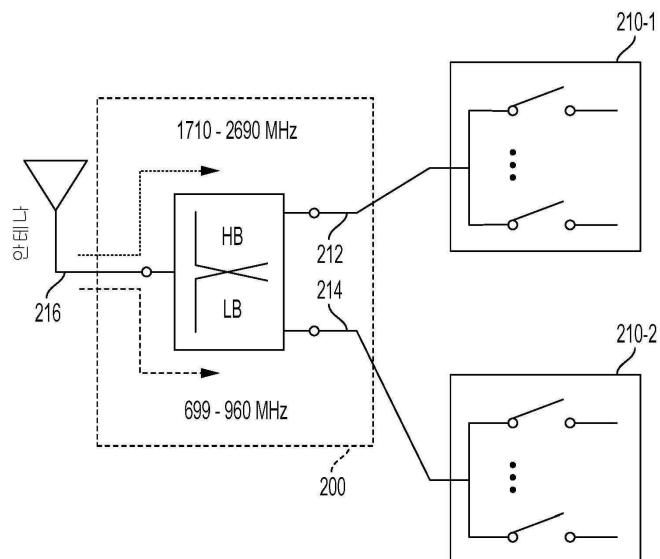

[0017] [0030] 도 1a는 본 개시의 양상에 따른 다이플렉서(200)를 이용하는 RFFE(radio frequency (RF) front end) 모듈(100)의 개략도이다. RF 프론트 엔드 모듈(100)은 전력 증폭기들(102), 듀플렉서/필터들(104), 및 RF(radio frequency) 스위치 모듈(106)을 포함한다. 전력 증폭기들(102)은 신호(들)를 송신을 위한 특정 전력 레벨로 증폭한다. 듀플렉서/필터들(104)은 주파수, 삽입 손실, 거부 또는 다른 유사한 파라미터들을 포함하는 다양한 상이한 파라미터들에 따라 입력/출력 신호들을 필터링한다. 또한, RF 스위치 모듈(106)은 RF 프론트 엔드 모듈(100)의 나머지 상에 전달할 입력 신호들의 특정 부분들을 선택할 수 있다.

[0018] [0031] RF 프론트 엔드 모듈(100)은 또한 투너 회로(112)(예를 들어, 제1 투너 회로(112A) 및 제2 투너 회로(112B)), 다이플렉서(200), 커패시터(116), 인덕터(118), 접지 단자(115) 및 안테나(114)를 포함한다. 투너 회로(112)(예를 들어, 제1 투너 회로(112A) 및 제2 투너 회로(112B))는 투너, PDET(portable data entry terminal) 및 HKADC(house keeping analog to digital converter)와 같은 컴포넌트들을 포함한다. 투너 회로(112)는 안테나(114)에 대한 임피던스 투닝(예를 들어, VSWR(voltage standing wave ratio) 최적화)을 수행할 수 있다. RF 프론트 엔드 모듈(100)은 또한 WTR(wireless transceiver)(120)에 커플링된 수동 결합기(108)를 포함한다. 수동 결합기(108)는 제1 투너 회로(112A) 및 제2 투너 회로(112B)로부터 검출된 전력을 결합한다. 무선 트랜시버(120)는 수동 결합기(108)로부터 정보를 프로세싱하고 이러한 정보를 모뎀(130)(예를 들어, MSM(mobile station modem))에 제공한다. 모뎀(130)은 AP(application processor)(140)에 디지털 신호를 제공한다.

[0019] [0032] 도 1a에 도시된 바와 같이, 다이플렉서(200)는 투너 회로(112)의 투너 컴포넌트와 커패시터(116), 인덕터(118) 및 안테나(114) 사이에 있다. 다이플렉서(200)는 무선 트랜시버(120), 모뎀(130) 및 애플리케이션 프로세서(140)를 포함하는 칩셋에 RF 프론트 엔드 모듈(100)로부터의 높은 시스템 성능을 제공하기 위해 안테나(114)와 투너 회로(112) 사이에 배치될 수 있다. 다이플렉서(200)는 또한 고대역 주파수들 및 저대역 주파수들을 모두에 대해 주파수 도메인 멀티플렉싱을 수행한다. 다이플렉서(200)가 입력 신호들에 대해 자신의 주파수 멀티플렉싱 기능들을 수행한 후, 다이플렉서(200)의 출력은 커패시터(116) 및 인덕터(118)를 포함하는 선택적 LC(인덕터/커패시터) 네트워크에 공급된다. LC 네트워크는 원하는 경우 안테나(114)에 대한 여분의 임피던스 매칭 컴포넌트들을 제공할 수 있다. 그 다음, 특정 주파수를 갖는 신호가 안테나(114)에 의해 송신되거나 수신된다. 단일 커패시터 및 인덕터가 도시되어 있지만, 다수의 컴포넌트들이 또한 고려된다.

[0020] [0033] 도 1b는 본 개시의 양상에 따른 캐리어 어그리게이션을 제공하기 위해 칩셋(160)에 대한 제1 다이플렉서(200-1)를 포함하는 WLAN(wireless local area network)(예를 들어, WiFi) 모듈(170) 및 제2 다이플렉서(200-2)를 포함하는 RF 프론트 엔드 모듈(150)의 개략도이다. WiFi 모듈(170)은 무선 로컬 영역 네트워크 모듈(예를 들어, WLAN 모듈(172))에 안테나(192)를 통신가능하게 커플링하는 제1 다이플렉서(200-1)를 포함한다. RF 프론트 엔드 모듈(150)은 듀플렉서(180)를 통해 WTR(wireless transceiver)(120)에 안테나(194)를 통신가능하게 커플링하는 제2 다이플렉서(200-2)를 포함한다. 무선 트랜시버(120) 및 WiFi 모듈(170)의 WLAN 모듈(172)은 PMIC(power management integrated circuit)(156)를 통해 전원(152)에 의해 전력공급되는 모뎀(MSM, 예를 들어, 기저대역 모뎀)(130)에 커플링된다. 칩셋(160)은 또한 신호 무결성을 제공하기 위해 커패시터들(162 및 164) 뿐만 아니라 인덕터(들)(166)를 포함한다. PMIC(156), 모뎀(130), 무선 트랜시버(120) 및 WLAN 모듈(172) 각각은 커패시터들(예를 들어, 158, 132, 122 및 174)을 포함하고 클럭(154)에 따라 동작한다. 칩셋(160)의 다양한 인덕터 및 커패시터 컴포넌트들의 기하구조 및 어레인지먼트는 컴포넌트들 사이의 전자기 커플링을 감소시킬 수 있다.

[0021] [0034] 도 2a는 본 개시의 양상에 따른 다이플렉서(200)의 도면이다. 다이플렉서(200)는 HB(high band) 입력 포트(212), LB(low band) 입력 포트(214) 및 안테나(216)를 포함한다. 다이플렉서(200)의 고대역 경로는 고대역 안테나 스위치(210-1)를 포함한다. 다이플렉서(200)의 저대역 경로는 저대역 안테나 스위치(210-2)를 포함한다. RF 프론트 엔드 모듈을 포함하는 무선 디바이스는 무선 디바이스의 RF 입력 및 RF 출력에 대한 광범위 대역을 가능하게 하기 위해 안테나 스위치들(210) 및 다이플렉서(200)를 사용할 수 있다. 또한, 안테나(216)는 MIMO(multiple input, multiple output) 안테나일 수 있다. 다중 입력, 다중 출력 안테나들은 캐리어 어그리

케이션과 같은 특징들을 지원하기 위해 무선 디바이스들의 RF 프론트 엔드에 널리 사용될 것이다.

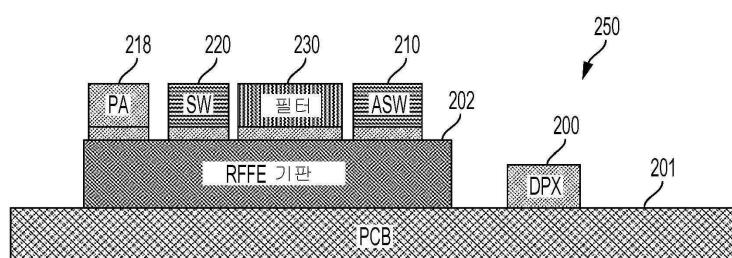

- [0022] [0035] 도 2b는 본 개시의 양상에 따른 RF 프론트 엔드 모듈(250)의 도면이다. RF 프론트 엔드 모듈(250)은 도 2a에서 언급된 광범위 대역을 가능하게 하기 위해 ASW(antenna switch)(210) 및 디이플렉서(200)(또는 트리플렉서)를 포함한다. 또한, RF 프론트 엔드 모듈(250)은 필터들(230), RF 스위치(220) 및 기판(202)에 의해 지원되는 전력 증폭기들(218)을 포함한다. 필터들(230)은, RF 프론트 엔드 모듈(250)에서 고차 고조파들을 방지하기 위해 디이플렉서, 트리플렉서, 저역 통과 필터들, 밸룬(balun) 필터들 및/또는 노치 필터들을 형성하기 위해 기판(202)과 함께 배열된 인덕터들(L) 및 커패시터들(C)을 갖는 다양한 LC 필터들을 포함할 수 있다. 디이플렉서(200)는 시스템 보드(201)(예를 들어, PCB(printed circuit board) 또는 패키지 기판) 상에 SMD(surface mount device)로서 구현될 수 있다. 대안적으로, 디이플렉서(200)는 기판(202) 상에 구현될 수 있다.

- [0023] [0036] 이러한 구성에서, RF 프론트 엔드 모듈(250)은 RF 프론트 엔드 모듈(250)에서 고차 고조파들을 감소시키는 것을 돋는 SOI(silicon on insulator) 기술을 사용하여 구현된다. SOI 기술은 기생 디바이스 커패시턴스를 감소시키고 성능을 개선하기 위해 종래의 실리콘 기판들을 계층화된 실리콘-절연체-실리콘 기판으로 대체한다. SOI-기반 디바이스들은 종래의 실리콘-구축 디바이스들과 상이한데, 이는 실리콘 접합이 통상적으로 BOX(buried oxide) 층인 전기 절연체 위에 있기 때문이다. 그러나, 감소된 두께의 BOX 층은 BOX 층을 지지하는 기판과 (실리콘 층 상의) 능동 디바이스 사이의 근접도에 의해 초래되는 기생 커패시턴스를 충분히 감소시키지 않을 수 있다. 그 결과, 본 개시의 양상들은 도 3a 내지 도 3e에 도시된 바와 같이, 기판으로부터 능동 디바이스를 추가로 분리시키는 층 전사 프로세스를 포함한다.

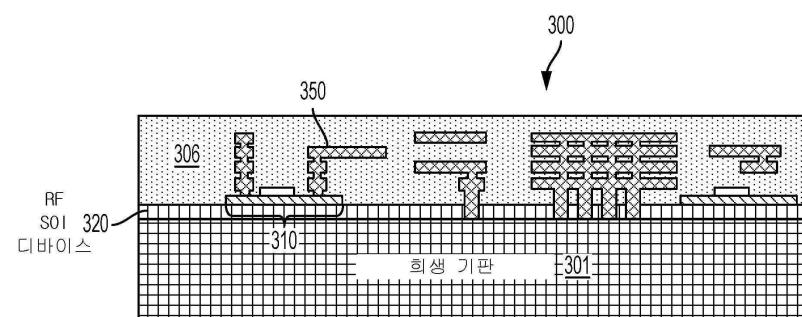

- [0024] [0037] 도 3a 내지 도 3e는 본 개시의 양상들에 따른 층 전사 프로세스 동안 접적 RF(radio frequency) 회로 구조(300)의 단면도들을 도시한다. 도 3a에 도시된 바와 같이, RF SOI(silicon on insulator) 디바이스는 회생 기판(301)(예를 들어, 벌크 웨이퍼)에 의해 지지되는 BOX(buried oxide) 층(320) 상에 능동 디바이스(310)를 포함한다. RF SOI 디바이스는 또한 제1 유전체 층(306) 내의 능동 디바이스(310)에 커플링된 상호연결부들(350)을 포함한다. 도 3b에 도시된 바와 같이, 핸들 기판(302)은 제1 유전체 층(306)에 본딩된다.

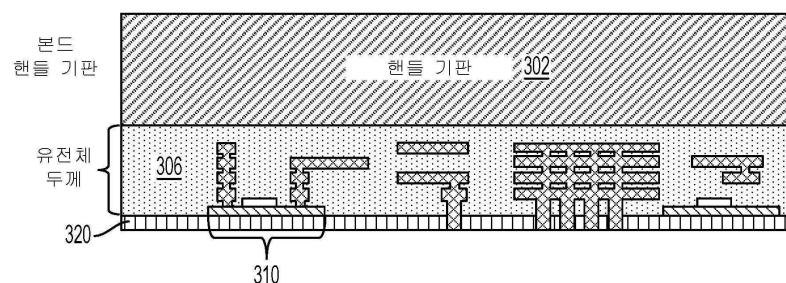

- [0025] [0038] 도 3b에 도시된 바와 같이, 핸들 기판(302)은 RF SOI 디바이스의 프론트-사이드 유전체 층(306)에 본딩된다. 또한, 회생 기판(301)이 제거된다. 층 전사 프로세스를 사용한 회생 기판(301)의 제거는 유전체 두께를 증가시킴으로써 고성능, 저-기생 RF 디바이스들을 가능하게 한다. 즉, RF SOI 디바이스의 기생 커패시턴스는 유전체 두께에 비례하고, 이는 능동 디바이스(310)와 핸들 기판(302) 사이의 거리를 결정한다.

- [0026] [0039] 도 3c에 도시된 바와 같이, RF SOI 디바이스는 핸들 기판(302)이 고정되고 회생 기판(301)이 제거되면 플립(flip)된다. 도 3d에 도시된 바와 같이, 층 전사 후 금속배선 프로세스는 예를 들어, 정규의 CMOS(complementary metal oxide semiconductor) 프로세스를 사용하여 수행된다. 도 3e에 도시된 바와 같이, 접적 RF 회로 구조(300)는 패시베이션 층을 증착하고, 본드 패드들을 개방하고, 재분포 층을 증착하고, 접적 RF 회로 구조(300)의 시스템 보드(예를 들어, PCB(printed circuit board))에의 본딩을 가능하게 하기 위해 전도성 범프들/기둥들을 형성함으로써 완료된다.

- [0027] [0040] 도 3a를 다시 참조하면, RF SOI 디바이스는 회생 기판(301)과 BOX 층(320) 사이에 트랩 풍부 층을 포함할 수 있다. 또한, 회생 기판(301)은 핸들 기판(302)으로 대체될 수 있고, BOX 층(320)의 두께는 고조파들을 개선하기 위해 증가될 수 있다. RF SOI 디바이스의 이러한 어레인지먼트는 순수 실리콘 또는 SOI 구현에 비해 개선된 고조파들을 제공할 수 있지만, RF SOI 디바이스는 특히 실리콘 핸들 기판이 사용되는 경우 핸들 기판으로부터의 비선형 응답들에 의해 제한된다. 즉, 도 3a에서, BOX 층(320)의 증가된 두께는 도 3b 내지 도 3e에 도시된 구성들에 비해 능동 디바이스(310)와 회생 기판(301) 사이에 충분한 거리를 제공하지 않는다. 또한, RF SOI 디바이스는 일반적으로 SOI 층의 일 사이드 상의 CMOS 트랜지스터 형성으로 제한된다.

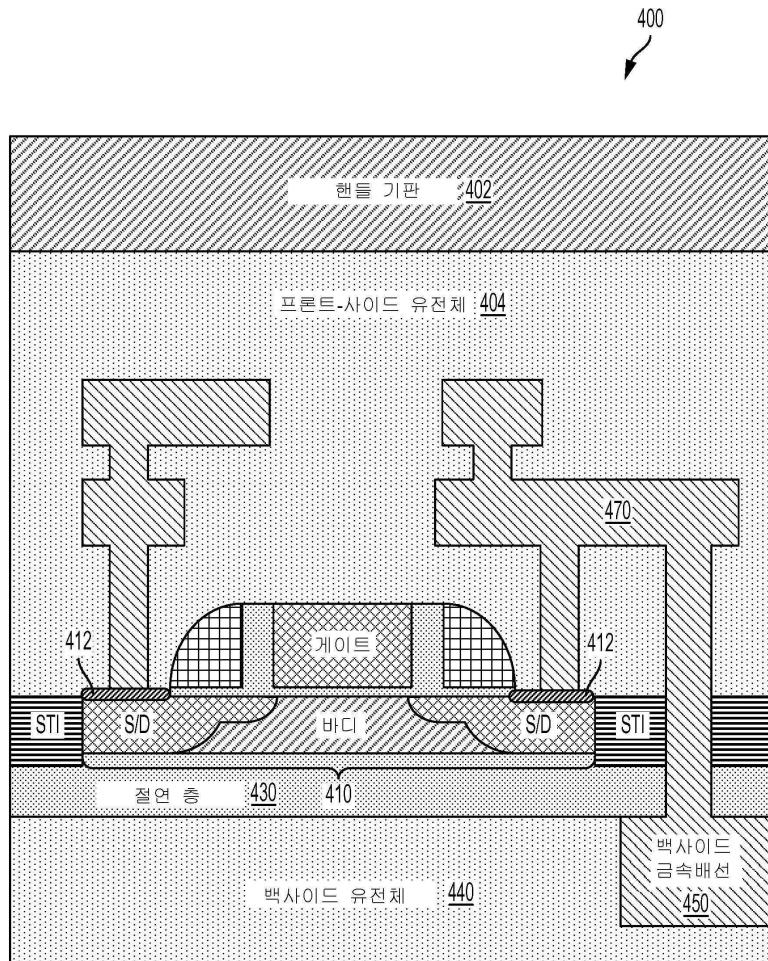

- [0028] [0041] 도 4는 본 개시의 양상들에 따른 층 전사 프로세스를 사용하여 제조된 접적 RF 회로 구조(400)의 단면도이다. 대표적으로, 접적 RF 회로 구조(400)는 절연 층(430) 상에 형성된 게이트, 바디 및 소스/드레인 영역들을 갖는 능동 디바이스(410)를 포함한다. SOI(silicon on insulator) 구현들에서, 절연 층(430)은 BOX(buried oxide) 층이고, 바디 및 소스/드레인 영역들은 BOX 층에 의해 지원되는 STI(shallow trench isolation) 영역들을 포함하는 SOI 층으로부터 형성된다.

- [0029] [0042] 접적 RF 회로 구조(400)는 또한 능동 디바이스(410)의 소스/드레인 영역들에 커플링된 MEOL(middle-end-of-line)/BEOL(back-end-of-line) 상호연결부들을 포함한다. 설명된 바와 같이, MEOL/BEOL 층들은 프론트-사이드 층들로 지칭된다. 반대로, 절연 층(430)을 지지하는 층들은 백사이드 층들로 지칭될 수 있다. 이러한

명명법에 따라, 프론트-사이드 상호연결부(470)는 프론트-사이드 유전체 층(404)의 프론트-사이드 콘택트들(412)을 통해 능동 디바이스(410)의 소스/드레인 영역들에 커플링된다. 또한, 핸들 기판(402)은 프론트-사이드 유전체 층(404)에 커플링된다. 이러한 구성에서, 백사이드 유전체(440)는 절연 층(430)에 인접하고 가능하게는 이를 지지한다. 또한, 백사이드 금속배선(450)은 프론트-사이드 상호연결부(470)에 커플링된다.

[0043] 도 4에 도시된 바와 같이, 층 전사 프로세스는 집적 RF 회로 구조(400)의 고조파들을 개선하기 위해 능동 디바이스(410)와 핸들 기판(402) 사이의 분리를 증가시킨다. 층 전사 프로세스는 고성능 저-기생 RF 디바이스들을 가능하게 하는 한편, 집적 RF 회로 구조(400)는 플로팅 바디 효과를 겪을 수 있다. 즉, SOI 기술을 사용하여 제조된 능동 디바이스들은 일반적으로 플로팅 바디 효과를 겪고, 여기서 트랜지스터의 바디는 절연된 기판에 대해 커패시터를 형성한다. 플로팅 바디 효과는 특히 아날로그 디바이스들에서 극심한데, 여기서 임계 전압 제어 및 바디 충전 제어는 플로팅 바디 효과에 의해 방지된다. 플로팅 바디 효과를 방지하기 위해 바디 콘택트가 사용될 수 있다. 불행하게도, 바디 콘택트의 사용은 상당한 영역 패널티를 초래한다. 그 결과, 본 개시의 양상들은 딥 트렌치 능동 디바이스에 대한 백사이드 바디 연결의 형성을 가능하게 하는 층 전사 후 프로세스(post-layer transfer process)를 포함한다.

[0044] 본 개시의 다양한 양상들은 집적 회로 구조에 대해 백사이드 바디 연결의 형성을 가능하게 하는 층 전사 후 프로세스를 위한 기술들을 제공한다. 반대로, FEOL(front-end-of-line) 프로세스 동안 형성된 능동 디바이스들에 대한 액세스는 종래에, 능동 디바이스들의 게이트들 및 소스/드레인 영역들과 BEOL(back-end-of-line) 상호연결부 층들(예를 들어, M1, M2 등) 사이의 콘택트들을 제공하는 MEOL(middle-end-of-line) 프로세스 동안 제공된다. 본 개시의 양상들은 고품질(Q)-팩터 RF(radio frequency) 애플리케이션들에 대한 집적 RF 회로 구조들에서 안테나 스위치 트랜지스터들로서 사용될 수 있는 백사이드 바디 연결들을 갖는 딥 트렌치 스위치 트랜지스터들을 형성하기 위한 층 전사 후 프로세스를 수반한다. 다른 애플리케이션들은 낮은 전력 증폭기 모듈, 저 잡음 증폭기 및 안테나 다이버시티 스위치 내의 능동 디바이스를 포함한다.

[0045] 도 5는 본 개시의 양상들에 따른 백사이드 바디 연결을 갖는 딥 트렌치 능동 디바이스(예를 들어, 스위치 트랜지스터)를 포함하는 집적 회로 구조(500)의 단면도이다. 본 개시의 양상들에서, 층 전사 후 프로세스는 백사이드 바디 연결의 형성을 가능하게 하고, 이는 절연체 제조 프로세스들 상의 종래의 실리콘과 연관된 플로팅 바디 효과를 해결한다. 대표적으로, 집적 회로 구조(500)는 절연 층(530)의 프론트-사이드 표면 상에서 절연 층(530)의 백사이드 표면까지 확장되는 딥 트렌치 능동 디바이스(510)를 포함한다. 이러한 구성에서, 딥 트렌치 능동 디바이스(510)의 바디는 반도체 층(예를 들어, SOI 구현을 위한 실리콘)으로부터 형성된 반도체 기둥들(512)로 구성된다. 기둥들은 더 작은 영역에서 더 긴 길이가 획득되는 한(예를 들어, "아코디언" 효과) 근접하게 이격될 필요가 없다. 또한, 게이트는 반도체 기둥들(512)과 서로 맞물리고 유전체 재료 층(522)(예를 들어, 게이트 유전체)에 의해 분리되고 절연 층(530)을 통해 확장되는 게이트 평거들(520)로 구성된다.

[0046] 절연 층(530)은 SOI(silicon on insulator) 구현을 위한 BOX(buried oxide) 층일 수 있고, 여기서 바디 및 소스/드레인 영역들(미도시)은 SOI 층으로부터 형성된다. 대안적으로, 절연 층(530)은 딥 트렌치 능동 디바이스(510)를 제1 트렌치-타입 능동 디바이스(580) 및 제2 트렌치-타입 능동 디바이스(590)로부터 절연하는 딥 트렌치 분리 영역일 수 있다. 제1 트렌치-타입 능동 디바이스(580) 및 제2 트렌치-타입 능동 디바이스(590)에 관한 추가적인 세부사항들은 본 개시의 세부사항들을 모호하게 하는 것을 회피하기 위해 생략된다. 또한, 트렌치-타입 스위치 트랜지스터들은 딥 트렌치 스위치 트랜지스터의 드레인 영역 및 소스 영역을 제공하기 위해 n-타입(예를 들어, 제1 도핑된 영역) 및 p-타입(예를 들어, 제2 도핑된 영역) 반도체 영역들을 도핑하기 위한 주입 프로세스에 따라, NMOS(negative metal oxide semiconductor) 스위치 트랜지스터들 또는 포지티브 MOS(PMOS 트랜지스터들)로서 구성될 수 있다.

[0047] 본 개시의 이러한 양상에서, 집적 회로 구조(500)는 또한 절연 층(530)의 프론트-사이드 표면에 대향하는 백사이드 표면을 지지하는 백사이드 유전체 층(540)에 배열된 백사이드 금속배선(550)을 포함한다. 본 개시의 양상들에 따른 백사이드 금속배선(550)은 딥 트렌치 능동 디바이스(510)에 대한 낮은 저항 바디 연결을 제공한다. 이러한 어레인지먼트에서, 백사이드 금속배선(550)의 제1 부분(550-1)은 콘택트 플러그들(552) 및 백사이드 실리사이드 층(554)을 통해 딥 트렌치 능동 디바이스(510)의 바디에 전기적으로 커플링된다. 딥 트렌치 능동 디바이스(510)의 이러한 구성은 백사이드 금속배선(550)을 바디에 전기적으로 커플링함으로써 플로팅 바디 효과를 방지한다.

[0048] 집적 회로 구조(500)는 또한 프론트-사이드 유전체 층(504)에 배열된 프론트-사이드 금속배선(570)(예를 들어, 제1 BEOL 상호연결부(M1))을 포함한다. 프론트-사이드 금속배선(570)은 비아(560)를 통해 백사이드 금속

배선(550)의 제2 부분(550-2)에 커플링된다. 백사이드 유전체 층(540) 내의 백사이드 금속배선(550)의 제2 부분(550-2)은 콘택트 플러그들(552) 및 백사이드 실리사이드 층(554) 중 하나를 통해 제2 트렌치-타입 능동 디바이스(590)의 바디에 전기적으로 커플링된다. 또한, 핸들 기판(502)은 프론트-사이드 유전체 층(504)에 커플링된다. 백사이드 유전체 층(540)는 절연 층(530)에 인접하고 가능하게는 이를 지지한다. 이러한 구성에서, 층 전사 후 금속배선 프로세스는 백사이드 금속배선(550)을 형성한다. 도 5에 도시된 바와 같이, 프론트-사이드 금속배선(570)은 백사이드 금속배선(550)으로부터 원위에 배열된다.

[0036] [0049] 본 개시의 양상들에 따르면, 핸들 기판(502)은 실리콘과 같은 반도체 재료로 구성될 수 있다. 이러한 구성에서, 핸들 기판(502)은 적어도 하나의 다른 능동 디바이스를 포함할 수 있다. 대안적으로, 핸들 기판(502)은 기생 커패시턴스를 감소시킴으로써 고조파들을 추가로 개선하기 위한 수동 기판일 수 있다. 이러한 구성에서, 핸들 기판(502)은 적어도 하나의 다른 수동 디바이스를 포함할 수 있다. 본원에서 설명된 바와 같이, "수동 기판"이라는 용어는 다이싱된 웨이퍼 또는 패널의 기판을 지칭할 수 있거나 또는 다이싱되지 않은 웨이퍼/패널의 기판을 지칭할 수 있다. 일 구성에서, 수동 기판은 유리, 공기, 석영, 사파이어, 높은 비저항 실리콘 또는 다른 유사한 수동 재료로 구성된다. 수동 기판은 또한 코어리스(coreless) 기판일 수 있다.

[0037] [0050] "층"이라는 용어는 막을 포함하고, 달리 언급되지 않으면 수직 또는 수평 두께를 표시하는 것으로 해석되지 않아야 하는 것으로 이해될 것이다. 본원에서 설명된 바와 같이, "기판"이라는 용어는 다이싱된 웨이퍼의 기판을 지칭할 수 있거나 또는 다이싱되지 않은 웨이퍼의 기판을 지칭할 수 있다. 유사하게, 칩 및 다이라는 용어들은 상호교환이 논리에 맞는다면 상호교환가능하게 사용될 수 있다.

[0038] [0051] 본 개시의 양상들에서, 층 전사 후 프로세스는 도 5 내지 도 8에 도시된 바와 같이, 트렌치-타입 능동 디바이스들의 바디를 연결하기 위한 백사이드 금속배선을 형성한다. 백사이드 실리시레이션 프로세스에서의 변경들은 도 7 및 도 8에 도시되어 있다. 또한, 반도체 층(예를 들어, 실리콘 온 절연체 층)에 대한 변경들은 도 7 및 도 8에 도시되어 있다. 본 개시의 추가적 양상에 따르면, 딥 트렌치 능동 디바이스(510)는 MOS(metal oxide semiconductor) 커패시터로 구성될 수 있다. 이러한 어레인지먼트에서, MOS 커패시터는 제1 플레이트로서 게이트 평거들(520), 제2 플레이트로서 반도체 기둥들(512) 및 커패시터 유전체로서 유전체 재료 층(522)을 포함한다.

[0039] [0052] 도 6은 본 개시의 양상들에 따른 백사이드 바디 연결을 갖는 트렌치-타입 능동 디바이스를 포함하는 집적 회로 구조(600)의 단면도이다. 인식될 바와 같이, 집적 회로 구조(600)의 구성은 도 5의 집적 회로 구조(500)의 구성과 유사하다. 그러나, 도 6에 도시된 구성에서, 딥 트렌치 능동 디바이스(510)의 바디의 부분들을 노출시키기 위한 실리사이드 홀들을 형성하기 위해 백-엔드-오브-라인 비아 프로세스(back-end-of-line via process)(V0)가 사용된다. 즉, 이러한 어레인지먼트에서, 백사이드 실리사이드 층(554)(도 5)은 도 5에 도시된 실리사이드 연속적 층보다 딥 트렌치 능동 디바이스(510)의 바디의 노출된 부분들 상에 이산적 엘리먼트들로서 증착된다. 또한, 백사이드 실리사이드 층(554)(도 5)은 제2 트렌치-타입 능동 디바이스(590)의 바디의 노출된 부분 상에 이산 엘리먼트들로서 증착된다.

[0040] [0053] 따라서, 본 개시의 이러한 양상은 또한, 트렌치 타입 능동 디바이스들의 바디를 연결하기 위한 단순화된 층 전사 후 프로세스 백사이드 실리시레이션 프로세스를 제공함으로써 종래의 실리콘 온 절연체 제조 프로세스들과 연관된 플로팅 바디 효과 문제를 해결한다. 도 6에 도시된 구성은 예를 들어, 도 7에 도시된 바와 같이 SOI 웨이퍼보다 벌크 웨이퍼를 사용하여 제조됨을 인식해야 한다.

[0041] [0054] 도 7은 본 개시의 양상들에 따른 백사이드 바디 연결을 갖는 트렌치-타입 능동 디바이스를 포함하는 집적 회로 구조(700)의 단면도이다. 인식될 바와 같이, 집적 회로 구조(700)의 구성은 도 6의 집적 회로 구조(600)의 구성과 유사하다. 그러나, 도 7에 도시된 구성에서, 증가된 두께 반도체 층은 SOI 웨이퍼에 의해 지지되는 실리콘 온 절연체(SOI) 층으로서 제공된다. 이러한 어레인지먼트에서, 절연 층(530)은 딥 트렌치 능동 디바이스(510)와 제1 트렌치-타입 능동 디바이스(580) 및 제2 트렌치-타입 능동 디바이스(590) 사이의 딥 트렌치 절연 층일 수 있다.

[0042] [0055] 이러한 어레인지먼트에 따르면, 딥 트렌치 능동 디바이스(510)의 바디는 또한 절연 층(530)에 의해 지지된다. 콘택트 플러그들(552)은 절연 층(530)의 일부를 통해 확장된다. 또한, 백사이드 금속배선(550)의 제1 부분(550-1) 및 제2 부분(550-2)은 딥 트렌치 능동 디바이스(510) 및 제2 트렌치-타입 능동 디바이스(590)를 연결하기 위해 절연 층(530)의 일부 및 백사이드 유전체 층(540)의 일부에 형성된다. 따라서, 본 개시의 이러한 양상은 종래의 실리콘 온 절연체 제조 프로세스들과 연관된 플로팅 바디 효과 문제를 해결한다.

[0043]

[0056] 도 8은 본 개시의 양상들에 따른 백사이드 바디 연결을 갖는 트렌치-타입 능동 디바이스를 포함하는 집적 회로 구조(800)의 단면도이다. 인식될 바와 같이, 집적 회로 구조(800)의 구성은 도 6의 집적 회로 구조(600)의 구성과 유사하다. 그러나, 도 8에 도시된 구성에서, 감소된 두께 반도체 층은 SOI 웨이퍼에 의해 지지되는 실리콘 온 절연체(SOI) 층으로서 제공된다. 이러한 어레인지먼트에서, 절연 층(530)은 딥 트렌치 능동 디바이스(510)와 제1 트렌치-타입 능동 디바이스(580) 및 제2 트렌치-타입 능동 디바이스(590) 사이의 딥 트렌치 절연 층(532)과 결합된다. 본 개시의 일 양상에서, 대체 게이트 프로세스는, 개선된 게이트 형성을 위해 폴리에칭 제한들(예를 들어, 라인/에지 거칠기)를 극복하기 위해, 딥 트렌치 능동 디바이스(510) 및/또는 제1 트렌치-타입 능동 디바이스(580) 및 제2 트렌치-타입 능동 디바이스(590)를 제조하기 위해 수행될 수 있다.

[0044]

[0057] 이러한 어레인지먼트에 따르면, 딥 트렌치 능동 디바이스(510)의 바디의 반도체 기둥들(512)은 딥 트렌치 절연 층(532)의 부분을 통해 확장된다. 또한, 반도체 층의 감소된 두께로 인해, 게이트는 반도체 기둥들(512)과 서로 맞물리는 게이트 평거들(520)에 커플링된 제1 부분(524)(예를 들어, 트렌치)를 포함한다. 본 개시의 이러한 양상에서, 딥 트렌치 능동 디바이스(510)는 백사이드 금속배선(550)의 제2 부분(550-2)에 의해 바이어싱되는 트렌치 반도체 층(582)을 포함한다. 본 개시의 이러한 양상은 백사이드 바이어싱된 트렌치-타입 능동 디바이스를 SOI 구현과 결합함으로써 종래의 실리콘 온 절연체 제조 프로세스들과 연관된 플로팅 바디 효과 문제를 해결한다. 도 8의 딥 트렌치 트랜지스터들은 고전력 또는 고전류 트랜지스터들이 요구되는 경우 유용하다.

[0045]

[0058] 도 9는 본 개시의 양상에 따른 딥 트렌치 능동 디바이스를 포함하는 집적 회로 구조를 구성하는 방법(900)을 예시하는 프로세스 흐름도이다. 블록(902)에서, 다수의 반도체 기둥들을 포함하는 바디를 형성하기 위해 절연 층 내의 반도체 층이 에칭된다. 예를 들어, 도 5에 도시된 바와 같이, 딥 트렌치 능동 디바이스(510)의 바디를 형성하기 위해 절연 층(530) 내의 반도체 영역이 에칭된다. 딥 트렌치 능동 디바이스(510)의 바디는 백사이드로부터 절연 층(530)의 프론트-사이드까지 확장되는 반도체 기둥들(512)을 포함한다. SOI(silicon on insulator) 구현에서, 절연 층(530)은 BOX(buried oxide) 층이고, 반도체 층은 SOI(silicon on insulator) 층이다. 그러나, 본 개시는 실리콘 온 절연체 구현들로 제한되지 않는다.

[0046]

[0059] 도 9를 다시 참조하면, 블록(904)에서, 유전체 재료 층은 절연 층의 프론트-사이드 표면 상에 및 반도체 기둥들을 분리하는 트렌치들에 증착된다. 예를 들어, 도 5에 도시된 바와 같이, 유전체 재료 층(522)은 절연 층(530)의 프론트-사이드 표면 상에 및 바디의 반도체 기둥들(512) 상에 증착된다. 블록(906)에서, 게이트 평거들을 포함하는 게이트를 형성하기 위해, 반도체 재료는 유전체 재료 층 상에 및 반도체 기둥들을 분리하는 트렌치들에 증착된다. 예를 들어, 도 5에 도시된 바와 같이, 딥 트렌치 능동 디바이스(510)의 게이트를 형성하기 위해 반도체 재료(예를 들어, 폴리실리콘 재료)는 유전체 재료 층(522) 상에 및 바디의 반도체 기둥들(512) 상에 증착된다. 이러한 어레인지먼트에서, 딥 트렌치 능동 디바이스(510)의 게이트는 바디의 반도체 기둥들(512)과 서로 맞물리는 게이트 평거들(520)로 구성된다. 딥 트렌치들의 깊이는 1 내지 5 마이크론 범위일 수 있다.

[0047]

[0060] 종래의 실리콘 온 절연체 구현들과 반대로, 딥 트렌치 능동 디바이스(510)의 바디는, 도 9에 추가로 예시된 바와 같이 딥 트렌치 능동 디바이스(510)의 바디를 연결함으로써 부동되는 것이 방지된다. 블록(908)에서, 핸들 기판은 절연 층의 프론트-사이드 표면 상의 프론트-사이드 유전체 층에 본딩된다. 예를 들어, 도 5에 도시된 바와 같이 프론트-사이드 유전체 층(504)에 핸들 기판(502)이 본딩되는 층 전사 프로세스가 수행된다. 본 개시의 이러한 양상에서, 딥 트렌치 능동 디바이스(510)의 바디를 연결하는 것은 층 전사 후 프로세스의 일부로서 수행된다.

[0048]

[0061] 도 9를 다시 참조하면, 블록(910)에서, 절연 층의 백사이드 표면을 지지하는 백사이드 유전체 층에 백사이드 금속배선이 제조된다. 백사이드 금속배선은 적어도 하나의 백사이드 콘택트를 통해 딥 트렌치 능동 디바이스의 바디에 커플링된다. 예를 들어, 도 5에 도시된 바와 같이, 백사이드 금속배선(550)은 딥 트렌치 능동 디바이스(510)의 바디에 커플링된다. 이러한 어레인지먼트에서, 백사이드 금속배선(550)은, 백사이드 실리사이드 층(554)을 통해 딥 트렌치 능동 디바이스(510)의 바디에 커플링되는 콘택트 플러그들(552)에 직접 커플링된다. 이러한 어레인지먼트에서, 딥 트렌치 능동 디바이스(510)의 바디는 층 전사 후 프로세스의 일부로서 제조되는 백사이드 금속배선(550)에 의해 부동되는 것이 방지된다.

[0049]

[0062] 본 개시의 추가적인 양상에 따르면, 트렌치-타입 능동 디바이스들을 포함하는 집적 회로들이 설명된다. 집적 RF 회로 구조는 게이트 평거들을 갖는 게이트, 및 게이트의 게이트 평거들과 서로 맞물리는 반도체 기둥들을 갖는 바디를 포함한다. 집적 RF 회로는 또한 바디에 커플링된 백사이드 콘택트(들)를 포함할 수 있다. 집

적 회로는 백사이드 콘택트(들)를 통해 바디를 연결하기 위한 수단을 더 포함할 수 있다. 연결 수단은 도 5 내지 도 8에 도시된 백사이드 금속배선(550)일 수 있다. 다른 양상에서, 전술된 수단은, 전술된 수단에 의해 인용된 기능들을 수행하도록 구성된 임의의 모듈 또는 임의의 장치일 수 있다.

[0050] [0063] 종래의 실리콘 온 절연체 제조 프로세스는 플로팅 바디 효과를 겪는다. 본 개시의 양상들은 고품질(Q)-팩터 RF(radio frequency) 애플리케이션들에 대한 접적 RF 회로 구조들에서 안테나 스위치 트랜지스터로서 사용될 수 있는 백사이드 바디 콘택트를 갖는 딥 트렌치 스위치 트랜지스터를 설명한다. 일 구성에서, 층 전사 전 프로세스(pre-layer transfer process)가 딥 트렌치 스위치 트랜지스터를 형성한다. 또한, 층 전사 후 프로세스는 딥 트렌치 스위치 트랜지스터의 바디를 연결하는 백사이드 바디 콘택트를 형성한다. 백사이드 바디 연결을 형성하는 층 전사 후 프로세스는 딥 스위치 트랜지스터의 바디가 부동되는 것을 방지함으로써 플로팅 바디 효과 문제를 해결한다. 백사이드 바디 콘택트는 종래의 바디 콘택트들과 연관된 영역 패널티 또는 원치 않는 저항 경로들을 회피한다. 또한, 게이트 평거들을 사용하는 딥 트렌치 스위치 트랜지스터의 어레인지먼트는 딥 트렌치 스위치 트랜지스터의 게이트에 의해 점유되는 표면 영역을 감소시킨다.

[0051] [0064] 도 10은 본 개시의 양상이 유리하게 이용될 수 있는 예시적인 무선 통신 시스템(1000)을 도시하는 블록도이다. 예시의 목적으로, 도 10은 3개의 원격 유닛들(1020, 1030 및 1050) 및 2개의 기지국들(1040)을 도시한다. 무선 통신 시스템들은 많은 더 원격의 유닛들 및 기지국들을 가질 수 있음이 인식될 것이다. 원격 유닛들(1020, 1030 및 1050)은 개시된 딥 트렌치 능동 디바이스를 포함하는 IC 디바이스들(1025A, 1025C 및 1025B)을 포함한다. 다른 디바이스들은 또한 기지국들, 스위칭 디바이스들 및 네트워크 장비와 같은 개시된 딥 트렌치 능동 디바이스를 포함할 수 있음이 인식될 것이다. 도 10은 기지국(1040)으로부터 원격 유닛들(1020, 1030 및 1050)로의 순방향 링크 신호들(1080) 및 원격 유닛들(1020, 1030 및 1050)로부터 기지국들(1040)로의 역방향 링크 신호들(1090)을 도시한다.

[0052] [0065] 도 10에서, 원격 유닛(1020)은 모바일 전화로서 도시되고, 원격 유닛(1030)은 휴대용 컴퓨터로서 도시되고, 원격 유닛(1050)은 무선 로컬 루프 시스템의 고정 위치 원격 유닛으로 도시된다. 예를 들어, 원격 유닛들은 모바일 폰, 핸드-헬드 PCS(personal communication systems) 유닛, 휴대용 데이터 유닛, 예를 들어, PDA(personal digital assistant), GPS 가능 디바이스, 내비게이션 디바이스, 셋탑 박스, 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 고정 위치 데이터 유닛, 예를 들어, 겸침(meter reading) 장비, 또는 데이터 또는 컴퓨터 명령들 또는 이들의 조합들을 저장 또는 리트리브하는 다른 통신 디바이스일 수 있다. 도 10이 본 개시의 양상들에 따른 원격 유닛들을 예시하지만, 본 개시는 이러한 예시적인 예시된 유닛들로 제한되지 않는다. 본 개시의 양상들은 개시된 딥 트렌치 능동 디바이스를 포함하는 많은 디바이스들에서 적절히 이용될 수 있다.

[0053] [0066] 도 11은 앞서 개시된 딥 트렌치 능동 디바이스와 같은 반도체 컴포넌트의 회로, 레이아웃 및 로직 설계에 사용되는 설계 워크스테이션을 예시하는 블록도이다. 설계 워크스테이션(1100)은 운영 시스템 소프트웨어, 지원 파일들 및 설계 소프트웨어, 예를 들어, Cadence 또는 OrCAD를 포함하는 하드 디스크(1101)를 포함한다. 설계 워크스테이션(1100)은 또한 회로(1110) 또는 반도체 컴포넌트(1112), 예를 들어, 딥 트렌치 능동 디바이스의 설계를 용이하게 하기 위해 디스플레이(1102)를 포함한다. 회로 설계(1110) 또는 반도체 컴포넌트(1112)를 유형으로 저장하기 위해 저장 매체(1104)가 제공된다. 회로 설계(1110) 또는 반도체 컴포넌트(1112)는 GDSII 또는 GERBER과 같은 파일 포맷으로 저장 매체(1104) 상에 저장될 수 있다. 저장 매체(1104)는 CD-ROM, DVD, 하드 디스크, 플래시 메모리 또는 다른 적절한 디바이스일 수 있다. 또한, 설계 워크스테이션(1100)은 저장 매체(1104)로부터의 입력을 수용하거나 그에 출력을 기록하기 위한 드라이브 장치(1103)를 포함한다.

[0054] [0067] 저장 매체(1104) 상에 기록된 데이터는 로직 회로 구성들, 포토리소그래피 마스크들에 대한 패턴 데이터 또는 전자 빔 리소그래피와 같은 일련의 기록 툴들에 대한 마스크 패턴 데이터를 특정할 수 있다. 데이터는 로직 시뮬레이션들과 연관된 네트 회로들 또는 타이밍 도면들과 같은 로직 검증 데이터를 더 포함할 수 있다. 저장 매체(1104) 상에 데이터를 제공하는 것은 반도체 웨이퍼들을 설계하기 위한 프로세스들의 수를 감소시킴으로써 회로 설계(1110) 또는 반도체 컴포넌트(1112)의 설계를 용이하게 한다.

[0055] [0068] 펌웨어 및/또는 소프트웨어 구현에 대해, 방법들은, 본 명세서에 설명된 기능들을 수행하는 모듈들(예를 들어, 절차들, 함수들 등)을 이용하여 구현될 수 있다. 명령들을 유형으로 구현하는 머신-판독가능 매체는 본 명세서에 설명된 방법들을 구현할 시에 사용될 수 있다. 예를 들어, 소프트웨어 코드들은 메모리에 저장될 수 있고, 프로세서 유닛에 의해 실행될 수 있다. 메모리는, 프로세서 유닛 내부 또는 프로세서 유닛 외부에서 구현될 수 있다. 본 명세서에 사용된 바와 같이, 용어 "메모리"는 장기, 단기, 휘발성, 비휘발성, 또는 다른 메

모리의 타입들을 지칭하며, 메모리의 특정 타입 또는 메모리들의 수, 또는 메모리가 저장되는 매체들의 타입에 제한되지 않는다.

[0056]

[0069] 펌웨어 및/또는 소프트웨어로 구현되면, 기능들은 컴퓨터-판독가능 매체 상의 하나 이상의 명령들 또는 코드로서 저장될 수 있다. 예들은, 데이터 구조로 인코딩된 컴퓨터-판독가능 매체들, 및 컴퓨터 프로그램으로 인코딩된 컴퓨터-판독가능 매체들을 포함한다. 컴퓨터-판독가능 매체들은 물리적 컴퓨터 저장 매체들을 포함한다. 저장 매체는 컴퓨터에 의해 액세스될 수 있는 이용가능한 매체일 수 있다. 제한이 아닌 예로서, 그러한 컴퓨터-판독가능 매체들은 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 저장부, 자기 디스크 저장 또는 다른 자기 저장 디바이스들, 또는 명령들 또는 데이터 구조들의 형태로 원하는 프로그램 코드를 저장하는데 사용될 수 있고 컴퓨터에 의해 액세스될 수 있는 다른 매체를 포함할 수 있으며; 본 명세서에 사용된 바와 같이, 디스크(disk) 및 디스크(disc)는, 컴팩트 디스크(disc)(CD), 레이저 디스크(disc), 광학 디스크(disc), DVD(digital versatile disc), 플로피 디스크(disk) 및 블루-레이 디스크(disc)를 포함하며, 여기서, 디스크(disk)들은 일반적으로 데이터를 자기적으로 재생하지만, 디스크(disc)들은 레이저들을 이용하여 광학적으로 데이터를 재생한다. 상기의 것들의 결합들이 또한 컴퓨터 판독가능 매체의 범위 내에 포함되어야 한다.

[0057]

[0070] 컴퓨터 판독가능 매체 상의 저장에 부가하여, 명령들 및/또는 데이터는 통신 장치에 포함된 송신 매체들 상에서 신호들로서 제공될 수 있다. 예를 들어, 통신 장치는, 명령들 및 데이터를 표시하는 신호들을 갖는 트랜시버를 포함할 수 있다. 명령들 및 데이터는 하나 이상의 프로세서들로 하여금, 청구항들에서 약술된 기능들을 구현하게 하도록 구성된다.

[0058]

[0071] 본 개시 및 이의 이점들이 상세히 설명되었지만, 첨부된 청구항들에 의해 정의된 바와 같이 본 개시의 기술로부터 벗어남이 없이 다양한 변화들, 대체들 및 변경들이 행해질 수 있음을 이해해야 한다. 예를 들어, "위" 및 "아래"와 같은 관계적 용어들이 기판 또는 전자 디바이스에 대해 사용된다. 물론, 기판 또는 전자 디바이스가 반전되면, 위는 아래가 되고, 아래는 위가 된다. 추가적으로, 측방향으로 배향되면, 위 및 아래는 기판 또는 전자 디바이스의 사이드들을 지칭할 수 있다. 또한, 본 출원의 범위는 본 명세서에 설명된 프로세스, 머신, 제조의 특정 구성들, 및 재료의 조성, 수단, 방법들 및 단계들로 제한되는 것으로 의도되지 않는다. 당업자가 본 개시로부터 쉽게 인식할 바와 같이, 본원에 설명된 대응하는 구성들과 실질적으로 동일한 결과를 달성하거나 실질적으로 동일한 기능을 수행하는, 현재 존재하는 또는 추후에 개발될 프로세스들, 머신들, 제조, 재료의 조성들, 수단, 방법들 또는 단계들이 본 개시에 따라 활용될 수 있다. 따라서, 첨부된 청구항들은 이러한 프로세스들, 머신들, 제조, 재료의 조성들, 수단, 방법들 또는 단계들을 청구항의 범위 내에 포함하는 것으로 의도된다.

## 도면

## 도면 1a

## 도면1b

## 도면2a

## 도면2b

## 도면3a

## 도면3b

도면3c

도면3d

도면3e

도면4

도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

## 도면11