(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5472712号

(P5472712)

(45) 発行日 平成26年4月16日(2014.4.16)

(24) 登録日 平成26年2月14日(2014.2.14)

(51) Int.Cl.

F 1

H02M 3/155 (2006.01)

H02M 3/28 (2006.01)H02M 3/155

H02M 3/28H

H

請求項の数 21 (全 17 頁)

(21) 出願番号 特願2009-250833 (P2009-250833)

(22) 出願日 平成21年10月30日 (2009.10.30)

(65) 公開番号 特開2010-115106 (P2010-115106A)

(43) 公開日 平成22年5月20日 (2010.5.20)

審査請求日 平成24年8月24日 (2012.8.24)

(31) 優先権主張番号 12/267,397

(32) 優先日 平成20年11月7日 (2008.11.7)

(33) 優先権主張国 米国(US)

(73) 特許権者 501315784

パワー・インテグレーションズ・インコーポレーテッド

アメリカ合衆国・95138・カリフォルニア州・サンホゼ・ヘリヤー・アベニュー

5245

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

最終頁に続く

(54) 【発明の名称】力率改善コンバータにおいて使用されるコントローラおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

力率改善(PFC)コンバータにおいて使用されるコントローラであって、

前記PFCコンバータの入力電流を積分するように結合された第1の積分器を備え、パワーコンバータのパワースイッチのオン期間を終了させるように、第1の積分器に応答して第1の信号が生成され、前記コントローラはさらに、

PFCコンバータの定電圧と入力電圧との差を積分するように結合された第2の積分器を備え、パワースイッチのオフ期間を終了させるように、第2の積分器に応答して第2の信号が生成され、前記コントローラはさらに、

第1の信号および第2の信号に応答してパワースイッチのスイッチング周波数を変動させ、かつ第3の信号を出力してパワースイッチを切換えて、入力電圧に実質的に比例するように入力電流を制御するように結合された駆動回路と、

PFCコンバータの出力における負荷を表わすエラー電圧信号を受取るように結合された周波数調整回路とを備え、周波数調整回路はさらに、調整されたエラー信号を出力して、エラー電圧信号に応答してパワースイッチのオフ期間の終了を調整するように結合される、コントローラ。

## 【請求項 2】

駆動回路は、PFCコンバータの出力における出力電圧を調節する、請求項1に記載のコントローラ。

## 【請求項 3】

10

20

パワースイッチは、金属 - 酸化物 - 半導体電界効果トランジスタ（MOSFET）を含む、請求項1に記載のコントローラ。

**【請求項4】**

PFCコンバータの出力を表わすフィードバック信号を基準電圧と比較するように結合され、かつエラー電圧信号を出力するように結合されたエラー増幅器をさらに備える、請求項1に記載のコントローラ。

**【請求項5】**

第1の積分器は、パワースイッチがオンになると変倍された電流で充電されるように結合された第1のキャパシタを含み、変倍された電流は入力電流を表わす、請求項1に記載のコントローラ。10

**【請求項6】**

第1のキャパシタ上の電圧をエラー電圧信号と比較して第1の信号を生成するように結合された第1の比較器をさらに備える、請求項5に記載のコントローラ。

**【請求項7】**

第2の積分器は、パワースイッチがオフになると変倍された電流と基準電流との差で充電されるように結合された第2のキャパシタを含み、変倍された電流は入力電圧を表わす、請求項1に記載のコントローラ。

**【請求項8】**

第2のキャパシタ上の電圧を調整されたエラー信号と比較して第2の信号を生成するように結合された第2の比較器をさらに備える、請求項7に記載のコントローラ。20

**【請求項9】**

力率改善（PFC）コントローラであって、

PFCコンバータの入力電流を積分するように結合された第1の積分器を備え、PFCコンバータのパワースイッチのオン期間を終了させるように、第1の積分器に応答して第1の信号が生成され、前記PFCコントローラはさらに、

PFCコンバータの定電圧と入力電圧との差を積分するように結合された第2の積分器を備え、PFCコンバータのパワースイッチのオフ期間を終了させるように、第2の積分器に応答して第2の信号が生成され、前記PFCコントローラはさらに、

第1の信号および第2の信号に応答してPFCコンバータのパワースイッチのスイッチング周波数を変動させ、かつ第3の信号を出力してPFCコンバータのパワースイッチを切換えて、入力電圧に実質的に比例するように入力電流を制御するように結合された駆動回路を備える、PFCコントローラ。30

**【請求項10】**

PFCコンバータの出力を表わすエラー電圧信号を受取るように結合された周波数調整回路をさらに備え、周波数調整回路はさらに、調整されたエラー信号を出力して、エラー電圧信号に応答してPFCコンバータのパワースイッチのオフ期間の終了を調整するように結合される、請求項9に記載のPFCコントローラ。

**【請求項11】**

駆動回路は、PFCコンバータの出力電圧を調節するように結合される、請求項10に記載のPFCコントローラ。40

**【請求項12】**

PFCコンバータのパワースイッチは、金属 - 酸化物 - 半導体電界効果トランジスタ（MOSFET）を含む、請求項9に記載のPFCコントローラ。

**【請求項13】**

PFCコンバータの出力を表わすフィードバック信号および基準電圧に応答してエラー電圧信号を生成するように結合されたエラー増幅器をさらに備える、請求項10に記載のPFCコントローラ。

**【請求項14】**

第1の積分器は、パワースイッチがオンになると変倍された電流で充電されるように結合された第1のキャパシタを含み、変倍された電流は入力電流を表わす、請求項9に記載50

の P F C コントローラ。

**【請求項 1 5】**

変倍された電流の変倍係数は、半ラインサイクルのピーク入力電圧を表わす、請求項 1 4 に記載の P F C コントローラ。

**【請求項 1 6】**

変倍された電流の変倍係数は、入力電圧の実効値を表わす、請求項 1 4 に記載の P F C コントローラ。

**【請求項 1 7】**

変倍された電流の変倍係数は、半サイクルの平均入力電圧を表わす、請求項 1 4 に記載の P F C コントローラ。

**【請求項 1 8】**

第 1 のキャパシタ上の電圧を、P F C コンバータの出力を表わすエラー電圧信号と比較して、第 1 の信号を生成するように結合された第 1 の比較器をさらに備える、請求項 1 4 に記載の P F C コントローラ。

**【請求項 1 9】**

第 2 の積分器は、パワースイッチがオフになると変倍された電流と基準電流との差で充電されるように結合された第 2 のキャパシタを含み、変倍された電流は入力電圧を表わす、請求項 9 に記載の P F C コントローラ。

**【請求項 2 0】**

変倍された電流の変倍係数は、瞬間的な d c 入力電圧を表わす、請求項 1 9 に記載の P F C コントローラ。

**【請求項 2 1】**

第 2 のキャパシタ上の電圧を調整されたエラー信号と比較して第 2 の信号を生成するよう結合された第 2 の比較器をさらに備える、請求項 1 9 に記載の P F C コントローラ。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

背景

開示の分野

本発明は概して電源の力率改善回路に関し、特に本発明は、力率改善回路の効率を高めることに関する。30

**【背景技術】**

**【0 0 0 2】**

背景

電源は、コンセントから与えられた交流（「a c」）電力を電気装置に利用可能な直流（「d c」）電力に変換するのに典型的に使用される。電源設計に関する重要な検討事項の 1 つは、どのように効率的に電力が電源に送出されるかという点である。電力送出効率を向上させるには、力率改善（P F C）回路を電源において使用し得る。具体的には、力率改善回路は、電流波形を電圧波形の形状に近似するように整形することを意図する。

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0 0 0 3】**

典型的に、P F C 回路はパワースイッチを含むように設計され、当該パワースイッチは、配電線から伝送される歪んだ入力電流波形を、入力電圧波形の形状に似たより理想的な電流波形に変形するために、オフ状態とオン状態との間で切換わるように制御される。具体的には、パワースイッチはエネルギー伝達素子に結合され、電源の出力にエネルギーを伝達する。しかし動作中、P F C 回路は、寄生容量によってパワースイッチで生じるスイッチング損失を蒙る。典型的に、寄生容量は、電気構成要素の部品同士の間に、それらが互いに近接していることによって存在する望ましくない容量として規定することができる。追加的な損失がエネルギー伝達素子においても認識される。

10

20

30

40

50

**【図面の簡単な説明】****【0004】****図面の簡単な説明**

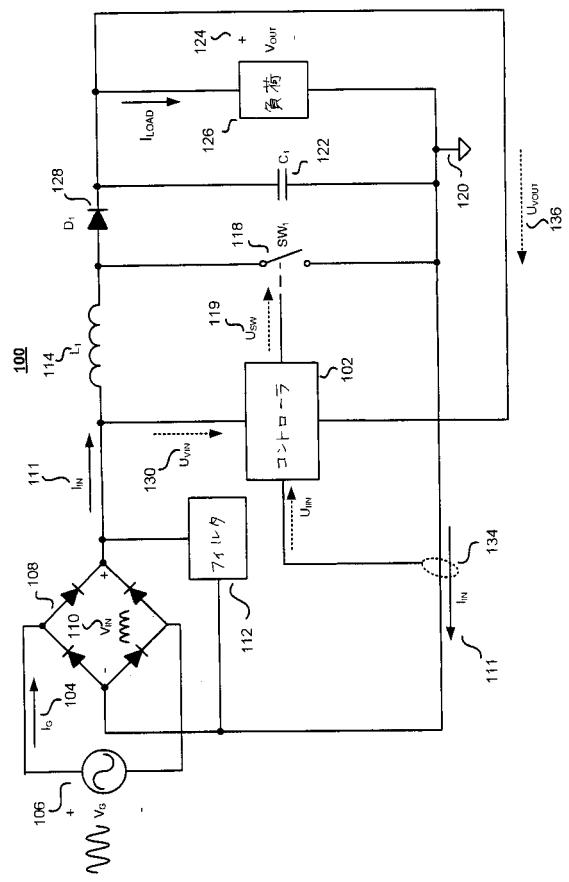

【図1】本発明の教示に係る例示的なコントローラを含む例示的な昇圧コンバータの機能ブロック図である。

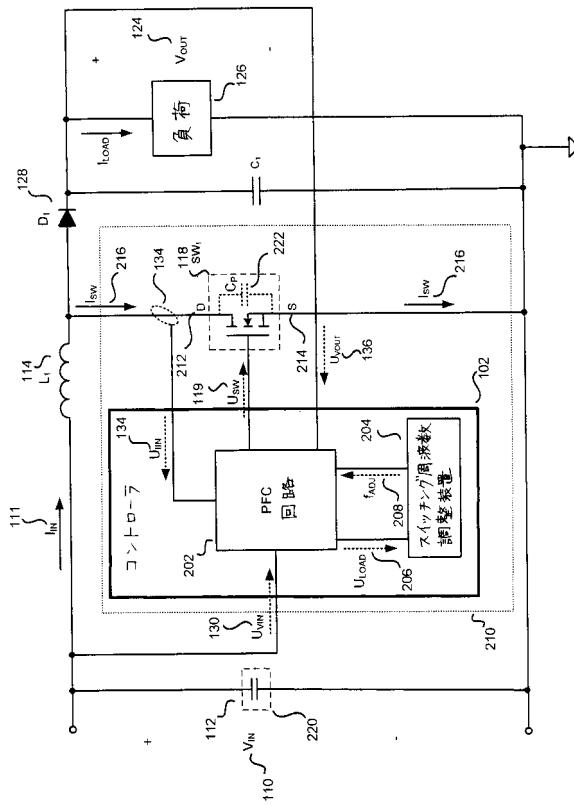

【図2】本発明の教示に係る図1の例示的なコントローラをさらに示す機能ブロック図である。

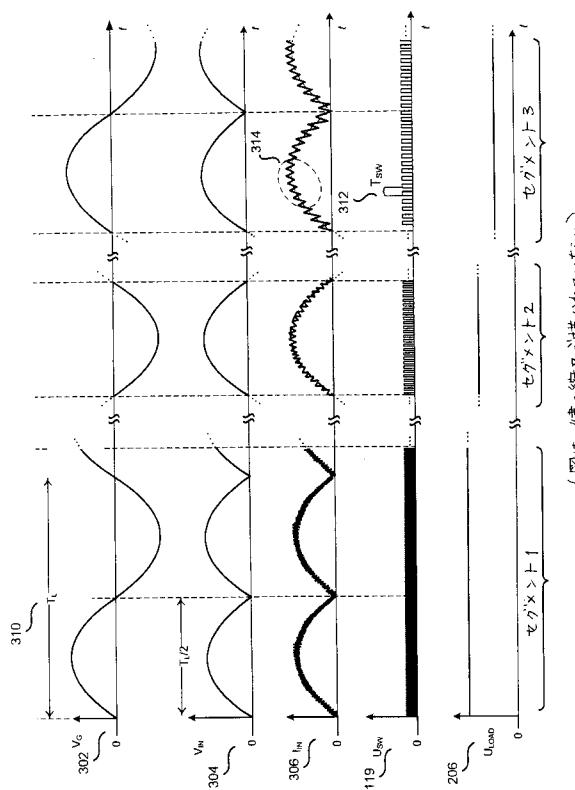

【図3A】図1および図2に関連付けられ、かつ本発明の教示に係るスイッチング信号および負荷信号に対応する例示的な入力波形を示す図である。

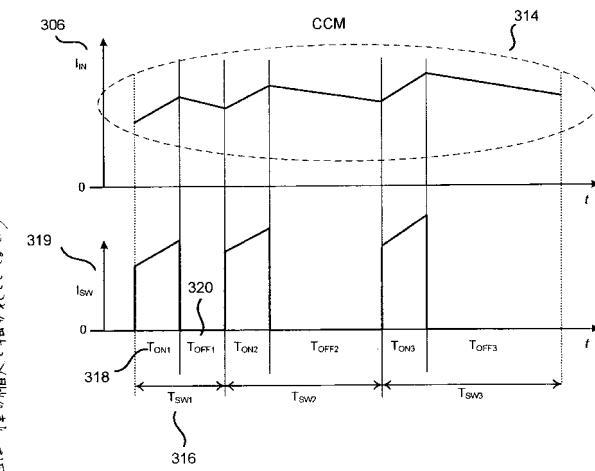

【図3B】図3Aの入力波形のうちの1つの拡大図と対応するスイッチング波形とを示す図である。 10

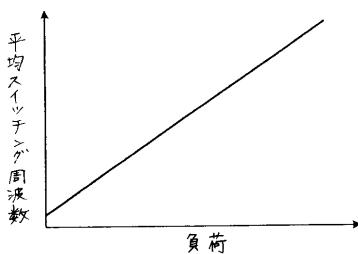

【図4A】本発明の教示に係る負荷と平均スイッチング周波数との間の例示的な関係を示す図である。

【図4B】本発明の教示に係る負荷と平均スイッチング周波数との間の代替例的な関係を示す図である。

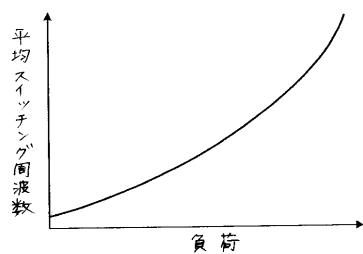

【図4C】本発明の教示に係る負荷と平均スイッチング周波数との間の代替例的な関係を示す図である。

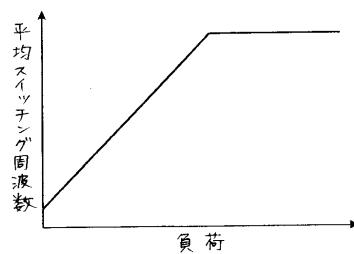

【図4D】本発明の教示に係る負荷と平均スイッチング周波数との間の代替例的な関係を示す図である。 20

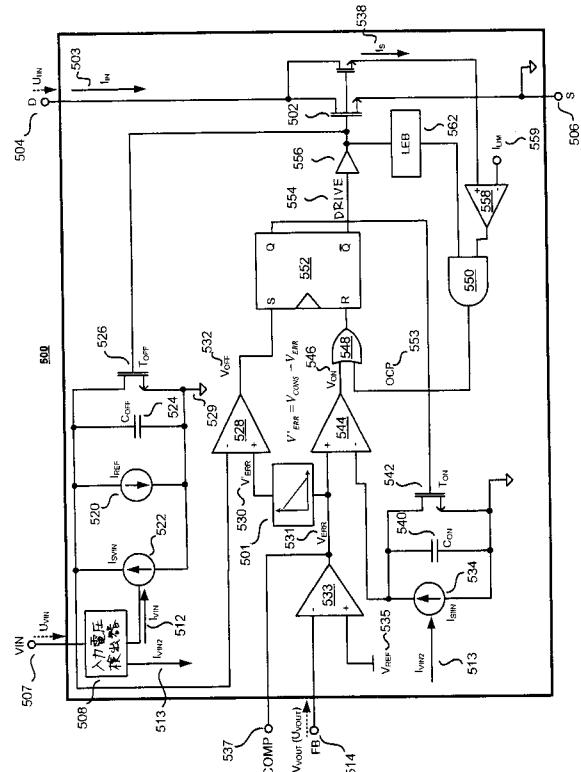

【図5A】本発明の教示に係る力率改善(PFC)のための制御技術を実現する例示的な集積回路を示す図である。

【図5B】本発明の教示に係る例示的なスイッチング周波数調整器を示す図である。

【図6A】本発明の教示に係るエラー電圧、調整されたエラー電圧および負荷の間の例示的な関係を示す図である。

【図6B】本発明の教示に係る調整されたエラー電圧の例示的なグラフである。

【図7】本発明の教示に係るPFC回路における変動負荷に応答して平均スイッチング周波数を調整するための例示的な方法を示すフローチャートである。

**【0005】**

限定的でなくかつ網羅的でない本発明の実施例を添付の図面を参照して説明する。同様の参照符号は、特に明記しない限り、さまざまな図に亘って同様の部分を指す。 30

**【発明を実施するための形態】****【0006】****詳細な説明**

本発明の一局面において、本明細書に開示される方法および装置は、力率改善(PFC)回路における効率を高めるための制御技術を使用する。以下の説明では、本発明を十分に理解できるように多くの具体的な詳細を記載する。しかし、本発明を実施するのにその具体的な詳細を必ずしも採用する必要がないことは当業者にとっては明らかであろう。本発明が不明瞭とならないように、具体化に関連する周知の方法は詳細には記載していない。

**【0007】**

本明細書全体に亘る「一実施例」、「ある実施例」、「一例」または「ある例」という言及は、当該実施例または例に関連して記載される特定の特徴、構造または特質が本発明の少なくとも一実施例に含まれることを意味する。したがって、本明細書中のさまざまな箇所に出現する「一実施例において」、「ある実施例において」、または「ある例」という語句は、すべて同じ実施例または例を指すとは限らない。さらに、特定の特徴、構造または特質は、1つ以上の実施例または例において、いずれかの好適な組合せおよび/または副組合せで組合せられ得る。 40

**【0008】**

以下に述べるように、本発明の教示に係るさまざまな例は、電力効率送出をさらに高めるための力率改善回路に関する制御技術を実現する。具体的には、当該制御技術は、P F

C回路の出力において結合された変動負荷に応答して、PFC回路のパワースイッチの平均スイッチング周波数を調整する。本発明の一実施例において、負荷は、PFC改善回路の出力に結合されるdc-dcコンバータを表わす。この概念は、以下に記載する図面に従って説明される。

#### 【0009】

図示すると、図1は、本発明の教示に係るコントローラ102を含む例示的な昇圧PFCコンバータ100(PFCコンバータとも称する)の機能ブロック図である。図示の例では、PFCコンバータ100は、acライン電圧 $V_{G106}$ に対応するacライン電流 $I_{G104}$ を受取る昇圧パワーコンバータである。典型的に、acライン電流 $I_{G104}$ および対応するacライン電圧 $V_{G106}$ は、配電システム(たとえばパワープラント)によって電気ソケットを介して与えられる。図示のように、ブリッジ整流器108は、acライン電圧 $V_{G106}$ をdc入力電圧 $V_{IN110}$ に変換する。

10

#### 【0010】

図3Aを参照し、例示的な波形302、304および306は、acライン電圧 $V_{G106}$ 、dc入力電圧 $V_{IN110}$ およびdc入力電流 $I_{IN111}$ をそれぞれ表わす。図示のように、「ac」波形は、ある間隔でその極性を反転させる波形によって示される。たとえば、acライン電圧 $V_{G106}$ は正の値と負の値とが交互する波形302によって表わされる。これに対して「dc」波形は、常に同じ極性である波形によって表わされる。たとえば、波形304および306によって例示されるように、dc入力電圧 $V_{IN110}$ およびdc入力電流 $I_{IN111}$ は実質的に常に正である。dc入力電圧 $V_{IN110}$ (すなわち波形304)およびdc入力電流 $I_{IN111}$ (すなわち波形306)は、時間とともに大きさが変動する。

20

#### 【0011】

図1に戻り、図示の例では、フィルタ112がブリッジ整流器108の両端に結合され、dc入力電流 $I_{IN111}$ からの高周波ノイズ電流をフィルタリングする。発明の一局面では、dc入力電流 $I_{IN111}$ は、dc入力電圧 $V_{IN110}$ の波形形状に従うように実質的に制御される。図3Aに示すように、dc入力電流 $I_{IN111}$ を表わす波形306は、dc入力電圧 $V_{IN110}$ を表わす波形304の形状におおむね従う。

#### 【0012】

図1の例に示すように、インダクタ $L_{114}$ として示されるエネルギー蓄積素子の一端はコントローラ102に結合され、インダクタ $L_{114}$ の他方端はパワースイッチ $SW_{1118}$ に結合される。動作の際、パワースイッチ $SW_{1118}$ は、スイッチ118が電流を伝えることができるときは「オン」すなわち「閉」状態にあり、スイッチ118が電流を伝えることができないときは「オフ」すなわち「開」状態にある。スイッチングサイクルは、スイッチがオンである期間、およびその後のスイッチがオフである期間として規定される。たとえば、スイッチングサイクルは、スイッチ $SW_{1118}$ が導通することができるオン期間と、その後のスイッチ $SW_{1118}$ が導通することができないオフ期間とを含み得る。別の例では、スイッチングサイクルは、スイッチ $SW_{1118}$ が導通することができないオフ期間と、その後のスイッチ $SW_{1118}$ が導通することができるオン期間とを含み得る。オン期間は、スイッチングサイクル中にスイッチ $SW_{1118}$ が導通している期間として規定され得、オフ期間はスイッチングサイクル中にスイッチ $SW_{1118}$ が導通していない期間として規定され得る。

30

40

#### 【0013】

図1の例では、入力帰線(return)120がパワースイッチ $SW_{1118}$ に結合される。動作の際、エネルギー蓄積インダクタ $L_{114}$ は、本発明の教示に係るスイッチ $SW_{1118}$ のスイッチングに応答してパワーコンバータ100の出力にエネルギーを伝達する。例に示したように、バルクキャパシタ122が、実質的に一定の出力電圧 $V_{OUT124}$ を負荷126に供給するように結合される。一例において、負荷126はdc-dc電源の入力であり得る。ダイオード $D_{1128}$ は、バルクキャパシタ122からの電流がインダクタ $L_{114}$ に戻ることを防ぐように結合される。図1の例では、dc入力電圧

50

$V_{IN110}$ を表わす入力電圧信号 $U_{VIN130}$ がコントローラ102によって受取られる。d c入力電流 $I_{IN111}$ を表わす入力電流検知信号 $U_{IIN132}$ もコントローラ102によって受取られる。具体的には、d c入力電流 $I_{IN111}$ を測定するために、たとえば変流器のような電流検知器134、単体の抵抗器の両端電圧、トランジスタが導通しているときのトランジスタの両端電圧、またはパワースイッチに結合された検知FET素子を使用し得る。図1の例では、出力電圧 $V_{OUT124}$ を表わす出力電圧信号 $U_{VOUT136}$ もコントローラ102によって受取られる。一例では、出力電圧信号 $U_{VOUT136}$ は一定の基準値を表わし得る。本発明の一実施例では、検知信号 $U_{VIN130}$ 、 $U_{IIN132}$ および $U_{VOUT136}$ は電圧または電流の形態であり得る。

## 【0014】

10

動作の際、コントローラ102はスイッチング信号 $U_{SW119}$ を出力する。スイッチング信号 $U_{SW119}$ は、出力電圧 $V_{OUT124}$ を調節し、「入力電圧 $V_{IN110}$ 」とも称するd c入力電圧 $V_{IN110}$ の波形に従うようにd c入力電流 $I_{IN111}$ を制御するために、入力電圧信号 $U_{VIN130}$ 、入力電流信号 $U_{IIN132}$ および/または出力電圧信号 $U_{VOUT136}$ に応答してスイッチ $SW_{118}$ のスイッチングを制御する。一例において、コントローラ102は、可変スイッチング周波数制御技術とも称するスイッチ $SW_{118}$ の各スイッチングサイクルの変動によって、出力電圧 $V_{OUT124}$ を調節し、d c入力電流 $I_{IN111}$ を制御する。別の例において、コントローラ102は、固定周波数制御とも称するスイッチ $SW_{118}$ の一定のスイッチングサイクルの維持によって、出力電圧 $V_{OUT124}$ を調節し、d c入力電流 $I_{IN111}$ を制御する。本発明の一局面において、コントローラ102は、負荷124に応答してスイッチの平均スイッチング周波数も調整して、PFCコンバータ100の効率をさらに高める。特に、平均スイッチング周波数は、複数のスイッチングサイクルにわたるスイッチング周波数として規定される。具体的には、コントローラ102は、負荷126に応答してスイッチ $SW_{118}$ の平均スイッチング周波数を調整することにより電力損失を減少させる制御技術を採用する。

20

## 【0015】

図2を参照し、パワーコンバータ100の機能ブロック図は、本発明の教示に係る図1のコントローラ102の一例をさらに例示する。図示のように、コントローラ102は、力率改善(PFC)回路202およびスイッチング周波数調整装置204を含む。図2の例によれば、PFC回路202は、スイッチング信号 $U_{SW119}$ と、PFCコンバータ100の出力に結合された負荷126を表わす負荷信号 $U_{LOAD206}$ とを出力する。PFC回路202は、入力電圧信号 $U_{VIN130}$ 、出力電圧信号 $U_{VOUT136}$ および/または入力電流信号 $U_{IIN134}$ を受取る。スイッチング周波数調整装置204は、負荷信号 $U_{LOAD206}$ を受取り、周波数調整信号 $f_{ADJ208}$ を出力する。

30

## 【0016】

動作の際、一例として、PFC回路202は、電源の出力を調節し、入力電圧信号 $U_{VIN130}$ 、入力電流信号 $U_{IIN134}$ および/または出力電圧信号 $U_{VOUT136}$ に応答して、入力電流 $I_{IN111}$ が入力電圧 $V_{IN110}$ の波形に従うように入力電流を制御する。スイッチング周波数調整装置204は、負荷信号 $U_{LOAD206}$ に応答して周波数調整信号 $f_{ADJ208}$ を出力し、PFC回路202は、周波数調整信号 $f_{ADJ208}$ に応答してパワースイッチ $SW_{118}$ の平均スイッチング周波数を調整する。

40

## 【0017】

図示のように、コントローラ102、電流検知器134およびスイッチ $SW_{118}$ は、集積回路210に含まれ得る。一例において、スイッチ $SW_{118}$ は、コントローラ102と同じ1個のモノリシック装置に含まれ得る。代替例では、コントローラ102は、スイッチ $SW_{118}$ を有さない1個のモノリシック装置に含まれ得る。一例において、スイッチ $SW_{118}$ は、金属-酸化物-半導体電界効果トランジスタ(MOSFET)であり得る。動作の際、スイッチ $SW_{118}$ によって、スイッチ $SW_{118}$ がオンのときにはドレイン端子212からソース端子214に電流の伝導が可能となり、スイッチ $SW_{118}$ がオフのときには電流の伝導が実質的に妨げられる。別の例において、電流

50

検知器 134 は、図示のスイッチ電流  $I_{SW216}$  を測定するためにスイッチ SW<sub>118</sub> に結合され得る。スイッチ電流  $I_{SW216}$  は、(図 3B に図示の) スイッチングサイクルのオン期間中は d c 入力電流  $I_{IN111}$  に実質的に等しいため、スイッチ電流  $I_{SW216}$  は、スイッチングサイクルのオン期間中は d c 入力電流  $I_{IN111}$  の代わりに検知され得る。図示のように、電流検知器 134 は、パワースイッチ SW<sub>118</sub> のドレイン端子 212 における入力電流  $I_{IN111}$  を検知し得る。代替的な実施例において、電流検知器 134 は、パワースイッチ SW<sub>118</sub> のソース端子 214 における入力電流  $I_{IN111}$  を検知し得る。代替的な実施例において、スイッチ電流  $I_{SW216}$  は、ドレイン端子 212 の前またはソース端子 214 の後で電流検知器 134 によって検知され得る。

## 【0018】

10

図示のように、スイッチ SW<sub>118</sub> は寄生容量  $C_{P222}$  を含む。具体的には、寄生容量は、電気構成要素の部品同士の間に、それらが互いに近接していることによって存在する望ましくない容量として規定することができる。動作の際、スイッチ SW<sub>118</sub> がオフ状態に切換ると、PFC コンバータ 100 の寄生容量  $C_{P222}$  は電気エネルギーを蓄積する。漂遊容量  $C_{P22}$  がパワースイッチ SW<sub>118</sub> の両端にあると示されているが、漂遊容量は PFC コントローラ 100 内のすべての構成要素からもたらされ得る。スイッチ SW<sub>118</sub> がオン状態に切換ると、PFC コンバータ 100 の構成要素内の蓄積電気エネルギーが放出され、エネルギーはパワースイッチ SW<sub>118</sub> で損失される。コントローラ 100 の動作中、スイッチ SW<sub>118</sub> のスイッチング周波数が上昇し、かつスイッチ SW<sub>118</sub> がオン状態とオフ状態との間でより頻繁に切換るにつれて、より多くのエネルギーがスイッチ SW<sub>118</sub> で損失される。したがって、スイッチ SW<sub>118</sub> のスイッチング周波数を可能な限り常に最小化することが有益であり得る。一例において、スイッチ SW<sub>118</sub> における電力損失を制限するために、PFC コンバータ 100 の出力の両端の負荷 126 が低減するにつれて、スイッチ SW<sub>118</sub> のスイッチング周波数が低下し得る。しかし、スイッチ SW<sub>118</sub> の周波数を制限すると、エネルギー伝達素子 L<sub>114</sub> における損失が増加する。具体的には、パワースイッチ SW<sub>118</sub> のスイッチング周波数が低下するにつれ、ピーク電流の増加によってより大きな電力損失がインダクタにおいて生じ得る。また、エネルギー変圧器の磁芯の磁束の偏位によって、当該磁芯における損失が増加する。典型的に、PFC コンバータにおいてスイッチング周波数を低下させると、エネルギー伝達素子 L<sub>114</sub> における損失はスイッチ SW<sub>118</sub> において防がれた損失よりもはるかに大きくなる。しかし、特定の PFC コンバータ構造では、エネルギー伝達素子 L<sub>114</sub> から生じる付加的な電力損失よりもパワースイッチにおける損失の方が大きいことから、スイッチング周波数を低下させることが有益であり得る。

20

## 【0019】

30

図の例に示されるように、フィルタ 112 は、限定はしないが、d c 入力電流  $I_{IN111}$  からの高周波ノイズをフィルタリングするキャパシタ 220 を含む。具体的には、一例において、キャパシタ 220 の容量値は、キャパシタ 220 が高周波ノイズを遮り得るが d c 入力電圧  $V_{IN110}$  の時間変動成分を低減するのに十分なほど大きくならないよう選択された値である。代替的な実施例では、集積回路 210 は、フライバックコンバータを含む PFC コンバータ 100 において使用され得る。

40

## 【0020】

先に参照したように、図 3A は本発明の教示に係る a c ライン電圧波形 302、d c 入力電圧波形 304、d c 入力電流波形 306、スイッチ信号  $U_{SW119}$  および負荷信号  $U_{LOAD206}$  を例示する。a c ライン電圧波形 302 は a c ライン電圧  $V_G106$  を表わし、実質的に正弦波形である。ラインサイクルは、a c ライン電圧波形 302 の 3 つの連続したゼロ交差の間の時間間隔として規定され、1 ラインサイクルを完了するのにかかる時間を表わすラインサイクル期間  $T_L310$  に対応する。具体的には、図示の例において、ラインサイクル期間  $T_L310$  は a c ライン電圧  $V_G106$  の周波数に依存する。たとえば、a c ライン電圧  $V_G106$  の周波数が上昇すると、ラインサイクル期間  $T_L310$  は短くなる。逆に、a c ライン電圧  $V_G106$  の周波数が低下すると、ラインサイクル期間  $T_L3$

50

10は長くなる。本発明の実施例によれば、ラインサイクル期間 $T_L$ 310はスイッチングサイクル期間 $T_{SW}$ 312よりも実質的に長い。さらに例示すると、一例において、ライン周波数は、16,666マイクロ秒のラインサイクル期間 $T_L$ 310に相当する60Hzであり、セグメント1における平均スイッチング周波数は、10マイクロ秒のスイッチングサイクル期間 $T_{SW}$ 312に相当する100kHzである。

#### 【0021】

図示のように、dc入力電圧波形304はdc入力電圧 $V_{IN110}$ を表わし、acライン電圧波形302の整流された波形である。動作の際、ブリッジ整流器108はacライン電圧波形302によって表わされるacライン電圧 $V_G106$ を整流して、dc入力電圧波形304によって表わされるdc入力電圧 $V_{IN110}$ を生成する。dc入力電流波形306は、dc入力電流 $I_{IN111}$ を表わす。図示のように、dc入力電流 $I_{IN111}$ が、dc入力電圧 $V_{IN110}$ に従うようスイッチングサイクル中にどのように制御されるかを例示するために、dc入力電流波形306が入力電圧波形304に重畠される。dc入力電流波形306の拡大図314を図3Bに示す。

#### 【0022】

図3Aに示すように、スイッチング信号 $U_{SW119}$ の平均スイッチング周波数は、信号 $U_{LOAD206}$ の大きさとともに変動する。本発明の教示によれば、平均スイッチング周波数は、負荷126に応答して調整される。具体的には、平均スイッチング周波数は、少なくとも半ラインサイクル以上にわたる平均スイッチング周波数として規定される。したがって、平均スイッチング周波数は、PFC回路の制御方式が可変スイッチング周波数を実現するときでも調整することができる。セグメント1に示すように、負荷信号 $U_{LOAD206}$ は最大の大きさにあり、最高平均スイッチング周波数にあるスイッチング信号 $U_{SW119}$ に対応する。セグメント2に示すように、負荷信号 $U_{LOAD206}$ は大きさが低下し、より低い平均スイッチング周波数を有するスイッチング信号 $U_{SW119}$ に対応する。セグメント3に示すように、負荷信号 $U_{LOAD206}$ はさらに大きさが低下し、より一層低い平均スイッチング周波数を有するスイッチング信号 $U_{SW119}$ に対応する。図3Aに示すように、スイッチング入力電流波形306は、入力電流 $I_{IN111}$ を連続導通モードで示す。具体的には、連続導通モードは、エネルギー伝達素子 $L_{1114}$ のエネルギーがゼロになる前にスイッチ $SW_{118}$ がオンすることから入力電流 $I_{IN111}$ がスイッチングサイクル中にゼロに達することを防ぐように実現されるスイッチング制御技術である。PFCコンバータ100への入力はac信号であるため、入力電圧がゼロのときは、ac入力電流は連続導通モードにおいてもゼロになることが理解されるであろう。不連続導通モード制御技術は、各スイッチングサイクルの各オフ期間中に入力電流 $I_{IN111}$ がゼロになることをPFCコントローラ102が防ぐように実現され得る。本発明に係る一実施例において、平均スイッチング周波数が低下すると、PFCコントローラ102は連続導通動作モードから不連続動作モードに切換り得る。逆に、平均スイッチング周波数が上昇すると、入力電流 $I_{IN111}$ は不連続動作モードから連続動作モードに移行し得る。

#### 【0023】

図3Bに示すように、拡大図314は、連続導通モードにおける図3Aの入力電流波形306の一部分を示す。図示のように、dc入力電流 $I_{IN111}$ は、スイッチのオン期間中のスイッチング電流 $I_{SW216}$ に対応する。動作の際、入力電流 $I_{IN111}$ は、コントローラ102によって決定される第1のオン期間 $T_{ON1318}$ と第1のオフ期間 $T_{OFF1320}$ とに対応して、第1のスイッチングサイクル期間 $T_{SW1316}$ の間制御される。拡大図314に例示されるように、スイッチングサイクル $T_{SW1}$ 、 $T_{SW2}$ および $T_{SW3}$ は、PFC改善のためにコントローラ102によって実現される可変周波数制御技術によって変動される。したがって、本発明の一実施例によれば、コントローラ102は、変動する負荷に応答して複数のラインサイクルにわたってスイッチ $SW_{118}$ の平均スイッチング周波数を調整し得、また、スイッチングサイクル周波数によりサイクルを調整して、出力電圧を調節し、PFCへの入力電圧 $V_{IN110}$ に従うように入力電流 $I_{IN111}$ を制御し得る。

10

20

30

40

50

## 【0024】

図4A、図4B、図4Cおよび図4Dを参照し、平均スイッチング周波数は、PFCコンバータ100の負荷に応答してさまざまなやり方で調整され得る。図4Aでは、スイッチSW<sub>1</sub>118の平均スイッチング周波数は、負荷126とともに直線的にかつ連続して変動する。図4Bでは、スイッチSW<sub>1</sub>118の平均スイッチング周波数は、負荷126とともに指数関数的にかつ連続して変動する。図4Cでは、スイッチSW<sub>1</sub>118の平均スイッチング周波数は、負荷126とともに直線的にかつ離散的に変動する。本発明の実施例によれば、図4A、図4Bおよび図4Cに例示されるように、平均スイッチング周波数は昇圧コンバータの負荷範囲全体にわたって調整される。つまり、平均スイッチング周波数は、最小負荷状態に応答して最低周波数となり得、昇圧コンバータの最大負荷状態に応答して最高周波数となり得る。別の実施例では、図4Dに示されるように、平均スイッチング周波数は、負荷範囲全体の一部分にわたって直線的にかつ連続して調整される。本発明の別の実施例において、スイッチSW<sub>1</sub>118の平均スイッチング周波数と負荷126との関係を決定するために、図4A、図4B、図4Cおよび図4Dをいずれかの種類の組合せで組合せてもよい。

## 【0025】

図5Aを参照し、PFCを実現するために特定の制御技術を利用し、かつ本発明の教示に従って効率を向上させるためにスイッチング周波数調整装置501をさらに含む、例示的な集積回路コントローラ500を示す。この例では、パワーMOSFET502がオン状態とオフ状態との間で切換わり、ドレイン端子D504とソース端子S506との間の入力電流I<sub>IN</sub>503の流れを可能にしたり妨げたりする。電圧端子V<sub>IN</sub>507は、入力電圧信号V<sub>IN</sub>110を受取るように結合される。図示のように、入力電圧検出器508は、PFCコンバータ100の瞬間的なdc入力電圧を表わす電流I<sub>VIN</sub>512を出力する。動作の際、生成された電流信号I<sub>VIN2</sub>513が入力電圧検出器508から引出される。本発明の実施例の教示によれば、生成された電流信号I<sub>VIN2</sub>513は、半ラインサイクルのピーク入力電圧、または入力電圧の実効値(rms value)、または半サイクルの平均入力電圧を表わし得る。フィードバック端子FB514は、PFCコンバータ100の出力における出力電圧を表わす電圧V<sub>VOUT</sub>を受取る。一例において、電圧V<sub>VOUT</sub>はいずれかの一定値であり得る。

## 【0026】

図示のように、基準電流I<sub>REF</sub>は、電流源522から流れる変倍された電流I<sub>SVIN</sub>の反対方向に、電流源520から流れる。具体的には、変倍された電流I<sub>SVIN</sub>は、信号処理のための変倍係数で乗算した電流I<sub>VIN</sub>に等しい。キャパシタC<sub>OFF</sub>524は、トランジスタT<sub>OFF</sub>526の両端に結合される。動作の際、キャパシタC<sub>OFF</sub>524は、トランジスタT<sub>OFF</sub>526がオフのときに充電する。具体的には、キャパシタC<sub>OFF</sub>524を充電する電流は、基準電流I<sub>REF</sub>と変倍された電流I<sub>SVIN</sub>との差である。トランジスタT<sub>OFF</sub>526がオンになると、キャパシタC<sub>OFF</sub>524は共通帰線529を介して放電する。電圧比較器528は、比較器528の負端子がキャパシタC<sub>OFF</sub>524と同じ電位の電圧となるようにキャパシタC<sub>OFF</sub>524に結合される。キャパシタC<sub>OFF</sub>524の電圧が調整されたエラー電圧信号V<sub>ERR</sub>530に等しいとき、電圧信号V<sub>OFF</sub>532がローからハイに遷移し、その結果パワーMOSFET502がオン状態に遷移する。このように、パワーMOSFET502のスイッチングサイクルのオフ期間が調整される。本発明の一実施例において、キャパシタC<sub>OFF</sub>524は、パワーコンバータの定電圧と入力電圧との差を積分してスイッチングサイクルのオフ期間を決定する積分器として機能する。

## 【0027】

動作の際、図示の例において、エラー電圧信号V<sub>ERR</sub>531はエラーアンプ533の出力である。動作の際、エラーアンプ533は、電圧V<sub>VOUT</sub>を基準電圧V<sub>REF</sub>535と比較して、パワーコンバータの出力における出力電圧を表わすエラー電圧信号V<sub>ERR</sub>531を決定する。本発明の一実施例によれば、エラー電圧信号V<sub>ERR</sub>531は、パワーコンバータ100の出力電圧と、コントローラの出力における負荷とを示す。本発明の教示によれ

ば、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  は、スイッチング信号  $U_{SW\ 1\ 1\ 9}$  (たとえば駆動信号 5 5 4) と比較して実質的により低速な応答時間有するように設計される。たとえば、一実施例において、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  は、1 ラインサイクルにわたって入力電流を制御する際に出力電圧  $V_{OUT\ 1\ 2\ 4}$  が実質的に一定値と考えられるように、数ラインサイクルにわたる出力電圧  $V_{OUT\ 1\ 2\ 4}$  の平均された大きさを表わす平均値である。

### 【0028】

具体的には、この例において、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  は、1 ラインサイクルの出力電圧  $V_{OUT\ 1\ 2\ 4}$  における a c 時間変動には実質的に応答しない。エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  は複数のスイッチングサイクルにわたって実質的に一定であると想定することもできる。一例において、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  は、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  の応答時間を調整する利得設定フィルタに COMP 端子 5 3 7 を介して出力され得る。10

### 【0029】

例に示すように、スイッチング周波数調整装置 5 0 1 は、エラー増幅器 5 3 3 の出力と比較器 5 2 8 の非反転端子との間に結合される。スイッチング周波数調整装置 5 0 1 は、図 2 のスイッチング周波数調整装置 2 0 4 の可能な実現例の 1 つであり、集積回路コントローラ 5 0 0 の残りの回路の一部またはすべては、PFC 回路 2 0 2 の可能な実現例である。動作の際、スイッチング周波数調整装置 5 0 1 は、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  の受取りに応答して、調整されたエラー電圧信号  $V_{ERR\ 5\ 3\ 0}$  を出力する。本発明の実施例に係る一例において、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  は以下の式に基づいて修正される：

$$V_{ERR} = V_C - V_{ERR} \quad \dots \text{式 1} \quad \text{20}$$

ここで  $V_C$  は、PFC コンバータ 1 0 0 のフィードバックループの設計パラメータに基づいて決定される一定値である。本発明の教示によれば、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  は図 2 に示した負荷信号  $U_{LOAD\ 2\ 0\ 6}$  に等しいと考えることができる。具体的には、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  の大きさは、パワーコンバータの出力における負荷に正比例する。典型的に、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  の大きさは、入力電圧を変動させることと負荷状態を変化させることによって影響され得、したがってエラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  の大きさとパワーコンバータの出力における負荷状態との正比例関係は成立させるのが困難であり得る。本発明の実施例によれば、入力電圧検出器が、平均入力電圧値を表わしかつ電流源 5 3 4 で乗算される信号電流  $I_{VIN\ 2}$  を生成して、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  の大きさに対する入力電圧の効果をオフセットする。換言すると、電流  $I_{VIN\ 2}$  は、エラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  が入力電圧  $V_{IN\ 1\ 1\ 1}$  に依存しないようにフィードフォワードシステムにおいて電流源 5 3 4 に乗算され、かつ PFC コンバータ 1 0 0 の出力に結合された負荷 1 2 6 を表わし得る。本発明に係る一実施例において、調整されたエラー電圧信号  $V_{ERR\ 5\ 3\ 0}$  は、図 2 の周波数調整信号  $f_{ADJ\ 2\ 0\ 8}$  に等しいと考えることができる。30

### 【0030】

本発明に係る別の実施例において、スイッチング周波数調整装置 5 0 1 は、エラー増幅器 5 3 3 と電圧比較器 5 4 4 の正入力端子との間に結合される。この例の動作の際、調整されたエラー電圧信号  $V_{ERR\ 5\ 3\ 0}$  は電圧比較器 5 4 4 によって受取られる。

### 【0031】

図 5 A の例に示すように、電流源 5 3 4 は、信号処理のための変倍係数で乗算した検知入力電流  $I_{S\ 5\ 3\ 8}$  を表わす変倍された電流  $I_{SIIN}$  を出力する。キャパシタ  $C_{ON\ 5\ 4\ 0}$  はトランジスタ  $T_{ON\ 5\ 4\ 2}$  の両端に結合される。動作の際、トランジスタ  $T_{ON\ 5\ 4\ 2}$  がオフのときには変倍された電流  $I_{SIIN}$  がキャパシタ  $C_{ON\ 5\ 4\ 0}$  を充電する。トランジスタ  $T_{ON\ 5\ 4\ 2}$  がオンのときには、キャパシタ  $C_{ON\ 5\ 4\ 0}$  は共通帰線 5 2 9 を介して放電する。電圧比較器 5 4 4 は、比較器 5 4 4 の負の入力がキャパシタ  $C_{ON\ 5\ 4\ 0}$  と同じ電位の電圧となるようにキャパシタ  $C_{ON\ 5\ 4\ 0}$  に結合される。キャパシタ  $C_{ON\ 5\ 4\ 0}$  の電圧がエラー電圧信号  $V_{ERR\ 5\ 3\ 1}$  に等しいとき、比較器 5 4 4 の出力における電圧信号  $V_{ON\ 5\ 4\ 6}$  はロー信号からハイ信号に遷移し、その結果パワー MOSFET 5 0 2 がオフ状態に設定される。このように、パワー MOSFET 5 0 2 のスイッチングサイクルのオン期間が制御される。本発明の一局面において、キャパシタ  $C_{ON\ 5\ 4\ 0}$  は、パワーコンバータの入力電流4050

を積分してスイッチングサイクルのオン期間を決定する積分器として機能する。

### 【0032】

#### 【数1】

図5Aの例に示すように、ORゲート548の第1の入力は比較器544の出力に結合され、ORゲート548の第2の入力はANDゲート550の出力に結合される。動作の際、電圧信号 $V_{ON\ 5\ 4\ 6}$ がハイに遷移するかまたは過電流保護(OCP)信号553がハイに遷移すると、ORゲート548はラッチ552のリセット(R)にハイ信号を出力する。動作の際、ラッチ552のリセット入力Rがハイ信号を受取ると、出力Qはハイに設定され、相補出力 $\bar{Q}$ はローに設定される。逆に、電圧信号 $V_{OFF\ 5\ 3\ 2}$ がハイに遷移すると

、ラッチ552の入力Sは出力Qをローに設定し、相補出力 $\bar{Q}$ はハイに設定される。このように、相補出力 $\bar{Q}$ は、パワーMOSFET502のスイッチングを制御する駆動信号D R I V E 5 5 4を出力する。パワーMOSFET502のゲートを充放電するのに適切な電流を供給してパワーMOSFET502のスイッチングを制御するために、増幅器556が駆動信号D R I V E 5 5 4を増幅する。

### 【0033】

この例に示すように、電流制限比較器558は、検知された入力電流 $I_{S\ 5\ 3\ 8}$ を電流制限基準 $I_{LIM\ 5\ 5\ 9}$ と比較する。一例において、検知された入力電流 $I_{S\ 5\ 3\ 8}$ が電流制限基準 $I_{LIM\ 5\ 5\ 9}$ に達すると、電流制限比較器558の出力はハイになる。具体的には、この例において、検知された入力電流 $I_{S\ 5\ 3\ 8}$ は入力電流 $I_{IN\ 5\ 0\ 3}$ の一部分である。一例において、検知された入力電流 $I_{S\ 5\ 3\ 8}$ は本発明の教示に係る入力電流 $I_{IN\ 5\ 0\ 3}$ を表わす。一例において、駆動信号554は、ANDゲート550の入力に与えられる前に、立上がりエッジ帰線消去(leading edge blanking: LEB)回路562によって遅延され、パワーMOSFET502がオンとなるために漂遊容量を一時的に放出するとき、過電流保護信号553が誤った電流制限条件を示すことを防ぐ。具体的には、過電流保護信号553は、パワーMOSFET502の電流が電流制限基準 $I_{LIM\ 5\ 5\ 9}$ にいつ達したかを示し、パワーMOSFET502および/または集積回路500のいずれかの他の内部構成要素への損傷を防ぐ。

### 【0034】

上記のように、本発明の教示は、パワーコンバータの入力電流波形を整形するための制御技術をパワーコンバータが採用することを可能とする。また、平均周波数調整回路501は、全負荷範囲に沿ってMOSFET502の平均スイッチング周波数を調整してコントローラにおける損失を制限するために含まれる。上記の例では、PFCコントローラは、パワーコンバータのパワースイッチのオン期間とオフ期間とを変動させることによって、入力電圧波形の形状に従うように入力電流波形を制御する。具体的には、入力電流は、各半ラインサイクルの入力電圧に正比例するように制御される。しかし、複数の半ラインサイクルにわたって入力電流が平均される場合は、入力電流 $I_{IN\ 1\ 1\ 1}$ は入力電圧 $V_{IN\ 1\ 1\ 0}$ に比例しなくなる。具体的には、制御技術は、オフ期間について一定のボルト・秒を設定することによって、パワースイッチのオン期間を整流された時間変動入力電圧 $V_{IN}(t)$ に反比例させる。オフ期間は以下の式の一定の積となるように制御される：

$$(V_{OUT} - V_{IN}) \times T_{OFF} \quad \dots \text{式2}$$

特に、オフ期間中に以下の量：

$$V_{OUT} - V_{IN} \quad \dots \text{式3}$$

を積分することによって、オフ期間中に一定のボルト・秒を設定することが可能となる。

10

20

30

40

50

昇圧インダクタの特性を満たすボルト - 秒の均衡を維持するために、一定のボルト - 秒を有するようにオフ期間を設定することによって、オン期間のボルト - 秒を数スイッチングサイクルにわたって実質的に一定とする。昇圧インダクタのボルト - 秒の均衡は、オン期間を入力電圧に実質的に反比例させることを可能とする。入力電圧に対するオン期間との関係は、入力ライン電圧を表わす整流された時間変動入力電圧  $V_{IN}(t)$  の関数として入力電流を制御するための好都合かつ単純な手段をもたらす。オン期間中に入力電流を積分することによって入力電流が検知されると、以下の一定の積分値に達することによってオン期間を終了させることができる：

【0035】

【数2】

10

$$\int_{T_1}^{T_2} I_{INPUT} dt \quad \text{式4}$$

【0036】

ここで  $T_1$  から  $T_2$  の継続時間は、数スイッチングサイクルにわたって実質的に一定のフィードバック信号によって決定されるオン期間である。これにより、1スイッチングサイクルの平均入力電流は、入力電圧に実質的に比例することになる。

【0037】

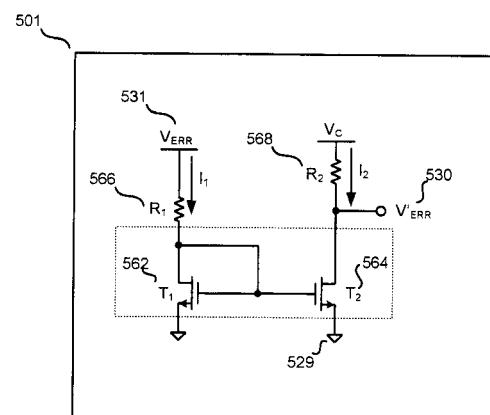

図5Bを参照し、例示的なスイッチング周波数調整装置501は、本発明の教示に係るカレントミラー560を含む。図示のように、カレントミラー560は、第2のトランジスタT2 564のゲートに結合された第1のトランジスタT1 562のゲートをさらに含む。動作の際、カレントミラー560は第1の電流  $I_1$  を受取り、第2のトランジスタT2 564を介して第2の電流  $I_2$  を制御する。具体的には、エラー電圧信号  $V_{ERR\ 531}$  が第1の抵抗器R1 566によって第1の電流  $I_1$  に変換され、第2の電流  $I_2$  は、カレントミラー構成により第1の電流  $I_1$  に比例する。換言すると、第1の電流  $I_1$  が増加すると、第2の電流  $I_2$  は比例して増加する。第2の抵抗器R2 568は、図5Aで述べた定電圧  $V_C$  を第2の電流  $I_2$  に変換する。調整されたエラー電圧信号  $V_{ERR\ 530}$  が決定される。例示的な動作において、調整されたエラー電圧信号  $V_{ERR\ 530}$  の上昇によって第1の電流  $I_1$  が増加すると、比例して第2の電流  $I_2$  が増加する。第2の電流  $I_2$  が増加すると、第2の抵抗器R2 568の両端の電圧降下が増大し、それゆえ調整されたエラー電圧信号  $V_{ERR\ 530}$  の大きさが低下する。図5Aの実施例によれば、図5Aの例示的な制御回路に示すように、調整されたエラー電圧信号  $V_{ERR\ 530}$  はオフ期間を決定するためのしきい値として機能するため、調整されたエラー電圧信号  $V_{ERR\ 530}$  は、スイッチングサイクル中にパワースイッチSW1 118のオフ期間を変動させることによって、スイッチの平均スイッチング周波数を調整する。

20

30

【0038】

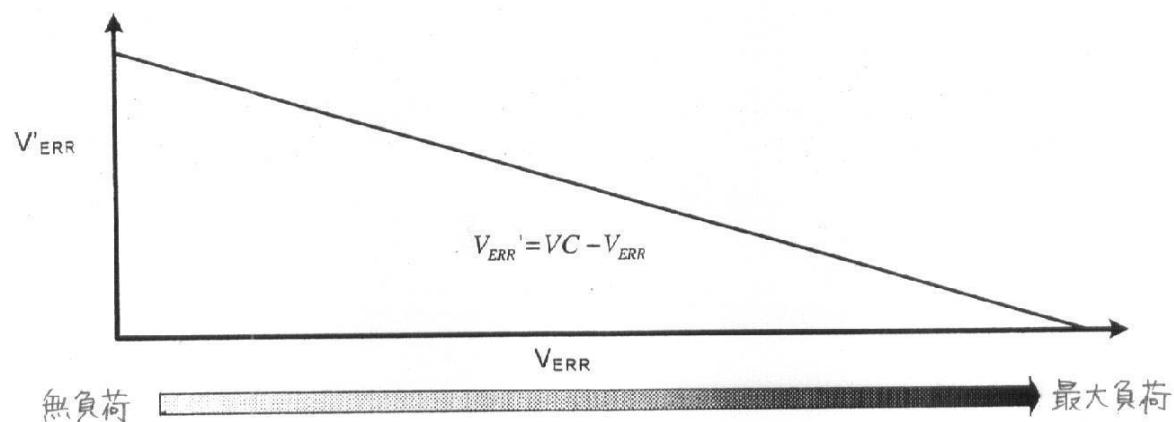

図6Aを参照し、例示的なグラフ600は、本発明の実施例に係る平均周波数調整装置501によって実現されるエラー電圧信号  $V_{ERR\ 531}$  の関数である調整されたエラー電圧信号  $V_{ERR\ 530}$  の関数的関係をさらに例示する。一例において、エラー電圧信号  $V_{ERR\ 531}$  は負荷信号  $U_{LOAD\ 206}$  を表わし、調整されたエラー電圧信号  $V_{ERR\ 530}$  は周波数調整信号  $f_{ADJ\ 208}$  を表わす。図示のように、エラー電圧信号  $V_{ERR\ 531}$  の大きさは、負荷が増大するにつれて上昇する。逆に、負荷が低減するにつれて調整されたエラー電圧信号  $V_{ERR\ 530}$  は低下する。上記のように、一例において、エラー電圧信号  $V_{ERR\ 531}$  、調整されたエラー電圧信号  $V_{ERR\ 530}$  および定電圧  $V_C$  の関係は以下のとおりである：

$$V_{ERR} = V_C - V_{ERR} \quad \dots \text{式5}$$

40

ここで  $V_C$  は、PFCコンバータ100のフィードバックループの設計パラメータに応じて選択される定電圧である。本発明の教示に係る代替的な実施例において、グラフ600は、図4A、図4B、図4Cおよび図4Dに例示した平均スイッチング周波数と負荷との間の他の関数的関係、またはそれらの組合せに類似し得る。

50

## 【0039】

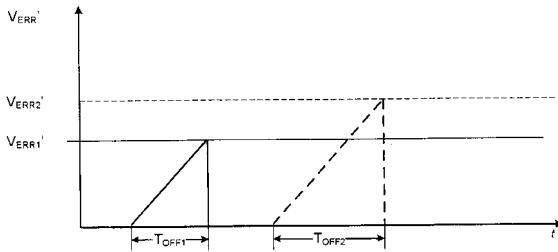

図6Bを参照し、グラフ650は、第1の調整されたエラー電圧 $V_{ERR1}$ および第2の調整された電圧 $V_{ERR2}$ を例示する。図示のように、調整されたエラー電圧信号 $V_{ERR}$ 530は負荷と逆の関係を有し、したがって、調整されたエラー電圧信号 $V_{ERR530}$ が $V_{ERR1}$ から $V_{ERR2}$ に増加するときには、PFCコンバータ100の出力において低減する負荷を表わす。

## 【0040】

図5に戻り、調整されたエラー電圧しきい値 $V_{ERR530}$ が上昇すると、上昇した調整しきい値をキャパシタ $C_{OFF524}$ の両端電圧が満たすにはより長い時間がかかり、したがってMOSFET502が再びオンする時間が遅延し、それゆえスイッチングサイクルのオフ期間が長くなる。このように、PFCコンバータ100の出力における負荷126が低減すると、平均スイッチング周波数が低下する。集積コントローラ500において実現される制御技術により、各スイッチングサイクルのオン期間も同じデューティ比を維持するように延ばされる。逆に、電圧比較器528の正端子に結合された調整電圧基準が負荷126によって上昇すると、平均スイッチング周波数を上昇させることができ、それゆえ $C_{ON540}$ を充電するのにかかる時間が短縮され、オフ期間の短縮につながる。

## 【0041】

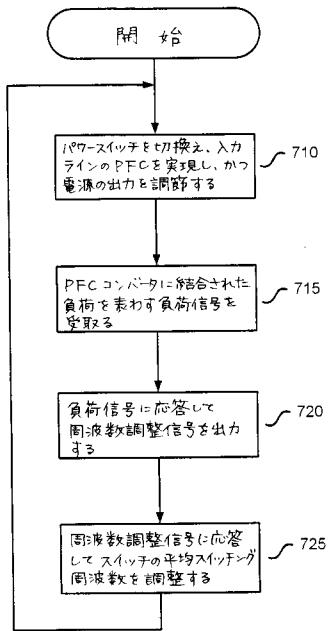

図7は、本発明の教示に係る変動する負荷状態に応答してスイッチング周波数を調整するための例示的な方法を例示するフローチャートである。処理ブロック710において、スイッチSW<sub>118</sub>が切換えられ、入力電流 $I_{IN111}$ が入力電流 $V_{IN110}$ に正比例するように出力電圧を調節しつつ力率改善を実現する。次の処理ブロック715において、PFC回路212は、負荷126を表わす負荷信号 $U_{LOAD206}$ を平均周波数調整装置204に出力する。次の処理ブロック720において、スイッチング周波数調整装置は周波数調整信号 $f_{ADJ208}$ をPFC回路に出力し、負荷信号 $U_{LOAD206}$ に応答して平均スイッチング周波数を調整する。次の処理ブロック725において、PFC回路は、PFCコンバータ100の出力に結合された負荷126に応答してパワースイッチSW<sub>118</sub>の平均スイッチング周波数が調整されるように、スイッチング信号 $U_{SW119}$ を調整する。決定ブロック725の実行後、処理は処理ブロック710に戻る。

## 【0042】

要約書に記載されるものを含む例示した本発明の例の上記の説明は、網羅的であるように意図されるものではなく、または開示した厳密な形態に限定されるように意図されるものではない。本発明の具体的な実施例および例は本明細書において例示の目的で記載されており、本発明のより広い精神および範囲から逸脱することなく、種々の等価の変形が可能である。

## 【0043】

これらの変形は、上記の詳細な説明に鑑みて、本発明の例に対してなされることができる。以下の特許請求の範囲の中で用いられる用語は、明細書および特許請求の範囲に開示されている具体的な実施例に本発明を限定するように解釈されるべきではない。むしろ、その範囲は専ら以下の特許請求の範囲によって決まり、特許請求の範囲は、確立されたクレーム解釈の原理に従って解釈される。したがって、本明細書および図面は限定的ではなく例示的であると見なされる。

## 【符号の説明】

## 【0044】

100 力率改善コンバータ、102 コントローラ、118 パワースイッチ、126 負荷、202 力率改善回路、204 スイッチング周波数調整装置。

【図1】

【図2】

【図3A】

【図3B】

【図4A】

【図4B】

【図4D】

【図4C】

【図 5 A】

【図5B】

【図 6 B】

【図 7】

【図 6 A】

---

フロントページの続き

(74)代理人 100109162

弁理士 酒井 將行

(74)代理人 100111246

弁理士 荒川 伸夫

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 ローランド・シリビエ・サン・ピエール

アメリカ合衆国、95135 カリフォルニア州、サン・ノゼ、リトルワース・ウェイ、4233

審査官 構木澤 昌司

(56)参考文献 米国特許第6768655(US, B1)

特開2007-181362(JP, A)

特開2005-218224(JP, A)

国際公開第2004/019473(WO, A1)

特開2000-224849(JP, A)

米国特許出願公開第2007/0133234(US, A1)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155

H02M 3/28