(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-214296

(P2013-214296A)

(43) 公開日 平成25年10月17日(2013.10.17)

(51) Int.Cl.

**G06F 1/32 (2006.01)**

**H01L 21/822 (2006.01)**

**H01L 27/04 (2006.01)**

**H01L 29/786 (2006.01)**

F 1

GO6F 1/00 332B

H01L 27/04 D 5FO38

H01L 29/78 618B 5F11O

H01L 29/78 613B

テーマコード(参考)

5B011

5FO38

5F11O

審査請求 未請求 請求項の数 6 O L (全 33 頁)

(21) 出願番号 特願2013-42571 (P2013-42571)

(22) 出願日 平成25年3月5日 (2013.3.5)

(31) 優先権主張番号 特願2012-50085 (P2012-50085)

(32) 優先日 平成24年3月7日 (2012.3.7)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 5B011 DC01 EA08 EB01 JA04 KK01

KK03 LL01 MB16

5F038 AZ08 CA16 CD16 DF03 DF04

DF05 DF08 EZ13 EZ14 EZ15

EZ17 EZ20

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【要約】 (修正有)

【課題】パワーゲーティングを用いた半導体装置において、消費電力が削減された半導体装置を提供する。

【解決手段】パワーゲーティングが可能であり、複数の回路ブロックを有する半導体集積回路100に温度センサを複数配置し、各温度センサによって各回路ブロックの温度を検出して、各回路ブロックにおいて当該温度に対応した最適なオフ期間を設定する。具体的には、演算回路105、107と、演算回路によって得られたデータを保持する記憶回路109、111と、演算回路に対する電源電圧の供給を制御する電源供給制御スイッチ101、103と、記憶回路の温度を検出し、当該温度に応じたオーバーヘッドを導出する温度検出回路113、115と、オーバーヘッドよりも削減できる消費電力が大きい場合、前記電源電圧の供給を遮断する期間を設定し、電源供給制御スイッチを制御するコントローラ117と、を有する半導体装置である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

演算回路と、

前記演算回路によって得られたデータを保持する記憶回路と、

前記演算回路に対する電源電圧の供給を制御する電源供給制御スイッチと、

前記記憶回路の温度を検出し、前記温度に応じたオーバーヘッドを導出する温度検出回路と、

前記オーバーヘッドよりも削減できる消費電力が大きい場合、前記電源電圧の供給を遮断する期間を設定し、前記電源供給制御スイッチを制御するコントローラと、を有する半導体装置。

10

**【請求項 2】**

演算回路と、

キャッシュメモリと、

前記演算回路によって得られたデータ、及び、前記キャッシュメモリに記憶されたデータを保持する記憶回路と、

前記演算回路及び前記キャッシュメモリに対する電源電圧の供給を制御する電源供給制御スイッチと、

前記記憶回路の温度を検出し、前記温度に応じたオーバーヘッドを導出する温度検出回路と、

前記オーバーヘッドよりも削減できる消費電力が大きい場合、前記電源電圧の供給を遮断する期間を設定し、前記電源供給制御スイッチを制御するコントローラと、を有する半導体装置。

20

**【請求項 3】**

請求項 1 又は請求項 2 において、

前記記憶回路は、不揮発性を有する半導体記憶装置を有する半導体装置。

**【請求項 4】**

請求項 3 において、

前記半導体記憶装置は、チャネル形成領域が酸化物半導体によって構成されるトランジスタを有する半導体装置。

30

**【請求項 5】**

請求項 1 乃至請求項 4 のいずれか一において、

前記電源供給制御スイッチは、チャネル形成領域が酸化物半導体によって構成されるトランジスタを有する半導体装置。

**【請求項 6】**

請求項 1 乃至請求項 5 のいずれか一において、

前記電源電位を供給する配線と、前記演算回路及び前記キャッシュメモリの一方又は双方との電気的な接続を前記電源供給制御スイッチが有するトランジスタのスイッチングによって、前記演算回路及び前記キャッシュメモリの一方又は双方に対する電源電圧の供給を制御する半導体装置。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用して機能し得る装置全般をいい、例えば、トランジスタなどの半導体素子を含む半導体集積回路、表示装置などの電気光学装置、及び電子機器は全て半導体装置である。

**【背景技術】****【0003】**

論理回路を有する半導体集積回路は、年々その回路規模が拡大している。集積回路が誕

50

生した時には数素子によって構成されていたものが、CPU(Central Processing Unit)及びDSP(Digital Signal Processor)などは、数千万の素子によって構成されるものも存在している。

#### 【0004】

これらCPU及びDSPを構成する素子は、微細化及び低駆動電圧化によって、素子1個あたりの消費電力は下がってきているが、それ以上に素子数が増加しているため、集積回路全体の消費電力は増加しつつある。

#### 【0005】

集積回路の消費電力を下げる方法として、部分的にクロックを止めるクロックゲーティング、クロックの周波数を下げる方法、及び部分的に電源電圧を下げる方法などが開発されている。

10

#### 【0006】

また、消費電力には、トランジスタなどの素子がスイッチングすることにより生じる充放電などに起因した動作電力のみならず、当該素子のオフ状態におけるリーク電流などに起因した静止電力も含まれる。素子数が少ない集積回路における静止電力は、ほとんど無視できるが、素子数が膨大な集積回路における静止電力は無視できない大きさである。そこで、大きな静止電力を有する集積回路において、集積回路に含まれる回路に対する電源電圧の供給をスイッチ(電源供給制御スイッチ又はパワーゲートともいう。)によって制御する方法(パワーゲーティング)が開発されている。これによって、トランジスタなどの素子のリーク電流による静止電力、さらには集積回路の消費電力を削減することが可能である。

20

#### 【0007】

例えば、パワーゲーティングを行うことが可能な半導体集積回路が開示されている(特許文献1)。具体的には、論理回路と、電源供給ラインとの間にトランジスタを有し、該トランジスタのスイッチングを制御することで当該論理回路に対する電源電圧の供給を制御することが可能な半導体集積回路が開示されている。

30

#### 【0008】

他にも、例えば、電源供給の不要な期間において、CPU及びメモリなどに対する電源電圧の供給を停止することが可能なマイクロコンピュータなどが開示されている(特許文献2)。

30

#### 【先行技術文献】

##### 【特許文献】

##### 【0009】

【特許文献1】特開2005-268694号公報

【特許文献2】特開2009-116851号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0010】

パワーゲーティングによって、CPUなどの半導体集積回路の消費電力の削減を行う場合、半導体集積回路に搭載された不揮発性を有する半導体記憶装置(不揮発性メモリとも記載する)にデータを転送する際、オーバーヘッドとして余分な電力を消費する。具体的には、不揮発性メモリの書き込み及び読み出しの処理においてオーバーヘッドとして余分な電力を消費する。

40

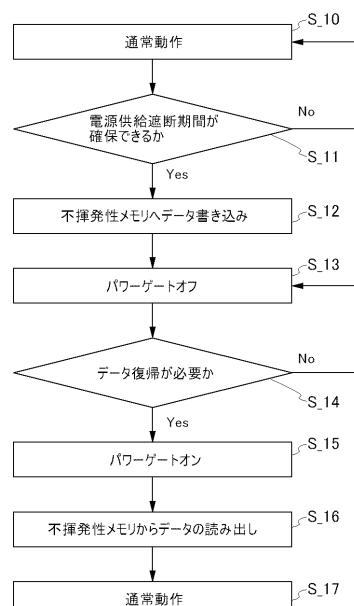

##### 【0011】

ここで、パワーゲーティングの一例について、図15に示したフローチャートを参照して説明する。

##### 【0012】

まず、電源供給制御スイッチを有してパワーゲーティングが可能な集積回路が、ある一定の動作速度で動作しているものとする。なお、便宜上、この動作を通常動作という(ステップS\_10)。

50

## 【0013】

通常動作している集積回路のうち、例えば演算回路において電源供給は行われているが処理は行われていない場合、当該演算回路に対する電源供給を遮断する期間（電源供給遮断期間）を確保できるか否かを判別する（ステップS\_11）。電源供給遮断期間は演算回路が動作していないとき（例えば、動作クロックが入力されていないとき）に確保することができるため、この判別は演算回路の動作速度とデータを不揮発性メモリに書き込む又は読み出す際のオーバーヘッドとの兼ね合いによって行われる。当該演算回路に対する電源供給遮断期間を確保できる場合は、電源供給遮断期間が始まる前に演算回路によって得られたデータを不揮発性メモリに書き込む（ステップS\_12）。なお、当該演算回路に対する電源供給遮断期間を確保できない場合は通常動作のままとする（ステップS\_10）。

10

## 【0014】

不揮発性メモリにデータを書き込んだ後、演算回路と電源の間に設けられた電源供給制御スイッチを切ることで演算回路に対する電源供給を遮断する（ステップS\_13）。

## 【0015】

電源供給制御スイッチをオフした後、書き込まれたデータの復帰を必要とするか否かを判別する（ステップS\_14）。この判別は、演算回路を再び動作させるときまで行われる。演算回路を再び動作させる期間ではなく、データの復帰が必要ない場合においてパワーゲートはオフしたままである（ステップS\_13）。従って、演算回路を再び動作させるときまで演算回路に対する電源供給は遮断されることになる。

20

## 【0016】

その後、演算回路を再び動作させるときなどデータの復帰を必要とする場合、電源供給制御スイッチをオンして演算回路に対する電源供給を再開する（ステップS\_15）。

## 【0017】

その後、不揮発性メモリから転送されていたデータを読み出し、当該データを演算回路に戻し（ステップS\_16）、通常動作に戻る（ステップS\_17）。

## 【0018】

また、オーバーヘッドは不揮発性メモリを構成する素子の電気特性によって決まるため、半導体集積回路が形成されたチップの温度が変動して素子の電気特性が変化すると、オーバーヘッドの量も変動する。

30

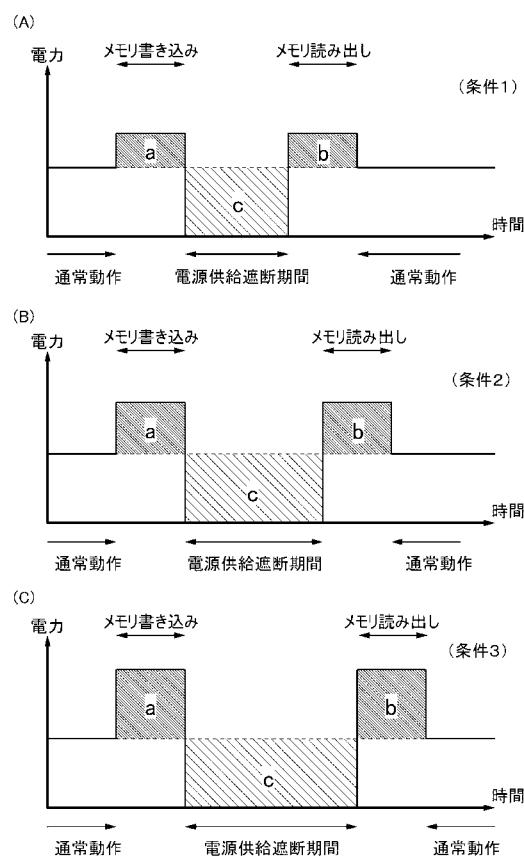

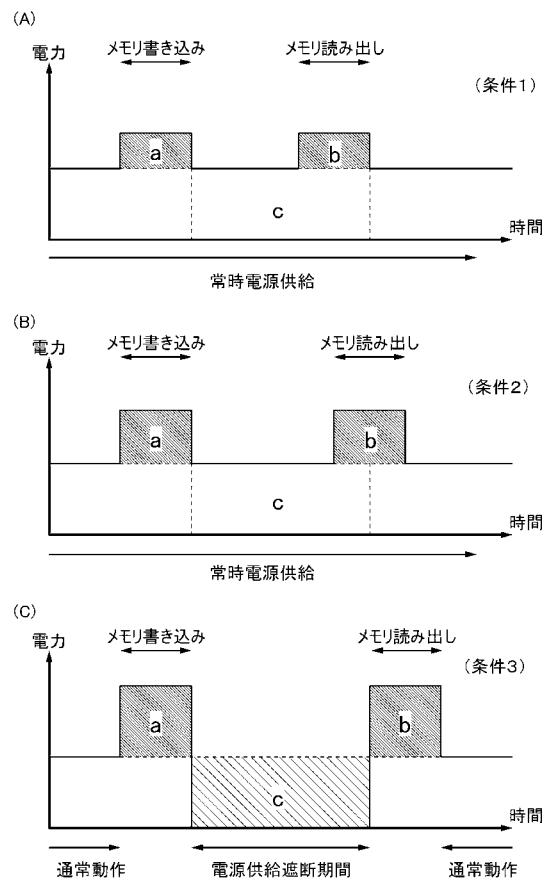

## 【0019】

それゆえ、上記パワーゲーティングにおいて、半導体集積回路への電源供給をオフするか否かの選択は、素子の温度依存性を含めた電気特性が最も悪い場合を想定して決める。図16（A）、（B）、（C）は上記パワーゲーティングとオーバーヘッドの関係を示した図である。なお、図16（A）、（B）、（C）において、横軸は時間を表し、縦軸は消費電力を表す。また、図16（A）は、不揮発性を有する半導体記憶装置（以下、不揮発性メモリとも記載する）、及び不揮発性メモリを制御する周辺回路の温度が条件1である場合の図であり、図16（B）は条件2である場合の図であり、図16（C）は条件3の場合の図である。不揮発性メモリ及び周辺回路の温度は、低い方から順に条件1、2、3とし、不揮発性メモリ及び周辺回路の動作速度は、遅い方から順に条件3、2、1とする。

40

## 【0020】

図16（A）、（B）、（C）において、a及びbの領域がオーバーヘッドを表し、cの領域がパワーゲーティングによって削減できる電力を表す。パワーゲーティングを行って消費電力を削減するためには、オーバーヘッドの和よりパワーゲーティングを行って削減できる消費電力が大きい必要があり、図16（A）、（B）、（C）において、 $a + b < c$ の関係を満たす必要がある。上記関係に満たない場合は、むしろ消費電力の増大を招くことになる。

## 【0021】

また、不揮発性メモリ及び周辺回路の温度が高くなるにつれて、不揮発性メモリのオ-

50

バー・ヘッドは大きくなる。図16( C )に示した条件3の場合が、オーバー・ヘッドは最も大きく、この場合においても  $a + b < c$  の関係を満たすとき、半導体集積回路の消費電力を削減できる。上記パワーゲーティングは、素子の電気特性が最も悪い、換言するとオーバー・ヘッドが最も大きい場合において  $a + b < c$  の関係が成り立つときに電源供給を遮断する。それゆえ、例えばオーバー・ヘッドが小さい状況下で高速動作させている場合、電源供給を遮断することができる期間があっても電源供給を遮断できず、高速動作させている間は常に電源が供給されたままになる。このように、オーバー・ヘッドが最も大きい場合に合わせて電源供給を遮断するため、温度が低くオーバー・ヘッドが小さい状態で動作する場合においては、電源供給を遮断することで消費電力削減の効果があるにも関わらず、上記関係を満たすことができないために電源供給を遮断できないという問題がある。つまり、上記パワーゲーティングによる低消費電力化は、条件3に合わせて電源供給遮断期間を設けるため、条件1又は条件2のような場合においては電源供給遮断期間を設けることができず、さらなる消費電力の削減の余地を残している。

10

## 【0022】

そこで、本発明の一態様は、消費電力が削減された半導体装置を提供することを課題の一とする。

## 【課題を解決するための手段】

## 【0023】

上記課題に鑑みて、本発明の一態様は、パワーゲーティングが可能であり、複数の回路ブロックを有する半導体装置に温度センサを複数配置し、各温度センサによって各回路ブロックの温度を検出して、各回路ブロックにおいて当該温度に対応した最適なオフ期間を設定することである。具体的には、各回路ブロックに設けられている記憶回路の温度を検出して、各回路ブロックにおいて当該温度に対応した最適なオフ期間を設定する。なお、回路ブロックとは、半導体装置において、演算処理やデータの記憶など、ある機能を有した回路又は記憶媒体を含む集合体である。

20

## 【0024】

そこで、本発明の一態様は、演算回路と、演算回路によって得られたデータを保持する記憶回路と、演算回路に対する電源電圧の供給を制御する電源供給制御スイッチと、記憶回路の温度を検出し、当該温度に応じたオーバー・ヘッドを導出する温度検出回路と、当該オーバー・ヘッドよりも削減できる消費電力が大きい場合、前記電源電圧の供給を遮断する期間を設定し、電源供給制御スイッチを制御するコントローラと、を有する半導体装置である。

30

## 【0025】

なお、本明細書において、オーバー・ヘッドとは、記憶回路にデータを書き込む際、及び記憶回路からデータを読み出す際に過剰に消費される電力のこという。

## 【0026】

さらに、本発明の一態様は、演算回路と、キャッシュメモリと、演算回路によって得られたデータ、及び、キャッシュメモリに記憶されたデータを保持する記憶回路と、演算回路及びキャッシュメモリに対する電源電圧の供給を制御する電源供給制御スイッチと、記憶回路の温度を検出し、当該温度に応じたオーバー・ヘッドを導出する温度検出回路と、当該オーバー・ヘッドよりも削減できる消費電力が大きい場合、前記電源電圧の供給を遮断する期間を設定し、電源供給制御スイッチを制御するコントローラと、を有する半導体装置である。

40

## 【0027】

上記半導体装置において、記憶回路は主に不揮発性を有する半導体装置（不揮発性メモリとも記載する）で構成されており、例えば、トランジスタを用いたフラッシュメモリ、磁気トンネル接合素子（MTJ素子）を用いた磁気抵抗メモリ、抵抗変化型メモリ（ReRAM）又は相変化メモリ（PRAM）などがある。また、揮発性メモリを構成するトランジスタにオフ電流が極めて低いトランジスタを用いることで不揮発性メモリとして機能させることができ、当該記憶回路を構成する不揮発性メモリに適用することができる。才

50

フ電流が極めて低いトランジスタの例として、チャネル形成領域が酸化物半導体によって構成されるトランジスタ（以下、酸化物半導体を用いたトランジスタと記す）がある。なぜなら、酸化物半導体を用いたトランジスタは、酸化物半導体中の酸素欠損及び水素を低減することで、チャネル幅  $1 \mu m$ あたりのオフ電流が  $100 zA$ 以下のトランジスタとなるからである。

#### 【0028】

また、パワーゲーティングを行うためのパワーゲートには、電源電位が供給される配線と電気的に接続されるスイッチング素子を用いることができ、当該スイッチング素子としてトランジスタなどが挙げられる。トランジスタをパワーゲートとして用いる場合は、トランジスタを1つ設ける構成でもよく、複数のトランジスタを設ける構成であってもよい。さらに、複数のトランジスタを設ける構成では、複数のトランジスタを並列に接続して用いてもよいし、直列に接続して用いても良いし、直列接続と並列接続を組み合わせて用いてもよい。なお、パワーゲートを構成するトランジスタにチャネル形成領域が酸化物半導体で構成されるトランジスタを用いることができる。

10

#### 【発明の効果】

#### 【0029】

本発明の一態様は、回路ブロックを有する半導体装置に温度センサを配置し、各温度センサによって各回路ブロックの温度を検出して、各回路ブロックにおける最適な電源供給の遮断期間を設定できる。そのため、図15に示したフローチャートに従ったパワーゲーティングでは電源供給を遮断できなかった場合においても電源供給の遮断期間を設定でき、半導体装置の消費電力を削減することができる。

20

#### 【0030】

例えば、オーバーヘッドの量が小さく高速に動作しているときなど、電源供給を遮断できなかった期間においても適切な期間、電源供給を遮断することができるため、本発明の一態様である半導体装置は消費電力を削減しながら高速動作させることができる。

#### 【図面の簡単な説明】

#### 【0031】

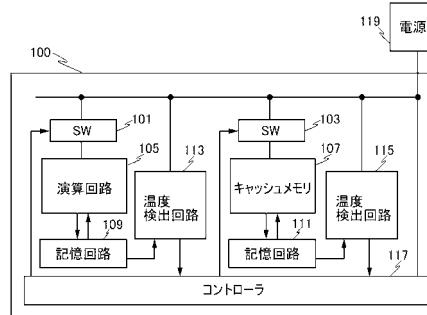

【図1】半導体装置の例を説明するための図。

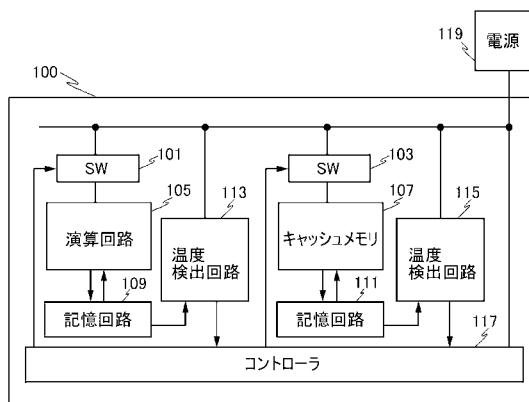

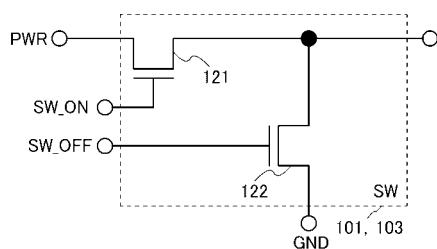

【図2】半導体装置の電源供給制御スイッチを説明するための図。

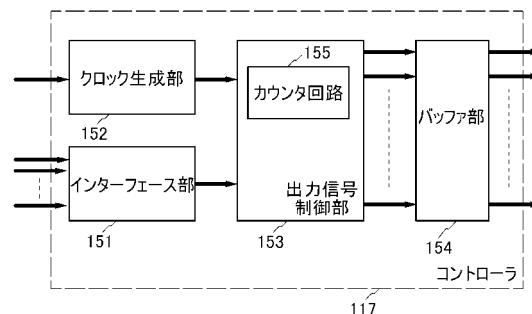

【図3】半導体装置のコントローラを説明するための図。

30

【図4】半導体装置の温度センサを説明するための図。

【図5】温度センサに含まれるダイオードの温度特性を説明するための図。

【図6】半導体装置の記憶回路に含まれる半導体記憶装置を説明するための図。

【図7】半導体装置の記憶回路に含まれる半導体記憶装置を説明するための図。

【図8】半導体装置の記憶回路に含まれる半導体記憶装置の動作を説明するための図。

【図9】半導体装置の動作を説明するための図。

【図10】オーバーヘッドと電源供給遮断期間の関係を説明するための図。

【図11】半導体装置に含まれるトランジスタの構造を説明するための図。

【図12】半導体装置に含まれるトランジスタの電気特性を説明するための図。

【図13】半導体装置の記憶回路に含まれる半導体記憶装置の一例を説明するための図。

40

【図14】電子機器を説明するための図。

【図15】パワーゲーティングの一例を説明するための図。

【図16】図15に示したパワーゲーティングによって電源供給を遮断できる期間を説明するための図。

#### 【発明を実施するための形態】

#### 【0032】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

50

**【0033】**

また、本明細書では、各実施の形態の内容を互いに適宜組み合わせることができる。また、各実施の形態の内容を互いに適宜置き換えることができる。

**【0034】**

また、第1、第2などの序数詞は、構成要素の混同を避けるために付しており、各構成要素の数は、序数の数に限定されない。

**【0035】****(実施の形態1)**

はじめに、本発明の一態様である半導体装置の構成例について図1を参照して説明する。なお、本実施の形態において、プロセッサを例に本発明の一態様である半導体装置を説明する。

10

**【0036】**

図1は、プロセッサ100のブロック図である。プロセッサ100は、演算回路105及びキャッシュメモリ107を有する。プロセッサ100は、演算回路105及びキャッシュメモリ107と電源119との間にパワーゲートとして機能する電源供給制御スイッチ101及び電源供給制御スイッチ103を有する。プロセッサ100は、電源供給制御スイッチ101及び電源供給制御スイッチ103を制御するコントローラ117を有する。プロセッサ100は、演算回路105によって得られたデータを保持する記憶回路109、及びキャッシュメモリ107に記憶されたデータを保持する記憶回路111を有する。プロセッサ100は、記憶回路109の温度を検出し、当該温度に応じたオーバーヘッドを導出する温度検出回路113、及び記憶回路111の温度を検出し、当該温度に応じたオーバーヘッドを導出する温度検出回路115を有する。なお、図1では、電源供給制御スイッチ101及び電源供給制御スイッチ103をSWと記載する。本実施の形態において図面に示した矢印は信号の伝送方向を示す。

20

**【0037】**

演算回路105は汎用されている論理回路であればよく、例えばAND回路、OR回路、NAND回路及びNOR回路など組み合わせ回路の一以上を用いて構成されている。なお、演算回路105には上記組み合わせ回路にフリップフロップなどの順序回路を組み合わせて用いて構成してもよい。また、図示していないが演算回路105には演算処理を制御する周辺回路が含まれているものとする。

30

**【0038】**

キャッシュメモリ107は汎用されているキャッシュメモリであればよく、例えばフリップフロップなどの順序回路が組み合わされて構成されている。具体的に、キャッシュメモリ107にはSRAMなどで構成されたキャッシュメモリを用いることができる。なお、図示していないがキャッシュメモリ107には書き込み及び読み出しなどの動作を制御する周辺回路が含まれているものとする。

**【0039】**

記憶回路109及び記憶回路111は、不揮発性を有する半導体記憶装置（不揮発性メモリ）と当該不揮発性メモリを動作させる動作回路を含む。不揮発性メモリとしては、フラッシュメモリ（NAND型及びNOR型を含む）、磁気トンネル接合素子（MTJ素子）を用いた磁気抵抗メモリ、抵抗変化型メモリ（ReRAM）又は相変化メモリ（PRAM）などがある。また、当該動作回路は、パワーゲーティングによって、電源電圧の供給が遮断される前に演算回路105によって得られたデータ、又はキャッシュメモリ107に記憶されたデータを記憶回路109又は記憶回路111に転送するための信号を出力する。

40

**【0040】**

また、揮発性メモリを構成するトランジスタにオフ電流が極めて低いトランジスタを用いることで不揮発性メモリとして機能させることができ、記憶回路109及び記憶回路111を構成する不揮発性メモリに適用することができる。例えば、オフ電流が極めて低いトランジスタとしては酸化物半導体を用いたトランジスタがある。酸化物半導体を用いた

50

トランジスタの詳細は後述する。なお、図1では演算回路105と記憶回路109を独立して設けているが、演算回路105に記憶回路109を一体形成する構成としてもよく、同様にキャッシュメモリ107と記憶回路111を一体形成する構成としてもよい。

#### 【0041】

温度検出回路113及び温度検出回路115は、ダイオードを有する温度センサ及び当該温度センサを制御する周辺回路を含む。プロセッサ100には、記憶回路109の温度を検出し、当該温度に応じたオーバーヘッドを導出する温度検出回路113、及び記憶回路111の温度を検出し、当該温度に応じたオーバーヘッドを導出する温度検出回路115をそれぞれ独立して設けているが、1つの温度検出回路に温度センサを2つ設けて、スイッチによって切り替えることで記憶回路109及び記憶回路111の温度を検出し、当該温度に応じたオーバーヘッドを導出する構成としてもよい。なお、本明細書において、温度検出回路113及び温度検出回路115で導出され、記憶回路109及び記憶回路111の温度に応じたオーバーヘッドを温度データということができる。

10

#### 【0042】

電源供給制御スイッチ101及び電源供給制御スイッチ103は、電源電位が供給される配線と電気的に接続されるスイッチング素子を用いることができ、例えば、当該スイッチング素子としてトランジスタなどがある。

#### 【0043】

ここで、電源供給制御スイッチ101及び電源供給制御スイッチ103の構成例について説明する。本実施の形態では、トランジスタを用いる場合について説明する。

20

#### 【0044】

電源供給制御スイッチ101は、演算回路105に対する電源電圧の供給を制御する機能を有する。電源供給制御スイッチ103は、キャッシュメモリ107に対する電源電位の供給を制御する機能を有する。

#### 【0045】

電源供給制御スイッチ101及び電源供給制御スイッチ103を構成するトランジスタとして、オフ電流が極めて低いトランジスタを用いてもよく、オフ電流が極めて低いトランジスタとしては酸化物半導体を用いたトランジスタがある（詳細は後述）。

30

#### 【0046】

電源供給制御スイッチ101及び電源供給制御スイッチ103の構成は、トランジスタを1つ設ける構成でもよく、複数のトランジスタを設ける構成であってもよい。ここでは、複数のトランジスタを設ける構成を説明する。

#### 【0047】

図2は、電源供給制御スイッチ101及び電源供給制御スイッチ103に適用できる回路構成の一例を示した回路図である。電源供給制御スイッチ101及び電源供給制御スイッチ103は、nチャネル型トランジスタであるトランジスタ121及びトランジスタ122を有する。

40

#### 【0048】

トランジスタ121は、電源119と、演算回路105又はキャッシュメモリ107との間に設けられる。トランジスタ121のゲートには、コントローラ117から制御信号SW\_ONが入力される。トランジスタ121がオン状態又はオフ状態になることにより、演算回路105又はキャッシュメモリ107に電源電圧を供給するか否かが制御される。

#### 【0049】

トランジスタ122のゲートには、コントローラ117から制御信号SW\_OFFが入力される。トランジスタ122がオン状態又はオフ状態になることにより、演算回路105又はキャッシュメモリ107に接地電位を供給するか否かが制御される。

50

#### 【0050】

トランジスタ121がオン状態であり、トランジスタ122がオフ状態であるとき、図2に示す電源供給制御スイッチがオン状態となる。トランジスタ121がオフ状態であ

り、トランジスタ 122 がオン状態であるときに、図 2 に示す電源供給制御スイッチがオフ状態となる。

#### 【0051】

また、電源供給制御スイッチ 101 及び電源供給制御スイッチ 103 を 1 つのトランジスタで構成する場合は、図 2 に示す電源供給制御スイッチにおいてトランジスタ 121 又はトランジスタ 122 の一方のみ設ける構成とすればよい。例えば、トランジスタ 121 のみで構成する場合、トランジスタ 121 のゲートに制御信号 SW\_ON が入力されている間は電源電圧が供給され、トランジスタ 121 のゲートに制御信号 SW\_ON が入力されていない間は、電源電圧の供給が遮断される。

#### 【0052】

コントローラ 117 は、温度検出回路 113 及び温度検出回路 115 によって導出された記憶回路 109 及び記憶回路 111 の温度データが伝送され、当該温度データに対応した、電源供給制御スイッチ 101 及び電源供給制御スイッチ 103 のスイッチングを制御する信号（制御信号 SW\_ON 又は制御信号 SW\_OFF）を出力できる構成とすればよい。これは、記憶回路 109 及び記憶回路 111 に含まれる不揮発性メモリの書き込み及び読み出しのオーバーヘッドが温度によって異なるからである。

#### 【0053】

コントローラ 117 の構成例を図 3 に示す。コントローラ 117 は、インターフェース部 151 と、クロック生成部 152 と、出力信号制御部 153 と、バッファ部 154 と、を含む。

#### 【0054】

温度検出回路 113 及び温度検出回路 115 から導出される温度データ、並びにその他入力される命令信号又は入力信号は、インターフェース部 151 を介して出力信号制御部 153 に入力される。

#### 【0055】

クロック生成部 152 では、入力された信号を用いてコントローラ 117 で使用するクロック信号を生成して出力信号制御部 153 を含む各回路に出力する。このとき、入力されたクロック信号を分周してコントローラ 117 で用いることにより、コントローラ 117 の消費電力を小さくすることができる。

#### 【0056】

出力信号制御部 153 は、カウンタ回路 155 を有する。出力信号制御部 153 は、カウンタ回路 155 でクロック信号をカウントし、コントローラ 117 に入力される信号（例えば、温度検出回路 113 及び温度検出回路 115 から導出される温度データ）に従って、出力する複数の信号のハイ状態又はロー状態を設定する機能を有する。上記複数の信号としては、電源供給制御スイッチ 101 又は電源供給制御スイッチ 103 を個別に制御するための制御信号（例えば、制御信号 SW\_ON 又は制御信号 SW\_OFF）がある。

#### 【0057】

出力信号制御部 153 で生成された制御信号は、バッファ部 154 を介して電源供給制御スイッチ 101 又は電源供給制御スイッチ 103 に出力される。

#### 【0058】

なお、図 1 に示したプロセッサ 100 は、演算回路 105 及びキャッシュメモリ 107 をそれぞれ 1 つずつ有する構成であるが、これに限定されず、演算回路 105 及びキャッシュメモリ 107 をそれぞれ 2 つ以上有する構成であってもよい。さらには、その他の機能を有する回路ブロックを新たに設けてよい。その場合、設けた演算回路 105、キャッシュメモリ 107 及び回路ブロックの数に応じて、電源供給制御スイッチ、記憶回路、温度検出回路を設ける。

#### 【0059】

ここで、温度検出回路 113 及び温度検出回路 115 に含まれる温度センサ及び周辺回路について説明する。図 4 (A) 及び図 4 (B) は当該温度センサ及び当該周辺回路の一構成例を示したブロック図である。

10

20

30

40

50

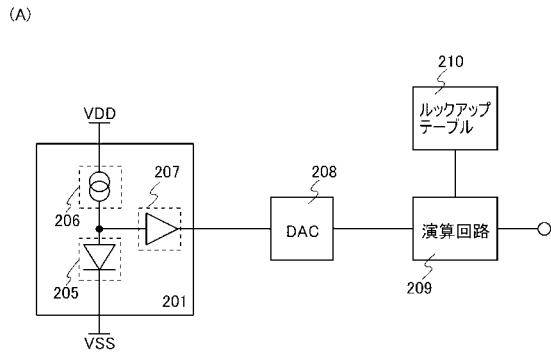

## 【0060】

図4(A)より、温度センサ201は温度検出用ダイオード205、定電流源206、及びバッファアンプ207によって構成されている。そして、周辺回路として、温度センサ201からの出力(記憶回路109又は記憶回路111の温度データ)をアナログ信号からデジタル信号に変換するDAC(Digital to Analog Converter)208と、記憶回路109及び記憶回路111の温度を検出するための参照データ、及び当該検出した温度に対応するオーバーヘッドのデータが保存されたルックアップテーブル210と、当該データと変換されたデジタル信号を比較、演算する演算回路209と、を有する。なお、図4(A)に図示していないが、周辺回路として、DAC208、演算回路209及びルックアップテーブル210を制御する制御回路を含んでいてよい。温度センサ201は、温度検出用ダイオード205、定電流源206、及びバッファアンプ207の他にDAC208を含めたデジタル出力の温度センサとしてもよい。

10

## 【0061】

図4(A)に示した、温度センサ201、DAC208、演算回路209及びルックアップテーブル210を1つのユニットとすると、プロセッサ100は、温度検出回路113又は温度検出回路115それぞれに当該ユニットが設けられている構成とすることができる。

20

## 【0062】

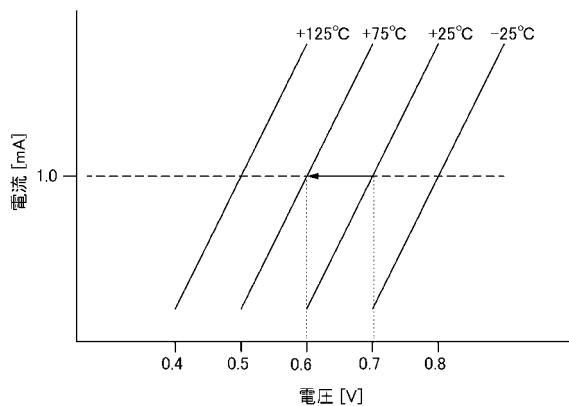

また、温度検出回路113及び温度検出回路115に含まれる温度センサ及び周辺回路は、図4(B)に示したように、記憶回路109の温度検出用である温度センサ201、温度センサ201と同様の構成を有し、記憶回路111の温度検出用である温度センサ202、スイッチ211と、DAC208、演算回路209及びルックアップテーブル210を有する回路構成としてもよい。このような回路構成とすることで、図4(A)の場合とは異なり、スイッチ211の切り替えによって温度センサ201又は温度センサ202を動作させることができる。つまり、スイッチ211の切り替えによって、記憶回路109又は記憶回路111の温度を検出することができる。なお、図4(B)に図示していないが、周辺回路として、スイッチ211、DAC208、演算回路209及びルックアップテーブル210を制御する制御回路を含んでいてよい。また、温度検出回路に設ける温度センサの数は、設ける演算回路の数やキャッシュメモリの数と同数にすることが好ましく、設けた温度センサのそれぞれをスイッチで切り替えることができる構成とすることが好ましい。

30

## 【0063】

そして、温度センサ201を構成する温度検出用ダイオード205は、温度によって順方向電圧が変化する半導体ダイオードを用いることができる。例えば、温度検出用ダイオード205には、ダイオードの順方向電圧が温度によって $-2\text{mV}/^\circ\text{C}$ という温度特性を有するダイオードを用いる。図5に当該ダイオードの温度特性を示す。なお、図5において、横軸はダイオードの順方向電圧[V]を示し、縦軸は対数表示した順方向電流[mA]を示す。

30

## 【0064】

図4(A)に示したユニットを用いる場合、温度検出回路113は、定電流源206の設定電流に対応する温度検出用ダイオード205の電圧を定期的にサンプリングして(例えば1秒に1回など)、バッファアンプ207で増幅した後、DAC208でデジタル信号に変換し、演算回路209によって、ルックアップテーブル210に保存されたデータと比較、演算することで記憶回路109の温度を検出し、当該温度に応じた記憶回路109のオーバーヘッドを導出する。

40

## 【0065】

例えば、温度検出回路113において、温度検出用ダイオード205に流れる設定電流を $1.0\text{mA}$ とし、 $25^\circ\text{C}$ での温度センサ201から出力される電圧が $0.7\text{V}$ である場合、一定期間後、温度センサ201から出力される電圧が $0.6\text{V}$ であった場合、温度検出用ダイオード205は $-2\text{mV}/^\circ\text{C}$ という温度特性を有することから、一定期間後の温

50

度検出用ダイオード 205 は 25 から 50 上昇し、75 であることがわかる（図 5 参照）。これを利用し、記憶回路 109 の温度を検出することができる。

#### 【0066】

また、図 4 (B) に示した回路構成を用いる場合、例えば、記憶回路 109 又は記憶回路 111 のサンプリング間隔に合わせてスイッチ 211 を切り替えることで、記憶回路 109 又は記憶回路 111 の温度を選択的に検出することができる。また、図 4 (B) に示した回路構成のようにすることで、プロセッサのサイズを小さくすることができる。なお、温度検出回路 113 及び温度検出回路 115 はプロセッサチップ内に内蔵することができる。

#### 【0067】

このように、温度センサ 201 や DAC 208 から得られるデータ（記憶回路 109 及び / 又は記憶回路 111 の温度）と、ルックアップテーブル 210 に保存されたデータとを照らし合わせることで、記憶回路 109 及び / 又は記憶回路 111 のオーバーヘッドを導出することができる。

#### 【0068】

次に、記憶回路 109 及び記憶回路 111 に含まれる不揮発性を有する半導体記憶装置について図面を参照して説明する。特に、ここでは、揮発性メモリを構成するトランジスタにオフ電流が極めて低いトランジスタを用いた半導体記憶装置を用いる場合について説明する。

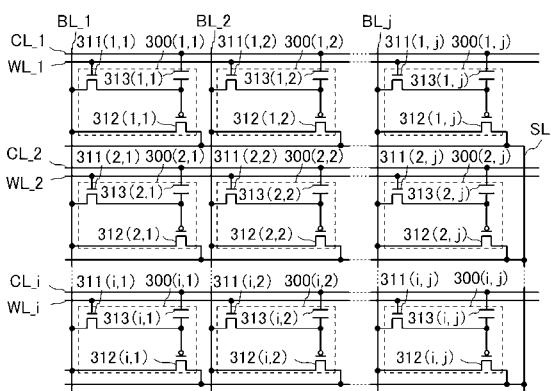

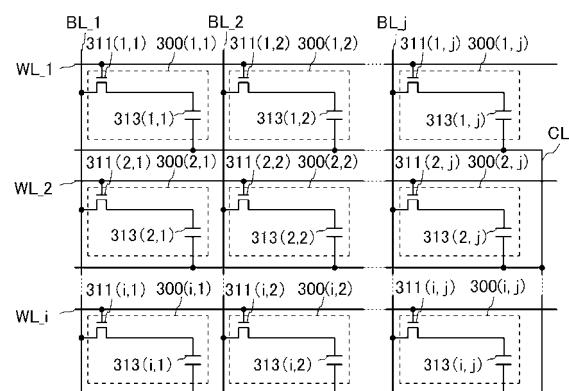

#### 【0069】

記憶回路 109 及び記憶回路 111 は、揮発性メモリとして、 $i$  行 ( $i$  は 2 以上の自然数)  $j$  列 ( $j$  は自然数) にマトリクス状に配列された複数のメモリセルを備えたメモリセルアレイを含む（図 6 及び図 7 参照）。なお、記憶回路 109 及び記憶回路 111 は、図 6 及び図 7 に示したメモリセルアレイの一方又は双方を含む。

#### 【0070】

図 6 に示すメモリセルアレイの例について説明する。

#### 【0071】

図 6 に示すメモリセルアレイは、 $i$  行  $j$  列のマトリクス状に配列された複数のメモリセル 300 と、第 1 乃至第  $j$  のビット線 BL と、第 1 乃至第  $i$  のワード線 WL と、第 1 乃至第  $i$  の容量線 CL と、所定の値の電位が与えられるソース線 SL と、を有する。

#### 【0072】

図 6 に示すメモリセルアレイにおいて、 $M$  ( $M$  は 1 以上  $i$  以下の自然数) 行  $N$  ( $N$  は 1 以上  $j$  以下の自然数) 列目のメモリセル 300 (メモリセル 300 ( $M, N$ )) は、トランジスタ 311 ( $M, N$ ) と、トランジスタ 312 ( $M, N$ ) と、容量素子 313 ( $M, N$ ) と、を備える。

#### 【0073】

また、トランジスタ 311 ( $M, N$ ) のソース及びドレインの一方は、ビット線  $BL_N$  に電気的に接続されている。また、トランジスタ 311 ( $M, N$ ) のゲートは、ワード線  $WL_M$  に電気的に接続されている。

#### 【0074】

そして、トランジスタ 311 ( $M, N$ ) は、 $n$  チャネル型トランジスタであり、データの書き込み及び保持を制御するトランジスタである。

#### 【0075】

また、トランジスタ 311 ( $M, N$ ) としては、上記したようにオフ電流の低いトランジスタを用いることができる。例えば、酸化物半導体を用いたトランジスタを用いることができる。このようにすることで、データの保持期間を長くすることができます、電源電圧の供給を停止した場合であってもデータを保持することができる。つまり、図 6 に示すメモリセルアレイを含む揮発性メモリを不揮発性メモリとして機能させることができます。従って、記憶回路 109 及び記憶回路 111 に図 6 に示すメモリセルアレイを含む揮発性メモリを用いることができる。

10

20

30

40

50

## 【0076】

トランジスタ312(M,N)は、pチャネル型トランジスタである。トランジスタ312(M,N)のソース及びドレインの一方はビット線BL\_Nに電気的に接続され、ソース及びドレインの他方はソース線SLに電気的に接続されている。また、トランジスタ312(M,N)のゲートは、トランジスタ311(M,N)のソース及びドレインの他方に電気的に接続されている。

## 【0077】

トランジスタ312(M,N)は、出力するデータの電位を設定する出力トランジスタとしての機能を有する。

## 【0078】

容量素子313(M,N)の一対の電極の一方は、トランジスタ311(M,N)のソース及びドレインの他方に電気的に接続され、他方は、容量線CL\_Mに電気的に接続されている。

10

## 【0079】

容量素子313(M,N)は、データを保持する保持容量としての機能を有する。

## 【0080】

以上が図6に示すメモリセルアレイの構成例の説明である。

## 【0081】

なお、メモリセルにトランジスタ312は設けられていなくてもよい。例えばメモリセルを図7に示す構成にしてもよい。このとき、容量線CLを1つにまとめてソース線SLの代わりとすることができます。

20

## 【0082】

図7に示すメモリセルアレイにおいても、トランジスタ311(M,N)としては、上記したようにオフ電流の低いトランジスタを用いることができる。例えば、酸化物半導体を用いたトランジスタを用いることができる。このようにすることで、データの保持期間を長くすることができ、電源電圧の供給を停止した場合であってもデータを保持することができる。つまり、図7に示すメモリセルアレイを含む半導体記憶装置を不揮発性メモリとして機能させることができる。従って、記憶回路109及び記憶回路111に図7に示すメモリセルアレイを含む半導体記憶装置を用いることができる。

30

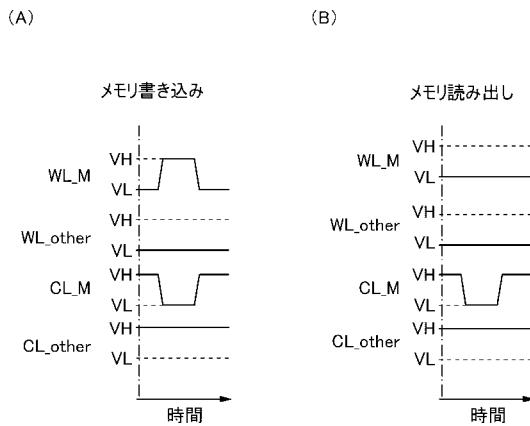

## 【0083】

次に、図6に示すメモリセルアレイを具備する半導体記憶装置の駆動方法の一例について、図8(A)及び図8(B)を参照して説明する。図8(A)及び図8(B)は、図6に示す半導体記憶装置の駆動方法の一例を説明する、タイミングチャートである。ここでは、一例としてM行目のメモリセル300に順次データを書き込み、その後書き込まれたデータを読み出す場合について説明するが、これに限定されない。

## 【0084】

まず、M行目のメモリセル300にデータを書き込む場合(メモリ書き込みともいう)、図8(A)に示すように、第Mのワード線WL\_Mの電位をVHにし、それ以外のすべてのワード線WL\_otherの電位をVLにする。

40

## 【0085】

なお、VHは、例えば基準電位(例えば接地電位)より大きい値の電位(例えば高電源電位)であり、VLは基準電位以下の電位(例えば低電源電位)である。

## 【0086】

このとき、M行目のメモリセル300のそれぞれにおいて、トランジスタ311がオン状態になり、容量素子313の一対の電極の一方の電位が各ビット線BLの電位と同等の値になる。

## 【0087】

その後、トランジスタ311がオフ状態となり、トランジスタ312のゲートは浮遊状態になり、トランジスタ312のゲートの電位は保持される。

## 【0088】

50

上記動作を行毎に行うことにより、全てのメモリセル 300 にデータを書き込むことができる。

【0089】

また、M 行目のメモリセル 300 からデータを読み出す場合（メモリ読み出しともいう）、図 8（B）に示すように、すべてのワード線 WL の電位を VL にし、第 M の容量線 CL\_M を VL にし、それ以外のすべての容量線 CL\_other の電位を VH にする。

【0090】

なお、M 行目のメモリセル 300 において、トランジスタ 312 のソースとドレインの間の抵抗値は、トランジスタ 312 のゲートの電圧に応じて決まる。また、トランジスタ 312 のソースとドレインの間に流れる電流に応じた値の電位をデータとしてメモリセル 300 から読み出すことができる。

10

【0091】

さらに、上記動作を行毎に繰り返し行うことにより、全てのメモリセル 300 においてデータを読み出すことができる。以上が図 6 に示す半導体記憶装置の駆動方法例の説明である。

【0092】

図 6 乃至図 8 を参照して説明したように、記憶回路 109 及び記憶回路 111 に含まれる半導体記憶装置では、データの書き込み及び保持を制御するトランジスタ（トランジスタ 311（M, N））としてオフ電流が極めて低いトランジスタを用いることでデータの保持期間を長くすることができ、電源電圧の供給を停止した場合であってもデータを保持することができる。従って、記憶回路 109 及び記憶回路 111 において、データの書き込み及び保持を制御するトランジスタにオフ電流が極めて低いトランジスタを用いることで、パワーゲーティングが可能となり、消費電力が低減されたプロセッサを作製することができる。

20

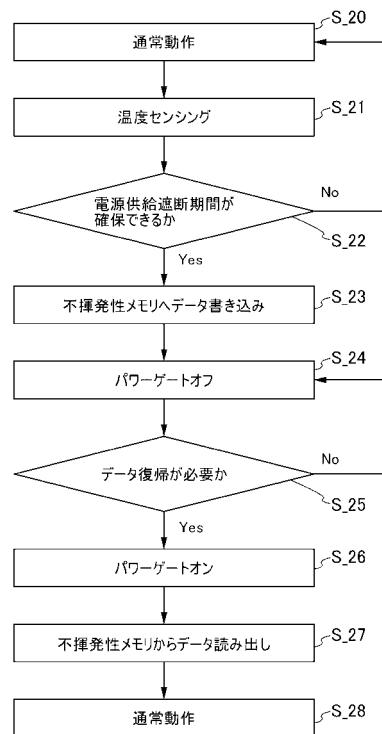

【0093】

次に、プロセッサ 100 の動作について図面を参照して説明する。図 9 は、プロセッサ 100 の動作を説明するフローチャートである。図 10（A）、（B）、（C）は、プロセッサ 100 におけるオーバーヘッドと電源供給遮断期間の関係を示した図である。なお、図 10（A）、（B）、（C）において、横軸は時間を表し、縦軸は消費電力を表す。記憶回路 109 及び記憶回路 111 の温度は低い方から順に条件 1、2、3 とし、記憶回路 109 及び記憶回路 111 の動作速度は、遅い方から順に条件 3、2、1 とする。

30

【0094】

プロセッサ 100（特に演算回路 105 及びキャッシュメモリ 107）は、ある一定の動作速度で動作しているものとする。なお、便宜上、この動作を通常動作という（ステップ S\_20）。なお、通常動作しているプロセッサ 100 において、演算回路 105 及びキャッシュメモリ 107 には電源電圧が供給されている。

【0095】

通常動作しているプロセッサ 100 において、温度検出回路 113 は記憶回路 109 の温度を検出し、温度検出回路 115 は記憶回路 111 の温度を検出する（ステップ S\_21）。当該温度を検出することで、記憶回路 109 及び記憶回路 111 にデータを転送する際のオーバーヘッドを導出する（見積もる）ことができる。具体的には、演算回路 105 によって得られたデータ及びキャッシュメモリ 107 に記憶されているデータを記憶回路 109 及び記憶回路 111 に含まれる不揮発性メモリに書き込む際のオーバーヘッドを導出することができる。

40

【0096】

次に、プロセッサ 100 のうち、演算回路 105 及びキャッシュメモリ 107 に電源供給は行われているが処理（演算処理及びキャッシュメモリの書き込み又は読み出し）は行われていない場合、演算回路 105 及びキャッシュメモリ 107 に対する電源供給を遮断する期間（電源供給遮断期間）を確保できるか否かを判別する（ステップ S\_22）。この判別は、演算回路 105 及びキャッシュメモリ 107 の動作速度と、検出した温度から

50

導出されるオーバーヘッドなど温度データとの兼ね合いによって行われる。例えば、条件1乃至条件3のように、記憶回路111がどのような温度であっても、オーバーヘッドを導出することができ、動作のなかで  $a + b < c$  の関係を満たすことができる時間ががあれば、電源供給遮断期間として確保する(図10(A)、(B)、(C)参照)。演算回路105及びキャッシュメモリ107に対する電源供給遮断期間を確保できる場合は、電源供給遮断期間が始まる前に演算回路105によって得られたデータ及びキャッシュメモリ107に記憶されているデータを記憶回路109及び記憶回路111に転送する。具体的には、当該データを記憶回路109及び記憶回路111に含まれる不揮発性メモリに書き込む(ステップS\_23)。なお、演算回路105及びキャッシュメモリ107に対する電源供給遮断期間を確保できない場合は通常動作のままでする(ステップS\_20)。

10

#### 【0097】

不揮発性メモリにデータを書き込んだ後、演算回路105と電源の間、及びキャッシュメモリ107と電源の間に設けられた電源供給制御スイッチを切ることで演算回路105及びキャッシュメモリ107に対する電源供給を遮断する(ステップS\_24)。

#### 【0098】

パワーゲートをオフした後、書き込まれたデータの復帰を必要とするか否かを判別する(ステップS\_25)。この判別は、演算回路105及びキャッシュメモリ107を再び動作させるときまで行われる。演算回路105及びキャッシュメモリ107を再び動作させる期間ではなく、データの復帰が必要ない場合においてパワーゲートはオフしたままである。従って、演算回路105及びキャッシュメモリ107を再び動作させるときまで演算回路105及びキャッシュメモリ107に対する電源供給は遮断されることになる。

20

#### 【0099】

その後、演算回路105及びキャッシュメモリ107を再び動作させる期間などデータの復帰を必要とする場合、動作させる期間の前にパワーゲートをオンして演算回路105及びキャッシュメモリ107に対する電源供給を再開する(ステップS\_26)。

#### 【0100】

その後、不揮発性メモリから転送されていたデータを読み出し、当該データを演算回路及びキャッシュメモリに戻し(ステップS\_27)、通常動作に戻る(ステップS\_28)。

30

#### 【0101】

図10(A)、(B)、(C)において、a及びbの領域は、記憶回路109及び記憶回路111に含まれる不揮発性メモリの書き込み又は読み出しをする際のオーバーヘッドを表す。cの領域がパワーゲーティングによって削減される電力を表す。また、当該オーバーヘッドの量は、記憶回路109及び記憶回路111の温度が高くなるにつれて増大する。つまり、オーバーヘッドの量は、小さい方から順に条件1、2、3と増大する。

#### 【0102】

図15に示したフローチャートに従ったパワーゲーティングでは、記憶回路109及び記憶回路111の温度が最も高い条件3のオーバーヘッドの量を基準に電源供給を遮断する期間を設定し、毎回その期間の長さしか電源供給を遮断することができない。そのため、条件1又は条件2の場合は電源供給を遮断することができない(図16参照)。

40

#### 【0103】

一方、プロセッサ100は、温度検出回路113及び温度検出回路115によって記憶回路109及び記憶回路111の温度データを導出することができ、演算回路105によって得られたデータ、及びキャッシュメモリ107に記憶されたデータを記憶回路109、及び記憶回路111に保持させる際のオーバーヘッド(詳細には不揮発性メモリの書き込み又は読み出しのオーバーヘッド)を見積もることができる。従って、図15に示したフローチャートに従ったパワーゲーティングでは電源供給を遮断できなかった条件1又は条件2の場合においても、電源供給を遮断する期間(電源供給遮断期間)を設定し、演算回路105及びキャッシュメモリ107に対して供給される電源電圧を遮断することができる(図10(A)、(B)参照)。

50

## 【0104】

つまり、記憶回路109及び記憶回路111の温度データを導出することで、プロセッサ100の動作速度に関わらず、演算回路105及びキャッシュメモリ107に対する電源供給遮断期間を設定できる。例えば、図9に示したフローチャートに従ったパワーゲーティングでは、電源供給遮断期間を設けることが難しい高速動作させた場合においても電源供給遮断期間を設定することができ、消費電力を低減することができる。このようにプロセッサ100は、優れた低消費電力化を実現できる。

## 【0105】

以上、本発明の一態様により、記憶回路の温度を検出することで、動作速度に関わらず、記憶回路におけるオーバーヘッドの温度依存性に対して回路ブロックに対する電源供給を遮断する期間を最適に設定することができる。それゆえ、本発明の一態様の半導体装置は、動作速度に関わらず、回路ブロックに対する電源供給を遮断する期間を設定することができるため、優れた低消費電力化された半導体装置である。

10

## 【0106】

なお、本実施の形態に記載の構成、方法などは、他の実施の形態に記載の構成、方法などと適宜、組み合わせて用いることができる。

## 【0107】

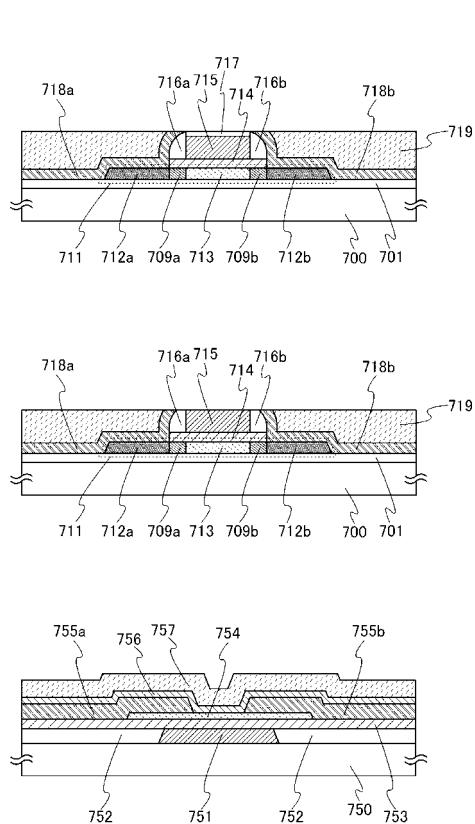

## (実施の形態2)

本実施の形態では、本発明の一態様である半導体装置に適用可能なトランジスタの構造の一例について、図11の断面模式図を参照して説明する。なお、図11に示す各構成要素は、実際の寸法と異なる場合がある。

20

## 【0108】

図11(A)に示すトランジスタは、半導体層711と、絶縁層714と、導電層715と、絶縁層716a及び絶縁層716bと、絶縁層717と、導電層718a及び導電層718bと、絶縁層719と、を含む。

## 【0109】

半導体層711は、絶縁層701を介して被素子形成層700上に設けられる。なお、必ずしも絶縁層701の上に半導体層711を設けなくてもよく、被素子形成層700上に半導体層711を直接設けてよい。

30

## 【0110】

半導体層711は、互いに離間して、ドーパントが添加された領域709a、709b及びドーパントが添加された領域712a、712bを有し、領域709a、709bの間にチャネル形成領域713を有する。なお、ドーパントが添加された領域709a、709bよりもドーパントが添加された領域712a、712bのほうがドーパント濃度は高く、抵抗率は低い。領域712a及び領域712bはソース領域又はドレイン領域として機能する。半導体層711のように抵抗率を段階的にすることで、ドレイン領域近傍の電界集中を緩和することができるため、当該電界集中によって、しきい値電圧の変動やトランジスタの破壊などを抑制することができる。

## 【0111】

絶縁層714は、半導体層711の一部の上に設けられる。

40

## 【0112】

導電層715は、絶縁層714を介して半導体層711に重畠して設けられる。

## 【0113】

絶縁層716aは、導電層715の一対の側面の一方に接して設けられ、絶縁層716bは、該一対の側面の他方に接して設けられる。

## 【0114】

絶縁層717は、導電層715の上に設けられる。なお、図11(B)に示すように、絶縁層717を設けなくてもよい。

## 【0115】

導電層718aは、領域712aに接して設けられ、導電層718bは、領域712b

50

に接して設けられる。また、導電層 718a は、絶縁層 716a の側面に接し、導電層 718b は、絶縁層 716b の側面に接する。

【0116】

絶縁層 719 は、導電層 718a 及び 718b の上に設けられる。

【0117】

導電層 718a 及び導電層 718b、並びに絶縁層 719 は、例えば導電膜及び絶縁層の積層に対して平坦化処理（例えば CMP 処理、又はエッチバック処理など）を行うことにより形成される。なお、図 11(A) に示すトランジスタのように、絶縁層 717 を設けることによって、当該平坦化処理によって導電層 715 と、導電層 718a 及び導電層 718b とが接して短絡することを防ぐことができる。

10

【0118】

また、図 11(C) に示すトランジスタは、導電層 751 と、絶縁層 752 と、絶縁層 753 と、半導体層 754 と、導電層 755a 及び導電層 755b と、絶縁層 756 と、絶縁層 757 と、を有する。

【0119】

導電層 751 は、被素子形成層 750 の上に設けられる。

【0120】

絶縁層 752 は、被素子形成層 750 の上に設けられる。絶縁層 752 及び導電層 751 の表面は平坦であることが好ましい。

20

【0121】

導電層 751 及び絶縁層 752 は、例えば導電膜及び絶縁層の積層に対して平坦化処理（例えば CMP 処理、又はエッチバック処理など）を行うことにより形成される。

【0122】

絶縁層 753 は、導電層 751 及び絶縁層 752 の上に設けられる。

【0123】

半導体層 754 は、絶縁層 753 を介して導電層 751 に重畠して設けられる。

【0124】

導電層 755a 及び導電層 755b は、互いに離間し、半導体層 754 に電気的に接続される。このとき、導電層 755a と導電層 755b の間隔は、トランジスタのチャネル長に相当し、例えば 50nm 未満であることが好ましい。例えば、電子ビームで露光して形成したレジストマスクを用いて、導電膜の一部をエッチングすることにより、導電層 755a と 755b の間隔を 50nm 未満にできる。また、電子ビームを用いずに、導電層 755a と 755b の間隔を 50nm 未満にする場合は、紫外光など他の光源を用いてレジストマスクを形成し、当該レジストマスクをスリミングした後に導電膜の一部をエッチングすることで実施できる。

30

【0125】

図示していないが、導電層 755a 及び導電層 755b と絶縁層 756 の間に、導電層 755a と導電層 755b の間隔よりも長い間隔を有する一対の導電層を設けてもよい。当該一対の導電層は、導電層 755a 及び導電層 755b の電気抵抗よりも低いことが好ましく、このようにすることで、図 11(C) に示すトランジスタのオン電流を増大させることができる。

40

【0126】

絶縁層 757 は、半導体層 754 の上を覆うように設けられる。

【0127】

さらに、各構成要素について以下に説明する。各構成要素は、必ずしも単層に限定されず、積層であってもよい。

【0128】

絶縁層 701 は下地層である。絶縁層 701 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を

50

適用できる。

【0129】

絶縁層752は、絶縁層701と同様の材料を含む層を適用できる。

【0130】

半導体層711及び半導体層754は、トランジスタのチャネルが形成される層（チャネル形成層ともいう）としての機能を有する。

【0131】

半導体層711及び半導体層754としては、例えば酸化物半導体を用いた半導体層（酸化物半導体層ともいう）を適用できる。

【0132】

酸化物半導体層は、例えば非単結晶を有してもよい。非単結晶は、例えば、CAAC (C Axis Aligned Crystal)、多結晶、微結晶、非晶質部を有する。非晶質部は、微結晶、CAACよりも欠陥準位密度が高い。また、微結晶は、CAACよりも欠陥準位密度が高い。なお、CAACを有する酸化物半導体を、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) と呼ぶ。

【0133】

酸化物半導体層は、例えばCAAC-OSを有してもよい。CAAC-OSは、例えば、c軸配向し、a軸または/およびb軸はマクロに揃っていない。

【0134】

を、微結晶酸化物半導体と呼ぶ。微結晶酸化物半導体層は、例えば、1nm以上10nm未満のサイズの微結晶（ナノ結晶ともいう。）を膜中に含む。

【0135】

酸化物半導体層は、例えば非晶質部を有してもよい。なお、非晶質部を有する酸化物半導体を、非晶質酸化物半導体と呼ぶ。非晶質酸化物半導体層は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質酸化物半導体層は、例えば、完全な非晶質であり、結晶部を有さない。

【0136】

なお、酸化物半導体層が、CAAC-OS、微結晶酸化物半導体、非晶質酸化物半導体の混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-OSの領域と、を有する。また、混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-OSの領域と、の積層構造を有してもよい。

【0137】

なお、酸化物半導体層は、例えば、単結晶を有してもよい。

【0138】

酸化物半導体層は、複数の結晶部を有し、当該結晶部のc軸が被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃っていることが好ましい。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。そのような酸化物半導体層の一例としては、CAAC-OS膜がある。

【0139】

CAAC-OS層に含まれる結晶部は、一辺が100nm未満の立方体内に收まる大きさであることが多い。また、透過型電子顕微鏡（TEM：Transmission Electron Microscope）による観察像では、CAAC-OS膜に含まれる結晶部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には明確な粒界（グレインバウンダリーともいう。）は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0140】

CAAC-OS層に含まれる結晶部は、例えば、c軸がCAAC-OS層の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃い、かつab面に垂

10

20

30

40

50

直な方向から見て金属原子が三角形状または六角形状に配列し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、80°以上100°以下、好ましくは85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-10°以上10°以下、好ましくは-5°以上5°以下の範囲も含まれることとする。

#### 【0141】

なお、CAC-O<sub>5</sub>層において、結晶部の分布が一様でなくてもよい。例えば、CAC-O<sub>5</sub>膜の形成過程において、酸化物半導体層の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAC-O<sub>5</sub>膜へ不純物を添加することにより、当該不純物添加領域において結晶部が低下することもある。

10

#### 【0142】

CAC-O<sub>5</sub>層に含まれる結晶部のc軸は、CAC-O<sub>5</sub>膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃うため、CAC-O<sub>5</sub>膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。また、結晶部は、成膜したとき、または成膜後に加熱処理などの結晶化処理を行ったときに形成される。従って、結晶部のc軸は、CAC-O<sub>5</sub>膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃う。

20

#### 【0143】

CAC-O<sub>5</sub>膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

#### 【0144】

酸化物半導体層に適用可能な酸化物半導体としては、例えばインジウム及びガリウムの一方若しくは両方と、亜鉛と、を含む金属酸化物、又は該金属酸化物に含まれるガリウムの一部若しくは全部の代わりに他の金属元素を含む金属酸化物などが挙げられる。

30

#### 【0145】

上記金属酸化物としては、例えばIn系金属酸化物、Zn系金属酸化物、In-Zn系金属酸化物、又はIn-Ga-Zn系金属酸化物などを適用できる。また、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の一部若しくは全部の代わりに他の金属元素を含む金属酸化物を用いてもよい。

30

#### 【0146】

上記他の金属元素としては、例えばガリウムよりも多くの酸素原子と結合が可能な金属元素を用いればよく、例えばチタン、ジルコニウム、ハフニウム、ゲルマニウム、及び錫のいずれか一つ又は複数の元素を用いればよい。さらに、上記他の金属元素としては、ランタン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、及びルテチウムのいずれか一つ又は複数の元素を用いればよい。これらの金属元素は、スタビライザーとしての機能を有する。なお、これらの金属元素の添加量は、金属酸化物が半導体として機能することが可能な量である。ガリウムよりも多くの酸素原子と結合が可能な金属元素を用い、さらには金属酸化物中に酸素を供給することにより、金属酸化物中の酸素欠陥を少なくできる。

40

#### 【0147】

例えば、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の全部の代わりに錫を用いるとIn-Sn-Zn系金属酸化物となり、上記In-Ga-Zn系金属酸化物に含まれるGa（ガリウム）の一部の代わりにチタンを用いるとIn-Ti-Ga-Zn系金属酸化物となる。

#### 【0148】

また、半導体層711及び754として酸化物半導体層を用いる場合、例えば脱水化・脱水素化を行い、酸化物半導体層中の水素、水、水酸基、又は水素化物（水素化合物とも

50

いう)などの不純物を排除し、且つ酸化物半導体層に酸素を供給すると、酸化物半導体層を高純度化させることができる。例えば、酸化物半導体層に接する層として酸素を含む層を用い、また、加熱処理を行うことにより、酸化物半導体層を高純度化させることができる。

#### 【0149】

具体的には、図11(A)、(B)に示すトランジスタの作製において、少なくとも半導体層711を形成する工程以降で適宜加熱処理を行うことが好ましい。当該加熱処理は、例えば、300以上700以下、又は基板の歪み点未満とする。また、加熱処理は減圧下、窒素雰囲気下、酸素雰囲気下、又は希ガス雰囲気下などで行うことができる。なお、加熱処理を複数回行ってもよい。

10

#### 【0150】

また、図11(C)に示すトランジスタの作製において、少なくとも半導体層754を形成した後、及び絶縁層757を形成した後の一又は双方で加熱処理を行うことが好ましい。当該加熱処理は、例えば、300以上700以下、又は基板の歪み点未満とする。また、加熱処理は減圧下、窒素雰囲気下、酸素雰囲気下、又は希ガス雰囲気下などで行うことができる。

20

#### 【0151】

また、形成直後の酸化物半導体層は、化学量論的組成より酸素が多い過飽和の状態であることが好ましい。例えば、スパッタリング法を用いて酸化物半導体層を形成する場合、成膜ガスの酸素の占める割合が多い条件で形成することが好ましく、特に酸素雰囲気(例えば酸素ガス100%)で成膜を行うことが好ましい。

20

#### 【0152】

また、スパッタリング法を用いて酸化物半導体膜を成膜する際に、基板温度を100以上500以下、好ましくは200以上350以下にして酸化物半導体膜を成膜してもよい。このようにすることで容易にCACAC-O<sub>5</sub>を形成することができる。

#### 【0153】

また、酸化物半導体層に十分な酸素が供給されて酸素を過飽和の状態するために、酸化物半導体層に接する絶縁層(例えば絶縁層701、714、753、757など)として過剰酸素を含む絶縁層を形成してもよい。

30

#### 【0154】

例えば、スパッタリング法を用いて膜中に酸素が多く含まれる成膜条件で絶縁膜を成膜することにより、過剰酸素を含む絶縁層を形成できる。また、より多くの過剰酸素を絶縁層に含ませたい場合には、イオン注入法やイオンドーピング法やプラズマ処理によって酸素を添加すればよい。また、酸化物半導体層に酸素を添加してもよい。

#### 【0155】

また、スパッタリング装置において、成膜室内の残留水分は、少ないことが好ましい。このため、スパッタリング装置に吸着型の真空ポンプを用いることが好ましい。また、コードトラップを用いてもよい。

#### 【0156】

上記加熱処理に用いられる加熱処理装置としては、G R T A ( G a s R a p i d T h e r m a l A n n e a l i n g ) 装置又はL R T A ( L a m p R a p i d T h e r m a l A n n e a l i n g ) 装置などのR T A ( R a p i d T h e r m a l A n n e a l i n g ) 装置を用いてもよい。なお、これに限定されず、電気炉など、別の加熱処理装置を用いてもよい。

40

#### 【0157】

また、上記加熱処理を行った後、その加熱温度を維持しつつ、又はその加熱温度から降温する過程で該加熱処理を行った炉と同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア(露点が-40以下、好ましくは-60以下の雰囲気)を導入する。このとき、酸素ガス又はN<sub>2</sub>Oガスは、水及び水素などを含まないことが好ましい。また、加熱処理装置に導入する酸素ガス又はN<sub>2</sub>Oガスの純度は、6N以上、好ましく

50

は 7 N 以上であるとよい。すなわち、酸素ガス又は N<sub>2</sub>O ガス中の不純物濃度は、1 ppm 以下、好ましくは 0.1 ppm 以下であることが好ましい。この工程により、酸化物半導体層に酸素が供給され、酸化物半導体層中の酸素欠損を低減できる。なお、上記高純度の酸素ガス、高純度の N<sub>2</sub>O ガス、又は超乾燥エアの導入は上記加熱処理時に行つてもよい。

#### 【 0 1 5 8 】

高純度化させた酸化物半導体層の水素濃度は、二次イオン質量分析法 (SIMS ともいいう) の測定値において、 $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、さらには  $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、さらには  $5 \times 10^{-7}$  atoms / cm<sup>3</sup> 以下であることが好ましい。

10

#### 【 0 1 5 9 】

高純度化させた酸化物半導体層のキャリア密度を  $1 \times 10^{14}$  / cm<sup>3</sup> 未満、好ましくは  $1 \times 10^{12}$  / cm<sup>3</sup> 未満、さらに好ましくは  $1 \times 10^{11}$  / cm<sup>3</sup> 未満にすることができる。このようにキャリア密度を少なくすることにより、チャネル幅 1 μmあたりのトランジスタのオフ電流を  $1 \times 10^{-19}$  A (100 zA) 以下、より好ましくは  $1 \times 10^{-22}$  A (100 yA) 以下にまで抑制できる。一般にトランジスタのオフ電流は、低ければ低いほどよいが、トランジスタのオフ電流の下限値は、約  $1 \times 10^{-30}$  A / μm であると見積もられる。

#### 【 0 1 6 0 】

領域 712a 及び領域 712b に含まれるドーパントとしては、例えば元素周期表における 13 族の元素 (例えば硼素など)、15 族の元素 (例えば窒素、リン、及び砒素の一つ又は複数)、及び希ガス元素 (例えばヘリウム、アルゴン、及びキセノンの一つ又は複数) を挙げることができ、これらのいずれか一つ又は複数を適用できる。導電層 715 を形成した後、導電層 715 をマスクとして当該ドーパントを添加し、少なくとも絶縁層 716a 及び絶縁層 716b を形成した後に導電層 715、絶縁層 716a 及び絶縁層 716b をマスクとして当該ドーパントを再度添加することで、自己整合的に領域 709a、領域 709b、領域 712a、及び領域 712b、並びにチャネル形成領域 713 を形成することができる。

20

#### 【 0 1 6 1 】

絶縁層 714 及び 753 は、トランジスタのゲート絶縁層としての機能を有する。絶縁層 714 及び 753 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

30

#### 【 0 1 6 2 】

導電層 715 及び導電層 751 は、トランジスタのゲート電極としての機能を有する。導電層 715 及び 751 としては、例えばモリブデン、チタン、クロム、タンタル、マグネシウム、銀、タンゲステン、アルミニウム、銅、ネオジム、又はスカンジウムなどの金属材料を含む層を適用できる。なお、導電層 715 及び導電層 751 はゲート配線としても機能する。

40

#### 【 0 1 6 3 】

絶縁層 716a、716b、717 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

#### 【 0 1 6 4 】

導電層 718a 及び導電層 718b、並びに導電層 755a 及び導電層 755b は、トランジスタのソース電極又はドレイン電極としての機能を有する。導電層 718a 及び導電層 718b、並びに導電層 755a 及び導電層 755b としては、例えばモリブデン、チタン、クロム、タンタル、マグネシウム、銀、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム、又はルテニウムなどの金属材料を含む層を適用できる。なお、導電

50

層 7 1 8 a 及び導電層 7 1 8 b、並びに導電層 7 5 5 a 及び導電層 7 5 5 b は、ソース配線又はドレン配線としても機能する。

【 0 1 6 5 】

絶縁層 7 1 9 及び 7 5 7 は、保護層としての機能を有する。絶縁層 7 1 9 及び 7 5 7 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

【 0 1 6 6 】

さらに、上記トランジスタの電気特性の一例として、図 1 1 ( B ) に示すトランジスタの一例の  $I_d - V_g$  特性について、図 1 2 を参照して説明する。なお、図 1 2 に示す  $I_d - V_g$  特性を示すトランジスタは、半導体層 7 1 1 が厚さ 20 nm の In - Ga - Zn 系酸化物半導体層であり、絶縁層 7 1 4 が厚さ 20 nm の酸化窒化シリコン層であり、導電層 7 1 5 が厚さ 30 nm の窒化タンタル層と厚さ 200 nm のタンゲステン層の積層であり、導電層 7 1 8 a 及び 7 1 8 b が厚さ 30 nm のタンゲステン層であるとする。また、領域 7 1 2 a 及び 7 1 2 b を形成するためにリンを添加し、該リンの添加量が  $1 \times 10^{-5} \text{ cm}^{-2}$  であり、加速電圧は 30 kV であるとする。また、チャネル長が 5 μm であり、チャネル幅が 10 μm であるとする。また、横軸がゲート電圧  $V_g$  であり、縦軸がドレン電流  $I_d$  又は電界効果移動度  $\mu F_E$  である。

10

【 0 1 6 7 】

図 1 2 に示す  $I_d - V_g$  特性であるトランジスタの電界効果移動度は約  $20 \text{ cm}^2 / \text{V s}$  であり、オフ電流は検出限界以下であり、しきい値電圧が 0 V 以上である。

20

【 0 1 6 8 】

さらに、以下に示す式 (1) を参照して、図 1 2 に示す  $I_d - V_g$  特性であるトランジスタのオン抵抗の値を算出する。

【 0 1 6 9 】

【 数 1 】

$$R_d = \frac{V_d}{I_d} = \frac{V_d}{\frac{W}{L} \mu C_{ox} \left\{ (V_g - V_{th})V_d - \frac{1}{2} V_d^2 \right\}} \quad (1)$$

30

【 0 1 7 0 】

絶縁層 7 1 4 の比誘電率を 4.1 とするとゲート容量  $C_{ox}$  は  $1.82 \times 10^{-3} \text{ F/m}^2$  となる。さらに、図 1 2 のデータから、トランジスタの電界効果移動度  $\mu F_E$  を  $20 \text{ cm}^2 / \text{V s}$  とし、しきい値電圧  $V_{th}$  を 0.6 V とし、記憶回路の仕様例としてゲート電圧  $V_g$  を 3.3 V とし、ドレン電圧  $V_d$  を 1.8 V をすると、上記の式 (1) からオン抵抗  $R_d$  は 76.3 kΩ となる。

40

【 0 1 7 1 】

以上が図 1 1 に示すトランジスタの構造例の説明である。

【 0 1 7 2 】

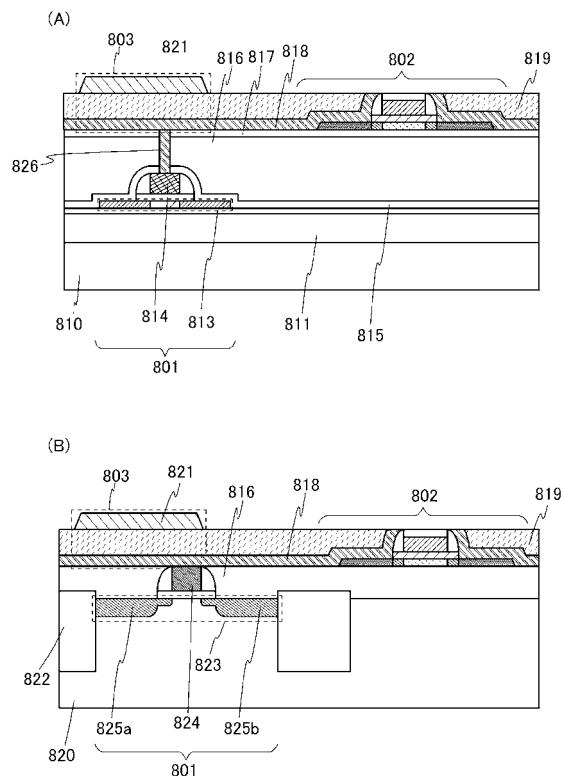

さらに、本発明の一態様である半導体装置に含まれる記憶回路の半導体記憶装置（図 6 参照）に、図 1 1 ( A ) に示すトランジスタを適用した場合について、図 1 3 を参照して説明する。図 1 3 は、本実施の形態に係る記憶回路の構造例を説明するための断面模式図である。なお、これに限定されず、図 1 1 ( B ) 及び図 1 1 ( C ) に示すトランジスタを用いて記憶回路を構成してもよい。

【 0 1 7 3 】

図 1 3 ( A ) に示す記憶回路は、チャネル形成層である単結晶シリコン層 8 1 3 を含むトランジスタ 8 0 1 と、絶縁層 8 1 5 乃至絶縁層 8 1 7 を介してトランジスタ 8 0 1 の上

50

に積層され、図 11(A)に示すトランジスタと同じ構造であるトランジスタ 802 と、トランジスタ 801 の作製工程で形成される容量素子 803 を有する。なお、ここでは、図 6 に示した半導体記憶装置を例にしていることから、トランジスタ 801 は p チャネル型トランジスタとし、トランジスタ 802 は n チャネル型トランジスタとする。なお、トランジスタ 802 の説明としては、図 11(A)に示すトランジスタの説明を適宜援用できる。

#### 【0174】

単結晶シリコン層 813 は、絶縁層 811 (BOX 層ともいう) を介して基板 810 の上に設けられる。なお、基板 810、絶縁層 811、及び単結晶シリコン層 813 の代わりに、図 13(B)に示すように、単結晶半導体基板 820 の埋め込み絶縁領域 822 に囲まれた半導体領域 823 を用いてトランジスタ 801 を構成してもよい。このとき、半導体領域 823 には、n 型又は p 型の導電型である不純物領域 825a 及び 825b が設けられる。10

#### 【0175】

絶縁層 815 は、保護層としての機能を有する。絶縁層 816 は、保護層のみならず、平坦化層としての機能を有する。また、絶縁層 817 は、下地層としての機能を有する。絶縁層 815 乃至絶縁層 817 としては、図 11(A)に示す絶縁層 701 と同様の材料を含む層を適用できる。

#### 【0176】

トランジスタ 802 のソース電極又はドレイン電極としての機能を有する導電層 818 は、トランジスタ 801 のゲート電極としての機能を有する導電層 814 に接続される。なお、導電層 818 と導電層 814 は、複数の導電層を介して接続されていてもよい。なお、図 13(B)に示すように、記憶回路の構造を、トランジスタ 801 のゲート電極としての機能を有する導電層 824 と導電層 818 が直接接する構造にしてもよい。また、導電層 818 と導電層 814 を直接接続せず、別の導電層（例えば導電層 826）を介して導電層 818 と導電層 814 を電気的に接続させてもよい（図 13(A)参照）。なお、導電層 826 は図 11(A)に示すトランジスタの導電層 718a、導電層 718b と同様の材料を含む層を形成し、当該層を平坦化又はエッチングすることで形成できる。20

#### 【0177】

また、トランジスタ 802 には上記したオフ電流が極めて低いトランジスタを適用できる。例えば、導電層 818 は図 11(A)に示すトランジスタの導電層 718a に対応する。30

#### 【0178】

容量素子 803 は一対の導電層の間に誘電体を有する構造であり、一対の導電層の一方は導電層 818 であり、他方の導電層は導電層 821 であり、誘電体は絶縁層 819 である。絶縁層 819 は、図 11(A)に示すトランジスタの絶縁層 719 に対応する。導電層 821 は導電層 818 と同様の構成とすればよい。

#### 【0179】

以上が図 13 に示す記憶回路の構造例の説明である。

#### 【0180】

以上より、オフ電流が極めて低いトランジスタとして、酸化物半導体を用いることで実施でき、揮発性メモリを構成するトランジスタに酸化物半導体を用いたトランジスタを適用することで不揮発性メモリとして機能させることができ、本発明の一態様である半導体装置に含まれる記憶回路の半導体記憶装置に適用することができる。40

#### 【0181】

なお、本実施の形態に記載の構成、方法などは、他の実施の形態に記載の構成、方法などと適宜、組み合わせて用いることができる。

#### 【0182】

#### (実施の形態 3)

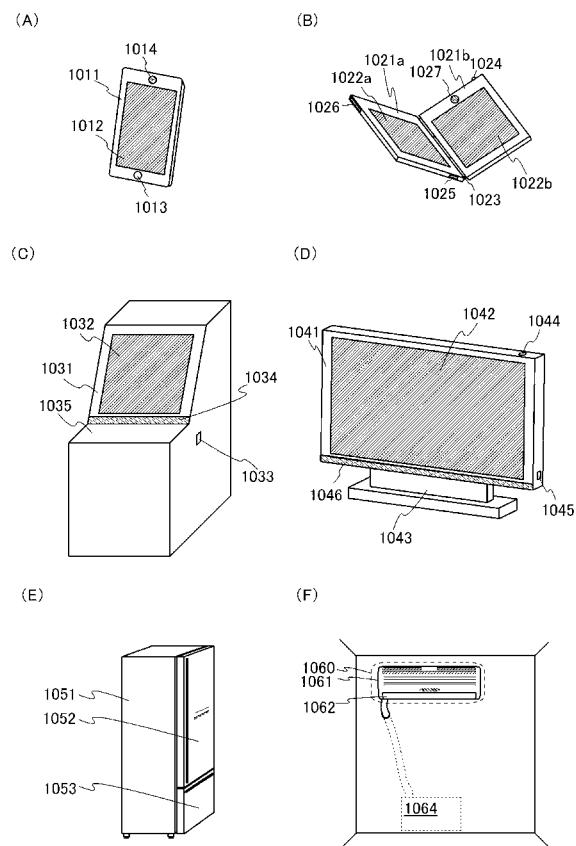

本実施の形態では、本発明の一態様である半導体装置を用いた電子機器の例について、50

図面を参照して説明する。先の実施の形態で説明したプロセッサに加えて、レジスタ、レジスタコントローラ、インストラクションデコーダ、インターフェースなどを設けることでC P U又はD S Pなど処理能力を有する半導体装置を構成することができる。

【0183】

また、先の実施の形態で説明したプロセッサは優れた低消費電力化が可能であるため、当該プロセッサを有する半導体装置についても優れた低消費電力化が可能である。図14に当該半導体装置を適用した電子機器の具体例を示す。

【0184】

図14(A)に示す電子機器は、携帯型情報端末の一例である。

10

【0185】

図14(A)に示す電子機器は、筐体1011と、筐体1011に設けられたパネル1012と、ボタン1013と、スピーカー1014と、を具備する。

【0186】

なお、筐体1011に、外部機器に接続するための接続端子及び操作ボタンが設けられてもよい。

【0187】

パネル1012は、表示パネル(ディスプレイ)である。パネル1012は、タッチパネルの機能を有することが好ましい。

【0188】

ボタン1013は、筐体1011に設けられる。例えば、ボタン1013が電源ボタンであれば、ボタン1013を押すことにより、電子機器をオン状態にするか否かを制御することができる。

20

【0189】

スピーカー1014は、筐体1011に設けられる。スピーカー1014は音声を出力する。

【0190】

なお、筐体1011にマイクが設けられていてもよい。筐体1011にマイクを設けられることにより、例えば図14(A)に示す電子機器を電話機として機能させることができる。

30

【0191】

図14(A)に示す電子機器は、筐体1011の内部に先の実施の形態で説明したプロセッサを有する半導体装置などを有する。

【0192】

図14(A)に示す電子機器は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊戯機の一つ又は複数としての機能を有する。

【0193】

図14(B)に示す電子機器は、折り畳み式の情報端末の一例である。

【0194】

図14(B)に示す電子機器は、筐体1021aと、筐体1021bと、筐体1021aに設けられたパネル1022aと、筐体1021bに設けられたパネル1022bと、軸部1023と、ボタン1024と、接続端子1025と、記録媒体挿入部1026と、スピーカー1027と、を備える。

40

【0195】

筐体1021aと筐体1021bは、軸部1023により接続される。

【0196】

パネル1022a及びパネル1022bは、表示パネル(ディスプレイ)である。パネル1022a及びパネル1022bは、タッチパネルとしての機能を有することが好ましい。

【0197】

50

図14(B)に示す電子機器は、軸部1023を有するため、パネル1022aとパネル1022bを対向させて折り畳むことができる。

【0198】

ボタン1024は、筐体1021bに設けられる。なお、筐体1021aにボタン1024を設けてもよい。例えば、電源ボタンとしての機能を有するボタン1024を設けることより、ボタン1024を押すことで電子機器に対する電源電圧の供給を制御できる。

【0199】

接続端子1025は、筐体1021aに設けられる。なお、筐体1021bに接続端子1025が設けられていてもよい。また、接続端子1025が筐体1021a及び筐体1021bの一方又は両方に複数設けられていてもよい。接続端子1025は、図14(B)に示す電子機器と他の機器を接続するための端子である。

10

【0200】

記録媒体挿入部1026は、筐体1021aに設けられる。筐体1021bに記録媒体挿入部1026が設けられていてもよい。また、記録媒体挿入部1026が筐体1021a及び筐体1021bの一方又は両方に複数設けられていてもよい。例えば、記録媒体挿入部にカード型記録媒体を挿入することにより、カード型記録媒体のデータを電子機器に読み出し、又は電子機器内のデータをカード型記録媒体に書き込むことができる。

【0201】

スピーカー1027は、筐体1021bに設けられる。スピーカー1027は、音声を出力する。なお、筐体1021aにスピーカー1027を設けてもよい。

20

【0202】

なお、筐体1021a又は筐体1021bにマイクを設けてもよい。筐体1021a又は筐体1021bにマイクが設けられることにより、例えば図14(B)に示す電子機器を電話機として機能させることができる。

【0203】

図14(B)に示す電子機器は、筐体1021a又は筐体1021bの内部に実施の形態1で説明したプロセッサを有する半導体装置などを有する。

【0204】

図14(B)に示す電子機器は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊技機の一つ又は複数としての機能を有する。

30

【0205】

図14(C)に示す電子機器は、据え置き型情報端末の一例である。図14(C)に示す据え置き型情報端末は、筐体1031と、筐体1031に設けられたパネル1032と、ボタン1033と、スピーカー1034と、を具備する。

【0206】

パネル1032は、表示パネル(ディスプレイ)である。パネル1032は、タッチパネルとしての機能を有することが好ましい。

【0207】

なお、筐体1031の甲板部1035にパネル1032と同様のパネルを設けてもよい。上記パネルは、タッチパネルとしての機能を有することが好ましい。

40

【0208】

さらに、筐体1031に券などを出力する券出力部、硬貨投入部、及び紙幣挿入部などを設けてもよい。

【0209】

ボタン1033は、筐体1031に設けられる。例えば、ボタン1033が電源ボタンであれば、ボタン1033を押すことで電子機器に対する電源電圧の供給を制御できる。

【0210】

スピーカー1034は、筐体1031に設けられる。スピーカー1034は、音声を出力する。

【0211】

50

図14(C)に示す電子機器は、筐体1031の内部に実施の形態1で説明したプロセッサを有する半導体装置などを有する。

【0212】

図14(C)に示す電子機器は、例えば現金自動預け払い機、チケットなどの注文をするための情報通信端末(マルチメディアステーションともいう)、又は遊技機としての機能を有する。

【0213】

図14(D)は、据え置き型情報端末の一例である。図14(D)に示す電子機器は、筐体1041と、筐体1041に設けられたパネル1042と、筐体1041を支持する支持台1043と、ボタン1044と、接続端子1045と、スピーカー1046と、を備える。

10

【0214】

なお、筐体1041に外部機器に接続させるための接続端子を設けてもよい。

【0215】

パネル1042は、表示パネル(ディスプレイ)としての機能を有する。

【0216】

ボタン1044は、筐体1041に設けられる。例えば、ボタン1044が電源ボタンであれば、ボタン1044を押すことで電子機器に対する電源電圧の供給を制御できる。

【0217】

接続端子1045は、筐体1041に設けられる。接続端子1045は、図14(D)に示す電子機器と他の機器を接続するための端子である。例えば、接続端子1045により図14(D)に示す電子機器とパソコンコンピュータを接続すると、パソコンコンピュータから入力されるデータ信号に応じた画像をパネル1042に表示させることができる。例えば、図14(D)に示す電子機器のパネル1042が接続する他の電子機器のパネルより大きければ、当該他の電子機器の表示画像を拡大することができ、複数の人が同時に視認しやすくなる。

20

【0218】

スピーカー1046は、筐体1041に設けられる。スピーカー1046は、音声を出力する。

【0219】

図14(D)に示す電子機器は、筐体1041の内部に実施の形態1で説明したプロセッサを有する半導体装置などを有する。

30

【0220】

図14(D)に示す電子機器は、例えば出力モニタ、パソコンコンピュータ、及びテレビジョン装置の一つ又は複数としての機能を有する。

【0221】

図14(E)は、電気冷凍冷蔵庫の一例である。図14(E)に示す電子機器は、筐体1051と、冷蔵室用扉1052と、冷凍室用扉1053と、を備える。

【0222】

図14(E)に示す電子機器は、筐体1051の内部に実施の形態1で説明したプロセッサを有する半導体装置などを有する。上記構成にすることにより、例えば、冷蔵室用扉1052及び冷凍室用扉1053の開閉に従って、筐体1051内の半導体装置に対する電源電圧の供給を制御できる。

40

【0223】

図14(F)は、エアコンディショナーの一例である。図14(F)に示す電子機器は、室内機1060及び室外機1064により構成される。

【0224】

室内機1060は、筐体1061と、送風口1062と、を備える。

【0225】

図14(F)に示す電子機器は、筐体1061の内部に実施の形態1で説明したプロセ

10

20

30

40

50

ッサを有する半導体装置などを有する。上記構成にすることにより、例えば、リモートコントローラからの信号に従って、筐体 1061 内の半導体装置に対する電源電圧の供給を制御できる。

#### 【0226】

なお、図 14 (F) では、室内機と室外機で構成されるセパレート型のエアコンディショナーを例示しているが、室内機の機能と室外機の機能とを 1 つの筐体に有するエアコンディショナーであってもよい。

#### 【0227】

なお、これに限定されず、電子レンジなどの高周波加熱装置、又は電気炊飯器などにも先の実施の形態で説明したプロセッサを有する半導体装置を適用できる。

10

#### 【0228】

以上より、先の実施の形態で説明したプロセッサを有する半導体装置を用いることにより、優れた低消費電力化された電子機器を作製することができる。

#### 【0229】

なお、本実施の形態に記載の構成、方法などは、他の実施の形態に記載の構成、方法などと適宜、組み合わせて用いることができる。

#### 【符号の説明】

#### 【0230】

|     |            |    |

|-----|------------|----|

| 100 | プロセッサ      |    |

| 101 | 電源供給制御スイッチ | 20 |

| 103 | 電源供給制御スイッチ |    |

| 105 | 演算回路       |    |

| 107 | キャッシュメモリ   |    |

| 109 | 記憶回路       |    |

| 111 | 記憶回路       |    |

| 113 | 温度検出回路     |    |

| 115 | 温度検出回路     |    |

| 117 | コントローラ     |    |

| 119 | 電源         |    |

| 121 | トランジスタ     | 30 |

| 122 | トランジスタ     |    |

| 151 | インターフェース部  |    |

| 152 | クロック生成部    |    |

| 153 | 出力信号制御部    |    |

| 154 | バッファ部      |    |

| 155 | カウンタ回路     |    |

| 201 | 温度センサ      |    |

| 202 | 温度センサ      |    |

| 205 | 温度検出用ダイオード |    |

| 206 | 定電流源       | 40 |

| 207 | バッファアンプ    |    |

| 208 | D A C      |    |

| 209 | 演算回路       |    |

| 210 | ルックアップテーブル |    |

| 211 | スイッチ       |    |

| 300 | メモリセル      |    |

| 311 | トランジスタ     |    |

| 312 | トランジスタ     |    |

| 313 | 容量素子       |    |

| 700 | 被素子形成層     | 50 |

|           |          |    |

|-----------|----------|----|

| 7 0 1     | 絶縁層      |    |

| 7 0 9 a   | 領域       |    |

| 7 0 9 b   | 領域       |    |

| 7 1 1     | 半導体層     |    |

| 7 1 2 a   | 領域       |    |

| 7 1 2 b   | 領域       |    |

| 7 1 3     | チャネル形成領域 |    |

| 7 1 4     | 絶縁層      |    |

| 7 1 5     | 導電層      | 10 |

| 7 1 6 a   | 絶縁層      |    |

| 7 1 6 b   | 絶縁層      |    |

| 7 1 7     | 絶縁層      |    |

| 7 1 8 a   | 導電層      |    |

| 7 1 8 b   | 導電層      |    |

| 7 1 9     | 絶縁層      |    |

| 7 5 0     | 被素子形成層   |    |

| 7 5 1     | 導電層      |    |

| 7 5 2     | 絶縁層      |    |

| 7 5 3     | 絶縁層      |    |

| 7 5 4     | 半導体層     | 20 |

| 7 5 5 a   | 導電層      |    |

| 7 5 5 b   | 導電層      |    |

| 7 5 6     | 絶縁層      |    |

| 7 5 7     | 絶縁層      |    |

| 8 0 1     | トランジスタ   |    |

| 8 0 2     | トランジスタ   |    |

| 8 0 3     | 容量素子     |    |

| 8 1 0     | 基板       |    |

| 8 1 1     | 絶縁層      |    |

| 8 1 3     | 単結晶シリコン層 | 30 |

| 8 1 4     | 導電層      |    |

| 8 1 5     | 絶縁層      |    |

| 8 1 6     | 絶縁層      |    |

| 8 1 7     | 絶縁層      |    |

| 8 1 8     | 導電層      |    |

| 8 1 9     | 絶縁層      |    |

| 8 2 0     | 単結晶半導体基板 |    |

| 8 2 1     | 導電層      |    |

| 8 2 2     | 絶縁領域     |    |

| 8 2 3     | 半導体領域    | 40 |

| 8 2 4     | 導電層      |    |

| 8 2 5 a   | 不純物領域    |    |

| 8 2 6     | 導電層      |    |

| 1 0 1 1   | 筐体       |    |

| 1 0 1 2   | パネル      |    |

| 1 0 1 3   | ボタン      |    |

| 1 0 1 4   | スピーカー    |    |

| 1 0 2 1 a | 筐体       |    |

| 1 0 2 1 b | 筐体       |    |

| 1 0 2 2 a | パネル      | 50 |

|           |         |    |

|-----------|---------|----|

| 1 0 2 2 b | パネル     |    |

| 1 0 2 3   | 軸部      |    |

| 1 0 2 4   | ボタン     |    |

| 1 0 2 5   | 接続端子    |    |

| 1 0 2 6   | 記録媒体挿入部 |    |

| 1 0 2 7   | スピーカー   |    |

| 1 0 3 1   | 筐体      |    |

| 1 0 3 2   | パネル     | 10 |

| 1 0 3 3   | ボタン     |    |

| 1 0 3 4   | スピーカー   |    |

| 1 0 3 5   | 甲板部     |    |

| 1 0 4 1   | 筐体      |    |

| 1 0 4 2   | パネル     |    |

| 1 0 4 3   | 支持台     |    |

| 1 0 4 4   | ボタン     |    |

| 1 0 4 5   | 接続端子    |    |

| 1 0 4 6   | スピーカー   |    |

| 1 0 5 1   | 筐体      |    |

| 1 0 5 2   | 冷蔵室用扉   | 20 |

| 1 0 5 3   | 冷凍室用扉   |    |

| 1 0 6 0   | 室内機     |    |

| 1 0 6 1   | 筐体      |    |

| 1 0 6 2   | 送風口     |    |

| 1 0 6 4   | 室外機     |    |

【図 1】

【図 3】

【図 2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 16】

---

フロントページの続き

F ターム(参考) 5F110 AA06 BB05 CC02 DD12 DD13 DD14 DD15 DD21 DD25 EE02

EE03 EE04 EE31 EE38 FF01 FF02 FF03 FF04 FF05 FF36

GG01 GG02 GG06 GG12 GG13 GG14 GG15 GG16 GG17 GG19

GG25 GG28 GG58 HJ01 HK02 HK03 HK04 HK21 HK42 HM02

NN03 NN22 NN23 NN24 NN40 NN72 NN74 NN78 QQ11 QQ19