(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6356140号

(P6356140)

(45) 発行日 平成30年7月11日(2018.7.11)

(24) 登録日 平成30年6月22日(2018.6.22)

(51) Int.Cl.

F 1

H02M 3/155 (2006.01)

H03K 7/08 (2006.01)H02M 3/155

H03K 7/08H

C

請求項の数 16 (全 23 頁)

(21) 出願番号 特願2015-542803 (P2015-542803)

(86) (22) 出願日 平成25年11月15日 (2013.11.15)

(65) 公表番号 特表2016-503643 (P2016-503643A)

(43) 公表日 平成28年2月4日 (2016.2.4)

(86) 國際出願番号 PCT/US2013/070244

(87) 國際公開番号 WO2014/078625

(87) 國際公開日 平成26年5月22日 (2014.5.22)

審査請求日 平成28年11月14日 (2016.11.14)

(31) 優先権主張番号 61/726,977

(32) 優先日 平成24年11月15日 (2012.11.15)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/080,151

(32) 優先日 平成25年11月14日 (2013.11.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 397050741

マイクロチップ テクノロジー インコーポレイテッド

MICROCHIP TECHNOLOGY INCORPORATED

アメリカ合衆国 85224-6199

アリゾナ チャンドラー ウエスト チャンドラー ブルヴァード 2355

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100113413

弁理士 森下 夏樹

前置審査

最終頁に続く

(54) 【発明の名称】スロープ補償モジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

スロープ補償モジュールを備えるスイッチモード電力供給装置(SMPS)コントローラであって、前記スロープ補償モジュールは、前記SMPSコントローラ内の電流モード制御と併用するためのものであり、

前記SMPSコントローラは、

出力を備える誤差増幅器と、

第1の入力を備える電圧コンパレータと

を備え、

前記電圧コンパレータの第2の入力は、電流信号を測定する電流/電圧回路に結合するために適合されており、

前記SMPSコントローラは、

前記誤差増幅器と結合された電圧基準と、

周期ジェネレータと、

リセット支配ラッチと

をさらに備え、

前記スロープ補償モジュールは、

前記誤差増幅器の出力と前記電圧コンパレータの第1の入力との間に結合されたスロープ補償キャパシタと、

前記スロープ補償キャパシタと並列に結合されたスロープ補償スイッチと、

10

20

前記スロープ補償キャパシタの出力側および前記スロープ補償スイッチに結合されたプログラム可能定電流源と

を備え、

前記スロープ補償スイッチが開放されると、前記スロープ補償キャパシタは、前記定電流源を通して回路コモンに充電し、それによって、線形減少ランプ電圧を発生させ、

前記リセット支配ラッチは、

前記周期ジェネレータの出力に結合された設定入力と、

前記電圧コンパレータの出力に結合されたリセット入力と、

前記スロープ補償スイッチに結合され、前記スロープ補償スイッチの開閉を制御する出力と

を備え、

前記リセット支配ラッチの出力はまた、制御信号を提供し、

前記周期ジェネレータは、あるパルス周期において、複数のパルスを前記リセット支配ラッチの設定入力に提供し、パルスが前記リセット支配ラッチの設定入力で受信される度に、前記リセット支配ラッチの出力は、第1の論理レベルから第2の論理レベルになり、

前記リセット支配ラッチの出力が前記第2の論理レベルにあるとき、前記スロープ補償スイッチは、開放し、前記スロープ補償キャパシタは、前記プログラム可能定電流源を通して回路コモンに充電し、それによって、前記誤差増幅器からのフィードバック誤差電圧をスロープ補償フィードバック誤差電圧に変調させるための線形減少ランプ電圧を発生させ、

前記電圧コンパレータの第1の入力に結合されている前記スロープ補償フィードバック誤差電圧が、前記電圧コンパレータの第2の入力におけるS M P S インダクタを通る電流を表す電圧未満であるとき、前記リセット支配ラッチの出力は、前記第1の論理レベルに戻り、前記スロープ補償スイッチは、閉鎖し、それによって、前記スロープ補償キャパシタを放電させ、前記電圧コンパレータの第1の入力を前記誤差増幅器からのフィードバック誤差電圧に戻す、S M P S コントローラ。

#### 【請求項2】

前記誤差増幅器の出力と前記誤差増幅器の第2の入力との間に結合されたループ補償ネットワークをさらに備える、請求項1に記載のS M P S コントローラ。

#### 【請求項3】

前記S M P S インダクタを通る電流を表す電圧は、電流／電圧センサを用いて発生される、請求項1に記載のS M P S コントローラ。

#### 【請求項4】

前記電流／電圧センサは、前記S M P S インダクタの電流経路内の電流変圧器と、前記電流変圧器に結合された整流器ダイオードと、レジスタに結合された負荷レジスタとを備える、請求項3に記載のS M P S コントローラ。

#### 【請求項5】

前記電流／電圧センサは、前記S M P S インダクタの電流経路内のレジスタと、前記レジスタに結合されたダイオードとを備える、請求項3に記載のS M P S コントローラ。

#### 【請求項6】

前記周期ジェネレータは、複数のパルス周期時間のうちの1つを選択するためにプログラム可能である、請求項1～5のうちの1項に記載のS M P S コントローラ。

#### 【請求項7】

前記スロープ補償スイッチは、金属酸化物半導体電界効果トランジスタ（M O S F E T）である、請求項1～6のうちの1項に記載のS M P S コントローラ。

#### 【請求項8】

前記リセット支配ラッチの出力と前記スロープ補償スイッチとの間に結合されたスロープ補償スイッチコントローラをさらに備え、前記スロープ補償スイッチコントローラは、前記スロープ補償スイッチのためのプログラム可能開放遅延を提供する、請求項1～7のうちの1項に記載のS M P S コントローラ。

10

20

30

40

50

## 【請求項 9】

前記スロープ補償スイッチコントローラが、前記スロープ補償スイッチのためのプログラム可能最小閉鎖時間を提供することをさらに含む、請求項<sup>8</sup>に記載のSMP<sub>S</sub>コントローラ。

## 【請求項 10】

SMP<sub>S</sub>フィルタキャパシタからの出力電圧は、抵抗分圧器を通して提供される、請求項<sup>1</sup>～<sup>9</sup>のうちの1項に記載のSMP<sub>S</sub>コントローラ。

## 【請求項 11】

前記定電流源は、前記SMP<sub>S</sub>コントローラの試験の間、較正のために適合される、請求項<sup>1</sup>に記載のSMP<sub>S</sub>コントローラ。

10

## 【請求項 12】

前記スロープ補償キャパシタは、所望の容量値に対してプログラム可能に選択可能な複数のスロープ補償キャパシタである、請求項<sup>1</sup>に記載のSMP<sub>S</sub>コントローラ。

## 【請求項 13】

前記スロープ補償キャパシタは、前記SMP<sub>S</sub>コントローラの試験の間、所望の容量値に対してプログラム可能に選択可能な複数のスロープ補償キャパシタである、請求項<sup>1</sup>に記載のSMP<sub>S</sub>コントローラ。

## 【請求項 14】

前記プログラム可能定電流源と前記周期ジェネレータとに結合されたデジタルプロセッサをさらに備え、前記デジタルプロセッサは、それぞれ、前記プログラム可能定電流源および前記周期ジェネレータに定電流値およびパルス周期時間提供する、請求項<sup>1</sup>～<sup>13</sup>のうちの1項に記載のSMP<sub>S</sub>コントローラ。

20

## 【請求項 15】

前記SMP<sub>S</sub>コントローラは、マイクロコントローラ中に埋め込まれている、請求項<sup>1</sup>～<sup>6</sup>のうちの1項に記載のSMP<sub>S</sub>コントローラ。

## 【請求項 16】

スロープ補償モジュールを備えるスイッチモード電力供給装置(SMP<sub>S</sub>)コントローラ内にスロープ補償を提供するための方法であって、前記スロープ補償モジュールは、前記SMP<sub>S</sub>コントローラ内の電流モード制御と併用するためのものであり、

前記SMP<sub>S</sub>コントローラは、

30

出力を備える誤差増幅器と、

第1の入力を備える電圧コンパレータと

を備え、

前記電圧コンパレータの第2の入力は、電流信号を測定する電流／電圧回路に結合するために適合されており、

前記スロープ補償モジュールは、

前記誤差増幅器の出力と前記電圧コンパレータの第1の入力との間に結合されたスロープ補償キャパシタと、

前記スロープ補償キャパシタと並列に結合されたスロープ補償スイッチと、

前記スロープ補償キャパシタの出力側および前記スロープ補償スイッチに結合されたプログラム可能定電流源と

を備え、

前記スロープ補償スイッチが開放されると、前記スロープ補償キャパシタは、前記定電流源を通して回路コモンに充電し、それによって、線形減少ランプ電圧を発生させ、

前記方法は、

基準電圧を提供するステップと、

前記基準電圧とSMP<sub>S</sub>フィルタキャパシタからの電圧との間の差異である誤差電圧を提供する前記誤差増幅器を用いて、前記基準電圧を前記SMP<sub>S</sub>コントローラからのファードバック電圧と比較するステップと、

前記スロープ補償キャパシタからのスロープ補償誤差電圧をSMP<sub>S</sub>インダクタ内で測

40

50

定された電流の電圧表現と比較するステップと、

周期ジェネレータの出力に結合された設定入力と、前記電圧コンパレータの出力に結合されたリセット入力と、前記スロープ補償スイッチの開閉を制御し、制御信号を供給するための出力とを有するリセット支配ラッチを提供するステップと、

あるパルス周期において、前記周期ジェネレータから複数のパルスを前記リセット支配ラッチの設定入力に提供するステップであって、パルスが前記リセット支配ラッチの設定入力において受信される度に、前記リセット支配ラッチの出力は、第1の論理レベルから第2の論理レベルになる、ステップと、

前記リセット支配ラッチの出力が前記第2の論理レベルにあるとき、前記スロープ補償スイッチを開放するステップと、

前記誤差増幅器からのフィードバック誤差電圧をスロープ補償フィードバック誤差電圧に変調するための線形減少ランプ電圧を発生させるステップと、

前記スロープ補償誤差電圧が、前記SMPsインダクタを通る電流を表す電圧未満であるとき、前記リセット支配ラッチの出力を前記第1の論理レベルに戻し、前記スロープ補償スイッチを閉鎖するステップと

を含む、方法。

【発明の詳細な説明】

【技術分野】

【0001】

(関連の特許出願)

本出願は、2012年11月15日に出願された、Hartono Darmawaskitia、Sean Stacy Steedman、Christian Nicola Groza、Marilena Mancioiu、John Robert CharaisおよびZeke Lundstrumによる「Slope Compensation Module」という題名の共同所有された米国仮特許出願第61/726,977号に対して優先権を主張する。上記文献は、全ての目的のために本明細書において参考することによって援用される。

【0002】

(技術分野)

本開示は、スロープ補償モジュールに関し、特に、例えば、限定ではないが、コンパレータおよび演算増幅器等の他のモジュールと組み合わせて、マイクロコントローラ内で使用し、スイッチモード電力供給装置回路および類似用途を制御するためのスロープ補償モジュールに関する。

【背景技術】

【0003】

(背景)

リアルタイムアナログ閉ループシステムならびに周波数ジェネレータおよび/またはパルス幅変調器等の他の用途のための回路を有する、マイクロコントローラの必要性が、存在する。従来のスイッチモード電力供給装置実施形態では、ユーザは、レジスタおよび/またはキャパシタ等の外部コンポーネントを提供し、スイッチモード電力供給装置用途においてスロープ値を設定しなければならず、故に、選択は、固定される。言い換えると、印刷回路基板上のコンポーネントを物理的に変更せずに、調節または変更されることができない。特に、他の周辺デバイスおよび外部デバイスと組み合わせて、マイクロコントローラ制御スイッチモード電力供給装置または他の用途を形成するとき、特に、マイクロコントローラ内で使用するためのスロープ補償モジュールの必要性が、存在する。

【0004】

コモン(common)スイッチモード電力供給装置(SMPs)制御方法論は、「ピーク電流モード制御」(PCM)と呼ばれる。PCMでは、SMPs電力インダクタ電流は、アナログコンパレータによって監視される。コンパレータ閾値は、ピーク電流限界を設定する。ピーク電流は、平均電流に関連する(いくつかの仮定を伴う)。平均電流

とピーク電流との間の比率は、ユーザの PWM デューティサイクルが、50%を上回るときに変化し得る。50%を上回るデューティサイクルは、サブサイクル振動に関する問題を有する。これらの振動を停止することは、PWM デューティサイクルが増加するにつれて、ピーク電流限界を低下させる、「スロープ補償」の追加を要求する。ピーク電流の減少は、PWM デューティサイクルの増加に伴って、同一の平均電流を維持するように設計される。50%を上回るデューティサイクルでは、インダクタ電流は、次のサイクルの開始までにゼロに戻らない場合がある。本不安定性を防止するために、従来のアナログ PWM コントローラは、スロープ補償を使用して、電流基準値へと下向きスロープを変調させ、電源回路を安定させる。しかしながら、適切なスロープ補償の成分値の選択は、非常に狭くかつ具体的範囲の Smps 動作条件に対してのみ最適化され得る。

10

【発明の概要】

【課題を解決するための手段】

【0005】

(要約)

したがって、広範な動作範囲の PWM デューティサイクルにわたって、かつ Smps 用途等のためのマイクロコントローラと組み合わせ使用され得る、向上されたスロープ補償モジュールの必要性が、存在する。

【0006】

ある実施形態によると、スイッチモード電力供給装置 (Smps) コントローラ内の電流モード制御と併用するためのスロープ補償モジュールであって、入力と出力との間に結合されるスロープ補償キャパシタと、スロープ補償キャパシタと並列に結合されるスロープ補償スイッチと、スロープ補償キャパシタの出力側およびスロープ補償スイッチに結合される定電流源とを備えてもよく、スロープ補償スイッチが開放され得ると、スロープ補償キャパシタは、定電流源を通して回路コモンに充電し、それによって、線形減少 (負スロープ) ランプ電圧を発生させる、スロープ補償モジュールが、開示される。

20

【0007】

さらなる実施形態によると、スロープ補償スイッチが閉鎖されると、スロープ補償キャパシタは、放電し得る。さらなる実施形態によると、定電流源は、スロープ補償スイッチが第1の位置にあり得るとき、スロープ補償キャパシタの出力側から分断されてもよく、スロープ補償スイッチが第2の位置にあり得るとき、スロープ補償キャパシタの出力側に結合されてもよい。さらなる実施形態によると、線形減少 (負スロープ) ランプ電圧は、自動的に、フィードバックループ誤差電圧を調節するように適合されてもよい。さらなる実施形態によると、定電流源は、複数の選択可能定電流値を有する、プログラム可能定電流源を備えてもよい。さらなる実施形態によると、スロープ補償キャパシタは、所望の容量値に対してプログラム可能に選択可能な複数のスロープ補償キャパシタを備えてもよい。

30

【0008】

別の実施形態によると、スロープ補償モジュールを有する、スイッチモード電力供給装置 (Smps) コントローラは、電圧基準と、電圧基準に結合される第1の入力と、Smps フィルタキャパシタからの出力電圧に結合するために適合される第2の入力とを有する、演算増幅器と、演算増幅器の出力に結合される入力と、出力とを有する、スロープ補償モジュールであって、スロープ補償モジュールの入力と出力との間に結合されるスロープ補償キャパシタと、スロープ補償キャパシタと並列に結合されるスロープ補償スイッチと、スロープ補償キャパシタの出力側に結合される定電流源とを備え得る、スロープ補償モジュールと、電圧コンパレータであって、スロープ補償モジュールの出力に結合される第1の入力と、電流信号を測定する、電流 / 電圧回路に結合するために適合される第2の入力とを有する、電圧コンパレータと、周期ジェネレータと、リセット支配ラッチであって、周期ジェネレータの出力に結合される設定入力と、電圧コンパレータの出力に結合されるリセット入力と、スロープ補償スイッチに結合され、その開閉を制御し得る、出力とを備え得、リセット支配ラッチの出力はまた、制御信号を提供し得る、リセット支配ラッ

40

50

チとを備えててもよく、周期ジェネレータは、あるパルス周期において、リセット支配ラッチの設定入力に複数のパルスを提供してもよく、パルスが、リセット支配ラッチの設定入力において受信され得る度に、その出力は、第1の論理レベルから第2の論理レベルになつてもよく、リセット支配ラッチの出力が、第2の論理レベルにあり得るとき、スロープ補償スイッチは、開放してもよく、スロープ補償キャパシタは、定電流源を通して回路コモンに充電し、それによって、演算増幅器からのフィードバック誤差電圧をスロープ補償フィードバック誤差電圧に変調させるための線形減少（負スロープ）ランプ電圧を発生させてもよく、電圧コンパレータの第1の入力に結合され得る、スロープ補償フィードバック誤差電圧が、電圧コンパレータの第2の入力におけるSMPStを通過する電流を表す電圧未満であり得るとき、リセット支配ラッチの出力は、第1の論理レベルに戻ってもよく、スロープ補償スイッチは、閉鎖し、それによって、スロープ補償キャパシタを放電させ、電圧コンパレータの第1の入力を演算増幅器からのフィードバック誤差電圧に戻してもよい。10

#### 【0009】

さらなる実施形態によると、定電流源は、複数の選択可能定電流値を有する、プログラム可能定電流源であつてもよい。さらなる実施形態によると、バッファ増幅器は、演算増幅器の出力とスロープ補償キャパシタおよびスイッチとの間に結合されてもよい。さらなる実施形態によると、ループ補償ネットワークは、演算増幅器の出力と第2の入力との間に結合されてもよい。さらなる実施形態によると、SMPStを通過する電流を表す電圧は、電流／電圧センサを用いて発生されてもよい。さらなる実施形態によると、電流／電圧センサは、SMPStの電流経路内の電流変圧器と、電流変圧器に結合される整流器ダイオードと、レジスタに結合される負荷レジスタとを備えててもよい。さらなる実施形態によると、電流／電圧センサは、SMPStの電流経路内のレジスタと、レジスタに結合されるダイオードとを備えててもよい。さらなる実施形態によると、周期ジェネレータは、複数のパルス周期時間のうちの1つを選択するためにプログラム可能であつてもよい。20

#### 【0010】

さらなる実施形態によると、スロープ補償スイッチは、金属酸化物半導体電界効果トランジスタ（MOSFET）であつてもよい。さらなる実施形態によると、スロープ補償スイッチコントローラは、リセット支配ラッチの出力とスロープ補償スイッチとの間に結合されてもよく、スロープ補償スイッチコントローラは、スロープ補償スイッチのためのプログラム可能開放遅延を提供してもよい。さらなる実施形態によると、スロープ補償スイッチコントローラは、スロープ補償スイッチのためのプログラム可能最小閉鎖時間を提供してもよい。さらなる実施形態によると、SMPStからの出力電圧は、抵抗分圧器を通して提供されてもよい。さらなる実施形態によると、定電流源は、SMPStの試験の間、較正のために適合されてもよい。さらなる実施形態によると、スロープ補償キャパシタは、所望の容量値に対してプログラム可能に選択可能な複数のスロープ補償キャパシタであつてもよい。さらなる実施形態によると、スロープ補償キャパシタは、SMPStの試験の間、所望の容量値に対してプログラム可能に選択可能な複数のスロープ補償キャパシタであつてもよい。30

#### 【0011】

さらなる実施形態によると、デジタルプロセッサは、プログラム可能であり得る、定電流源と、プログラム可能であり得る、周期ジェネレータとに結合されてもよく、デジタルプロセッサは、それぞれ、定電流源および周期ジェネレータに定電流値およびパルス周期時間を提供してもよい。さらなる実施形態によると、SMPStは、マイクロコントローラを備えててもよい。さらなる実施形態によると、定電流源は、スロープ補償スイッチを用いて、スロープ補償キャパシタの出力側に結合されてもよい。さらなる実施形態によると、定電流源は、スロープ補償スイッチが第1の位置にあり得るとき、スロープ補償キャパシタの出力側から分断され、スロープ補償スイッチが第2の位置にあり得るとき、スロープ補償キャパシタの出力側に結合されてもよい。40

## 【0012】

さらに別の実施形態によると、アナログパルス幅変調（P W M）ジェネレータは、第1の電圧基準に結合される入力を有するキャパシタと、キャパシタの入力および出力と並列に結合されるスイッチと、キャパシタの出力に結合される定電流源と、キャパシタの出力に結合される第1の入力と、第2の電圧基準に結合された第2の入力と、スイッチの開閉を制御する出力とを有する、第1の電圧コンパレータと、キャパシタの出力に結合される第1の入力と、スイッチモード電力供給装置（S M P S）からの電圧に結合するために適合される第2の入力と、スイッチモード電力供給装置の電源スイッチを制御するためのパルス幅変調（P W M）制御信号を提供する出力とを有する、第2の電圧コンパレータとを備えてもよく、キャパシタの出力における電圧が、第1の電圧基準からの電圧未満であり得るとき、スイッチは、開放してもよく、それによって、キャパシタおよび定電流源は、線形負スロープ電圧波形を用いて、第1の電圧基準からの電圧を変調させてもよく、第1の電圧基準と第2の電圧基準との間の電圧差は、P W M制御信号の周期を判定してもよく、S M P Sからの電圧とキャパシタの第2のノードにおける電圧との間の電圧差は、P W M制御信号のデューティサイクルを判定してもよい。

10

## 【0013】

さらなる実施形態によると、定電流源は、複数の選択可能定電流値を有する、プログラム可能定電流源であってもよい。さらなる実施形態によると、キャパシタは、所望の容量値に対してプログラム可能に選択可能な複数のキャパシタであってもよい。さらなる実施形態によると、第1の電圧基準は、デジタル／アナログコンバータ（D A C）であってもよく、プログラム可能な第1の基準電圧値を提供してもよい。さらなる実施形態によると、第1の電圧基準は、固定されてもよい。さらなる実施形態によると、第1の電圧基準は、変調波形信号であってもよい。さらなる実施形態によると、バッファ増幅器は、第1の電圧基準の出力とキャパシタの入力との間に結合されてもよい。さらなる実施形態によると、定電流源は、スイッチが第1の位置にあり得るとき、キャパシタの出力から分断され、スイッチが第2の位置にあり得るとき、キャパシタの出力に結合されてもよい。

20

## 【0014】

さらに別の実施形態によると、スイッチモード電力供給装置（S M P S）コントローラ内にスロープ補償を提供するための方法は、基準電圧を提供するステップと、基準電圧とS M P Sフィルタキャパシタからの電圧との間の差異であり得る誤差電圧を提供し得る出力を有する演算増幅器を用いて、基準電圧とS M P Sフィルタネットワークからの出力電圧を比較するステップと、演算増幅器の出力に結合されるスロープ補償キャパシタを提供するステップと、スロープ補償キャパシタと並列に結合されるスロープ補償スイッチを提供するステップと、スロープ補償キャパシタおよびスロープ補償スイッチに結合される定電流源を提供するステップと、スロープ補償キャパシタからのスロープ補償誤差電圧とS M P Sインダクタ内で測定された電圧表現を比較するステップと、周期ジェネレータの出力に結合される設定入力と、電圧コンパレータの出力に結合されるリセット入力と、スロープ補償スイッチの開閉を制御し得、制御信号を供給するための出力とを有する、リセット支配ラッチを提供するステップと、あるパルス周期において、周期ジェネレータからの複数のパルスをリセット支配ラッチの設定入力に提供するステップであって、パルスが、リセット支配ラッチの設定入力において受信され得る度に、その出力は、第1の論理レベルから第2の論理レベルになり得る、ステップと、リセット支配ラッチの出力が第2の論理レベルにあり得るとき、スロープ補償スイッチを開放するステップと、演算増幅器からのフィードバック誤差電圧をスロープ補償フィードバック誤差電圧に変調するための線形減少（負スロープ）ランプ電圧を発生させるステップと、スロープ補償誤差電圧が、S M P Sインダクタを通る電流を表す電圧未満であり得るとき、リセット支配ラッチの出力を第1の論理レベルに戻し、スロープ補償スイッチを閉鎖するステップとを含んでもよい。本願明細書は、例えれば、以下の項目も提供する。

30

## (項目1)

スイッチモード電力供給装置（S M P S）コントローラ内の電流モード制御と併用する

40

50

ためのスロープ補償モジュールであって、前記スロープ補償モジュールは、

入力と出力との間に結合されたスロープ補償キャパシタと、

前記スロープ補償キャパシタと並列に結合されたスロープ補償スイッチと、

前記スロープ補償キャパシタの出力側および前記スロープ補償スイッチに結合された定電流源と

を備え、

前記スロープ補償スイッチが開放されると、前記スロープ補償キャパシタは、定電流源

を通して回路コモンに充電し、それによって、線形減少（負スロープ）ランプ電圧を発生

させる、スロープ補償モジュール。

（項目2）

10

前記スロープ補償スイッチが閉鎖されると、前記スロープ補償キャパシタは、放電する

、項目1に記載のスロープ補償モジュール。

（項目3）

前記定電流源は、前記スロープ補償スイッチが第1の位置にあるとき、前記スロープ補

償キャパシタの出力側から分断され、前記スロープ補償スイッチが第2の位置にあるとき

、前記スロープ補償キャパシタの出力側に結合される、項目1に記載のスロープ補償モジ

ュール。

（項目4）

前記線形減少（負スロープ）ランプ電圧は、自動的に、フィードバックループ誤差電圧

を調節するように適合されている、項目1に記載のスロープ補償モジュール。

20

（項目5）

前記定電流源は、複数の選択可能定電流値を有するプログラム可能定電流源を備える、

項目1に記載のスロープ補償モジュール。

（項目6）

前記スロープ補償キャパシタは、所望の容量値に対してプログラム可能に選択可能な複

数のスロープ補償キャパシタを備える、項目1に記載のスロープ補償モジュール。

（項目7）

スロープ補償モジュールを有するスイッチモード電力供給装置（SMPs）コントローラであって、前記SMPsコントローラは、

電圧基準と、

30

前記電圧基準に結合された第1の入力と、SMPsフィルタキャパシタからの出力電圧

に結合するために適合された第2の入力とを有する演算増幅器と、

前記演算増幅器の出力に結合された入力と、出力とを有するスロープ補償モジュールであって、前記スロープ補償モジュールは、

前記スロープ補償モジュールの入力と出力との間に結合されたスロープ補償キャパシタと、

前記スロープ補償キャパシタと並列に結合されたスロープ補償スイッチと、

前記スロープ補償キャパシタの出力側に結合された定電流源と、

を備える、スロープ補償モジュールと、

電圧コンパレータであって、前記電圧コンパレータは、

40

前記スロープ補償モジュールの出力に結合された第1の入力と、

電流信号を測定する電流／電圧回路に結合するために適合された第2の入力と、

を有する、電圧コンパレータと、

周期ジェネレータと、

リセット支配ラッチであって、前記リセット支配ラッチは、

前記周期ジェネレータの出力に結合された設定入力と、

前記電圧コンパレータの出力に結合されたリセット入力と、

前記スロープ補償スイッチに結合され、前記スロープ補償スイッチの開閉を制御する

出力と、

を備え、

50

前記リセット支配ラッチの出力はまた、制御信号を提供する、リセット支配ラッチとを備え、

前記周期ジェネレータは、あるパルス周期において、複数のパルスを前記リセット支配ラッチの設定入力に提供し、パルスが前記リセット支配ラッチの設定入力で受信される度に、前記リセット支配ラッチの出力は、第1の論理レベルから第2の論理レベルになり、

前記リセット支配ラッチの出力が前記第2の論理レベルにあるとき、前記スロープ補償スイッチは、開放し、前記スロープ補償キャパシタは、定電流源を通して回路コモンに充電し、それによって、前記演算増幅器からのフィードバック誤差電圧をスロープ補償フィードバック誤差電圧に変調させるための線形減少（負スロープ）ランプ電圧を発生させ、

前記電圧コンパレータの第1の入力に結合されている前記スロープ補償フィードバック誤差電圧が、前記電圧コンパレータの第2の入力におけるSMPStを通過する電流を表す電圧未満であるとき、前記リセット支配ラッチの出力は、前記第1の論理レベルに戻り、前記スロープ補償スイッチは、閉鎖し、それによって、前記スロープ補償キャパシタを放電させ、前記電圧コンパレータの第1の入力を前記演算増幅器からのフィードバック誤差電圧に戻す、SMPStコントローラ。

（項目8）

前記定電流源は、複数の選択可能定電流値を有するプログラム可能定電流源である、項目7に記載のSMPStコントローラ。

（項目9）

前記演算増幅器の出力と前記スロープ補償キャパシタおよびスイッチとの間に結合されたバッファ増幅器をさらに備える、項目7に記載のSMPStコントローラ。

（項目10）

前記演算増幅器の出力と第2の入力との間に結合されたループ補償ネットワークをさらに備える、項目7に記載のSMPStコントローラ。

（項目11）

前記SMPStを通過する電流を表す電圧は、電流/電圧センサを用いて発生される、項目7に記載のSMPStコントローラ。

（項目12）

前記電流/電圧センサは、前記SMPStを通過する電流経路内の電流変圧器と、前記電流変圧器に結合された整流器ダイオードと、前記レジスタに結合された負荷レジスタとを備える、項目11に記載のSMPStコントローラ。

（項目13）

前記電流/電圧センサは、前記SMPStを通過する電流経路内のレジスタと、前記レジスタに結合されたダイオードとを備える、項目11に記載のSMPStコントローラ。

（項目14）

前記周期ジェネレータは、複数のパルス周期時間のうちの1つを選択するためにプログラム可能である、項目7に記載のSMPStコントローラ。

（項目15）

前記スロープ補償スイッチは、金属酸化物半導体電界効果トランジスタ（MOSFET）である、項目7に記載のSMPStコントローラ。

（項目16）

前記リセット支配ラッチの出力と前記スロープ補償スイッチとの間に結合されたスロープ補償スイッチコントローラをさらに備え、前記スロープ補償スイッチコントローラは、前記スロープ補償スイッチのためのプログラム可能開放遅延を提供する、項目7に記載のSMPStコントローラ。

（項目17）

前記スロープ補償スイッチコントローラが、前記スロープ補償スイッチのためのプログラム可能最小閉鎖時間を提供することをさらに含む、項目16に記載のSMPStコントローラ。

（項目18）

10

20

30

40

50

前記 S M P S フィルタキャパシタからの出力電圧は、抵抗分圧器を通して提供される、項目 7 に記載の S M P S コントローラ。

(項目 19)

前記定電流源は、前記 S M P S コントローラの試験の間、較正のために適合される、項目 7 に記載の S M P S コントローラ。

(項目 20)

前記スロープ補償キャパシタは、所望の容量値に対してプログラム可能に選択可能な複数のスロープ補償キャパシタである、項目 7 に記載の S M P S コントローラ。

(項目 21)

前記スロープ補償キャパシタは、前記 S M P S コントローラの試験の間、所望の容量値に対してプログラム可能に選択可能な複数のスロープ補償キャパシタである、項目 7 に記載の S M P S コントローラ。

10

(項目 22)

プログラム可能な前記定電流源とプログラム可能な前記周期ジェネレータとに結合されたデジタルプロセッサをさらに備え、前記デジタルプロセッサは、それぞれ、前記定電流源および前記周期ジェネレータに定電流値およびパルス周期時間を探求する、項目 7 に記載の S M P S コントローラ。

(項目 23)

前記 S M P S コントローラは、マイクロコントローラを備える、項目 7 に記載の S M P S コントローラ。

20

(項目 24)

前記定電流源は、前記スロープ補償スイッチを用いて、前記スロープ補償キャパシタの出力側に結合されている、項目 7 に記載の S M P S コントローラ。

(項目 25)

前記定電流源は、前記スロープ補償スイッチが第 1 の位置にあるとき、前記スロープ補償キャパシタの出力側から分断され、前記スロープ補償スイッチが第 2 の位置にあるとき、前記スロープ補償キャパシタの出力側に結合される、項目 7 に記載の S M P S コントローラ。

(項目 26)

アナログパルス幅変調 ( P W M ) ジェネレータであって、前記アナログ P W M ジェネレータは、

30

第 1 の電圧基準に結合された入力を有するキャパシタと、

前記キャパシタの入力および出力と並列に結合されたスイッチと、

前記キャパシタの出力に結合された定電流源と、

前記キャパシタの出力に結合された第 1 の入力と、第 2 の電圧基準に結合された第 2 の入力と、前記スイッチの開閉を制御する出力とを有する第 1 の電圧コンパレータと、

前記キャパシタの出力に結合された第 1 の入力と、スイッチモード電力供給装置 ( S M P S ) からの電圧に結合するために適合された第 2 の入力と、スイッチモード電力供給装置の電源スイッチを制御するためのパルス幅変調 ( P W M ) 制御信号を提供する出力とを有する第 2 の電圧コンパレータと

40

を備え、

前記キャパシタの出力における電圧が、前記第 1 の電圧基準からの電圧未満であるとき、前記スイッチは、開放し、それによって、前記キャパシタおよび前記定電流源は、線形負スロープ電圧波形を用いて、前記第 1 の電圧基準からの電圧を変調させ、

前記第 1 の電圧基準と前記第 2 の電圧基準との間の電圧差は、前記 P W M 制御信号の周期を判定し、前記 S M P S からの電圧と前記キャパシタの第 2 のノードにおける電圧との間の電圧差は、前記 P W M 制御信号のデューティサイクルを判定する、アナログ P W M ジェネレータ。

(項目 27)

前記定電流源は、複数の選択可能定電流値を有するプログラム可能定電流源である、項

50

目 2 6 に記載のアナログ PWM ジェネレータ。

( 項目 2 8 )

前記キャパシタは、所望の容量値に対してプログラム可能に選択可能な複数のキャパシタである、項目 2 6 に記載のアナログ PWM ジェネレータ。

( 項目 2 9 )

前記第 1 の電圧基準は、デジタル / アナログコンバータ ( D A C ) であり、プログラム可能な第 1 の基準電圧値を提供する、項目 2 6 に記載のアナログ PWM ジェネレータ。

( 項目 3 0 )

前記第 1 の電圧基準は、固定されている、項目 2 6 に記載のアナログ PWM ジェネレータ。

10

( 項目 3 1 )

前記第 1 の電圧基準は、変調波形信号である、項目 2 6 に記載のアナログ PWM ジェネレータ。

( 項目 3 2 )

前記第 1 の電圧基準の出力と前記キャパシタの入力との間に結合されたバッファ増幅器をさらに備える、項目 2 6 に記載のアナログ PWM ジェネレータ。

( 項目 3 3 )

前記定電流源は、前記スイッチが第 1 の位置にあるとき、前記キャパシタの出力から分断され、前記スイッチが第 2 の位置にあるとき、前記キャパシタの出力に結合される、項目 2 6 に記載のアナログ PWM ジェネレータ。

20

( 項目 3 4 )

スイッチモード電力供給装置 ( S M P S ) コントローラ内にスロープ補償を提供するための方法であって、前記方法は、

基準電圧を提供するステップと、

前記基準電圧と S M P S フィルタキャパシタからの電圧との間の差異である誤差電圧を提供する出力を有する演算増幅器を用いて、前記基準電圧と S M P S フィルタネットワークからの出力電圧を比較するステップと、

前記演算増幅器の出力に結合されたスロープ補償キャパシタを提供するステップと、

前記スロープ補償キャパシタと並列に結合されたスロープ補償スイッチを提供するステップと、

30

前記スロープ補償キャパシタおよび前記スロープ補償スイッチに結合された定電流源を提供するステップと、

前記スロープ補償キャパシタからのスロープ補償誤差電圧と S M P S インダクタ内で測定された電流の電圧表現を比較するステップと、

周期ジェネレータの出力に結合された設定入力と、前記電圧コンパレータの出力に結合されたリセット入力と、前記スロープ補償スイッチの開閉を制御し、制御信号を供給するための出力を有するリセット支配ラッチを提供するステップと、

あるパルス周期において、周期ジェネレータから複数のパルスを前記リセット支配ラッチの設定入力に提供するステップであって、パルスが前記リセット支配ラッチの設定入力において受信される度に、前記リセット支配ラッチの出力は、第 1 の論理レベルから第 2 の論理レベルになる、ステップと、

40

前記リセット支配ラッチの出力が前記第 2 の論理レベルにあるとき、前記スロープ補償スイッチを開鎖するステップと、

前記演算増幅器からのフィードバック誤差電圧をスロープ補償フィードバック誤差電圧に変調するための線形減少 ( 負スロープ ) ランプ電圧を発生させるステップと、

前記スロープ補償誤差電圧が、前記 S M P S インダクタを通る電流を表す電圧未満であるとき、前記リセット支配ラッチの出力を前記第 1 の論理レベルに戻し、前記スロープ補償スイッチを閉鎖するステップと

を含む、方法。

**【 0 0 1 5 】**

50

本開示のより完全な理解は、付隨の図面と関連して検討される、以下の説明を参照することによって得られ得る。

【図面の簡単な説明】

【0016】

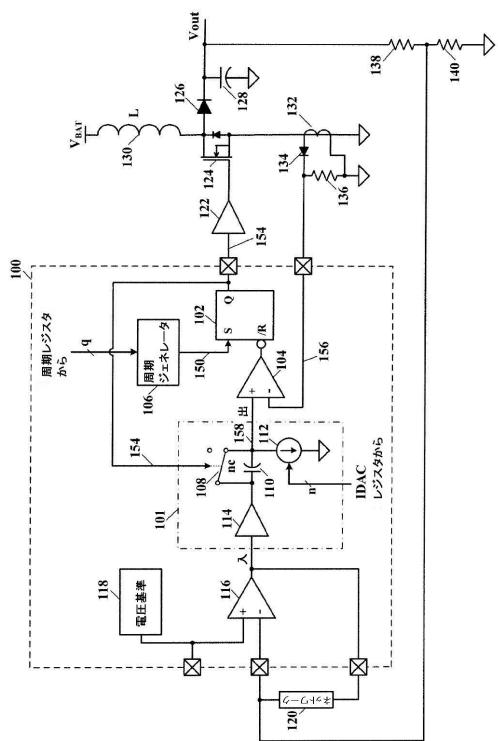

【図1】図1は、本開示の具体的例示的実施形態による、スロープ補償を伴う、ブーストスイッチモード電力コンバータの概略ブロック図を図示する。

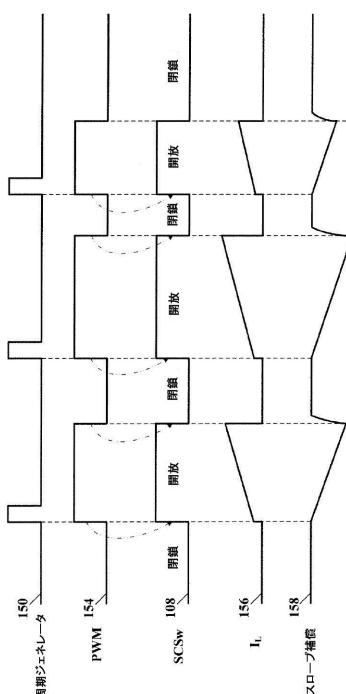

【図2】図2は、図1に示される具体的例示的実施形態による、スロープ補償を伴う、ブーストスイッチモードコンバータの概略波形タイミング図を図示する。

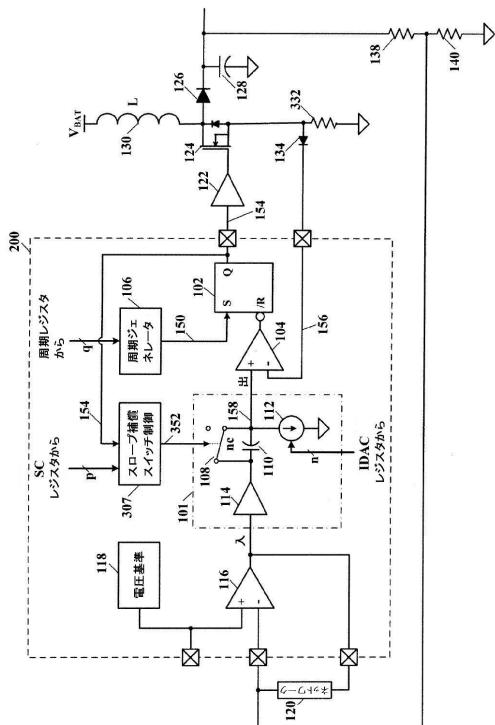

【図3】図3は、本開示の別の具体的例示的実施形態による、スロープ補償を伴う、ブーストスイッチモード電力コンバータの概略ブロック図を図示する。 10

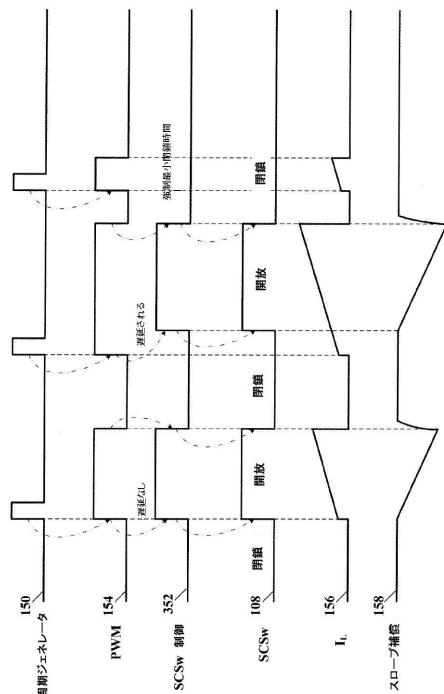

【図4】図4は、図3に示される具体的例示的実施形態による、スロープ補償を伴う、ブーストスイッチモードコンバータの概略波形タイミング図を図示する。

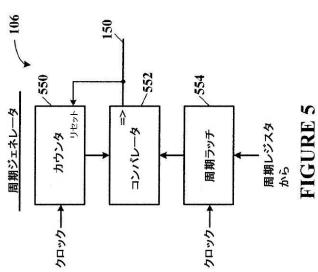

【図5】図5は、本開示の教示による、周期ジェネレータの概略ブロック図を図示する。

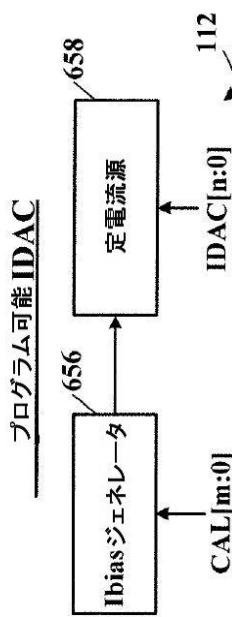

【図6】図6は、本開示の教示による、プログラム可能電流デジタル／アナログコンバータの概略ブロック図を図示する。

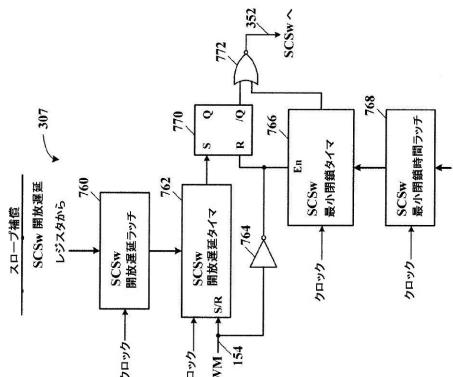

【図7】図7は、本開示の具体的例示的実施形態による、スロープ補償コントローラの概略ブロック図を図示する。

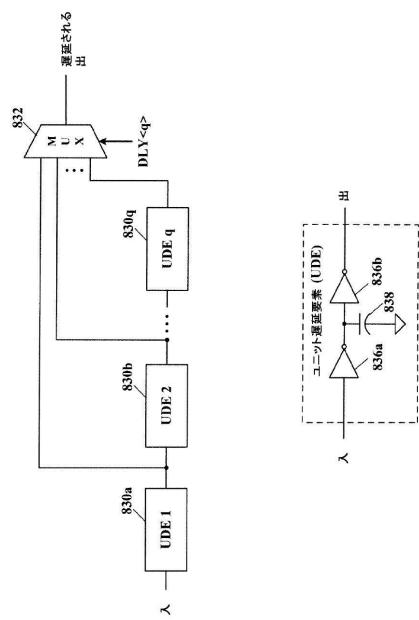

【図8】図8は、本開示の教示による、アナログ時間遅延回路のより詳細な概略ブロック図を図示する。

【図9】図9は、本開示の教示による、デジタル時間遅延回路のより詳細な概略ブロック図を図示する。 20

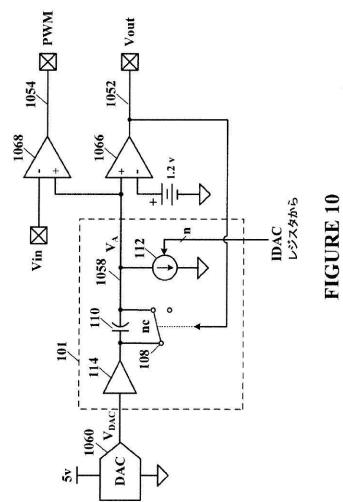

【図10】図10は、本開示のさらに具体的例示的実施形態による、スロープ補償モジュールを使用する、アナログ鋸歯およびパルス幅変調ジェネレータの概略ブロック図を図示する。

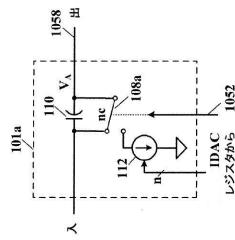

【図10A】図10Aは、代替として、本開示の実施形態の全てにおいて使用され得る、スロープ補償モジュールの概略図を図示する。

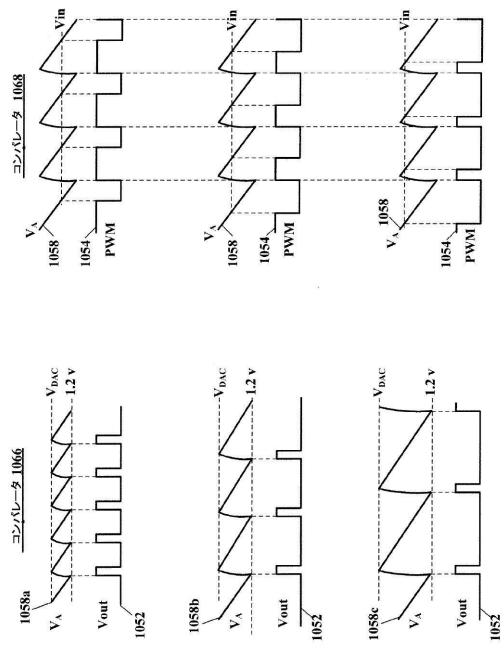

【図11】図11は、図10に示される具体的例示的実施形態による、鋸歯およびパルス幅変調ジェネレータの概略波形タイミング図を図示する。

【図12】図12は、本開示の教示による、スロープ補償を伴うパルス幅変調ジェネレータを有する、混合信号集積回路デバイスの概略ブロック図を図示する。 30

【図13】図13は、典型的スイッチモード電力供給装置(SMPS)用途において使用される、電源コンポーネントの概略図を図示する。

【発明を実施するための形態】

【0017】

本開示は、種々の修正および代替形態を被り得るが、その具体的例示的実施形態が、図面に図示され、本明細書に詳細に説明される。しかしながら、具体的例示的実施形態の本明細書の説明は、本開示を本明細書に開示される特定の形態に限定することを意図するものではなく、対照的に、本開示は、添付の請求項によって定義される、あらゆる修正および均等物を網羅するものとすることを理解されたい。

【0018】

(詳細な説明)

種々の実施形態によると、スロープ補償は、特に、スイッチモード電力供給装置(SMPS)および他の電源制御用途において使用するためのマイクロコントローラの能力を拡張させる。例えば、多くのスイッチモード電力供給装置(SMPS)用途の機能性は、スロープ補償の能力を有することによって、改良され得る。例えば、SMPS用途が、そうでなければ、SMPSシステムの不安定性につながるであろう、50%を上回るデューティサイクルを有するときである。種々の実施形態によると、そのようなスロープ補償モジュールは、他のモジュール、例えば、限定ではないが、コンバレータならびに他の内部および外部アナログおよび／またはデジタルデバイスとともに、マイクロコントローラ集積回路内にプログラム可能に組み合わせられてもよい。 50

## 【0019】

マイクロコントローラ周辺機器としてのスロープ補償実装は、本明細書に開示される種々の実施形態によると、コンフィギュアビリティを可能にし、マイクロコントローラメモリマップ内のレジスタに書き込むことによって、スロープ値を設定し、電力供給装置用途が、マイクロコントローラを使用することによって、オンザフライで、動的に適合可能または構成可能となることを可能にする。スロープ補償機能全体は、外部コンポーネントの必要なく、自給式であってもよい。本向上された機能性は、マイクロコントローラ制御S M P S、例えば、限定ではないが、ブーストまたはバックコンバータタイプS M P Sに適用されてもよい。

## 【0020】

種々の実施形態によると、スロープ補償モジュールは、コンパレータデバイスと組み合わせて、アナログ鋸歯波形周波数ジェネレータおよびアナログパルス幅変調(P W M)ジェネレータとして機能してもよい。P W Mジェネレータ用途では、スロープ補償モジュールは、両方とも、マイクロコントローラおよび/またはマイクロコントローラの他の周辺機器と一体型である、電圧基準およびデジタル/アナログコンバータ(D A C)と併用されてもよい。マイクロコントローラによる高速かつ柔軟なスロープ値選択は、非常に多様な種々の波形振幅および周波数を提供し得、故に、スロープ補償モジュールは、構成可能アナログP W Mジェネレータとして使用されてもよい。

## 【0021】

スロープ補償モジュールは、例えば、製造時の製品試験の間に呼び出され得る、較正能力を含んでもよい。シリコンプロセスは、スロープ補償モジュール回路のために使用され得る電流源およびキャパシタに大きなばらつきをもたらし得るが、較正は、加工ばらつきの補償調節を可能にし、したがって、電源システム設計を行なうときに依拠され得る正確なスロープパラメータを有する、マイクロコントローラベースの製品をもたらす。

## 【0022】

ここで図面を参照すると、具体的例示的実施形態の詳細が、図式的に図示される。図面中の同一要素は、同一番号によって表され、類似要素は、異なる小文字の添え字を伴う同一番号によって表されるであろう。

## 【0023】

図1を参照すると、描寫されるのは、本開示の具体的例示的実施形態による、スロープ補償を伴う、ブーストスイッチモード電力コンバータの概略ブロック図である。スイッチモード電力コンバータは、電力インダクタ130と、電力切替トランジスタ124と、ドライバトランジスタ122と、電力整流器126と、フィルタキャパシタ128と、電流センサ132、整流器134、および負荷レジスタ136を備える電流/電圧回路と、分圧器レジスタ138および140と、電圧誤差ループ補償ネットワーク120と、混合信号集積回路100とを備えてもよい。インダクタ130を通る電流を測定する電流/電圧回路はまた、電力切替トランジスタ124のソースリード内のレジスタ332(図3)、インダクタ130にわたるレジスタ-キャパシタネットワーク等を備えてもよい。

## 【0024】

混合信号集積回路100、例えば、マイクロコントローラは、リセット支配S R - ラッチ102と、電圧コンパレータ104と、周期ジェネレータ106と、演算増幅器116と、電圧基準118と、スロープ補償モジュール101とを備えてもよい。スロープ補償モジュール101は、スロープ補償スイッチ108と、スロープ補償キャパシタ110と、定電流デジタル/アナログコンバータ(I D A C)112と、随意に、バッファ増幅器114とを備えてもよい。I D A C112は、電流値のプログラム可能範囲を有してもよい。スロープ補償キャパシタ110は、容量値のプログラム可能範囲を有してもよい。スロープ補償スイッチ108は、ある電圧の範囲にわたって動作するために適合される半導体デバイス、例えば、金属酸化物半導体電界効果トランジスタ(M O S F E T)であってもよい。周期ジェネレータ106は、それが発生し得る周波数(周期)のプログラム可能範囲を有してもよい。混合信号集積回路100はさらに、それぞれ、周期ジェネレータ1

10

20

30

40

50

0 6 および I D A C 1 1 2 に、周期および電流値を提供し得る、メモリ 1 2 6 2 ( 図 1 2 ) を伴う、デジタルプロセッサを備えてもよい。

【 0 0 2 5 】

演算増幅器 1 1 6 、例えば、演算増幅器は、電圧基準 1 1 8 からの基準電圧と、分圧器レジスタ 1 3 8 および 1 4 0 によって分割される出力電圧  $V_{out}$  との間の差異である、誤差電圧をその出力に提供する。本誤差電圧は、演算増幅器 1 1 6 が、定電流源 I D A C 1 1 2 を直接駆動させる十分な駆動能力を有していない場合、バッファ増幅器 1 1 4 によってバッファされてもよい。代替スロープ補償モジュール 1 0 1 a が、代わりに使用されてもよい ( 図 1 0 A 参照 ) 。スロープ補償スイッチ 1 0 8 が閉鎖されると ( 通常、閉鎖されている ) 、スロープ補償キャパシタ 1 1 0 は、効果的に短絡および放電され、キャパシタ 1 1 0 の容量プレートの両側は、誤差電圧にあり、例えば、キャパシタ 1 1 0 は、演算増幅器の出力 1 1 6 と電圧コンパレータ 1 0 4 の正入力との間の回路動作に影響を及ぼさない。

【 0 0 2 6 】

電圧コンパレータ 1 0 4 は、スロープ補償モジュール 1 0 1 から出力を受信し、それを電流 / 電圧感知回路 ( 電流センサ 1 3 2 、整流器 1 3 4 、および負荷レジスタ 1 3 6 ) からのインダクタ 1 3 0 電流を表す電圧と比較する。電圧コンパレータ 1 0 4 の正入力における電圧が、インダクタ 1 3 0 電流を表す負入力における電圧以上であるとき、電圧コンパレータ 1 0 4 の出力は、論理高にある。正入力における電圧が、負入力における電圧未満であるとき、電圧コンパレータ 1 0 4 の出力は、論理低である。電圧コンパレータ 1 0 4 の出力は、リセット支配 S R - ラッチ 1 0 2 のリセット入力に結合され、周期ジェネレータ 1 0 6 の出力は、リセット支配 S R - ラッチ 1 0 2 の設定入力に結合される。リセット支配 S R - ラッチ 1 0 2 の設定入力が、論理高にあるとき、その Q 出力は、論理高となるであろう。リセット支配 S R - ラッチ 1 0 2 のリセット入力が、論理低にあるとき、その Q 出力は、論理低となるであろう。

【 0 0 2 7 】

図 2 を参照すると、描寫されるのは、図 1 に示される具体的な実施形態による、スロープ補償を伴う、ブーストスイッチモードコンバータの概略波形タイミング図である。周期ジェネレータの出力において、論理低から論理高への遷移が存在するとき ( 波形信号 1 5 0 として図 2 に示される ) 、リセット支配 S R - ラッチ 1 0 2 の Q - 出力は、論理高となり、 P W M 信号 1 5 4 として表されるパルス幅変調 ( P W M ) 周期を開始するであろう。電圧コンパレータ 1 0 4 の出力が、論理低となると、リセット支配 S R - ラッチ 1 0 2 の Q - 出力は、論理低に戻り、それによって、 ( 論理高 ) 持続時間、例えば、パルス幅または「デューティサイクル」に関する P W M 信号 1 5 4 を判定する。 P W M 信号 1 5 4 は、電力切替トランジスタ 1 2 4 のオンおよびオフを制御し得る。

【 0 0 2 8 】

P W M デューティサイクルが、例えば、 5 0 % を上回ると、インダクタ 1 3 0 内の瞬時電流は、所望のインダクタ 1 3 0 平均電流  $I_L$  と比較して、不均衡に大きくなり得る。これは、 S M P S 制御ループにおける不安定性および望ましくない分周波振動を生成し得る。ループ不安定性および分周波振動は、電圧フィードバック誤差電圧 1 5 8 を負スロープ波形を用いて変調することによって、ピーク電流モード制御スイッチモード電力供給装置設計内で効果的に防止されている。本負スロープ波形は、外部コンポーネントを要求する回路とともに、従来技術の S M P S 設計に実装されている。本アナログ外部コンポーネント設計は、 S M P S システムの狭範囲の動作条件に対してのみ効果的であり、用途毎に具体的に実装されなければならない。

【 0 0 2 9 】

本開示の教示によると、スイッチ ( スイッチ 1 0 8 ) スロープ補償キャパシタ 1 1 0 は、定電流源 I D A C 1 1 2 と組み合わせて、 S M P S の適切なスロープ補償のための線形減少 ( 負スロープ ) ランプ電圧を用いて、電圧フィードバック誤差電圧 1 5 8 を変調させるために効果的に使用され得る。スロープ補償スイッチ 1 0 8 が開放すると、スロープ補

償キャパシタ 110 は、最初に、放電され、キャパシタ 110 の両プレート（側）を同一の電圧電位、例えば、演算増幅器の出力 116 からの誤差電圧にさせる。しかし、ここで、定電流源 I DAC 112 に接続されるキャパシタ 110 のプレートは、I DAC 112 を通してコモン（例えば、接地または Vss）に充電し始め、それによって、線形減少（負スロープ）ランプ電圧として、電圧コンバレータ 104 の正入力における電圧を降下させるであろう。スロープ補償キャパシタ 110 の容量値および I DAC 112 のための定電流値を適切に選択することによって、SMPSS のための広範な動作範囲のスロープ補償が、外部コンポーネントを要求せずに、単純統合解決策において提供され得る。

### 【0030】

電圧制御ループは、大容量値フィルタキャパシタ 128 によって生じる長時間定数のため、Vout に非常にゆっくりな移動平均電圧値変化を「被る」。しかしながら、インダクタ 130 電流 156 (IL) は、各 PWM パルス周期内で急変する（パワートランジスタ 124 がオンであるとき）。PWM 信号 154 のデューティサイクルが、50% を上回ると、急変するインダクタ電流 156 は、SMPSS の電流ループ制御不安定性を生じさせ得る。本不安定性問題の補正は、PWM パルスが、電流ループ不安定性が生じ得る前に、終了される（パワートランジスタ 124 オフ）ように、誤差電圧 158 を負スロープ変調させる単純なスロープ補償を使用して行なわれる。スロープ補償は、信号波形 158 として図 2 に示される。

### 【0031】

スロープ補償スイッチ 108 は、PWM 信号 154 を用いて制御されてもよく、リセット支配 SR - ラッチ 102 の Q - 出力が、論理高にあるとき、スロープ補償スイッチ 108 は、開放し、リセット支配 SR - ラッチ 102 の Q - 出力が、論理低にあるとき、スロープ補償スイッチ 108 は、閉鎖され、それによって、スロープ補償キャパシタ 110 を放電し、それを誤差電圧フィードバックループから効果的に除去する。具体的定電流値をキャパシタ 110 の容量値と組み合わせて選択することによって、最適線形減少（負スロープ）ランプ電圧（波形 158）が、提供され得る。線形減少（負スロープ）ランプ電圧波形 158 (Vc) のスロープは、I DAC 112 からの定電流値 (I<sub>DAC</sub>) として、キャパシタ 110 の容量値 (C) によって判定されてもよい（キャパシタ電圧の変化は、キャパシタを充電するために印加される電流の量および電流が印加される時間の量に正比例する）。キャパシタ 110 の容量は、固定値であってもよく、またはプログラム可能であり（図示せず）、例えば、複数のスイッチキャパシタであってもよい。I DAC 112 の定電流値は、プログラム可能であってもよく、所望の定電流値が、例えば、限定ではないが、マイクロコントローラの、例えば、デジタルプロセッサ 1262（図 12）から、I DAC レジスタ（図示せず）によって提供されてもよい。

### 【0032】

図 3 を参照すると、描寫されるのは、本開示の別の具体的例示的実施形態による、スロープ補償を伴う、ブーストスイッチモード電力コンバータの概略ブロック図である。図 3 に示されるスイッチモードコンバータ 200 は、図 1 に示され、本明細書に前述されるスイッチモードコンバータ 100 と実質的に同一の方法で機能するが、以下により完全に説明されるように、スロープ補償スイッチのプログラム可能スロープ補償開始遅延および強制最小時間閉鎖の追加特徴を伴う。PWM 信号 154 は、スロープ補償スイッチコントローラ 307 の入力に結合される。スロープ補償スイッチコントローラ 307 の目的は、スロープ補償スイッチ 108 の閉鎖をプログラム可能に遅延させ、および / またはプログラム可能時間長、例えば、スロープ補償キャパシタ 110 の完全電圧放電のために十分な時間の間、スロープ補償スイッチ 108 を閉鎖されたままである、すなわち、スロープ補償キャパシタ 110 の両末端が実質的に同一の電圧電位にある状態に強制することを可能にすることである。

### 【0033】

図 4 を参照すると、描寫されるのは、図 3 に示される具体的例示的実施形態による、スロープ補償を伴う、ブーストスイッチモードコンバータの概略波形タイミング図である。

10

20

30

40

50

左から右に見て、周期ジェネレータ 106 からの第 1 のパルス 150 では、遅延は、スイッチ制御信号 352 に導入されず、スロープ補償スイッチ 108 は、PWM 信号 154 の論理レベルに従って、開閉する（図 2 に示されるものと正に同じように）。第 2 のパルス 150 では、スイッチ制御信号 352 は、遅延され、スロープ補償スイッチ 108 は、PWM 信号 154 パルス幅に後に開放する。第 3 のパルス 150 では、スイッチ制御信号 352 は、（短パルス幅持続時間の）PWM パルスが生じても、スロープ補償スイッチ 108 を開放しない。これは、スロープ補償キャパシタ 110 を適切に放電させるための時間が不十分であったためであり得る。図 4 に示されるように、第 2 の PWM パルス 154 は、高パルス持続時間にあり、次の（第 3 の）PWM パルスは、第 2 の PWM パルス終了直後に生じ、したがって、スロープ補償スイッチ 108 は、スロープ補償キャパシタ 110 を適切に放電させるために十分な時間の間、閉鎖されたままでなく、第 3 の PWM パルス幅は、非常に短い持続時間であった。IDAC112 電流値、スロープ補償スイッチ 108 開放遅延時間、およびスロープ補償スイッチ 108 最小閉鎖時間は全て、図 3 に示されるスイッチモードコンバータ 200 の動作の間、プログラム可能であり得ることも検討され、本開示の範囲内である。

10

#### 【0034】

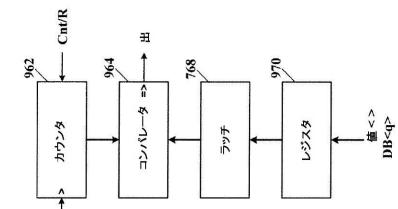

図 5 を参照すると、描寫されるのは、本開示の教示による、周期ジェネレータの概略ブロック図である。周期ジェネレータ 106 は、カウンタ 550 と、コンパレータ 552 と、周期ラッチ 554 とを備えてもよい。PWM 信号 154 のための周期値は、クロックパルスに応じて、周期レジスタ（図示せず）から周期ラッチ 554 に同期的にロードされてもよい。カウンタ 550 は、ゼロから周期値までのクロックレートにおいて、継続的にカウントする。コンパレータ 552 が、周期パルス 150 を出力する度に、カウンタ 550 のカウント値は、周期ラッチ 554 内の周期値と等しくなり、また、カウンタ 550 をゼロにリセットし、それによって、カウンタ 550 は、再び、カウントアップを開始する。周期レジスタ内の周期値を変更することによって、PWM 周期（周波数）も変更され得る。

20

#### 【0035】

図 6 を参照すると、描寫されるのは、本開示の教示による、プログラム可能電流デジタル／アナログコンバータの概略ブロック図である。プログラム可能 IDAC112 は、プログラム可能定電流源 658 と、プログラム可能定電流源 658 に結合されるプログラム可能バイアス電流ジェネレータ 656 とを備えてもよい。プログラム可能定電流源 658 およびプログラム可能バイアス電流ジェネレータ 656 両方のプログラム可能性は、プログラム可能 IDAC112 の較正と、例えば、製品試験の間の SMPS および／またはスロープ較正の動作の間、デジタルプロセッサ 1262 によるオンザフライでのその電流源値の変更とを可能にする。

30

#### 【0036】

図 7 を参照すると、描寫されるのは、本開示の具体的例示的実施形態による、スロープ補償コントローラの概略ブロック図である。スロープ補償スイッチコントローラ 307 は、スロープ補償開放遅延ラッチ 760 と、スロープ補償開放遅延タイマ 762 と、リセット支配ラッチ 770 と、インバータ 764 と、NOR ゲート 772 と、スロープ補償最小閉鎖タイマ 766 と、スロープ補償最小閉鎖ラッチ 768 とを備えてもよく、全て、図 7 に示されるように、ともに結合される。スロープ補償スイッチ 108 の開放を遅延させることができると、非ゼロ開放時間遅延値が、開放遅延ラッチレジスタ（図示せず）から開放遅延ラッチ 760 にロードされてもよい。開放遅延タイマ 762 は、次いで、非ゼロ開放時間遅延値に従って、リセット支配ラッチ 770 の設定入力への論理高の出力を遅延させるであろう。開放遅延タイマ 762 が、タイムアウトすると、その出力は、論理高となる。リセット支配ラッチ 770 の Q 出力は、論理低となる。開放時間遅延値が、ゼロになると、スイッチ 108 の開放遅延は存在しないであろう。PWM 信号 154 が、論理低に戻ると、開放遅延タイマ 762 は、ゼロに戻るようにリセットし、リセット支配ラッチ 770 のリセット入力は、その Q 出力を論理高に戻るように強制するであろう。

40

50

## 【0037】

PWM信号154が、論理低になると、最小閉鎖タイマ766は、スロープ補償スイッチ108の最小閉鎖時間のタイミングを開始する。最小閉鎖時間は、スロープ補償最小閉鎖時間ラッチ768内に記憶された最小閉鎖時間値から判定されてもよい。最小閉鎖時間値は、スロープ補償最小閉鎖時間レジスタ(図示せず)からスロープ補償最小閉鎖時間ラッチ768にロードされてもよい。スロープ補償スイッチ制御信号352は、最小閉鎖タイマ766がタイムアウトするまで、スイッチ108を開放しないように防止されてもよい。最小閉鎖時間値が、ゼロに設定される場合、スロープ補償スイッチ108のための強制最小閉鎖時間は存在しないであろう。開放遅延タイマ762および最小閉鎖タイマ766は、以下により完全に説明されるように、アナログおよび/またはデジタル回路であってもよい。例えば、開放遅延タイマ762は、アナログまたはデジタル遅延ラインであってもよく、最小閉鎖タイマ766は、単純アナログワンショット単安定またはデジタルカウンタであってもよい。電子回路設計の当業者および本開示の利益を有する者によって、多くの他の回路構成および組み合わせが、本明細書に説明される意図される機能を行なうために設計され得ることも検討され、本開示の範囲である。

## 【0038】

図8を参照すると、描写されるのは、本開示の教示による、アナログ時間遅延回路のより詳細な概略ブロック図である。本時間遅延回路は、複数のユニット遅延要素(UBE)830と、マルチブレクサ832とを備えてもよい。具体的時間遅延は、開放遅延ラッチ760内の非ゼロ開放時間遅延値からの入力選択アドレスから制御され得る、マルチブレクサ832を伴う、適切な数の直列に結合されたUBE830の選択によって得られ得る。マルチブレクサ832からの出力が、論理高になると、開放遅延タイマ762出力は、論理高にある。最小閉鎖タイマ766は、例えば、限定ではないが、単安定ワンショットであってもよい。

## 【0039】

図9を参照すると、描写されるのは、本開示の教示による、デジタル時間遅延回路のより詳細な概略ブロック図である。本時間遅延回路は、各クロックパルスをカウントし、そのカウント値をコンパレータ964に出力する、カウンタ962を備えてもよい。コンパレータ964は、カウント値と、時間値、例えば、最小閉鎖時間ラッチ768内に記憶され得る、最小閉鎖時間値を比較する。カウント値が、時間値以上であるとき、コンパレータ964からの出力Outは、論理高となる。レジスタ970は、最小閉鎖時間ラッチ768への後続同期転送のために、時間値を非同期的に記憶するために使用されてもよい。

## 【0040】

図10を参照すると、描写されるのは、本開示のさらに具体的例示的実施形態による、スロープ補償モジュールを使用する、アナログ鋸歯およびパルス幅変調ジェネレータの概略ブロック図である。本明細書に開示されるスロープ補償モジュール101は、それぞれ、第1および第2の電圧コンパレータ1066および1068と、アナログ(デジタル回路もクロック入力も要求されない)パルス幅変調(PWM)ジェネレータおよび/または鋸歯発振器を提供するためのデジタル/アナログコンバータ(DAC)1060と組み合わせて使用されてもよい。第1の電圧コンパレータ1066、第2の電圧コンパレータ1068、およびDAC1060は、図10に示されるように、スロープ補償モジュール101に結合され得る。定電流源112は、本明細書に前述でより完全に説明されるように、プログラム可能であってもよい。第1のコンパレータ1066の負入力に結合される電圧基準は、任意の値の電圧であってもよい。1.2ボルトが、例証目的のためだけに、本電圧基準として示される。バッファ增幅器114は、随意であり、ソース、例えば、DAC1060が、スロープ補償モジュール101内のキャパシタ110を駆動するために十分な出力能力を有していない場合のみ、要求される。図10Aは、代わりに使用され得る、代替スロープ補償モジュール101aを示す。

## 【0041】

スロープ補償モジュール101の出力電圧1058(V<sub>A</sub>)が、基準電圧、例えば、1

10

20

30

40

50

. 2 ボルトを上回ると、第 1 の電圧コンパレータ 1066 の出力は、論理高であり、スイッチ 108 は、開放され、それによって、定電流源 112 が、線形電圧ランプにおいてキャパシタ 110 を放電することを可能にするであろう（図 11 参照）。本電圧放電ランプは、容量値によって除算される定電流値に比例するスロープを有するであろう。出力電圧 1058 (V<sub>A</sub>) が、基準電圧未満となると、第 1 の電圧コンパレータ 1066 の出力は、論理低に切り替わり、スイッチ 108 は、閉鎖するであろう。いったんスイッチ 108 が閉鎖すると、出力電圧 1058 (V<sub>A</sub>) は、スロープ補償モジュール 101 の入力における電圧、例えば、DAC 1060 からの電圧出力にすぐに戻る。したがって、第 1 の電圧コンパレータ 1066 の出力は、非常に短時間の間のみ、論理高のままである（図 11 参照）。本オンおよびオフ切替は、DAC 1060 の電圧出力と第 1 の電圧コンパレータ 1066 の負入力における基準電圧との間の電圧差によって判定される周期を有し得る。電圧差が大きくなるほど、振動周期が長くなる（周波数が低くなる）（図 11 参照）。したがって、DAC 1060 からの電圧値は、パルス周期（周波数）を設定し、かつプログラム可能キャパシタ 110 の値を変更するために使用され得る。

#### 【0042】

第 2 の電圧コンパレータ 1068 は、前述のように発生される鋸歯電圧波形および電圧入力 V<sub>in</sub>、例えば、電力供給装置からの出力電圧（例えば、図 13 の V<sub>SEN</sub>）を比較する。いったんパルス周期（スロープ繰り返し率）が、前述のように設定されると、第 2 の電圧コンパレータ 1068 は、PWM 出力 1054 のための種々のパルス幅を発生させるために使用されてもよい。したがって、DAC 1060、スロープ補償モジュール 101、および第 1 のコンパレータ 1066 は、PWM 周期（周波数）を判定し得る。スロープ補償モジュール 101 および第 2 のコンパレータ 1068 は、入力電圧 V<sub>in</sub> の変化に伴って変動するであろう、PWM デューティサイクル（パルス幅）を判定し得る。

#### 【0043】

図 10A を参照すると、描写されるのは、代替として、本開示の実施形態の全てにおいて使用され得る、スロープ補償モジュールの概略図である。図 1、3、および 10 に示されるバッファ增幅器 114 は、スイッチ 108a がその通常閉鎖位置にあり、キャパシタ 110 を放電しているとき、定電流源 112 をスロープ補償キャパシタ 110 から切断することによって、完全に排除されてもよい。単極双投（S P D T）スイッチが、スイッチ 108a のために使用されてもよく、または一方は、通常閉鎖、他方は、通常開放の 2 つの単極单投（S P S T）スイッチが、使用されてもよい。スイッチ 108a は、固体状態スイッチ、例えば、金属酸化物半導体電界効果トランジスタ（M O S F E T）であってもよい。

#### 【0044】

図 11 に描写されるのは、図 10 に示される具体的例的実施形態による、鋸歯およびパルス幅変調ジェネレータの概略波形タイミング図である。第 1 のコンパレータ 1066 のための波形を参照すると、DAC 1060 出力電圧と基準電圧（例えば、1.2 ボルト）との間の電圧差が増加するにつれて、振動波形（鋸歯およびパルス）時間周期が、増加する（周波数が低下する）。第 2 のコンパレータ 1068 のための波形を参照すると、入力電圧 V<sub>in</sub> が、スロープ補償モジュール 101 からの出力電圧 V<sub>A</sub> に連動して増加するにつれて、PWM 信号のパルス幅またはデューティサイクル（第 2 のコンパレータ 1068 からの出力 1054）は、低下する。これは、PWM パルス幅が、S M P S 出力電圧の変化によって生じる誤差電圧の値に反比例するため、スイッチモード電力供給装置の制御のために有利である。

#### 【0045】

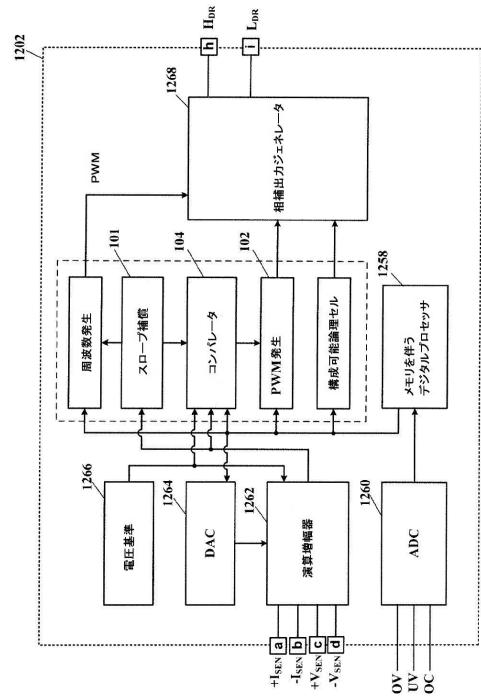

図 12 を参照すると、描写されるのは、本開示の教示による、スロープ補償を伴うパルス幅変調ジェネレータを有する、混合信号集積回路デバイスの概略ブロック図である。混合信号集積回路デバイス 1202 が、スイッチモード電力供給装置（S M P S）等を制御するために使用されてもよい。混合信号集積回路デバイス 1202 は、相補出力ジェネレータ 1268、スロープ補償（図 1 および 3 参照）を伴うパルス幅変調（P W M）ジェネ

レータ、メモリを伴うデジタルプロセッサ 1258、アナログ／デジタルコンバータ A/D C1260、演算増幅器 1262、デジタル／アナログコンバータ (D/A C) 1264、および電圧基準 1266 のうちの 1 つ以上を備えてよい。

【 0 0 4 6 】

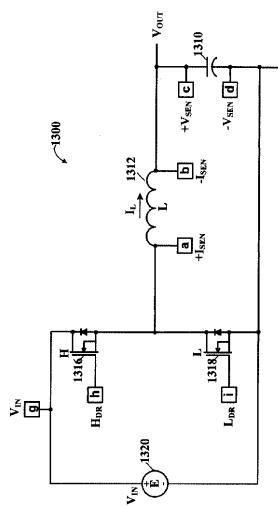

図13を参照すると、描寫されるのは、典型的スイッチモード電力供給装置(SMPs)用途において使用される電源コンポーネントの概略図である。SMPs1300の電源コンポーネントは、電圧源1320(Vin)からフィードされ、高トランジスタ1316と、低トランジスタ1318と、インダクタ1312と、フィルタキャパシタ1310とを備えてよく、全て、図12に示される混合信号集積回路デバイス1202に結合される。

10

〔 0 0 4 7 〕

本開示の実施形態が、本開示の例示的実施形態を参照して、描写、説明、および定義されたが、そのような参照は、本開示の限定を含意するものではなく、かつそのような限定が推測されるものでもない。開示される主題は、当業者および本開示の利益を有する者に想起されるであろうように、少なからず、形態および機能における修正、改変、および均等物が可能である。本開示の描写および説明される実施形態は、実施例にすぎず、本開示の範囲の包括ではない。

(  1 )

【 2 】

FIGURE 2

### 【 义 3 】

FIGURE 3

【 図 4 】

FIGURE 4

【 义 5 】

FIGURE 5

【図6】

FIGURE 6

【 义 7 】

FIGURE 7

【 図 8 】

FIGURE 8

【 9 】

FIGURE 9

【図10】

FIGURE 10

【図10A】

FIGURE 10A

【図11】

FIGURE 11

【 図 1 2 】

FIGURE 12

### 【図13】

FIGURE 13

---

フロントページの続き

- (72)発明者 ダーマワスキタ, ハートノ

アメリカ合衆国 アリゾナ 85249, チャンドラー, イー. リブラ プレイス 206

6

- (72)発明者 スティードマン, ショーン ステイシー

アメリカ合衆国 アリゾナ 85048, フェニックス, イースト ロックレッジ ロード

2622

- (72)発明者 グローザ, クリスチャン ニコラエ

ルーマニア国 パシュカニ, エスシー エー イーティー 4 エーピー. 9, エヌアール

7 ピーエル. ディー 8, ブカレスト エスイーシー. 6 エスティーアール.

- (72)発明者 マンシオイウ, マリーレナ

ルーマニア国 コラビア オルト, イーティー. 2 エーピー. 8, エスティーアール.

カライマン エヌアール. 14 ピーエル. 9

- (72)発明者 シャレー, ジョン ロバート

アメリカ合衆国 アリゾナ 85048, フェニックス, サウス 25ティーエイチ ストリ

ート 16618

- (72)発明者 ランドストラム, ジーク

アメリカ合衆国 アリゾナ 85225, チャンドラー, イースト サン タン ストリート

1732

審査官 小林 秀和

- (56)参考文献 特開2005-039925(JP, A)

特開2008-161001(JP, A)

特開2006-149065(JP, A)

特開平11-284497(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155

H03K 7/08