(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5535219号

(P5535219)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

(51) Int.CI.

F 1

|                     |                  |              |         |

|---------------------|------------------|--------------|---------|

| <b>G 11 C 29/42</b> | <b>(2006.01)</b> | G 11 C 29/00 | 6 3 1 D |

| <b>G 06 F 12/16</b> | <b>(2006.01)</b> | G 06 F 12/16 | 3 1 OH  |

| <b>G 11 C 16/06</b> | <b>(2006.01)</b> | G 11 C 17/00 | 6 3 9 C |

| <b>G 11 C 16/04</b> | <b>(2006.01)</b> | G 11 C 17/00 | 6 2 4   |

| <b>G 11 C 16/02</b> | <b>(2006.01)</b> | G 11 C 17/00 | 6 4 1   |

請求項の数 10 (全 55 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-530195 (P2011-530195)  |

| (86) (22) 出願日 | 平成21年9月30日 (2009.9.30)        |

| (65) 公表番号     | 特表2012-504842 (P2012-504842A) |

| (43) 公表日      | 平成24年2月23日 (2012.2.23)        |

| (86) 國際出願番号   | PCT/US2009/059081             |

| (87) 國際公開番号   | W02010/039869                 |

| (87) 國際公開日    | 平成22年4月8日 (2010.4.8)          |

| 審査請求日         | 平成24年9月27日 (2012.9.27)        |

| (31) 優先権主張番号  | 61/194,751                    |

| (32) 優先日      | 平成20年9月30日 (2008.9.30)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | PCT/US2009/049333             |

| (32) 優先日      | 平成21年6月30日 (2009.6.30)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                |

|-----------|--------------------------------------------------------------------------------|

| (73) 特許権者 | 508243639<br>エルエスアイ コーポレーション<br>アメリカ合衆国カリフォルニア州95131, サンノゼ, リッダー・パーク・ドライヴ 1320 |

| (74) 代理人  | 100094112<br>弁理士 岡部 譲                                                          |

| (74) 代理人  | 100104352<br>弁理士 朝日 伸光                                                         |

| (74) 代理人  | 100128657<br>弁理士 三山 勝巳                                                         |

| (74) 代理人  | 100160967<br>弁理士 ▲濱▼口 岳久                                                       |

最終頁に続く

(54) 【発明の名称】基準セルを使用する、メモリ・デバイスの軟データ生成の方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリ・デバイス内で少なくとも1つの軟データ値を生成する方法であって、1つまたは複数の基準セルに既知のデータを書き込むことと、前記基準セルのうちの1つまたは複数を読み取ることと、前記読み取られた1つまたは複数の基準セルに基づいて読み取統計を入手することと、前記入手された読み取統計に基づいて前記少なくとも1つの軟データ値を入手することとを含む方法。

## 【請求項 2】

前記軟データ値は、(i) 1つまたは複数の対数尤度比を生成するのに使用される軟読み取値、および(ii) 1つまたは複数の対数尤度比、の1つ以上を含む、請求項1に記載の方法。 10

## 【請求項 3】

前記読み取統計は、前記1つまたは複数の基準セルから読み取られた1つまたは複数のビットを前記既知のデータ内の1つまたは複数のビットと比較することによって判定される、請求項1に記載の方法。

## 【請求項 4】

前記読み取統計は、前記既知のデータ内の基準ビットの総数に対する誤りのあるビットの個数に基づく、請求項1に記載の方法。

## 【請求項 5】

20

前記読取統計は、メモリ・アレイの 1 つまたは複数の所望の位置について入手され、前記書き込むステップは、前記既知のデータを前記 1 つまたは複数の所望の位置に書き込むことを含む、請求項 1 に記載の方法。

【請求項 6】

前記所望の位置は、ページ位置、ワード線位置、ピット線位置、およびマルチレベル・セル内の所与のピットのうちの 1 つまたは複数を含む、請求項 5 に記載の方法。

【請求項 7】

1 つまたは複数の所望の位置に関する前記読取統計は、前記 1 つまたは複数の所望の位置に関するデータを復号するのに使用される、請求項 5 に記載の方法。

【請求項 8】

前記読取統計は、少なくとも 1 つのターゲット・セルに関連する 1 つまたは複数のアグレッサ・セル内の所与のパターン PATT について入手され、前記書き込むステップは、前記既知のデータを前記少なくとも 1 つのターゲット・セルに書き込むことを含み、前記方法は、前記 1 つまたは複数のアグレッサ・セル内の前記所与のパターン PATT を有する誤りのあるターゲット・ピットの個数を判定するステップと、誤りのあるターゲット・ピットの前記個数に基づいて前記所与のパターンに関する前記読取統計を入手するステップとをさらに含む、請求項 1 に記載の方法。

【請求項 9】

前記所与のパターン PATT に関する前記読取統計は、前記 1 つまたは複数の関連するアグレッサ・セルが前記パターン PATT を含むときにデータを復号するのに使用される、請求項 8 に記載の方法。

【請求項 10】

メモリ・デバイス内で少なくとも 1 つの軟データ値を生成するシステムであって、メモリと、

前記メモリに結合され、

1 つまたは複数の基準セルに既知のデータを書き込み、

前記基準セルのうちの 1 つまたは複数を読み取り、

前記読み取られた 1 つまたは複数の基準セルに基づいて読取統計を入手し、

前記入手された読取統計に基づいて前記少なくとも 1 つの軟データ値を入手するように動作可能な少なくとも 1 つのプロセッサと

を含むシステム。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本願は、それぞれ参照によって本明細書に組み込まれている、2008年9月30日に出願した米国仮出願第 61/194,751 号および 2009 年 6 月 30 日に出願した国際出願第 PCT/US09/49333 号、名称「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」の優先権を主張するものである。

【0002】

本願は、それぞれ本願と同時に出願され、参照によって本明細書に組み込まれている、国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Based on Performance Factor Adjustment」、国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices」、および国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Using Decoder」

10

20

30

40

50

Performance Feedback」に関連する。

#### 【0003】

本発明は、全般的にはフラッシュ・メモリ・デバイスに関し、より具体的には、そのようなフラッシュ・メモリ・デバイスでのセル間干渉、バック・パターン依存 (back pattern dependency)、雑音、および他のひずみを軽減する改善された軟デマッピング (soft demapping) および軟データ生成 (soft data generation) の技法に関する。

#### 【背景技術】

#### 【0004】

フラッシュ・メモリ・デバイスなどの複数のメモリ・デバイスは、データを格納するのにアナログ・メモリ・セルを使用する。各メモリ・セルは、電荷または電圧など、ストレージ・バリュー (storage value) とも称するアナログ値を格納する。ストレージ・バリューは、セルに格納された情報を表す。たとえば、フラッシュ・メモリ・デバイスでは、各アナログ・メモリ・セルは、通常はある電圧を格納する。各セルの可能なアナログ値の範囲は、しきい領域に分割され、各領域は、1つまたは複数のデータ・ビット値に対応する。データは、所望の1つまたは複数のビットに対応する公称アナログ値を書き込むことによってアナログ・メモリ・セルに書き込まれる。

10

#### 【0005】

たとえば、シングルレベル・セル (SLC) フラッシュ・メモリ・デバイスは、メモリ・セルあたり1ビット (すなわち、2つの可能なメモリ状態) を格納する。その一方で、マルチレベル・セル (MLC) フラッシュ・メモリ・デバイスは、メモリ・セルあたり複数のビットを格納する (すなわち、各セルが、4つ以上のプログラム可能な状態を有する)。MLC フラッシュ・メモリ・デバイスのより詳細な議論については、たとえば、参照によって本明細書に組み込まれている、2009年3月11日に出願した国際出願第PCT/US09/36810号、名称「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding And Per-Page Coding」を参照されたい。

20

#### 【0006】

30

たとえば、マルチレベルNAND フラッシュ・メモリ・デバイスでは、フローティング・ゲート・デバイスが、複数の間隔に分割される範囲内のプログラム可能しきい電圧と共に使用され、各間隔は、異なるマルチビット値に対応する。所与のマルチビット値をメモリ・セルにプログラムするためには、メモリ・セル内のフローティング・ゲート・デバイスのしきい電圧を、その値に対応するしきい電圧間隔にプログラムする。

#### 【0007】

メモリ・セルに格納されたアナログ値は、しばしば、ひずむ。ひずみは、通常、たとえばバック・パターン依存 (BPD)、雑音、およびセル間干渉 (ICI) に起因する。フラッシュ・メモリ・デバイスでのひずみのより詳細な議論については、たとえば、それぞれ参照によって本明細書に組み込まれている、J. D. Lee他、「Effects of Floating-Gate Interference on NAND Flash Memory Cell Operations」、IEEE Electron Device Letters、264~266頁(2002年5月)、またはKi-Tae Park他、「A Zeroing Cell-to-Cell Interference Page Architecture With Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE J. of Solid State Circuits、Vol. 43、No. 4、919~928頁(2008年4月)を参照されたい。

40

#### 【0008】

50

複数の技法が、ICCIおよび他の外乱の影響を軽減するために提案されまたは提唱されてきた。たとえば、Ki-Tae Park他は、ICCIを軽減する、偶数/奇数プログラミング(even/odd programming)、ボトム・アップ・プログラミング(bottom up programming)、およびマルチステージ・プログラミング(multi-stage programming)などの既存のプログラミング技法を説明している。2009年6月30日に出願された国際出願第PCT/US09/49333号、名称「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」は、フラッシュ・メモリでの軟デマッピングおよび外乱軽減の方法および装置を開示している。

10

## 【先行技術文献】

## 【特許文献】

## 【0009】

【特許文献1】米国仮出願第61/194,751号

【特許文献2】国際出願第PCT/US09/49333号

【特許文献3】国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Based on Performance Factor Adjustment」

【特許文献4】国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices」

20

【特許文献5】国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Using Decoder Performance Feedback」

【特許文献6】国際出願第PCT/US09/36810号

【特許文献7】米国特許第6,522,580号

【特許文献8】国際出願第PCT/US09/49326号

【特許文献9】国際出願第PCT/US09/49327号

【特許文献10】国際出願第PCT/US09/49328号

## 【非特許文献】

30

## 【0010】

【非特許文献1】J.D.Lee他、「Effects of Floating-Gate Interference on NAND Flash Memory Cell Operation」、IEEE Electron Device Letters、264~266頁(2002年5月)

【非特許文献2】Ki-Tae Park他、「A Zeroing Cell-to-Cell Interference Page Architecture With Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE J.of Solid State Circuits、Vol.43、No.4、919~928頁(2008年4月)

40

【非特許文献3】A.J.BlanksbyおよびC.J.Howland、「A 690-mW 1-Gb/s 1024-b, Rate-1/2 Low-Density Parity-Check Decoder」、IEEE J.Solid-State Circuits、Vol.37、404~412頁(2002年3月)

【非特許文献4】D.E.Hocevar、「LDPC Code Construction With Flexible Hardware Implementation」、IEEE Int'l Conf. on Comm. (ICC)、米国アラスカ州アンカレッジ、2708~2712頁(2003年5月)

【非特許文献5】R.N.S.Ratnayake、E.F.Haratsch、および

50

Gu-Yeon Wei、「A Bit-node centric architecture for low-density parity check decoders」、IEEE Global Telecommunications Conference (Globecom)、米国コロンビア特別区ワシントン、265～270頁(2007年11月)

【非特許文献6】E. Yeo他、「VLSI Architectures for Iterative Decoders in Magnetic Recording Channels」、IEEE Trans. On Magnetics、Vol. 37、No. 2、748～755頁(2001年3月)

【発明の概要】

10

【発明が解決しようとする課題】

【0011】

これらの既存の方法は、フラッシュ・メモリの復号性能を改善するのを助けたが、複数の制約をこうむり、この制約は、克服されたならば、フラッシュ・メモリの信頼性をさらに改善することができる。たとえば、現在のフラッシュ・メモリは、通常、復号のためにフラッシュ制御システムに硬データ(hard data)のみを供給する。しかし、軟データが、復号プロセスの誤り率性能を改善できることが周知である。したがって、フラッシュ・メモリからの硬データを使用して軟データを推定するかその質を高め、これによつて復号性能を改善する、軟データ生成技法の必要が存在する。

【課題を解決するための手段】

20

【0012】

一般に、基準セルを使用する、メモリ・デバイスの軟データ生成の方法および装置が提供される。本発明の一態様によれば、少なくとも1つの軟データ値が、1つまたは複数の基準セルに既知のデータを書き込むことと、基準セルのうちの1つまたは複数を読み取ることと、読み取られた1つまたは複数の基準セルに基づいて読み取統計を入手することと、入手された読み取統計に基づいて少なくとも1つの軟データ値を入手することによって、メモリ・デバイス内で生成される。既知のデータを、電圧、電流、および抵抗のうちの1つまたは複数を使用して基準セルに書き込むことができる。同様に、読み取るステップは、データ・ビット、電圧レベル、電流レベル、および抵抗レベルのうちの1つまたは複数を読み取る。既知のデータは、ビット・パターンまたは記号パターンを含むことができる。生成される軟データ値は、(i)1つまたは複数の対数尤度比を生成するのに使用される軟読み取値、あるいは(ii)1つまたは複数の対数尤度比を含むことができる。統計は、ビット・ベースの統計、セル・ベースの統計、およびパターン依存統計のうちの1つまたは複数を含むことができる。

30

【0013】

一実施形態では、読み取統計は、1つまたは複数の基準セルから読み取られた1つまたは複数のビットを既知のデータ内の1つまたは複数のビットと比較することによって判定される。たとえば、読み取統計を、既知のデータ内の基準ビットの総数に対する相対的な誤りのあるビットの個数に基づくものとすることができます。読み取統計または軟データ値(あるいはその両方)を、耐久性、プログラム/消去サイクルの個数、読み取サイクルの個数、保持時間、温度、温度変化、プロセス・コーナー、セル間干渉影響、メモリ・デバイス内の位置、ワード線内の位置、メモリ・アレイ内の位置、およびアグレッサ・セル内のパターンのうちの1つまたは複数の関数として計算することができる。

40

【0014】

一態様によれば、読み取統計を、メモリ・アレイの1つまたは複数の所望の位置について入手することができ、書き込むステップは、既知のデータを1つまたは複数の所望の位置に書き込むことを含む。たとえば、所望の位置は、ページ位置、ワード線位置、ビット線位置、およびマルチレベル・セル内の所与のビットのうちの1つまたは複数を含むことができる。

【0015】

50

もう 1 つの態様によれば、読み取り統計を、少なくとも 1 つのターゲット・セルに関連する 1 つまたは複数のアグレッサ・セル内の所与のパターン P A T T について入手することができ、書き込むステップは、既知のデータを少なくとも 1 つのターゲット・セルに書き込むことを含み、方法は、1 つまたは複数のアグレッサ・セル内の所与のパターン P A T T を有する誤りのあるターゲット・ビットの個数を判定するステップと、誤りのあるターゲット・ビットの個数に基づいて所与のパターンに関する読み取り統計を入手するステップとをさらに含む。

【 0 0 1 6 】

もう 1 つの態様によれば、読み取り統計は、複数の可能な値について入手された非対称読み取り統計を含むことができ、方法は、既知のデータ内の第 1 の値を有する誤りのあるビットの個数を判定するステップと、既知のデータ内の第 2 の値を有する誤りのあるビットの個数を判定するステップと、第 1 の値を有する誤りのあるビットの個数に基づいて第 1 の値に関する読み取り統計を入手するステップと、第 2 の値を有する誤りのあるビットの個数に基づいて第 2 の値に関する読み取り統計を入手するステップとをさらに含む。

【 0 0 1 7 】

本発明ならびに本発明のさらなる特徴および利益のより完全な理解は、次の詳細な説明および図面を参照することによって得られる。

【 図面の簡単な説明 】

【 0 0 1 8 】

【 図 1 】従来のフラッシュ・メモリ・システムを示す概略ブロック図である。

10

【 図 2 】図 1 の例示的なフラッシュ・メモリの例示的なしきい電圧分布を示す図である。

【 図 3 】マルチレベル・セル ( M L C ) フラッシュ・メモリ・デバイス内の例示的なフラッシュ・セル・アレイのアーキテクチャを示す図である。

【 図 4 】図 2 の電圧割当て方式の例示的な 2 ステージ M L C プログラミング方式を示す図である。

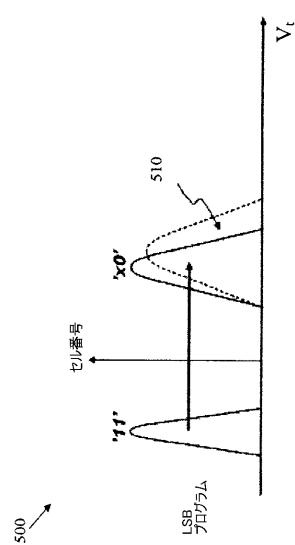

【 図 5 A 】隣接セルに加えられる I C I を減らす代替 M L C プログラミング方式を集合的に示す図である。

【 図 5 B 】隣接セルに加えられる I C I を減らす代替 M L C プログラミング方式を集合的に示す図である。

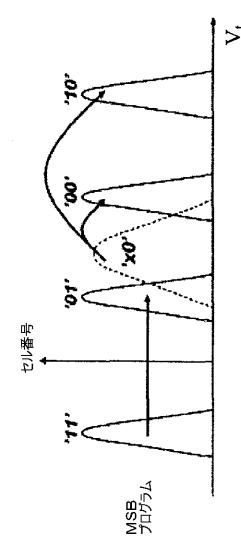

【 図 6 】マルチレベル・セル ( M L C ) フラッシュ・メモリ・デバイス内の例示的なフラッシュ・セル・アレイをさらに詳細に示す図である。

30

【 図 7 】セル間干渉、バック・パターン依存、雑音、および他のひずみなどの複数の例示的なアグレッサ・セルに起因するターゲット・セルについて存在する外乱を示す図である。

【 図 8 】本発明によるコントローラ・ベースの軟デマッピング / 軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システムを示す概略ブロック図である。

【 図 9 】本発明の代替実施形態によるメモリ・ベースの軟デマッピング / 軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システムを示す概略ブロック図である。

【 図 1 0 】反復的なデマッピングおよび復号ならびにオプションのインターリービングを用いる例示的なフラッシュ読み取りチャネル・アーキテクチャを示す図である。

40

【 図 1 1 】本発明による軟データ生成を用いる例示的なフラッシュ・メモリ・システムを示す図である。

【 図 1 2 A 】それぞれ例示的な軟デマッピング・プロセスおよび例示的な軟データ生成プロセスを説明する流れ図である。

【 図 1 2 B 】それぞれ例示的な軟デマッピング・プロセスおよび例示的な軟データ生成プロセスを説明する流れ図である。

【 図 1 3 】 L D P C ( l o w - d e n s i t y p a r i t y - c h e c k ) 符号の例示的な 2 部グラフ表現を示す図である。

【 図 1 4 】例示的な L D P C デコーダ・アーキテクチャを示すブロック図である。

【 図 1 5 】本発明の一実施形態による軟データ生成を用いる例示的なフラッシュ・メモリ

50

・システムを示す図である。

【図16】例示的な2進チャネルの誤り確率pおよびqを示すトレリスである。

【図17A】フラッシュ・メモリからのデータの読み出に関する統計を記録する例示的なセル・ベースの統計テーブルを示す図である。

【図17B】フラッシュ・メモリからのデータの読み出に関する統計を記録する例示的なセル・ベースの統計テーブルを示す図である。

【図17C】フラッシュ・メモリからのデータの読み出に関する統計を記録する例示的なセル・ベースの統計テーブルを示す図である。

【図18】フラッシュ・メモリからのデータの読み出に関するパターン依存統計を記録する例示的なパターン依存セル・ベース統計テーブルを示す図である。

【図19】本発明の基準セル実施形態に関する、図3の例示的なフラッシュ・セル・アレイをさらに詳細に示す図である。

【図20】本発明の基準セル実施形態に関するビット・ベースの統計生成プロセスの例示的実施態様を説明する流れ図である。

【図21】本発明の基準セル実施形態に関するセル・ベースの統計生成プロセスの例示的実施態様を説明する流れ図である。

【図22】本発明の復号済み符号語実施形態に関するビット・ベースの統計生成プロセスの例示的実施態様を説明する流れ図である。

【図23】本発明の復号済み符号語実施形態に関するセル・ベースの統計生成プロセスの例示的実施態様を説明する流れ図である。

【図24】メモリ・アレイ内の複数の異なる位置に関する誤り確率統計を計算する例示的なビット・ベースの位置固有統計生成プロセスを説明する流れ図である。

【図25】メモリ・アレイ内の複数の異なる位置に関する統計を計算する例示的なセル・ベースの位置固有統計生成プロセスを説明する流れ図である。

【図26】各アグレッサ・セルのすべての可能な値に基づく、所与のターゲット・セルに対するパターン依存外乱の影響を示す確率密度関数の集団を示す図である。

【図27】少なくとも1つのターゲット・セルに関連する1つまたは複数のアグレッサ・セル内の所与のデータ・パターンに依存する誤り確率統計を推定する例示的なビット・ベースのパターン依存統計生成プロセスを説明する流れ図である。

【図28】少なくとも1つのターゲット・セルに関連する1つまたは複数のアグレッサ・セル内の所与のデータ・パターンに依存する統計を推定する例示的なセル・ベースのパターン依存統計生成プロセスを説明する流れ図である。

【図29】本発明の基準セル実施形態の2つの可能な2進値の誤り確率統計を推定する例示的な非対称統計生成プロセスを説明する流れ図である。

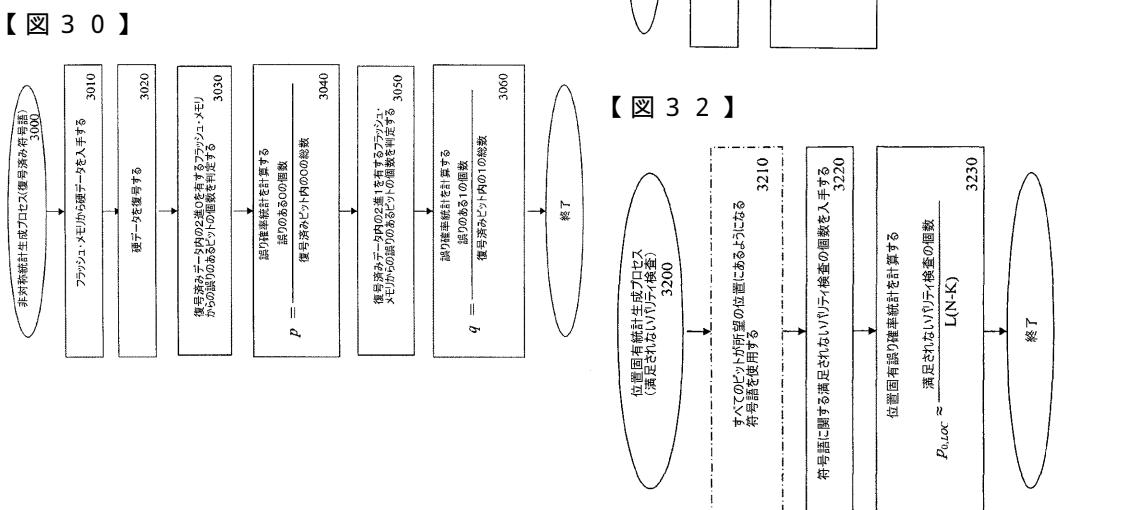

【図30】本発明の復号済み符号語実施形態の2つの可能な2進値の誤り確率統計を推定する例示的な非対称統計生成プロセスを説明する流れ図である。

【図31】満足されないパリティ検査を使用する統計生成プロセスの例示的実施態様を説明する流れ図である。

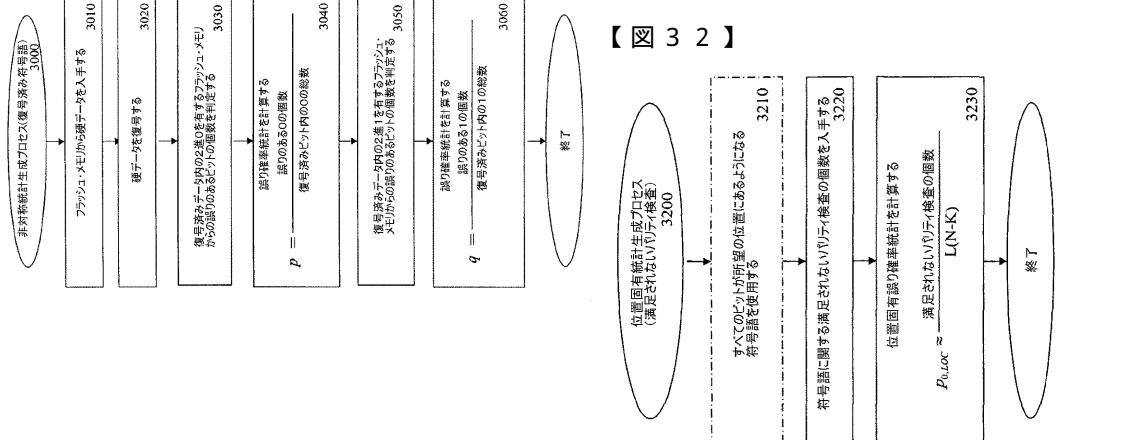

【図32】満足されないパリティ検査を使用してメモリ・アレイ内の複数の異なる位置の誤り確率統計を推定する例示的な位置固有統計生成プロセスを説明する流れ図である。

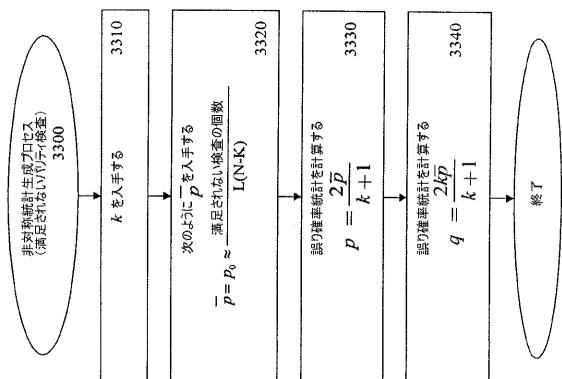

【図33】満足されないパリティ検査を使用して2つの可能な2進値の誤り確率統計を推定する例示的な非対称統計生成プロセスを説明する流れ図である。

【発明を実施するための形態】

【0019】

本発明のさまざまな態様は、シングルレベル・セルまたはマルチレベル・セル(MLC)NANDフラッシュ・メモリ・デバイスなどのメモリ・デバイスでの改善された復号のための軟データ生成技法を対象とする。本明細書で使用されるときに、マルチレベル・セル・フラッシュ・メモリは、各メモリ・セルが複数のビットを格納するメモリを含む。通常、1つのフラッシュ・セルに格納される複数のビットは、異なるページに属する。本発明は、本明細書ではアナログ値を電圧として格納するメモリ・セルを使用して例示される

10

20

30

40

50

が、当業者に明白であるように、本発明を、格納されたデータを表すのに電圧または電流を使用することなど、メモリ・デバイスの任意のストレージ機構と共に使用することができる。

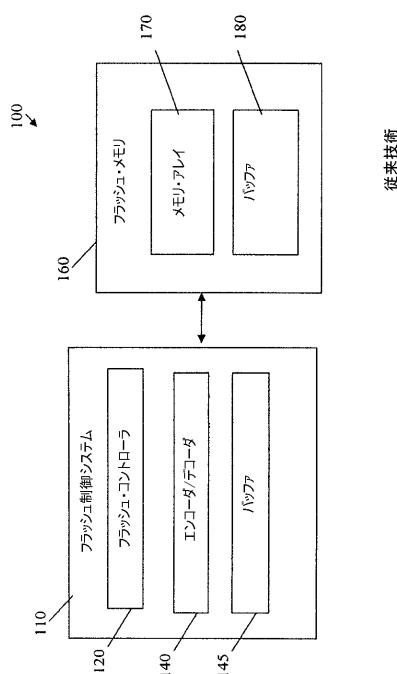

#### 【0020】

図1は、従来のフラッシュ・メモリ・システム100の概略ブロック図である。図1に示されているように、例示的なフラッシュ・メモリ・システム100は、フラッシュ制御システム110およびフラッシュ・メモリ・ブロック160を含む。例示的なフラッシュ制御システム110は、フラッシュ・コントローラ120、エンコーダ/デコーダ・ブロック140、および1つまたは複数のバッファ145を含む。代替実施形態では、エンコーダ/デコーダ・ブロック140およびいくつかのバッファ145を、フラッシュ・コントローラ120の内部で実施することができる。エンコーダ/デコーダ・ブロック140およびバッファ145を、たとえば、周知の市販の技法および/または製品を使用して実施することができる。

#### 【0021】

例示的なフラッシュ・メモリ・ブロック160は、それぞれ周知の市販の技法および/または製品を使用して実施できる、メモリ・アレイ170および1つまたは複数のバッファ180を含む。メモリ・アレイ170は、NANDフラッシュ・メモリ、相変化メモリ(PCM)、MRAMメモリ、NORフラッシュ・メモリ、または別の不揮発性フラッシュ・メモリなど、シングルレベル・セルまたはマルチレベル・セルのフラッシュ・メモリとして実施することができる。本発明を、主にマルチレベル・セルNANDフラッシュ・メモリの文脈で例示するが、当業者に明白であるように、本発明を、シングルレベル・セル・フラッシュ・メモリおよび他の不揮発性メモリに適用することができる。

#### 【0022】

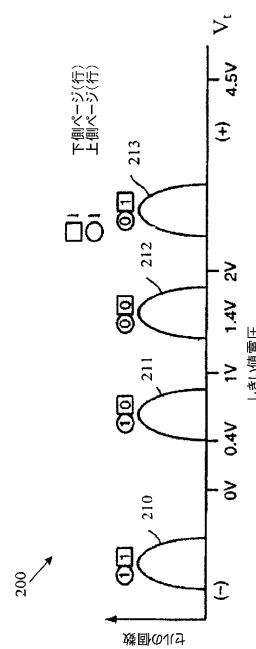

##### マルチレベル・セル・フラッシュ・メモリ

マルチレベル・セルNANDフラッシュ・メモリでは、しきい値検出器が、通常、特定のセルに関連する電圧値を事前定義のメモリ状態に変換するのに使用される。図2に、参考によって本明細書に組み込まれている米国特許第6,522,580号の教示に基づく、図1の例示的なマルチレベル・セル・フラッシュ・メモリ170の例示的なしきい電圧分布を示す。一般に、セルのしきい電圧は、そのセルがある量の電流を導通するようにするためそのセルに印加される必要がある電圧である。しきい電圧は、セルに格納されるデータに関する測定値である。

#### 【0023】

図2に示された例示的な実施形態では、各ストレージ要素は、各メモリ・セル内に2ビットのデータを格納するために4つの可能なデータ状態を使用する。図2は、4つのピーク210～213を示し、各ピークは1つの状態に対応する。マルチレベル・セル・フラッシュ・デバイスでは、しきい電圧分布グラフ200の異なるピーク210～213が、セルに2ビットを格納するのに使用される。

#### 【0024】

しきい電圧分布グラフ200のピーク210～213は、対応する2進値を用いてラベルを付けられている。したがって、あるセルが第1状態210であるときに、そのセルは、下側ビット(最下位ビット、LSBとも称する)について「1」を、上側ビット(最上位ビット、MSBとも称する)について「1」を表す。状態210は、一般に、セルの初期未プログラム状態または消去状態である。同様に、あるセルが、第2状態211であるときに、そのセルは、下側ビットについて「0」、上側ビットについて「1」を表す。あるセルが第3状態212であるときに、そのセルは、下側ビットについて「0」、上側ビットについて「0」を表す。最後に、あるセルが第4状態213であるときに、そのセルは、下側ビットについて「1」、上側ビットについて「0」を表す。

#### 【0025】

しきい電圧分布210は、0ボルト未満の負のしきい電圧レベルを有する、消去状態(「11」データ状態)であるアレイ内のセルのしきい電圧 $V_t$ の分布を表す。それぞれ「

10

20

30

40

50

10」および「00」のユーザ・データを格納するメモリ・セルのしきい電圧分布211および212が、それぞれ0ボルトと1ボルトとの間ならびに1ボルトと2ボルトとの間にあるものとして示されている。しきい電圧分布213は、読取経路電圧の2ボルトと4.5ボルトとの間にセットされたしきい電圧レベルを有する、「01」データ状態になるようにプログラムされたセルの分布を示す。

#### 【0026】

したがって、図2の例示的実施形態では、0ボルト、1ボルト、および2ボルトを、各レベルまたは各状態の間の電圧レベルしきい値として使用することができる。これらの電圧レベルしきい値は、フラッシュ・メモリ160（たとえば、フラッシュ・メモリ160内のセンシング回路）によって、所与のセルの電圧レベルまたは状態を判定するのに使用される。フラッシュ・メモリ160は、電圧レベルしきい値に対する測定電圧の比較に基づいて各セルに1つまたは複数のビットを割り当て、この割当ては、その後、硬判定としてフラッシュ制御システム110に送られる。それに加えてまたはその代わりに、軟情報（soft information）を使用する実施態様では、フラッシュ・メモリ160は、測定電圧または測定電圧の量子化版を軟情報としてフラッシュ制御システム110に送ることができ、ここでは、メモリ・セルに格納されたビット数より多数のビットが、測定電圧を表すのに使用される。

#### 【0027】

さらに、セルが、通常は周知のプログラム／検証技法を使用してプログラムされることに留意されたい。一般に、プログラム／検証サイクル中には、フラッシュ・メモリ160は、最小ターゲットしきい電圧を超えるまで、セル・トランジスタ内に電荷をたくわえるために増加する電圧を徐々に印加する。たとえば、図2の例で「10」データ状態をプログラムする時に、フラッシュ・メモリ160は、0.4Vの最小ターゲットしきい電圧を超えるまで、セル・トランジスタ内に電荷をたくわえるために増加する電圧を徐々に印加することができる。

#### 【0028】

下でさらに述べるように、単一のメモリ・セルに格納された2ビットのそれぞれは、異なるページからのものである。言い換えると、各メモリ・セルに格納された2ビットの各ビットは、異なるページ・アドレスを担う。図2に示された右側ビットは、下側ページ・アドレスが入力される時にアクセスされる。左側ビットは、上側ページ・アドレスが入力される時にアクセスされる。

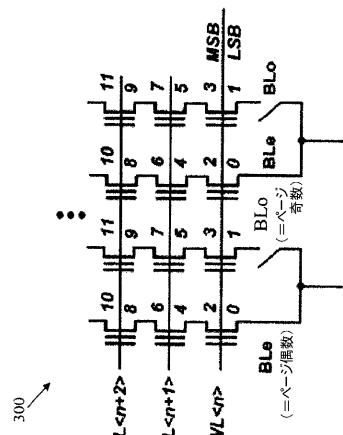

#### 【0029】

図3に、マルチレベル・セル（MLC）フラッシュ・メモリ・デバイス160内の例示的なフラッシュ・セル・アレイ300のアーキテクチャを示し、ここで、各例示的セルは、通常、2ビットを格納するフローティングゲート・トランジスタに対応する。図3では、各セルが、2ビットが属する2つのページの2つの番号に関連する。例示的なセル・アレイ・セクション300は、ワード線nからn+2および4つのビット線を示す。例示的なフラッシュ・セル・アレイ300は、偶数ページおよび奇数ページに区分され、たとえば、偶数番号を有するセル（番号0および2を有するセルなど）は、偶数ページに対応し、奇数番号を有するセル（番号1および3を有するセルなど）は、奇数ページに対応する。ワード線nは、たとえば、偶数ビット線に偶数ページ0および2を格納し、奇数ビット線に奇数ページ1および3を格納する。

#### 【0030】

さらに、図3は、偶数ビット線セルまたは奇数ビット線セルのいずれかが選択され、示された順序で順次（ボトム・アップ）プログラムされる、例示的なプログラム・シーケンスを示す。番号は、ページがプログラムされる順序を示す。たとえば、ページ0は、ページ1の前にプログラムされる。偶数ページおよび帰趣ページのプログラミングのさらなる議論については、参照によって本明細書に組み込まれている、K.-T. Park他、「A Zeroing Cell-to-Cell Interference Page Architecture with Temporary LSB Storing

and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE Journal of Solid-State Circuits、Vol. 43、No. 4、919～928頁(2008年4月)を参照されたい。

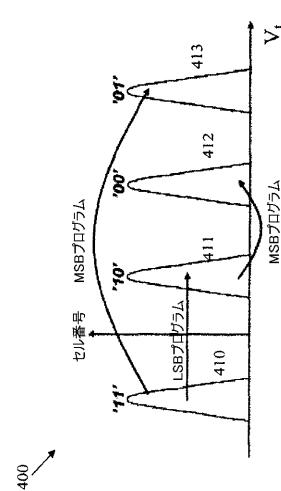

【0031】

図4に、図2の電圧割当て方式の例示的な2ステージMLCプログラミング方式400を示す。図4に示されているように、LSBプログラミング・ステージ中には、消去状態410である選択されたセルの状態は、LSBが0である場合には最低のプログラム済み状態411に移動する。したがって、LSBプログラミング状態で、メモリ・セルは、消去状態「11」から「10」にプログラムされる。次に、MSBプログラミング・ステージ中に、2つの状態すなわち状態「00」(412)および状態「01」(413)が、以前のLSBデータに応じて順次形成される。一般に、MSBプログラミング状態中には、「10」状態が「00」にプログラムされ、状態「11」が「01」にプログラムされる。

【0032】

図4のプログラミング方式400が、状態410から状態413への状態の変化に関連する最大電圧シフトを示すことに留意されたい。複数のプログラミング方式が、状態の変化に関連する最大電圧シフトを減らし、これによって、電圧シフトによって引き起こされるICを減らすために提案されまたは提唱されてきた。

【0033】

図5Aおよび5Bは、隣接セルに加えられるICを減らす代替MLCプログラミング方式500を集合的に示す。図5Aに示されているように、LSBプログラミング・ステージ中に、メモリ・セルは、SLCプログラミングに似た形で、状態「11」から一時的(または中間)状態として状態「x0」にプログラムされる。同一ワード線内の隣接セルもLSBプログラムされた後に、分布は、おそらくは、ICに起因して図5Aのピーク510によって示されるように広げられる。その後、図5Bに示されたMSBプログラミング・ステージで、「x0」状態が、入力データに対応する最終状態として「00」および「10」のいずれかにプログラムされ、あるいは、「11」状態が、最終的な「01」状態にプログラムされる。一般に、「11」セルを除くすべてのメモリ・セルは、MSBプログラミング・ステージで、LSBデータについて一時的にプログラムされた状態からその最終的な状態に再プログラムされ、その結果、隣接セルによって引き起こされるICを大幅に減らせるようになる。最終的な状態のセルは、最終的な状態に再プログラムされたので、中間状態である間に経験したICから損害を受けない。最終的な状態のセルは、最終的な状態になって以降に経験したICからのみ損害を受ける。上で注記したように、中間プログラム状態を使用する、図5Aおよび5Bのマルチステップ・プログラミング・シーケンスは、最大電圧変化を減らし、したがって、これらの電圧変化によって引き起こされるICを減らす。図5Bで、たとえばMSBプログラミング・ステージ中の最大電圧シフトが、それぞれ状態「11」から「01」へおよび状態「x0」から状態「10」への遷移に関連することがわかる。これらの電圧シフトは、図4の状態「11」から「01」への最大電圧シフトより大幅に小さい。

【0034】

図6に、マルチレベル・セル(MLC)フラッシュ・メモリ・デバイス130内の例示的なフラッシュ・セル・アレイ600をさらに詳細に示す。図6に示されているように、フラッシュ・セル・アレイ600は、フラッシュ・セルあたり3つのビット $c_i$ を格納する。図6は、1ブロックのフラッシュ・セル・アレイ・アーキテクチャを示し、ここで、各例示的なセルは、通常、3ビットを格納するフローティングゲート・トランジスタに対応する。例示的なセル・アレイ600は、m個のワード線およびn個のビット線からなる。通常、現在のマルチページ・セル・フラッシュ・メモリでは、单一のセル内のビットは、異なるページに属する。図6の例では、各セルの3つのビットは、3つの異なるページに対応し、各ワード線は、3つのページを格納する。次の議論では、ページ0、1、および2を、ワード線内の下側ページ・レベル、中央ページ・レベル、および上側ページ・レ

10

20

30

40

50

ベルと称する。

【0035】

上で示したように、フラッシュ・セル・アレイを、偶数ページおよび奇数ページにさらに区分することができ、たとえば、偶数番号を有するセル（図6のセル2および4など）は、偶数ページに対応し、奇数番号を有するセル（図6のセル1および3など）は、奇数ページに対応する。この場合に、ページ（ページ0など）は、偶数セル内に偶数ページ（偶数ページ0）を含み、奇数セル内に奇数ページ（奇数ページ0）を含む。

【0036】

セル間干渉および他の外乱

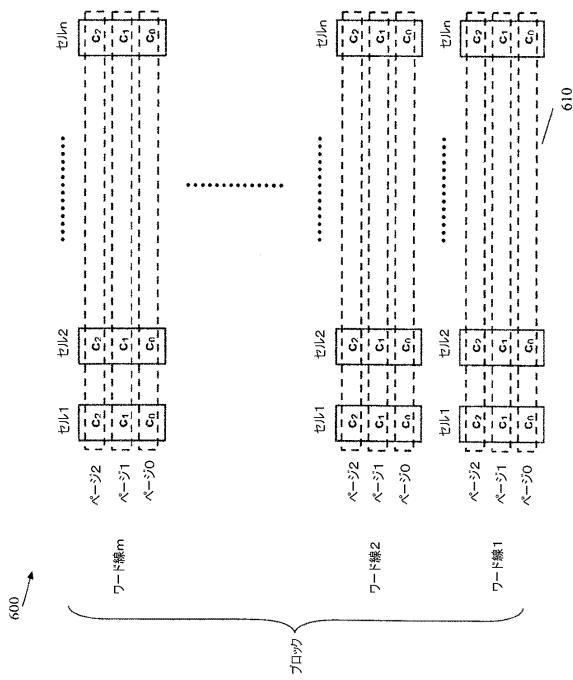

図7に、セル間干渉、バック・パターン依存、雑音、および他のひずみなどの複数の例示的なアグレッサ・セル720に起因するターゲット・セル710について存在する外乱を示す。次の表記か、図7で使用されている。

WL ワード線、

BL ビット線、

BLo 奇数ビット線、

BLE 偶数ビット線、および

C キャパシタンス。

【0037】

たとえば、IC1は、ターゲット・セル710がプログラムされた後にプログラムされるアグレッサ・セル720によって引き起こされる。IC1は、ターゲット・セル710の電圧 $V_t$ を変更する。例示的実施形態では、「ボトム・アップ」プログラミング方式が仮定され、ワード線 $i$ および $i+1$ 内の近接アグレッサ・セルが、ターゲット・セル710のIC1を引き起こす。ロックのそのようなボトム・アップ・プログラミングを用いると、図7に示されているように、下側ワード線 $i-1$ からのIC1が除去され、5つまでの隣接するセルが、アグレッサ・セル720としてIC1に寄与する。しかし、当業者に明白であるように、本明細書で開示される技法を、ワード線 $i-1$ などの他のワード線からのアグレッサ・セルもIC1に寄与する場合に一般化できることに留意されたい。ワード線 $i-1$ 、 $i$ 、および $i+1$ からのアグレッサ・セルがIC1に寄与する場合には、8つまでの最も近い隣接セルを考慮する必要がある。ターゲット・セルからより遠い他のセルは、そのIC1への寄与を無視できる場合には、無視することができる。一般に、アグレッサ・セル720は、所与のターゲット・セル710の後にプログラムされるアグレッサ・セル720を識別するためにプログラミング・シーケンス方式（ボトム・アップまたは偶数/奇数技法など）を分析することによって識別される。

【0038】

一般に、 $V_t$ は、セルに格納されたデータを表す電圧であり、読み取り動作中に入手される。 $V_t$ を、読み取り動作によって、たとえばセルあたりに格納されるビット数より高い精度を有する軟電圧値として、またはセルあたりに格納されるビット数と同一の分解能を有する硬電圧レベル（たとえば、3ビット/セル・フラッシュについて3ビット）に量子化された値として、入手することができる。

【0039】

IC1軽減技法のより詳細な議論については、たとえば、それぞれ参照によって本明細書に組み込まれている国際出願第PCT/US09/49326号、名称「Methods and Apparatus for Read-Side Inter-cell Interference Mitigation in Flash Memories」または国際出願第PCT/US09/49327号、名称「Methods and Apparatus for Write-Side Inter-cell Interference Mitigation in Flash Memories」を参照されたい。

【0040】

軟データ生成

10

20

30

40

50

本発明は、フラッシュ・メモリの軟マッピング技法および軟データ生成技法を提供する。下で図12Aに関連してさらに述べる、1つの例示的実施形態では、質を高められた軟データが、確率密度関数、その近似、ビット・ベースの確率、またはセル・ベースの確率などの確率統計を使用してフラッシュ・メモリによって割り当てられる軟データから生成される。下で図12Bに関連してさらに述べる、別の例示的実施形態では、軟データは、確率密度関数、その近似、ビット・ベースの確率、またはセル・ベースの確率などの確率統計を使用してフラッシュ・メモリによって割り当てられる硬データから生成される。一般に、フラッシュ・メモリによって割り当てられるデータは、最初に入手される。次に、本発明は、フラッシュ・メモリからのデータに基づいて、確率または信頼性情報などの軟情報を生成し、またはその質を高める。生成された軟情報を、オプションで、軟判定復号に使用することができる。本明細書で使用されるときに、用語「確率密度関数」は、確率密度関数と、ヒストグラムおよびガウス近似などのその近似とを含まなければならない。

10

#### 【0041】

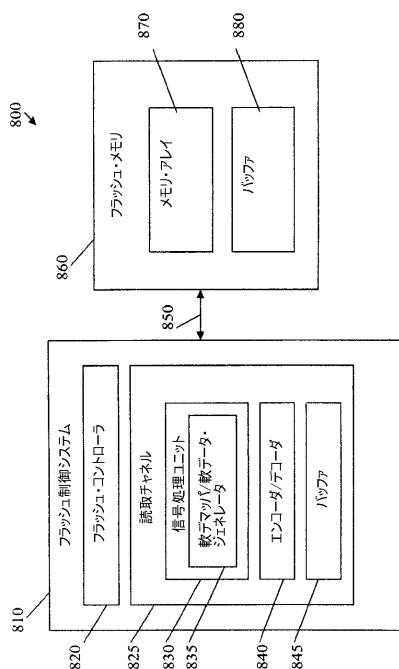

図8は、本発明によるコントローラ・ベースの軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システム800の概略ブロック図である。図8に示されているように、例示的なフラッシュ・メモリ・システム800は、インターフェース850によって接続された、フラッシュ制御システム810およびフラッシュ・メモリ・ブロック860を含む。例示的なフラッシュ制御システム810は、通常は1つまたは複数の集積回路である、フラッシュ・コントローラ820および読み取りチャネル825を含む。

20

#### 【0042】

例示的な読み取りチャネル825は、信号処理ユニット830、エンコーダ/デコーダ・ブロック840、および1つまたは複数のバッファ845を含む。用語「読み取りチャネル」が、書き込みチャネルをも含むことができることに留意されたい。代替実施形態では、エンコーダ/デコーダ・ブロック840およびいくつかのバッファ845を、フラッシュ・コントローラ820の内部で実施することができる。エンコーダ/デコーダ・ブロック840およびバッファ845を、たとえば、本発明の特徴および機能を提供するために本明細書で変更される、周知の市販の技法および/または製品を使用して実施することができる。

#### 【0043】

例示的な信号処理ユニット830は、それぞれたとえば図12Aおよび12Bに関連して下でさらに述べる1つまたは複数の軟マッパーおよび/または軟データ生成プロセス835を実施する1つまたは複数のプロセッサを含む。例示的なフラッシュ・メモリ・ブロック860は、それぞれ周知の市販の技法および/または製品を使用して実施できるメモリ・アレイ870および1つまたは複数のバッファ880を含む。

30

#### 【0044】

開示される軟データ生成技法のさまざまな実施形態では、例示的なインターフェース850は、アグレッサ・セルに関連する情報を表す値など、従来のフラッシュ・メモリ・システムに関連する追加情報を伝える必要がある場合がある。したがって、インターフェース850は、従来のフラッシュ・メモリ・システム内のインターフェースより大きい容量またはより高速のレートを有する必要がある場合がある。インターフェース850を、オプションで、参照によって本明細書に組み込まれている、2009年6月30日に出願した国際出願第PCT/US09/49328号、名称「Methods and Apparatus for Interfacing Between a Flash Memory Controller and a Flash Memory Array」(弁理士整理番号第08-0769号)の教示に従って実施することができ、この国際出願第PCT/US09/49328号の教示は、たとえばダブル・データ・レート(DDR)技法を使用してインターフェース850の情報搬送容量を高める。書き動作中に、インターフェース850は、通常はページ・レベル・アクセス技法またはワード線レベル・アクセス技法を使用して、ターゲット・セルに格納されるプログラム値を転送する。例示的なページ・レベル・アクセス技法またはワード線レベル・アクセス技法のより詳細

40

50

な議論については、たとえば、参照によって本明細書に組み込まれている、2009年3月11日に出願した国際出願第PCT/US09/36810号、名称「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding」を参照されたい。

【0045】

読み取り動作中に、インターフェース850は、ターゲット・セルおよびアグレッサ・セルについてメモリ・アレイ870から入手された硬読み取り値および/または軟読み取り値を転送する。たとえば、ターゲット・セルを有するページの読み取り値に加えて、上側/下側ワード線または隣接する偶数ビット線もしくは奇数ビット線内の1つまたは複数の近接ページの読み取り値が、インターフェース・バスを介して転送される。図8の実施形態では、開示される軟データ生成技法は、フラッシュ・メモリの外部で、通常は最小面積を達成するために論理回路用に最適化されたプロセス・テクノロジで実施される。しかし、これは、インターフェース850上で転送される可能性がある追加のアグレッサ・セル・データという犠牲を払うものである。

【0046】

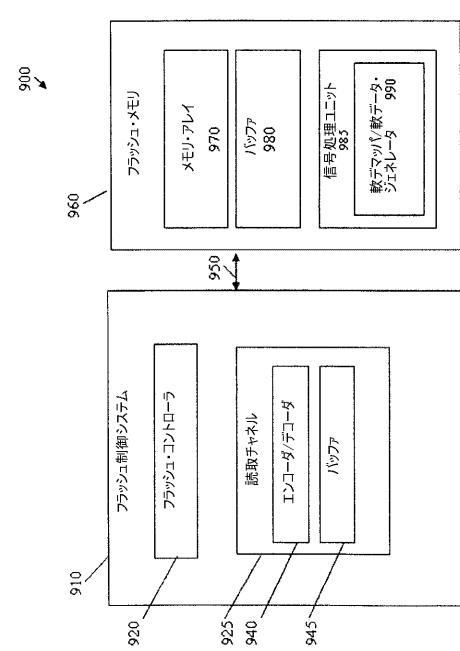

図9は、本発明の代替実施形態によるメモリ・ベースの軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システム900の概略ブロック図である。図9に示されているように、例示的なフラッシュ・メモリ・システム900は、インターフェース950によって接続された、フラッシュ制御システム910およびフラッシュ・メモリ・ブロック960を含む。

【0047】

例示的なフラッシュ制御システム910は、通常は1つまたは複数の集積回路である、フラッシュ・コントローラ920およびオプションの読み取りチャネル925を含む。代替実施形態では、エンコーダ/デコーダ・ブロック940およびいくつかのバッファ945を、フラッシュ・コントローラ920の内部で実施することができる。例示的なフラッシュ・コントローラ920を、たとえば、本発明の特徴および機能をサポートするために本明細書で変更される、周知の市販の技法および/または製品を使用して実施することができる。例示的な読み取りチャネル925は、エンコーダ/デコーダ・ブロック940および1つまたは複数のバッファ945を含む。エンコーダ/デコーダ・ブロック940およびバッファ945を、周知の市販の技法および/または製品を使用して実施することができる。

【0048】

例示的なフラッシュ・メモリ・ブロック960は、それぞれ周知の市販の技法および/または製品を使用して実施することができる、メモリ・アレイ970および1つまたは複数のバッファ980を含む。さらに、例示的なフラッシュ・メモリ・ブロック960は、それぞれたとえば図12Aおよび12Bに関連して下でさらに述べる1つまたは複数の軟データマッピングおよび/または軟データ生成プロセス990を実施する1つまたは複数のプロセッサを含む例示的な信号処理ユニット985を含む。

【0049】

開示される軟データ生成技法のさまざまな実施形態では、例示的なインターフェース950は、アグレッサ・セルに関連する情報を表す値など、従来のフラッシュ・メモリ・システムに関連する追加情報を伝える必要がある場合がある。したがって、インターフェース950は、従来のフラッシュ・メモリ・システム内のインターフェースより大きい容量またはより高速のレートを有する必要がある場合がある。インターフェース950を、オプションで、参照によって本明細書に組み込まれている、2009年6月30日に出願した国際出願第PCT/US09/49328号、名称「Methods and Apparatus for Interfacing Between a Flash Memory Controller and a Flash Memory Array」(弁理士整理番号第08-0769号)の教示に従って実施することができ、この国

10

20

30

40

50

際出願第PCT/US09/49328号の教示は、たとえばダブル・データ・レート(DDR)技法を使用してインターフェース950の情報搬送容量を高める。

#### 【0050】

書込動作中に、インターフェース950は、ターゲット・セルおよびアグレッサ・セルに格納されるプログラム・データを転送する。読取動作中に、インターフェース950は、ターゲット・セル(1つまたは複数)およびオプションでアグレッサ・セルの新しい硬読取値、硬データ、軟読取値、または軟データを転送する。通常、単一の読取アクセスについて伝えられる情報は、1ページまたは1ワード線のデータである。ターゲット・セルのデータだけを送ることは、通常は論理回路用ではなくメモリ用に最適化された、フラッシュ・メモリの製造に使用されるメモリ・プロセス・テクノロジを使用してメモリの内部で軟データ生成プロセスを実施するという犠牲を払って、インターフェース950の帯域幅要件を減らすことに留意されたい。10

#### 【0051】

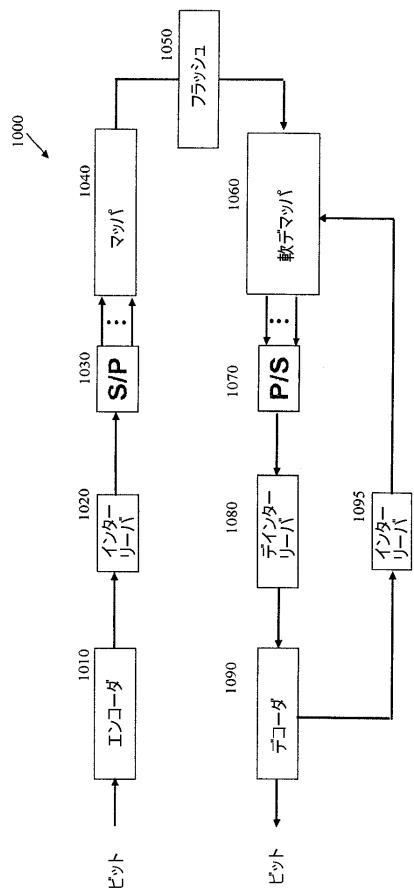

図10に、参照によって本明細書に組み込まれている2009年6月30日に出願した国際出願第PCT/US09/49333号、名称「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」の教示に従う反復的なデマッピングおよび復号ならびにオプションのインターリービングを用いる例示的なフラッシュ読取チャネル・アーキテクチャ1000を示す。図10に示されているように、例示的な書込経路は、エンコーダ1010、オプションのインターリーバ1020、直並列コンバータ1030、およびマッパ1040を含む。データは、既知の形でメモリ1050に書き込まれ、メモリ1050から読み取られる。例示的な読取経路は、軟デマッパまたは軟データ・ジェネレータ1060、並直列コンバータ1070、デインターリーバ1080、デコーダ1090、およびインターリーバ1095を含む。一般に、下でさらに述べるように、軟デマッパまたは軟データ・ジェネレータ1060は、反復プロセスが最終判断に収束するまで反復的な形で新しい軟情報を生成し、軟デマッパにフィード・バックするためにデコーダ1090によって処理される、下でさらに説明される軟情報を生成する。20

#### 【0052】

本発明に従って軟情報(LLR)を生成するのに軟デマッパ1060によって使用される式を、下の「読取統計を使用する軟データ(LLR)の計算」という題名のセクションで述べる。図10に示されているように、軟デマッパ1060によって生成される軟情報を、軟デマッパ1060、デインターリーバ1080、デコーダ1090、およびフィードバック経路内のインターリーバ1095の間の反復デマッピングおよび復号に使用することができる。30

#### 【0053】

##### フラッシュからのデータに基づく軟データ生成

本発明は、現在のフラッシュ・メモリ860、960が、通常はフラッシュ制御システム810、910に硬データだけを供給することを認めるものである。しかし、軟データが、復号プロセスで誤り率性能を改善できることが周知である。したがって、本発明の一態様によれば、フラッシュ・メモリ860、960からの硬データは、軟データを推定するのに使用され、これによって、フラッシュ制御システム810、910での復号性能を改善する。たとえば、後で述べるように、硬データの統計特性を使用して、軟データを推定するかその質を高めることができる。生成された軟データを、その後、誤り率性能を改善するために、LDPC符号の確率伝搬(belief propagation)復号などの復号に使用することができる。40

#### 【0054】

本発明のもう1つの態様によれば、フラッシュ・メモリ860、960は、フラッシュ制御システム810、910に軟データまたは軟情報を供給する。質を高められた軟データが、フラッシュ・メモリ860、960によって供給された軟データから生成されて、50

これによって、フラッシュ制御システム 810、910 での復号性能が改善される。軟情報を使用する実施態様では、フラッシュ・メモリ・システム 860、960 は、測定電圧または測定電圧の量子化版を軟情報としてフラッシュ制御システム 810、910 に送り、ここで、メモリ・セルに格納されるビット数より多数のビットが、測定電圧を表すのに使用される。

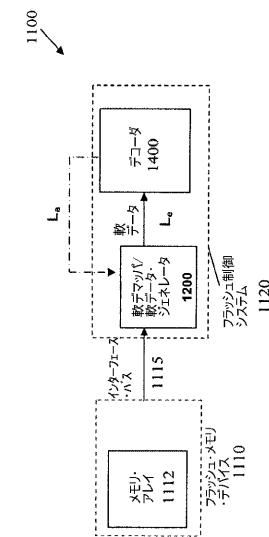

【0055】

図 11 に、本発明の一実施形態によるコントローラ・ベースの軟データ生成を用いる例示的なフラッシュ・メモリ・システム 1100 を示す。図 11 に示されているように、例示的なフラッシュ・メモリ・システム 1100 は、インターフェース 1115 によって接続された、フラッシュ・メモリ・ブロック 1110 およびフラッシュ制御システム 1120 を含む。後で述べるように、軟データ値または硬データ値（あるいはその両方）は、フラッシュ・メモリ・ブロック 1110 によって割り当てることができ、さらなる復号および処理のためにインターフェース 1115 を介してフラッシュ制御システム 1120 に転送される。例示的なフラッシュ制御システム 1120 は、下で図 12A および 12B に関連してさらに述べる軟デマッパ / 軟データ・ジェネレータ 1200 と、下で図 13 ~ 14 に関連してさらに述べるデコーダ 1400 とを含む。デコーダ 1400 は、たとえば、確率伝搬、メッセージ・パッシング、Sum-Product、または Min-Sum アルゴリズムなど、LDPC 復号アルゴリズムを使用して実施することができる。

【0056】

図 11 に示されているように、軟デマッパ / 軟データ・ジェネレータ 1200 によって生成される軟情報を、オプションで、軟デマッパ / 軟データ・ジェネレータ 1200 とデコーダ 1400 との間の反復的なデマッピングおよび復号に使用することができる。一般に、図 11 に示されているように、軟デマッパ / 軟データ・ジェネレータ 1200 は、下の「読み取り統計を使用する軟データ (LLR) の計算」という題名のセクションで述べるように、LLR の形の軟情報  $L_e$  を生成する。当初に、軟デマッパ / 軟データ・ジェネレータ 1200 によって計算された LLR、 $L_e$  は、フラッシュ・メモリ 1100 からの軟読み出または硬読み出（あるいはその両方）および対応する統計に基づく。LLR、 $L_e$  は、デコーダ 1400 によって処理されて、新しい軟情報  $L_a$  を生成し、この軟情報  $L_a$  は、反復プロセスが最終判断に収束するまで、反復的な形で軟デマッパ / 軟データ・ジェネレータ 1200 にフィード・バックされる。

【0057】

軟デマッパ / 軟データ・ジェネレータ 1200

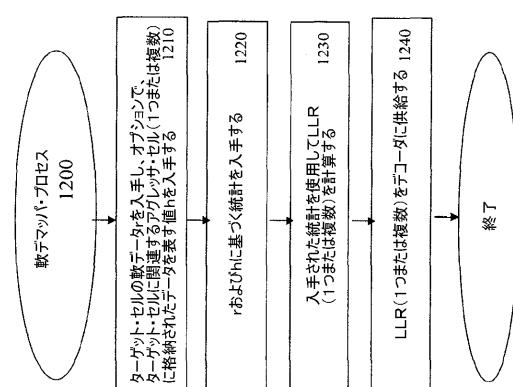

図 12A は、フラッシュ・メモリ 810、910 によって供給される軟データから質を高めた軟データを生成するために本発明の特徴を組み込んだ例示的な軟デマッピング・プロセス 1200 を説明する流れ図である。図 12A に示されているように、例示的な軟デマッピング・プロセス 1200 は、当初に、ステップ 1210 中にターゲット・セルの軟データ  $r$  をフラッシュ・メモリ 810、910 から入手し、オプションで、ターゲット・セルに関連するアグレッサ・セル（1つまたは複数）に格納されたデータを表す 1 つまたは複数の値  $h$  を入手する。

【0058】

その後、軟デマッピング・プロセス 1200 は、ステップ 1220 中に、1 つまたは複数の確率密度関数など、 $r$  およびオプションで  $h$  に基づく統計（または確率）を入手する。この統計は、下の「統計の収集」という題名のセクションでさらに述べる。

【0059】

その後、ステップ 1230 中に、入手された統計を使用して LLR（1 つまたは複数）を計算する。LLR（1 つまたは複数）は、下の「読み取り統計を使用する軟データ (LLR) の計算」という題名のセクションで述べる。その後、ステップ 1240 中に、計算された LLR をデコーダ 1400 に供給し、あるいはオプションでデインターリーバに供給する。計算された LLR を、オプションで、たとえば LLR の符号に基づいて、読み取りデータに対する最終判断を行うのに使用することができる。

10

20

30

40

50

## 【0060】

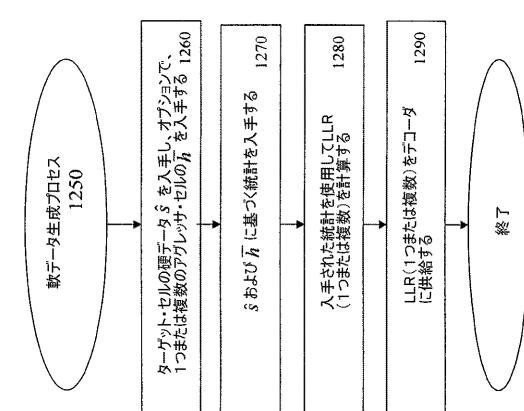

図12Bは、フラッシュ・メモリ810、910によって供給される硬データから軟データを生成するために本発明の特徴を組み込んだ例示的な軟データ生成プロセス1250を説明する流れ図である。図12Bに示されているように、例示的な軟データ生成プロセス1250は、当初に、ステップ1260中にターゲット・セルの硬データ

## 【数1】

$$\hat{s}$$

(以下、「 $s^{\wedge}$ 」と表記。他の変数についても同)をフラッシュ・メモリ810、910から入手し、オプションで、ターゲット・セルに関連するアグレッサ・セル(1つまたは複数)に格納されたデータを表す1つまたは複数の値

10

## 【数2】

$$\bar{h}$$

(以下、単に「 $h^-$ 」と表記。他の変数についても同)を入手する。硬データ $s^{\wedge}$ は、たとえば、フラッシュ・メモリ810、910によって各セルに割り当てられた2進ビットまたはレベルとすることができます。

## 【0061】

セル内の1ビットのLLRを計算するために、他のビットは使用不能であり、セル内他のビットは、たとえば、ページ・アクセス技法およびワード線アクセス技法を使用して読み取られる。例示的なページ・レベル・アクセス技法およびワード線レベル・アクセス技法のより詳細な議論については、たとえば、参照によって本明細書に組み込まれている2009年3月11日に出願した国際出願第PCT/US09/36810号、名称「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding」を参照されたい。ページ・アクセス技法を用いると、そのLLRが計算されようとしているページが読み取られ、オプションで、同ワード線内の他のページをも読み取ることができ、その結果、硬データをセルのレベル $s^{\wedge}$ にマッピングできるようになる。ワード線アクセス技法を用いると、ワード線全体を読み取って、セル内のすべてのビットを入手することができ、これらのビットから、硬データ・レベル $s^{\wedge}$ が入手される。

20

## 【0062】

たとえば、アグレッサ・セル720(または、アグレッサ・セル720が格納されているページもしくはワード線)からビットを読み出すことによって、パターン $h^-$ が入手される。アグレッサ・セルを読み出す技法のより詳細な議論については、たとえば、参照によって本明細書に組み込まれている国際出願第PCT/US09/49326号、名称「Methods and Apparatus for Read-Side Inter-cell Interference Mitigation in Flash Memories」を参照されたい。

30

## 【0063】

次に、軟データ生成プロセス1250は、ステップ1270中に、1つまたは複数の確率密度関数など、 $s^{\wedge}$ およびオプションで $h^-$ に基づく統計(または確率)を入手する。この統計は、下の「統計の収集」という題名のセクションでさらに述べるように、ビット・ベースの確率またはセル・ベースの確率とすることもできる。軟読取値の分布のガウス近似が使用されるときには、この統計は、ガウス近似式について「読取統計を使用する軟データ(LLR)の計算」という題名のセクションで述べるように、分布の平均値または分散を含む。平均値および分散は、たとえば、プログラム/消去サイクル、読取サイクル、および温度などの異なる性能要因についてフラッシュ・メモリ・チップの特性試験中に事前計算し、テーブルに格納することができる。平均値および分散を、性能要因に基づき

40

50

、オプションで、アグレッサ・セル 720 に格納されたパターン  $h^-$  にも基づいて、テーブルから入手することができる。

【0064】

次に、ステップ 1280 中に、入手された統計を使用して、LLR (1つまたは複数) を計算する。LLR (1つまたは複数) は、下の「読み取り統計を使用する軟データ (LLR) の計算」という題名のセクションで述べる。「読み取り統計を使用する軟データ (LLR) の計算」という題名のセクションで説明するように、統計に加えてまたはその代わりに、デコーダによって供給される先駆的 LLR  $L_a$  をオプションで使用して、LLR を計算できることに留意されたい。セル内のビットの LLR が計算される時に、先駆的 LLR  $L_a$  は、セル内の少なくとも 1 つのビット (オプションで他のすべてのビット) に使用される。これは、セル内のこれらの他のビットが読み取られており、先駆的 LLR  $L_a$  がデコーダによってそれらについて計算済みであることを必要とする。 10

【0065】

その後、ステップ 1290 中に、計算された LLR がデコーダ 1400 に供給され、あるいはオプションでデインターリーバに供給される。計算された LLR を、オプションで、たとえば LLR の符号に基づいて、読み取りデータに対する最終判断を行うのに使用することができる。セル内のすべてのビット (またはワード線内のすべてのページ) を、2009 年 3 月 11 日に出願した国際出願第 PCT/US09/36810 号、名称「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding」に記載されているように共同で符号化し、復号することができることに留意されたい。別の実施形態では、セル内のビット (またはワード線内のすべてのページ) を、やはり国際出願第 PCT/US09/36810 号に記載されているように、別々に符号化し、復号することができる。 20

【0066】

デコーダ 1400 LDPC 実施態様

LDPC 符号および LDPC 復号の次の背景の議論は、参照によって本明細書に組み込まれている、A. J. Blanksby および C. J. Howland、「A 690-mW 1-Gb/s 1024-b, Rate-1/2 Low-Density Parity-Check Decoder」、IEEE J. Solid-State Circuits、Vol. 37、404~412 頁 (2002 年 3 月) の議論に基づく。より詳細な議論について、読者は、Blanksby および Howland の論文全体を参照されたい。 30

【0067】

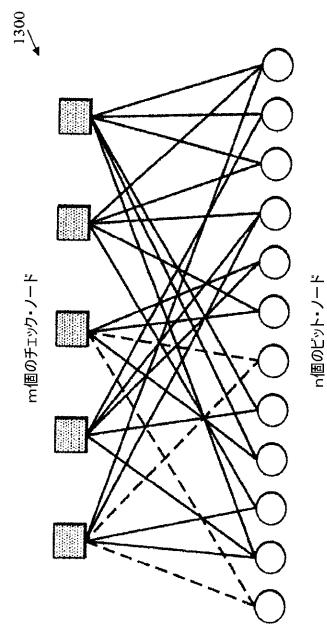

LDPC 符号のグラフ表現

LDPC 符号を、2 部グラフを使用して表すことができ、2 部グラフでは、ノードの一方の集合は、パリティ検査制約を表し、他方の集合は、データ・ビットを表す。図 13 は、LDPC 符号の例示的な 2 部グラフ表現 1300 を示す図である。パリティ検査行列は、グラフの結合行列であり、ここで、H の列  $i$  に対応するビット・ノード  $i$  は、H の項目  $h_{j,i}$  がセットされているすなわち非 0 である場合に、H の行  $j$  に対応するチェック・ノード  $j$  に接続される。 40

【0068】

LDPC 符号を復号するのに使用される 1 つのアルゴリズムが、sum-product アルゴリズムとして知られている。このアルゴリズムを用いる良い復号性能のためには、LDPC 符号のグラフ表現内のサイクルの長さが、できる限り長いことが重要である。図 13 の例示的な表現では、長さ 4 の例示的な短いサイクルが図示されている。図 13 に示された長さ 4 のサイクルなどの短いサイクルは、sum-product アルゴリズムの性能を劣化させる。LDPC 符号を復号する別の周知のアルゴリズムが、min-sum アルゴリズムである。 50

## 【0069】

Sum-Productアルゴリズム

sum-productアルゴリズムは、LDPC符号を復号するための反復アルゴリズムである。sum-productアルゴリズムは、メッセージ・パッシング・アルゴリズムまたは確率伝搬としても知られている。sum-productアルゴリズムのより詳細な議論については、たとえば、それぞれ参照によって本明細書に組み込まれている、A. J. BlanksbyおよびC. J. Howland、「A 690-mW 1-Gb/s 1024-b, Rate-1/2 Low-Density Parity-Check Decoder」、IEEE J. Solid-State Circuits, Vol. 37, 404~412頁(2002年3月)、D. E. Hocevar、「LDPC Code Construction With Flexible Hardware Implementation」、IEEE Int'l Conf. on Comm. (ICC)、米国アラスカ州アンカレッジ、2708~2712頁(2003年5月)、ならびにR. N. S. Ratnayake、E. F. Haratsch、およびGu-Yeon Wei、「A Bit-node centric architecture for low-density parity check decoders」、IEEE Global Telecommunications Conference (Globecom)、米国コロンビア特別区ワシントン、265~270頁(2007年11月)を参照されたい。

## 【0070】

ビット・ノード*i*からチェック・ノード*j*へのメッセージ $Q_{i,j}$ は、

## 【数3】

$$Q_{i,j} = \sum_{l \in B_i, l \neq j} R_{l,i} + L_{e,i}$$

によって与えられ、ここで、 $L_{e,i}$ は、ビット*i*の軟デマッパノード・データ・ジェネレータによって供給される外来LLRである。チェック・ノード*j*からビット・ノード*i*へのメッセージ $R_{j,i}$ は、

## 【数4】

$$R_{j,i} = s_{j,i} \cdot \phi \left( \sum_{l \in C_j, l \neq i} \phi(|Q_{l,j}|) \right)$$

によって与えられ、ここで、

## 【数5】

$$s_{j,i} = \prod_{l \in C_j, l \neq i} \text{sign}(Q_{l,j})$$

かつ

## 【数6】

$$\phi(x) = -\log \tanh(x/2) = \log \frac{e^x + 1}{e^x - 1}$$

である。ビット*i*の帰納的対数尤度比(LLR)とも呼ばれる帰納的情報値 $l_i$ は、

10

20

30

40

【数7】

$$\Lambda_i = \sum_{l \in B_i} R_{l,i} + L_{e,i}$$

によって与えられる。

【0071】

反復的なデマッピングおよび復号のために軟デマッパー/軟データ・ジェネレータに供給されるビット*i*のLLR  $L_{a,i}$ は、

【数8】

10

$$L_{e,i} = \sum_{l \in B_i} R_{l,i}$$

として与えられ、ここで、 $B_i$ は、ビット・ノード*i*に接続されたチェック・ノードの集合であり、 $C_j$ は、チェック・ノード*j*に接続されたビット・ノードの集合である。

【0072】

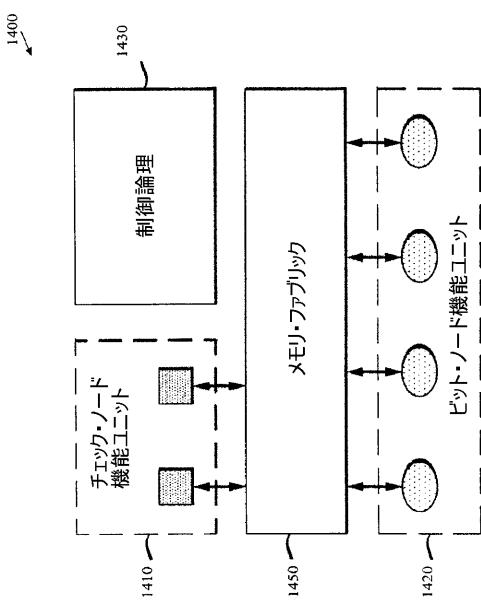

LDPCデコーダ ハードウェア共有デコーダ・アーキテクチャ

LDPC符号を復号するsum-productアルゴリズムを実施する時の重要な課題は、メッセージの受渡しを管理することである。チェック・ノードとビット・ノードとの両方の機能性が、比較的単純なので、そのそれぞれの実現は、少数のゲートだけを用いる。主な問題は、機能ノードの間のメッセージの受渡しに必要な帯域幅の実施である。

20

【0073】

図14は、例示的なハードウェア共有LDPCデコーダ・アーキテクチャ1400のブロック図である。図14に示されているように、一般化されたLDPCデコーダ・アーキテクチャ1400は、それぞれチェック・ノード機能性またはビット・ノード機能性のいずれかを実施する複数の機能ユニット1410、1420と、メッセージを格納し、グラフ接続性を実現するメモリ・ファブリック1450とを含む。制御論理1430は、メモリ・ファブリック1450の構成を制御する。ハードウェア共有LDPCデコーダ・アーキテクチャ1400の実施態様の詳細な議論については、たとえば、E. Yeo他、「VLSI Architectures for Iterative Decoders in Magnetic Recording Channels」、IEEE Trans. On Magnetics、Vol. 37、No. 2、748~755頁(2001年3月)を参照されたい。

30

【0074】

そのようなハードウェア共有アーキテクチャが、デコーダの面積を減らすことが認められている。

【0075】

40

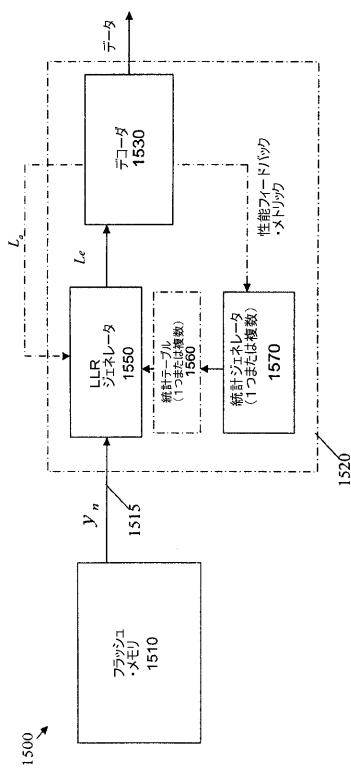

図15に、本発明の一実施形態による軟データ生成を用いる例示的なフラッシュ・メモリ・システム1500を示す。図15に示されているように、例示的なフラッシュ・メモリ・システム1500は、フラッシュ・メモリ・ブロック1510を含む。後で述べるように、硬データ値または軟データ値(あるいはその両方)は、通常、フラッシュ・メモリ・ブロック1510によって割り当てられ、さらなる復号および処理のためにインターフェース1515を介してフラッシュ制御システム1520に転送される。例示的なフラッシュ制御システム1520は、下で図16に関連してさらに述べるLLRジェネレータ1550、下の「統計の収集」という題名のセクションでさらに述べる統計ジェネレータ(1つまたは複数)1570、およびデコーダ1530を含む。統計ジェネレータ(1つまたは複数)1570によって生成される統計は、オプションで、下でたとえば図17Aから17Cおよび18に関連してさらに述べる1つまたは複数の統計テーブル1560に記録され、あるいはその代わりに、リアルタイムで生成され得る。

【0076】

50

統計ジェネレータ（1つまたは複数）1570によって生成された統計は、LLRジェネレータ1550によって使用されて、たとえばLLR、 $L_e$ の形の軟データを生成する。当初に、LLR、 $L_e$ は、フラッシュ・メモリ1510からの軟読出または硬読出（あるいはその両方）および対応する統計に基づく。LLR、 $L_e$ は、デコーダ1530によって処理されて、新しい軟情報 $L_a$ を生成し、この軟情報 $L_a$ は、反復プロセスが最終判断に収束するまで、反復的な形でLLRジェネレータ1550にフィード・バックされる。

#### 【0077】

デコーダ1530は、やはり、たとえば確率伝搬、メッセージ・パッシング、Sum-Product、またはMin-SumアルゴリズムなどのLDPC復号アルゴリズムを使用して実施することができる。本明細書で説明される統計ジェネレータ1570およびLLRジェネレータ1550の機能を、フラッシュ制御システム1520、デコーダ1530、および読み取りチャネル825（たとえば、図8を参照されたい）のうちの1つまたは複数で実施できることに留意されたい。

#### 【0078】

読み取り統計を使用する軟データ（LLR）の計算

ビットcの先驗的対数尤度比（LLR） $L_a$ は、次のように定義することができる。

#### 【数9】

$$L_a(c) = \log \frac{P(c=0)}{P(c=1)}$$

10

20

ここで、 $P(\cdot \cdot \cdot)$ は確率である。

#### 【0079】

同様に、フラッシュ出力rに対して条件付けられたビットcのLLRは、次のように計算される。

#### 【数10】

$$\begin{aligned} L(c|r) &= \log \frac{P(c=0|r)}{P(c=1|r)} = \log \frac{P(c=0)}{P(c=1)} + \log \frac{p(r|c=0)}{p(r|c=1)} \\ &= L_a(c) + L_e(c) \end{aligned}$$

30

ここで、 $L_e(c)$ は、後続デコーダに渡される外来LLRまたは軟情報であり、 $p(\cdot \cdot \cdot)$ は、確率密度関数（PDF）である。

#### 【0080】

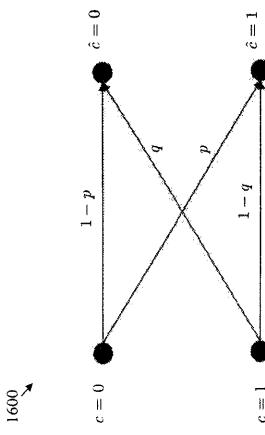

図16は、例示的な2進チャネルの誤り確率pおよびqを示すトレリス1600である。2進チャネルの文脈で、pが誤り確率を表し、そうでない場合に、p(...)が確率密度関数を表すことに留意されたい。p=qの場合には、この2進チャネルは非対称である。p=qの場合には、この2進チャネルは対称である。図16に示されているように、pは、2進0の誤り確率（すなわち、0が書き込まれた時に1を読み取る確率）である。同様に、qは、2進1の誤り確率（すなわち、1が書き込まれた時に0を読み取る確率）である。2進0を正しく読み取る確率（すなわち、0が書き込まれた時に0を読み取る確率）は、1-pとして表すことができる。同様に、2進1を正しく読み取る確率（すなわち、1が書き込まれた時に1を読み取る確率）は、1-qとして表すことができる。

40

#### 【0081】

2進非対称チャネルの外来LLR

トレリス1600によって定義される2進非対称チャネルのビットcの外来LLR、 $L_e(c)$ は、次のように表すことができる。

【数11】

$$L_e(c) = \log \frac{P(\hat{c} | c = 0)}{P(\hat{c} | c = 1)}$$

【0082】

読み取ビット  $c \wedge = 0$  の外来 LLR、 $L_e(c)$  は、

【数12】

$$L_e(c) = \log \frac{P(\hat{c} = 0 | c = 0)}{P(\hat{c} = 0 | c = 1)} = \log \frac{1-p}{q}$$

として計算される。

【0083】

読み取ビット  $c \wedge = 1$  の外来 LLR、 $L_e(c)$  は、

【数13】

$$L_e(c) = \log \frac{P(\hat{c} = 1 | c = 0)}{P(\hat{c} = 1 | c = 1)} = \log \frac{p}{1-q}$$

として計算される。

【0084】

2進対称チャネルの外来 LLR (ただし、 $p = q = p_0$ )読み取ビット  $c \wedge = 0$  の外来 LLR、 $L_e(c)$  は、

【数14】

$$L_e(c) = \log \frac{P(\hat{c} = 0 | c = 0)}{P(\hat{c} = 0 | c = 1)} = \log \frac{1-p_0}{p_0}$$

として計算される。

【0085】

読み取ビット  $c \wedge = 1$  の外来 LLR、 $L_e(c)$  は、

【数15】

$$L_e(c) = \log \frac{P(\hat{c} = 1 | c = 0)}{P(\hat{c} = 1 | c = 1)} = \log \frac{p_0}{1-p_0}$$

として計算される。

【0086】

フラッシュ・メモリからの軟出力の外来 LLR

2ビット/セル・フラッシュ・メモリについて、外来 LLR を、フラッシュ・メモリ 8 40

10、910 から受け取られる軟値  $r$  について、次のように計算することができる。

## 【数16】

$$\begin{aligned}

L_e(c_0) &= \log \frac{p(r | c_0 = 0)}{p(r | c_0 = 1)} = \log \frac{P(c_0 = 0)}{P(c_0 = 1)} \cdot \frac{P(c_0 = 0, c_1 = 0 | r) + P(c_0 = 0, c_1 = 1 | r)}{P(c_0 = 1, c_1 = 0 | r) + P(c_0 = 1, c_1 = 1 | r)} \\

&= \log \frac{p(r | c_0 = 0, c_1 = 0) + \frac{P(c_1 = 1)}{P(c_1 = 0)} p(r | c_0 = 0, c_1 = 1)}{p(r | c_0 = 1, c_1 = 0) + \frac{P(c_1 = 1)}{P(c_1 = 0)} p(r | c_0 = 1, c_1 = 1)} \\

&= \log \frac{p(r | c_0 = 0, c_1 = 0) + \exp(-L_a(c_1)) \cdot p(r | c_0 = 0, c_1 = 1)}{p(r | c_0 = 1, c_1 = 0) + \exp(-L_a(c_1)) \cdot p(r | c_0 = 1, c_1 = 1)}

\end{aligned}$$

10

## 【0087】

一般に、セルあたりの任意のビット数について、ビット  $C_i$  の外来  $L L R$  は、

## 【数17】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} p(r | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} p(r | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

20

と表すことができ、ここで、

$r$  : 受け取られた信号

$s$  : 格納されたビット ( $c_0, c_1, \dots, c_m$ ) によって与えられるオリジナルの格納された状態またはレベル

$c_i$  : 符号化されたビット

$m$  : セルあたりのビット数

## 【数18】

$$L_a(C_i) = \log \frac{P(C_i = 0)}{P(C_i = 1)} \quad : \text{先驗的 } L L R$$

30

$L_e(C_i)$  : 外来  $L L R$

$c_i$  : そのビット・ラベルが位置  $i$  で値  $C_i = c_i$  を有する状態またはレベルの部分集合であり、ここで、 $L_a(C_i)$  は、たとえば LDPC デコーダ 1090 または 1400 などのデコーダによって供給される。最初の反復では、 $L_a(C_i)$  を 0 に初期化することができる。

## 【0088】

次の等値性

## 【数19】

$$p(r | s) = \frac{p(r)}{P(s)} \cdot P(s | r)$$

40

を使用すると、外来  $L L R$  の式を、次のように書くこともできる。

【数20】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \frac{P(s | r)}{P(s)} \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} \frac{P(s | r)}{P(s)} \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

【0089】

この式を、

【数21】

10

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} P(s | r) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} P(s | r) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

にさらに単純化することができる。

【0090】

この式は、数学的には、すべての状態またはレベルが同様にありそうである場合の上の式と同等である。

【0091】

20

フラッシュ・メモリからの軟出力のパターン依存外来 L L R

フラッシュ・メモリ 810、910 から受け取られる、ターゲット・セルの 1 つまたは複数の軟値  $r$  およびアグレッサ・セル (1 つまたは複数) の 1 つまたは複数の値  $h^-$  について、

【数22】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} p(r, \bar{h} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} p(r, \bar{h} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

30

であることを示すことができ、ここで、 $h^-$  は、ターゲット・セルに対する外乱を引き起こす周囲のセル (1 つまたは複数) または他のセル内に格納されたデータ・パターンである。たとえば、

【数23】

$$\bar{h} = (h^{k \pm 1, l}, h^{k, l \pm 1}, h^{k \pm 1, l \pm 1})$$

は、L L R が計算されようとしている位置 (k, l) のターゲット・セルに近接するすべてのアグレッサ・セルを表す。

【0092】

40

パターン  $h^-$  を、たとえばアグレッサ・セルから硬データを読み出すことによって入手することができる。

【0093】

外来 L L R の式を、次のように書くこともできる。

【数24】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \frac{P(s | r, \bar{h})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} \frac{P(s | r, \bar{h})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

【0094】

この式を、

【数25】

10

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} P(s | r, \bar{h}) \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} P(s | r, \bar{h}) \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

にさらに単純化することができる。

【0095】

この式は、数学的に、すべての状態が同等にありそうである場合に上の式と同等である。

【0096】

20

フラッシュ・メモリからの硬出力の外来LLR

軟出力がフラッシュ・メモリから使用可能ではなく、フラッシュ・メモリが、フラッシュ・メモリによって格納されたデータに割り当てられた状態またはレベルである硬データ  $s^{\wedge}$  だけを供給するときには、外来LLRを、

【数26】

$$\begin{aligned} L_e(C_i) &\approx \log \frac{\sum_{s \in \chi_0^i} p(E\{r | \hat{s}\} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} p(E\{r | \hat{s}\} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \\ &\approx \log \frac{\sum_{s \in \chi_0^i} P(\hat{s} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} P(\hat{s} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \end{aligned}$$

30

として計算することができ、ここで、 $E\{r | s^{\wedge}\}$  は、軟値  $r$  (電圧など) の期待値または硬値  $s^{\wedge}$  を仮定する軟値  $r$  に関する他の推定値である。 $P(s^{\wedge} | s)$  は、状態またはレベル  $s$  が最初に書き込まれ格納されたと仮定して、硬値 (状態またはレベルなど)  $s^{\wedge}$  が読み取られる確率である。

【0097】

外来LLRを、その代わりに

40

【数27】

$$\begin{aligned}

L_e(C_i) &\approx \log \frac{\sum_{s \in \chi_0^i} \frac{P(s | E\{r | \hat{s}\})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} \frac{P(s | E\{r | \hat{s}\})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \\

&\approx \frac{\sum_{s \in \chi_0^i} \frac{P(s | \hat{s})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} \frac{P(s | \hat{s})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \quad 10 \\

&\approx \frac{\sum_{s \in \chi_0^i} P(s | \hat{s}) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} P(s | \hat{s}) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}

\end{aligned}$$

として計算することができ、ここで、 $P(s | s^{\wedge})$ は、硬値（状態またはレベル） $s^{\wedge}$ が読み取られると仮定して、状態またはレベル $s$ が最初に書き込まれるか格納された確率である。

【0098】

20

フラッシュ・メモリからの硬出力のパターン依存外来 L L R

軟出力がフラッシュ・メモリから使用可能ではなく、フラッシュ・メモリが、フラッシュ・メモリによって格納されたデータに割り当てられた状態またはレベルである硬データ $s^{\wedge}$ だけを供給するときには、外来 L L Rを、アグレッサ・セルに格納されたパターン $h^-$ に基づいて計算することができ、

【数28】

$$\begin{aligned}

L_e(C_i) &\approx \log \frac{\sum_{s \in \chi_0^i} p(E\{r | \hat{s}, \bar{h}\}, \bar{h} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} p(E\{r | \hat{s}, \bar{h}\}, \bar{h} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \quad 30 \\

&\approx \log \frac{\sum_{s \in \chi_0^i} P(\hat{s}, \bar{h} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} P(\hat{s}, \bar{h} | s) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}

\end{aligned}$$

ここで、 $P(s^{\wedge}, h^- | s)$ は、状態またはレベル $s$ が最初に書き込まれ格納されたと仮定して、硬値（状態またはレベル） $s^{\wedge}$ が読み取られ、アグレッサ・セル内のパターンが $h^-$ である確率である。 $h^-$ は、ターゲット・セルに対する外乱を引き起こす周囲のセル（1つまたは複数）または他のセルに格納されたデータ・パターンである。たとえば、

【数29】

40

$$\bar{h} = (h^{k \pm 1, l}, h^{k, l \pm 1}, h^{k \pm 1, l \pm 1})$$

は、その L L R が計算されようとしている位置 (k, l) のターゲット・セルに近接するすべてのアグレッサ・セルを表す。

【0099】

パターン $h^-$ を、たとえばアグレッサ・セルからの硬データを読み出すことによって入手することができる。

【0100】

パターン依存 L L R を、その代わりに

50

## 【数30】

$$\begin{aligned}

L_e(C_i) &\approx \log \frac{\sum_{s \in \chi_0^i} \frac{P(s | E\{r | \hat{s}, \bar{h}\}, \bar{h})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} \frac{P(s | E\{r | \hat{s}, \bar{h}\}, \bar{h})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \\

&\approx \frac{\sum_{s \in \chi_0^i} \frac{P(s | \hat{s}, \bar{h})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} \frac{P(s | \hat{s}, \bar{h})}{P(s)} \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \\

&\approx \frac{\sum_{s \in \chi_0^i} P(s | \hat{s}, \bar{h}) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} P(s | \hat{s}, \bar{h}) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)} \quad 10

\end{aligned}$$

として計算することができ、ここで、 $P(s | s^{\wedge}, h^-)$ は、硬値（状態またはレベルなど） $s^{\wedge}$ が読み取られ、アグレッサ・セル内のパターンが $h^-$ であると仮定して、状態またはレベル $s$ が最初に書き込まれたか格納された確率である。

## 【0101】

フラッシュからの軟出力の軟デコーダ・フィードバックなしの外来LLR

20

デコーダからの軟出力が、軟デマッパ／軟データ・ジェネレータ内で使用されない（言い換えると、 $L_a(C_i) = 0$ ）であるときには、軟デマッパ／軟データ・ジェネレータ内の外来LLRを、次のように計算することができる。

## 【数31】

$$\begin{aligned}

L_e(C_i) &= \log \frac{\sum_{s \in \chi_0^i} p(r | s)}{\sum_{s \in \chi_1^i} p(r | s)} \\

L_e(C_i) &= \log \frac{\sum_{s \in \chi_0^i} \frac{P(s | r)}{P(s)}}{\sum_{s \in \chi_1^i} \frac{P(s | r)}{P(s)}} \approx \log \frac{\sum_{s \in \chi_0^i} P(s | r)}{\sum_{s \in \chi_1^i} P(s | r)} \quad 30

\end{aligned}$$

## 【0102】

これらの外来LLRは、その後、図10および11に示されたデコーダに渡される。次に、LDPCは、たとえばデータ・ビットが復号されるまでデコーダの内部の局所反復のためにメッセージ渡し復号アルゴリズムを適用することができる。この場合に、軟デマッパ／軟データ・ジェネレータの大域検出／復号反復は、全体的な計算の複雑さを下げるために、実行されない。

## 【0103】

パターン依存LLRを、この場合には次のように計算することができる。

40

## 【数32】

$$L_e(C_i) = \log \frac{\sum_{s \in X_0^i} p(r, \bar{h} | s)}{\sum_{s \in X_1^i} p(r, \bar{h} | s)}$$

$$L_e(C_i) = \log \frac{\sum_{s \in X_0^i} \frac{P(s | r, \bar{h})}{P(s)}}{\sum_{s \in X_1^i} \frac{P(s | r, \bar{h})}{P(s)}} \approx \log \frac{\sum_{s \in X_0^i} P(s | r, \bar{h})}{\sum_{s \in X_1^i} P(s | r, \bar{h})} \quad 10$$

## 【0104】

フラッシュからの硬出力の軟デコーダ・フィードバックなしの外来LLR

軟データがフラッシュ・メモリから使用可能ではなく、デコーダからの軟出力が、計算の複雑さを減らすのに使用される場合には、外来LLRを次のように計算することができる。

## 【数33】

$$L_e(C_i) \approx \log \frac{\sum_{s \in X_0^i} p(E\{r | \hat{s}\} | s)}{\sum_{s \in X_1^i} p(E\{r | \hat{s}\} | s)} \quad 20$$

$$\approx \log \frac{\sum_{s \in X_0^i} P(\hat{s} | s)}{\sum_{s \in X_1^i} P(\hat{s} | s)}$$

ここで、 $E\{r | s^{\wedge}\}$ は、軟値 $r$ （電圧など）の期待値または硬値 $s^{\wedge}$ を仮定する軟値 $r$ のある他の推定値である。 $P(s^{\wedge} | s)$ は、状態またはレベル $s$ が最初に書き込まれ格納されたと仮定して、硬値（状態またはレベルなど） $s^{\wedge}$ が読み取られる確率である。

## 【0105】

代替実施態様では、LLRを

## 【数34】

$$L_e(C_i) \approx \log \frac{\sum_{s \in X_0^i} \frac{P(s | E\{r | \hat{s}\})}{P(s)}}{\sum_{s \in X_1^i} \frac{P(s | E\{r | \hat{s}\})}{P(s)}} \quad 30$$

$$\approx \frac{\sum_{s \in X_0^i} \frac{P(s | \hat{s})}{P(s)}}{\sum_{s \in X_1^i} \frac{P(s | \hat{s})}{P(s)}} \quad 40$$

$$\approx \frac{\sum_{s \in X_0^i} P(s | \hat{s})}{\sum_{s \in X_1^i} P(s | \hat{s})}$$

として計算することができ、ここで、 $P(s | s^{\wedge})$ は、硬値（状態またはレベルなど） $s^{\wedge}$ が読み取られると仮定して、状態またはレベル $s$ が最初に書き込まれるか格納された確率である。

## 【0106】

パターン依存LLRは、この場合に、次のように計算することができる。

【数35】

$$L_e(C_i) \approx \log \frac{\sum_{s \in X_0^i} P(\hat{s}, \bar{h} | s)}{\sum_{s \in X_1^i} P(\hat{s}, \bar{h} | s)}$$

$$L_e(C_i) \approx \frac{\sum_{s \in X_0^i} \frac{P(s | \hat{s}, \bar{h})}{P(s)}}{\sum_{s \in X_1^i} \frac{P(s | \hat{s}, \bar{h})}{P(s)}},$$

$$\approx \frac{\sum_{s \in X_0^i} P(s | \hat{s}, \bar{h})}{\sum_{s \in X_1^i} P(s | \hat{s}, \bar{h})}$$

10

【0107】

フラッシュからの軟出力の外来 L L R のガウス近似

フラッシュ・メモリからの軟出力（読み取りしきい電圧など）が、ガウス分布を有してモデル化される場合には、最初に格納されたか書き込まれたレベル  $s$  を仮定した軟出力  $p(r | s)$  の条件 PDF  $p(r | s)$  を

20

【数36】

$$p(r | s) = \frac{1}{\sqrt{2\pi}\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2}(r - E\{r | s\})^2\right)$$

と表すことができ、ここで、 $\sigma(s)$  は、標準偏差であり、 $E\{r | s\}$  は、状態  $s$  の軟出力（しきい電圧など）の平均値または期待値である。

【0108】

すると、外来 L L R を

【数37】

30

$$L_e(C_i) = \log \frac{\sum_{s \in X_0^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2}(r - E\{r | s\})^2\right) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in X_1^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2}(r - E\{r | s\})^2\right) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

$$= \log \frac{\sum_{s \in X_0^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2}(r - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}{\sum_{s \in X_1^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2}(r - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}$$

40

として計算することができる。

【0109】

すべての状態の電圧分布が同一の標準偏差  $\sigma(s) = \sigma$  を有する場合には、この式を次の式に単純化することができる。

【数38】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \exp\left(-\frac{1}{2\sigma^2} (r - E\{r | s\})^2\right) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}{\sum_{s \in \chi_1^i} \exp\left(-\frac{1}{2\sigma^2} (r - E\{r | s\})^2\right) \cdot \prod_{j=1, j \neq i}^m \exp(-L_a(C_j) \cdot c_j)}$$

$$= \log \frac{\sum_{s \in \chi_0^i} \exp\left(-\frac{1}{2\sigma^2} (r - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}{\sum_{s \in \chi_1^i} \exp\left(-\frac{1}{2\sigma^2} (r - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}$$

10

【0110】

この式を、

【数39】

$$L_e(C_i) \approx \max_{s \in \chi_0^i} \left[ -\frac{1}{2\sigma^2} (r - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j \right] - \max_{s \in \chi_1^i} \left[ -\frac{1}{2\sigma^2} (r - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j \right]$$

20

にさらに単純化することができる。

【0111】

フラッシュからの硬出力の外來LLRのガウス近似

フラッシュ・メモリからの軟出力が使用可能ではないときには、LLRを、軟出力がガウス分布であると仮定して次のように計算することができ、

【数40】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2} (E\{r | \hat{s}\} - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}{\sum_{s \in \chi_1^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2} (E\{r | \hat{s}\} - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}$$

30

ここで、 $E\{r | s\}$ は、状態  $s$  に関する軟出力  $r$  (しきい電圧など) の平均値または期待値であり、 $E\{r | s^{\wedge}\}$  は、フラッシュ・メモリによって割り当てられ、供給される状態またはレベルである硬出力  $s^{\wedge}$  に関する軟出力  $r$  (しきい電圧など) の平均値または期待値である。

【0112】

すべての状態に関する電圧分布が、同一の標準偏差  $(s) =$  を有する場合には、この式を、次の式に単純化することができる。

【数41】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}{\sum_{s \in \chi_1^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}$$

40

【0113】

この式を、さらに

【数42】

$$L_e(C_i) \approx \max_{s \in \chi_0^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j \right]$$

$$- \max_{s \in \chi_1^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j \right]$$

に単純化することができる。

【0114】

フラッシュ・メモリからの硬出力のパターン依存外来LLRのガウス近似

硬出力のパターン依存LLRは、軟出力の分布がガウシアンとしてモデル化される場合に、次のように計算することができる。

【数43】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \frac{1}{\sigma(s, \bar{h})} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}{\sum_{s \in \chi_1^i} \frac{1}{\sigma(s, \bar{h})} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}$$

10

ここで、 $\bar{h}$  は、上で定義したように、アグレッサ・セルに格納されるパターンであり、 $(s, \bar{h})$  は、状態  $s$  およびパターン  $\bar{h}$  に関する軟出力の分布の標準偏差である。

【0115】

すべての状態およびパターンの電圧分布が、同一の標準偏差  $(s, \bar{h}) = \bar{h}$  を有する場合には、この式を次の式に単純化することができる。

【数44】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}{\sum_{s \in \chi_1^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j\right)}$$

20

【0116】

この式を、さらに

【数45】

$$L_e(C_i) \approx \max_{s \in \chi_0^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j \right]$$

$$- \max_{s \in \chi_1^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 - \sum_{j=1, j \neq i}^m L_a(C_j) \cdot c_j \right]$$

30

40

に単純化することができる。

【0117】

フラッシュ・メモリからの軟出力の軟デコーダ・フィードバックなしの外来LLRのガウス近似

軟デコーダ・フィードバックが使用されないときには、外来LLRを、フラッシュ・メモリからの軟出力が使用可能であるときの軟出力分布に関するガウス近似を使用して次のように計算することができる。

【数46】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2} (r - E\{r | s\})^2\right)}{\sum_{s \in \chi_1^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2} (r - E\{r | s\})^2\right)}$$

【0118】

すべての状態の電圧分布が同一の標準偏差  $(s) =$  を有する場合には、この式を、

次の式に単純化することができる。

【数47】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \exp\left(-\frac{1}{2\sigma^2} (r - E\{r | s\})^2\right)}{\sum_{s \in \chi_1^i} \exp\left(-\frac{1}{2\sigma^2} (r - E\{r | s\})^2\right)}$$

【0119】

この式を、さらに

【数48】

$$L_e(C_i) \approx \max_{s \in \chi_0^i} \left[ -\frac{1}{2\sigma^2} (r - E\{r | s\})^2 \right] - \max_{s \in \chi_1^i} \left[ -\frac{1}{2\sigma^2} (r - E\{r | s\})^2 \right]$$

に単純化することができる。

【0120】

フラッシュ・メモリからの硬出力の軟デコーダ・フィードバックなしの外来LLRのガウス近似

軟デコーダ・フィードバックが使用されないときには、外来LLRを、フラッシュ・メモリからの硬出力だけが使用可能であるときの軟出力分布のガウス近似を使用して次のように計算することができる。

【数49】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2} (E\{r | \hat{s}\} - E\{r | s\})^2\right)}{\sum_{s \in \chi_1^i} \frac{1}{\sigma(s)} \exp\left(-\frac{1}{2\sigma(s)^2} (E\{r | \hat{s}\} - E\{r | s\})^2\right)}$$

【0121】

すべての状態の電圧分布が同一の標準偏差  $(s) =$  を有する場合には、この式を、

次の式に単純化することができる。

【数50】

$$L_e(C_i) = \log \frac{\sum_{s \in \chi_0^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2\right)}{\sum_{s \in \chi_1^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2\right)}$$

【0122】

この式を、さらに

10

20

30

40

50

【数51】

$$L_e(C_i) \approx \max_{s \in X_0^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2 \right]$$

$$-\max_{s \in X_1^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}\} - E\{r | s\})^2 \right]$$

に単純化することができる。

【0123】

対応するパターン依存  $L_L R$  は、次のように計算される。

【数52】

$$L_e(C_i) = \log \frac{\sum_{s \in X_0^i} \frac{1}{\sigma(s, \bar{h})} \exp\left(-\frac{1}{2\sigma(s, \bar{h})^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2\right)}{\sum_{s \in X_1^i} \frac{1}{\sigma(s, \bar{h})} \exp\left(-\frac{1}{2\sigma(s, \bar{h})^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2\right)}$$

【0124】

すべての状態およびパターンの電圧分布が同一の標準偏差 ( $s, h^+$ ) を有する場合には、この式を次の式に単純化することができる。

【数53】

$$L_e(C_i) = \log \frac{\sum_{s \in X_0^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2\right)}{\sum_{s \in X_1^i} \exp\left(-\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2\right)}$$

【0125】

これを、さらに

【数54】

$$L_e(C_i) \approx \max_{s \in X_0^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 \right]$$

$$-\max_{s \in X_1^i} \left[ -\frac{1}{2\sigma^2} (E\{r | \hat{s}, \bar{h}\} - E\{r | s, \bar{h}\})^2 \right]$$

に単純化することができる。

【0126】

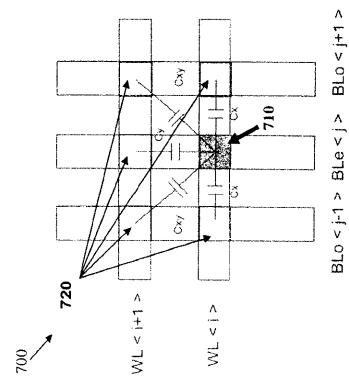

読取統計テーブル

図17A～17Cは、フラッシュ・メモリからのデータの読出に関する統計を記録する例示的なセル・ベースの統計テーブルである。図17Aは、(書込レベル ( $s$ ) および読取レベル ( $s^+$ )) の所与の対について、書込レベル ( $s$ ) が書き込まれたときに読取レベル ( $s^+$ ) が読み取られた回数を示す、例示的なセル・ベースの統計カウント・テーブル 1700 である。たとえば、書込レベル ( $s$ ) も 00 と等しいときに、読取レベル ( $s^+ = 00$ ) は、10617 回読み取られた。さらに、書込レベル ( $s$ ) が 01 と等しいときに、読取レベル ( $s^+ = 00$ ) は、誤って 148 回読み取られた。カウント・テーブル 1700 は、オプションで、各行および列の合計をも示す。カウント・テーブル 1700 内の値は、図21、23、25、および 28 に関連して下で述べる、複数のセル・ベース

10

20

30

40

50

の統計プロセスによって使用される。

【0127】

図17Bは、(書込レベル(s)および読み取レベル(s<sup>^</sup>))の所与の対について、読み取レベル(s<sup>^</sup>)が読み取られたという条件の下で書込レベル(s)が書き込まれた確率p(s|s<sup>^</sup>)を示す、例示的なセル・ベースの統計テーブルである。図17Cは、(書込レベル(s)および読み取レベル(s<sup>^</sup>))の所与の対について、書込レベル(s)が書き込まれたという条件の下で、読み取レベル(s<sup>^</sup>)が読み取られた確率p(s<sup>^</sup>|s)を示す、例示的なセル・ベースの統計テーブル1740である。

【0128】

図18は、所与のパターンの存在下でフラッシュ・メモリからのデータの読み出に関するパターン依存統計を記録する例示的なパターン依存セル・ベース統計テーブル1800である。例示的なテーブル1800は、(書込レベル(s)および読み取レベル(s<sup>^</sup>))の所与の対について、所与のパターンh<sup>-</sup>の存在下で、書込レベル(s)が書き込まれたという条件の下で、読み取レベル(s<sup>^</sup>)がパターンh<sup>-</sup>の存在下で読み取られた確率p(s<sup>^</sup>, h<sup>-</sup> | s)を示す。

【0129】

統計の収集

基準セルを使用する統計収集

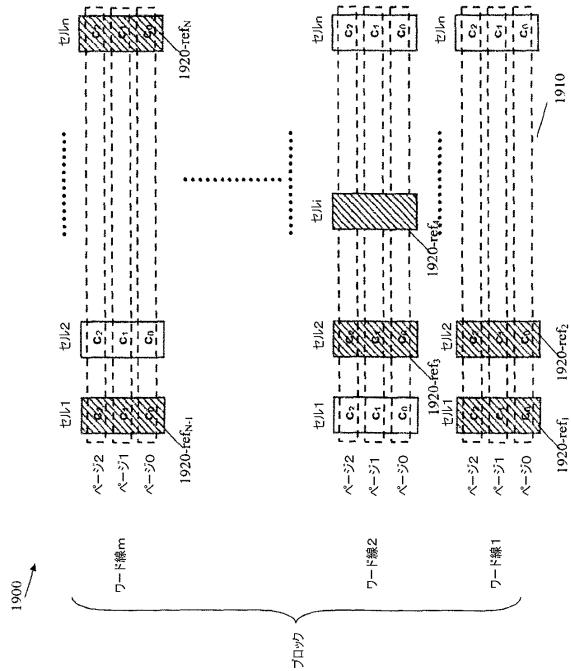

図19に、図3の例示的なフラッシュ・セル・アレイをさらに詳細に示す。図19に示されているように、例示的なフラッシュ・セル・アレイ1900は、すべての動作条件で信頼できるチャネル推定値または統計を提供するために複数の基準セル1920-refer<sub>1</sub>から1920-refer<sub>N</sub>(本明細書では集合的に基準セル1920と称する)を含む。

【0130】

例示的な基準セル1920は、図19では切り刻まれた背景を有して図示されている。基準セル1920を、既知のビット・パターンまたは既知の記号パターンなどの既知のパターンを使用して周期的にまたは間欠的にプログラムすることができる。基準セル1920を、任意の所望の形で、たとえば、各ワード線内の一貫したまた可変の個数のセルを使用して、フラッシュ・セル・アレイ1900の中で分散させることができることに留意されたい。基準セル1920の位置は、固定することができ、あるいは、たとえば使い古されたまたは損傷を受けたセルを回避するために、経時的に変更することができる。一実施態様では、基準セル1920の位置は、固定され、同一の基準セル1920の性能を、経時的に観察することができる。この固定位置実施態様では、基準セル1920を、オプションで、1回だけ書き込むことができ、あるいは、フラッシュ・メモリ・アレイ内の他のセルに匹敵する回数だけ書き込み、読み取ることができる。

【0131】

さらなる変形形態では、基準セル1920の位置は、基準セル1920の性能がアレイ1900全体の性能を反映するために、経時的に変更される。さらに別の変形形態では、統計を、複数の異なるアレイ1900内の基準セル1920から入手することができ、その後、結果は、平均をとられる。

【0132】

下でさらに述べるように、基準セル1920は、読み取られ、既知のパターンと比較される。たとえば、誤りを検出する確率p<sub>0</sub>の推定値を、次のように入手することができる。

【数55】

$$p_0 = \frac{\text{不正な読み出の個数}}{\text{基準セルの個数}}$$

基準セルのプログラミングおよび読み取を、オプションで、既知の形で、メモリにまたがつて消耗を拡散させるウェアレベル・アルゴリズムと組み合わせることができる。

10

20

30

40

50

## 【0133】

さまざまな実施形態では、基準セル1920は、すべての可能なレベルを格納することができ、周期的パターン（レベルが交番する場合）を有し、周期的に書き込まれまたは経時に読み取られるのいずれかとすることができます。

## 【0134】

後で述べるように、本発明のさまざまな実施形態は、ビット・ベースの統計、セル・ベースの統計、またはパターン依存統計を収集し、使用する。ビット・ベースの統計を使用する実施形態について、ビット誤り性能が測定される。セル・ベースの統計を使用する実施形態について、読み取統計が、セルを基礎として測定される。パターン依存統計について、読み取統計は、アグレッサ・セルに格納されたデータ・パターンをも説明する。

10

## 【0135】

## 1. 基準セルを使用するビット・ベースの統計

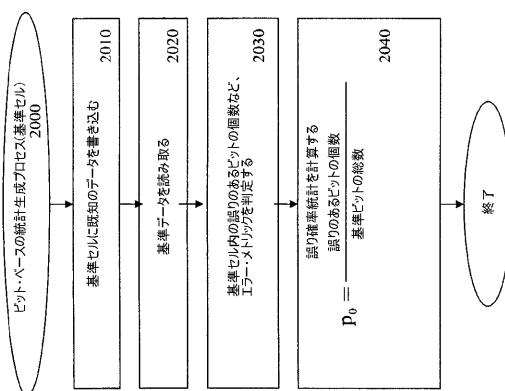

図20は、本発明の基準セル実施形態に関するビット・ベースの統計生成プロセス2000の例示的実施態様を説明する流れ図である。一般に、ビット・ベースの統計生成プロセス2000は、ビット誤りを検出する確率 $p_0$ を計算する。その後、誤りを検出する確率 $p_0$ をLLRジェネレータ1550（図15）によって使用して、所望の軟データを計算することができる。当初に、統計生成プロセス2000は、ステップ2010中に、1つまたは複数の基準セル1920に既知のパターンを書き込む。前に示したように、既知のパターンは、たとえば、既知のビット・パターンまたは既知の記号パターンとすることができます。

20

## 【0136】

その後、ステップ2020中に、基準セルを読み取る。その後、統計生成プロセス2000は、ステップ2030中に、基準セル1920内の誤りのあるビットの個数など、エラー・メトリックを判定する。前に示したように、ステップ2020中に読み取られた基準セル1920を、既知のパターンと比較することができる。

## 【0137】

統計生成プロセス2000は、ステップ2040中に、次のように誤り確率統計を計算する。

## 【数56】

$$p_0 = \frac{\text{誤りのあるビットの個数}}{\text{基準ビットの総数}}$$

30

## 【0138】

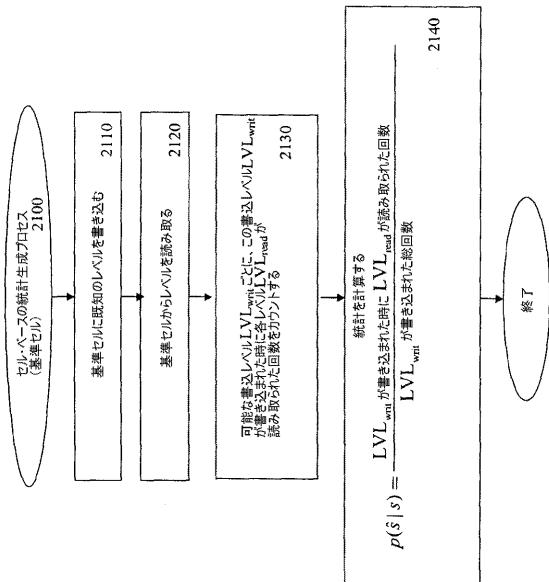

## 2. 基準セルを使用するセル・ベースの統計

図21は、本発明の基準セル実施形態に関するセル・ベースの統計生成プロセス2100の例示的実施態様を説明する流れ図である。図21に示されているように、セル・ベースの統計生成プロセス2100は、当初に、ステップ2110中に基準セル1920に1つまたは複数の既知の電圧レベルを書き込む。

40

## 【0139】

その後、セル・ベースの統計生成プロセス2100は、ステップ2120中に基準セル1920から電圧レベルを読み取る。可能な書込レベル $s$ または $LVL_{write}$ ごとに、セル・ベースの統計生成プロセス2100は、ステップ2130中に、この書込レベル $s$ または $LVL_{write}$ が書き込まれた時に各レベル $s$ ^または $LVL_{read}$ が読み取られた回数をカウントする。

## 【0140】

ステップ2140中に、次のように誤り確率統計を計算する。

## 【数57】

$$p(\hat{s} | s) = \frac{LVL_{writ} \text{が書き込まれた時に} LVL_{read} \text{が読み取られた回数}}{LVL_{writ} \text{が書き込まれた総回数}}$$

## 【0141】

代替案では、ステップ2140中に、誤り確率統計を次のように計算することができる（逆の事例）。

## 【数58】

$$p(s | \hat{s}) = \frac{LVL_{read} \text{が読み取られた時に} LVL_{writ} \text{が書き込まれた回数}}{LVL_{read} \text{が読み取られた総回数}}$$

10

## 【0142】

代替の正規化項を、ステップ2140中に計算される式の分母に使用できることに留意されたい。

## 【0143】

## 復号済み符号語を使用する統計収集

本発明の復号済み符号語実施形態では、軟データは、基準セルとして復号済み符号語から入手されたデータを使用して、フラッシュ・メモリ・デバイス810、910などのメモリ・デバイスについて生成される。一般に、フラッシュ・メモリ・デバイスなどのメモリ・デバイスからの硬データが復号され、誤りのある復号済みビットの個数などのエラー・メトリックが入手される。たとえば、誤りのある復号済みビットの個数を、復号済みビットをメモリ・デバイスから入手された硬データと比較することによって入手することができる。この形で、復号済み符号語を、正しいと仮定することができ、復号済み符号語は、上で述べた基準セルとして働くことができる。

20

## 【0144】

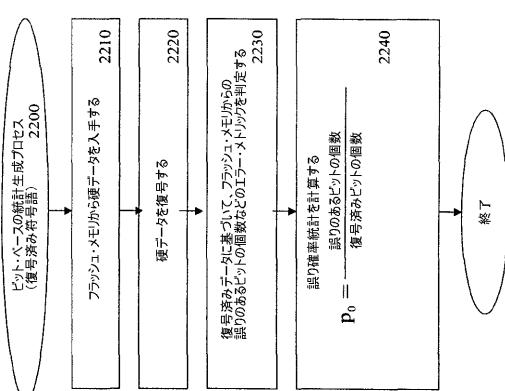

## 1. 復号済み符号語を使用するビット・ベースの統計

図22は、本発明の復号済み符号語実施形態に関するビット・ベースの統計生成プロセス2200の例示的実施態様を説明する流れ図である。一般に、ビット・ベースの統計生成プロセス2200は、復号済み符号語を使用して、誤りを検出する確率 $p_0$ を計算する。その後、誤りを検出する確率 $p_0$ を、LLRジェネレータ1550（図15）によって使用して、所望の軟データを計算することができる。当初に、統計生成プロセス2200は、ステップ2210中に、フラッシュ・メモリから硬データを入手する。

30

## 【0145】

その後、ビット・ベースの統計生成プロセス（復号済み符号語）2200は、ステップ2220中に硬データを復号する。フラッシュ・メモリからの誤りのあるビットの個数などのエラー・メトリックを、ステップ2230中に判定する。誤りのあるビットの個数は、たとえば、復号済みビット（正しいと仮定される）をフラッシュ・メモリからの硬データと比較することによって判定することができる。

40

## 【0146】

統計生成プロセス2200は、ステップ2240中に次のように誤り確率統計を計算する。

## 【数59】

$$p_0 = \frac{\text{誤りのあるビットの個数}}{\text{復号済みビットの総数}}$$

## 【0147】

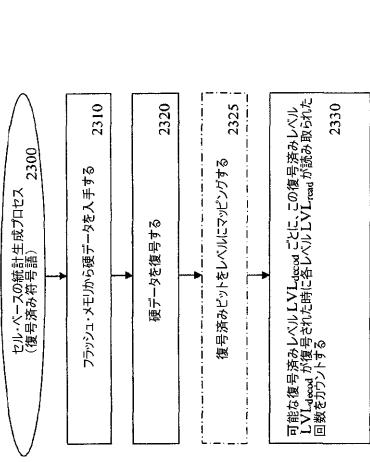

## 2. 復号済み符号語を使用するセル・ベースの統計

50

図23は、本発明の特徴を組み込んだセル・ベースの統計生成プロセス（復号済み符号語）2300の例示的実施態様を説明する流れ図である。一般に、統計生成プロセス2300は、復号済み符号語を使用して、セル・ベースの誤り確率を計算する。当初に、セル・ベースの統計生成プロセス2300は、ステップ2310中にフラッシュ・メモリから硬データを入手する。

【0148】

その後、セル・ベースの統計生成プロセス（復号済み符号語）2300は、ステップ2320中に硬データを復号する。その後、ステップ2325中に、復号済みビットを対応する電圧レベルにマッピングする。

【0149】

その後、可能な復号済み電圧レベル  $s$  または  $LVL_{decod}$  ごとに、セル・ベースの統計生成プロセス（復号済み符号語）2300は、ステップ2330中に、この復号済みレベル  $s$  または  $LVL_{decod}$  が復号された時に各電圧レベル  $s$  または  $LVL_{read}$  が読み取られた回数をカウントする。

【0150】

ステップ2340中に、次のように誤り確率統計を計算する。

【数60】

$$p(\hat{s}|s) = \frac{LVL_{decod} \text{ が復号された時に } LVL_{read} \text{ が読み取られた回数}}{LVL_{decod} \text{ が復号された総回数}}$$

10

20

【0151】

代替案では、誤り確率統計を、ステップ2340中に次のように計算することができる（逆の事例）

【数61】

$$p(s|\hat{s}) = \frac{LVL_{read} \text{ が読み取られた時に } LVL_{decod} \text{ が復号された回数}}{LVL_{read} \text{ が読み取られた総回数}}$$

【0152】

30

条件固有の誤り確率

前に示したように、誤り確率統計を、オプションで、メモリ・アレイの異なる位置について、アグレッサ・セルの異なるパターンについて、異なる温度について、異なる個数のプログラム／消去サイクルまたは読み取りサイクルについて、その他など、異なる条件について入手することができる。その後、同一条件が観察される時に、軟データを、正しい条件依存の統計または確率を使用して入手することができる。

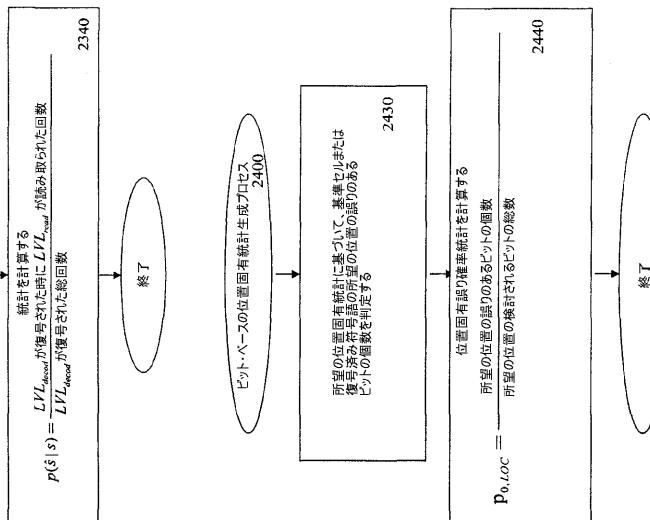

【0153】

下で図24および25に関連して述べるように、例示的な位置固有統計生成プロセス2400、2500は、それぞれビット・ベースの統計およびセル・ベースの統計を使用して、メモリ・アレイの異なる位置に関する誤り確率統計入手する。

40

【0154】

ビット・ベースの位置固有統計

図24は、メモリ・アレイ内の複数の異なる位置に関するビット誤りを検出する確率を推定する例示的なビット・ベースの位置固有統計生成プロセス2400を説明する流れ図である。たとえば、誤りを検出する確率  $p_{0, loc}$  を、異なるページ位置、ワード線位置、ビット線位置（偶数ビット線および奇数ビット線など）、およびマルチレベル・セル内の異なるビット（最上位ビット（MSB）および最下位ビット（LSB）など）のうちの1つまたは複数について入手することができる。図24に示されているように、例示的なビット・ベースの位置固有統計生成プロセス2400は、当初に、ステップ2430中に、所望の位置固有統計に基づいて、基準セルまたは復号済み符号語の所望の位置の誤り

50

のあるビットの個数を判定する。たとえば、位置固有統計が M S B に関するものである場合には、ステップ 2430 中に、誤りのある M S B ビットの個数を評価する。M S B 統計が入手されつつあるときには、たとえば、L S B ビットなど、各セル内のすべての他のビットをオプションで無視できることに留意されたい。

#### 【0155】

次に、位置固有統計生成プロセス 2400 は、ステップ 2440 中に次のように位置固有誤り確率統計を計算する。

#### 【数 62】

$$p_{0,loc} = \frac{\text{所望の位置の誤りのあるビットの個数}}{\text{所望の位置の検討されるビットの総数}}$$

10

#### 【0156】

##### セル・ベースの位置固有統計

セル・ベースの位置固有実施態様について、メモリ・アレイ内の関心を持たれている異なる位置は、たとえば、異なるワード線位置またはビット線位置（偶数ビット線および奇数ビット線など）のうちの 1 つまたは複数を含むことができる。

#### 【0157】

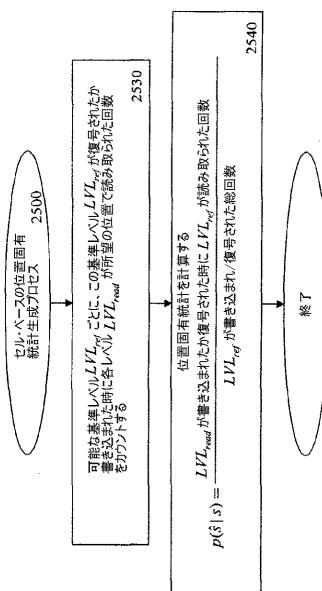

図 25 は、異なるワード線位置またはビット線位置（偶数ビット線および奇数ビット線など）のうちの 1 つまたは複数など、メモリ・アレイ 1900 内の複数の異なる位置について誤り確率統計を入手する例示的なセル・ベースの位置固有統計生成プロセス 2500 を説明する流れ図である。図 25 に示されているように、可能な基準電圧レベル  $s$  または  $LVL_{ref}$  ごとに、例示的なセル・ベースの位置固有統計生成プロセス 2500 は、当初に、ステップ 2530 中に、この基準レベル  $s$  または  $LVL_{ref}$  が復号されたか書き込まれた時に各電圧レベル  $s \wedge LVL_{read}$  が所望の位置で読み取られた回数をカウントする。

20

#### 【0158】

次に、セル・ベースの位置固有統計生成プロセス 2500 は、ステップ 2540 中に次のように位置固有誤り確率統計を計算する。

#### 【数 63】

$$p(\hat{s} | s) = \frac{LVL_{ref} \text{が書き込まれたか復号された時に} \\ LVL_{read} \text{が読み取られた回数}}{LVL_{ref} \text{が書き込まれたか復号された総回数}}$$

30

#### 【0159】

代替案では、 $p(s | s')$  を、上で述べたように計算することができる。

#### 【0160】

本発明のさまざまな実施態様では、別々のビット・ベースの、セル・ベースの、またはパターン・ベースの統計を、ページごと、ワード線ごと、もしくはメモリ・アレイごとに、またはページのグループ、ワード線のグループ、もしくはメモリ・アレイのグループについて（あるワード線内の異なるページ・レベル、またはあるメモリ・アレイ内の下ワード線、中ワード線、および上ワード線についてなど）、収集することができる。さらに、統計を、複数のページ、ワード線、またはメモリ・アレイにまたがって平均化することができ、その後、平均統計を、これらのページ、ワード線、またはメモリ・アレイについて使用することができる。

40

#### 【0161】

##### パターン依存の統計

前に示したように、本発明のさまざまな実施形態は、1 つまたは複数の軟値  $r$  について、ターゲット・セルおよび 1 つまたは複数の値  $h$  について、アグレッサ・セル（1 つま

50

たは複数)について、外来  $L_L R$ 、 $L_r$  を計算し、ここで、 $h^-$  は、アグレッサ・セル(囲むセル(1つまたは複数)などに格納されたデータ・パターンである。

#### 【0162】

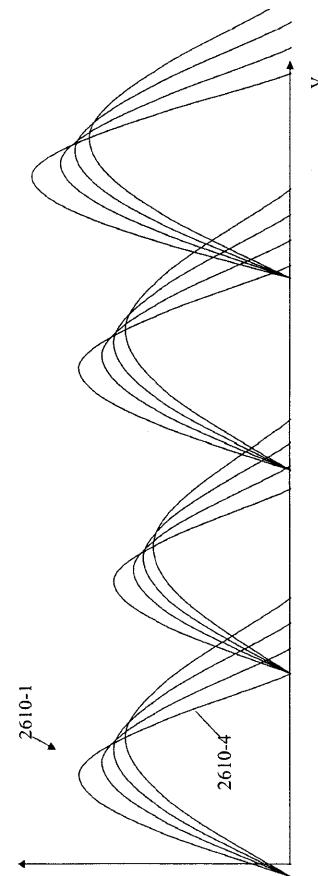

図26に、各アグレッサ・セル720のすべての可能な値に基づく、例示的なマルチレベル・セル・フラッシュ・メモリ600の所与のターゲット・セル710に関する確率密度関数2610の例示的な集団2600を示す。例示的なマルチレベル・セル・フラッシュ・メモリは、セルあたり4つのレベル(2ビット)を有し、1つのアグレッサ・セル720が、データ依存pdfについて考慮される。所与のターゲット・セル710の各可能なレベルに適用可能な確率密度関数の個数は、各アグレッサ・セル720の可能なレベルの個数を、所与のターゲット・セル710に影響するアグレッサ・セル720の個数乗したものである。前に示したように、例示的実施形態では、各セルは、4つの可能な値のうちの1つを有することができ、ターゲット・セル710あたり1つのアグレッサ・セル720があり、各アグレッサ・セル720は、4つの可能なレベルのうちの1つを有することができる。したがって、例示のために、確率密度関数の集団2600は、アグレッサ・セルのパターンに適用可能なデータまたは電圧レベル0に関する4つの確率密度関数2610-1から2610-4を含む。他のデータ・レベル1、2、および3のそれぞれについても、4つの確率密度関数がある。当業者に明白であるように、本発明を、セルあたり任意の個数のレベルおよび任意の個数のアグレッサ・セル720を有するマルチレベル・セル・フラッシュ・メモリ600に拡張することができる。

#### 【0163】

一般に、図26の各確率密度関数は、他の雑音および外乱の影響の中でも、対応するアグレッサ・セル720の所与の値に関する所与のターゲット・セル710に対するICIの影響を表す。本発明のさらなる実施形態では、データ依存確率密度関数は、ICIの代わりにまたはICIに加えて、他のデータ依存ひずみを表すことができる。後で述べるように、さまざまな実施形態では、確率密度関数を、事前定義の静的なものとするか、リアルタイム観察に基づいて適合されるものとするか、あるいは、ガウス関数など、アグレッサ・セル720の測定されたまたは検出された値 $h$ の関数として表すことができる。

#### 【0164】

本発明の一態様によれば、フラッシュ・メモリ・デバイス内の外乱は、少なくとも1つのターゲット・セルに対する1つまたは複数のアグレッサ・セルのパターン依存外乱を表す1つまたは複数の確率密度関数を入手することによって特徴を表すことができる。外乱は、たとえば、バック・パターン依存、セル間干渉、プログラム妨害、読取妨害、および/または追加の雑音を含むことができる。確率密度関数を、1つまたは複数のデータ判断に基づいて更新することができる。確率密度関数を、格納されたテーブルおよび/または式として表すことができる。

#### 【0165】

さらに、確率密度関数のテーブル・エントリまたは関数パラメータを、オプションで、たとえば受け取られたデータ判断に基づいて、適応式に更新できることに留意されたい。たとえば、確率密度関数を、受け取られたアグレッサ・パターン $h^-$ に基づいて選択することができる。選択された確率密度関数は、その後、受け取られたターゲット・セル値 $r$ に基づいて、既知の技法を使用して、最新のオカレンスを用いて更新される(たとえば、対応するカウンタを増やすことによって)。

#### 【0166】

前に示したように、所与のターゲット・セル710に影響するアグレッサ・セル720の個数を、複数の要因に基づいて減らすか無視することができる。この形で、検討する必要がある確率密度関数の個数を減らすことができる。たとえば、ICIを軽減する例示的実施態様では、斜めに結合する係数 $k_{x,y}$ が、他の結合する係数よりはるかに小さい(しばしばそうであるように)場合には、斜めに位置するセルからのICIを無視することができる。さらに、プログラミング・シーケンスは、検討される必要があるアグレッサ・セル720の個数に影響する。たとえば、ボトム・アップ手法など、ワード線が必ず固定さ

10

20

30

40

50

れた順序で書き込まれる場合には、下側ワード線内のセルからの外乱 I C I 寄与がない場合がある。さらに、外乱 I C I がターゲット・セル 710 の左右の隣に関して対称である場合には、特性を表される必要がある確率密度関数の個数が、半分だけ減らされる。

#### 【0167】

前に示したように、1つの例示的実施態様では、確率密度関数を、ガウス確率密度関数を使用して近似することができる。さらなる変形形態では、確率密度関数が、たとえばヒストグラムに基づく場合に、追加の複雑さという犠牲を払って、改善された性能を得ることができる。確率密度関数がヒストグラムを使用して実施されるときに、確率密度関数を、成功して復号されたワード線を使用してヒストグラムをトレーニングすることによって適応式に更新することができる。

10

#### 【0168】

さらなる実施形態では、確率密度関数およびその近似を、読み取りデータを検出するために、ビタビ・アルゴリズム、軟出力ビタビ(SOVA)アルゴリズム、およびBCJRアルゴリズムなどのトレリス・ベースの検出アルゴリズムによって使用することができる。

#### 【0169】

##### 1. ビット・ベースのパターン依存統計

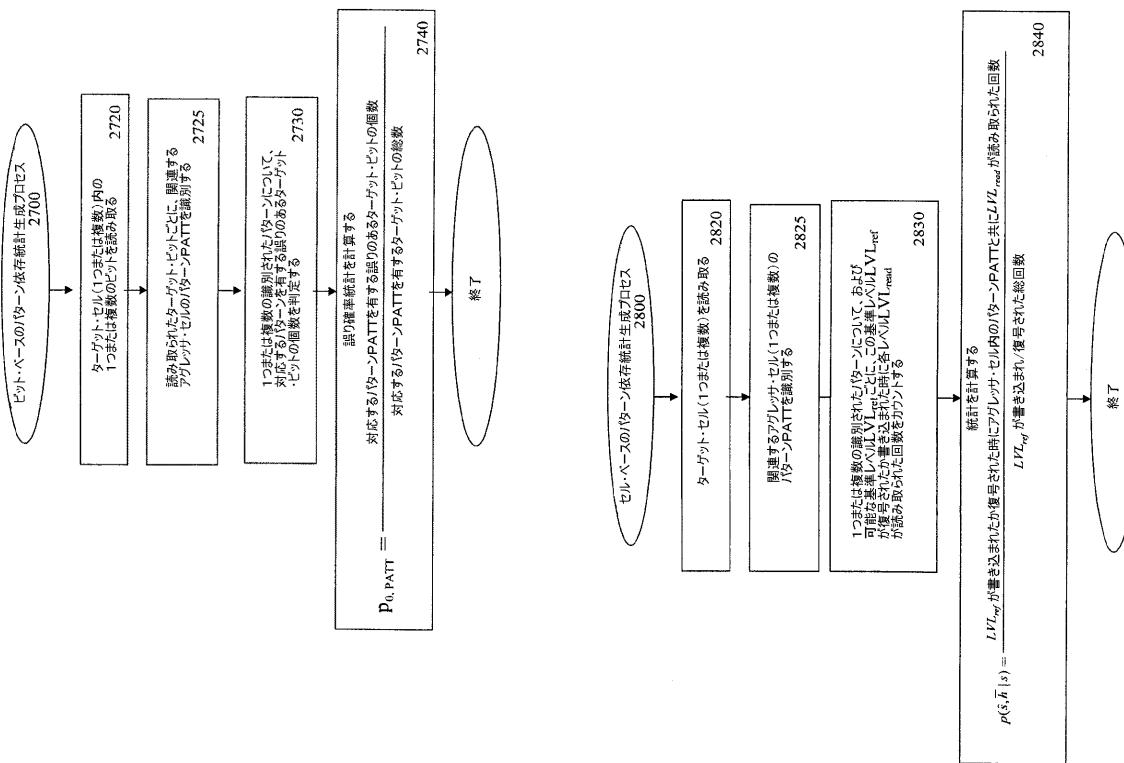

図27は、少なくとも1つのターゲット・セル710(図7)に関連する1つまたは複数のアグレッサ・セル720の所与のパターン $h^-$ またはPATTに関するビット・エラーを検出する確率 $p_{0, PATT}$ を推定する例示的なビット・ベースのパターン依存統計生成プロセス2700を説明する流れ図である。当初に、ビット・ベースのパターン依存統計生成プロセス2700は、ステップ2720中に基準ターゲット・セル710および潜在的に関連するアグレッサ・セル(1つまたは複数)720を読み取る。さらに、ステップ2725中に、読み取られたターゲット・ビットごとに、関連するアグレッサ・セル720のパターンPATTを識別する。このパターンは、ステップ2725中に、たとえば書き込まれた既知のパターンを評価することによって、または基準セルもしくは復号済み符号語の実際の読み取り動作に基づいて、識別することができる。

20

#### 【0170】

ステップ2730中に、1つまたは複数の識別されたパターンについて、対応するパターンを有する誤りのあるターゲット・ビットの個数を判定する。その後、ステップ2740中に、次のように誤り確率統計を計算する。

30

##### 【数64】

$$p_{0, PATT} = \frac{\text{対応するパターンPATTを有する誤りのあるターゲット・ビットの個数}}{\text{対応するパターンPATTを有するターゲット・ビットの総数}}$$

#### 【0171】

当業者に明白であるように、上で説明した諸技法を、オプションで、位置固有パターン依存統計入手するために統合できることに留意されたい。さらに、さらなる変形形態では、それに加えてまたはその代わりに、読み取り統計を、メモリ・デバイスの耐久性、読み取りサイクル数、保持特性、温度、または他のパラメータの関数として入手することができる。

40

#### 【0172】

##### 2. セル・ベースのパターン依存統計

図28は、少なくとも1つのターゲット・セルに関連する1つまたは複数のアグレッサ・セルの所与のパターンに関する誤りを検出する確率を推定する例示的なセル・ベースのパターン依存統計生成プロセス2800を説明する流れ図である。図28に示されているように、セル・ベースのパターン依存統計生成プロセス2800は、当初に、ステップ2820中に1つまたは複数のターゲット・セルを読み取る。その後、ステップ2825中に、関連するアグレッサ・セル(1つまたは複数)のパターン $h^-$ またはPATTを識別する。

#### 【0173】

50

その後、ステップ 2830 中に、1つまたは複数の識別されたパターンについて、および可能な基準電圧レベル  $s$  または  $LVL_{ref}$  ごとに、セル・ベースのパターン依存統計生成プロセス 2800 は、この基準レベル  $s$  または  $LVL_{ref}$  が復号されたか書き込まれた時に各電圧レベル  $s^+$  または  $LVL_{read}$  が読み取られた回数をカウントする。

## 【0174】

ステップ 2840 中に、パターン依存誤り確率統計が、次のように計算される。

## 【数 65】

$$p(\hat{s}, h | s) = \frac{LVL_{ref} \text{ が書き込まれたか復号された時にアグレッサ・セル内の } \\ \text{ パターン PATT と共に } LVL_{read} \text{ が読み取られた回数}}{LVL_{ref} \text{ が書き込まれ / 復号された総回数}} \quad 10$$

## 【0175】

## 非対称誤り確率統計

前に示したように、NAND フラッシュ・メモリ・チャネルなどのある種のチャネルでは、2進0および2進1などの異なる可能な2進値の誤りを検出する確率が、大きく異なる可能性がある。したがって、本発明は、オプションで、非対称チャネルの誤りを検出する確率を提供する。図29および30は、2進0および2進1などの2つの可能な2進値の誤り確率  $p$  および  $q$  を推定する例示的な非対称統計生成プロセス 2900、3000 を提供する。下でさらに述べるように、図29は、基準セルを使用して非対称統計を推定し、図30は、復号済み符号語を使用して非対称統計を推定する。したがって、本発明は、フラッシュ・メモリからの硬データに基づいて可能な2進値ごとに非対称 LLR を提供する。

## 【0176】

## 非対称誤り確率 - 基準セル

前に示したように、NAND フラッシュ・メモリ・チャネルなどのある種のチャネルでは、2進0および2進1などの異なる可能な2進値の誤りを検出する確率が、大きく異なる可能性がある。したがって、本発明は、オプションで、非対称チャネルの誤りを検出する確率を提供する。図29は、本発明の基準セル実施形態の2つの可能な2進値の誤り確率を推定する例示的な非対称統計生成プロセス 2900 を説明する流れ図である。

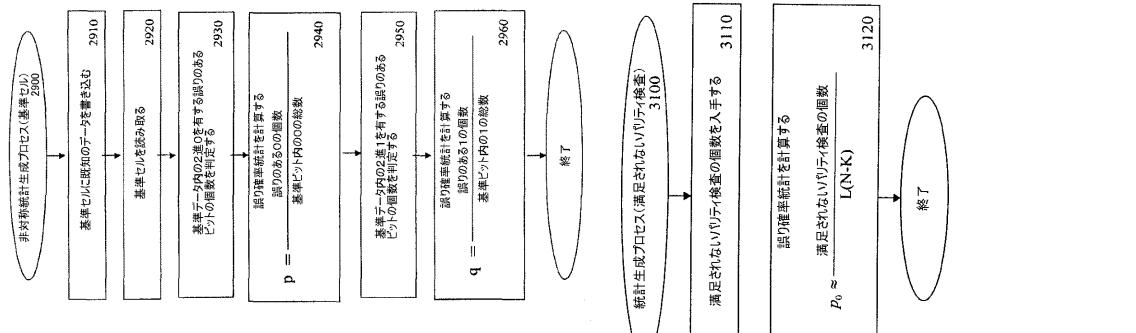

## 【0177】

図29に示されているように、非対称統計生成プロセス 2900 は、当初に、ステップ 2910 中に基準セル 1920 に既知のパターンを書き込み、その後、ステップ 2020 中に基準セル 1920 を読み取る。非対称統計生成プロセス 2900 は、ステップ 2930 中に基準データ内の2進0を有する誤りのあるビットの個数を判定し、その後、次のように、ステップ 2940 中に2進0の誤り確率統計を計算する。

## 【数 66】

$$p = \frac{\text{誤りのある } 0 \text{ の個数}}{\text{基準ビット内の } 0 \text{ の総数}} \quad 40$$

## 【0178】

その後、非対称統計生成プロセス 2900 は、ステップ 2950 中に基準データ内の2進1を有する誤りのあるビットの個数を判定し、その後、次のように、ステップ 2960 中に2進1の誤り確率統計を計算する。

## 【数 67】

$$q = \frac{\text{誤りのある } 1 \text{ の個数}}{\text{基準ビット内の } 1 \text{ の総数}} \quad 50$$

## 【0179】

## 非対称誤り確率 - 復号済み符号語

図30は、本発明の復号済み符号語実施形態の2つの可能な2進値の誤り確率を推定する例示的な非対称統計生成プロセス3000を説明する流れ図である。図30に示されているように、非対称統計生成プロセス3000は、当初に、ステップ3010中にフラッシュ・メモリから硬データ入手し、ステップ3020中に硬データを復号する。

## 【0180】

その後、非対称統計生成プロセス3000は、ステップ3030中に復号済みデータ内の2進0を有するフラッシュ・メモリからの誤りのあるビットの個数を判定する。その後、ステップ3040中に、次のように2進0の誤り確率統計を計算する。

## 【数68】

$$p = \frac{\text{誤りのある0の個数}}{\text{復号済みビット内の0の総数}}$$

## 【0181】

同様に、ステップ3050中に、復号済みデータ内の2進1を有するフラッシュ・メモリからの誤りのあるビットの個数を判定する。その後、ステップ3060中に、次のように2進1の誤り確率統計を計算する。

## 【数69】

$$q = \frac{\text{誤りのある1の個数}}{\text{復号済みビット内の1の総数}}$$

## 【0182】

一実施形態では、NANDフラッシュ・メモリがアイドルである（すなわち、ユーザ・データを能動的に読み取っても書き込んでもいない）間に、統計を収集し、計算し、格納することができる。

## 【0183】

例示的実施形態は、基準セルまたはデコーダ・フィードバックを使用する統計収集を使用したが、検出されたデータまたは復号されたデータを使用して、たとえば最小平均二乗誤差判断基準を使用して、統計を推定するのに適応的方法を使用することもできる。

## 【0184】

代替実施形態では、統計または対応するLLRを、ワーストケース動作条件（たとえば、プログラム／消去サイクルの個数、保持時間、および温度に関する）について、たとえばフラッシュ・メモリの実験的特性試験に基づいて事前に計算し、その後、これらを悪いチャネル条件について使用することができる。この形で、より正確な統計またはLLRが、誤り確率が最大であるときに使用可能である。言い換えると、事前定義の統計または対応するLLRを、事前定義の動作条件について事前に計算することができる。

## 【0185】

さらなる変形形態では、軟データを、復号が成功するまで異なる統計（誤り確率など）に基づいて反復して生成することができる。統計を、データの成功の検出または復号まで、ある範囲にわたって変更することができる。本発明のこの変形形態は、データの仮想再読み取りを提供する。データは、実際にはフラッシュ・メモリから再読み取られないが、データは、異なる軟情報を用いて成功して復号される。

## 【0186】

## 満足されないパリティ検査に基づく誤り性能

本発明の諸態様は、満足されないパリティ検査を、軟データ入手するために性能メトリックとして使用することもできることを認めるものである。（N, K, J, L）LDPC符号を検討されたく、Nは、符号語長であり、Kは、未符号化符号語長（符号語内のユ

10

20

30

40

50

ーザ・データ長)であり、JおよびLは、それぞれパリティ検査行列の列重みおよび行重みである。(N, K, J, L) LDPC符号語が、誤り確率  $p_0$  で伝送されるか格納される時に、チェック・サムが最初の反復で不合格になる確率を、次のように表すことができる。

【数70】

$$p_c = \frac{1 - (1 - 2p_0)^L}{2}$$

この確率を、次のように推定することができる。

10

【数71】

$$p_c = \frac{\text{最初の反復での満足されない検査の個数}}{N-K}$$

【0187】

したがって、誤り確率  $p_0$  を、次のように推定することができる。

【数72】

$$p_0 = \frac{1 - \sqrt[4]{1 - 2p_c}}{2} \approx \frac{p_c}{L}$$

20

【0188】

上の手順では、チャネルおよび初期LLR値を、反復復号を実行する前に推定することができる。チャネル推定の複雑さおよび待ち時間は、軟判定復号の1反復のそれより小さく、LDPC符号の硬判定復号に対するかなりの性能利益を伴う。軟判定復号の標準実施態様と比較した追加のハードウェアは、次の計算を実行するブロックである。

【数73】

$$p_0 \approx \frac{\text{最初の反復での満足されない検査の個数}}{L(N-K)}$$

30

【0189】

図31は、本発明の一態様による、満足されないパリティ検査を使用する統計生成プロセス3100の例示的実施態様を説明する流れ図である。一実施形態では、最初の反復の後の満足されないパリティ検査が使用される。一般に、統計生成プロセス3100は、満足されないパリティ検査を使用して、誤りを検出する確率  $p_0$  を計算する。その後、誤りを検出する確率  $p_0$  を、LLRジェネレータ1550(図15)によって使用して、所望の軟データを計算することができる。

【0190】

40

当初に、統計生成プロセス3100は、ステップ3110中に満足されないパリティ検査の個数を入手する。次に、統計生成プロセス3100は、ステップ3120中に次のように誤り確率統計を計算する。

【数74】

$$p_0 \approx \frac{\text{満足されない検査の個数}}{L(N-K)}$$

【0191】

位置固有統計 - 満足されないパリティ検査

50

図32は、満足されないパリティ検査を使用してメモリ・アレイ1900内の複数の異なる位置の誤り確率統計を入手する例示的な位置固有統計生成プロセス3200を説明する流れ図である。たとえば、誤り確率統計を、異なるページ位置、ワード線位置、ビット線位置（偶数ビット線および奇数ビット線など）、およびマルチレベル・セル内の異なるビット（最上位ビット（MSB）および最下位ビット（LSB）など）のうちの1つまたは複数について入手することができる。一般に、位置固有統計は、満足されないパリティ検査を使用して、所望の位置にビットを位置決めする符号語を使用することによって入手される（ステップ3210）。

【0192】

次に、図32に示されているように、例示的な位置固有統計生成プロセス3200は、

ステップ3220中に、符号語に関する満足されないパリティ検査の個数を入手する。その後、ステップ3230中に、次のように位置固有誤り確率統計を計算する。

【数75】

$$p_{0,LOC} \approx \frac{\text{満足されない検査の個数}}{L(N-K)}$$

【0193】

満足されないパリティ検査に基づく非対称統計

図33は、満足されないパリティ検査を使用して2つの可能な2進値の誤りを検出する確率を推定する例示的な非対称統計生成プロセス3300を説明する流れ図である。本発明のこの態様は、平均誤り確率 $p^-$ を、満足されないパリティ検査に基づいて計算できることを認めるものである（ただし、 $p^- = (p + q) / 2$ ）。 $p$ および $q$ の値を、平均誤り確率確率 $p^-$ と、誤り確率 $p$ および $q$ の比 $k$ に基づいて計算することができる。

【0194】

誤り確率 $p$ および $q$ の比 $k$ を、上で説明した復号済み符号語技法などのデータ分析を使用して入手することができる。代替案では、誤り確率 $p$ および $q$ の比 $k$ を、たとえば、本願と同時に出願され、参照によって本明細書に組み込まれている、国際出願、名称「Methods and Apparatus for Soft Data Generation for memory devices Using Reference Cells」に記載の基準セル技法を使用して入手することができる。誤り確率 $p$ および $q$ の比 $k$ は、通常は、オフラインで計算され、たとえばテーブルに格納されるはずである。図33に示されているように、例示的な非対称統計生成プロセス（満足されないパリティ検査）3300は、当初に、ステップ3310中に誤り確率 $p$ および $q$ の比 $k$ 入手する。

【0195】

平均誤り確率確率 $p^-$ を、ステップ3320中に、図16に関連して上で説明した技法を使用して入手することができる。具体的に言うと、平均誤り確率確率 $p^-$ を、次のように推定することができる。

【数76】

$$\bar{p} \approx p_0 \approx \frac{\text{満足されない検査の個数}}{L(N-K)}$$

【0196】

その後、ステップ3330中に、次のように2進0の誤り確率統計 $p$ を計算する。

10

20

30

40

【数77】

$$p = \frac{2\bar{p}}{k+1}$$

【0197】

その後、ステップ3340中に、次のように2進1の誤り確率統計qを計算する。

【数78】

$$q = \frac{2k\bar{p}}{k+1}$$

10

【0198】

非対称統計生成プロセス（満足されないパリティ検査）3300によって計算される誤り確率統計pおよびqを、オプションで位置固有および/またはパターン依存にすることができるように留意されたい。

【0199】

プロセス、システム、および製造品の詳細

本明細書の複数の流れ図は、ステップの例示的シーケンスを説明するが、そのシーケンスを変更できることも、本発明の実施形態である。アルゴリズムのさまざまな置換が、本発明の代替実施形態として企図されている。本発明の例示的実施形態を、ソフトウェア・プログラム内の処理ステップに関して説明したが、当業者に明白であるように、さまざまな機能を、デジタル領域でソフトウェア・プログラム内の処理ステップとして、ハードウェアで回路要素または状態機械によって、あるいはソフトウェアとハードウェアとの両方の組合せで実施することができる。そのようなソフトウェアを、たとえば、デジタル信号プロセッサ、特定用途向け集積回路、マイクロコントローラ、または汎用コンピュータで使用することができる。そのようなハードウェアおよびソフトウェアを、集積回路内で実施される回路内で実施することができる。

20

【0200】

したがって、本発明の機能を、方法およびこれらの人手を実践する装置の形で実施することができる。本発明の1つまたは複数の態様を、たとえば、記憶媒体に格納されるか、機械にロードされかつ/または機械によって実行されるか、あるいはある伝送媒体を介して伝送されるかのいずれかであるプログラム・コードの形で実施することができ、ここで、そのプログラム・コードがコンピュータなどの機械にロードされ、その機械によって実行される時に、その機械は、本発明を実践する装置になる。汎用コンピュータで実施される時に、プログラム・コード・セグメントは、特定の論理回路に類似して動作するデバイスを提供するためにプロセッサと組み合わされる。本発明を、集積回路、デジタル信号プロセッサ、マイクロプロセッサ、およびマイクロコントローラのうちの1つまたは複数で実施することもできる。

30

【0201】

当技術分野で既知のように、本明細書で述べられた方法および装置を、コンピュータ可読コード手段をその上で実施されたコンピュータ可読媒体をそれ自体が含む製造品として配布することができる。コンピュータ可読プログラム・コード手段は、本明細書で述べられた方法を実行するステップのすべてまたは一部を実行したまたは本明細書で述べられた装置を作成するために、コンピュータ・システムに関連して動作可能である。コンピュータ可読媒体は、記録可能媒体（たとえば、フロッピ・ディスク、ハード・ドライブ、コンパクト・ディスク、メモリ・カード、半導体デバイス、チップ、特定用途向け集積回路（A S I C））とすることができます、あるいは、伝送媒体（たとえば、光ファイバを含むネットワーク、ワールド・ワイド・ウェブ、ケーブル、または時分割多元接続、符号分割多元接続、もしくは他の無線周波数チャネルを使用する無線チャネル）とすることができます。コ

40

50

ンピュータ・システムと共に使用するのに適切な情報を格納できる既知のまたは開発されるすべての媒体を、使用することができる。コンピュータ可読コード手段は、磁気媒体上の磁気変動またはコンパクト・ディスクの表面上の高さ変動など、コンピュータが命令およびデータを読み取ることを可能にするすべての機構である。

【0202】

本明細書で説明されるコンピュータ・システムおよびサーバは、それぞれ、本明細書で開示される方法、ステップ、および機能を実施するために関連プロセッサを構成するメモリを含む。メモリを、分散型またはローカルとすることができます、プロセッサを、分散型または単独とすることができます。メモリを、電子メモリ、磁気メモリ、または光メモリ、あるいは上記または他のタイプのストレージ・デバイスの任意の組合せとして実施することができます。さらに、用語「メモリ」は、関連するプロセッサによってアクセスされるアドレス空間内のアドレスから読み取られるかそのアドレスに書き込まれることが可能なすべての情報を包含するのに十分に広く解釈されなければならない。この定義を用いると、ネットワーク上の情報は、それでも、関連するプロセッサがネットワークからその情報を取り出すことができるので、メモリに含まれる。

10

【0203】

本明細書で図示され、説明された実施形態および変形形態が、本発明の原理の単なる例示であり、さまざまな修正形態を、本発明の範囲および趣旨から逸脱せずに当業者が実施できることを理解されたい。

【図1】

【図2】

【 义 3 】

【 図 4 】

【図 5 A】

【図5B】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

【図 1 2 A】

### 【図12B】

【図13】

【 図 1 4 】

【図15】

### 【図16】

【図 1 7 A】

セル・ベースの統計カウント・テーブル 1740

| 書き (s) | 00      | 01      | 10      | 11      | sum   |

|--------|---------|---------|---------|---------|-------|

| 読み (s) |         |         |         |         |       |

| 00     | 1.39E-2 | 1.88E-4 | 9.41E-5 |         | 10617 |

| 01     | 0       | 0.9850  | 0       | 1.32E-3 | 0     |

| 10     | 1.41E-3 | 4.70E-4 | 0.9998  | 3.76E-4 | 5     |

| 11     | 0       | 6.58E-4 | 0       | 0.9982  | 0     |

| 合計     |         |         |         |         | 10632 |

|        |         |         |         |         | 10640 |

|        |         |         |         |         | 10612 |

|        |         |         |         |         | 10622 |

【図 1 7 B】

$p(s | \hat{s})$  のセル・ベースの統計テーブル 1720

| 書き (s) | 00      | 01      | 10       | 11       | sum |

|--------|---------|---------|----------|----------|-----|

| 読み (s) |         |         |          |          |     |

| 00     | 0.98598 | 0.01374 | 1.86E-04 | 9.29E-05 |     |

| 01     | 0       | 0.99866 | 0        | 1.334E-3 |     |

| 10     | 1.41E-3 | 4.7E-4  | 0.9977   | 3.76E-4  |     |

| 11     | 0       | 6.6E-4  | 0        | 0.9993   |     |

【図 1 7 C】

$p(\hat{s} | s)$  のセル・ベースの統計テーブル 1740

| 書き (s)                        | 00   | 01   | 10   | 11   |  |

|-------------------------------|------|------|------|------|--|

| 読み (s), / $\gamma_2(\hat{s})$ |      |      |      |      |  |

| 00, 00                        | 0.24 | 1E-2 | 0    | 0    |  |

| 00, 01                        | 0.3  | 1E-2 | 0    | 0    |  |

| 00, 10                        | 0.25 | 5E-2 | 0    | 0    |  |

| 00, 11                        | 0.2  | 3E-2 | 1E-3 | 0    |  |

| 01, 00                        | 0    | 0.3  | 0    | 2E-2 |  |

| 01, 01                        | 0    | 0.2  | 3E-3 | 1E-2 |  |

| 01, 10                        | 0    | 0.1  | 0    | 2E-2 |  |

| 01, 11                        | 0    | 0.1  | 0    | 5E-2 |  |

| 10, 00                        | 1E-3 | 0    | 0.4  | 4E-3 |  |

| 10, 01                        | 2E-3 | 0    | 0.3  | 3E-3 |  |

| 10, 10                        | 3E-3 | 0    | 0.2  | 1E-3 |  |

| 10, 11                        | 4E-3 | 1E-1 | 9E-2 | 2E-3 |  |

| 11, 00                        | 0    | 0    | 0    | 0.25 |  |