(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6149572号

(P6149572)

(45) 発行日 平成29年6月21日(2017.6.21)

(24) 登録日 平成29年6月2日(2017.6.2)

(51) Int.Cl.

F 1

H04N 5/341 (2011.01)

H04N 5/335 410

H04N 5/3745 (2011.01)

H04N 5/335 745

請求項の数 7 (全 36 頁)

(21) 出願番号 特願2013-154457 (P2013-154457)

(22) 出願日 平成25年7月25日 (2013.7.25)

(65) 公開番号 特開2015-26938 (P2015-26938A)

(43) 公開日 平成27年2月5日 (2015.2.5)

審査請求日 平成27年12月22日 (2015.12.22)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 山口 和哲

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 吉川 玲

東京都港区港南1丁目7番1号 ソニー株

式会社内

最終頁に続く

(54) 【発明の名称】イメージセンサ、制御方法、及び、電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換によって電気信号を出力する複数の画素を有する2個以上の共有画素が2次元に配列された画素アレイ部と、

前記共有画素の配列のうちの、複数行の共有画素から同時に読み出される電気信号を処理するカラム処理部と、

前記共有画素が有する前記画素から前記電気信号を読み出すためのアクセス制御として、前記複数行のうちの1の行と他の1の行とで、異なるアクセス制御を行う行制御部とを備え、

前記共有画素の1列に対して、複数の列信号線が配線され、

前記共有画素から読み出された電気信号は、前記列信号線を介して、前記カラム処理部に供給され、

前記カラム処理部は、

前記列信号線の一端側に設けられており、

前記複数行の各列の共有画素から同時に読み出される電気信号をAD(Analog Digital)変換するAD変換部として、前記共有画素の列数に、前記複数行を乗算した乗算値だけの数のAD変換部を有する

イメージセンサ。

## 【請求項 2】

前記共有画素が有する複数の画素は、FD(Floating Diffusion)を共有し、

10

20

前記行制御部は、前記FDを共有する複数の画素のうちの2以上の画素から前記電気信号を同時に読み出すアクセス制御を行うことで、前記2以上の画素から同時に読み出された前記電気信号が前記FDで加算されるFD加算により得られる加算信号を、前記共有画素から読み出す

請求項1に記載のイメージセンサ。

【請求項3】

前記行制御部は、前記カラム処理部の処理で画素値が得られる画素の垂直方向の間隔を略等間隔にする前記FD加算が行われるように、前記アクセス制御を行う

請求項2に記載のイメージセンサ。

【請求項4】

前記行制御部は、1行の1の列と他の列とでも、異なるアクセス制御を行う

請求項1ないし3のいずれかに記載のイメージセンサ。

【請求項5】

前記行制御部は、複数の異なる行の、同一の列信号線に接続されている複数の共有画素から前記電気信号を同時に読み出すアクセス制御を行うことで、前記複数の共有画素から同時に読み出された前記電気信号を前記列信号線上で加算して、前記カラム処理部に供給する

請求項2または3に記載のイメージセンサ。

【請求項6】

光電変換によって電気信号を出力する複数の画素を有する2個以上の共有画素が2次元に配列された画素アレイ部と、

前記共有画素の配列のうちの、複数行の共有画素から同時に読み出される電気信号を処理するカラム処理部と

を備え、

前記共有画素の1列に対して、複数の列信号線が配線され、

前記共有画素から読み出された電気信号は、前記列信号線を介して、前記カラム処理部に供給され、

前記カラム処理部は、

前記列信号線の一端側に設けられており、

前記複数行の各列の共有画素から同時に読み出される電気信号をAD(Analog Digital)変換するAD変換部として、前記共有画素の列数に、前記複数行を乗算した乗算値だけの数のAD変換部を有するイメージセンサの前記共有画素が有する前記画素から前記電気信号を読み出すためのアクセス制御として、前記複数行のうちの1の行と他の1の行とで、異なるアクセス制御を行う

制御方法。

【請求項7】

光を集光する光学系と、

光を受光し、画像を撮像するイメージセンサと

を備え、

前記イメージセンサは、

光電変換によって電気信号を出力する複数の画素を有する2個以上の共有画素が2次元に配列された画素アレイ部と、

前記共有画素の配列のうちの、複数行の共有画素から同時に読み出される電気信号を処理するカラム処理部と、

前記共有画素が有する前記画素から前記電気信号を読み出すためのアクセス制御として、前記複数行のうちの1の行と他の1の行とで、異なるアクセス制御を行う行制御部とを有し、

前記共有画素の1列に対して、複数の列信号線が配線され、

前記共有画素から読み出された電気信号は、前記列信号線を介して、前記カラム処理部に供給され、

10

20

30

40

50

前記カラム処理部は、

前記列信号線の一端側に設けられており、

前記複数行の各列の共有画素から同時に読み出される電気信号をAD(Analog Digital)変換するAD変換部として、前記共有画素の列数に、前記複数行を乗算した乗算値だけの数のAD変換部を有する

電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、イメージセンサ、制御方法、及び、電子機器に関し、共有画素を採用するイメージセンサにおいて高速撮像を行うことができるようとするイメージセンサ、制御方法、及び、電子機器に関する。 10

【背景技術】

【0002】

近年、イメージセンサの多画素化に伴い、光電変換を行う画素からの電気信号の読み出しに、時間を要するようになっている。

【0003】

そこで、多画素のイメージセンサにおいて、フレームレートを低下させずに、画像を撮像する技術や、より高速のフレームレートで画像を撮像する高速撮像を行う技術が提案されている（例えば、特許文献1）。 20

【0004】

なお、以下では、説明の便宜上、高速撮像には、適宜、フレームレートを低下させずに画像を撮像することが含まれることとする。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2012-253624号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、現在提案されている高速撮像のための技術は、1個の画素で、1個のFD(Floating Diffusion)を使用する単位画素を対象としており、複数の画素で、1個のFDを共有（して使用）する共有画素にとって、適切であるとは限らない。 30

【0007】

本技術は、このような状況に鑑みてなされたものであり、共有画素を採用するイメージセンサにおいて高速撮像を行うことができるようとするものである。

【課題を解決するための手段】

【0008】

本技術のイメージセンサは、光電変換によって電気信号を出力する複数の画素を有する2個以上の共有画素が2次元に配列された画素アレイ部と、前記共有画素の配列のうちの、複数行の共有画素から同時に読み出される電気信号を処理するカラム処理部と、前記共有画素が有する前記画素から前記電気信号を読み出すためのアクセス制御として、前記複数行のうちの1の行と他の1の行とで、異なるアクセス制御を行う行制御部とを備え、前記共有画素の1列に対して、複数の列信号線が配線され、前記共有画素から読み出された電気信号は、前記列信号線を介して、前記カラム処理部に供給され、前記カラム処理部は、前記列信号線の一端側に設けられており、前記複数行の各列の共有画素から同時に読み出される電気信号をAD(Analog Digital)変換するAD変換部として、前記共有画素の列数に、前記複数行を乗算した乗算値だけの数のAD変換部を有する。 40

【0009】

本技術の制御方法は、光電変換によって電気信号を出力する複数の画素を有する2個以

50

上の共有画素が2次元に配列された画素アレイ部と、前記共有画素の配列のうちの、複数行の共有画素から同時に読み出される電気信号を処理するカラム処理部とを備え、前記共有画素の1列に対して、複数の列信号線が配線され、前記共有画素から読み出された電気信号は、前記列信号線を介して、前記カラム処理部に供給され、前記カラム処理部は、前記列信号線の一端側に設けられており、前記複数行の各列の共有画素から同時に読み出される電気信号をAD(Analog Digital)変換するAD変換部として、前記共有画素の列数に、前記複数行を乗算した乗算値だけの数のAD変換部を有するイメージセンサの前記共有画素が有する前記画素から前記電気信号を読み出すためのアクセス制御として、前記複数行のうちの1の行と他の1の行とで、異なるアクセス制御を行う。

【0010】

10

本技術の電子機器は、光を集光する光学系と、光を受光し、画像を撮像するイメージセンサとを備え、前記イメージセンサは、光電変換によって電気信号を出力する複数の画素を有する2個以上の共有画素が2次元に配列された画素アレイ部と、前記共有画素の配列のうちの、複数行の共有画素から同時に読み出される電気信号を処理するカラム処理部と、前記共有画素が有する前記画素から前記電気信号を読み出すためのアクセス制御として、前記複数行のうちの1の行と他の1の行とで、異なるアクセス制御を行う行制御部とを有し、前記共有画素の1列に対して、複数の列信号線が配線され、前記共有画素から読み出された電気信号は、前記列信号線を介して、前記カラム処理部に供給され、前記カラム処理部は、前記列信号線の一端側に設けられており、前記複数行の各列の共有画素から同時に読み出される電気信号をAD(Analog Digital)変換するAD変換部として、前記共有画素の列数に、前記複数行を乗算した乗算値だけの数のAD変換部を有する。

【0011】

20

本技術においては、光電変換によって電気信号を出力する複数の画素を有する2個以上の共有画素が2次元に配列されており、前記共有画素の配列のうちの、複数行の共有画素から同時に読み出される電気信号が処理される。前記共有画素が有する前記画素から前記電気信号を読み出すためのアクセス制御としては、前記複数行のうちの1の行と他の1の行とで、異なるアクセス制御が行われる。

【0012】

なお、イメージセンサは、独立した装置であっても良いし、1つの装置を構成している内部ブロックであっても良い。

30

【発明の効果】

【0013】

本技術によれば、共有画素を採用するイメージセンサにおいて高速撮像を行うことができる。

【0014】

なお、ここに記載された効果は必ずしも限定されるものではなく、本開示中に記載されたいづれかの効果であってもよい。

【図面の簡単な説明】

【0015】

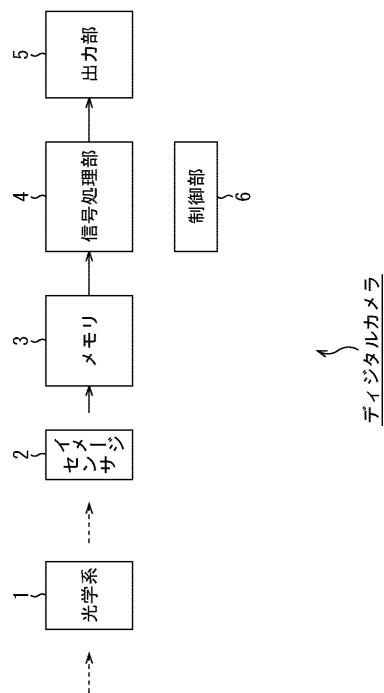

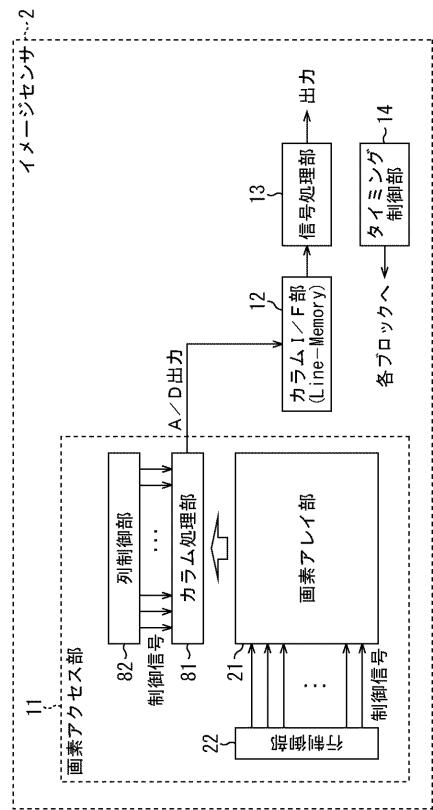

【図1】本技術を適用したデジタルカメラの一実施の形態の構成例を示すブロック図である。

40

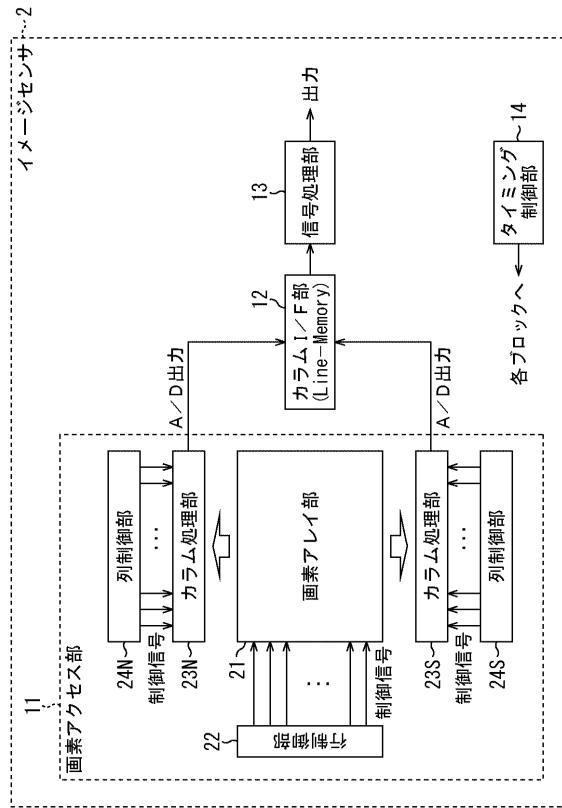

【図2】イメージセンサ2の構成例を示すブロック図である。

【図3】イメージセンサ2の構成例を示す斜視図である。

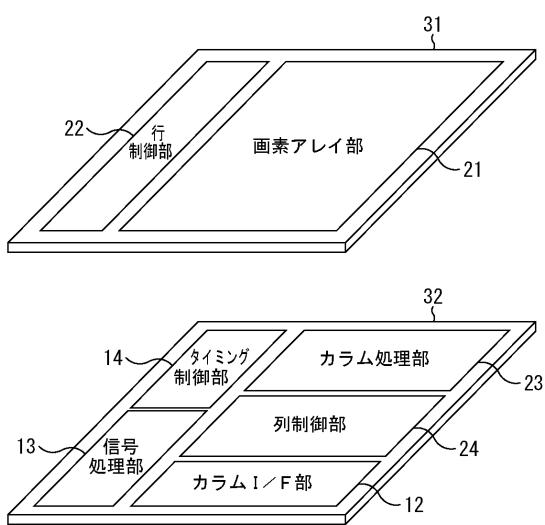

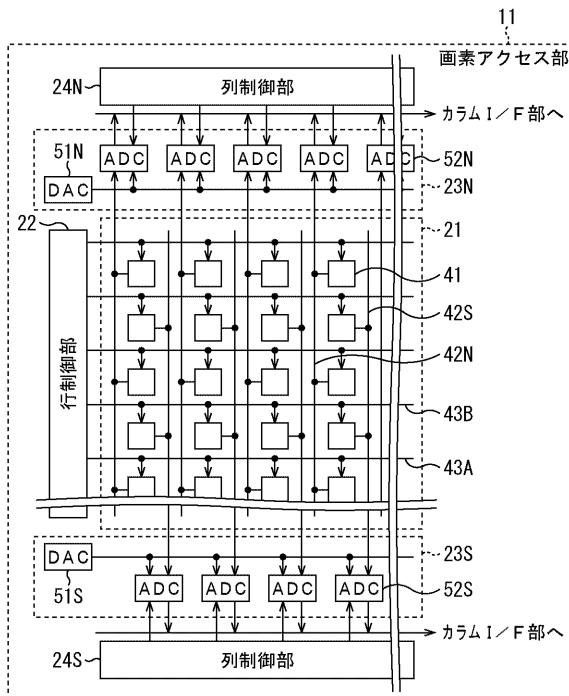

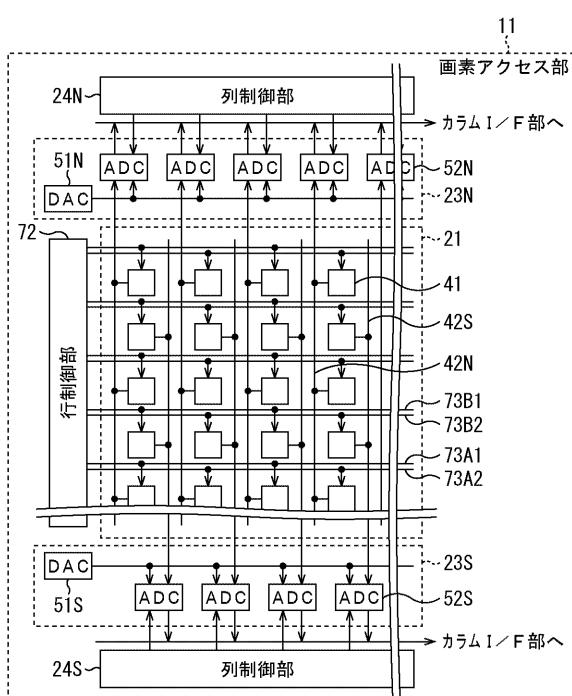

【図4】画素アクセス部11の詳細な構成例を示すブロック図である。

【図5】共有画素41の構成例を示す回路図である。

【図6】共有画素41を構成する画素の配置の例を示す図である。

【図7】2×2画素の共有画素41において、ベイヤ配列を採用した場合の、共有画素41の画素の配置の例を示す図である。

【図8】2×2画素の共有画素41からの画素信号の読み出しの例を説明する図である。

【図9】1/2間引きでの画素信号の読み出しで得られる画素値の画素重心を示す図である

50

。

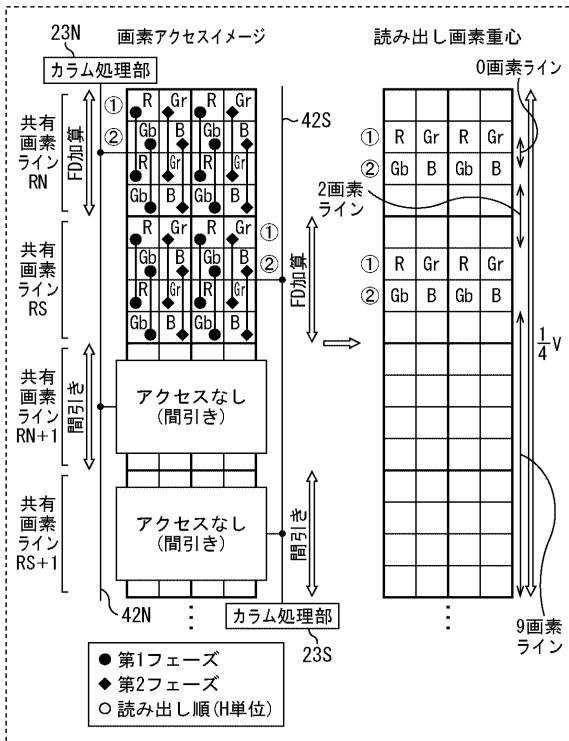

【図10】個別アクセス制御による、 $2 \times 2$ 画素の共有画素41からの、1/2間引きでの画素信号の読み出しの例を説明する図である。

【図11】1/2間引きでの画素信号の読み出しで得られる画素値の画素重心を示す図である。

【図12】 $2 \times 4$ 画素の共有画素41において、ベイヤ配列を採用した場合の、共有画素41の画素の配置の例を示す図である。

【図13】 $2 \times 4$ 画素の共有画素41からの、間引きなしでの画素信号の読み出しの例を説明する図である。

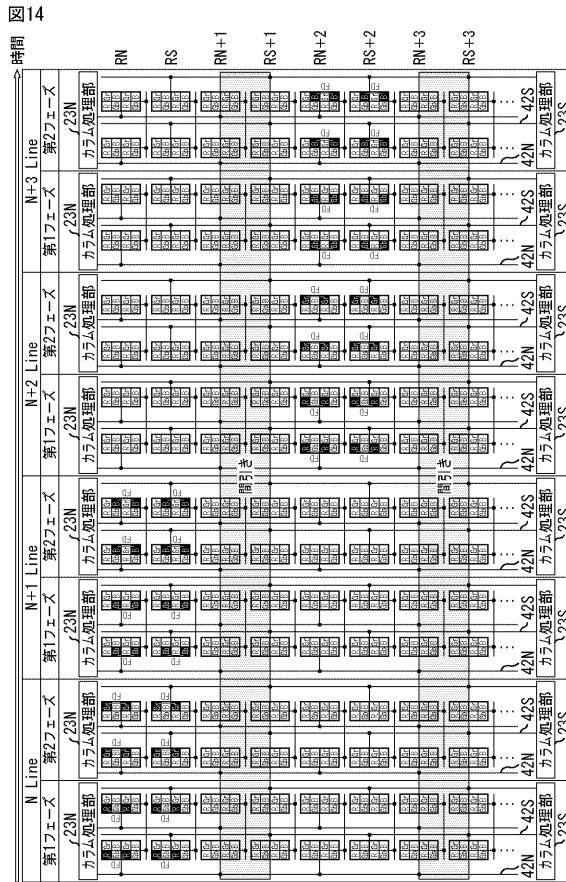

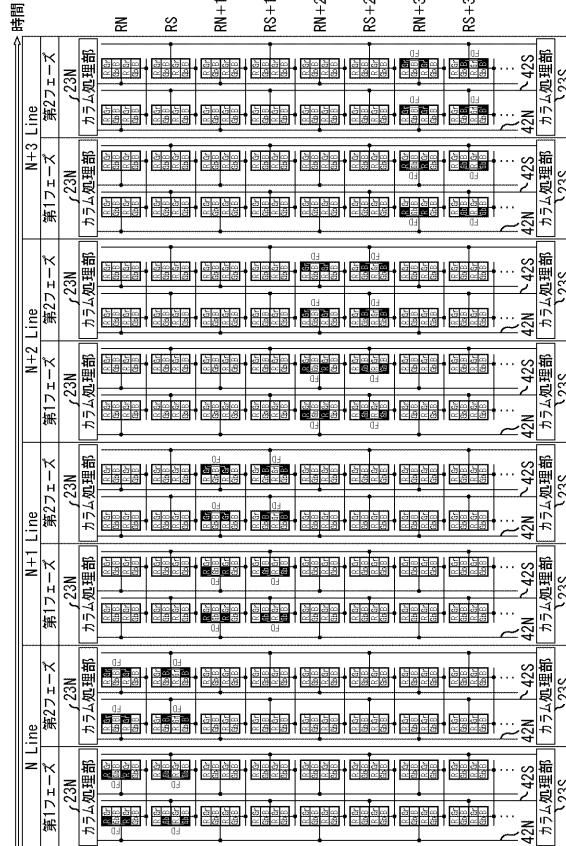

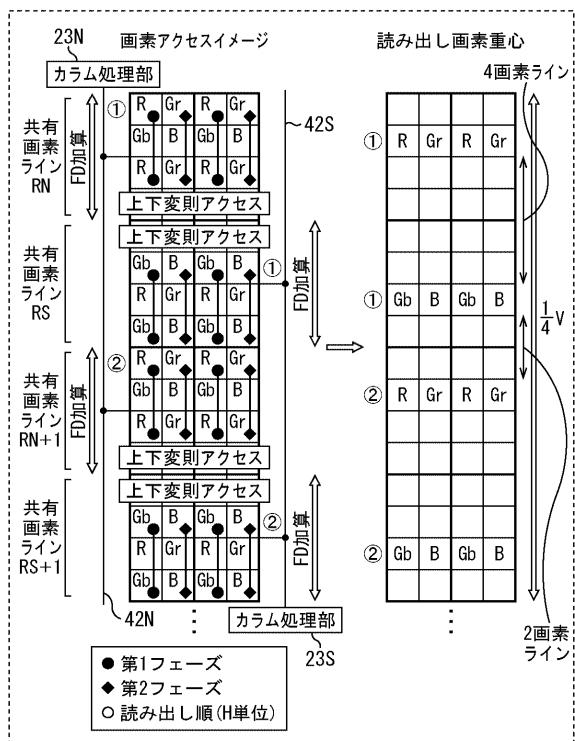

【図14】同一アクセス制御による、 $2 \times 4$ 画素の共有画素41からの、1/4間引きでの画素信号の読み出しの例を説明する図である。

10

【図15】同一アクセス制御による1/4間引きでの画素信号の読み出しで得られる画素値の画素重心を示す図である。

【図16】個別アクセス制御による、 $2 \times 4$ 画素の共有画素41からの、1/4間引きでの画素信号の読み出しの例を説明する図である。

【図17】1/4間引きでの画素信号の読み出しで得られる画素値の画素重心を示す図である。

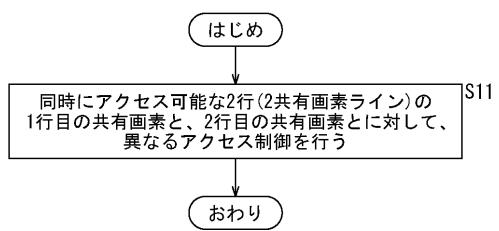

【図18】行制御部22による個別アクセス制御を説明するフローチャートである。

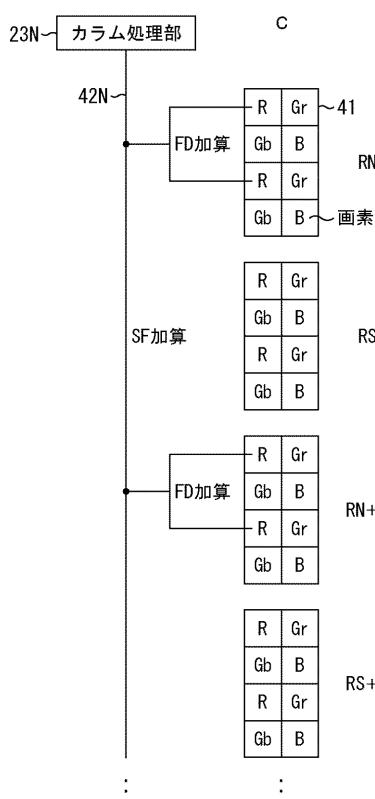

【図19】SF加算を説明する図である。

【図20】画素アクセス部11の他の詳細な構成例を示すブロック図である。

20

【図21】イメージセンサ2の他の構成例を示すブロック図である。

【発明を実施するための形態】

【0016】

<本技術を適用したデジタルカメラの一実施の形態>

【0017】

図1は、本技術を適用したデジタルカメラの一実施の形態の構成例を示すブロック図である。

【0018】

なお、デジタルカメラは、静止画、及び、動画のいずれも撮像することができる。

【0019】

図1において、デジタルカメラは、光学系1、イメージセンサ2、メモリ3、信号処理部4、出力部5、及び、制御部6を有する。

30

【0020】

光学系1は、例えば、図示せぬズームレンズや、フォーカスレンズ、絞り等を有し、外部からの光を、イメージセンサ2に入射させる。

【0021】

イメージセンサ2は、例えば、CMOS(Complementary Metal Oxide Semiconductor)イメージセンサであり、光学系1からの入射光を受光し、光電変換を行って、光学系1からの入射光に対応する画像データを出力する。

【0022】

40

メモリ3は、イメージセンサ2が出力する画像データを一時記憶する。

【0023】

信号処理部4は、メモリ3に記憶された画像データを用いた信号処理としての、例えば、ノイズの除去や、ホワイトバランスの調整等の処理を行い、出力部5に供給する。

【0024】

出力部5は、信号処理部4からの画像データを出力する。

【0025】

すなわち、出力部5は、例えば、液晶等で構成されるディスプレイ(図示せず)を有し、信号処理部4からの画像データに対応する画像を、いわゆるスルー画として表示する。

【0026】

50

また、出力部 5 は、例えば、半導体メモリや、磁気ディスク、光ディスク等の記録媒体を駆動するドライバ(図示せず)を有し、信号処理部 4 からの画像データを記録媒体に記録する。

【0027】

制御部 6 は、ユーザの操作等に従い、デジタルカメラを構成する各ブロックを制御する。

【0028】

以上のように構成されるデジタルカメラでは、イメージセンサ 2 が、光学系 1 からの入射光を受光し、その入射光に応じて、画像データを出力する。

【0029】

イメージセンサ 2 が出力する画像データは、メモリ 3 に供給されて記憶される。メモリ 3 に記憶された画像データについては、信号処理部 4 による信号処理が施され、その結果得られる画像データが、出力部 5 に供給されて出力される。

【0030】

<イメージセンサ 2 の構成例>

【0031】

図 2 は、図 1 のイメージセンサ 2 の構成例を示すブロック図である。

【0032】

図 2において、イメージセンサ 2 は、画素アクセス部 11、カラムI/F(Interface)部 12、信号処理部 13、及び、タイミング制御部 14 を有する。

【0033】

画素アクセス部 11 は、光電変換を行う画素を内蔵し、その画素にアクセスして、画像データとなる画素値を取得して出力する。

【0034】

すなわち、画素アクセス部 11 は、画素アレイ部 21、行制御部 22、カラム処理部 23N 及び 23S、並びに、列制御部 24N 及び 24S を有する。

【0035】

画素アレイ部 21 は、光電変換によって電気信号を出力する複数の画素を有する 2 個以上の共有画素が 2 次元に規則的に配列されて構成される。

【0036】

画素アレイ部 21 は、行制御部 22 の制御にしたがって、画素アレイ部 21 を構成する画素から電気信号を読み出し、カラム処理部 23N 及び 23S に供給する。

【0037】

行制御部 22 は、画素アレイ部 21 の共有画素が有する画素から電気信号を読み出すためのアクセス制御を行う。

【0038】

カラム処理部 23N 及び 23S は、画素アレイ部 21 から供給される電気信号(電圧)のAD変換等の処理を行い、その結果得られるデジタル信号を、画素値として、カラムI/F部 12 に供給する。

【0039】

列制御部 24N は、カラム処理部 23N の処理によって得られた画素値を、カラムI/F部 12 に供給(出力)するための制御である列制御を行う。

【0040】

列制御部 24S は、カラム処理部 23S の処理によって得られた画素値を、カラムI/F部 12 に供給するための列制御を行う。

【0041】

カラムI/F部 12 は、ラインメモリを内蔵し、画素アクセス部 11 (のカラム処理部 23N 及び 23S) からの画素値を一時記憶することで、その画素値を受け取るインターフェースとして機能する。

【0042】

10

20

30

40

50

信号処理部 13 は、カラム I/F 部 12 に記憶された画素値を用いて、画素の並べ替えや、画素重心の補正、その他の必要な信号処理を行って、イメージセンサ 2 の外部（例えば、メモリ 3（図 1））に出力する。

【0043】

タイミング制御部 14 は、イメージセンサ 2 を構成する各ブロックの動作のタイミングを制御するタイミング信号を生成し、必要なブロックに供給する。

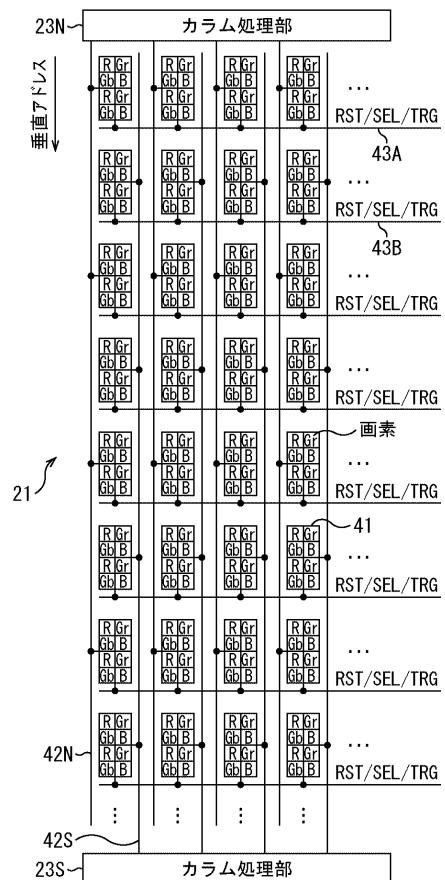

【0044】

図 3 は、図 1 のイメージセンサ 2 の構成例を示す斜視図である。

【0045】

イメージセンサ 2 は、1 つのペアチップで構成することもできるし、上下に積層される 10 2 つのペアチップで構成することもできる。

【0046】

図 3 は、イメージセンサ 2 を、上下に積層される 2 つのペアチップにより構成する場合の、その 2 つのペアチップの概要の構成例を示す斜視図である。

【0047】

図 3 では、上下に積層される 2 つのペアチップのうちの上側に積層される上チップ 31 に、画素アレイ部 21、及び、行制御部 22 が形成されている。

【0048】

さらに、図 3 では、2 つのペアチップのうちの下側に積層される下チップ 32 に、カラム I/F 部 12、信号処理部 13、タイミング制御部 14、カラム処理部 23N 及び 23S 20 を含むカラム処理部 23、並びに、列制御部 24N 及び 24S を含む列制御部 24 が形成されている。

【0049】

イメージセンサ 2 は、以上のような上チップ 31 と下チップ 32 とを積層することにより、積層型イメージセンサとして構成することができる。

【0050】

<画素アクセス部 11 の詳細構成例>

【0051】

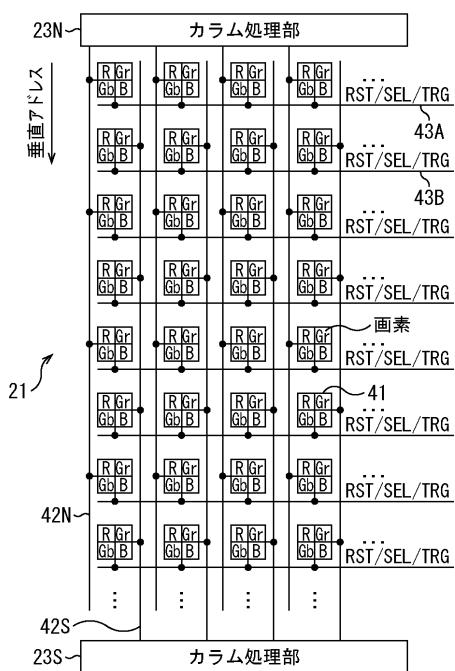

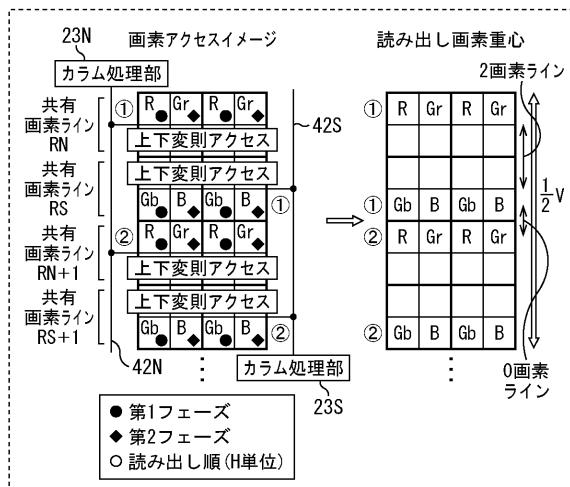

図 4 は、図 2 の画素アクセス部 11 の詳細な構成例を示すブロック図である。

【0052】

図 2 で説明したように、画素アクセス部 11 は、画素アレイ部 21、行制御部 22、カラム処理部 23N 及び 23S、並びに、列制御部 24N 及び 24S を有する。

【0053】

画素アレイ部 21 は、2 個以上の共有画素 41 が 2 次元に規則的に配列されて構成される。

【0054】

ここで、共有画素 41 は、光電変換によって電気信号を出力する複数の画素を有するが、詳細については、後述する。

【0055】

また、図 4 では、画素アレイ部 21 において、共有画素 41 は、行列状に配列されているが、共有画素 41 は、その他、例えば、偶数行の共有画素 41 が、奇数行の共有画素 41 に対して、共有画素 41 どうしの水平方向の間隔の 1/2 だけずれた位置になるように配列することができる。

【0056】

画素アレイ部 21 では、共有画素 41 の 1 列に対して、複数としての、例えば、2 本の列信号線 42N 及び 42S が、列方向（上下方向）に配線されている。

【0057】

図 4 では、列信号線 42N は、共有画素 41 の列の左側に配線され、奇数行の共有画素 41 と接続されている。また、列信号線 42S は、共有画素 41 の列の右側に配線され、偶数行の共有画素 41 と接続されている。

10

20

30

40

50

## 【0058】

さらに、列信号線42N及び42Sの一端側としての上側には、カラム処理部23Nが設けられており、他端側としての下側には、カラム処理部23Sが設けられている。

## 【0059】

そして、列信号線42Nは、上側(North側)のカラム処理部23Nに接続されており、列信号線42Sは、下側(South側)のカラム処理部23Sに接続されている。

## 【0060】

したがって、図4では、奇数行の共有画素41から読み出された電気信号は、列信号線42Nを介して、カラム処理部23Nに供給される。また、偶数行の共有画素41から読み出された電気信号は、列信号線42Sを介して、カラム処理部23Sに供給される。 10

## 【0061】

以上のように、奇数行の共有画素41と接続されている列信号線42Nは、カラム処理部23Nに接続され、偶数行の共有画素41と接続されている列信号線42Sは、カラム処理部23Sに接続されているので、画素アクセス部11では、例えば、ある奇数行RNの各列の共有画素41と、その奇数行の次の行としての偶数行RSの各列の共有画素41とから、電気信号を同時に読み出して処理することができる。

## 【0062】

すなわち、ある奇数行RNの各列の共有画素41から読み出された電気信号については、列信号線42Nを介して、カラム処理部23Nに供給して処理することができる。

## 【0063】

また、奇数行RNの次の行の偶数行RSの各列の共有画素41から読み出された電気信号については、列信号線42Sを介して、カラム処理部23Sに供給して処理することができる。 20

## 【0064】

以上のように、カラム処理部23N及び23Sでは、奇数行RN及び偶数行RSの2行の各列の共有画素41から同時に読み出された電気信号を処理することができる。

## 【0065】

画素アレイ部21では、共有画素41の各行に対して、行信号線43A又は43Bが、行方向(左右方向)に配線されている。

## 【0066】

行信号線43Aは、奇数行に配線されており、行制御部22は、行信号線43Aに制御信号を供給する(流す)ことで、奇数行の共有画素41に対するアクセス制御を行う。 30

## 【0067】

行信号線43Bは、偶数行に配線されており、行制御部22は、行信号線43Bに制御信号を供給することで、偶数行の共有画素41に対するアクセス制御を行う。

## 【0068】

行信号線43Aと43Bとは、いわば別系統の信号線であり、行制御部22は、別系統の信号線である行信号線43Aと43Bとには、異なる制御信号を供給することができる。

## 【0069】

これにより、行制御部22は、電気信号が同時に読み出される奇数行RN及び偶数行RSの2行の共有画素41に対し、奇数行RNと偶数行RSとで、異なるアクセス制御を行うことができる。 40

## 【0070】

カラム処理部23Nは、DAC(Digital Analog Converter)51Nと、画素アレイ部21を構成する共有画素41の列数と同一の数のADC(AD Converter)52Nとを有する。

## 【0071】

DAC51Nは、DA変換を行うことにより、例えば、ランプ(ramp)信号のような一定の傾きで、所定の初期値から所定の最終値までレベルが変化する期間を有するアナログの参照信号を生成し、ADC52Nに供給する。 50

## 【0072】

いま、共有画素41の列数をXで表すこととすると、X個のADC52Nのうちのx番目(x=1,2,...,X)のADC52Nは、x列目の列信号線42Nに接続されており、したがって、x番目のADC52Nには、x列目の共有画素41から読み出された電気信号が、x列目の列信号線42Nを介して供給される。

## 【0073】

x番目のADC52Nは、x列目の共有画素41から、x列目の列信号線42Nを介して供給される電気信号と、DAC51Nから供給される参照信号とを比較し、それらの電気信号と参照信号とのレベルが一致するまでの、参照信号のレベルの変化に要する時間をカウントすることで、電気信号のAD変換等を行う。

10

## 【0074】

そして、ADC52Nは、列制御部24Nの制御に従い、AD変換等の結果得られるデジタルの電気信号である画素値を、カラムI/F部12(図2)に出力する。

## 【0075】

カラム処理部23Sは、DAC51Sと、画素アレイ部21を構成する共有画素41の列数Xと同一の数であるX個のADC52Sとを有する。

## 【0076】

DAC51Sは、DAC51Nと同様に、参照信号を生成し、ADC52Sに供給する。

## 【0077】

X個のADC52Sのうちのx番目のADC52Sは、x列目の列信号線42Sに接続されており、したがって、x番目のADC52Sには、x列目の共有画素41から読み出された電気信号が、x列目の列信号線42Sを介して供給される。

20

## 【0078】

x番目のADC52Sは、ADC52Nと同様に、x列目の共有画素41から、x列目の列信号線42Nを介して供給される電気信号のAD変換等を、DAC51Nから供給される参照信号を用いて行う。

## 【0079】

そして、ADC52Sは、列制御部24Sの制御に従い、AD変換等の結果得られるデジタルの電気信号である画素値を、カラムI/F部12(図2)に出力する。

## 【0080】

30

なお、DAC51Nと51Sとは、1個のDACで兼用することができる。

## 【0081】

<共有画素41の構成例>

## 【0082】

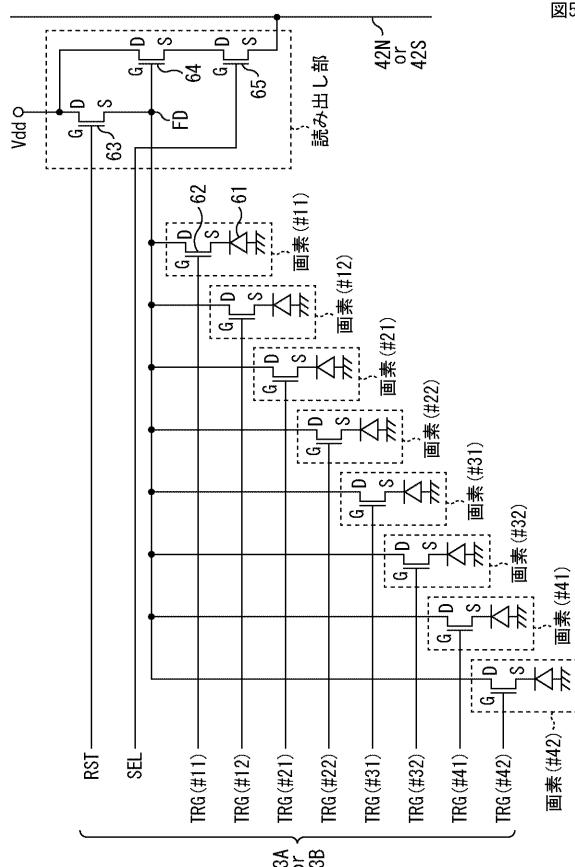

図5は、共有画素41の構成例を示す回路図である。

## 【0083】

図5の共有画素41は、複数としての、例えば、8個の画素と、FET(Field Effect Transistor)63, 64、及び、65とを有する。

## 【0084】

画素は、PD(Photo Diode)61とFET62とを有し、光電変換によって電気信号を出力する。

40

## 【0085】

PD61は、光電変換素子の一例であり、入射光を受光して、その入射光に対応する電荷を蓄積することにより、光電変換を行う。

## 【0086】

PD61のアノードはグランド(ground)に接続され(接地され)、PD61のカソードは、FET62のソースに接続されている。

## 【0087】

FET62は、PD61に蓄積された電荷を、PD61からFDに転送するためのトランジスタ(Tr)であり、以下、転送Tr62ともいう。

50

## 【0088】

転送Tr62のソースは、PD61のカソードに接続され、転送Tr62のドレインは、FDを介して、FET64のゲートに接続されている。

## 【0089】

また、転送Tr62のゲートは、行制御線43A又は43Bに接続されており、転送Tr62のゲートには、行制御線43A又は43Bを介して、転送パルスTRG(#11,#12,#21,#22,#31,#32,#41,#42)が供給される。

## 【0090】

ここで、行制御部22(図4)が、行制御線43A又は43Bを介して、共有画素41を駆動(アクセス制御)するために、行制御線43A又は43Bに流す制御信号には、転送パルスTRGの他、後述するリセットパルスRST、及び、選択パルスSELがある。

10

## 【0091】

また、FDは、FET63のソースとFET64のゲートとの接続点に形成された領域であり、FDでは、そこに供給された電荷が、コンデンサの如く電圧に変換される。

## 【0092】

図5では、簡略化のため、8個の画素が、1個のFDを共有するように、共有画素41が図示されているが、例えば、共有画素41には、2個のFDを形成し、その2個のFDのうちの1個のFDを、4画素で共有するとともに、他の1個のFDを、残りの4画素で共有することができる。

20

## 【0093】

FET63は、FDに蓄積された電荷(電圧(電位))をリセットするためのトランジスタであり、以下、リセットTr63ともいう。

## 【0094】

リセットTr63のドレインは、電源Vddに接続され、ソースは、FDに接続されている。

## 【0095】

また、リセットTr63のゲートは、行制御線43A又は43Bに接続されており、リセットTr63のゲートには、行制御線43A又は43Bを介して、リセットパルスRSTが供給される。

## 【0096】

FET64は、FDの電圧を増幅するためのトランジスタであり、以下、増幅Tr64ともいう。

30

## 【0097】

増幅Tr64のゲートは、FDに接続され、増幅Tr64のドレインは、電源Vddに接続されている。また、増幅Tr64のソースは、FET65のドレインに接続されている。

## 【0098】

FET65は、列信号線42N又は42Sへの電気信号(電圧)の出力を選択するためのFETであり、以下、選択Tr65ともいう。

## 【0099】

選択Tr65のソースは、列信号線42N又は42Sに接続されている。

## 【0100】

また、選択Tr65のゲートは、行制御線43A又は43Bに接続されており、選択Tr65のゲートには、行制御線43A又は43Bを介して、選択パルスSELが供給される。

40

## 【0101】

なお、選択Tr65のソースに接続されている列信号線42N及び42Sには、図示せぬ電流源が接続されており、この電流源と、増幅Tr64、及び、選択Tr65とは、SF(Source Follower)の回路を構成している。したがって、FDは、SFの回路を介して、列信号線42N又は42Sに接続されている。

## 【0102】

ここで、共有画素41は、選択Tr65なしで構成することができる。

## 【0103】

50

また、図5の構成において、8個の画素を、1個の画素だけにした構成は、単位画素と呼ばれる。

【0104】

以上のように構成される共有画素41では、PD61は、そこに入射する光を受光し、光電変換を行うことにより、受光した入射光の光量に応じた電荷の蓄積を開始する。なお、ここでは、説明を簡単にするために、選択パルスSELはHレベルになっており、選択Tr65はオン状態であることとする。

【0105】

PD61での電荷の蓄積が開始されてから、所定の時間（露光時間）が経過すると、行制御部22（図4）は、転送パルスTRGを、一時的に、（L（Low）レベルから）H（High）レベルにする。

10

【0106】

転送パルスTRGが一時的にHレベルになることにより、転送Tr62は、一時的に、オン状態になる。

【0107】

転送Tr62がオン状態になると、PD61に蓄積された電荷は、転送Tr62を介して、FDに転送されて蓄積される。

【0108】

行制御部22は、転送パルスTRGを一時的にHレベルにする前に、リセットパルスRSTを、一時的に、Hレベルにし、これにより、リセットTr63を、一時的に、オン状態にする。

20

【0109】

リセットTr63がオン状態になることにより、FDは、リセットTr63を介して、電源Vddに接続され、FDにある電荷は、リセットTr63を介して、電源Vddに掃き出されてリセットされる。

【0110】

ここで、以上のように、FDが、電源Vddに接続され、FDにある電荷がリセットされることを、共有画素41のリセットともいう。

【0111】

FDの電荷のリセット後、行制御部22は、上述のように、転送パルスTRGを、一時的に、Hレベルにし、これにより、転送Tr62は、一時的に、オン状態になる。

30

【0112】

転送Tr62がオン状態になることにより、PD61に蓄積された電荷は、転送Tr62を介して、リセット後のFDに転送されて蓄積される。

【0113】

そして、FDに蓄積された電荷に対応する電圧（電位）が、増幅Tr64及び選択Tr65を介して、信号線電圧（電気信号）として、列信号線42N又は42S上に出力される。

【0114】

列信号線42N又は42Sに接続されているADC52N又は52S（図4）では、共有画素41のリセットが行われた直後の信号線電圧であるリセットレベルがAD変換される。

40

【0115】

さらに、ADC52N又は52Sでは、転送Tr62が一時的にオン状態になった後の信号線電圧（PD61に蓄積され、FDに転送された電荷に対応する電圧）である信号レベル（リセットレベルと、画素値となるレベルとを含む）がAD変換される。

【0116】

そして、ADC52N又は52Sでは、リセットレベルのAD変換結果と、信号レベルのAD変換結果との差分を、画素値として求めるCDS(Correlated Double Sampling)が行われ、そのCDSの結果得られる電気信号が、画素値として、カラムI/F部12（図2）に出力される。

【0117】

50

以上のようにして、共有画素 4 1 の 1 個の画素から画素値が読み出される。

【0118】

行制御部 2 2 は、8 個の画素について、例えば、転送Tr 6 2 を順番にオン状態にすることで、8 個の画素から、順番に、画素値を読み出す。

【0119】

ここで、以下では、説明を簡単にするため、共有画素 4 1 (の画素)からの、画素値となる電気信号である画素信号の読み出しには、CDSは、考慮しないこととする。

【0120】

なお、図 5において、リセットTr 6 3、増幅Tr 6 4、選択Tr 6 5、及び、FDが、画素から画素信号を読み出す読み出し部を構成する。

10

【0121】

図 5 の共有画素 4 1 では、8 個の画素で、読み出し部が共有されているが、共有画素 4 1 を構成する画素の数は、8 個に限定されるものではなく、2 個や 4 個等の任意の個数を採用することができる。

【0122】

図 6 は、共有画素 4 1 を構成する画素の配置の例を示す図である。

【0123】

図 6 A は、4 個の画素を有する共有画素 4 1 の画素の配置の例を示す図である。

【0124】

共有画素 4 1 が 4 個の画素を有する場合、その 4 個の画素は、例えば、図 6 A に示すように、横 × 縦 (行方向 × 列方向) が  $2 \times 2$  画素になるように配置することができる。

20

【0125】

図 6 B は、8 個の画素を有する共有画素 4 1 の画素の配置の例を示す図である。

【0126】

共有画素 4 1 が 8 個の画素を有する場合、その 8 個の画素は、例えば、図 6 B に示すように、横 × 縦が  $2 \times 4$  画素になるように配置することができる。

【0127】

<  $2 \times 2$  画素の共有画素 4 1 >

【0128】

図 7 は、 $2 \times 2$  画素の共有画素 4 1 ( $2 \times 2$  画素に配置されている 4 画素を有する共有画素 4 1)において、カラーフィルタのパターンとして、ベイヤ(BAYER)配列を採用した場合の、共有画素 4 1 の画素の配置の例を示す図である。

30

【0129】

図 7において、共有画素 4 1 が有する  $2 \times 2$  画素のうちの、左上の画素は、R(Red)成分の光を受光するR画素として機能し、右上の画素は、G成分の光を受光するGr画素として機能する。また、左下の画素は、G成分の光を受光するGb画素として機能し、右下の画素は、B(Blue)成分の光を受光するB画素として機能する。

【0130】

図 8 は、図 7 に示した  $2 \times 2$  画素の共有画素 4 1 からの画素信号の読み出しの例を説明する図である。

40

【0131】

ここで、1 行の共有画素 4 1 の並びを、共有画素ラインともいい、1 行の画素の並びを、画素ラインともいう。

【0132】

本実施の形態では、1 共有画素ラインを構成する共有画素 4 1 の数は、共有画素 4 1 の列数Xに等しい。また、1 画素ラインを構成する画素の数は、共有画素 4 1 が、 $2 \times 2$  画素で構成される場合には、共有画素 4 1 の列数Xの 2 倍に等しい。

【0133】

また、奇数番目の共有画素ラインを、奇数共有画素ラインともいい、偶数番目の共有画素ラインを、偶数共有画素ラインともいう。

50

## 【0134】

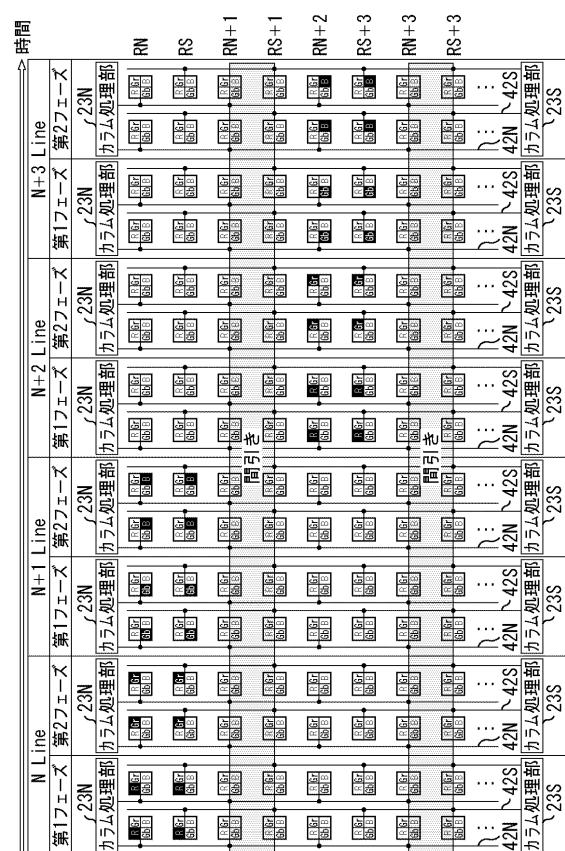

さらに、以下では、ADC52N及び52S(図4)は、いずれも、1画素ラインの期間に、2回のAD変換を行うことができる速度で動作することとする。ADC52N及び52Sで行われる1回目のAD変換を、第1フェーズともいい、2回目のAD変換を、第2フェーズともいう。

## 【0135】

なお、図8は、連続する2列の共有画素41からの画素信号の読み出しの様子を示しているが、他の列の共有画素41からも、同様にして、画素信号の読み出しが行われる。また、図8において、横軸は、1画素ラインの期間ごとの時間を表す。以上の点、後述する図でも、同様である。

10

## 【0136】

図8において、N番目の第N画素ライン(N Line)の期間の第1フェーズでは、奇数共有画素ラインRNの共有画素41の左上のR画素から、図中、白抜きで示すように、画素信号が読み出され、列信号線42Nを介して、カラム処理部23N(のADC52N)に供給されてAD変換される。

## 【0137】

さらに、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの次の偶数共有画素ラインRSの共有画素41の左上のR画素から、画素信号が読み出され、列信号線42Sを介して、カラム処理部23S(のADC52S)に供給されてAD変換される。

20

## 【0138】

図4で説明したように、画素アレイ部21は、共有画素41の1列に対して、2本の列信号線42N及び42Sが配線されているので、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ライン(の各列)から、同時に、画素信号を読み出すことができる。

## 【0139】

その後、第N画素ラインの期間の第2フェーズにおいて、奇数共有画素ラインRNの共有画素41の右上のGr画素から、画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

## 【0140】

さらに、第N画素ラインの期間の第2フェーズでは、偶数共有画素ラインRSの共有画素41の右上のGr画素から、画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

30

## 【0141】

次の第N+1画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの共有画素41の左下のGb画素から、画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

## 【0142】

同時に、偶数共有画素ラインRSの共有画素41の左下のGb画素から、画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

## 【0143】

その後の第N+1画素ラインの期間の第2フェーズでは、奇数共有画素ラインRNの共有画素41の右下のB画素から、画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

40

## 【0144】

同時に、偶数共有画素ラインRSの共有画素41の右下のB画素から、画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

## 【0145】

以上のようにして、2画素ラインの期間に、2画素ラインよりも多い2共有画素ラインの画素のすべてから、画素信号を読み出すことができる。

## 【0146】

50

したがって、以下、同様にして、奇数共有画素ラインRN及び偶数共有画素ラインRSの2共有画素ライン以外の共有画素ラインの共有画素41からの画素信号の読み出しを、2共有画素ラインの単位で、順番に行うことにより、イメージセンサ2では、所定のフレームレートで、すべての共有画素41のすべての画素から、画素信号を読み出す通常撮像を行うことができる。

【0147】

ところで、イメージセンサ2では、画素信号の読み出し（画素信号の、カラム処理部23N及び23Sへの供給）を、画素ラインを間引いて行うことにより、所定のフレームレートよりも高速なフレームレートでの撮像である高速撮像を行うことができる。

【0148】

画素ラインを間引く方法としては、例えば、一部の画素ラインを読み飛ばす（画素信号を読み出さない）方法がある。

【0149】

図8では、8画素ライン（4共有画素ライン）につき、4画素ライン（2共有画素ライン）の割合で画素ラインを読み飛ばす1/2読み飛ばしを行うことで、画素ラインを1/2に間引く1/2間引きが行われている。

【0150】

すなわち、図8では、奇数共有画素ラインRN、及び、偶数共有画素ラインRSの2共有画素ラインの共有画素41（の4画素）から、画素信号が読み出された後、その後に続く奇数共有画素ラインRN+1、及び、偶数共有画素ラインRS+1の2共有画素ラインの共有画素41（の4画素）の画素信号が読み飛ばされている。

【0151】

そして、次の奇数共有画素ラインRN+2、及び、偶数共有画素ラインRS+2の2共有画素ラインの共有画素41から、画素信号が読み出され、その後に続く奇数共有画素ラインRN+3、及び、偶数共有画素ラインRS+3の2共有画素ラインの共有画素41の画素信号が読み飛ばされている。

【0152】

以下、同様にして、画素信号を読み出すことで、1/2間引きを行うことができる。

【0153】

1/2間引きでの画素信号の読み出しによれば、通常撮像時のフレームレートの2倍のフレームレートでの高速撮像を行うことができる。

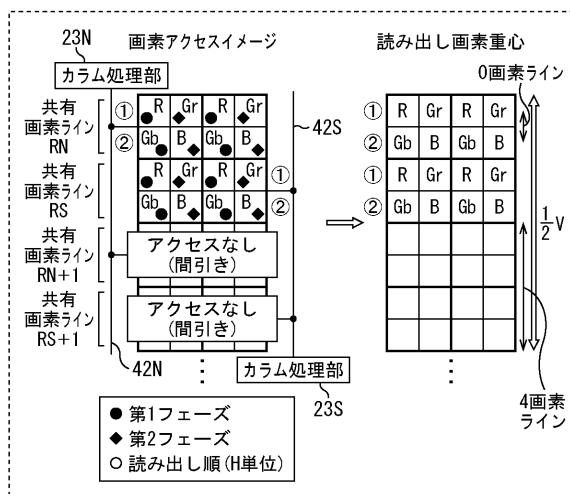

【0154】

図9は、図8の1/2間引きでの画素信号の読み出しで得られる画素値の画素重心（画素値を有する画素の位置）を示す図である。

【0155】

図8の1/2間引きでの画素信号の読み出しへは、上述したように、2共有画素ラインの共有画素41から、画素信号が読み出され、その後に続く2共有画素ラインの共有画素41の画素信号が読み飛ばされることが繰り返される。

【0156】

この場合、共有画素41のある位置posの画素から読み出された画素信号から得られる画素値は、その位置posを画素重心とする画素の画素値になるので、1フレームの画像は、2共有画素ラインおきに、2共有画素ライン分の画素値が存在する、共有画素ラインが1/2に間引かれた画像、すなわち、4画素ラインおきに、4画素ライン分の画素値が存在する、画素ラインが1/2に間引かれた画像（通常撮像で画素信号を読み出す画素ラインの数Vの1/2の数V/2の画素ラインの画像）になる。

【0157】

したがって、図8の1/2間引きでの画素信号の読み出しで得られる画像では、画素値を有する画素ラインの間隔（画素値が得られる画素の垂直方向の間隔）（以下、画素値のサンプリング間隔ともいう）は、図9に示すように、等間隔ではなく、0画素ラインである場合と、4画素ラインである場合とがある。

10

20

30

40

50

## 【0158】

以上のように、画素値のサンプリング間隔が、0画素ラインと4画素ラインのように、大きく異なる場合には、特に、高周波数成分を有する画像については、モアレや偽色が発生し、画質が低下することがある。

## 【0159】

なお、図9において、丸印を付した数字は、1画素ラインの期間での画素信号の読み出し順を表す。また、黒丸印は、第1フェーズで画素信号がAD変換される画素を表し、黒く塗りつぶしたひし形は、第2フェーズで画素信号がAD変換される画素を表す。以下の図でも、同様である。

## 【0160】

ところで、図8の1/2間引きでの画素信号の読み出しでは、例えば、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインから、同時に、画素信号を読み出すにあたり、共有画素41の同一の位置の画素から、画素信号が読み出されている。

## 【0161】

すなわち、例えば、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインから、同時に、画素信号が読み出されるが、その画素信号の読み出しの対象の画素（以下、読み出し対象画素ともいう）は、奇数共有画素ラインRN、及び、偶数共有画素ラインRSのいずれについても、共有画素41の左上のR画素である。

## 【0162】

以上のように、2つの共有画素ラインから、同時に、画素信号を読み出すにあたり、読み出し対象画素が、2つの共有画素ラインの共有画素41の同一の位置の画素である場合には、画素信号を間引いて読み出したときに、図9で説明したように、画素値のサンプリング間隔が大きく異なる画像が得られる。

## 【0163】

ところで、図4で説明したように、行信号線43Aと43Bとは、別系統の信号線であり、行制御部22は、行信号線43Aと43Bとには、異なる制御信号を供給することで、画素信号（電気信号）が同時に読み出される2行（2共有画素ライン）の共有画素41に対し、奇数行（奇数共有画素ライン）RNと偶数行（偶数共有画素ライン）RSとで、異なるアクセス制御を行うことができる。

## 【0164】

したがって、行制御部22では、例えば、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインから、同時に、画素信号を読み出すにあたり、その2つの共有画素ラインそれぞれについて、共有画素41の別個の位置の画素から、画素信号を読み出すアクセス制御（以下、個別アクセス制御ともいう）を行うことができる。

## 【0165】

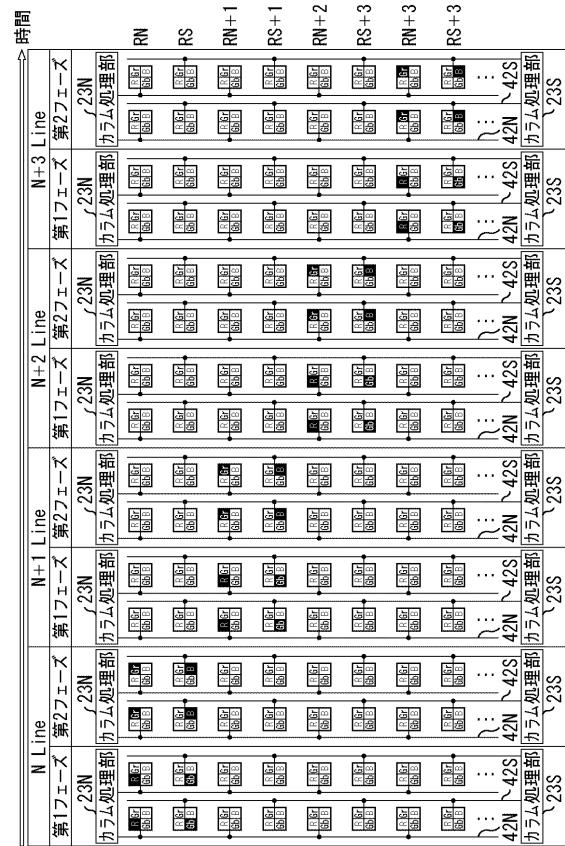

図10は、個別アクセス制御による、2×2画素の共有画素41からの、1/2間引きでの画素信号の読み出しの例を説明する図である。

## 【0166】

個別アクセス制御によれば、2×2画素の共有画素41について、1/2間引きでの画素信号の読み出しが、以下のように行うことができる。

## 【0167】

すなわち、図10において、第N画素ライン(N Line)の期間の第1フェーズでは、奇数共有画素ラインRNの共有画素41の左上のR画素から、図中、白抜きで示すように、画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

## 【0168】

さらに、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの次の偶数共有画素ラインRSの共有画素41の、左上ではなく、左下のGb画素から、画素信号が読み

10

20

30

40

50

出され、列信号線 4 2 S を介して、カラム処理部 2 3 S に供給されてAD変換される。

【 0 1 6 9 】

以上のように、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインから、同時に、画素信号が読み出されるが、個別アクセス制御によれば、奇数共有画素ラインRNの共有画素 4 1については、左上のR画素から、画素信号を読み出し、偶数共有画素ラインRSの共有画素 4 1については、左上とは異なる位置の左下のGb画素から、画素信号を読み出すことができる。

【 0 1 7 0 】

その後、第N画素ラインの期間の第2フェーズにおいて、奇数共有画素ラインRNの共有画素 4 1 の右上のGr画素から、画素信号が読み出され、列信号線 4 2 N を介して、カラム処理部 2 3 N に供給されてAD変換される。 10

【 0 1 7 1 】

さらに、第N画素ラインの期間の第2フェーズでは、偶数共有画素ラインRSの共有画素 4 1 の、右上ではなく、右下のB画素から、画素信号が読み出され、列信号線 4 2 S を介して、カラム処理部 2 3 S に供給されてAD変換される。

【 0 1 7 2 】

以上のように、第N画素ラインの期間の第2フェーズでは、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインから、同時に、画素信号が読み出されるが、個別アクセス制御によれば、奇数共有画素ラインRNの共有画素 4 1については、右上のGr画素から、画素信号を読み出し、偶数共有画素ラインRSの共有画素 4 1については、右上とは異なる位置の右下のB画素から、画素信号を読み出すことができる。 20

【 0 1 7 3 】

ここで、 $2 \times 2$  画素の共有画素 4 1 の並びの共有画素ラインは、2画素ラインであるから、画素信号が同時に読み出される奇数共有画素ラインRNと偶数共有画素ラインRSとの2つの共有画素ラインは、4画素ラインである。

【 0 1 7 4 】

第N画素ラインの期間では、上述のようにして、2つの共有画素ラインである4画素ラインのうちの、(上から)1番目及び4番目の画素ラインの画素を、読み出し対象画素として、その読み出し対象画素の画素信号が読み出され、残りの2番目及び3番目の画素ラインの画素の画素信号は、読み飛ばされる。 30

【 0 1 7 5 】

次の第N+1画素ラインの期間の第1フェーズでは、偶数共有画素ラインRSの次の奇数共有画素ラインRN+1の共有画素 4 1 の左上のR画素から、画素信号が読み出され、列信号線 4 2 N を介して、カラム処理部 2 3 N に供給されてAD変換される。

【 0 1 7 6 】

同時に、奇数共有画素ラインRN+1の次の偶数共有画素ラインRS+1の共有画素 4 1 の左下のGb画素から、画素信号が読み出され、列信号線 4 2 S を介して、カラム処理部 2 3 S に供給されてAD変換される。

【 0 1 7 7 】

その後の第N+1画素ラインの期間の第2フェーズでは、奇数共有画素ラインRN+1の共有画素 4 1 の右上のGr画素から、画素信号が読み出され、列信号線 4 2 N を介して、カラム処理部 2 3 N に供給されてAD変換される。 40

【 0 1 7 8 】

同時に、偶数共有画素ラインRS+1の共有画素 4 1 の右下のB画素から、画素信号が読み出され、列信号線 4 2 S を介して、カラム処理部 2 3 S に供給されてAD変換される。

【 0 1 7 9 】

以上のように、第N+1画素ラインの期間の第1フェーズでは、奇数共有画素ラインRN+1の共有画素 4 1 の左上のR画素から、画素信号が読み出されるのと同時に、偶数共有画素ラインRS+1の共有画素 4 1 の左下のGb画素から、画素信号が読み出される。

【 0 1 8 0 】

そして、第N+1画素ラインの期間の第2フェーズでは、奇数共有画素ラインRN+1の共有画素41の右上のGr画素から、画素信号が読み出されるのと同時に、偶数共有画素ラインRS+1の共有画素41の右下のB画素から、画素信号が読み出される。

【0181】

すなわち、第N+1画素ラインの期間では、第N画素ラインの場合と同様に、2つの共有画素ラインである4画素ラインのうちの、1番目及び4番目の画素ラインの画素を、読み出し対象画素として、その読み出し対象画素の画素信号が読み出され、残りの2番目及び3番目の画素ラインの画素の画素信号は、読み飛ばされる。

【0182】

以下、同様に、2つの共有画素ラインである4画素ラインのうちの、1番目及び4番目の画素ラインの画素の画素信号を読み出すとともに、残りの2番目及び3番目の画素ラインの画素の画素信号を読み飛ばす1/2読み飛ばしが繰り返し行われることで、1/2間引きでの画素信号の読み出しが行われ、これにより、通常撮像時のフレームレートの2倍のフレームレートでの高速撮像を行うことができる。

10

【0183】

図11は、図10の1/2間引きでの画素信号の読み出しで得られる画素値の画素重心を示す図である。

【0184】

図10の1/2間引きでの画素信号の読み出しでは、上述したように、2つの共有画素ラインである4画素ラインのうちの、1番目及び4番目の画素ラインの画素の画素信号を読み出すとともに、残りの2番目及び3番目の画素ラインの画素の画素信号を読み飛ばす1/2読み飛ばしが繰り返される。

20

【0185】

この場合、共有画素41のある位置posの画素から読み出された画素信号から得られる画素値は、その位置posを画素重心とする画素の画素値になるので、1フレームの画像は、2共有画素ラインである4画素ラインごとに、その4画素ラインのうちの1番目及び4番目の2つの画素ラインの画素値が存在する、画素ラインが1/2に間引かれた画像になる。

【0186】

したがって、図10の1/2間引きでの画素信号の読み出しで得られる画像では、画素値のサンプリング間隔（画素値を有する画素ラインの間隔）は、図11に示すように、0画素ラインである場合と、2画素ラインである場合とがあり、図9の場合に比較して、等間隔に（近く）なる。

30

【0187】

その結果、図9の場合に比較して、モアレや偽色の発生に起因する画質の低下を抑制することができる。

【0188】

以上のように、共有画素41を採用するイメージセンサ2において、2つの共有画素ラインの共有画素41から、同時に、画素信号を読み出すにあたり、行制御部22において、その2つの共有画素ラインそれぞれについて、共有画素41の別個の位置の画素から、画素信号を読み出す個別アクセス制御を行う場合には、そのような個別アクセス制御を行わない場合、すなわち、2つの共有画素ラインの共有画素41の同一の位置の画素から、画素信号を読み出すアクセス制御（以下、同一アクセス制御ともいう）を行う場合に比較して、画質の低下を抑制しつつ、高速撮像を行うことができる。

40

【0189】

<2×4画素の共有画素41>

【0190】

図12は、2×4画素の共有画素41（2×4画素に配置されている8画素を有する共有画素41）において、カラーフィルタのパターンとして、ベイヤ配列を採用した場合の、共有画素41の画素の配置の例を示す図である。

50

## 【0191】

ここで、共有画素41が有する $2 \times 4$ 画素の上からi番目で左からj番目の画素の位置を、位置(i,j)と表すとともに、位置(i,j)の画素を、画素#(i,j)と表すこととする。

## 【0192】

図12において、共有画素41が有する $2 \times 4$ 画素のうちの画素#(1,1)及び#(3,1)は、R成分の光を受光するR画素として機能し、画素#(1,2)及び#(3,2)は、G成分の光を受光するGr画素として機能する。また、画素#(2,1)及び#(4,1)は、G成分の光を受光するGb画素として機能し、画素#(2,2)及び#(4,2)は、B成分の光を受光するB画素として機能する。

## 【0193】

図13は、図12に示した $2 \times 4$ 画素の共有画素41からの、間引きなしでの画素信号の読み出しの例を説明する図である。 10

## 【0194】

ここで、本実施の形態では、 $2 \times 4$ 画素の共有画素41については、1画素ラインを構成する画素の数は、共有画素41が、 $2 \times 2$ 画素で構成される場合と同様に、共有画素41の列数Xの2倍に等しい。

## 【0195】

間引きなしでの画素信号の読み出しでは、行制御部22では、例えば、個別アクセス制御を行わずに、2つの共有画素ラインの共有画素41の同一の位置の画素から、画素信号を読み出す同一アクセス制御が行われる。

## 【0196】

すなわち、図13において、第N画素ライン(N Line)の期間の第1フェーズでは、奇数共有画素ラインRNの共有画素41の位置(1,1)のR画素から、図中、白抜きで示すように、画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。 20

## 【0197】

さらに、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの次の偶数共有画素ラインRSの共有画素41の位置(1,1)のR画素から、画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

## 【0198】

以上のように、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインそれぞれの共有画素41の位置(1,1)のR画素から、画素信号が、同時に読み出される。 30

## 【0199】

その後、第N画素ラインの期間の第2フェーズにおいて、奇数共有画素ラインRNの共有画素41の位置(1,2)のGr画素から、画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

## 【0200】

さらに、第N画素ラインの期間の第2フェーズでは、偶数共有画素ラインRSの共有画素41の位置(1,2)のGr画素から、画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。 40

## 【0201】

次の第N+1画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの共有画素41の位置(2,1)のGb画素から、画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

## 【0202】

同時に、偶数共有画素ラインRSの共有画素41の位置(2,1)のGb画素から、画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

## 【0203】

その後の第N+1画素ラインの期間の第2フェーズでは、奇数共有画素ラインRNの共有画素41の位置(2,2)のB画素から、画素信号が読み出され、列信号線42Nを介して、カラ 50

ム処理部 23N に供給されてAD変換される。

【0204】

同時に、偶数共有画素ラインRSの共有画素 41 の位置(2,2)のB画素から、画素信号が読み出され、列信号線 42S を介して、カラム処理部 23S に供給されてAD変換される。

【0205】

次の第N+2画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの共有画素 41 の位置(3,1)のR画素から、画素信号が読み出され、列信号線 42N を介して、カラム処理部 23N に供給されてAD変換される。

【0206】

同時に、偶数共有画素ラインRSの共有画素 41 の位置(3,1)のR画素から、画素信号が読み出され、列信号線 42S を介して、カラム処理部 23S に供給されてAD変換される。 10

【0207】

その後の第N+2画素ラインの期間の第2フェーズでは、奇数共有画素ラインRNの共有画素 41 の位置(3,2)のGr画素から、画素信号が読み出され、列信号線 42N を介して、カラム処理部 23N に供給されてAD変換される。

【0208】

同時に、偶数共有画素ラインRSの共有画素 41 の位置(3,2)のGr画素から、画素信号が読み出され、列信号線 42S を介して、カラム処理部 23S に供給されてAD変換される。

【0209】

次の第N+3画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの共有画素 41 の位置(4,1)のGb画素から、画素信号が読み出され、列信号線 42N を介して、カラム処理部 23N に供給されてAD変換される。 20

【0210】

同時に、偶数共有画素ラインRSの共有画素 41 の位置(4,1)のGb画素から、画素信号が読み出され、列信号線 42S を介して、カラム処理部 23S に供給されてAD変換される。

【0211】

その後の第N+3画素ラインの期間の第2フェーズでは、奇数共有画素ラインRNの共有画素 41 の位置(4,2)のB画素から、画素信号が読み出され、列信号線 42N を介して、カラム処理部 23N に供給されてAD変換される。

【0212】

同時に、偶数共有画素ラインRSの共有画素 41 の位置(4,2)のB画素から、画素信号が読み出され、列信号線 42S を介して、カラム処理部 23S に供給されてAD変換される。 30

【0213】

以上のように、4画素ラインの期間に、4画素ラインよりも多い2共有画素ラインの画素のすべてから、画素信号を読み出すことが、奇数共有画素ラインRN及び偶数共有画素ラインRSの2共有画素ライン以外の共有画素ラインについても、2共有画素ラインの単位で、順番に行われることで、イメージセンサ2では、所定のフレームレートで、すべての共有画素 41 のすべての画素から、画素信号を読み出す通常撮像を行うことができる。

【0214】

図14は、同一アクセス制御による、 $2 \times 4$ 画素の共有画素 41 からの、1/4間引きでの画素信号の読み出しの例を説明する図である。 40

【0215】

ここで、画素ラインを間引く方法としては、図8ないし図11で説明した、(一部の)画素ラインを読み飛ばす方法の他、2画素ライン等の複数の画素ラインを加算することにより1画素ラインに変換するライン加算を行う方法がある。

【0216】

画素ラインを間引くライン加算を行う方法としては、FD加算を利用する方法がある。

【0217】

FD加算は、行制御部22のアクセス制御によって、共有画素 41 を構成する $2 \times 4$ 画素のうちの、異なる画素ラインの2個(以上)の画素から、画素信号を、同時に読み出すこ 50

とで行うことができる。

【0218】

すなわち、共有画素41を構成する2個(以上)の画素から、画素信号を、同時に読み出す場合には、共有画素41を構成する2個の画素(図5)の転送Tr62が、同時にオン状態にされ、その2個の画素のPD61に蓄積された電荷が、いずれも、FDに転送されて蓄積される。

【0219】

この場合、FDでは、転送Tr62が同時にオン状態にされた2個の画素のPD61に蓄積された電荷が加算され、その電荷に対して、列信号線42N又は42S上に読み出される画素信号は、2個の画素それぞれから単独で読み出される画素信号を加算した加算信号と等価の信号になる。

10

【0220】

以上のように、共有画素41を構成する2個の画素の転送Tr62が、同時にオン状態にされる場合には、その2個の画素それぞれから単独で読み出される画素信号が、いわば、FDで加算されるFD加算が行われ、そのFD加算により得られる加算信号としての画素信号が、共有画素41から読み出される。

【0221】

ここで、M画素ラインを1画素ラインに加算するライン加算を、Mライン加算ともいう。

【0222】

20

FD加算によって、例えば、2ライン加算を行うことにより、画素ラインを1/2に間引く1/2間引きを行うことができる。

【0223】

図14では、1/2読み飛ばしと、2ライン加算とを行うことで、画素ラインを1/4に間引く1/4間引きが行われている。

【0224】

すなわち、図14では、第N画素ラインの期間の第1フェーズにおいて、奇数共有画素ラインRNの共有画素41から、図中、白抜きで示すように、位置(1,1)と(3,1)のR画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

30

【0225】

さらに、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの次の偶数共有画素ラインRSの共有画素41の位置(1,1)と(3,1)のR画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

【0226】

その後、第N画素ラインの期間の第2フェーズにおいて、奇数共有画素ラインRNの共有画素41の位置(1,2)と(3,2)のGr画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

40

【0227】

さらに、第N画素ラインの期間の第2フェーズでは、偶数共有画素ラインRSの共有画素41の位置(1,2)と(3,2)のGr画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

【0228】

次の第N+1画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの共有画素41の位置(2,1)と(4,1)のGb画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

【0229】

同時に、偶数共有画素ラインRSの共有画素41の位置(2,1)と(4,1)のGb画素の画素信号

50

をFD加算した加算信号としての画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

【0230】

その後の第N+1画素ラインの期間の第2フェーズでは、奇数共有画素ラインRNの共有画素41の位置(2,2)と(4,2)のB画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

【0231】

同時に、偶数共有画素ラインRSの共有画素41の位置(2,2)と(4,2)のB画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

10

【0232】

以上のように、 $2 \times 4$ 画素を有する共有画素41について、同一の色成分どうしの画素の画素信号をFD加算して読み出すことにより、2ライン加算が行われ、 $2 \times 4$ 画素を有する共有画素41の並びで構成される1共有画素ラインである4画素ラインは、1/2に間引かれて、2画素ラインになる。

【0233】

ここで、図14において、"FD"の文字は、白抜きで示す2個の画素の画素信号が、FD加算されて読み出されることを表している。後述する図でも、同様である。

【0234】

奇数共有画素ラインRN、及び、偶数共有画素ラインRSの2共有画素ラインの共有画素41から、2ライン加算によって、画素信号が読み出された後、その後に続く奇数共有画素ラインRN+1、及び、偶数共有画素ラインRS+1の2共有画素ラインの共有画素41(の $2 \times 4$ 画素)については、画素信号が読み飛ばされる。

20

【0235】

以上のように、2共有画素ラインについて、画素信号を読み出した後、次の2共有画素ラインについては、画素信号を読み飛ばす1/2読み飛ばしを行うことで、2共有画素ラインと、次の2共有画素ラインとの合計で、4共有画素ラインである16画素ラインは、1/2に間引かれて、8画素ラインになる。

【0236】

そして、次の奇数共有画素ラインRN+2、及び、偶数共有画素ラインRS+2の2共有画素ラインについては、上述の場合と同様にして、2ライン加算が行われ、その後に続く奇数共有画素ラインRN+3、及び、偶数共有画素ラインRS+3の2共有画素ラインについては、画素信号を読み飛ばす1/2読み飛ばしが行われる。

30

【0237】

以下、同様にして、画素信号の2ライン加算と1/2読み飛ばしが行われることで、1/4間引きが行われる。

【0238】

1/4間引きでの画素信号の読み出しによれば、通常撮像時のフレームレートの4倍のフレームレートでの高速撮像を行うことができる。

【0239】

40

図15は、図14の同一アクセス制御による1/4間引きでの画素信号の読み出しで得られる画素値の画素重心を示す図である。

【0240】

図14の1/4間引きでの画素信号の読み出しでは、上述したように、2共有画素ラインについて、2ライン加算が行われ、その後に続く2共有画素ラインについて、画素信号の読み飛ばしが行われることが繰り返される。

【0241】

図14の2ライン加算では、その2ライン加算の結果の画素信号(加算信号)から得られる画素値の画素重心は、2ライン加算としてのFD加算の対象となった2個の画素の間の位置になり、信号処理部13(図2)では、例えば、2ライン加算の結果の画素信号から

50

得られる画素値の画素重心を、その2ライン加算としてのFD加算の対象となった2個の画素の間の位置に補正する画素重心の補正が行われる。

【0242】

したがって、図14の1/4間引きでの画素信号の読み出しで得られる1フレームの画像は、図15に示すように、1共有画素ラインである4画素ラインの2番目と3番目の画素ライン、及び、その次の1共有画素ラインである4画素ラインの2番目と3番目の画素ラインに画素値が存在し、その後の2共有画素ラインである8画素ラインには画素値が存在しない状態を繰り返す画像になる。

【0243】

その結果、図14の1/4間引きでの画素信号の読み出しで得られる画像では、画素値のサンプリング間隔（画素値を有する画素ラインの間隔）は、図15に示すように、等間隔ではなく、0画素ラインである場合、2画素ラインである場合、及び、9画素ラインである場合がある。

【0244】

画素値のサンプリング間隔が、0画素ライン、2画素ライン、及び、9画素ラインのように、大きく異なる場合には、上述したように、モアレや偽色が発生し、画質が低下することがある。

【0245】

以上のように、同一アクセス制御では、高速撮像のための間引きにおいて、モアレや偽色に起因する画質の低下が生じるが、個別アクセス制御によれば、そのような画質の低下を低減することができる。

【0246】

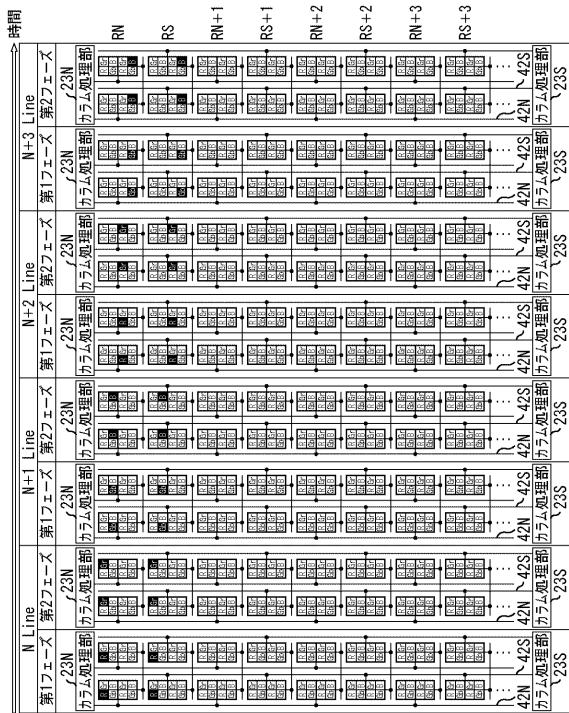

図16は、個別アクセス制御による、 $2 \times 4$ 画素の共有画素41からの、1/4間引きでの画素信号の読み出しの例を説明する図である。

【0247】

個別アクセス制御によれば、 $2 \times 4$ 画素の共有画素41について、1/4間引きでの画素信号の読み出しが、以下のような1/2読み飛ばしと2ライン加算とによって行うことができる。

【0248】

すなわち、図16において、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの共有画素41の位置(1,1)と(3,1)のR画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

【0249】

さらに、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNの次の偶数共有画素ラインRSの共有画素41の、位置(1,1)と(3,1)とは異なる位置(2,1)と(4,1)のGb画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

【0250】

以上のように、第N画素ラインの期間の第1フェーズでは、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインから、同時に、画素信号が読み出されるが、個別アクセス制御によれば、奇数共有画素ラインRNの共有画素41については、位置(1,1)と(3,1)のR画素の画素信号がFD加算されて読み出され、偶数共有画素ラインRSの共有画素41については、位置(1,1)と(3,1)とは異なる位置(2,1)と(4,1)のGb画素の画素信号がFD加算されて読み出される。

【0251】

その後、第N画素ラインの期間の第2フェーズにおいて、奇数共有画素ラインRNの共有画素41の位置(1,2)と(3,2)のGr画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Nを介して、カラム処理部23Nに供給されてAD変換される。

10

20

30

40

50

## 【0252】

さらに、第N画素ラインの期間の第2フェーズでは、偶数共有画素ラインRSの共有画素41の、位置(1,2)と(3,2)とは異なる位置(2,2)と(4,2)のB画素の画素信号をFD加算した加算信号としての画素信号が読み出され、列信号線42Sを介して、カラム処理部23Sに供給されてAD変換される。

## 【0253】

以上のように、第N画素ラインの期間の第2フェーズでは、奇数共有画素ラインRNと、その次の偶数共有画素ラインRSとの2つの共有画素ラインから、同時に、画素信号が読み出されるが、個別アクセス制御によれば、奇数共有画素ラインRNの共有画素41については、位置(1,2)と(3,2)のGr画素の画素信号がFD加算されて読み出され、偶数共有画素ラインRSの共有画素41については、位置(1,2)と(3,2)とは異なる位置(2,2)と(4,2)のB画素の画素信号がFD加算されて読み出される。

10

## 【0254】

ここで、 $2 \times 4$ 画素の共有画素41の並びの共有画素ラインは、4画素ラインであるから、画素信号が同時に読み出される奇数共有画素ラインRNと偶数共有画素ラインRSとの2つの共有画素ラインは、8画素ラインである。

## 【0255】

第N画素ラインの期間では、上述のようにして、2つの共有画素ラインである8画素ラインのうちの、(上から)1番目及び3番目の画素ライン(奇数共有画素ラインRNの1番目及び3番目の画素ライン)の画素であるR画素とGr画素を、読み出し対象画素として、その読み出し対象画素の画素信号がFD加算されて読み出される。

20

## 【0256】

さらに、第N画素ラインの期間では、2つの共有画素ラインである8画素ラインのうちの、6番目及び8番目の画素ライン(偶数共有画素ラインRSの2番目及び4番目の画素ライン)の画素であるGb画素とB画素を、読み出し対象画素として、その読み出し対象画素の画素信号がFD加算されて読み出される。

## 【0257】

以上のように、2つの共有画素ラインである8画素ラインのうちの、1番目及び3番目の画素ラインの2ライン加算と、6番目及び8番目の画素ラインの2ライン加算とが行われる。

30

## 【0258】

また、第N画素ラインの期間では、2つの共有画素ラインである8画素ラインのうちの、残りの画素ラインである2番目及び4番目、並びに、5番目及び7番目の画素ライン(奇数共有画素ラインRNの2番目及び4番目の画素ライン、並びに、偶数共有画素ラインRSの1番目及び3番目の画素ライン)の画素については、画素信号は読み出されずに、読み飛ばされる。

## 【0259】

すなわち、2つの共有画素ラインである8画素ラインのうちの、2ライン加算が行われない2番目及び4番目、並びに、5番目及び7番目の画素ラインについては、読み飛ばしが行われる。

40

## 【0260】

したがって、第N画素ラインの期間では、2つの共有画素ラインである8画素ラインのうちの半分(1/2)の4画素ラインを読み飛ばす1/2読み飛ばしと、残りの4画素ラインを対象とした2ライン加算とが行われ、元の8画素ラインが2画素ラインに間引かれる1/4間引きが行われる。

## 【0261】

その後の第N+1ラインの期間では、偶数共有画素ラインRSの次の2つの共有画素ラインである奇数共有画素ラインRN+1、及び、偶数共有画素ラインRS+1について、第Nラインの期間と同様の画素信号の読み出しが行われる。

## 【0262】

50

その結果、第N+1ラインの期間では、やはり、2つの共有画素ラインである8画素ラインのうちの、1番目及び3番目の画素ライン、並びに、6番目及び8番目の画素ライン（奇数共有画素ラインRN+1の1番目及び3番目の画素ライン、並びに、偶数共有画素ラインRS+1の2番目及び4番目の画素ライン）の画素については、画素信号がFD加算されて読み出される。そして、残りの2番目及び4番目、並びに、5番目及び7番目の画素ライン（奇数共有画素ラインRN+1の2番目及び4番目の画素ライン、並びに、偶数共有画素ラインRS+1の1番目及び3番目の画素ライン）の画素については、画素信号は読み出されずに、読み飛ばされる。

#### 【0263】

以下、同様に、以降の共有画素ラインについて、1/4間引きでの画素信号の読み出しを行うことで、通常撮像時のフレームレートの4倍のフレームレートでの高速撮像を行うことができる。

10

#### 【0264】

図17は、図16の1/4間引きでの画素信号の読み出しで得られる画素値の画素重心を示す図である。

#### 【0265】

図16の1/4間引きでの画素信号の読み出しでは、上述したように、2共有画素ラインの単位で、2ライン加算と1/2読み飛ばしが繰り返される。

#### 【0266】

図16の2ライン加算では、その2ライン加算の結果の画素信号（加算信号）から得られる画素値の画素重心は、2ライン加算としてのFD加算の対象となった2個の画素の間の位置になり、信号処理部13（図2）では、2ライン加算の結果の画素信号から得られる画素値の画素重心を、その2ライン加算としてのFD加算の対象となった2個の画素の間の位置に補正する画素重心の補正が行われる。

20

#### 【0267】

したがって、図16の1/4間引きでの画素信号の読み出しで得られる1フレームの画像は、図17に示すように、1共有画素ラインである4画素ラインの2番目の画素ラインに画素値が存在し、他の3画素ラインに画素値が存在しない状態と、その後の1共有画素ラインである4画素ラインの3番目の画素ラインに画素値が存在し、他の3画素ラインに画素値が存在しない状態とを繰り返す画像になる。

30

#### 【0268】

その結果、図16の1/4間引きでの画素信号の読み出しで得られる画像では、画素値のサンプリング間隔（画素値を有する画素ラインの間隔）は、図17に示すように、2画素ラインである場合と、4画素ラインである場合とがあり、図15の場合に比較して、等間隔に（近く）なる。

#### 【0269】

その結果、図15の場合に比較して、モアレや偽色の発生に起因する画質の低下を抑制することができる。

#### 【0270】

以上のように、共有画素41を採用するイメージセンサ2において、2つの共有画素ラインの共有画素41から、同時に、画素信号を読み出すにあたり、その2つの共有画素ラインについては、共有画素41の別個の位置の画素から、画素信号を読み出す個別アクセス制御を行うので、そのような個別アクセス制御を行わない場合、すなわち、例えば、2つの共有画素ラインの共有画素41の同一の位置の画素から、画素信号を読み出す同一アクセス制御を行う場合（図14及び図15）に比較して、画質の低下を抑制しつつ、高速撮像を行うことができる。

40

#### 【0271】

すなわち、個別アクセス制御によれば、画素値のサンプリング間隔（画素値を有する画素の垂直方向の間隔）を、なるべく等間隔にするFD加算が行われるように、共有画素41が有する画素から画素信号を読み出すアクセス制御を行うことができ、これにより、共有

50

画素 4 1 を採用するイメージセンサ 2 において、画質の低下を抑制しつつ、高速撮像を行うことができる。

【0272】

<個別アクセス制御>

【0273】

図 18 は、行制御部 2 2 による個別アクセス制御を説明するフローチャートである。

【0274】

行制御部 2 2 は、ステップ S 1 1 において、画素信号を同時に読み出すことができる（同時にアクセス可能な）2 共有画素ラインのうちの奇数共有画素ラインの共有画素 4 1 に対して、行信号線 4 3 A を介して制御信号を供給するとともに、偶数共有画素ラインの共有画素 4 1 に対して、行信号線 4 3 A とは別系統の行信号線 4 3 B を介して制御信号を供給することにより、異なるアクセス制御としての個別アクセス制御を行う。

【0275】

かかる個別アクセス制御によれば、画素信号が同時に読み出される奇数共有画素ラインと偶数共有画素ラインとで、共有画素 4 1 の異なる位置の画素から、画素信号を読み出すことができる。

【0276】

その結果、例えば、画素値のサンプリング間隔を、なるべく等間隔（略等間隔）にする FD 加算が行われるように、共有画素 4 1 が有する画素から画素信号を読み出すアクセス制御を行うことができ、これにより、共有画素 4 1 を採用するイメージセンサ 2 において、画質の低下を抑制しつつ、高速撮像を行うことができる。

【0277】

<SF加算>

【0278】

図 19 は、SF(Source Follower)加算を説明する図である。

【0279】

ここで、ライン加算を行う方法としては、FD加算の他、SF加算を利用する方法がある。

【0280】

図 5 で説明したように、共有画素 4 1 の選択 Tr 6 5 のソースに接続されている列信号線 4 2 N（及び 4 2 S）には、図示せぬ電流源が接続されており、この電流源と、増幅 Tr 6 4、及び、選択 Tr 6 5 とは、SF の回路を構成している。

【0281】

SF 加算は、SF の回路の電流源が接続されている列信号線 4 2 N（又は 4 2 S）上で行われる加算である。

【0282】

図 19 に示すように、例えば、各奇数共有画素ラインの、ある列 C に注目した場合、各奇数共有画素ラインの列 C の共有画素 4 1 は、同一の列信号線 4 2 N に接続されているが、行制御部 2 2（図 4）において、列 C の共有画素 4 1 のうちの、複数の異なる奇数共有画素ライン（行）の、同一の列信号線 4 2 N に接続されている複数の共有画素 4 1 としての、例えば、奇数共有画素ライン RN の共有画素 4 1 と、奇数共有画素ライン RN+1 の共有画素 4 1 との 2 個の共有画素 4 1 から、画素信号を同時に読み出すアクセス制御を行うことで、その 2 個の共有画素 4 1 から読み出された画素信号を、列信号線 4 2 N 上で加算する SF 加算を行い、その列信号線 4 2 N が接続されているカラム処理部 2 3 N に供給することができる。

【0283】

すなわち、例えば、行制御部 2 2 において、奇数共有画素ライン RN の共有画素 4 1 から、位置(1,1)と(3,1)の R 画素の画素信号を FD 加算した加算信号としての画素信号を読み出し、列信号線 4 2 N 上に出力するのと同時に、奇数共有画素ライン RN の次の奇数共有画素ライン RN+1 の共有画素 4 1 から、位置(1,1)と(3,1)の R 画素の画素信号を FD 加算した加算信号としての画素信号を読み出し、列信号線 4 2 N 上に出力するアクセス制御を行うこと

10

20

30

40

50

で、奇数共有画素ラインRNの共有画素4 1の位置(1,1)と(3,1)のR画素の画素信号をFD加算して得られる画素信号と、奇数共有画素ラインRN+1の共有画素4 1の位置(1,1)と(3,1)のR画素の画素信号をFD加算して得られる画素信号とは、列信号線4 2 N上でSF加算される。

【0284】

そして、列信号線4 2 N上のSF加算で得られる加算信号としての画素信号は、列信号線4 2 Nに接続されているカラム処理部2 3 Nに供給される。

【0285】

奇数共有画素ラインRN及びRN+1のR画素以外のGr画素、Gb画素、及び、B画素、奇数共有画素ラインRN及びRN+1以外の奇数ラインのペア、さらには、偶数共有画素ラインについても、同様のアクセス制御を行うことで、FD加算による2ライン加算と、SF加算による2ライン加算とが行われ、1/4間引きでの画素信号の読み出しを行うことができる。10

【0286】

また、図16及び図17で説明した、1/2読み飛ばし、及び、FD加算による2ライン加算に加え、上述のようなSF加算による2ライン加算を行うことで、1/8間引きでの画素信号の読み出しを行うことができ、この場合、画質の低下を抑制しつつ、通常撮像時のフレームレートの8倍のフレームレートでの高速撮像を行うことができる。

【0287】

なお、前述の特許文献1には、単位画素で構成され、AD変換を行うカラム処理部に並列に接続された複数のキャパシタと、その複数のキャパシタの中から、列信号線に接続するキャパシタを選択するスイッチとが設けられているイメージセンサが記載されている。20

【0288】

特許文献1に記載のイメージセンサでは、スイッチによって、列信号線に接続するキャパシタを切り替えることで、異なる2行の単位画素から同時に読み出された画素信号が、列信号線に接続されたキャパシタを介してカラム処理部に供給されるときに重み付け加算される容量加算が行われる。

【0289】

個別アクセス制御は、以上のような容量加算を行うイメージセンサにも適用することができ、したがって、図4の個別アクセス制御を行うイメージセンサの構成としては、容量加算を行う構成を採用することができる。30

【0290】

図4の個別アクセス制御を行うイメージセンサの構成として、容量加算を行う構成を採用した場合には、行制御部2 2は、異なる複数の共有画素ライン(行)の共有画素4 1から画素信号を同時に読み出すアクセス制御を行うことで、複数の共有画素ラインの共有画素4 1から同時に読み出された画素信号を列信号線に接続されたキャパシタを介して、カラム処理部に供給する。これにより、複数の共有画素ラインの共有画素4 1から同時に読み出された画素信号は、容量加算によって重み付け加算されて、カラム処理部に供給される。

【0291】

<画素アクセス部1 1の他の詳細構成例>

【0292】

図20は、図2の画素アクセス部1 1の他の詳細な構成例を示すブロック図である。

【0293】

なお、図中、図4の場合と対応する部分については、同一の符号を付してあり、以下では、その説明は、適宜省略する。

【0294】

図20の画素アクセス部1 1は、画素アレイ部2 1、カラム処理部2 3 N及び2 3 S、並びに、列制御部2 4 N及び2 4 Sを有する点で、図4の場合と共通する。

【0295】

さらに、図20の画素アクセス部1 1は、画素アレイ部2 1が、複数の共有画素4 1を50

有し、カラム処理部 23N が、DAC 51N、及び、共有画素 41 の列数 X と同一の X 個の ADC 52N を有するとともに、カラム処理部 23S が、DAC 51S、及び、X 個の ADC 52S を有する点で、図 4 の場合と共通する。

【0296】

また、図 20 の画素アクセス部 11 は、列信号線 42N 及び 42S が設けられている点で、図 4 の場合と共通する。

【0297】

但し、図 20 の画素アクセス部 11 は、行制御部 22 に代えて、行制御部 72 が設けられているとともに、行信号線 43A 及び 43B に代えて、行信号線 73A1 及び 73A2、並びに、73B1 及び 73B2 が設けられている点で、図 4 の場合と相違する。

10

【0298】

行信号線 73A1 及び 73A2 は、行信号線 43A と同様に、奇数行（奇数共有画素ライン）に配線されており、行制御部 72 は、行信号線 73A1 及び 73A2 に制御信号を供給する（流す）ことで、奇数行の共有画素 41 に対するアクセス制御を行う。

【0299】

行信号線 73B1 及び 73B2 は、行信号線 43B と同様に、偶数行（偶数共有画素ライン）に配線されており、行制御部 72 は、行信号線 73B1 及び 73B2 に制御信号を供給することで、偶数行の共有画素 41 に対するアクセス制御を行う。

【0300】

但し、行信号線 73A1 は、奇数行の共有画素 41 のうちの、奇数列の共有画素 41 にのみ接続され、行信号線 73A2 は、奇数行の共有画素 41 のうちの、偶数列の共有画素 41 にのみ接続されている。

20

【0301】

また、行信号線 73B1 は、偶数行の共有画素 41 のうちの、奇数列の共有画素 41 にのみ接続され、行信号線 73B2 は、偶数行の共有画素 41 のうちの、偶数列の共有画素 41 にのみ接続されている。

【0302】

行信号線 73A1 及び 73A2、並びに、73B1 及び 73B2 は、それぞれ、別系統の信号線であり、行制御部 72 は、別系統の信号線である行信号線 73A1 及び 73A2、並びに、73B1 及び 73B2 のそれぞれには、異なる制御信号を供給することができる。

30

【0303】

これにより、行制御部 72 は、画素信号（電気信号）が同時に読み出される奇数行及び偶数行の 2 行の共有画素 41 に対し、奇数行と偶数行とで、異なるアクセス制御を行うことができる他、さらに、1 行の 1 の列と他の列でも、すなわち、奇数列と偶数列とでも、異なるアクセス制御を行うことができる。

【0304】

この場合、同一の行の共有画素 41 について、奇数列と偶数列とで、異なる位置の画素から、画素信号を読み出すことができ、間引きの方法、すなわち、例えば、画素ラインを読み飛ばすパターンや、ライン加算を行う対象について、自由度を向上させることができる。

40

【0305】

この場合、画素信号を間引いて得られる画像の画素値のサンプリング間隔（画素値を有する画素ラインの間隔）を、より等間隔に近づけ、モアレの発生等に起因する画質の低下を、より抑制することができる。

【0306】

<イメージセンサ 2 の他の構成例 >

【0307】

図 21 は、図 1 のイメージセンサ 2 の他の構成例を示すブロック図である。

【0308】

50

なお、図中、図2の場合と対応する部分については、同一の符号を付してあり、以下では、その説明は、適宜省略する。

【0309】

図21のイメージセンサ2は、画素アクセス部11、カラムI/F部12、信号処理部13、及び、タイミング制御部14を有する点で、図2の場合と共通する。

【0310】

さらに、図21のイメージセンサ2は、画素アクセス部11が、画素アレイ部21、及び、行制御部22を有する点で、図2の場合と共通する。

【0311】

但し、図21のイメージセンサ2は、画素アクセス部11において、2つのカラム処理部23N及び23Sに代えて、1つのカラム処理部81が設けられているとともに、2つの列制御部24N及び24Sに代えて、1つの列制御部82が設けられている点で、図2の場合と相違する。

【0312】

すなわち、図2のイメージセンサ2では、列信号線42N及び42S(図4)の一端側としての上側に、カラム処理部23N及び列制御部24Nが設けられているとともに、他端側としての下側に、カラム処理部23S及び列制御部24Sが設けられているが、図21のイメージセンサ2では、列信号線42N及び42Sの一端側としての上側にだけ、カラム処理部81及び列制御部82が設けられている。

【0313】

カラム処理部81は、カラム処理部23N及び23Sと同様に、画素アレイ部21から供給される画素信号のAD変換等を行い、その結果得られるデジタル信号を、画素値として、カラムI/F部12に供給する。

【0314】

列制御部82は、列制御部24N及び24Sと同様に、カラム処理部81がAD変換等によって得た画素値を、カラムI/F部12に供給するための制御である列制御を行う。

【0315】

なお、カラム処理部81は、カラム処理部23N及び23S(図4)と同様に、図示せぬDACとADCとを有する。

【0316】

但し、カラム処理部23Nは(カラム処理部23Sも同様)、共有画素41の列数Xと同一のX個のADC52N(図4)を有するが、カラム処理部81は、複数行の各列の共有画素41から同時に読み出される画素信号をAD変換するADC(AD変換部)として、共有画素41の列数Xに、画素信号が同時に読み出される複数行を乗算した乗算値だけの数のADCを有する。

【0317】

すなわち、本実施の形態では、画素信号が同時に読み出される共有画素41の行数(共有画素ラインのライン数)は、2行であるため、カラム処理部81は、2X個のADCを有する。

【0318】

ここで、画素信号をAD変換するカラム処理部を1個だけ有する構成を、シングルカラム構成というとともに、カラム処理部を複数個に分けた構成を、マルチカラム構成といふこととすると、図2のイメージセンサ2は、マルチカラム構成のイメージセンサであり、図21のイメージセンサ2は、シングルカラム構成のイメージセンサである。

【0319】

上述のように、2個のカラム処理部23N及び23Sを有するマルチカラム構成の図2のイメージセンサ2では、カラム処理部23N(カラム処理部23Sも同様)は、X個のADC52Nを有するが、1個のカラム処理部81を有するシングルカラム構成の図21のイメージセンサ2では、カラム処理部81は、2X個のADCを有する。

【0320】

10

20

30

40

50

したがって、マルチカラム構成の図2のイメージセンサ2では、2個のカラム処理部23N及び23Sを有するので、1個のカラム処理部81を有するシングルカラム構成の図21のイメージセンサ2に比較して、回路面積が大になることがあるが、カラム処理部23N及び23Sが有するADC52N及び52Sの数が、それぞれX個であるため、2X個のADCを有するシングルカラム構成の図21のイメージセンサ2に比較して、ADC52Nどうしの間やADC52Sどうしの間に余裕があり、設計が容易である。

#### 【0321】

一方、シングルカラム構成の図21のイメージセンサ2では、カラム処理部81が2X個のADCを有するので、それぞれがX個のADC52N及び52Sを有するカラム処理部23N及び23Sで構成されるマルチカラム構成の図2のイメージセンサ2に比較して、カラム処理部81が有するADCどうしの間に余裕がなく、設計がシビアになるが、画素信号のAD変換を行うカラム処理部がカラム処理部81の1個だけなので、2個のカラム処理部23N及び23Sを有するマルチカラム構成の図2のイメージセンサ2に比較して、回路面積を小にすることができます。

#### 【0322】

なお、本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

#### 【0323】

例えば、本実施の形態では、共有画素41が、 $2 \times 2$ 画素や $2 \times 4$ 画素で構成される場合について説明したが、共有画素41の構成としては、 $2 \times 2$ 画素や $2 \times 4$ 画素の構成以外の構成を採用することができる。

#### 【0324】

また、本実施の形態では、カラーフィルタのパターンとして、ベイヤ配列を採用したが、カラーフィルタのパターンは、ベイヤ配列に限定されるものではない。

#### 【0325】

さらに、本実施の形態では、2行の共有画素ラインの共有画素41から、画素信号を同時に読み出すこととしたが、本技術は、3行以上のL行の共有画素ラインの共有画素41から、画素信号を同時に読み出す場合に適用することができる。

#### 【0326】

この場合、画素アクセス部11では、共有画素41の1列に対して、L本の列信号線が必要となる。さらに、画素信号を同時に読み出すL行の共有画素ラインの各行ごとに、異なるアクセス制御（個別アクセス制御）を行う場合には、R系統の別系統の行信号線が必要となる。

#### 【0327】

また、本技術は、デジタルカメラの他、PC(Personal Computer)や、携帯電話機、タブレット端末、スマートフォン、ウェアラブルカメラ、その他の画像を撮像する機能を搭載することができるあらゆる電子機器に適用することができる。

#### 【0328】

さらに、本明細書に記載された効果はあくまで例示であって限定されるものではなく、他の効果があつてもよい。

#### 【符号の説明】

#### 【0331】

1 光学系， 2 イメージセンサ， 3 メモリ， 4 信号処理部， 5 出力部，

6 制御部， 11 画素アクセス部， 12 カラムI/F部， 13 信号処理部，

14 タイミング制御部， 21 画素アレイ部， 22 行制御部， 23N, 23S

カラム処理部， 24N, 24S 列制御部， 31 上チップ， 32 下チップ，

41 共有画素， 42N, 42S 列信号線， 43A, 43B 行信号線， 51N, 51S

DAC, 52N, 52S ADC, 61 PD, 62 ないし 65 FET, 72 行制御部，

73A1, 73A2, 73B1, 73B2 行信号線， 81 カラム処理部， 82 列制御部

10

20

30

40

50

【 図 1 】

図1

【 図 2 】

図2

【図3】

図3

【 図 4 】

図4

【 図 5 】

図5 図6

図5 図6

【図7】

図7

【 8 】

図8

【 図 9 】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図15】

図15

【図14】

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

---

フロントページの続き

(72)発明者 樋爪 幸二

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 川又 大典

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 鈴木 明

(56)参考文献 特開2011-151800(JP, A)

特開2012-253624(JP, A)

特開2009-206883(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378