【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成26年4月10日(2014.4.10)

【公表番号】特表2013-520789(P2013-520789A)

【公表日】平成25年6月6日(2013.6.6)

【年通号数】公開・登録公報2013-028

【出願番号】特願2012-553345(P2012-553345)

【国際特許分類】

|        |         |           |

|--------|---------|-----------|

| H 01 L | 27/06   | (2006.01) |

| H 01 L | 21/822  | (2006.01) |

| H 01 L | 27/04   | (2006.01) |

| H 01 L | 29/74   | (2006.01) |

| H 01 L | 21/8222 | (2006.01) |

| H 01 L | 21/8248 | (2006.01) |

| H 01 L | 21/8249 | (2006.01) |

【F I】

|        |       |         |

|--------|-------|---------|

| H 01 L | 27/06 | 1 0 1 P |

| H 01 L | 27/04 | H       |

| H 01 L | 27/06 | 3 1 1 C |

| H 01 L | 29/74 | F       |

| H 01 L | 29/74 | G       |

| H 01 L | 27/06 | 1 0 1 U |

| H 01 L | 27/06 | 3 2 1 B |

【手続補正書】

【提出日】平成26年2月21日(2014.2.21)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

静電放電(E S D)保護回路であって、

第1の導電型の第1の低ドープウェルと、

第2の導電型の第2の低ドープウェルと、

前記第1の低ドープウェル内に形成された前記第1の導電型の第1の高ドープ領域と、

前記第1の低ドープウェル内に形成された前記第2の導電型の第2の高ドープ領域と、

前記第2の低ドープウェル内に形成された前記第1の導電型の第3の高ドープ領域であ

って、前記第2の高ドープ領域が前記E S D保護回路のカソード及びアノードの一方として機能し、前記第3の高ドープ領域が前記アノード及び前記カソードの他方として機能する、第3の高ドープ領域と、

前記第2の低ドープウェル内に形成された前記第2の導電型の第4の高ドープ領域と、

前記第2の高ドープ領域と前記第2の低ドープウェルとの間にある前記第1の低ドープウェル内に形成された前記第1の導電型の第5の高ドープ領域と、

前記第2の高ドープ領域と前記第2の低ドープウェルとの間にある前記第1の低ドープウェル内に形成された前記第2の導電型の第6の高ドープ領域と、

E S D事象中、前記E S D保護回路をオンにするトリガ回路とを備え、

前記トリガ回路が、前記第1の高ドープ領域、前記第2の高ドープ領域、前記第3の高

ドープ領域、前記第4の高ドープ領域、前記第5の高ドープ領域及び前記第6の高ドープ領域の任意の2つの間に電気的に結合され、

第1のトランジスタが、前記第3の高ドープ領域を含むエミッタ、前記第2の低ドープウェルを含むベース、及び前記第1の低ドープウェルを含むコレクタにより形成され、

第2のトランジスタが、前記第2の高ドープ領域を含むエミッタ、前記第1の低ドープウェルを含むベース、及び前記第2の低ドープウェルを含むコレクタにより形成され、

第3のトランジスタが、前記第2の高ドープ領域を含むエミッタ、前記第1の低ドープウェルを含むベース、及び前記第6の高ドープ領域を含むコレクタにより形成される、ESD保護回路。

#### 【請求項2】

前記第1の高ドープ領域と前記第2の高ドープ領域との間に電気的に結合された第1の外部レジスタと、

前記第3の高ドープ領域と前記第4の高ドープ領域との間に電気的に結合された第2の外部レジスタとをさらに備える、請求項1に記載のESD保護回路。

#### 【請求項3】

前記第5の高ドープ領域が、前記第6の高ドープ領域に電気的に直接接続され、前記第5の高ドープ領域及び前記第6の高ドープ領域に他の高ドープ領域は電気的に直接接続されない、請求項1に記載のESD保護回路。

#### 【請求項4】

前記トリガ回路が、

前記第4の高ドープ領域と前記第2の高ドープ領域との間に電気的に結合された第1のトリガ回路、

前記第3の高ドープ領域と前記第1の高ドープ領域との間に電気的に結合された第2のトリガ回路、

前記第5の高ドープ領域が前記第6の高ドープ領域に電気的に接続され、前記第3のトリガ回路が、第3の高ドープ領域と前記第5の高ドープ領域との間に電気的に結合される、第3のトリガ回路、

前記第4の高ドープ領域と前記第1の高ドープ領域との間に電気的に結合された第4のトリガ回路、および

前記第5の高ドープ領域が前記第6の高ドープ領域に電気的に接続され、第5のトリガ回路が、前記第4の高ドープ領域と前記第5の高ドープ領域との間に電気的に結合される、第5のトリガ回路のうちの少なくとも1つを備え、

前記第1、第2、第3、第4および第5のトリガ回路の任意のものが、ESD事象中に、前記ESD保護回路をオンにするように構成される、請求項1に記載のESD保護回路。

#### 【請求項5】

前記第6の高ドープ領域が、前記第2の高ドープ領域と前記第5の高ドープ領域との間に形成される、請求項1に記載のESD保護回路。

#### 【請求項6】

前記第5の高ドープ領域と前記第2の低ドープウェルとの間に高ドープ領域が形成されず、

前記第5の高ドープ領域と前記第6の高ドープ領域との間に高ドープ領域が形成されず、

前記第6の高ドープ領域と前記第2の高ドープ領域との間に高ドープ領域が形成されない、請求項1に記載のESD保護回路。

#### 【請求項7】

前記第5の高ドープ領域が、接続要素によって前記第6の高ドープ領域に電気的に結合され、

前記接続要素が、金属接続、金属コンタクト、バイア、金属線、レジスタ、キャパシタ、ダイオード、金属酸化膜半導体(MOS)デバイス、バイポーラトランジスタおよび制

御回路の少なくとも 1 つを含む、請求項 1 に記載の E S D 保護回路。

**【請求項 8】**

前記接続要素が、半導体デバイスの通常動作中に前記第 5 の高ドープ領域を前記第 6 の高ドープ領域から切り離すように構成され、前記接続要素が、E S D 事象の第 1 の期間中に前記第 5 の高ドープ領域と前記第 6 の高ドープ領域とを短絡するように構成される、請求項 7 に記載の E S D 保護回路。

**【請求項 9】**

前記接続要素が、前記 E S D 事象の前記第 1 の期間の後に前記第 5 の高ドープ領域を前記第 6 の高ドープ領域から切り離すように構成される、請求項 8 に記載の E S D 保護回路。

**【請求項 10】**

前記第 6 の高ドープ領域と前記第 2 の高ドープ領域との間に形成された前記第 1 の導電型の第 7 の高ドープ領域と、

前記第 2 の高ドープ領域と前記第 3 の高ドープ領域との間の前記第 1 の低ドープウェル内に形成された前記第 2 の導電型の第 8 の領域とをさらに備え、

前記第 8 の領域が、前記第 6 の高ドープ領域および前記第 7 の高ドープ領域を少なくとも部分的に取り囲む、請求項 1 に記載の E S D 保護回路。

**【請求項 11】**

前記第 6 の高ドープ領域を少なくとも部分的に取り囲む前記第 2 の導電型の第 7 の領域をさらに備える、請求項 1 に記載の E S D 保護回路。

**【請求項 12】**

前記第 7 の領域のドーパントレベルが、前記第 2 の低ドープウェルのドーパントレベルより高く、前記第 7 の領域のドーパントレベルが、前記第 6 の高ドープ領域のドーパントレベルより低い、請求項 1 に記載の E S D 保護回路。

**【請求項 13】**

前記第 5 の高ドープ領域を少なくとも部分的に取り囲む前記第 1 の導電型の第 7 の領域をさらに備える、請求項 1 に記載の E S D 保護回路。

**【請求項 14】**

前記第 7 の領域のドーパントレベルが、前記第 1 の低ドープウェルのドーパントレベルより高く、前記第 7 の領域のドーパントレベルが、前記第 5 の高ドープ領域のドーパントレベルより低い、請求項 1 に記載の E S D 保護回路。

**【請求項 15】**

前記第 1 の低ドープウェルおよび前記第 2 の低ドープウェルを取り囲む前記第 2 の導電型の第 3 の低ドープウェルをさらに備える、請求項 1 に記載の E S D 保護回路。

**【請求項 16】**

前記第 2 の導電型の第 3 の低ドープウェルと、

前記第 1 の低ドープウェルの下方に位置し、前記第 2 の低ドープウェルおよび前記第 3 の低ドープウェルの下方に少なくとも部分的に位置する前記第 2 の導電型の第 4 の低ドープウェルとをさらに備え、

前記第 2 の低ドープウェル、前記第 3 の低ドープウェルおよび前記第 4 の低ドープウェルの組み合わせが、前記第 1 の低ドープウェルを少なくとも部分的に取り囲む、請求項 1 に記載の E S D 保護回路。

**【請求項 17】**

前記第 2 の導電型の第 3 の低ドープウェルと、

前記第 1 の低ドープウェル、前記第 2 の低ドープウェルおよび前記第 3 の低ドープウェルの下方に位置する前記第 2 の導電型の第 4 の低ドープウェルと、

前記第 4 の低ドープウェルと前記第 2 の低ドープウェルとの間に位置付けられた前記第 1 の導電型の第 5 の低ドープウェルとをさらに備え、

前記第 3 の低ドープウェルおよび前記第 4 の低ドープウェルの組み合わせが、前記第 1 の低ドープウェル、前記第 2 の低ドープウェルおよび前記第 5 の低ドープウェルを少なく

とも部分的に取り囲む、請求項 1 に記載の ESD 保護回路。

**【請求項 18】**

前記第 1 の導電型が p 型であり、前記第 2 の導電型が n 型である、請求項 1 に記載の ESD 保護回路。

**【請求項 19】**

前記第 1 の導電型が n 型であり、前記第 2 の導電型が p 型である、請求項 1 に記載の ESD 保護回路。

**【請求項 20】**

前記第 1 の低ドープウェルと前記第 2 の低ドープウェルとの間の接合に形成された前記第 2 の導電型の第 7 の領域をさらに備え、前記第 7 の領域が、前記第 1 の低ドープウェルおよび前記第 2 の低ドープウェル内に少なくとも部分的に拡張し、前記トリガ回路が前記第 7 の領域を含む、請求項 1 に記載の ESD 保護回路。

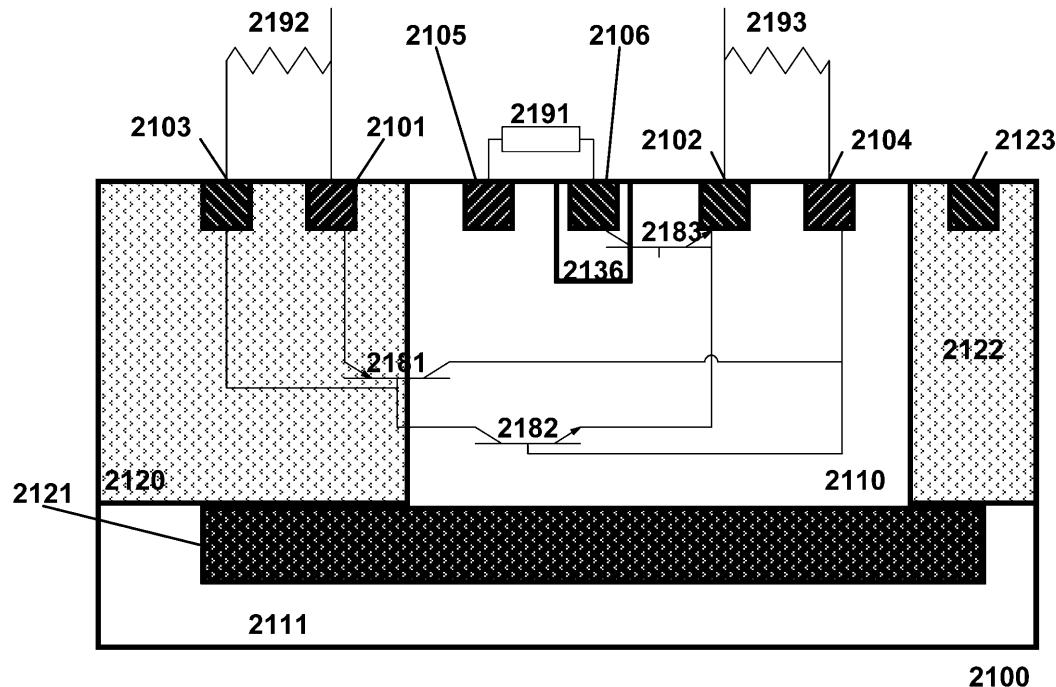

**【手続補正 2】**

**【補正対象書類名】** 図面

**【補正対象項目名】** 図 2 1

**【補正方法】** 変更

**【補正の内容】**

**【図 2 1】**