#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

18 April 2013 (18.04.2013)

(10) International Publication Number WO 2013/054933 A1

(51) International Patent Classification:

H01L 29/786 (2006.01)

H01L 27/108 (2006.01)

H01L 21/336 (2006.01)

H01L 27/11 (2006.01)

H01L 21/477 (2006.01)

H01L 29/788 (2006.01)

H01L 21/8242 (2006.01)

H01L 29/792 (2006.01)

H01L 21/8244 (2006.01)

(21) International Application Number:

PCT/JP2012/076563

(22) International Filing Date:

5 October 2012 (05.10.2012)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 2011-227022 14 October 2011 (14.10.2011) JP

- (71) Applicant (for all designated States except US): SEMI-CONDUCTOR ENERGY LABORATORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

- (72) Inventors; and

- (71) Applicants (for US only): HONDA, Tatsuya [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP). TSUBUKU, Masashi. NONAKA, Yusuke. SHIMAZU, Takashi. YAMAZAKI, Shunpei.

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: SEMICONDUCTOR DEVICE

# FIG. 1B

(57) Abstract: The concentration of impurity elements included in an oxide semiconductor film in the vicinity of a gate insulating film is reduced. Further, crystallinity of the oxide semiconductor film in the vicinity of the gate insulating film is improved. A semi-conductor device includes an oxide semiconductor film over a substrate, a source electrode and a drain electrode over the oxide semiconductor film, a gate insulating film which includes an oxide containing silicon and is formed over the oxide semiconductor film, and a gate electrode over the gate insulating film. The oxide semiconductor film includes a region in which the concentration of silicon is lower than or equal to 1.0 at.%, and at least the region includes a crystal portion.

#### DESCRIPTION

#### SEMICONDUCTOR DEVICE

## 5 TECHNICAL FIELD

[0001]

The present invention relates to a semiconductor device and a method for manufacturing the semiconductor device.

[0002]

In this specification, a semiconductor device generally means a device which can function by utilizing semiconductor characteristics, and an electrooptic device, a semiconductor circuit, and an electronic device are all semiconductor devices.

#### **BACKGROUND ART**

15 [0003]

20

25

30

A technique for forming transistors using a semiconductor thin film formed over a substrate having an insulating surface has attracted attention. The transistor is applied to a wide range of electronic devices such as an integrated circuit (IC) or an image display device (display device). As a semiconductor thin film applicable to the transistor, a silicon based semiconductor material is widely known for example; moreover, an oxide semiconductor has been attracting attention as another material. [0004]

For example, a transistor whose active layer includes an amorphous oxide including indium (In), gallium (Ga), and zinc (Zn) is disclosed (see Patent Document 1). [0005]

Transistors including oxide semiconductors have on-state characteristics (on-state current) superior to those of transistors including amorphous silicon. In order to apply the transistors including oxide semiconductors to high-performance devices, such transistors are required to have further improved characteristics, and thus techniques of crystallization of oxide semiconductors have been developed (see Patent Document 2). In Patent Document 2, a technique in which an oxide semiconductor is crystallized by heat treatment is disclosed.

WO 2013/054933 PCT/JP2012/076563

2

[Reference]

[Patent Document]

[0006]

[Patent Document 1] Japanese Published Patent Application No. 2006-165528

[Patent Document 2] Japanese Published Patent Application No. 2008-311342 5

## DISCLOSURE OF INVENTION

[0007]

10

15

20

25

30

In the case where a top-gate transistor including an oxide semiconductor film is formed, a gate insulating film is formed over the oxide semiconductor film. When the gate insulating film is formed, a constituent element of the gate insulating film may enter the oxide semiconductor film over which the gate insulating film is formed. [8000]

For example, in the case where a silicon oxide (SiO<sub>x</sub>, x = 2 or more) film is formed as a gate insulating film by a sputtering method after an oxide semiconductor film is formed, silicon that is a constituent element of the silicon oxide and a rare gas element such as argon used for sputtering are together implanted into the oxide semiconductor film. Such silicon breaks a bond between constituent elements of the oxide semiconductor film (an indium atom and an oxygen atom (In-O bond)) and is included as an impurity element in the oxide semiconductor film. The impurity element may be included at a high concentration particularly in the vicinity of the interface between the oxide semiconductor film and the gate insulating film. In the vicinity of the interface between the oxide semiconductor film and the gate insulating film, a channel formation region is formed; thus, when an impurity element such as silicon is included, the resistance of the oxide semiconductor film is increased. As a result, the on-state current which is one of electric characteristics of a transistor is decreased. As described above, the impurity element left in the oxide semiconductor film becomes a cause which affects electric characteristics of the transistor. [0009]

Further, in the case where the oxide semiconductor film includes a crystal portion, by entry of the constituent element of the gate insulating film into the oxide semiconductor film, a bond in the crystal portion of the oxide semiconductor film is broken, and accordingly, amorphous regions are more formed in the oxide semiconductor film in the vicinity of the gate insulating film.

[0010]

In view of the above problems, an object is to reduce the concentration of an impurity element included in an oxide semiconductor film in the vicinity of a gate insulating film. Another object is to improve crystallinity of the oxide semiconductor film in the vicinity of the gate insulating film. Further, another object is to provide a semiconductor device with stable electric characteristics by using the oxide semiconductor film.

10 [0011]

5

15

20

25

30

One embodiment of the present invention to be disclosed is a semiconductor device including a base insulating film, an oxide semiconductor film formed over the base insulating film, a source electrode and a drain electrode formed over the oxide semiconductor film, a gate insulating film which includes an oxide containing silicon and is formed over the oxide semiconductor film, the source electrode and the drain electrode, and a gate electrode provided to be in contact with the gate insulating film and overlap with at least the oxide semiconductor film. The oxide semiconductor film includes a region in which a concentration of silicon distributed from an interface with the gate insulating film toward an inside of the oxide semiconductor film is lower than or equal to 1.0 at.%, and at least the region includes a crystal portion.

[0012]

Another embodiment of the present invention to be disclosed is a semiconductor device including a base insulating film, an oxide semiconductor film formed over the base insulating film, a gate insulating film which includes an oxide containing silicon and is formed over the oxide semiconductor film, a gate electrode provided to be in contact with the gate insulating film and overlap with at least the oxide semiconductor film, an interlayer insulating film formed over the gate insulating film and the gate electrode, and a source electrode and a drain electrode provided over the interlayer insulating film to be electrically connected to at least the oxide semiconductor film. The oxide semiconductor film includes a region in which a concentration of silicon distributed from an interface with the gate insulating film

toward an inside of the oxide semiconductor film is lower than or equal to 1.0 at.%, and at least the region includes a crystal portion.

[0013]

In each of the above structures, the region is preferably formed to be in contact with the gate insulating film and have a thickness less than or equal to 5 nm. In addition, the oxide semiconductor film other than the region preferably includes a crystal portion. In the crystal portion, c-axes are preferably aligned in a direction perpendicular to the interface between the base insulating film and the oxide semiconductor film.

10 [0014]

5

Further, in each of the above structures, the region preferably has a silicon concentration lower than or equal to 0.1 at.%. In addition, the region preferably has a carbon concentration lower than or equal to  $1.0 \times 10^{20}$  atoms/cm<sup>3</sup>.

[0015]

When the oxide semiconductor film in the vicinity of the gate insulating film has the above silicon concentration or the above carbon concentration, an increase in resistance of the oxide semiconductor film can be suppressed and crystallinity of the oxide semiconductor film can be improved. As a result, a semiconductor device with stable electric characteristics can be provided.

20 [0016]

25

30

According to one embodiment of the present invention to be disclosed, the concentration of an impurity element included in the oxide semiconductor film in the vicinity of the gate insulating film can be decreased. In addition, crystallinity of the oxide semiconductor film in the vicinity of the gate insulating film can be improved. Further, a semiconductor device with stable electric characteristics can be provided.

**BRIEF DESCRIPTION OF DRAWINGS**

[0017]

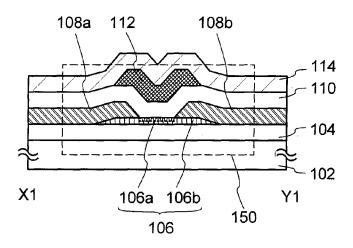

FIGS. 1A and 1B are a plan view and a cross-sectional view illustrating one embodiment of a semiconductor device.

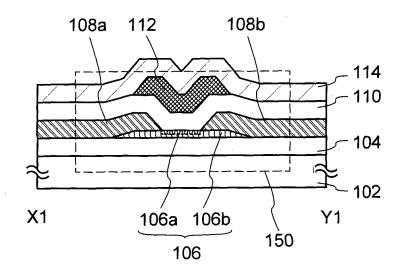

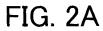

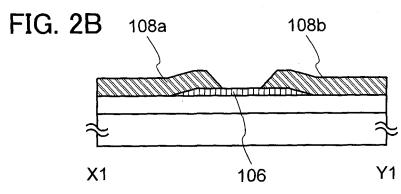

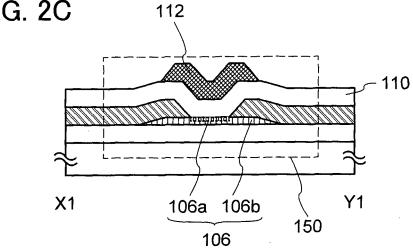

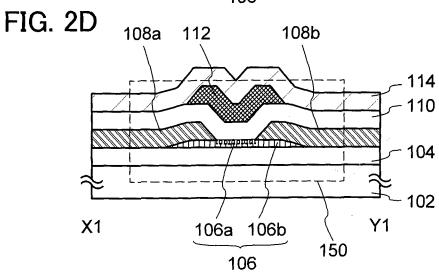

FIGS. 2A to 2D are cross-sectional views illustrating an example of a

5

15

manufacturing process of a semiconductor device.

FIGS. 3A and 3B are a plan view and a cross-sectional view illustrating one embodiment of a semiconductor device.

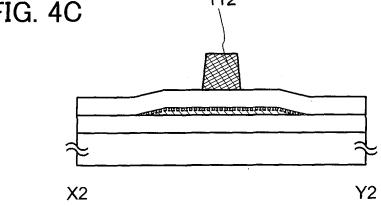

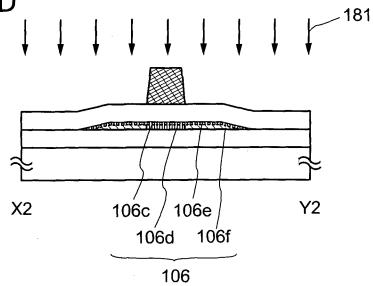

FIGS. 4A to 4D are cross-sectional views illustrating an example of a manufacturing process of a semiconductor device.

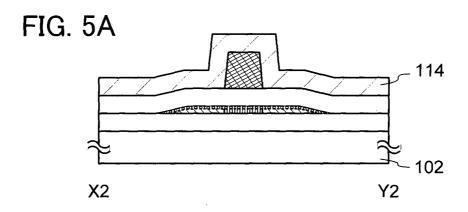

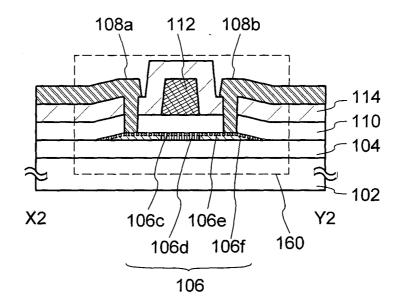

FIGS. 5A and 5B are cross-sectional views illustrating an example of a manufacturing process of a semiconductor device.

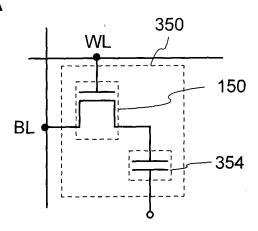

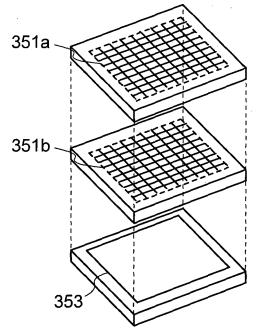

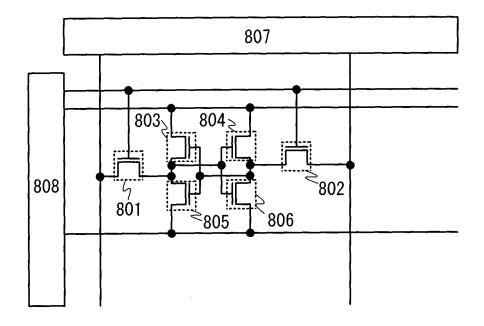

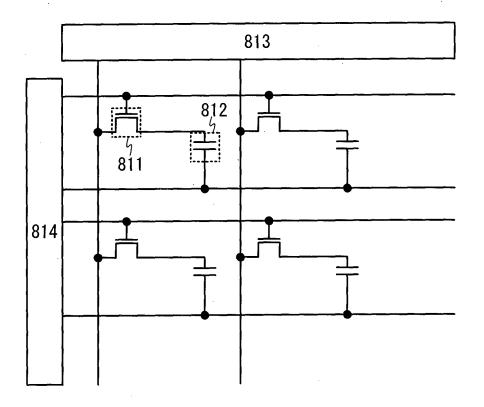

FIGS. 6A to 6C illustrate one embodiment of a semiconductor device.

FIGS. 7A and 7B illustrate one embodiment of a semiconductor device.

FIGS. 8A and 8B illustrate one embodiment of a semiconductor device.

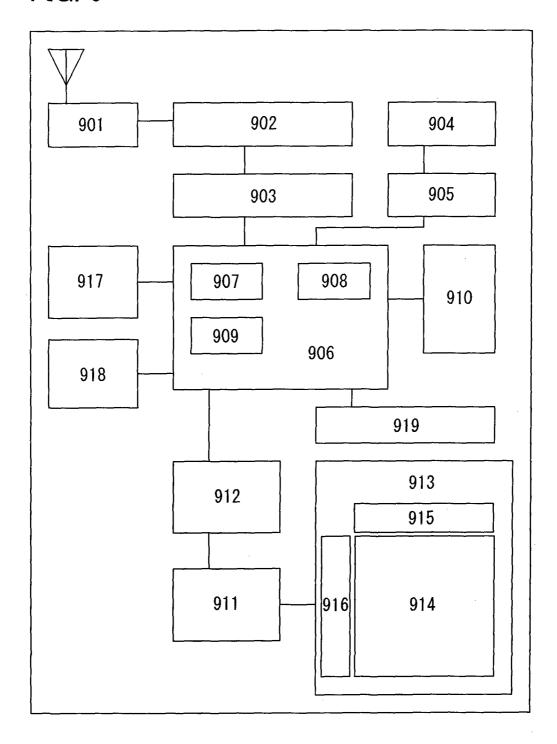

FIG. 9 illustrates one embodiment of a semiconductor device.

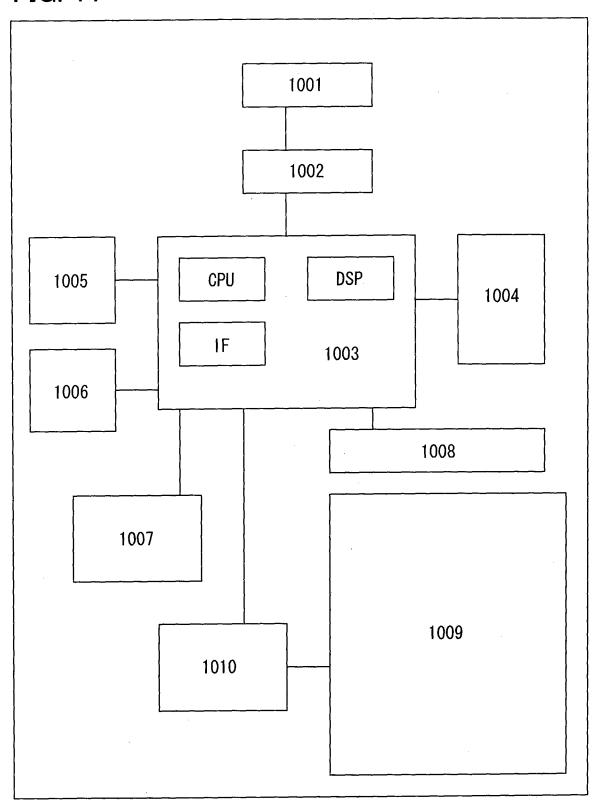

FIG. 10 illustrates one embodiment of a semiconductor device.

FIG. 11 illustrates one embodiment of a semiconductor device.

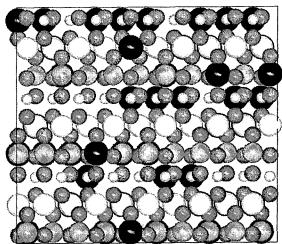

FIGS. 12A and 12B are model diagrams used for calculation.

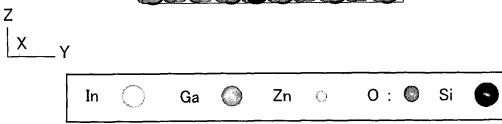

FIGS. 13A and 13B are model diagrams used for calculation.

FIG. 14 shows calculation results.

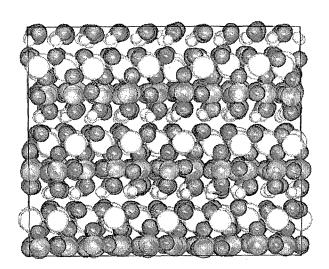

FIGS. 15A and 15B are model diagrams used for calculation.

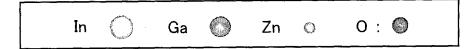

FIG. 16 shows calculation results.

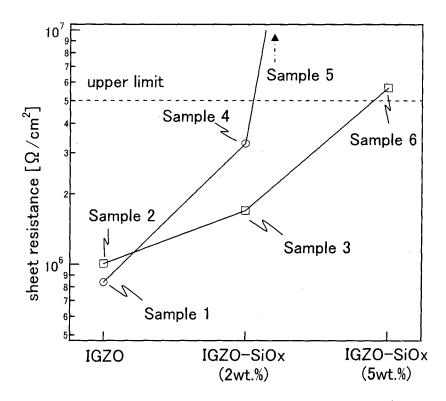

FIG. 17 shows measurement results according to Example of the present 20 invention.

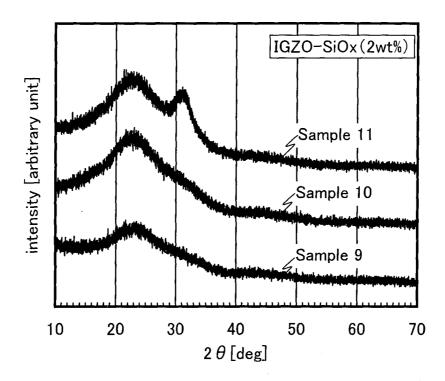

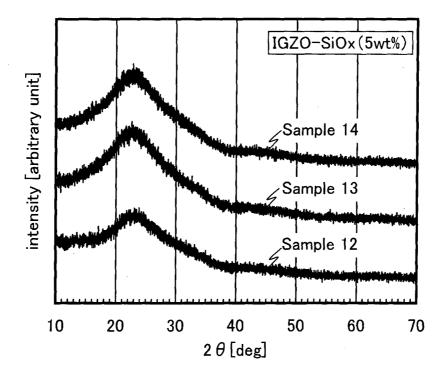

FIGS. 18A and 18B show measurement results according to Example of the present invention.

# BEST MODE FOR CARRYING OUT THE INVENTION

## 25 [0018]

30

Hereinafter, embodiments of the invention disclosed in this specification will be described with reference to the accompanying drawings. Note that the present invention is not limited to the following description and it will be readily appreciated by those skilled in the art that modes and details can be modified in various ways without departing from the spirit and the scope of the present invention. Therefore, the invention should not be construed as being limited to the description in the following embodiments.

[0019]

Note that the position, the size, the range, or the like of each structure illustrated in drawings and the like is not accurately represented in some cases for easy understanding. Therefore, the disclosed invention is not necessarily limited to the position, size, range, or the like as disclosed in the drawings and the like.

[0020]

In this specification and the like, ordinal numbers such as "first", "second", and "third" are used in order to avoid confusion among components, and the terms do not limit the components numerically.

10 [0021]

[0022]

15

20

25

30

5

Note that in this specification and the like, the term such as "over" or "below" does not necessarily mean that a component is placed "directly on" or "directly under" another component. For example, the expression "a gate electrode over a gate insulating layer" can mean the case where there is an additional component between the gate insulating layer and the gate electrode.

In addition, in this specification and the like, the term such as "electrode" or "wiring" does not limit a function of a component. For example, an "electrode" is sometimes used as part of a "wiring", and vice versa. Furthermore, the term "electrode" or "wiring" can include the case where a plurality of "electrodes" or "wirings" are formed in an integrated manner.

[0023]

Functions of a "source" and a "drain" are sometimes replaced with each other when a transistor of opposite polarity is used or when the direction of current flowing is changed in circuit operation, for example. Therefore, the terms "source" and "drain" can be replaced with each other in this specification and the like.

[0024]

Note that in this specification and the like, the term "electrically connected" includes the case where components are connected through an object having any electric function. There is no particular limitation on an object having any electric function as long as electric signals can be transmitted and received between components that are connected through the object. Examples of an "object having any electric function"

7

are a switching element such as a transistor, a resistor, an inductor, a capacitor, and an element with a variety of functions as well as an electrode and a wiring.

[0025]

5

15

20

25

30

(Embodiment 1)

In this embodiment, one embodiment of a semiconductor device and one embodiment of a method for manufacturing the semiconductor device will be described with reference to FIGS. 1A and 1B and FIGS. 2A to 2D.

[0026]

< Example of Structure of Semiconductor Device>

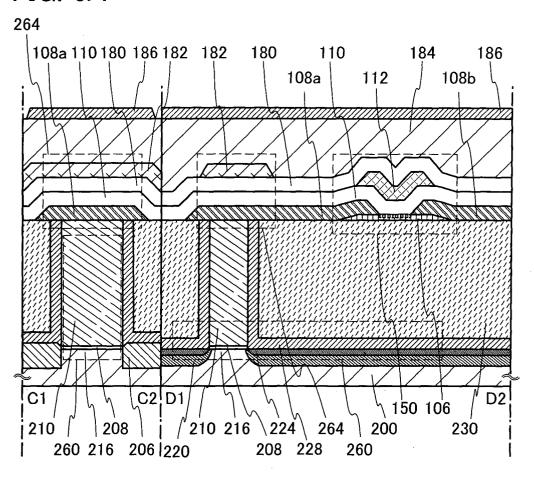

10 As an example of a semiconductor device, a top-gate transistor is illustrated in FIGS. 1A and 1B. FIG. 1A is a plan view and FIG. 1B is a cross-sectional view taken along dashed line X1-Y1 in FIG. 1A. Note that in FIG. 1A, some components of a transistor 150 (e.g., a gate insulating film 110) are omitted for simplicity. [0027]

The transistor 150 illustrated in FIGS. 1A and 1B includes, over a substrate 102, a base insulating film 104, an oxide semiconductor film 106 which is formed over the base insulating film 104 and includes a region 106a and a region 106b, a source electrode 108a and a drain electrode 108b formed over the base insulating film 104 and the oxide semiconductor film 106, the gate insulating film 110 formed over the oxide semiconductor film 106 and the source electrode 108a and the drain electrode 108b, and a gate electrode 112 provided to be in contact with the gate insulating film 110 and overlap with at least the oxide semiconductor film 106. In addition, an interlayer insulating film 114 is formed over the transistor 150.

[0028]

[0029]

The thickness of the oxide semiconductor film 106 is greater than 5 nm and less than or equal to 200 nm, preferably greater than or equal to 10 nm and less than or equal to 30 nm. Further, the oxide semiconductor film 106 preferably has a structure with crystallinity (e.g., a single crystal structure, a microcrystalline structure, or the like).

As illustrated in FIG. 1B, an end portion of the oxide semiconductor film 106 is preferably tapered at an angle of 20° to 50°. When the oxide semiconductor film 106

has a perpendicular end portion, oxygen is more likely to be released from the end portion of the oxide semiconductor film 106, and accordingly, oxygen vacancies are likely to be generated. When the oxide semiconductor film 106 has a tapered end portion, generation of oxygen vacancies is suppressed, and thus generation of leakage current of the transistor 150 can be reduced.

[0030]

5

In this embodiment, the oxide semiconductor film 106 is preferably a c-axis aligned crystalline oxide semiconductor (CAAC-OS) film. Note that the CAAC-OS film will be described in detail later in a manufacturing method of the transistor 150.

10 [0031]

For the gate insulating film 110, an oxide containing silicon, which has a sufficient withstand voltage and sufficient insulating properties, is preferably used. In the case where the gate insulating film 110 has a single-layer structure, an insulating film such as a silicon oxide film may be used, for example.

15 [0032]

20

25

30

Alternatively, the gate insulating film 110 may have a stacked structure. In the case where the gate insulating film 110 has a stacked structure, an oxide containing silicon may be stacked over a gallium oxide, an aluminum oxide, a silicon nitride, a silicon oxynitride, an aluminum oxynitride, a yttrium oxide, a lanthanum oxide, a silicon nitride oxide, or the like. Alternatively, an oxide containing silicon may be stacked over a high-k material such as hafnium oxide, hafnium silicate (HfSi<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)), hafnium silicate to which nitrogen is added (HfSiO<sub>x</sub>N<sub>y</sub> (x > 0, y > 0)), or hafnium aluminate (HfAl<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)).

[0033]

In the case of using an oxide containing silicon as the gate insulating film 110, part of contained oxygen can be released from the insulating film when the insulating film is heated; thus, oxygen can be supplied to the oxide semiconductor film 106, and oxygen vacancies in the oxide semiconductor film 106 can be filled. In particular, the gate insulating film 110 preferably contains a large amount of oxygen which exceeds at least the stoichiometry thereof. For example, a film of silicon oxide represented by the formula  $SiO_{2+\alpha}$  ( $\alpha > 0$ ) is preferably used as the gate insulating film 110. When such a

silicon oxide film is used as the gate insulating film 110, oxygen can be supplied to the oxide semiconductor film 106, so that the transistor 150 using the oxide semiconductor film 106 can have favorable transistor characteristics.

[0034]

L

5

10

15

20

25

30

However, in the case of using a silicon oxide film as the gate insulating film 110, silicon that is a constituent element of the gate insulating film 110 might be taken as an impurity into the oxide semiconductor film 106. Silicon or the like which is a constituent element of the gate insulating film 110 enters the oxide semiconductor film 106 and serves as an impurity, which affects characteristics of the transistor.

[0035]

Further, in the case where the oxide semiconductor film 106 is a CAAC-OS film, silicon or the like, which is a constituent element of the gate insulating film 110, enters the oxide semiconductor film 106, and a bond in the crystal portion in the oxide semiconductor film 106 is broken. Thus, amorphous regions are more formed in the oxide semiconductor film 106 in the vicinity of the gate insulating film 110. [0036]

In particular, impurities such as silicon are likely to enter the oxide semiconductor film 106 in the vicinity of the gate insulating film 110. A channel formation region of the transistor 150 is formed in the oxide semiconductor film 106 in the vicinity of the interface with the gate insulating film 110; thus, when impurities such as silicon enter the vicinity of the interface between the oxide semiconductor film 106 and the gate insulating film 110, characteristics of the transistor 150 might be changed. [0037]

Change in structure of the oxide semiconductor film 106 when SiO<sub>2</sub>, oxide containing silicon, is added as an impurity was examined by classical molecular dynamics calculation. The results thereof are described with reference to FIGS. 12A and 12B, FIGS. 13A and 13B, and FIG. 14. Note that simulation software "SCIGRESS ME" manufactured by Fujitsu Limited was used for classical molecular dynamics calculation. An empirical potential which characterizes the interaction between atoms is defined in the classical molecular dynamics method, so that force that acts on each atom is estimated. Newton's equation of motion is numerically solved, whereby motion (time-dependent change) of each atom can be deterministically tracked.

[0038]

5

10

15

20

25

30

Hereinafter, calculation models and calculation conditions are described.

Note that in this calculation, the Born-Mayer-Huggins potential was used.

[0039]

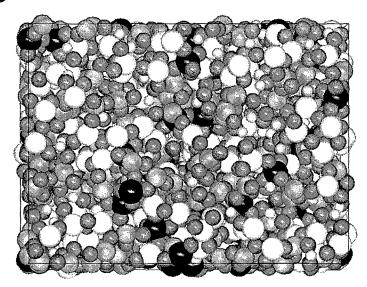

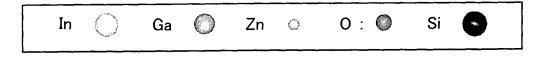

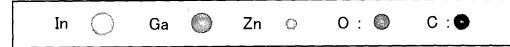

A single crystal structure of InGaZnO<sub>4</sub> including 1680 atoms (see FIG. 12A) and a structure of InGaZnO<sub>4</sub> including 1680 atoms in which 20 atoms of each of In, Ga, and Zn are substituted by silicon (Si) atoms (see FIG. 12B) were formed as calculation models. In the model of silicon (Si) substitution shown in FIG. 12B, silicon atoms are included at 3.57 at.% (2.34 wt.%). Further, the density of the model of the single crystal shown in FIG. 12A is 6.36 g/cm<sup>3</sup>, and the density of the model of Si substitution shown in FIG. 12B is 6.08 g/cm<sup>3</sup>.

[0040]

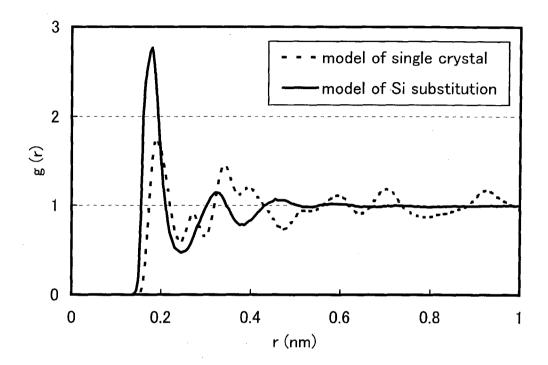

At 1727 °C which is lower than the melting point of the InGaZnO<sub>4</sub> single crystal (about 2000 °C according to estimation by the classical molecular dynamics calculation), structure relaxation was performed on the calculation models shown in FIGS. 12A and 12B by the classical molecular dynamics calculation at a fixed pressure (1 atom) for 150 psec (time step width 0.2 fsec  $\times$  750000 steps). The radial distribution functions g(r) of the two structures were calculated. Note that the radial distribution function g(r) is a function representing the probability density of atoms existing at a distance of r from one atom. As the correlation between atoms disappears, g(r) becomes closer to 1.

[0041]

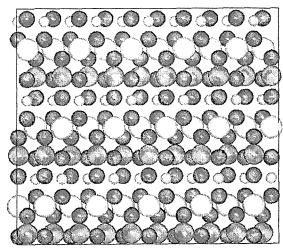

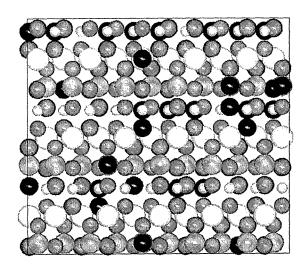

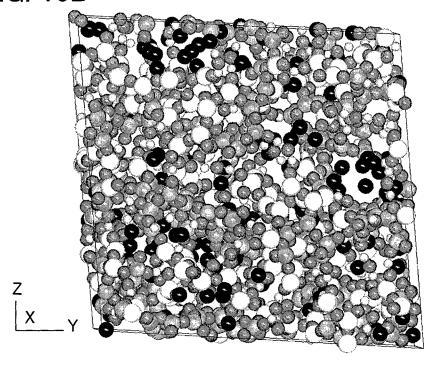

FIGS. 13A and 13B show final structures obtained by performing the classical molecular dynamics calculation for 150 psec on the above two calculation models. In addition, FIG. 14 shows the radial distribution function g (r) in each structure.

[0042]

The model of single crystal shown in FIG. 13A is stable and keeps the crystal structure even in the final structure, whereas the model of Si substitution shown in FIG. 13B is unstable, and it can be observed that the crystal structure is distorted with time and changes into an amorphous structure. When the radial distribution functions g(r) of the structural models are compared with each other in FIG. 14, it is found that the

single crystal model has peaks even at a long distance and has a long-range order. On the other hand, it is found that in the model of Si substitution, the peak disappears at a distance about 0.6 nm, and the model of Si substitution does not have the long-range order.

## 5 [0043]

The above calculation results indicate that when silicon (Si) is included in InGaZnO<sub>4</sub>, InGaZnO<sub>4</sub> is likely to become amorphous. Further, according to the above results, even when InGaZnO<sub>4</sub> including silicon (Si) is heated at high temperature, such InGaZnO<sub>4</sub> is not crystallized.

## 10 [0044]

Next, change in structure of the oxide semiconductor film 106 when carbon atoms (C) are added was examined by classical molecular dynamics calculation. The results thereof are described with reference to FIG. 12A, FIGS. 15A and 15B, and FIG. 16. Note that simulation software "SCIGRESS ME" manufactured by Fujitsu Limited was used for classical molecular dynamics calculation.

Calculation models and calculation conditions are as follows. Note that in this calculation, the Born-Mayer-Huggins potential was used. Further, for the interaction between carbon atoms (C), a Lennard-Jones potential was used.

## 20 [0046]

15

25

30

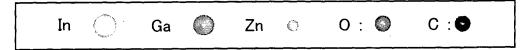

A single crystal structure of InGaZnO<sub>4</sub> including 1680 atoms (see FIG. 12A) and a structure of InGaZnO<sub>4</sub> including 1680 atoms in which 20 atoms of each of In, Ga, and Zn are substituted by carbon atoms (C) and 80 atoms of oxygen (O) are substituted by carbon atoms (C) (see FIG. 15A) were formed as calculation models. In the model of C substitution shown in FIG. 15A, carbon atoms (C) are included at 8.33 at.%. Further, the density of the model of the single crystal shown in FIG. 12A is 6.36 g/cm<sup>3</sup>, and the density of the model of C substitution shown in FIG. 15A is 5.89 g/cm<sup>3</sup>.

At 1727 °C which is lower than the melting point of the InGaZnO<sub>4</sub> single crystal (about 2000 °C according to estimation by the classical molecular dynamics calculation), structure relaxation was performed on the calculation models shown in FIG.

12A and FIG. 15A by the classical molecular dynamics calculation at a fixed pressure (1 atom) for 150 psec (time step width 0.2 fsec  $\times$  750000 steps). The radial distribution functions g(r) of the two structures were calculated. Note that the radial distribution function g(r) is a function representing the probability density of atoms existing at a distance of r from one atom. As the correlation between atoms disappears, g(r) becomes closer to 1.

[0048]

5

10

15

20

25

30

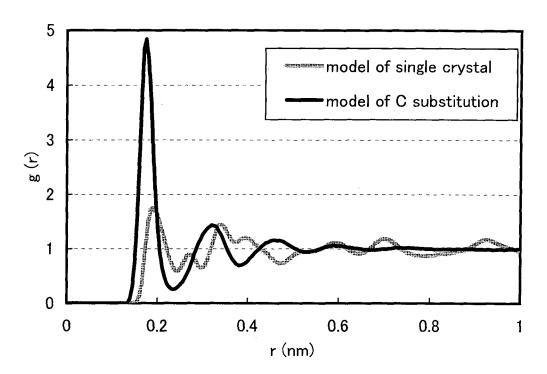

FIG. 13A and FIG. 15B show final structures obtained by performing the classical molecular dynamics calculation for 150 psec on the above two calculation models. The radial distribution function g(r) in each structure is shown in FIG. 16. [0049]

The model of single crystal shown in FIG. 13A is stable and keeps the crystal structure even in the final structure, whereas the model of C substitution shown in FIG. 15B is unstable, and it can be observed that the crystal structure is distorted with time and changes into an amorphous structure. As seen in FIG. 16, by comparing the radial distribution functions g(r) of the structural models with each other, it is found that the model of single crystal has peaks even at a long distance and the long-range order. On the other hand, it is found that in the model of C substitution, the peak disappears at a distance about 0.7 nm, and the model of C substitution does not have the long-range order.

[0050]

The above calculation results indicate that when carbon (C) is included in InGaZnO<sub>4</sub>, InGaZnO<sub>4</sub> is likely to become amorphous. In addition, according to the above results, even when InGaZnO<sub>4</sub> including carbon (C) is heated at high temperature, such InGaZnO<sub>4</sub> is not crystallized.

[0051]

Thus, in the semiconductor device described in this embodiment, entry of impurities such as silicon into the oxide semiconductor film 106 in the vicinity of the interface with the gate insulating film 110 is suppressed. As a result, in the oxide semiconductor film 106, a region in which the concentration of silicon distributed from an interface with the gate insulating film 110 toward an inside of the oxide

semiconductor film 106 is lower than or equal to 1.0 at.% is formed. Such a region is referred to as a region 106a as illustrated in FIG. 1B. The concentration of silicon included in the region 106a is further preferably lower than or equal to 0.1 at.%. Further, the region 106a is provided to be in contact with the gate insulating film 110 and have a thickness less than or equal to 5 nm.

[0052]

5

10

20

25

30

Note that as shown in FIG. 1B, a region in the oxide semiconductor film 106 other than the region 106a is referred to as a region 106b.

[0053]

Further, in the case where impurities such as carbon is included in the gate insulating film 110, such impurities might also enter the oxide semiconductor film 106 and serve as impurities, as in the case of silicon. In that case, the concentration of carbon included in the region 106a is lower than or equal to  $1.0 \times 10^{20}$  atoms/cm<sup>3</sup>, preferably lower than or equal to  $1.0 \times 10^{19}$  atoms/cm<sup>3</sup>.

15 [0054]

In order to prevent impurities such as silicon from entering the oxide semiconductor film 106, the gate insulating film may be formed in such a manner as not to damage the oxide semiconductor film 106. For example, in the case where a silicon oxide film is formed as the gate insulating film 110 by a sputtering method, the impact caused by silicon (that is a constituent element of the gate insulating film 110) colliding with the oxide semiconductor film 106 may be reduced. For achieving the above, specifically, a method in which the power for deposition of the gate insulating film 110 is low, a method in which the pressure for deposition of the gate insulating film 110 is high, a method in which a distance between a target and a substrate (T-S distance) is increased in deposition of the gate insulating film 110, or the like can be used. However, a formation method of the gate insulating film 110 is not limited to the above. For example, a silicon oxide film, a silicon oxynitride film, a silicon nitride oxide film, or the like, which is formed by a PE-CVD method, can be used. A PE-CVD method is preferred to a sputtering method because with use of the PE-CVD method, the oxide semiconductor film 106 serving as a base film is less damaged.

[0055]

As described above, the concentration of impurities such as silicon and carbon entering the region 106a in the oxide semiconductor film 106 is reduced, whereby change in characteristics of the transistor 150 can be suppressed. Further, in the case where the oxide semiconductor film 106 is a CAAC-OS film, a crystal portion can be formed even in the vicinity with the gate insulating film 110. When the transistor 150 is formed using such an oxide semiconductor film 106, a semiconductor device with stable electric characteristics can be provided.

[0056]

5

10

15

20

25

30

Note that the details of the other components of the transistor are described with reference to FIGS. 2A to 2D, in description of a method for manufacturing the transistor 150 below.

[0057]

<Manufacturing Method of Transistor 150>

Hereinafter, an example of a method for manufacturing the transistor 150 illustrated in FIGS. 1A and 1B of this embodiment is described with reference to FIGS. 2A to 2D.

[0058]

First, the substrate 102 is prepared. Although there is no particular limitation on a substrate that can be used as the substrate 102, it is necessary that the substrate have heat resistance to withstand at least a heat treatment performed later. For example, a glass substrate such as a barium borosilicate glass substrate or an aluminoborosilicate glass substrate, a ceramic substrate, a quartz substrate, a sapphire substrate, or the like can be used. Alternatively, a single crystal semiconductor substrate or a polycrystalline semiconductor substrate made of silicon or silicon carbide, a compound semiconductor substrate made of silicon germanium or the like, an SOI substrate, or the like can be used.

[0059]

A flexible substrate may be used as the substrate 102. In the case of using a flexible substrate, a transistor including the oxide semiconductor film 106 may be directly formed over the flexible substrate. Alternatively, a transistor including the oxide semiconductor film 106 may be formed over another substrate, and then, the transistor may be separated and transferred to a flexible substrate. For separation of

the transistor from the substrate and transfer to the flexible substrate, a separation layer may be provided between the substrate and the transistor including the oxide semiconductor film 106.

[0060]

5

Next, the base insulating film 104 is formed over the substrate 102 (see FIG. 2A). The base insulating film 104 has an effect to prevent diffusion of an impurity element such as hydrogen or moisture from the substrate 102, and can be formed with a single-layer structure or a stacked structure using one or more of a silicon nitride film, a silicon oxide film, a silicon nitride oxide film, and a silicon oxynitride film.

10 [0061]

15

20

25

30

Further, as another effect of the base insulating film 104, oxygen can be supplied to the oxide semiconductor film 106 formed later. For example, in the case where an insulating film including oxide is formed as the base insulating film 104, by heating the base insulating film 104, part of contained oxygen can be released. Thus, oxygen can be supplied to the oxide semiconductor film 106, and oxygen vacancies in the oxide semiconductor film 106 can be filled accordingly. In particular, the base insulating film 104 preferably contains a large amount of oxygen which exceeds at least the stoichiometry thereof. For example, a film of silicon oxide represented by the formula  $SiO_{2+\alpha}$  ( $\alpha > 0$ ) is preferably used as the base insulating film 104. When such a silicon oxide film is used as the base insulating film 104, oxygen can be supplied to the oxide semiconductor film 106, so that the transistor 150 using the oxide semiconductor film 106 can have favorable transistor characteristics.

[0062]

Before the base insulating film 104 is formed, plasma treatment or the like may be performed on the substrate 102. As plasma treatment, reverse sputtering in which an argon gas is introduced and plasma is generated can be performed. The reverse sputtering refers to a method in which an RF power source is used for application of a voltage to the substrate 102 side in an argon atmosphere so that plasma is generated in the vicinity of the substrate 102 to modify a surface of the substrate. Note that instead of an argon atmosphere, a nitrogen atmosphere, a helium atmosphere, an oxygen atmosphere, or the like may be used. The reverse sputtering can remove particle substances (also referred to as particles or dust) attached to the surface of the substrate

102.

[0063]

Next, the oxide semiconductor film 106 is formed over the base insulating film 104 (see FIG. 2A). The oxide semiconductor film 106 is preferably a CAAC-OS film. Note that the base insulating film 104 and the oxide semiconductor film 106 are preferably formed successively without being exposed to the air. [0064]

The CAAC-OS film that can be used for the oxide semiconductor film 106 is described in detail below.

10 [0065]

5

The CAAC-OS film is not completely single crystal or completely amorphous. The CAAC-OS film is an oxide semiconductor film with a crystal-amorphous mixed phase structure where crystal portions are included in an amorphous phase. Note that in most cases, the crystal portion fits inside a cube whose one side is less than 100 nm. From an observation image obtained with a transmission electron microscope (TEM), a boundary between an amorphous portion and a crystal portion in the CAAC-OS film is not clear. Further, with the TEM, a grain boundary in the CAAC-OS film is not found. Thus, in the CAAC-OS film, a reduction in electron mobility due to the grain boundary is suppressed.

20 [0066]

15

25

30

In each of the crystal portions included in the CAAC-OS film, a c-axis is aligned in a direction parallel to a normal vector of a surface where the CAAC-OS film is formed or a normal vector of a surface of the CAAC-OS film, triangular or hexagonal atomic arrangement which is seen from the direction perpendicular to the a-b plane is formed, and metal atoms are arranged in a layered manner or metal atoms and oxygen atoms are arranged in a layered manner when seen from the direction perpendicular to the c-axis. Note that, among crystal portions, the directions of an a-axis and a b-axis of one crystal portion may be different from those of another crystal portion. In this specification and the like, a simple term "perpendicular" includes a range from 85° to 95°. In addition, a simple term "parallel" includes a range from -5° to 5°.

In the CAAC-OS film, distribution of crystal portions is not necessarily uniform. For example, in the formation process of the CAAC-OS film, in the case where crystal growth occurs from a surface side of the oxide semiconductor film, the proportion of crystal portions in the vicinity of the surface of the oxide semiconductor film is higher than that in a vicinity of a surface where the oxide semiconductor film is formed in some cases.

[0068]

5

10

15

20

25

30

Since the c-axes of the crystal portions included in the CAAC-OS film are aligned in the direction parallel to a normal vector of a surface where the CAAC-OS film is formed or a normal vector of a surface of the CAAC-OS film, the directions of the c-axes may be different from each other depending on the shape of the CAAC-OS film (the cross-sectional shape of the surface where the CAAC-OS film is formed or the cross-sectional shape of the surface of the CAAC-OS film). Note that when the CAAC-OS film is formed, the direction of c-axis of the crystal portion is the direction parallel to a normal vector of the surface where the CAAC-OS film is formed or a normal vector of the surface of the CAAC-OS film. The crystal portion is formed by film formation or by performing treatment for crystallization such as heat treatment after film formation.

[0069]

With use of the CAAC-OS film in a transistor, change in electric characteristics of the transistor due to irradiation with visible light or ultraviolet light can be reduced. Change and variation in threshold voltages can be suppressed. Thus, the transistor has high reliability.

[0070]

In an oxide semiconductor having crystallinity (crystalline oxide semiconductor), defects in the bulk can be further reduced. Further, when planarity of the surface of the crystalline oxide semiconductor film is enhanced, a top-gate transistor including such an oxide semiconductor can obtain higher field-effect mobility than a transistor including an amorphous oxide semiconductor. In order to enhance the surface planarity of the oxide semiconductor film, the oxide semiconductor is preferably formed over a flat surface. Specifically, the oxide semiconductor is preferably formed over a surface with an average surface roughness  $(R_a)$  less than or equal to 0.15 nm,

preferably less than or equal to 0.1 nm. [0071]

Note that the average surface roughness  $(R_a)$  is obtained by expanding, into three dimensions, arithmetic mean surface roughness so as to be able to apply it to a curved surface.  $R_a$  can be expressed as an "average value of the absolute values of deviations from a reference surface to a specific surface" and is defined by the following formula.

[0072]

[FORMULA 1]

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

[0073]

10

15

20

25

30

Here, the specific surface is a surface that is a target of roughness measurement, and is a quadrilateral region specified by four points represented by the coordinates  $(x_1, y_1, f(x_1, y_1))$ ,  $(x_1, y_2, f(x_1, y_2))$ ,  $(x_2, y_1, f(x_2, y_1))$ , and  $(x_2, y_2, f(x_2, y_2))$ . Moreover,  $S_0$  represents the area of a rectangle which is obtained by projecting the specific surface on the xy plane, and  $Z_0$  represents the height of the reference surface (the average height of the specific surface).  $R_a$  can be measured using an atomic force microscope (AFM).

An oxide semiconductor used for the oxide semiconductor film 106 preferably contains at least indium (In) or zinc (Zn). In particular, In and Zn are preferably contained. As a stabilizer for reducing variation in electric characteristics of a transistor using the oxide semiconductor film, gallium (Ga) is preferably additionally contained. Tin (Sn) is preferably contained as a stabilizer. In addition, as a stabilizer, one or more selected from hafnium (Hf), zirconium (Zr), titanium (Ti), scandium (Sc), yttrium (Y), and an lanthanoid element (such as cerium (Ce), neodymium (Nd), or gadolinium (Gd), for example) is preferably contained.

As the oxide semiconductor, for example, any of the following can be used: indium oxide, tin oxide, zinc oxide, an In-Zn-based oxide, a Sn-Zn-based oxide, an Al-Zn-based oxide, a Zn-Mg-based oxide, a Sn-Mg-based oxide, an In-Mg-based oxide,

5

10

15

20

30

[0076]

an In-Ga-based oxide, an In-Ga-Zn-based oxide (also referred to as IGZO), an In-Al-Zn-based oxide, an In-Sn-Zn-based oxide, a Sn-Ga-Zn-based oxide, an Al-Ga-Zn-based oxide, an In-Hf-Zn-based oxide, an In-Zr-Zn-based oxide, an In-Ti-Zn-based oxide, an In-Sc-Zn-based oxide, an In-Y-Zn-based oxide, an In-La-Zn-based oxide, an In-Ce-Zn-based oxide, an In-Pr-Zn-based oxide, an In-Nd-Zn-based oxide, an In-Sm-Zn-based oxide, an In-Eu-Zn-based oxide, an In-Gd-Zn-based oxide, an In-Tb-Zn-based oxide, an In-Dy-Zn-based oxide, an In-Ho-Zn-based oxide, an In-Er-Zn-based oxide, an In-Tm-Zn-based oxide, an In-Hf-Ga-Zn-based oxide, an In-Lu-Zn-based oxide, an In-Sn-Ga-Zn-based oxide, an In-Hf-Ga-Zn-based oxide, an In-Hf-Al-Zn-based oxide, an In-Sn-Al-Zn-based oxide, an In-Sn-Hf-Zn-based oxide, or an In-Hf-Al-Zn-based oxide.

Here, an "In-Ga-Zn-based oxide" means an oxide containing In, Ga, and Zn as its main components and there is no particular limitation on the ratio of In: Ga: Zn. The In-Ga-Zn-based oxide may contain a metal element other than the In, Ga, and Zn. [0077]

Alternatively, a material represented by  $InMO_3(ZnO)_m$  (m > 0 is satisfied, and m is not an integer) may be used as an oxide semiconductor. Note that M represents one or more metal elements selected from Ga, Fe, Mn, and Co, or the above-described element as a stabilizer. Alternatively, as the oxide semiconductor, a material expressed by a chemical formula,  $In_2SnO_5(ZnO)_n$  (n > 0, n is a natural number) may be used. [0078]

For example, an In-Ga-Zn-based oxide with an atomic ratio where In: Ga: Zn = 1:1:1, In: Ga: Zn = 3:1:2, or In: Ga: Zn = 2:1:3, or any of oxides whose composition is in the neighborhood of the above compositions can be used.

[0079]

In a formation step of the oxide semiconductor film 106, it is preferable that hydrogen or water be contained in the oxide semiconductor film 106 as little as possible. For example, it is preferable that the substrate 102 on which the base insulating film 104 is already formed be preheated in a preheating chamber of a sputtering apparatus as

WO 2013/054933 PCT/JP2012/076563

20

pretreatment for formation of the oxide semiconductor film 106 so that impurities such as hydrogen and moisture adsorbed to the substrate 102 and the base insulating film 104 are removed and evacuated. Then, the oxide semiconductor film 106 is preferably formed in a deposition chamber from which remaining moisture is removed.

5 [0080]

In order to remove the moisture in the preheating chamber and the deposition chamber, an entrapment vacuum pump, for example, a cryopump, an ion pump, or a titanium sublimation pump is preferably used. Further, an evacuation unit may be a turbo pump provided with a cold trap. From the preheating chamber and the deposition chamber which is evacuated with a cryopump, a hydrogen atom, a compound containing a hydrogen atom such as water (H<sub>2</sub>O) (more preferably, also a compound containing a carbon atom), and the like are removed, whereby the concentration of impurities such as hydrogen or moisture in the oxide semiconductor film 106 that is to be formed can be reduced.

15 [0081]

10

Note that in this embodiment, an In-Ga-Zn-based oxide is deposited as the oxide semiconductor film 106 by a sputtering method. The oxide semiconductor film 106 can be formed by a sputtering method in a rare gas (typically argon) atmosphere, an oxygen atmosphere, or a mixed atmosphere of a rare gas and oxygen.

20 [0082]

25

30

As a target used for forming an In-Ga-Zn-based oxide film as the oxide semiconductor film 106 by a sputtering method, for example, a metal oxide target with an atomic ratio where In: Ga: Zn =1:1:1, a metal oxide target with an atomic ratio where In: Ga: Zn =3:1:2, or a metal oxide target with an atomic ratio where In: Ga: Zn =2:1:3 can be used. However, a material and composition of a target used for formation of the oxide semiconductor film 106 is not limited to the above.

Further, when the oxide semiconductor film 106 is formed using the above metal oxide target, the composition of the target is different from the composition of a film formed over the substrate in some cases. For example, when the metal oxide target having a molar ratio where  $In_2O_3$ :  $Ga_2O_3$ : ZnO = 1:1:1 is used, the composition

ratio of the thin oxide semiconductor film 106 becomes  $In_2O_3$ :  $Ga_2O_3$ : ZnO = 1:1:0.6 to 1:1:0.8 [molar ratio] in some cases, though it depends on the film formation conditions. This is because in formation of the oxide semiconductor film 106, ZnO is sublimed, or because a sputtering rate differs between the components of  $In_2O_3$ ,  $Ga_2O_3$ , and ZnO.

5 [0084]

10

15

Accordingly, when a thin film having a preferable composition ratio is formed, a composition ratio of the metal oxide target needs to be adjusted in advance. For example, in order to make the composition ratio of the thin oxide semiconductor film 106 be In<sub>2</sub>O<sub>3</sub>: Ga<sub>2</sub>O<sub>3</sub>: ZnO = 1:1:1 [molar ratio], the composition ratio of the metal oxide target is made to be In<sub>2</sub>O<sub>3</sub>: Ga<sub>2</sub>O<sub>3</sub>: ZnO = 1:1:1.5 [molar ratio]. In other words, the ZnO content of the metal oxide target is made higher in advance. The composition ratio of the target is not limited to the above value, and can be adjusted as appropriate depending on the film formation conditions or the composition of the thin film to be formed. Further, it is preferable to increase the ZnO content of the metal oxide target because in that case, the crystallinity of the obtained thin film is improved.

[0085]

The relative density of the metal oxide target is 90 % to 100 % inclusive, preferably, 95 % to 99.9 % inclusive. By using the metal oxide target with high relative density, a dense oxide semiconductor film 106 can be formed.

20 [0086]

As a sputtering gas used for forming the oxide semiconductor film 106, it is preferable to use a high-purity gas from which an impurity such as hydrogen, water, a hydroxyl group, or a hydride is removed.

[0087]

25

30

There are three methods for forming a CAAC-OS film when the CAAC-OS film is used as the oxide semiconductor film 106. One of the methods (first method) is to form an oxide semiconductor film at a temperature higher than or equal to 100 °C and lower than or equal to 450 °C to form, in the oxide semiconductor film, crystal portions in which the c-axes are aligned in the direction parallel to a normal vector of a surface where the oxide semiconductor film is formed or a normal vector of a surface of the oxide semiconductor film. Another method (second method) is to form an oxide

semiconductor film with a small thickness and then heat it at a temperature higher than or equal to 200 °C and lower than or equal to 700 °C, to form, in the oxide semiconductor film, crystal portions in which the c-axes are aligned in the direction parallel to a normal vector of a surface where the oxide semiconductor film is formed or a normal vector of a surface of the oxide semiconductor film. The other method (third method) is to form a first oxide semiconductor film with a small thickness, then heat it at a temperature higher than or equal to 200 °C and lower than or equal to 700 °C, and form a second oxide semiconductor film, to form, in the oxide semiconductor film, crystal portions in which the c-axes are aligned in the direction parallel to a normal vector of a surface where the oxide semiconductor film is formed or a normal vector of a surface of the oxide semiconductor film.

[8800]

5

10

15

20

25

30

For example, the CAAC-OS film is formed by a sputtering method with a polycrystalline oxide semiconductor sputtering target. When ions collide with the sputtering target, a crystal region included in the sputtering target may be separated from the target along an a-b plane; in other words, a sputtered particle having a plane parallel to an a-b plane (flat-plate-like sputtered particle or pellet-like sputtered particle) may flake off from the sputtering target. In that case, the flat-plate-like sputtered particle reaches a substrate while maintaining their crystal state, whereby the CAAC-OS film can be formed.

[0089]

For formation of the CAAC-OS film, the following conditions are preferably used.

[0090]

By reducing the amount of impurities entering the CAAC-OS film during the deposition, the crystal state can be prevented from being broken by the impurities. For example, the concentration of impurities (e.g., hydrogen, water, carbon dioxide, or nitrogen) which exist in the deposition chamber may be reduced. Furthermore, the concentration of impurities in a deposition gas may be reduced. Specifically, a deposition gas whose dew point is -80 °C or lower, preferably -100 °C or lower is used.

[0091]

By increasing the substrate heating temperature during the deposition, migration of a sputtered particle is likely to occur after the sputtered particle reaches a substrate surface. Specifically, the substrate heating temperature during the deposition is higher than or equal to 100 °C and lower than or equal to 740 °C, preferably higher than or equal to 150 °C and lower than or equal to 500 °C. By increasing the substrate heating temperature during the deposition, when the flat-plate-like sputtered particle reaches the substrate, migration occurs on the substrate surface, so that a flat plane of the flat-plate-like sputtered particle is attached to the substrate.

10 [0092]

5

Furthermore, it is preferable that the proportion of oxygen in the deposition gas be increased and the power be optimized in order to reduce plasma damage at the deposition. The proportion of oxygen in the deposition gas is 30 vol.% or higher, preferably 100 vol.%.

15 [0093]

20

25

30

Note that when a crystalline (single-crystal or microcrystalline) oxide semiconductor film other than a CAAC-OS film is formed as the oxide semiconductor film 106, there is no particular limitation on the deposition temperature. [0094]

Next, a conductive film used for a source electrode and a drain electrode (as well as a wiring formed in the same layer as the gate electrode) is formed over the base insulating film 104 and the oxide semiconductor film 106. As the conductive film used for the source electrode and the drain electrode, for example, a metal film containing an element selected from aluminum, chromium, copper, tantalum, titanium, molybdenum, or tungsten, or a metal nitride film containing any of the above elements as its component (e.g., a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) can be used. Alternatively, the conductive film may have a structure in which a film of a high-melting-point metal such as titanium, molybdenum, or tungsten, or a nitride film of any of these metals (a titanium nitride film, a molybdenum nitride film, or a tungsten nitride film) is stacked on either or both of the bottom surface and the top surface of a metal film of aluminum, copper, or the like. Further, the

conductive film used for the source electrode and the drain electrode may be formed using a conductive metal oxide. As the conductive metal oxide, indium oxide  $(In_2O_3)$ , tin oxide  $(SnO_2)$ , zinc oxide (ZnO), indium tin oxide  $(In_2O_3-SnO_2)$ , which is abbreviated to ITO in some cases), or indium zinc oxide  $(In_2O_3-ZnO)$  can be used. The conductive film used for the source electrode and the drain electrode can be formed using any of the above materials to have a single layer or a stacked structure. There is no particular limitation on the method for forming the conductive film, and a variety of film formation methods such as an evaporation method, a CVD method, a sputtering method, and a spin coating method can be employed.

10 [0095]

5

15

20

25

30

Next, a resist mask is formed over the conductive film through a photolithography step and selective etching is performed, so that the source electrode 108a and the drain electrode 108b are formed. Then, the resist mask is removed (see FIG. 2B). For the light exposure for forming the resist mask in this photolithography step, ultraviolet, KrF laser, or ArF laser can be used. [0096]

In this step, a channel length L of the transistor 150 that is to be completed in a later step is determined by a distance between a lower end of the source electrode 108a and a lower end of the drain electrode 108b that are adjacent to each other over the oxide semiconductor film 106. When light exposure is performed for a channel length L smaller than 25 nm, the light exposure for forming the resist mask in the photolithography step may be performed using extreme ultraviolet light having an extremely short wavelength of several nanometers to several tens of nanometers, for example. In the light exposure by extreme ultraviolet light, the resolution is high and the focus depth is large. Thus, the channel length L of the transistor 150 formed later can be reduced, whereby the operation speed of a circuit can be increased.

In order to reduce the number of photomasks used in a photolithography step and reduce the number of photolithography steps, an etching step may be performed with use of a multi-tone mask which is a light-exposure mask through which light is transmitted to have a plurality of intensities. A resist mask formed with use of a multi-tone mask has a plurality of thicknesses and further can be changed in shape by

etching; therefore, the resist mask can be used in a plurality of etching steps for processing into different patterns. Therefore, a resist mask corresponding to at least two kinds or more of different patterns can be formed by one multi-tone mask. Thus, the number of light-exposure masks can be reduced and the number of corresponding photolithography steps can be also reduced, whereby simplification of a process can be achieved.

[0098]

5

10

20

25

30

Note that it is preferable that etching conditions be optimized so as not to etch and divide the oxide semiconductor film 106 when the conductive film is etched. However, it is difficult to obtain etching conditions in which only the conductive film is etched and the oxide semiconductor film 106 is not etched at all. In some cases, only part of the oxide semiconductor film 106, e.g., 5 % to 50 % in thickness of the oxide semiconductor film 106, is etched, so that the oxide semiconductor film 106 has a groove portion (a recessed portion) when the conductive film is etched.

15 [0099]

Next, the gate insulating film 110 is formed to cover the oxide semiconductor film 106 and the source electrode 108a and the drain electrode 108b. The gate insulating film 110 can have a thickness greater than or equal to 1 nm and less than or equal to 500 nm. There is no particular limitation on the formation method of the gate insulating film 110; for example, a sputtering method, an MBE method, a CVD method, a pulsed laser deposition method, an ALD method, or the like can be used as appropriate for formation of the gate insulating film 110.

[0100]

For the gate insulating film 110, an oxide insulating film having a sufficient withstand voltage and sufficient insulating properties is preferably used. In the case where the gate insulating film 110 has a single-layer structure, an oxide containing silicon such as a silicon oxide film may be used.

[0101]

Further, when the gate insulating film 110 is formed, impurities such as silicon are taken to the oxide semiconductor film 106 in the vicinity of the interface with the gate insulating film 110. As a result, in the oxide semiconductor film 106, the region 106a is formed in the vicinity of the interface with the gate insulating film 110, and a

region in the oxide semiconductor film 106 other than the region 106a is the region 106b.

[0102]

5

10

15

20

25

30

Note that the concentration of silicon included in the region 106a is lower than or equal to 1.0 at.%, preferably lower than or equal to 0.1 at.%. The region 106a is provided to be in contact with the gate insulating film 110 to have a thickness less than or equal to 5 nm.

[0103]

Further, in the case where impurities such as carbon is included in the gate insulating film 110, such impurities also enter the region 106a in the oxide semiconductor film 106 and serve as impurities, as in the case of silicon. In that case, the concentration of carbon included in the region 106a is lower than or equal to  $1.0 \times 10^{20}$  atoms/cm<sup>3</sup>, preferably lower than or equal to  $1.0 \times 10^{19}$  atoms/cm<sup>3</sup>.

Alternatively, the gate insulating film 110 may have a stacked structure. In the case where the gate insulating film 110 has a stacked structure, for example, gallium oxide, aluminum oxide, silicon nitride, silicon oxynitride, aluminum oxynitride, yttrium oxide, lanthanum oxide, silicon nitride oxide, or the like may be stacked over oxide containing silicon. Alternatively, a high-k material such as hafnium oxide, hafnium silicate (HfSi<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)), hafnium silicate to which nitrogen is added (HfSiO<sub>x</sub>N<sub>y</sub> (x > 0, y > 0)), or hafnium aluminate (HfAl<sub>x</sub>O<sub>y</sub> (x > 0, y > 0)) may be stacked over an oxide containing silicon.

[0105]

When an oxide containing silicon is used as the gate insulating film 110, part of oxygen contained in the insulating film can be released by performing heat treatment described later; thus, oxygen can be supplied to the oxide semiconductor film 106, and oxygen vacancies in the oxide semiconductor film 106 can be filled. In particular, the gate insulating film 110 preferably contains a large amount of oxygen which exceeds at least the stoichiometry. For example, a film of silicon oxide represented by the formula  $SiO_{2+\alpha}$  ( $\alpha > 0$ ) is preferably used as the gate insulating film 110. When such a silicon oxide film is used as the gate insulating film 110, oxygen can be supplied to the

oxide semiconductor film 106, so that the transistor 150 using the oxide semiconductor film 106 can have favorable transistor characteristics.

[0106]

In order to prevent impurities such as silicon from entering the oxide semiconductor film 106, the gate insulating film 110 is formed in such a manner as not to damage the oxide semiconductor film 106. For example, in the case where a silicon oxide film is formed as the gate insulating film 110 by a sputtering method, the impact of silicon (that is a constituent element of the gate insulating film 110) colliding with the oxide semiconductor film 106 may be reduced. For achieving the above, specifically, a method in which the power for deposition of the gate insulating film 110 is low, a method in which a distance between a target and a substrate (T-S distance) is increased in deposition of the gate insulating film 110, or the like can be used. However, a formation method of the gate insulating film 110 is not limited to the above. For example, a silicon oxide film, a silicon oxynitride film, a silicon nitride oxide film, or the like, which is formed by a PE-CVD method, can be used. A PE-CVD method is preferred to a sputtering method because with use of the PE-CVD method, the oxide semiconductor film 106 serving as a base film is less damaged.

[0107]

5

10

15

20

25

30

Next, a conductive film used for formation of a gate electrode (as well as a wiring formed in the same layer as the gate electrode) is formed over the gate insulating film 110. The conductive film used for the gate electrode can be formed using, for example, a metal material such as molybdenum, titanium, tantalum, tungsten, aluminum, copper, neodymium, or scandium, or an alloy material including any of these materials as a main component. Alternatively, the conductive film used for the gate electrode may be formed using a conductive metal oxide. As the conductive metal oxide, indium oxide (In<sub>2</sub>O<sub>3</sub>), tin oxide (SnO<sub>2</sub>), zinc oxide (ZnO), indium tin oxide (In<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>, which is abbreviated to ITO in some cases), indium zinc oxide (In<sub>2</sub>O<sub>3</sub>-ZnO), or any of these metal oxide materials in which silicon or silicon oxide is included can be used. The gate electrode can be formed to have a single layer or a stacked structure using any of the above materials. There is no particular limitation on the method for forming the conductive film, and a variety of film formation methods such as an evaporation method,

a CVD method, a sputtering method, and a spin coating method can be employed. [0108]

Next, a resist mask is formed over the conductive film through a photolithography step and selective etching is performed, so that the gate electrode 112 is formed. Then, the resist mask is removed (see FIG. 2C). The resist mask used for forming the gate electrode 112 may be formed by an inkjet method. Formation of the resist mask by an inkjet method needs no photomask; thus, manufacturing cost can be reduced. For etching the gate electrode 112, wet etching, dry etching, or both of them may be employed. Note that when the gate electrode 112 is formed, the transistor 150 is formed.

[0109]

5

10

15

20

25

30

Next, the interlayer insulating film 114 is formed over the gate insulating film 110 and the gate electrode 112 (see FIG. 2D).

[0110]

The interlayer insulating film 114 is preferably formed using an inorganic insulating film to have a single layer or a stacked layer of any of oxide insulating films such as a silicon oxide film, a silicon oxynitride film, an aluminum oxide film, an aluminum oxynitride film, a gallium oxide film, and a hafnium oxide film. Further, over the above oxide insulating film, a single layer or a stacked layer of any of nitride insulating films such as a silicon nitride film, a silicon nitride oxide film, an aluminum nitride film, and an aluminum nitride oxide film may be formed. For example, as a stacked layer, a silicon oxide film and an aluminum oxide film are deposited in this order over the gate electrode 112.

[0111]

After the formation of the interlayer insulating film 114, heat treatment is preferably performed on the oxide semiconductor film 106. The temperature of the heat treatment is higher than or equal to 300 °C and lower than or equal to 700 °C, or lower than the strain point of a substrate.

[0112]

The heat treatment may be performed in an atmosphere of nitrogen, oxygen, ultra-dry air (air in which the moisture content is less than or equal to 20 ppm, preferably less than or equal to 1 ppm, further preferably less than or equal to 10 ppb),

or a rare gas (such as argon or helium). Note that it is preferable that water, hydrogen, and the like be not contained in the atmosphere of nitrogen, oxygen, ultra-dry air, a rare gas, or the like. It is also preferable that the purity of nitrogen, oxygen, or the rare gas which is introduced into a heat treatment apparatus be set to higher than or equal to 6N (99.9999 %), preferably higher than or equal to 7N (99.99999 %) (that is, the impurity concentration is lower than or equal to 1 ppm, preferably lower than or equal to 0.1 ppm).

[0113]

5

10

15

20

30

In the case of performing heat treatment after formation of the oxide semiconductor film, oxygen that is one of main component materials included in the oxide semiconductor might be reduced. However, during the heat treatment in this step, oxygen can be supplied to the oxide semiconductor film 106 from the base insulating film 104 or the gate insulating film 110 which is formed using an oxide containing silicon; thus, oxygen vacancies in the oxide semiconductor film 106 can be filled.

[0114]

By performing the heat treatment as described above, the oxide semiconductor film 106 can be highly purified so as not to contain impurities other than main components as little as possible. The highly purified oxide semiconductor film 106 contains extremely few (close to zero) carriers derived from a donor, and the carrier concentration thereof is lower than  $1 \times 10^{14}$  /cm<sup>3</sup>, preferably lower than  $1 \times 10^{12}$  /cm<sup>3</sup>, further preferably lower than  $1 \times 10^{11}$  /cm<sup>3</sup>. In such a manner, the oxide semiconductor film 106 that becomes an i-type (intrinsic) oxide semiconductor can be formed.

25 [0115]

Through the above steps, the transistor 150 is formed. In the transistor 150, the concentration of impurities such as silicon taken into the region 106a of the oxide semiconductor film 106 is small. Further, in the case where the oxide semiconductor film is a CAAC-OS film, a crystal portion can be formed even in the vicinity of the interface between the oxide semiconductor film and the gate insulating film 110. Thus, the transistor 150 can have stable electric characteristics.

[0116]

5

10

15

25

30

Over the interlayer insulating film 114, a planarization insulating film may be further provided. The planarization insulating film can be formed using an organic material having heat resistance, such as, an acrylic resin, a polyimide resin, a benzocyclobutene-based resin, a polyamide resin, or an epoxy resin can be used. Other than such organic materials, a low-dielectric constant material (a low-k material) or a siloxane-based resin can be used. Note that the planarization insulating film may be formed by stacking a plurality of insulating films formed of any of these materials.

The methods and structures described in this embodiment can be combined as appropriate with any of the methods and structures described in the other embodiments.

[0118]

(Embodiment 2)

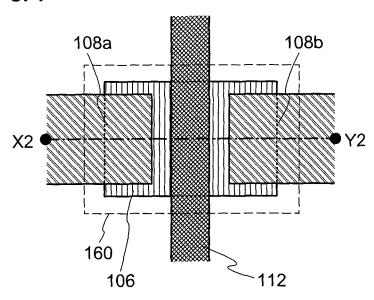

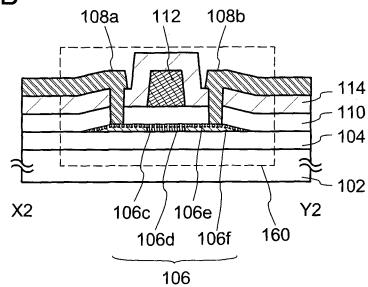

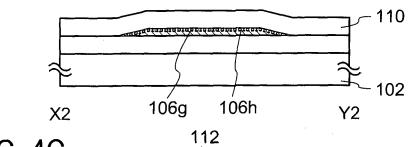

In this embodiment, modification examples of the semiconductor device and the method for manufacturing the semiconductor device of Embodiment 1, which are illustrated in FIGS. 1A and 1B and FIGS. 2A to 2D, will be described with reference to FIGS. 3A and 3B, FIGS. 4A to 4D, FIGS. 5A and 5B. Note that portions similar to those in FIGS. 1A and 1B and FIGS. 2A to 2D are denoted by the same reference numerals, and description thereof is skipped.

20 [0119]

<Example of Structure of Semiconductor Device (Modification Example)>

In FIGS. 3A and 3B, a top-gate transistor is illustrated as an example of a semiconductor device. FIG. 3A is a plan view, and FIG. 3B is a cross-sectional view taken along dashed line X2-Y2 in FIG. 3A. Note that in FIG. 3A, some components of a transistor 160 (e.g., a gate insulating film 110) are omitted for simplicity.

[0120]

The transistor 160 illustrated in FIGS. 3A and 3B includes, over a substrate 102, a base insulating film 104, an oxide semiconductor film 106 which is formed over the base insulating film 104 and includes a region 106c, a region 106d, a region 106e, and a region 106f, the gate insulating film 110 formed over the oxide semiconductor film 106, a gate electrode 112 provided to be in contact with the gate insulating film 110 and overlap with at least the oxide semiconductor film 106, an interlayer insulating film 114

formed over the gate insulating film 110 and the gate electrode 112, and a source electrode 108a and a drain electrode 108b which are provided over the interlayer insulating film 114 and electrically connected to the oxide semiconductor film 106. [0121]

The oxide semiconductor film 106 includes the region 106c and the region 106d, which function as a channel formation region, and the region 106e and the region 106f which function as a pair of low resistance regions provided so that the channel formation region is sandwiched therebetween.

[0122]

[0123]

[0124]

5

10

15

20

25

30

Further, as illustrated in FIG. 3B, an end portion of the oxide semiconductor film 106 is preferably tapered at an angle of 20° to 50°. When the oxide semiconductor film 106 has a perpendicular end portion, oxygen is more likely to be released from the end portion of the oxide semiconductor film 106, and accordingly, oxygen vacancies are likely to be generated. When the oxide semiconductor film 106 has a tapered end portion, generation of oxygen vacancies is suppressed, and thus generation of leakage current of the transistor 160 can be reduced.

For the gate insulating film 110, an oxide insulating film having a sufficient withstand voltage and sufficient insulating properties is preferably used. In the case where the gate insulating film 110 has a single-layer structure, an oxide containing silicon, such as a silicon oxide film, may be used, for example.

When an oxide containing silicon is used as the gate insulating film 110, part of oxygen contained in the insulating film can be released by performing heat treatment; thus, oxygen can be supplied to the oxide semiconductor film 106, and oxygen vacancies in the oxide semiconductor film 106 can be filled. In particular, the gate insulating film 110 preferably contains a large amount of oxygen which exceeds at least the stoichiometry. For example, a film of silicon oxide represented by the formula  $SiO_{2+\alpha}$  ( $\alpha > 0$ ) is preferably used as the gate insulating film 110. When such a silicon oxide film is used as the gate insulating film 110, oxygen can be supplied to the oxide semiconductor film 106, so that the transistor 160 using the oxide semiconductor film

106 can have favorable transistor characteristics.

[0125]

However, in the case of using a silicon oxide film as the gate insulating film 110, silicon that is a constituent element of the gate insulating film 110 might be taken as an impurity into the oxide semiconductor film 106. Silicon which is a constituent element of the gate insulating film 110 or the like enters the oxide semiconductor film 106 and serves as an impurity, which affects characteristics of the transistor. Further, in the case where the oxide semiconductor film 106 is a CAAC-OS film, a constituent element of the gate insulating film 110 enters the oxide semiconductor film 106, and a bond in the crystal portion in the oxide semiconductor film 106 is broken. Thus, amorphous regions are more formed in the oxide semiconductor film 106 in the vicinity of the gate insulating film 110.

[0126]

5

10

15

25

30

In particular, impurities such as silicon are likely to enter the oxide semiconductor film 106 in the vicinity of the gate insulating film 110. A channel formation region of the transistor 160 is formed in the oxide semiconductor film 106 in the vicinity of the interface with the gate insulating film 110; thus, when impurities such as silicon enter the vicinity of the interface between the oxide semiconductor film 106 and the gate insulating film 110, characteristics of the transistor 150 might be changed.

20 [0127]

Thus, in the semiconductor device described in this embodiment, entry of impurities such as silicon into the oxide semiconductor film 106 in the vicinity of the interface with the gate insulating film 110 is suppressed. As a result, in the oxide semiconductor film 106, a region in which the concentration of silicon distributed from an interface with the gate insulating film 110 toward an inside of the oxide semiconductor film 106 is lower than or equal to 1.0 at.% is formed. Such a region is referred to as the region 106c and the region 106e in FIG. 3B. The concentrations of silicon included in the region 106c and the region 106e are further preferably lower than or equal to 0.1 at.%. Further, the region 106c and the region 106e are provided to be in contact with the gate insulating film 110 and have a thickness less than or equal to 5 nm. [0128]

Note that in FIG. 3B, in the oxide semiconductor film 106, regions on the base insulating film 104 side are the region 106d and the region 106f, and regions on the gate insulating film 110 side are the region 106c and the region 106e.

[0129]

Further, in the case where impurities such as carbon is included in the gate insulating film 110, such impurities might also enter the oxide semiconductor film 106 and serve as impurities, as in the case of silicon. In that case, the concentrations of carbon included in the region 106c and the region 106e are lower than or equal to  $1.0 \times 10^{20}$  atoms/cm<sup>3</sup>, preferably lower than or equal to  $1.0 \times 10^{19}$  atoms/cm<sup>3</sup>.

10 [0130]

5

15

20

25

30

In order to prevent impurities such as silicon from entering the oxide semiconductor film 106, the gate insulating film 110 may be formed in such a manner as not to damage the oxide semiconductor film 106. For example, in the case where a silicon oxide film is formed as the gate insulating film 110 by a sputtering method, the impact caused by silicon (that is a constituent element of the gate insulating film 110) colliding with the oxide semiconductor film 106 may be reduced. For achieving the above, specifically, a method in which the power for deposition of the gate insulating film 110 is low, a method in which the pressure for deposition of the gate insulating film 110 is high, a method in which a distance between a target and a substrate (T-S distance) is increased in deposition of the gate insulating film 110, or the like can be used. However, a formation method of the gate insulating film 110 is not limited to the above. For example, a silicon oxide film, a silicon oxynitride film, a silicon nitride oxide film, or the like, which is formed by a PE-CVD method, can be used. A PE-CVD method is preferred to a sputtering method because with use of the PE-CVD method, the oxide semiconductor film 106 serving as a base film is less damaged.

[0131]

As described above, the concentrations of impurities such as silicon and carbon entering the region 106c and the region 106e in the oxide semiconductor film 106 are reduced, whereby change in characteristics of the transistor 160 can be suppressed. Further, in the case where the oxide semiconductor film 106 is a CAAC-OS film, a crystal portion can be formed even in the vicinity with the gate insulating film 110.

When the transistor 160 is formed using such an oxide semiconductor film 106, a semiconductor device with stable electric characteristics can be provided.

[0132]

5

10

20

25

30

Note that the details of the other components of the transistor are described with reference to FIGS. 4A to 4D and FIGS. 5A and 5B, in description of a method for manufacturing the transistor 160 below.

[0133]

<Manufacturing Method of Transistor 160>

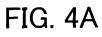

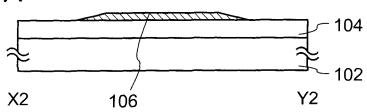

Hereinafter, an example of a method for manufacturing the transistor 160 illustrated in FIGS. 3A and 3B of this embodiment is described with reference to FIGS. 4A to 4D and FIGS. 5A and 5B.

[0134]

First, the substrate 102 is prepared. A substrate having a structure similar to that described in Embodiment 1 can be used as the substrate 102.

15 [0135]

Next, the base insulating film 104 is formed over the substrate 102 (see FIG. 4A). The base insulating film 104 has a function of preventing diffusion of an impurity element such as hydrogen or moisture from the substrate 102, and can be formed with a single-layer structure or a stacked structure using one or more of a silicon nitride film, a silicon oxide film, a silicon nitride oxide film, and a silicon oxynitride film.

[0136]

In addition, the base insulating film 104 has another function of supplying oxygen to the oxide semiconductor film 106 formed later. For example, in the case where an insulating film containing an oxide is formed as the base insulating film 104, by heating the base insulating film 104, part of contained oxygen can be released. Thus, oxygen can be supplied to the oxide semiconductor film 106, and oxygen vacancies in the oxide semiconductor film 106 can be filled accordingly. In particular, the base insulating film 104 preferably contains a large amount of oxygen which exceeds at least the stoichiometry thereof. For example, a film of silicon oxide represented by the formula  $SiO_{2+\alpha}$  ( $\alpha > 0$ ) is preferably used as the base insulating film 104, oxygen