(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-95064

(P2012-95064A)

(43) 公開日 平成24年5月17日(2012.5.17)

(51) Int.Cl.

HO3M 13/15 (2006.01)

F 1

HO3M 13/15

テーマコード(参考)

5 J O 6 5

審査請求 未請求 請求項の数 6 O L (全 15 頁)

(21) 出願番号

特願2010-240243 (P2010-240243)

(22) 出願日

平成22年10月27日 (2010.10.27)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

100082131

弁理士 稲本 義雄

100121131

弁理士 西川 孝

横川 峰志

東京都港区港南1丁目7番1号 ソニー株式会社内

新谷 修

東京都港区港南1丁目7番1号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】復号装置および方法、並びにプログラム

## (57) 【要約】

【課題】メモリの削減を行えるようにする。

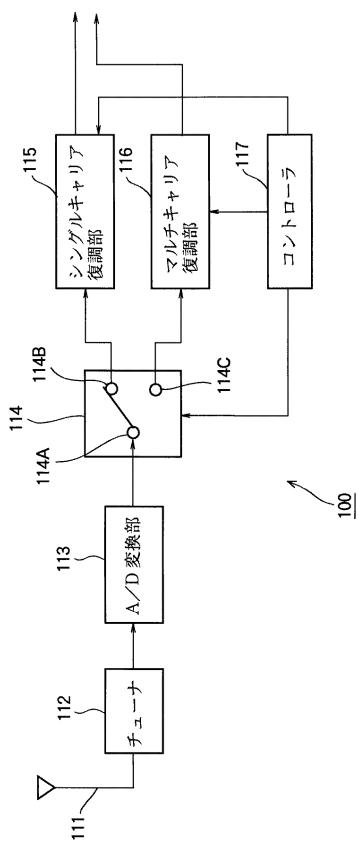

【解決手段】受信値メモリ152に記憶された1BCH符号語長のデータR0は、BCH復号処理部153に供給される。BCH復号処理部153は、供給されたデータR0における誤り位置と誤りの量を計算し、誤り訂正処理部154に供給するとともに、制御部151に対して、復号終了フラグを出力する。制御部151は、復号終了フラグを受信すると、データR0を、誤り訂正処理部154に供給するように受信値メモリ152に対して指示を出す。制御部151は、受信値メモリ152に対して、同一のデータを2度読み出すように指示を出す。本発明は、BCH復号を行う復号装置を含むデジタル放送波を受信する受信装置に適用できる。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

受信値を記憶する記憶手段と、

前記受信値の誤りを検知する検知手段と、

前記受信値に対して、前記検知手段により検知された誤りを訂正する誤り訂正手段と、

前記記憶手段からの前記受信値の読み出しを制御する制御手段と

を備え、

前記制御手段は、前記検知手段に前記受信値が読み出されるように1回目の読み出しを制御し、前記検知手段により誤りが検知された後の時点で、前記誤り訂正手段に前記1回目の読み出しのときと同一の前記受信値が読み出されるように2回目の読み出しを制御する

10

復号装置。

**【請求項 2】**

前記検知手段は、BCH復号を行う

請求項1に記載の復号装置。

**【請求項 3】**

前記制御手段は、1パケットに含まれる受信値単位で読み出しを制御する

請求項1に記載の復号装置。

**【請求項 4】**

前記受信値は、LDPC復号後のデータである

請求項1に記載の復号装置。

20

**【請求項 5】**

受信値を記憶する記憶手段と、

前記受信値の誤りを検知する検知手段と、

前記受信値に対して、前記検知手段により検知された誤りを訂正する誤り訂正手段と、

前記記憶手段からの前記受信値の読み出しを制御する制御手段と

を備える復号装置の復号方法において、

前記制御手段は、前記検知手段に前記受信値が読み出されるように1回目の読み出しを制御し、前記検知手段により誤りが検知された後の時点で、前記誤り訂正手段に前記1回目の読み出しのときと同一の前記受信値が読み出されるように2回目の読み出しを制御する

30

ステップを含む復号方法。

**【請求項 6】**

受信値を記憶する記憶手段と、

前記受信値の誤りを検知する検知手段と、

前記受信値に対して、前記検知手段により検知された誤りを訂正する誤り訂正手段と、

前記記憶手段からの前記受信値の読み出しを制御する制御手段と

を備える復号装置を制御するコンピュータが読み取り可能なプログラムであって、

前記制御手段は、前記検知手段に前記受信値が読み出されるように1回目の読み出しを制御し、前記検知手段により誤りが検知された後の時点で、前記誤り訂正手段に前記1回目の読み出しのときと同一の前記受信値が読み出されるように2回目の読み出しを制御する

40

ステップを含む処理をコンピュータに実行させるプログラム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は復号装置および方法、並びにプログラムに関し、特に、より精度良く復号ができるようにした復号装置および方法、並びにプログラムに関する。

**【背景技術】****【0002】**

50

BCH (Bose-Chaudhuri-Hocquenghem) 符号は、誤り訂正符号の 1 つであり、パラメータをうまく選択することで訂正できる誤りの数を決定することができる。近年では、デジタル放送波の規格であるDVB-T2(Digital Video Broadcasting-Terrestrial2)、DVB-C2(Digital Video Broadcasting-Cable2)、DTMB(Digital Terrestrial Multimedia Broadcast)などの規格の誤り訂正符号として、LDPC(Low-Density Parity-Check)符号と連接した形で BCH 符号が採用されている。

#### 【0003】

BCH 符号の復号は、1 BCH 符号語毎に復号処理を行うが、

(1)受信値から誤り位置および誤りの値を計算し、

(2)受信値のうち、求めた誤り位置のデータから誤りの値を除去する、

10

ことで誤り訂正が行われる。このような BCH 符号を復号する復号装置について説明する。

#### 【0004】

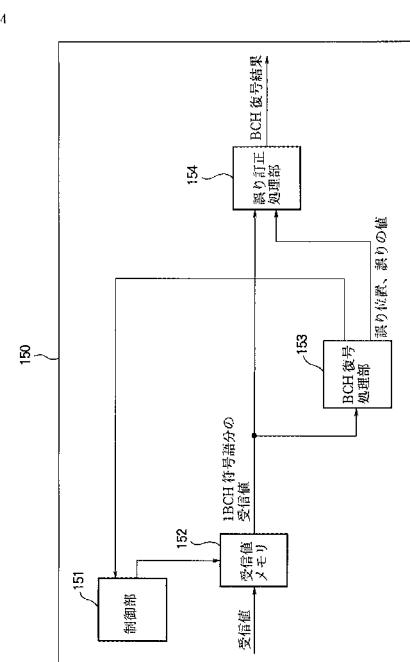

図 1 は、BCH 符号を復号する復号装置の一例の構成を示す図である。図 1 に示した復号装置 10 は、制御部 11、受信値メモリ 12、制御部 13、復号用メモリ 14、BCH 復号処理部 15、および誤り訂正処理部 16 を備えている。

#### 【0005】

制御部 11 は、受信値メモリ 12 を制御し、入力された受信値を受信値メモリ 12 に格納させる。また制御部 11 は、BCH 復号処理部 15 からの復号終了フラグを受け取った後、受信値メモリ 12 に格納された受信値から次の 1 BCH 符号語分を読み出すように指示を出す。受信値メモリ 12 から読み出された受信値は、復号用メモリ 14 および BCH 復号処理部 15 に入力される。

20

#### 【0006】

制御部 13 は、復号用メモリ 14 を制御し、受信値メモリ 12 からの出力である受信値(1 BCH 符号語分)を復号用メモリ 14 に格納させる。また制御部 13 は、1 BCH 符号語分の受信値が格納された後、BCH 復号処理部 15 からの復号終了フラグを受け取ったら、復号用メモリ 14 に、格納されている受信値を読み出すように指示を出し、制御する。

#### 【0007】

BCH 復号処理部 15 は、入力された 1 BCH 符号語分の受信値が入力されたら、誤り位置および誤りの値を計算する。また、BCH 復号処理部 15 は、復号の終了時に、そのことを制御部 11 と制御部 13 に通知するための復号終了フラグを生成し、供給する。

30

#### 【0008】

誤り訂正処理部 16 は、復号用メモリ 14 から読み出された受信値と BCH 復号処理部 15 で求められた誤り位置と誤りの値を取り、受信値の中で、誤り位置の受信値から誤りの値を除去することにより、誤りを訂正し、BCH の復号結果を後段の処理部に出力する。

#### 【0009】

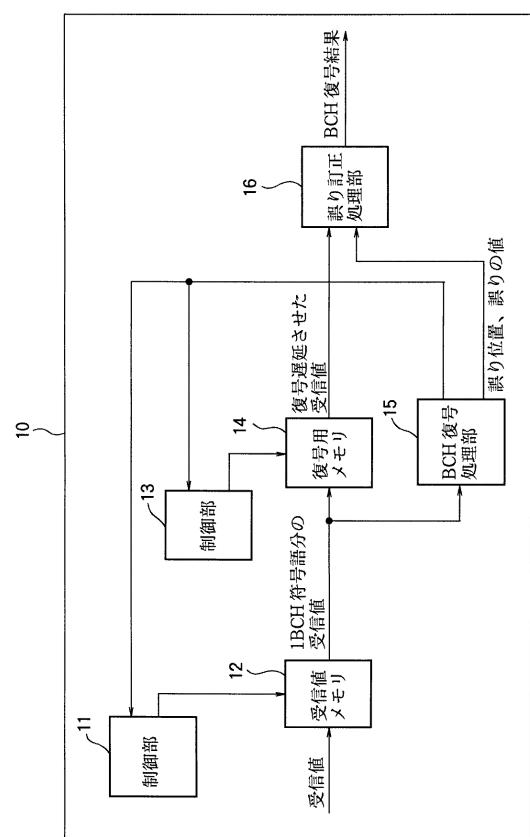

図 2 に、図 1 に示した復号装置 10 における復号処理の流れを示し、図 2 を参照して、上記の復号処理の流れについて説明する。

#### 【0010】

データ R0 を、時刻 t0 から時刻 t1 までの時間 T0 のときに、受信値メモリ 12 から読み出されるデータであるとし、1 BCH 符号長分の受信値ベクトルであるとする。時刻 t1 から、受信値メモリ 12 からデータ R0 が読み出されると、その読み出されたデータ R0 は、復号用メモリ 14 に供給され、格納されるとともに、BCH 復号処理部 15 にも供給される。BCH 復号処理部 15 は、時刻 t0 から、供給されたデータ R0 の復号を開始する。

40

#### 【0011】

時刻 t1 において、受信値メモリ 12 からのデータ R0 の読み出しが完了し、復号用メモリ 14 がデータ R0 の格納を完了し、BCH 復号処理部 15 が、データ R0 の復号を完了すると、復号用メモリ 14 から、データ R0 が、誤り訂正処理部 16 に出力される。同

50

タイミングで、BCH復号処理部15からは、誤り位置と誤りの量が、誤り訂正処理部16に供給される。さらに、受信値メモリ12からは、次のデータであるデータR1が、復号用メモリ14とBCH復号処理部15に対して出力される。誤り訂正処理部16は、時刻t1から、データR0に対して、誤り位置および誤りの値を用いた誤り訂正処理を施し、データD0を生成し、後段の処理部に出力する。

#### 【0012】

時刻t2において、受信値メモリ12からのデータR1の読み出しが完了し、復号用メモリ14がデータR1の格納を完了し、BCH復号処理部15が、データR1の復号を完了すると、復号用メモリ14から、データR1が、誤り訂正処理部16に出力される。同タイミングで、BCH復号処理部15からは、誤り位置と誤りの量が、誤り訂正処理部16に供給される。さらに、受信値メモリ12からは、次のデータであるデータR2が、復号用メモリ14とBCH復号処理部15に対して出力される。誤り訂正処理部16は、時刻t2から、データR1に対して、誤り位置および誤りの値を用いた誤り訂正処理を施し、データD1を生成し、後段の処理部に出力する。

10

#### 【0013】

このような各部での処理が行われることで、BCH符号における誤り訂正を施す復号処理が行われる。(特許文献1参照)

#### 【先行技術文献】

#### 【特許文献】

#### 【0014】

20

【特許文献1】特開平06-261024号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0015】

図1を参照するに、BCH符号を復号する際、受信値を1BCH符号語の復号遅延分だけ遅延させるための復号用メモリ14が必要である。すなわち、図1に示した従来の復号装置10においては、受信値メモリ12と復号用メモリ14の2つのメモリが必要であった。メモリの削減は、回路規模の縮小や、コストの削減につながるため、メモリを削減することが望まれている。

#### 【0016】

30

本発明は、このような状況に鑑みてなされたものであり、復号の性能を落とすことなく、メモリを削減することができるようとするものである。

#### 【課題を解決するための手段】

#### 【0017】

本発明の一側面の復号装置は、受信値を記憶する記憶手段と、前記受信値の誤りを検知する検知手段と、前記受信値に対して、前記検知手段により検知された誤りを訂正する誤り訂正手段と、前記記憶手段からの前記受信値の読み出しを制御する制御手段とを備え、前記制御手段は、前記検知手段に前記受信値が読み出されるように1回目の読み出しを制御し、前記検知手段により誤りが検知された後の時点で、前記誤り訂正手段に前記1回目の読み出しのときと同一の前記受信値が読み出されるように2回目の読み出しを制御する。

40

#### 【0018】

前記検知手段は、BCH復号を行うようにすることができる。

#### 【0019】

前記制御手段は、1パケットに含まれる受信値単位で読み出しを制御するようにすることができる。

#### 【0020】

前記受信値は、LDPC復号後のデータであるようにすることができる。

#### 【0021】

本発明の一側面の復号方法は、受信値を記憶する記憶手段と、前記受信値の誤りを検知

50

する検知手段と、前記受信値に対して、前記検知手段により検知された誤りを訂正する誤り訂正手段と、前記記憶手段からの前記受信値の読み出しを制御する制御手段とを備える復号装置の復号方法において、前記制御手段は、前記検知手段に前記受信値が読み出されるように1回目の読み出しを制御し、前記検知手段により誤りが検知された後の時点で、前記誤り訂正手段に前記1回目の読み出しのときと同一の前記受信値が読み出されるように2回目の読み出しを制御するステップを含む。

#### 【0022】

本発明の一側面のプログラムは、受信値を記憶する記憶手段と、前記受信値の誤りを検知する検知手段と、前記受信値に対して、前記検知手段により検知された誤りを訂正する誤り訂正手段と、前記記憶手段からの前記受信値の読み出しを制御する制御手段とを備える復号装置を制御するコンピュータが読み取り可能なプログラムであって、前記制御手段は、前記検知手段に前記受信値が読み出されるように1回目の読み出しを制御し、前記検知手段により誤りが検知された後の時点で、前記誤り訂正手段に前記1回目の読み出しのときと同一の前記受信値が読み出されるように2回目の読み出しを制御するステップを含む処理をコンピュータに実行させる。

10

#### 【0023】

本発明の一側面の復号装置および方法、並びにプログラムにおいては、受信値が記憶され、受信値の誤りが検知され、検知された誤りにより受信値が訂正される。受信値を記憶している記憶手段から、同一の受信値が、2回読み出されることで、誤り訂正が行われる。

20

#### 【発明の効果】

#### 【0024】

本発明の一側面によれば、復号の処理に用いられるメモリを削減することが可能となる。またメモリを削減しても、復号の精度を劣化させることなく復号を行うことができる。

#### 【図面の簡単な説明】

#### 【0025】

【図1】従来のBCH符号を復号する復号装置の一例の構成を示す図である。

【図2】復号装置の処理について説明するための図である。

【図3】デジタル放送波を受信する受信装置の構成を説明するための図である。

30

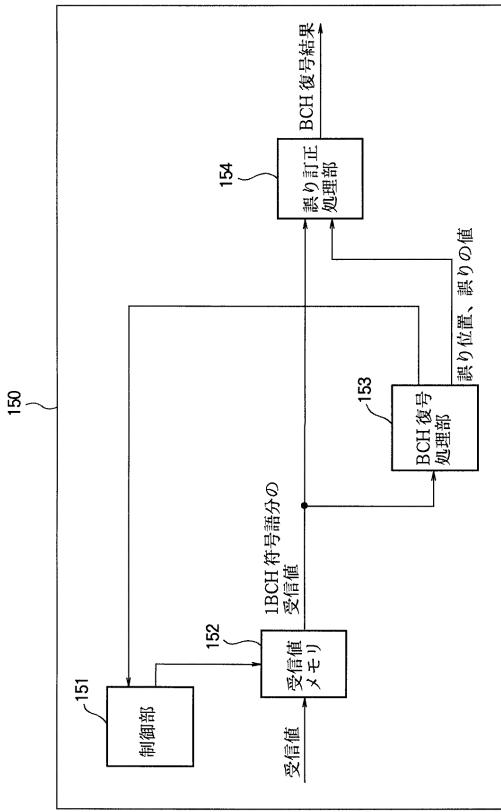

【図4】本発明を適用した復号装置の一実施の形態の構成を示す図である。

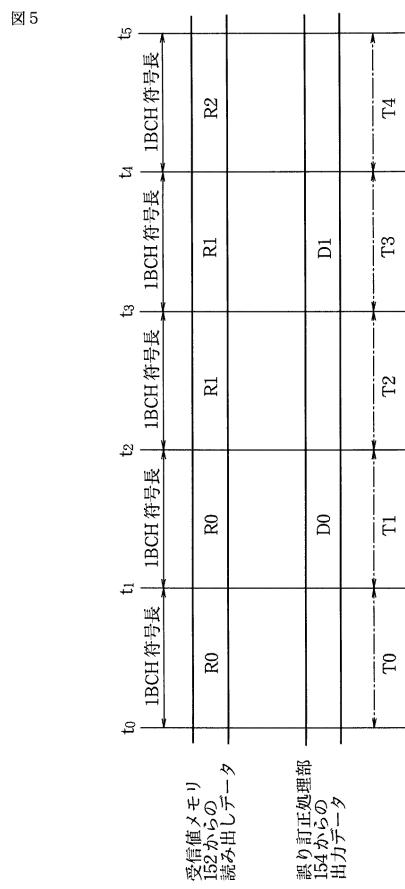

【図5】復号装置の処理について説明するための図である。

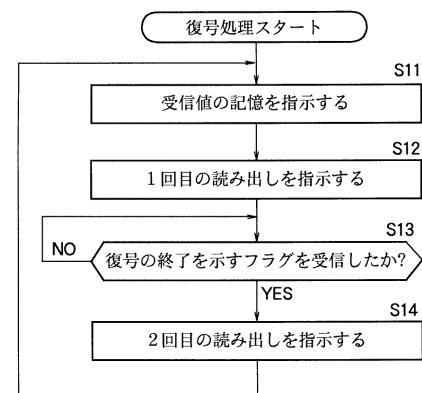

【図6】復号装置の処理について説明するためのフローチャートである。

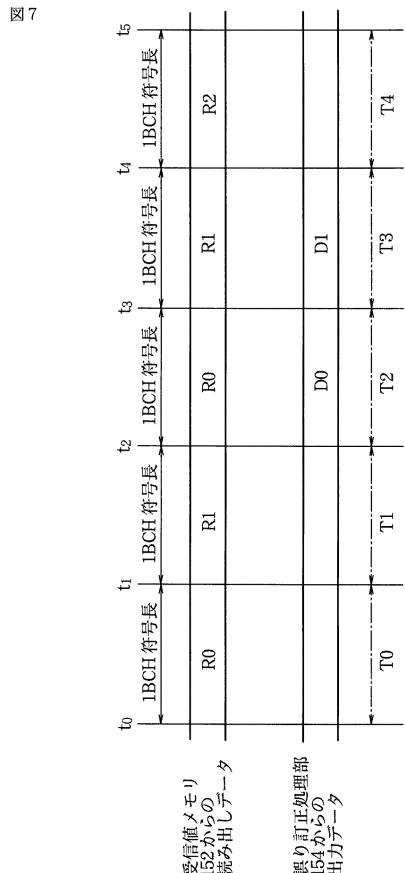

【図7】復号装置の処理について説明するための図である。

【図8】記録媒体について説明するための図である。

#### 【発明を実施するための形態】

#### 【0026】

以下に、本発明の実施の形態について図面を参照して説明する。以下に説明する復号装置は、デジタル地上波放送の受信装置に適用できる。よって、受信装置に適用した場合を一実施の形態として説明をする。

40

#### 【0027】

#### [受信装置の構成例]

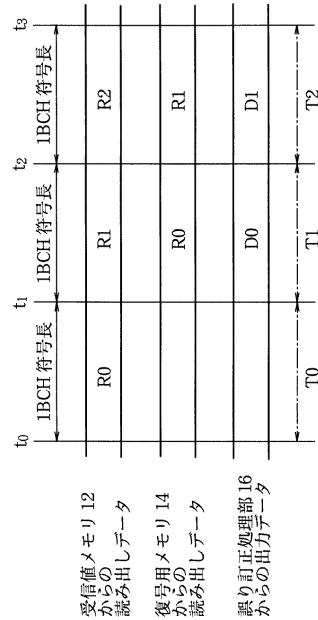

図3は、本発明の一実施形態に係る受信装置の構成例を示す図である。

#### 【0028】

受信装置100は、アンテナ111、チューナ112、A/D変換部113、切替部114、シングルキャリア復調部115、マルチキャリア復調部116、およびコントローラ117により構成される。受信装置100は、例えば、地上デジタル放送の規格であるDTMB(Digital Terrestrial Multimedia Broadcast)規格に対応した受信装置である。

#### 【0029】

DTMB規格では、データの変調方式として、シングルキャリアを使った変調方式とマルチキャリアを使った変調方式のうちのいずれかを選択することができるようになされている

50

。DTMB規格に対応した受信装置には、シングルキャリアを使った変調方式で伝送されてきたデータを復調するための機能と、マルチキャリアを使った変調方式で伝送されてきたデータを復調するための機能が用意される。

#### 【0030】

以下、適宜、シングルキャリアを使った変調方式でデータを伝送することをシングルキャリア伝送といい、マルチキャリアを使った変調方式でデータを伝送することをマルチキャリア伝送という。

#### 【0031】

チューナ112は、RF信号を受信し、周波数変換を行って得られたIF信号をA/D変換部113に出力する。

10

#### 【0032】

A/D変換部113は、チューナ112から供給された信号に対してA/D変換を施し、得られたデータを出力する。

#### 【0033】

切替部114は、A/D変換部113から供給されたデータの出力先をコントローラ117による制御に従って切り替える。切替部114は、シングルキャリア伝送によって伝送されてきたデータの復調を行う場合、スイッチ114Aを端子114Bに接続し、A/D変換部113から供給されたデータをシングルキャリア復調部115に出力する。また、切替部114は、マルチキャリア伝送によって伝送されてきたデータの復調を行う場合、スイッチ114Aを端子114Cに接続し、A/D変換部113から供給されたデータをマルチキャリア復調部116に出力する。

20

#### 【0034】

シングルキャリア復調部115は、切替部114から供給されたデータをコントローラ117による制御に従って復調し、得られたデータを出力する。

#### 【0035】

マルチキャリア復調部116は、切替部114から供給されたデータをコントローラ117による制御に従って復調し、得られたデータを出力する。マルチキャリア伝送にOFDM方式が用いられている場合、マルチキャリア復調部116に対しては、A/D変換部113の出力を対象として図示せぬ処理部において行われた直交復調によって得られたベースバンドのOFDM信号が入力される。

30

#### 【0036】

シングルキャリア復調部115、またはマルチキャリア復調部116により復調されたデータは、例えば後段の処理部に供給され、誤り訂正等の処理が施される。

#### 【0037】

コントローラ117は、所定のプログラムを実行し、受信装置100の全体の動作を制御する。例えば、コントローラ117は、受信中のチャネルで用いられている変調方式がシングルキャリア伝送であるのかマルチキャリア伝送であるのかに応じて切替部114を制御し、データの出力先を切り替える。

#### 【0038】

シングルキャリア復調部115またはマルチキャリア復調部116により復調されたデータは、図4に示す復号部に入力される。図4に示した復号部は、BCH符号を復号する復号部である。シングルキャリア復調部115またはマルチキャリア復調部116からのデータに、例えば、時間ディンタリープなどの処理が施されたデータであり、BCH復号ができる状態のデータが、復号部に入力される。また、DTMB規格では、時間ディンタリープの処理が施された後、LDPC復号が行われ、そのLDPC復号を行うLDPC復号部からの出力が、BCH復号を行う復号部に入力されるため、復号部に入力されるデータは、LDPC復号された復号結果であり、BCH復号ができる状態のデータである。

40

#### 【0039】

以下の説明においては、図4に示した復号部150に入力されるデータを受信値と記述する。この受信値は、上記したように、シングルキャリア復調部115またはマルチキャ

50

リア復調部 116 により復調されたデータが、時間ディンタリーブやLDPC復号の処理が施されたデータである。または、DTMB規格以外の装置において、BCH復号を行う場合におけるBCH復号を行う前のデータである。さらには、所定の通信路からのデータであっても良い。

#### 【0040】

図4に示した復号部150は、制御部151、受信値メモリ152、BCH復号処理部153、誤り訂正処理部154を備える。

#### 【0041】

制御部151は、受信値メモリ152を制御し、復号部150に入力された受信値を格納させる。受信値メモリ152に格納された受信値は、制御部151の制御のもと、BCH復号処理部153と誤り訂正処理部154に供給される。図5を参照し詳細は後述するが、受信値メモリ152からの受信値の読み出しは、以下のように行われる。

10

#### 【0042】

まず、1BCH符号語分の受信値が、所定のタイミングで受信値メモリ152から読み出され、BCH復号処理部153に供給される。このBCH復号処理部153に対する読み出しを、適宜、“1回目の読み出し”と記述する。その後、BCH復号処理部153が、復号の処理が終了したことを示す復号終了フラグを制御部151に出し、制御部151が、その復号終了フラグを受信すると、2回目の読み出しが行われる。

#### 【0043】

制御部151は、1回目の読み出しと同じ受信値を、2回目の読み出しとして、受信値メモリ152から読み出すための制御を行う。2回目の読み出しにおいては、受信値メモリ152から読み出された受信値（1BCH符号語分）は、誤り訂正処理部154に供給される。このように、制御部151は、受信値メモリ152から、2度の同一の受信値の読み出しを行うための制御を行う。

20

#### 【0044】

BCH復号処理部153は、1回目の読み出しで受信値メモリ152から読み出された1BCH符号語分の受信値が入力されると、誤り位置および誤りの値を計算し、保持する。BCH復号処理部153は、受信値の誤りを検知する。BCH復号処理部153は、誤り位置と誤りの値を計算すると、復号終了フラグを生成し、制御部151に出力する。

#### 【0045】

誤り訂正処理部154は、2回目の読み出しで受信値メモリ152から読み出された1BCH符号語分の受信値と、BCH復号処理部153で求められた誤り位置と誤りの値が入力されると、受信値の中の誤り位置の受信値から誤りの値を除去することにより、誤りを訂正し、受信値（符号語）を復号する。

30

#### 【0046】

次に、図5を参照し、図4に示した復号部150での処理について説明をする。データR0を、時刻t0から時刻t1までの時間T0のときに、受信値メモリ152から読み出されるデータであるとし、1BCH符号長分の受信値ベクトルであるとする。時刻t0から、受信値メモリ152からデータR0が読み出されると、その読み出されたデータR0は、BCH復号処理部153に供給される。BCH復号処理部153は、時刻t0から、供給されたデータR0の復号を開始する。

40

#### 【0047】

時刻t1において、受信値メモリ152からのデータR0の読み出しが完了し、BCH復号処理部153が、データR0の復号を完了する。BCH復号処理部153は、復号を完了すると、制御部151に復号終了フラグを出力する。時刻t1において、そのような復号終了フラグを受信した制御部151は、2度目の読み出しを開始する。すなわち、制御部151は、時刻t1から、受信値メモリ152を制御し、再度、データR0を、誤り訂正処理部154に対して出力するように指示を出す。

#### 【0048】

時刻t1においてはBCH復号処理部153から、誤り位置と誤りの量も、誤り訂正処

10

20

30

40

50

理部 154 に供給される。誤り訂正処理部 154 は、時刻 t1 から、データ R0 に対して、誤り位置および誤りの値を用いた誤り訂正処理を施し、データ D0 を生成し、後段の処理部に出力する。

#### 【0049】

時刻 t2 において、データ R1 が、受信値メモリ 152 から読み出されると、その読み出されたデータ R1 は、BCH復号処理部 153 に供給される。BCH復号処理部 153 は、時刻 t2 から、供給されたデータ R1 の復号を開始する。時刻 t3 において、受信値メモリ 152 からのデータ R1 の読み出しが完了し、BCH復号処理部 153 が、データ R1 の復号を完了する。BCH復号処理部 153 は、復号を完了すると、制御部 151 に復号終了フラグを出力する。時刻 t3 において、そのような復号終了フラグを受信した制御部 151 は、2 度目の読み出しを開始する。すなわち、制御部 151 は、時刻 t3 から、受信値メモリ 152 を制御し、再度、データ R1 を、誤り訂正処理部 154 に対して出力するように指示を出す。

10

#### 【0050】

時刻 t3 においては BCH復号処理部 153 から、誤り位置と誤りの量も、誤り訂正処理部 154 に供給される。誤り訂正処理部 154 は、時刻 t3 から、データ R1 に対して、誤り位置および誤りの値を用いた誤り訂正処理を施し、データ D1 を生成し、後段の処理部に出力する。このような処理が、復号部 150 内の各部で繰り返し行われる。

20

#### 【0051】

このように、受信値メモリ 152 から同一の受信値を 2 度読み出すように制御部 151 は受信値メモリ 152 を制御する。1 度目の読み出しほは、受信値メモリ 152 から BCH復号処理部 153 に対して行われ、2 度目の読み出しほは、受信値メモリ 152 から誤り訂正処理部 154 に対して行われる。このような読み出しほが行われることで、図 1 に示した従来の復号装置 10 における復号用メモリ 14 を削除することが可能となる。また、復号用メモリ 14 の受信値の書き込みや読み出しほを制御する制御部 13 も削除することが可能となる。

20

#### 【0052】

次に、図 5 を参照して説明した復号を行う復号部 150 の処理について、図 6 のフローチャートを参照して説明する。図 6 のフローチャートを参照して説明する処理は、主に、制御部 151 が行う処理である。

30

#### 【0053】

ステップ S11 において、制御部 151 は、受信値メモリ 152 を制御し、受信値を記憶させる。例えば、復号部 150 の前段に、LDPC復号を行う処理部がある場合、LDPC復号されたデータが、受信値（BCH符号語）として受信値メモリ 152 に供給され、記憶される。

30

#### 【0054】

ステップ S12 において、制御部 151 は、受信値メモリ 152 を制御し、記憶している受信値のうち 1 BCH 符号語分の受信値を、BCH復号処理部 153 に出力させる。すなわち 1 回目の読み出しほの指示が行われる。

40

#### 【0055】

ステップ S13 において、制御部 151 は、BCH復号処理部 153 から、復号の終了を示す信号を受信したか否かを判断する。BCH復号処理部 153 は、復号を終了し、誤り位置と誤りの値を算出できたとき、制御部 151 に対して、終了を通知する復号終了フラグを出すように構成されている。また、BCH復号処理部 153 は、誤り位置と誤りの値を算出した場合、その算出した誤り位置と誤りの値を、誤り訂正処理部 154 に出力するように構成されている。

40

#### 【0056】

制御部 151 は、ステップ S13 において、復号終了フラグを受信したと判断するまで、待機状態を維持し、復号の終了を示す信号を受信したと判断すると、処理をステップ S14 に進める。ステップ S14 において、制御部 151 は、2 回目の読み出しほを指示する

50

。すなわち、制御部 151 は、受信値メモリ 152 を制御し、ステップ S12において1回目の読み出しを指示した受信値と同一の受信値を、誤り訂正処理部 154 に対して出力させる。

#### 【0057】

誤り訂正処理部 154 は、受信値と、その受信値に対する誤り位置と誤りの値を取得すると、誤り訂正の処理を行い、誤りが訂正されたデータを後段の処理部（不図示）に出力する。制御部 151 は、2回目の読み出しを受信値メモリ 152 に指示した後、ステップ S11 に処理を戻し、それ以降の処理を繰り返す。

#### 【0058】

このように同一のデータが2度読み出され、誤り訂正の処理が行われることで、メモリを削減することが可能となる。

10

#### 【0059】

なお、図4に示した復号部 150においては、受信値メモリ 152 からの受信値は、BCH復号処理部 153 と誤り訂正処理部 154 に同時に供給される構成となっている。このように構成した場合、誤り訂正処理部 154 にも、1回目の読み出しのときに、受信値が供給されるが、BCH復号処理部 153 から誤り位置や誤りの値といった情報が供給されないときには、誤り訂正の処理を行わない。また、BCH復号処理部 153 には、2回目の読み出しのときにも受信値が供給されるが、BCH復号処理部 153 は、2回目の読み出しのときに供給されたデータに対して復号の処理は行わない。

20

#### 【0060】

復号部 150 の構成を、受信値メモリ 152 から出力される受信値の供給先を切り換えるスイッチを設ける構成としても良い。スイッチが切り換えられることにより、1回目の読み出しのときには、BCH復号処理部 153 に受信値メモリ 152 からの受信値が供給され、2回目の読み出しのときには、誤り訂正処理部 154 に受信値メモリ 152 からの受信値が供給されるような構成としても良い。このような構成とした場合、制御部 151 は、受信値メモリ 152 への読み出しの指示と、スイッチへの切り換えの指示を行う。

20

#### 【0061】

##### [第2の実施の形態について]

復号部 150 は、例えば、地上波デジタル放送の規格の1つであるDTMB方式で採用されているBCH復号を行う復号装置として適用できる。DTMB方式の場合、BCH符号の情報長が2つ分で1TSパケットが構成されている。このようなことを考慮し、第2の実施の形態として、1TSパケットで処理が行われるようにした場合について説明する。

30

#### 【0062】

1回目の読み出しのときに2つのBCH符号長分の受信値、すなわち1TSパケット分の受信値を受信値メモリ 152 から読み出し、それぞれの誤り位置および誤りの値を保持しておき、2回目の読み出しのときに2つのBCH符号長分の受信値を読み出し、それぞれのBCH符号に対して、保持した誤り位置および誤りの値を用いて訂正処理を行う。これにより、TSパケット単位で後段の処理に渡すことができる。

#### 【0063】

このような処理を行うようにした場合であっても、復号装置の構成は、図4に示した復号部 150 と同様の構成とすることができます、制御部 151 における処理を変えることで行うことができる。ここで、図7を参照し、第2の実施の形態における処理の流れについて説明する。

40

#### 【0064】

データ R0 を、時刻 t0 から時刻 t1 までの時間 T0 のときに、受信値メモリ 152 から読み出されるデータであるとし、1BCH符号長分の受信値ベクトルであるとする。時刻 t0 から、受信値メモリ 152 からデータ R0 が読み出されると、その読み出されたデータ R0 は、BCH復号処理部 153 に供給される。BCH復号処理部 153 は、時刻 t0 から、供給されたデータ R0 の復号を開始する。

#### 【0065】

50

時刻  $t_1$ において、受信値メモリ 152からのデータ  $R_0$ の読み出しが完了し、BCH復号処理部 153が、データ  $R_0$ の復号を完了する。BCH復号処理部 153は、データ  $R_0$ に対する誤り位置と誤りの量を保持する。一方で、時刻  $t_1$ において、データ  $R_1$ が、受信値メモリ 152から読み出される。その読み出されたデータ  $R_1$ は、BCH復号処理部 153に供給される。BCH復号処理部 153は、供給されたデータ  $R_1$ の復号を開始する。時刻  $t_2$ において、受信値メモリ 152からのデータ  $R_1$ の読み出しが完了し、BCH復号処理部 153が、データ  $R_2$ の復号を完了する。BCH復号処理部 153は、データ  $R_1$ に対する誤り位置と誤りの量を保持する。

#### 【0066】

1回目の読み出しが、このようにしてデータ  $R_0$ とデータ  $R_1$ が読み出される。すなわち、1TSパケットに含まれる2つのBCH符号長分の受信値が受信値メモリ 152から読み出され、復号される。制御部 151は、受信値メモリ 152に対して、1つのBCH符号長分の受信値の読み出しを指示する信号を出すようにしても良いし、2つのBCH符号長分の受信値の読み出しを指示する信号を出すようにしても良い。10

#### 【0067】

2回目の読み出しが、図7において、時刻  $t_2$ において開始される。すなわち、時刻  $t_2$ において、データ  $R_0$ が、受信値メモリ 152から読み出され、誤り訂正処理部 154に供給される。誤り訂正処理部 154は、時刻  $t_2$ から時刻  $t_3$ の時間  $T_2$ において、データ  $R_0$ に対して、BCH復号処理部 153で保持されていたデータ  $R_0$ の誤り位置および誤りの値を用いて誤り訂正処理を行う。誤り訂正処理後のデータ  $R_0$ は、データ  $D_0$ として、後段の処理部に出力される。20

#### 【0068】

同様に、時刻  $t_3$ において、データ  $R_1$ に対して2回目の読み出しが開始される。時刻  $t_3$ において、データ  $R_1$ が、受信値メモリ 152から読み出され、誤り訂正処理部 154に供給される。誤り訂正処理部 154は、時刻  $t_3$ から時刻  $t_4$ の時間  $T_3$ において、データ  $R_1$ に対して、BCH復号処理部 153で保持されていたデータ  $R_1$ の誤り位置および誤りの値を用いて誤り訂正処理を行う。誤り訂正処理後のデータ  $R_1$ は、データ  $D_1$ として、後段の処理部に出力される。

#### 【0069】

2回目の読み出しが、このようにしてデータ  $R_0$ とデータ  $R_1$ が読み出される。すなわち、1TSパケットに含まれる2つのBCH符号長分の受信値が受信値メモリ 152から読み出され、誤り訂正処理が施される。制御部 151は、受信値メモリ 152に対して、1つのBCH符号長分の受信値の読み出しを指示する信号を出すようにしても良いし、2つのBCH符号長分の受信値の読み出しを指示する信号を出すようにしても良い。30

#### 【0070】

このように復号、誤り訂正が行われることで、データ  $D_0$ とデータ  $D_1$ が連続して出力されることになる。すなわち、1TSパケットに含まれる2つのBCH符号長分のBCH復号結果が、後段の処理に供給されることになる。よって、1TSパケットでの処理ができるようになり、処理の簡素化など、後段の処理部で、データを扱いやすくなるといった効果を期待できる。40

#### 【0071】

このように、1TSパケットで処理が行われるようにした場合、復号部 150の処理は、図6のフローチャートに基づいて行われる。すなわち、第1の実施の形態と同様の処理フローで処理することが可能である。ここでは、再度図6を参照して復号部 150の処理について説明するが、異なる処理についてのみ説明を加える。

#### 【0072】

ステップ S12において、制御部 151において1回目の読み出しの指示が、受信値メモリ 152に対して行われるが、この指示は、2つのBCH符号長分の受信値を読み出すための指示である。よって、1つのBCH符号長分の受信値を読み出すための指示が、2回出されるようにしても良いし、2つのBCH符号長分の受信値を1回で読み出すための50

指示が出されるようにしても良い。

【0073】

同様に、ステップS14において、制御部151において2回目の読み出しの指示が、受信値メモリ152に対して行われるが、この指示は、2つのBCH符号長分の受信値を読み出すための指示である。よって、1つのBCH符号長分の受信値を読み出すための指示が、2回出されるようにしても良いし、2つのBCH符号長分の受信値を1回で読み出すための指示が出されるようにしても良い。

【0074】

このようにして、ステップS12、ステップS14において受信値の読み出しが行われるため、1回目の読み出しと、2回目の読み出しとを切り換えるための処理であるステップS13における判断は、2つのBCH符号長分の受信値に対する復号の処理が終了したか否かを示すフラグを受信したか否かが判断される処理となる。

10

【0075】

BCH復号処理部153が、1つのBCH符号長分の受信値に対する復号を行った時点で、復号終了フラグを出すように構成された場合、制御部151は、そのようなフラグを2回受信した時点で、復号の処理を示す信号を受信したと判断し、処理をステップS14に進め、2回目の読み出しの指示を出す。

【0076】

BCH復号処理部153が、2つのBCH符号長分の受信値に対する復号を行った時点で、復号終了フラグを出すように構成された場合、制御部151は、そのようなフラグを受信した時点で、復号の処理を示す信号を受信したと判断し、処理をステップS14に進め、2回目の読み出しの指示を出す。

20

【0077】

このようにして、同一のデータが2度読み出され、誤り訂正の処理が行われることで、メモリを削減することが可能となる。

【0078】

なお、上述した実施の形態においては、BCH符号を例にあげて説明したが、BCH符号以外の復号に関しても適用することができる。

【0079】

[記録媒体について]

30

上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、コンピュータにインストールされる。ここで、コンピュータには、専用のハードウェアに組み込まれているコンピュータや、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば汎用のパーソナルコンピュータなどが含まれる。

【0080】

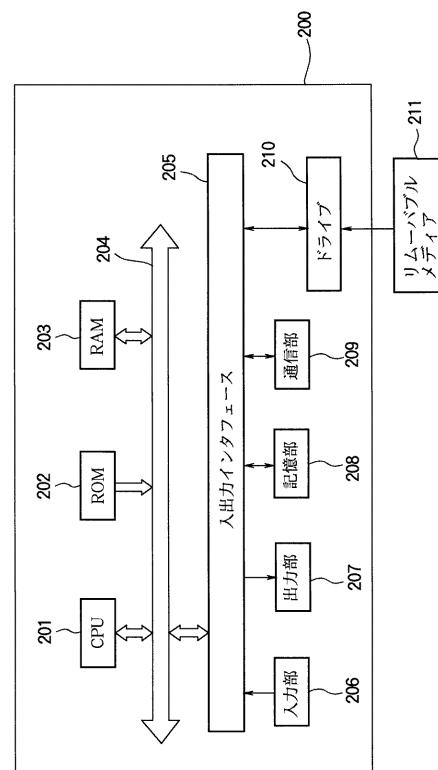

図8は、上述した一連の処理をプログラムにより実行するコンピュータのハードウェアの構成例を示すブロック図である。コンピュータにおいて、CPU(Central Processing Unit)201、ROM(Read Only Memory)202、RAM(Random Access Memory)203は、バス204により相互に接続されている。バス204には、さらに、入出力インターフェース205が接続されている。入出力インターフェース205には、入力部206、出力部207、記憶部208、通信部209、およびドライブ210が接続されている。

40

【0081】

入力部206は、キーボード、マウス、マイクロフォンなどよりなる。出力部207は、ディスプレイ、スピーカなどよりなる。記憶部208は、ハードディスクや不揮発性のメモリなどよりなる。通信部209は、ネットワークインターフェースなどよりなる。ドライブ210は、磁気ディスク、光ディスク、光磁気ディスク、または半導体メモリなどのリムーバブルメディア211を駆動する。

50

**【 0 0 8 2 】**

以上のように構成されるコンピュータでは、C P U 2 0 1 が、例えば、記憶部 2 0 8 に記憶されているプログラムを、入出力インターフェース 2 0 5 およびバス 2 0 4 を介して、R A M 2 0 3 にロードして実行することにより、上述した一連の処理が行われる。

**【 0 0 8 3 】**

コンピュータ(C P U 2 0 1)が実行するプログラムは、例えば、パッケージメディア等としてのリムーバブルメディア 2 1 1 に記録して提供することができる。また、プログラムは、ローカルエリアネットワーク、インターネット、デジタル衛星放送といった、有線または無線の伝送媒体を介して提供することができる。

**【 0 0 8 4 】**

コンピュータでは、プログラムは、リムーバブルメディア 2 1 1 をドライブ 2 1 0 に装着することにより、入出力インターフェース 2 0 5 を介して、記憶部 2 0 8 にインストールすることができる。また、プログラムは、有線または無線の伝送媒体を介して、通信部 2 0 9 で受信し、記憶部 2 0 8 にインストールすることができる。その他、プログラムは、R O M 2 0 2 や記憶部 2 0 8 に、あらかじめインストールしておくことができる。

**【 0 0 8 5 】**

なお、コンピュータが実行するプログラムは、本明細書で説明する順序に沿って時系列に処理が行われるプログラムであっても良いし、並列に、あるいは呼び出しが行われたとき等の必要なタイミングで処理が行われるプログラムであっても良い。

**【 0 0 8 6 】**

また、本明細書において、システムとは、複数の装置により構成される装置全体を表すものである。

**【 0 0 8 7 】**

なお、本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

**【 符号の説明 】****【 0 0 8 8 】**

1 1 1 アンテナ、 1 1 2 チューナ、 1 1 3 A / D 変換部、 1 1 5 シングルキャリア復調部、 1 1 6 マルチキャリア復調部、 1 1 7 コントローラ、 1 5 0 復号装置、 1 5 1 制御部、 1 5 2 受信値メモリ、 1 5 3 B C H 復号処理部、 1 5 4 誤り訂正処理部

10

20

30

【図 1】

図 1

【図 2】

図 2

【図 3】

図 3

【図 4】

図 4

【 四 5 】

【 図 7 】

【 四 6 】

【 図 8 】

---

フロントページの続き

(72)発明者 中田 豊

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 池谷 亮志

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 5J065 AD11 AH17 AH20