(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-4480

(P2009-4480A)

(43) 公開日 平成21年1月8日(2009.1.8)

(51) Int.Cl.

HO1L 29/78 (2006.01)

HO1L 29/423 (2006.01)

HO1L 29/49 (2006.01)

HO1L 21/8242 (2006.01)

HO1L 27/108 (2006.01)

F 1

HO1L 29/78

HO1L 29/58

HO1L 27/10

301V

G

671B

テーマコード(参考)

4M104

5F083

5F140

審査請求 未請求 請求項の数 4 O L (全 8 頁)

(21) 出願番号

(22) 出願日

特願2007-162424 (P2007-162424)

平成19年6月20日 (2007.6.20)

(71) 出願人 500174247

エルピーダメモリ株式会社

東京都中央区八重洲2-2-1

(74) 代理人 100123788

弁理士 宮崎 昭夫

(74) 代理人 100106138

弁理士 石橋 政幸

(74) 代理人 100127454

弁理士 緒方 雅昭

(72) 発明者 氏原 慎吾

東京都中央区八重洲2-2-1 エルピー

ダメモリ株式会社内

F ターム(参考) 4M104 AA01 BB01 CC05 DD03 EE03

EE16 FF27 GG09 GG16 HH14

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】素子特性の優れた半導体装置を簡便に製造する。

【解決手段】第1の溝内の素子分離膜と活性領域を有する半導体基板を用意する工程と、この半導体基板上にマスク形成用膜を形成する工程と、活性領域を横切る開口を有する第1のマスクを形成する工程と、第1のマスクを用いて異方性エッティングを行って、前記マスク形成用膜からなる第2のマスクと、活性領域内に、対向する素子分離膜露出面を有し且つ第1の溝より深い第2の溝を形成する工程と、第2の溝内の半導体基板表面と素子分離膜露出面との境界を含む領域に酸素イオンが照射されるように、第2のマスクを用いて酸素イオンを斜めに注入する工程と、第2の溝内の酸素イオンが注入された領域を酸化して酸化領域を形成する工程と、この酸化領域を除去する工程を有する半導体装置の製造方法。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

第1の溝と、第1の溝内に埋め込まれた素子分離膜と、この素子分離膜に囲まれた活性領域を有する半導体基板を用意する工程と、

前記半導体基板上にマスク形成用膜を形成する工程と、

前記マスク形成用膜上に、前記活性領域を横切る開口を有する第1のマスクを形成する工程と、

第1のマスクを用いて異方性エッティングを行って、前記開口に対応する開口を有する前記マスク形成用膜からなる第2のマスクと、前記活性領域内に、対向する素子分離膜露出面を有し且つ第1の溝より浅い第2の溝を形成する工程と、

第2の溝内の半導体基板表面と素子分離膜露出面との境界を含む領域に酸素イオンが照射されるように、第2の溝内に、第2のマスクを用いて、酸素イオンを斜めに注入する工程と、

第2の溝内の酸素イオンが注入された領域を酸化して酸化領域を形成する工程と、

前記酸化領域を除去する工程を有する半導体装置の製造方法。

**【請求項 2】**

第2の溝内を含む半導体基板表面の酸化を行って、第2の溝内の酸素イオンが注入された領域を酸化して酸化領域を形成するとともに、この酸化領域を含む酸化膜を形成する工程と、

前記酸化膜を除去するとともに、前記酸化領域を除去する工程を有する請求項1に記載の半導体装置の製造方法。

**【請求項 3】**

第2のマスクを除去する工程と、

第2の溝内を含む半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜が形成された第2の溝内を埋め込むように導電膜を形成し、この導電膜をパターニングしてゲート電極を形成する工程と、

前記ゲート電極の両側の当該活性領域に不純物を導入してソース／ドレイン領域を形成する工程をさらに有する請求項1又は2に記載の半導体装置の製造方法。

**【請求項 4】**

前記素子分離膜は酸化シリコン膜、前記マスク形成用膜は窒化シリコン膜である請求項1から3のいずれかに記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置の製造方法に関するものである。

**【背景技術】****【0002】**

近年の技術の発展に伴い、半導体装置の微細化が進んでおり、トランジスタの短チャネル効果が問題となっている。特許平5-167033号公報には、基板に掘った溝の側壁をチャネル領域とする半導体装置において、溝の底面から基板表面領域にある拡散層までの距離を、チャネル方向の平面寸法よりも長くすることで、平面的には微細な寸法でも、短チャネル効果およびパンチスルーの発生を抑える技術が開示されている。

**【特許文献1】特開平5-167033号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

溝ゲートを有する半導体装置の製造プロセスにおいて、溝ゲート用の溝をエッティングにより半導体基板に形成する際に、溝の底の半導体基板とSTI (Shallow Trench Isolation)との境界付近に、除去すべき基板材料の取り残りが生じる。そのため、ゲート長が局所的に短くなってしまう問題が生じていた。溝形成工程におけ

るエッティング条件改善により、取り残りが生じないようにする方法では、マスクやS T Iとの選択比、溝形状等の制限から、このような問題を解決することは困難であった。

【0004】

本発明の目的は、素子特性の優れた半導体装置を簡便な方法で提供することにある。

【課題を解決するための手段】

【0005】

本発明の一態様によれば、

第1の溝と、第1の溝内に埋め込まれた素子分離膜と、この素子分離膜に囲まれた活性領域を有する半導体基板を用意する工程と、

前記半導体基板上にマスク形成用膜を形成する工程と、

前記マスク形成用膜上に、前記活性領域を横切る開口を有する第1のマスクを形成する工程と、

第1のマスクを用いて異方性エッティングを行って、前記開口に対応する開口を有する前記マスク形成用膜からなる第2のマスクと、前記活性領域内に、対向する素子分離膜露出面を有し且つ第1の溝より浅い第2の溝を形成する工程と、

第2の溝内の半導体基板表面と素子分離膜露出面との境界を含む領域に酸素イオンが照射されるように、第2の溝内に、第2のマスクを用いて、酸素イオンを斜めに注入する工程と、

第2の溝内の酸素イオンが注入された領域を酸化して酸化領域を形成する工程と、

前記酸化領域を除去する工程を有する半導体装置の製造方法が提供される。

【0006】

本発明の他の態様によれば、

第2の溝内を含む半導体基板表面の酸化を行って、第2の溝内の酸素イオンが注入された領域を酸化して酸化領域を形成するとともに、この酸化領域を含む酸化膜を形成する工程と、

前記酸化膜を除去するとともに、前記酸化領域を除去する工程を有する上記の半導体装置の製造方法が提供される。

【0007】

本発明の他の態様によれば、

第2の絶縁膜を除去する工程と、

第2の溝内を含む半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜が形成された第2の溝内を埋め込むように導電膜を形成し、この導電膜をパターニングしてゲート電極を形成する工程と、

前記ゲート電極の両側の当該活性領域に不純物を導入してソース／ドレイン領域を形成する工程をさらに有する上記の半導体装置の製造方法が提供される。

【発明の効果】

【0008】

本発明によれば、素子特性の優れた半導体装置を簡便な方法で提供することができる。

【発明を実施するための最良の形態】

【0009】

溝ゲートトランジスタをセルトランジスタとするD R A M ( D y n a m i c R a n d o m A c c e s s M e m o r y ) の製造を例に挙げて、本発明の製造方法の一例について説明する。

【0010】

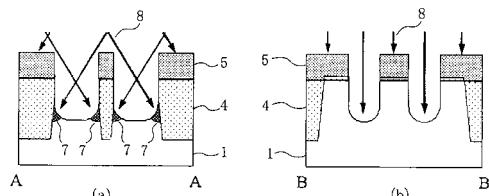

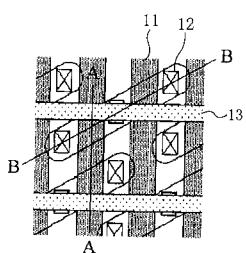

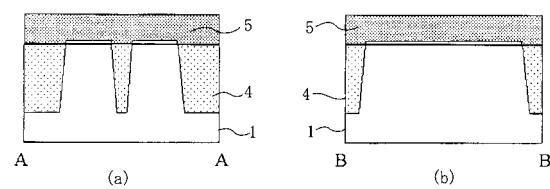

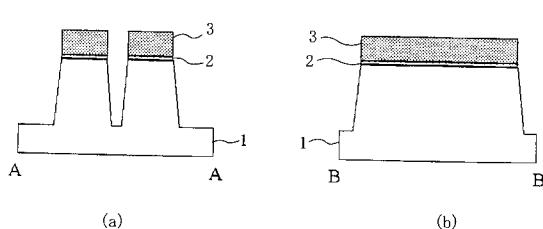

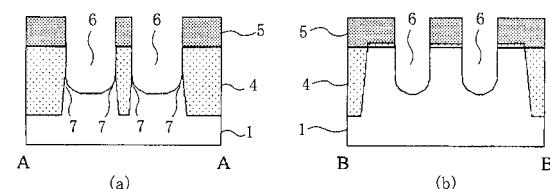

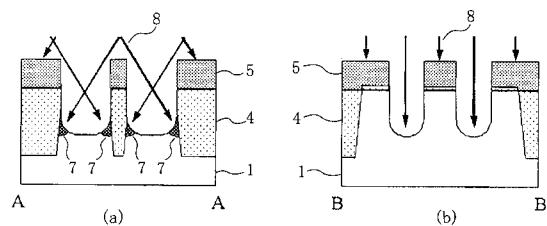

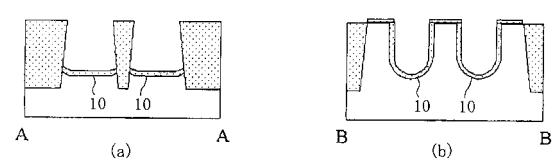

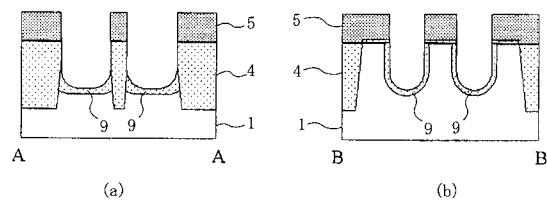

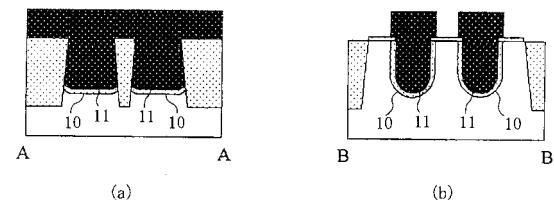

図1に、ピット線形成後のD R A Mの平面図を示し、図2から図8は、それぞれの工程における図1のA-A線、B-B線に沿った断面図を示す。

【0011】

始めに、単結晶シリコン半導体基板1を用意する。

【0012】

次に、半導体基板1を熱酸化し、表面に9nm程度の酸化シリコン膜2を形成する。次

いで、酸化シリコン膜2の上に、CVD (Chemical Vapor Deposition) 法を用いて120nm程度の窒化シリコン膜3を堆積する。

【0013】

次に、リソグラフィー技術によりレジストパターン形成し、これをマスクに用いて、窒化シリコン膜3、酸化シリコン膜2及び半導体基板1を順次ドライエッチングすることにより、図2に示すように、半導体基板1に素子分離用の溝を形成する。

【0014】

次に、半導体基板上に、この溝を埋め込むようにCVD法等を用いて酸化シリコン膜を堆積する。次いで、この酸化シリコン膜をCMP (Chemical Mechanical Polishing) 法を用いて研磨し、素子分離用の溝の外に形成された酸化シリコン膜を除去することにより、溝内に埋め込まれた酸化シリコン膜からなる素子分離膜4を形成する。フッ酸を用いて素子分離膜4の厚みを調整した後、熱リン酸を用いて窒化シリコン膜3を除去する。

10

【0015】

次に、図3に示すように、CVD法で120nm程度の窒化シリコン膜5を堆積する。

【0016】

次に、リソグラフィー技術によりレジストパターンを形成し、これをマスクに用いて、窒化シリコン膜5、酸化シリコン膜2及び半導体基板1を順次ドライエッチングすることにより、図4に示すように半導体基板に溝ゲート用の溝6を形成する。この溝ゲート用の溝6は、素子分離用の溝より浅く形成される。この溝6は、素子分離膜4で囲まれた活性領域内に、この活性領域の延在方向(長手方向)である第1方向(図1のB-B線方向)に交差する第2の方向(図1のA-A線方向)に沿って、当該活性領域を横切るように形成される。したがって、この溝6内の側面は、第2の方向での対向面がいずれも素子分離膜の露出面となり(図4(a))、第1方向での対向面がいずれも半導体基板表面となる(図4(b))。溝6の底面は半導体基板表面からなる(図4(a)、(b))。

20

【0017】

このとき、溝6の底の半導体基板表面と溝内側面の素子分離膜の露出面との境界付近にシリコンの取り残り(以下「シリコンバリ」)7ができる。

【0018】

次に、図5に示すように、上方から斜めに酸素イオン注入8を行う。本実施例では、図1のB-B線に垂直な面内で傾けて、斜めイオン注入を行う。この場合、図1の平面に対応する投射平面において、酸素イオンは、イオン照射領域(活性領域と素子分離領域との境界線)に対して垂直に照射される。例えば、ゲート方向の溝幅が80nm、窒化膜上面から溝底までの高さが100nm(溝6を形成するためのシリコンエッチング後の窒化シリコン膜5の残膜厚が20nm、シリコン基板上面から溝底までの高さが80nm)、シリコンバリの底部の幅が20nmとすると、酸素イオン注入の条件は、基板垂直方向を0°とした場合、注入角度は35~40°、注入エネルギーは5keV、注入量は1E15~1E16atom/cm<sup>2</sup>に設定することができる。

30

【0019】

酸素イオンの注入角度は、ゲート方向の溝幅をW、窒化膜から溝底までの高さをHとすると、 $\theta = \tan^{-1}(W/H)$ を目安に設定することができる。溝の形状、シリコンバリの形状、窒化シリコン膜5の膜厚に応じて、注入角度、注入エネルギー、注入量を適宜設定することができる。

40

【0020】

酸素イオンの注入において、溝の形成時のマスクとして利用された窒化シリコン膜5は斜めに注入される酸素イオンを遮蔽するマスクとして機能し、シリコンバリ7と溝内側面の素子分離膜露出面に酸素イオンが照射され、その他の場所(本例では溝底面のB-B線に沿った中央付近と溝の外部)には酸素8は照射されない。

【0021】

次に、図6に示すように、溝6の形成時の基板損傷や汚染除去のための犠牲酸化膜(酸

50

化シリコン膜) 9を、熱酸化により、溝内を含む基板表面に形成する。シリコンバリ7に酸素注入が行われない場合には、シリコン基板表面がほぼ等方的に酸化されるが、本実施例ではシリコンバリ7に酸素イオンが注入されているため、シリコンバリ7の酸化が速くなり、シリコンバリの全体を酸化することができる。

【0022】

次に、熱磷酸を用いて窒化シリコン膜5を除去し、続いてフッ酸を用いて犠牲酸化膜9を除去する。犠牲酸化膜9の除去とともに、酸化されたバリ7を除去することができる。

【0023】

次に、図7に示すように、熱酸化を行って、溝6内のシリコン基板表面に6nm程度の酸化シリコン膜(ゲート絶縁膜)10を形成する。

10

【0024】

次に、溝6内を埋め込むように、CVD法で不純物を含んだ多結晶シリコンをゲート絶縁膜10上に堆積する。次いで、リソグラフィー技術によりレジストパターンを形成し、これをマスクに用いてドライエッチングを行い、図8に示すようにゲート電極11を形成する。

【0025】

半導体基板のウェルや、トランジスタのチャネル、ソース/ドレイン等の形成のためのドーパント注入工程におけるドーパント種や、エネルギー、ドーズ量等の注入条件については、適宜、設定することができる。また、通常のプロセスに従って、層間絶縁膜、コンタクトプラグ12、容量、ビット線13等を形成してDRAMを完成することができる。

20

【0026】

本実施例の図4に示されるように、溝ゲート用の溝形成のためのエッチング後に、溝6の底においてシリコンと素子分離膜の境界付近にシリコンバリ7が残る。本発明によれば、図5に示す例のように、窒化シリコン膜5をマスクとして斜め方向に酸素イオン注入を行うことで、シリコンバリ部分のみに酸素イオンを注入できる。そして、図6に示すように、酸素イオンが注入されたバリ部分は犠牲酸化膜形成の際に酸化され、この酸化されたバリ部分は、犠牲酸化膜とともに除去することができる。なお、酸素イオンが注入されたバリ部分は、アニール処理によっても酸化することができ、酸化された領域はフッ酸等を用いたウェットエッチングにより容易に除去することができる。

【0027】

このようなプロセスにおいては、溝ゲート用の溝を形成する際に使用したマスク(窒化シリコン膜5)を、酸素イオン注入の際のマスクに利用することで、溝内に選択的に酸素イオン注入することができる。また、このマスクを利用しながら、酸素イオン注入を斜めに行なうことで、溝内のシリコンバリ部分に選択的に酸素イオンを注入できる。さらに、この酸素イオン注入後に、通常行われている酸化あるいはアニール工程で溝内のシリコンバリを選択的に酸化することができ、そして、この酸化されたバリは、通常行われている犠牲酸化膜除去工程で同時に除去できる。本発明による実施例は簡便な方法で良好な溝ゲート構造を形成することができ、結果、素子特性に優れたDRAMを製造することができる。

30

【0028】

上記実施例においては、DRAMのメモリセルトランジスタに溝ゲートトランジスタを適用した半導体装置の製造例を示したが、本発明は、メモリ、ロジック等を問わず、シリコンを材料とした溝ゲートトランジスタを有する半導体装置の製造方法に適用することができる。

40

【図面の簡単な説明】

【0029】

【図1】本発明により製造される半導体装置の一例の平面図である。

【図2】本発明の製造方法の一例を説明するための一工程を示す断面図である。

【図3】図2の工程に続く工程を示す断面図である。

【図4】図3の工程に続く工程を示す断面図である。

50

【図5】図4の工程に続く工程を示す断面図である。

【図6】図5の工程に続く工程を示す断面図である。

【図7】図6の工程に続く工程を示す断面図である。

【図8】図7の工程に続く工程を示す断面図である。

【符号の説明】

【0030】

- 1 半導体基板

- 2 酸化シリコン膜

- 3 窒化シリコン膜

- 4 素子分離膜

- 5 窒化シリコン膜

- 6 溝

- 7 取り残り部(バリ)

- 8 酸素イオン注入

- 9 犠牲酸化膜(酸化シリコン膜)

- 10 ゲート絶縁膜(酸化シリコン膜)

- 11 ゲート電極

- 12 コンタクトプラグ

- 13 ビット線

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

---

フロントページの続き

F ターム(参考) 5F083 AD04 LA12 LA16 LA21 NA01 PR05 PR12 PR37

5F140 AC32 BA01 BE01 BE03 BE07 BF01 BF04 BF43 BG28 BG38

BJ27 BK13 CB04 CE07