## (12) 特許協力条約に基づいて公開された国際出願

(19) 世界知的所有権機関

国際事務局

(43) 国際公開日

2012年7月19日 (19.07.2012)

W I P O | P C T

(10) 国際公開番号

W O 2012/096365 A 1

(51) 国際特許分類 :

G06K 19/077 (2006.01) H01Q 1/50 (2006.01)

G06K 19/07 (2006.01)

(72) 発明者 ; および

発明者 / 出願人 (米国についてのみ) : 道海 雄也

(DOKAI Yuva) [JP/JP]; 〒6178555 京都市長岡三条市

東神足1丁目10番1号 株式会社村田製作所

内 Kyoto (JP). 白木 浩司 SHIROKI Koji [JP/JP];

〒6178555 京都府長岡市東神足1丁目10番

1号 株式会社村田製作所内 Kyoto (JP).

(21) 国際出願番号 : PCT/JP2012/050557

(22) 国際出願日 : 2012年1月13日 (13.01.2012)

(25) 国際出願の言語 : 日本語

(26) 国際公開の言語 : 日本語

(30) 優先権データ :

特願 2011-005419 2011年1月14日 (14.01.2011) JP

(71) 出願人 (米国を除く全ての指定国について) : 株式会社村田製作所 (MURATA MANUFACTURING CO., LTD.) [JP/JP]; 〒6178555 京都府長岡市東神足1丁目10番1号 Kyoto (JP).

(74) 代理人 : 特許拿務法人 プロフィック特許事務所 (PROFIC PC); 〒5410054 大阪府大阪市中央区南本町4丁目2番10号 本町永和ビル Osaka (JP).

(81) 指定国 (表示のない限り、全ての種類の国内保護が可能) : AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, YL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

[続葉有]

(54) Title: RFID CHIP PACKAGE AND RFID TAG

(54) 発明の名称 : R F I D チップパッケージ及び R F I D タグ

[図2]

AA RFID chip side

BB Antenna side

(57) Abstract: Provided is an RFID chip package comprising: an RFID chip which is provided with a booster circuit and processes an RF signal in the UHF band; and a power feed circuit (15A) connected with the RFID chip and including at least one inductance element (L1, L2). The reactive component of input and output impedances at input and output terminals (21a, 21b) of the power feed circuit (15A) for antenna connection is substantially 0 (zero) Ω.

(57) 要約 : 昇圧回路を備え、UHF帯のRF信号を処理するRFIDチップと、前記RFIDチップに接続され、少なくとも一つのインダクタンス素子 (L1), (L2) を含む給電回路 (15A) と、を備えたRFIDチップパッケージ。給電回路 (15A) のアンテナ接続用入出力端子 (21a), (21b) における入出力インピーダンスのリアクタンス成分がほぼ0Ωである。

- (84) 指定国(表示のない限り、全ての種類の広域保護が可肯<sup>△</sup>: ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), ユーラシア (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), ヨーロッパ (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK,

SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

添付公開書類:

- 國際調査報告(条約第21条(3))

## 明 細 書

発明の名称：RFIDチップパッケージ及びRFIDタグ

### 技術分野

[0001] 本発明は、RFIDチップパッケージ、特にRFID (Radio Frequency Identification) システムにおいて、RFIDチップとそのアンテナとの間に介在されるRFIDチップパッケージ及びRFIDタグに関する。

### 背景技術

[0002] 近年、物品の情報管理システムとして、誘導磁界を発生するリーダライタと、物品に付されたRFIDタグとを電磁界を利用した非接触方式で通信し、所定の情報を伝達するRFIDシステムが実用化されている。ここで、RFIDタグは、所定の情報を記憶し、所定のRF信号を処理するRFIDチップと、RF信号の送受信を行うアンテナとで構成されている。

[0003] ところで、RFIDシステムにおいては、RF信号が微弱であるため、例えば、特許文献1，2に記載されているように、RFIDチップには多段チャージポンプなどの昇圧回路が備えられており、RFIDチップの入出力インピーダンスは極めて高くなっている。それゆえ、アンテナにおいても、その入出力インピーダンスをRFIDチップの入出力インピーダンスに整合させる必要があり、アンテナの設計が難しく、特に小型化や広帯域化が困難であるという問題点を有していた。

### 先行技術文献

#### 特許文献

[0004] 特許文献1：特開2005\_202943号公報

特許文献2：特開2009\_130896号公報

### 発明の概要

#### 発明が解決しようとする課題

[0005] そこで、本発明の目的は、高いインピーダンス特性を有するRFIDチップを低いインピーダンス特性のアンテナに好適に整合させることができ、ア

ンテナ設計の困難性を解消できる、RFIDチップを含むRFIDチップパッケージ及びRFIDタグを提供することにある。

### 課題を解決するための手段

- [0006] 本発明の第1の形態であるRFIDチップパッケージは、昇圧回路を備え、UHF帯のRF信号を処理するRFIDチップと、前記RFIDチップに接続され、少なくとも一つのインダクタンス素子を含む給電回路と、

を備え、

前記給電回路のアンテナ接続用入出力端子における入出力インピーダンスのリアクタンス成分がほぼ0Ωであること、

を備えたことを特徴とする。

- [0007] 本発明の第2の形態であるRFIDタグは、接続部を有するアンテナ素子と、該接続部に接続されたRFIDチップパッケージとを有するRFIDタグであって、前記RFIDチップパッケージは、昇圧回路を備え、UH「帯の」「信号を処理するRFIDチップと、該RFIDチップに接続され、少なくとも一つのインダクタンス素子を含む給電回路と、を備え、

前記給電回路のアンテナ接続用入出力端子における入出力インピーダンスのリアクタンス成分がほぼ0Ωであること、

を特徴とする。

- [0008] 前記RFIDチップパッケージにおいて、RFIDチップは昇圧回路を備えており、入出力インピーダンスのリアクタンス成分が-200Ω程度になっている。給電回路はこのRFIDチップに接続され、かつ、アンテナが接続されるアンテナ端子の入出力インピーダンスのリアクタンス成分がほぼ0Ωとされている。それゆえ、アンテナをダイポール型やパッチ型など一般的な形で整合をとることが容易になり、アンテナの設計に大きな自由度が生じて広帯域化が容易になる。また、RFIDチップを測定する際の測定系のインピーダンスは一般的に50Ωに設計されているため、RFIDチップの測

定も容易になる。

## 発明の効果

[0009] 本発明によれば、高いインピーダンス特性を有するRFIDチップを低いインピーダンス特性のアンテナに好適に整合させることができ、アンテナ設計の困難性を解消でき、RFIDチップパッケージが小型化する。

## 図面の簡単な説明

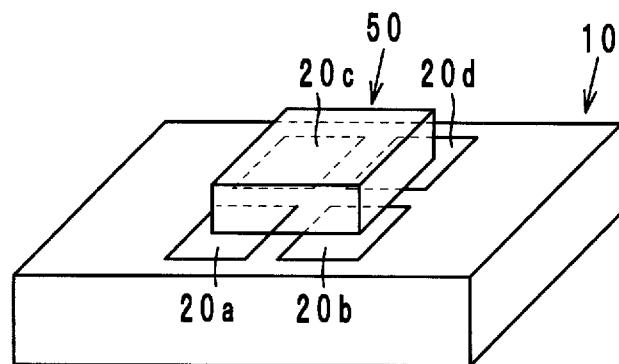

[0010] [図1] 実施例であるRFIDチップパッケージを示す斜視図である。

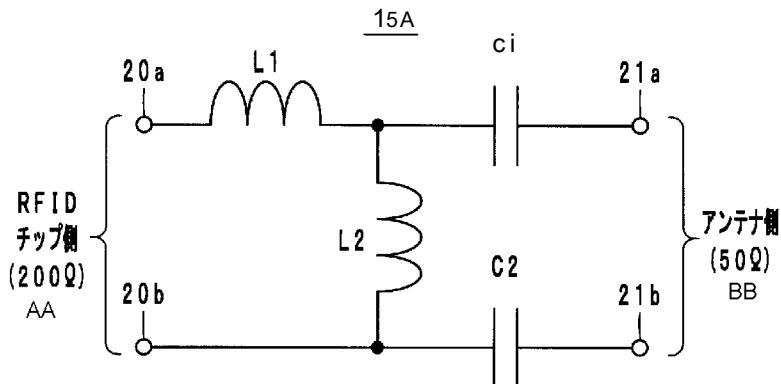

[図2] 第1例である給電回路を示す等価回路図である。

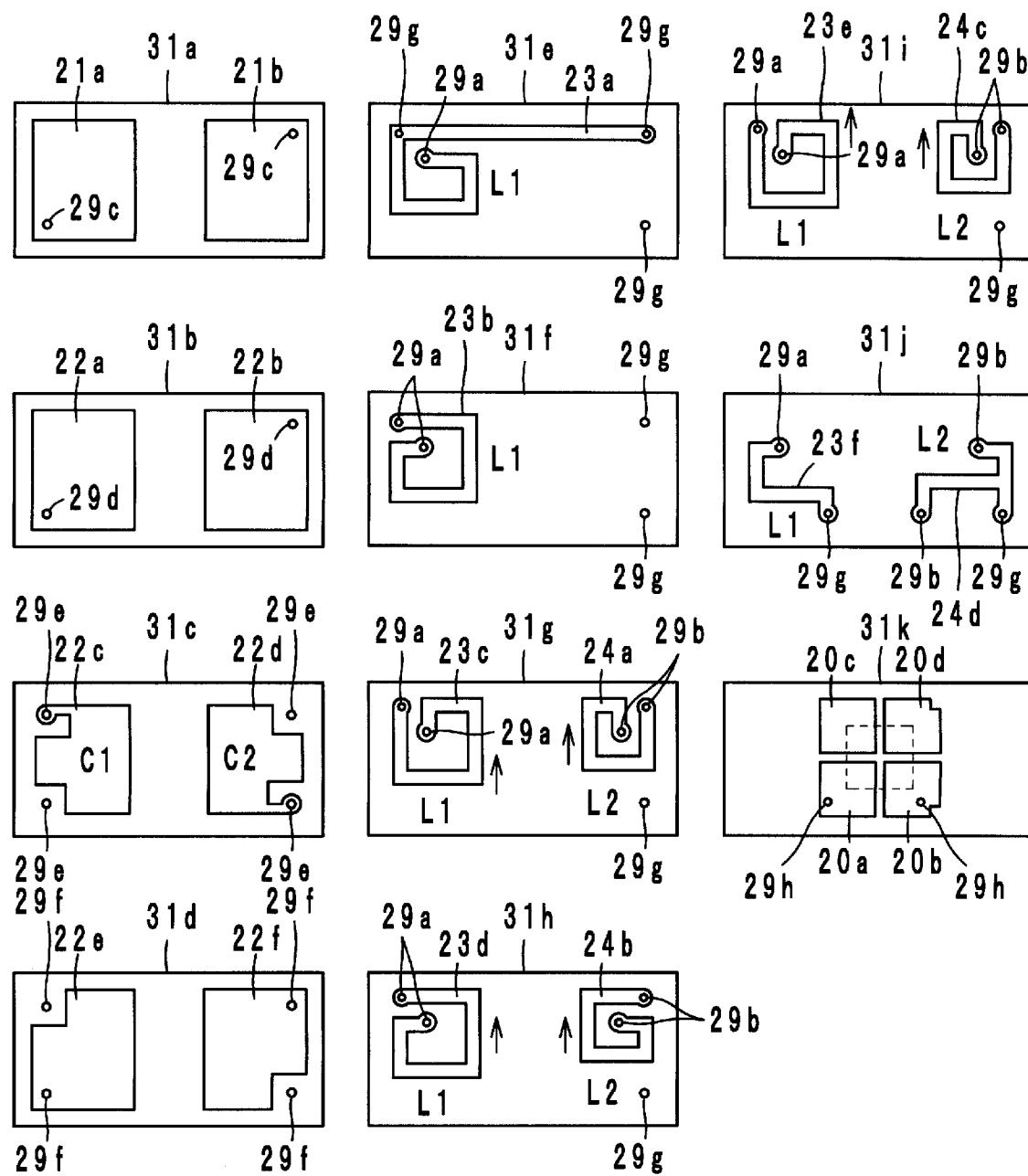

[図3] 第1例である給電回路を構成する積層体を各基材層ごとに分解して示す平面図である。

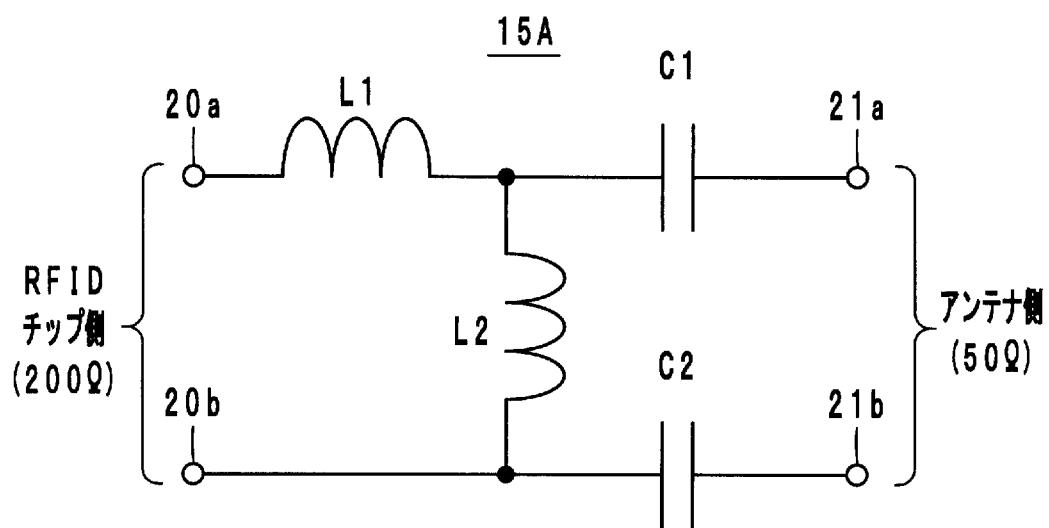

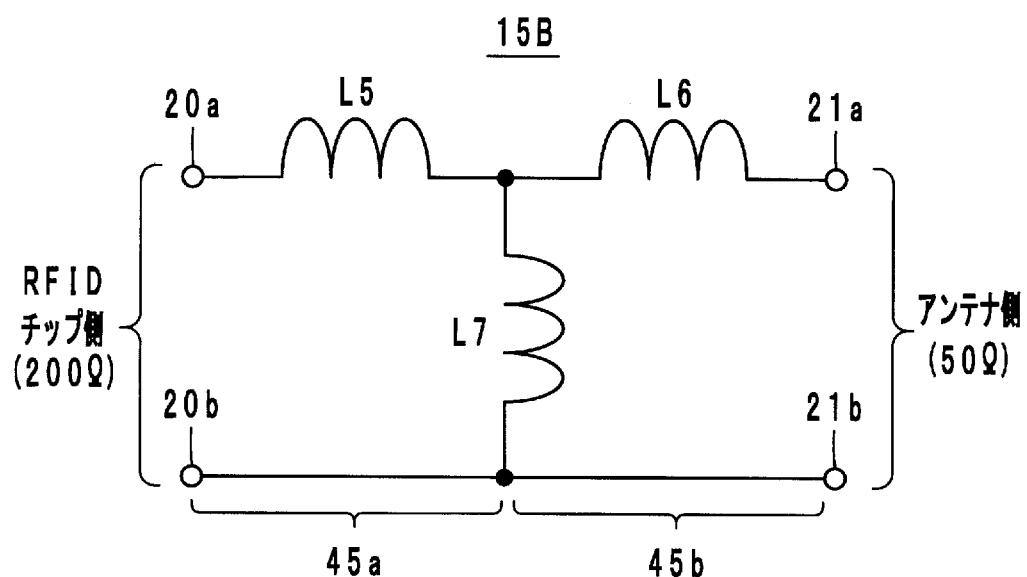

[図4] 第2例である給電回路を示す等価回路図である。

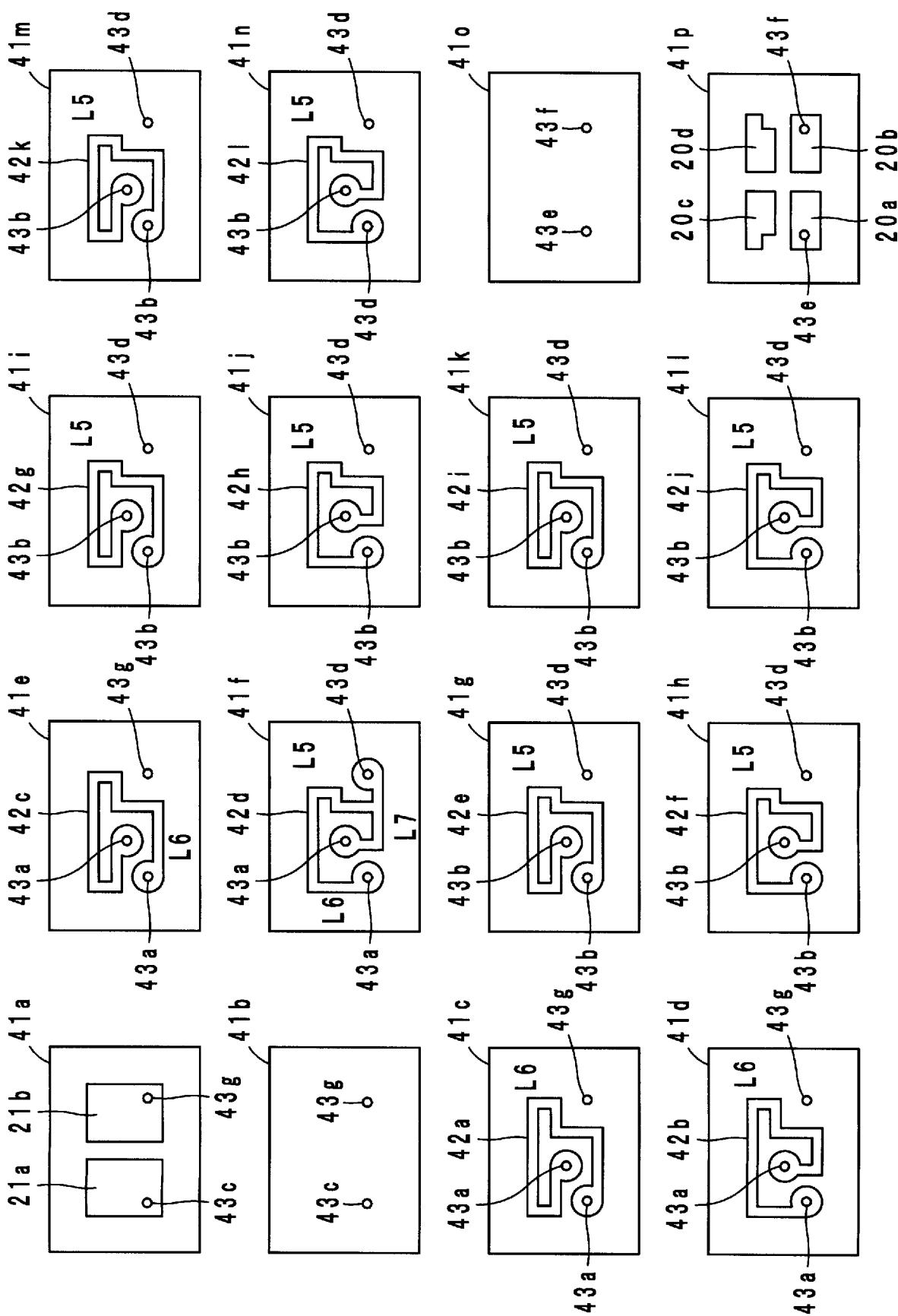

[図5] 第2例である給電回路を構成する積層体を各基材層ごとに分解して示す平面図である。

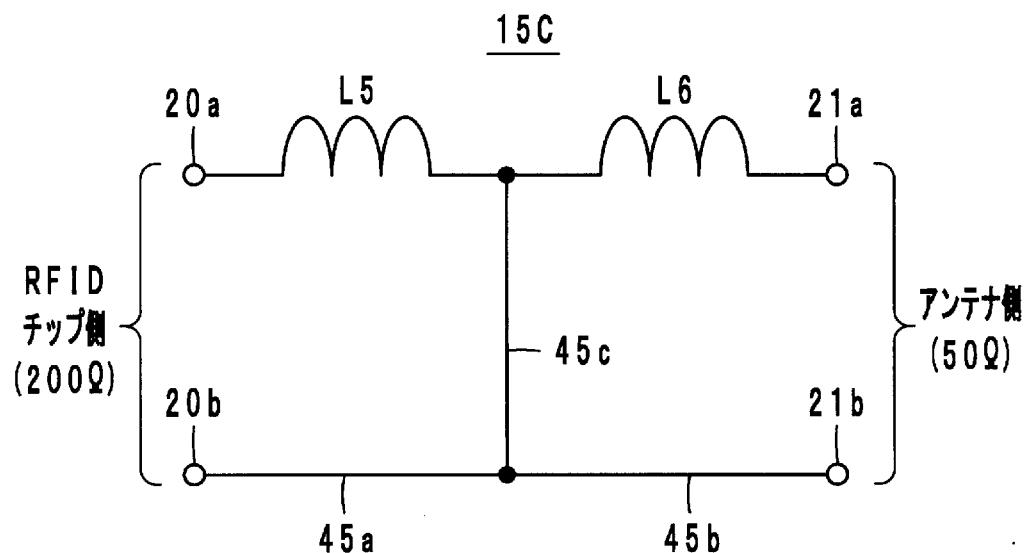

[図6] 第3例である給電回路を示す等価回路図である。

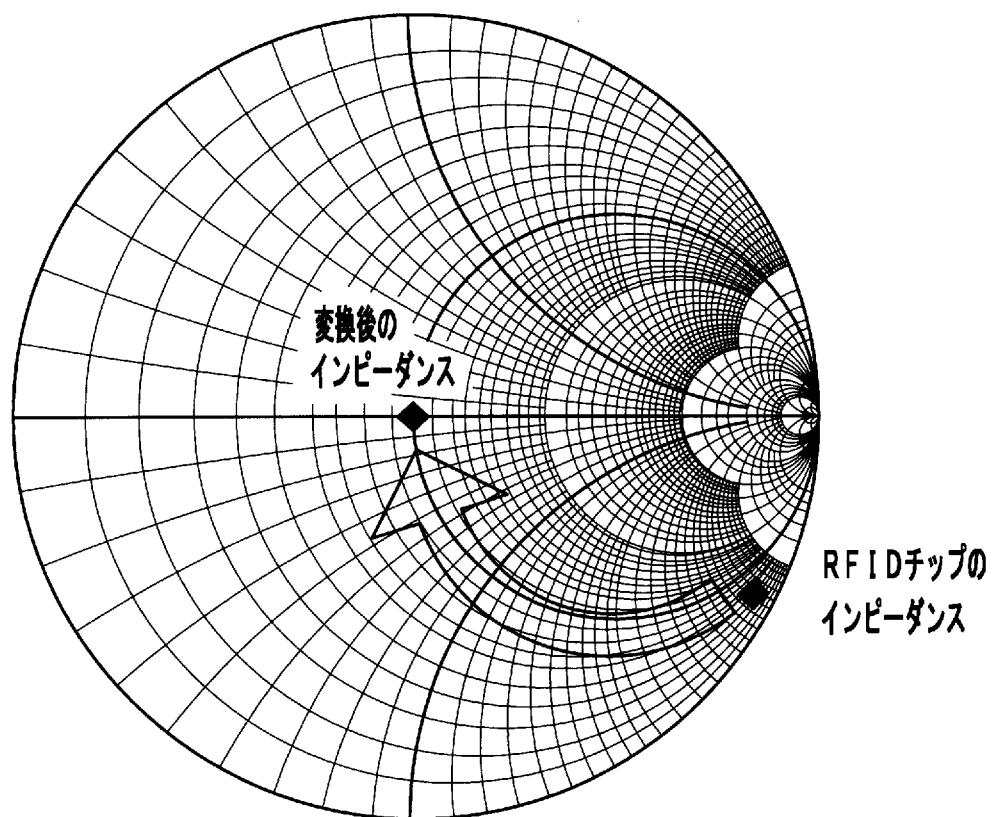

[図7] 第1例である給電回路のインピーダンス整合特性を示すスミスチャート図である。

[図8] RFIDタグの第1実施例を示し、(A)は分解斜視図、(B)は断面図である。

[図9] RFIDタグの第2実施例を示す分解斜視図である。

## 発明を実施するための形態

[0011] 以下、本発明に係るRFIDチップパッケージ及びRFIDタグの実施例について添付図面を参照して説明する。なお、各図において、共通する部品、部分は同じ符号を付し、重複する説明は省略する。

[0012] (RFIDチップパッケージ、図1参照)

—実施例であるRFIDチップパッケージは、図1に示すように、給電回路を内蔵した積層体からなる給電回路基板10上にRFIDチップ50を搭載したものである。なお、RFIDチップ50は給電回路基板10に内蔵あるいは基板10に形成した凹所(図示せず)に収容されていてもよい。

[0013] R F I D チップ 50 は、例えば U H F 帯の R F 信号を処理するもので、クロック回路、ロジック回路、メモリ回路などを含み、必要な情報がメモリされている。また、チャージポンプなどの昇圧回路をも含み、入出力インピーダンスは実部が  $20\Omega$ 、虚部が  $-20\text{O}\Omega$  程度である。R F I D チップ 50 は、その裏面に一对の入出力用端子電極及び一对の実装用端子電極が設かれている。入出力用端子電極は給電回路基板 10 の上面に設けた給電端子電極 20a, 20b に、実装用端子電極は給電回路基板 10 の上面に設けた実装用端子電極 20c, 20d に、それぞれ、金属バンプなどを介して電気的に接続される。なお、金属バンプの材料としては、Au、はんだなどを用いることができる。

[0014] 給電回路は、少なくとも一つのインダクタンス素子を含み、好ましくはキャパシタンス素子をも含み、積層体からなる給電回路基板に内蔵されている。そして、アンテナ端子電極の入出力インピーダンスのリアクタンス成分がほぼ  $0\Omega$  とされている。以下に、給電回路について第1例、第2例、第3例を記述する。

[0015] (給電回路の第1例、図2及び図3参照)

図2に示すように、第1例である給電回路 15A は、R F I D チップ 50 に接続される二つの給電端子電極 20a, 20b と、図示しないアンテナに接続されるアンテナ端子電極 21a, 21b とを備え、インダクタンス素子 L1, L2 とキャパシタンス素子 C1, C2 とを有している。インダクタンス素子 L1 とキャパシタンス素子 C1 は端子電極 20a, 21a 間に直列に接続されている。インダクタンス素子 L2 はインダクタンス素子 L1 とキャパシタンス素子 C1との接続点と端子電極 20b とキャパシタンス素子 C2 との接続点に接続されている。キャパシタンス素子 C2 は端子電極 20b, 21b 間に直列に接続されている。

[0016] インダクタンス素子 L1, L2 は互いに電磁界結合しており、インダクタンス素子 L1 とキャパシタンス素子 C1 とは、及び、インダクタンス素子 L2 とキャパシタンス素子 C2 とは、それぞれ、電磁界を介して結合しており

、それぞれの素子によって共振回路を形成している。また、図3を参照して説明するように、インダクタンス素子L1,L2を形成するそれぞれのコイルパターンも線間容量を持っている。

[0017] 給電回路15Aは、RFIDチップ50から発信されて端子電極20a,20bから入力された所定の周波数を有する高周波信号を端子電極21a,21bからアンテナに伝達し、かつ、アンテナで受信した高周波信号を前記とは逆方向にRFIDチップ50に供給する。給電回路15Aが所定の共振周波数を有し、端子電極21a,21bの入出力インピーダンスのリアクタンス成分がほぼ0Ωとされている。それゆえ、RFIDチップ50からの実部が20Ω、虚部が-200Ωの入力インピーダンスがほぼ実部が50Ω、虚部が0Ωの出力となるので、アンテナに対するインピーダンスが整合されることになる。また、RFIDチップ50を測定する際の測定系のインピーダンスは一般的に50Ωに設計されているため、RFIDチップ50の測定も容易になる。

[0018] 次に、給電回路15Aを内蔵した積層体(給電回路基板10)の構造について図3を参照して説明する。積層体は各基材層31a~31kからなり、基材層31a~31jは誘電体又は磁性体からなるセラミックシートであり、基材層31kは転写用シートである。図3において、各電極や各導体は各基材層31a~31k上に形成され、基材層31aを基材層31bの上に重ね、さらに基材層31c,31d…上に重ねるという順序で積層する。最下層に重ねた基材層(転写シート)31kは積層後に剥離することにより、端子電極20a~20dを積層体の下面に露出させる。

[0019] 詳しくは、基材層31a上にはアンテナに接続される端子電極21a,21b及びビアホール導体29cが形成され、基材層31b,31c,31d上にはそれぞれ容量電極22a~22f及びビアホール導体29d,29e,29fが形成されている。基材層31e~31j上にはループ状導体23a~23f,24a~24d及びビアホール導体29a,29b,29gが形成されている。基材層31k上には端子電極20a~20d及びビアホ-

ル導体 29 h が形成されている。

[0020] 前記各基材層 31 a ~ 31 k を積層することにより、図 2 に示した等価回路が形成される。即ち、容量電極 22 a, 22 c, 22 e にてキャパシタンス素子 C1 が形成され、容量電極 22 b, 22 d, 22 f にてキャパシタンス素子 C2 が形成される。また、ループ状導体 23 a ~ 23 f がビアホール導体 29 a を介して形成されるコイルパターンにてインダクタンス素子 L1 が形成され、ループ状導体 24 a ~ 24 d がビアホール導体 29 b を介して形成されるコイルパターンにてインダクタンス素子 L2 が形成される。

[0021] 以上のごとく、給電回路基板 10 に内蔵された給電回路 15 A のインピーダンス整合特性を、図 7 のスミスチャートに示す。RFIDチップ 50 の入出力インピーダンスは実部が  $20\Omega$ 、虚部が  $-20\Omega$  であり、アンテナ側（変換後）のインピーダンスは実部が  $50\Omega$ 、虚部が  $0\Omega$  である。

[0022] ところで、インダクタンス素子 L1, L2 は、それぞれを構成するコイルパターンがそれぞれの巻回軸が平行になるように積層体内に隣接して配置されており、それぞれのコイルパターンはある瞬間における磁束の向きが同方向になるように巻回されている（図 3 の矢印参照）。但し、逆方向になるように巻回されていてもよい。また、各コイルパターンの開口は、通過する磁束がキャパシタンス素子 C1, C2 に導かれるように容量電極 22 e, 22 f で覆われている。即ち、インダクタンス素子 L1 とキャパシタンス素子 C1、及び、インダクタンス素子 L2 とキャパシタンス素子 C2 とは、それぞれ、電磁界を介して結合している。また、アンテナ端子電極 21 a, 21 b にキャパシタンス素子 C1, C2 を接続することで ESD に強い RFID チップパッケージを実現できる。

[0023] （給電回路の第 2 例、図 4 及び図 5 参照）

図 4 に示すように、第 2 例である給電回路 15 B は、RFIDチップ 50 に接続される二つの給電端子電極 20 a, 20 b と、図示しないアンテナに接続されるアンテナ端子電極 21 a, 21 b とを備え、インダクタンス素子 L5, L6, L7 を有している。インダクタンス素子 L5, L6 は端子電極

間に直列に接続されている。インダクタンス素子 L 7 はインダクタンス素子 L 5 , L 6 の接続点と端子電極 20 b , 21 bとの間に接続されている。インダクタンス素子 L 5 , L 6 , L 7 はそれぞれ互いに電磁界結合している。また、図 5 を参照して説明するように、インダクタンス素子 L 5 , L 6 , L 7 を形成するそれぞれのコイルパターンも線間容量を持っており、共振回路を形成している。

[0024] 給電回路 15 B の機能は第 1 例である給電回路 15 A と基本的には同様であり、RFID チップ 50 から発信されて端子電極 20 a , 20 b から入力された所定の周波数を有する高周波信号を端子電極 21 a , 21 b からアンテナに伝達し、かつ、アンテナで受信した高周波信号を前記とは逆方向に RFID チップ 50 に供給する。給電回路 15 B が所定の共振周波数を有し、端子電極 21 a , 21 b の入出カインピーダンスのリアクタンス成分がほぼ 0 Ω とされている。それゆえ、RFID チップ 50 からの実部が 20 Ω 、虚部が -200 Ω の入カインピーダンスがほぼ実部が 50 Ω 、虚部が 0 Ω の出力となるので、アンテナに対するインピーダンスが整合されることになる。

[0025] 次に、給電回路 15 B を内蔵した積層体（給電回路基板 10）の構造について図 5 を参照して説明する。基材層 41 a ~ 41 o は誘電体又は磁性体からなるセラミツクシートであり、基材層 41 p は転写用シートである。また、各基材層 41 a ~ 41 p の積層順序も前記第 1 例と同様であり、最下層に重ねた基材層（転写シート）41 p は積層後に剥離することにより、端子電極 20 a ~ 20 d を積層体の下面に露出させる。

[0026] 詳しくは、基材層 41 a 上にはアンテナに接続される端子電極 21 a , 21 b 及びビアホール導体 43 c , 43 g が形成され、基材層 41 b 上にはビアホール導体 43 c , 43 g が形成されている。基材層 41 c ~ 41 n 上にはそれぞれループ状導体 42 a ~ 42 l 及びビアホール導体 43 a , 43 b , 43 d , 43 g が形成され、基材層 41 o 上にはビアホール導体 43 e , 43 f が形成されている。基材層 41 p 上には端子電極 20 a ~ 20 d 及びビアホール導体 43 e , 43 f が形成されている。

[0027] 前記各基材層4 1 a～4 1 p を積層することにより、図4に示した等価回路が形成される。即ち、ループ状導体4 2 d の一部とループ状導体4 2 e～4 2 i がビアホール導体4 3 b を介して形成されるコイルパターンにてインダクタンス素子L 5 が形成される。ループ状導体4 2 a～4 2 c とループ状導体4 2 d の一部がビアホール導体4 3 a を介して形成されるコイルパターンにてインダクタンス素子L 6 が形成される。さらに、基材層4 1 f 上に形成されたループ状導体4 2 d の一部がインダクタンス素子L 7 を形成する。また、図4に示す線路4 5 a はビアホール導体4 3 d , 4 3 f によって形成され、線路4 5 b はビアホール導体4 3 g と基材層4 1 f のビアホール導体4 3 d によって形成される。

[0028] 以上のごとく給電回路基板10に内蔵された給電回路15Bのインピーダンス整合特性は図7のスミスチャートと基本的には同様である。

[0029] (給電回路の第3例、図6参照)

図6に示すように、第3例である給電回路15Cは、前記第2例である給電回路15Bからインダクタンス素子L 7 を省略し、インダクタンス素子L 5 , L 6 の接続点と端子電極20b , 21b を結ぶ線路4 5 a , 4 5 b とを線路4 5 c にて接続したものである。インダクタンス素子L 5 , L 6 は互いに電磁界結合しており、それぞれのコイルパターンが線間容量を持って共振回路を形成している。この給電回路15Cの作用、機能は前記第2例である給電回路15Bと基本的に同様である。

[0030] ところで、前記インダクタンス素子L 5 , L 6 は、ともにRFIDチップとアンテナとのインピーダンスを整合させる機能を有している。特に、インダクタンス素子L 5 は、RFIDチップ側に直列に挿入されたインダクタンスである。このインダクタンスは、主に、インピーダンスチャート上の虚数軸方向にインピーダンスを動かすという機能を有する。一方、インダクタンス素子L 6 は、アンテナ側に直列に挿入されたインダクタンスであり、アンテナ側の二つの端子21a , 21b を跨るように配置されている。このインダクタンスは、主に、アドミッタンスチャート上の虚数軸上にインピーダン

スを動かすという機能を有する。インダクタンス素子L5,L6に前記機能を持たせることにより、インピーダンスを効率よくマッチングさせることができる。

[0031] 特に、インダクタンス素子L5のインダクタンス値をインダクタンス素子L6のインダクタンス値よりも大きくすることにより、RFIDチップ側のインピーダンス（入出力インピーダンス）が例えば実部が20Ω程度、虚部が-200Ω程度となるような場合であっても、これを比較的簡単な構成で50Ωに近づけることができる。

[0032] また、インダクタンス素子L5,L6は互いに電磁界（主に磁界）を介して結合していることが好ましい。これにて、必要なインダクタンス値を小さなパターンで得ることができる。また、インダクタンス素子L5,L6のコイルパターンを各コイルパターンに生じる磁界が同相（各コイルパターンに生じる磁界の向きが同じ）となるように巻回、配置することにより、各コイルの磁界が強め合うことになり、各コイルのサイズが小さくても大きなインダクタンス値を得ることができ、RFIDチップと給電回路基板とによって（アンテナを接続しなくとも）数cm以下の近距離での通信が可能になる。

[0033]（RFIDタグの第1実施例、図8参照）

第1実施例であるRFIDタグ60Aについて図8を参考して説明する。このRFIDタグ60Aは、基材フィルム61上にダイポール型アンテナとして機能する第1放射素子65及び第2放射素子66を薄膜導体又は厚膜導体として設け、RFIDチップ50を搭載した給電回路基板15を第1放射素子65及び第2放射素子66に接続したものである。具体的には、第1及び第2放射素子65,66の接続部65a,66aに給電回路基板15の裏面に設けたアンテナ端子電極21a,21b（第3端子21a、第4端子21b）が導電性接合材67a,67bを介して接続されている。給電回路基板15の表面に設けた給電端子電極20a,20b（第1端子20a、第2端子20b）は、RFIDチップ50の入出力用端子電極に導電性接合材68a,68bを介して接続されている。

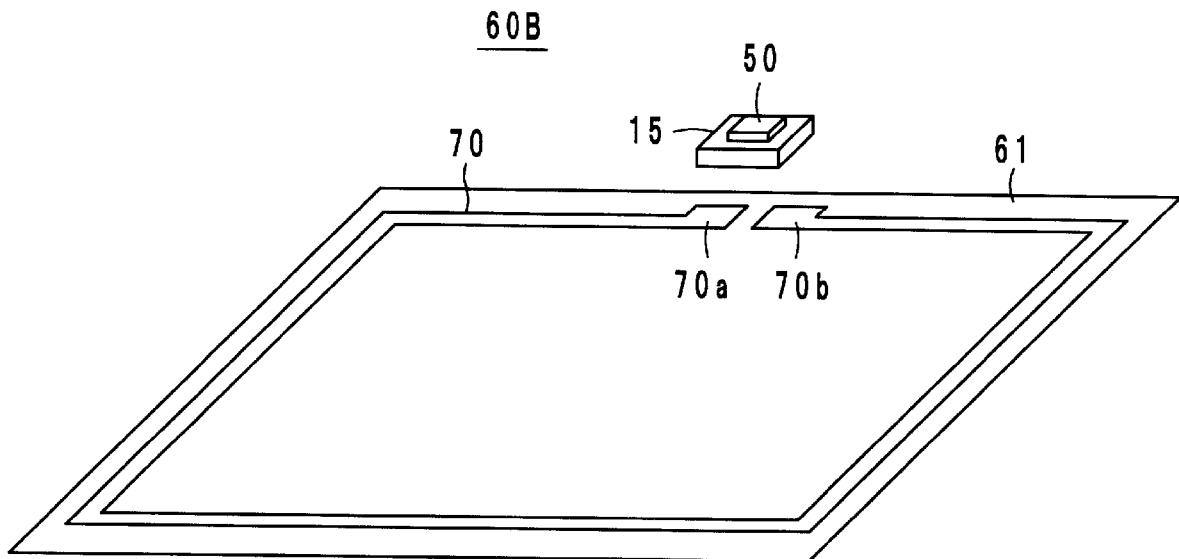

## [0034] (RFIDタグの第2実施例、図9参照)

第2実施例であるRFIDタグ60Bについて図9を参照して説明する。

このRFIDタグ60Bは、基材フィルム61上にループ型アンテナとして機能する放射素子70を薄膜導体又は厚膜導体として設け、RFIDチップ50を搭載した給電回路基板15を放射素子70の接続部70a, 70bに接続したものである。給電回路基板15とRFIDチップ50及び接続部70a, 70bとの接続関係は前記第1実施例であるRFIDタグ60Aと同様である。

## [0035] (他の実施例)

なお、本発明に係るRFIDチップパッケージ及びRFIDタグは前記実施例に限定するものではなく、その要旨の範囲内で種々に変更できることは勿論である。

## 産業上の利用可能性

[0036] 以上のように、本発明は、RFIDチップパッケージ及びRFIDタグに有用であり、特に、高いインピーダンス特性を有するRFIDチップを低いインピーダンス特性のアンテナに好適に結合できる点で優れている。

## 符号の説明

## [0037] 10…給電回路基板

15A, 15B, 15C…給電回路

31a～31k, 41a～41p…基材層

20a, 20b…給電端子電極

21a, 21b…アンテナ端子電極

23a～23f, 24a～24d…ループ状導体

42a～42l…ループ状導体

50…RFIDチップ

60A, 60B…RFIDタグ

65, 66, 70…放射素子

し1, し2, L5, L6, L7…インダクタンス素子

C1, C2 … キヤパシタンス素子

## 請求の範囲

- [請求項 1] 昇圧回路を備え、UHF帯のRF信号を処理するRFIDチップと、

前記RFIDチップに接続され、少なくとも一つのインダクタンス

素子を含む給電回路と、

を備え、

前記給電回路のアンテナ接続用入出力端子における入出カインピー

ダンスのリアクタンス成分がほぼ $0\Omega$ であること、

を特徴とするRFIDチップパッケージ。

- [請求項 2] 前記RFIDチップは第1入出力端子と第2入出力端子とからなる

平衡型の入出力端子を備え、

前記給電回路は、前記第1入出力端子に接続された第1端子と、前

記第2入出力端子に接続された第2端子と、アンテナ素子の第1接続

部に接続された第3端子と、前記アンテナ素子の第2接続部に接続さ

れた第4端子と、をそれぞれ有しております、

さらに、前記給電回路は、前記第1端子と前記第2端子との間に接

続された第1インダクタンス素子と、前記第3端子と前記第4端子と

の間に接続された第2インダクタンス素子と、を有していること、

を特徴とする請求項1に記載のRFIDチップパッケージ。

- [請求項 3] 前記第1インダクタンス素子のインダクタンス値は前記第2インダ

クタンス素子のインダクタンス値よりも大きいこと、を特徴とする請

求項2に記載のRFIDチップパッケージ。

- [請求項 4] 前記第1インダクタンス素子及び前記第2インダクタンス素子は互

いに電磁界を介して結合していること、を特徴とする請求項2又は請

求項3に記載のRFIDチップパッケージ。

- [請求項 5] 前記給電回路は前記インダクタンス素子を有する給電回路基板に配

置されており、

前記RFIDチップは前記給電回路基板に搭載又は内蔵されている

こと、

を特徴とする請求項 2 ないし請求項 4 のいずれかに記載の R F I D チップパッケージ。

[請求項 6] 前記給電回路基板は複数の基材層を積層してなる積層体として構成され、

前記インダクタンス素子は前記基材層に設けたループ状導体を巻回してコイルパターンとして構成したものであること、

を特徴とする請求項 5 に記載の R F I D チップパッケージ。

[請求項 7] 前記第 1 インダクタンス素子は第 1 のコイルパターン、前記インダクタンス素子は第 2 のコイルパターンにてそれぞれ構成され、

前記第 1 及び第 2 のコイルパターンはそれぞれの巻回軸がほぼ平行になるように前記積層体内に隣接して配置されていること、

を特徴とする請求項 6 に記載の R F I D チップパッケージ。

[請求項 8] 前記第 1 のコイルパターン及び前記第 2 のコイルパターンは、各コイルパターンに生じる磁界が同相となるように、それぞれ巻回、配置されていること、を特徴とする請求項 7 に記載の R F I D チップパッケージ。

[請求項 9] 前記給電回路は、さらにキャパシタンス素子を有しており、

前記キャパシタンス素子は前記基材層に互いに対向するように設けた容量電極にて構成されていること、

を特徴とする請求項 6 ないし請求項 8 のいずれかに記載の R F I D チップパッケージ。

[請求項 10] 接続部を有するアンテナ素子と、該接続部に接続された R F I D チップパッケージとを有する R F I D タグであって、

前記 R F I D チップパッケージは、昇圧回路を備え、U H 「帯の尺」 F 信号を処理する R F I D チップと、該 R F I D チップに接続され、少なくとも一つのインダクタンス素子を含む給電回路と、を備え、

前記給電回路のアンテナ接続用入出力端子における入出力インピー

ダンスの リアクタンス成分が ほぼ  $0 \Omega$  である こと、

を 特徴 と す る R F I D タグ。

[図1]

[図2]

[図3]

[図4]

[図5]

[図6]

[図7]

[図8]

[図9]

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2012/050557

## A. CLASSIFICATION OF SUBJECT MATTER

G06K1 9/0 77 {2006.01} i, G06K1 9/0 7 (2006.01) i, H01 Q1/50 (2006.01) i

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G06K1 9/077, G06K1 9/07, H01Q1/50

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

|         |         |        |            |           |        |         |        |           |           |

|---------|---------|--------|------------|-----------|--------|---------|--------|-----------|-----------|

| Jitsuyo | Shinan  | Koho   | 1922-1 996 | Jitsuyo   | Shinan | Toroku  | Koho   | 1996-2012 |           |

| Kokai   | Jitsuyo | Shinan | Koho       | 1971-2012 | Toroku | Jitsuyo | Shinan | Koho      | 1994-2012 |

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                  | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | WO 2010/119854 A1 (Murata Mfg. Co., Ltd.),<br>21 October 2010 (21.10.2010),<br>fig. 11, 12<br>(Family : none )                                                                                                                                                                                      | 1-10                  |

| A         | WO 2009/011144 A1 (Murata Mfg. Co., Ltd.),<br>22 January 2009 (22.01.2009),<br>fig. 9<br>& JP 2009-153166 A & JP 2009-44715 A<br>& JP 4301346 B & US 2009/0021352 A1<br>& US 2009/0021446 A1 & US 2011/0074584 A1<br>& EP 2056400 A1 & WO 2009/011154 A1<br>& KR 10-2009-0024663 A & CN 101542830 A | 1-10                  |

Further documents are listed in the continuation of Box C. See patent family annex.

\* Special categories of cited documents:

"A" document defining the general state of the art which is not considered to be of particular relevance

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"E" earlier application or patent but published on or after the international filing date

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"O" document referring to an oral disclosure, use, exhibition or other means

"&amp;" document member of the same patent family

"P" document published prior to the international filing date but later than the priority date claimed

Date of the actual completion of the international search

28 March, 2012 (28.03.12)Date of mailing of the international search report

10 April, 2012 (10.04.12)Name and mailing address of the ISA/

Japanese Patent Office

Authorized officer

Facsimile No.

Telephone No.

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2012/050557

C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                        | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | WO 2009/011423 A1 (Murata Mfg . Co . , Ltd . ) ,<br>22 January 2009 (22.01.2009) ,<br>fi . 7<br>& S 2010/0103058 A1 & EP 2166616 A1<br>& N 101682113 A    | 1~10                  |

| A         | WO 2008/001561 A1 (Murata Mfg . Co . , Ltd . ) ,<br>03 January 2008 (03.01.2008) ,<br>fi . 4 , 7<br>& P 4281850 B & US 2009/0080296 A1<br>& N 101467209 A | 1~10                  |

| P , A     | JP 2011-205384 A (Murata Mfg . Co . , Ltd . ) ,<br>13 October 2011 (13.10.2011) ,<br>fig . 3 to 6<br>(Family : none )                                     | 1~10                  |

## A. 発明の属する分野の分類(国際特許分類(IPC))

Int.Cl. G06K19/077 (2006. 01) i, G06K19/07 (2006. 01) i, H01Q1/50 (2006. 01) i

## B. — 調査を行った分野

## 調査を行った最小限資料(国際特許分類(IPC))

Int.Cl. G06K19/077, G06K19/07, H01Q1/50

## 最小限資料以外の資料で調査を行った分野に含まれるもの

|             |         |

|-------------|---------|

| 日本国実用新案公報   | 1922-19 |

| 日本国公開実用新案公報 | 1971-20 |

| 日本国実用新案登録公報 | 1996-20 |

| 日本国登録実用新案公報 | 1994-20 |

国際調査で使用した電子データベース(データベースの名称、調査に使用した用語)

年

## C. 関連すると認められる文献

| 引用文献の<br>カテゴリー* | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                                                                                              | 関連する<br>請求項の番号 |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| A               | WO 2010/119854 A1 (株式会社村田製作所) 2010. 10. 21, 図 11、図 12 (ファミリーなし)                                                                                                                                                                                | 1-10           |

| A               | WO 2009/011144 A1 (株式会社村田製作所) 2009. 01. 22, 図 9 & JP 2009-153166 A & JP 2009-44715 A & JP 4301346 B & US 2009/0021352 A1 & US 2009/0021446 A1 & US 2011/0074584 A1 & EP 2056400 A1 & WO 2009/011154 A1 & KR 10-2009-0024663 A & CN 101542830 A | 1-10           |

C 欄の続きにも文献が列挙されている。

D パテントファミリーに関する別紙を参照。

## \* 引用文献のカテゴリー

「A」特に関連のある文献ではなく、一般的技術水準を示すもの

「E」国際出願日前の出願または特許であるが、国際出願日以後に公表されたもの

「L」優先権主張に疑義を提起する文献又は他の文献の発行日若しくは他の特別な理由を確立するために引用する文献(理由を付す)

「R」口頭による開示、使用、展示等に言及する文献

「P」国際出願日前で、かつ優先権の主張の基礎となる出願

## の日の後に公表された文献

「T」国際出願日又は優先日後に公表された文献であって出願と矛盾するものではなく、発明の原理又は理論の理解のために引用するもの

「X」特に関連のある文献であって、当該文献のみで発明の新規性又は進歩性がないと考えられるもの

「Y」特に関連のある文献であって、当該文献と他の1以上の文献との、当業者にとって自明である組合せによって進歩性がないと考えられるもの

「I&amp;」同一パテントファミリー文献

|                                                                         |                                                                 |

|-------------------------------------------------------------------------|-----------------------------------------------------------------|

| 国際調査を完了した日<br>28.03.2012                                                | 国際調査報告の発送日<br>10.04.2012                                        |

| 国際調査機関の名称及びあて先<br>日本国特許庁 (ISA/JP)<br>郵便番号 100-8915<br>東京都千代田区霞が関三丁目4番3号 | 特許庁審査官(権限のある職員)<br>5T 9647<br>高野 洋<br>電話番号 03-3581-1101 内線 3568 |

| C(続き) . 関連すると認められる文献 |                                                                                                              |                |

|----------------------|--------------------------------------------------------------------------------------------------------------|----------------|

| 引用文献の<br>カテゴリー*      | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                            | 関連する<br>請求項の番号 |

| A                    | WO 2009/011423 AI (株式会社 村田製作所) 2009. 01. 22, 図 7 & US<br>2010/0103058 A1 & EP 2166616 A1 & CN 101682113 A    | 1-10           |

| A                    | WO 2008/001561 AI (株式会社 村田製作所) 2008. 01. 03, 図 4、図 7<br>& JP 4281850 B & US 2009/0080296 AI & CN 101467209 A | 1-10           |

| P, A                 | JP 2011-205384 A (株式会社 村田製作所) 2011. 10. 13, 図 3—図 6<br>(ファミリーなし)                                             | 1-10           |