### CONFÉDÉRATION SUISSE

OFFICE FÉDÉRAL DE LA PROPRIÉTÉ INTELLECTUELLE

(51) Int. Cl.3:

G 04 G

3/00 23/08

Brevet d'invention délivré pour la Suisse et le Liechtenstein Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

# 11)

618 577

Les pièces techniques diffèrent du fascicule de la demande no 4698/72

21) Numéro de la demande: 4698/72

29.03.1972

72 FASCICULE DU BREVET B5

(30) Priorité(s):

(22) Date de dépôt:

31.03.1971 JP 46-19075

42 Demande publiée le:

15.03.1977

(44) Fascicule de la demande

publié le:

15.03.1977

(24) Brevet délivré le:

15.08.1980

(45) Fascicule du brevet

publié le:

15.08.1980

(73) Titulaire(s): Kabushiki Kaisha Suwa Seikosha, Tokyo (JP)

(72) Inventeur(s): Tetsuro Hama, Suwa-shi/Nagano-ken (JP)

(74) Mandataire: Bovard & Cie., Bern

(56) Rapport de recherche au verso

#### (54) Montre électronique.

(57) Le circuit diviseur de fréquence de la montre comporte des étages tels que les étages (9 et 10) qui comprennent chacun deux anneaux (9A, 9B) formés chacun de MOST à canal P (11 à 14) et de MOST à canal N (15 à 18). La sortie de chaque anneau est connectée à un inverseur (19, 20). Les transistors (11 et 17) sont commandés par un même signal de temps  $\phi$  tandis que les transistors (12 et 18) sont commandés par un signal de temps  $(\phi)$  dont la phase est inversée par rapport à celle du signal  $(\phi)$ . La connexion (21) est une connexion pour l'asservissement en retour,

Bundesamt für geistiges Eigentum Office fédéral de la propriété intellectuelle Ufficio federale della proprietà intellettuale

## RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de brevet No.: Patentgesuch Nr.:

4698/72

HO 9441

1.1.B. Nr.:

|                        | Documents considérés comme pertinents<br>Einschlägige Dokumente                                                                                                                                                                                                                                                         |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catégorie<br>Kategorie | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile                                                                                                                                               | Revendications con-<br>cernées<br>Betrifft Anspruch<br>Nr. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | FR-A-2 010 828 (THE UNITED STATES TIME CORPORATION)  * figure 2, revendications 1, 6, 7, 8 *                                                                                                                                                                                                                            | I,1,2                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | Revue US "ELECTRONIC DESIGN", Vol. 17, no. 13, 21 juin 1969, pages 85-88, Notice technique: "Counters and Dividers"  * page 87, Build versatile counters with D-type flip-flops; figure 1 *                                                                                                                             |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | DE-A-1 958 648 (PHILIPS) *figure 4 *                                                                                                                                                                                                                                                                                    | 3                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | FR-A-2 018 275 (RCA)<br>CH-B-483 754 (CEH)                                                                                                                                                                                                                                                                              | 3                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | * figure 8 * Compte rendu d'une conférence de R.G. Ball et al: "The application of MOS Transistors in digital integrated circuits" tenu du 21-23 septembre 1965 au "Symposium on application of micro electronics" édité par "Institution of electrical engineers" (I.E.E.E. CONFERENCE PUBLICATION No. 14) pages 22/1- | ·                                                          | Domaines techniques recherchés<br>Recherchierte Sachgebiete<br>(INT. CL. <sup>2</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 22/11. *figure 12 *                                                                                                                                                                                                                                                                                                     | 3                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | "DOCUMENT SUISSE PUBLIE ENTRE LA DATE DE PRIORITÉ ET LA DAT<br>DE DEPOT".<br>CH-B-514 962 (C.E.H.)                                                                                                                                                                                                                      | E                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | * figure 3 *  Documents opposés en cours d'opposition:                                                                                                                                                                                                                                                                  | 3                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | FR-B-1 504 328 (RCA)  * figure 1 *  "Ferranti, The "MICRONOR II" Range of Silicione Integrated Circuits"; Mai                                                                                                                                                                                                           | 1                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | 1967<br>* pages 213 à 223 *                                                                                                                                                                                                                                                                                             | 1                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | "The Electronic Engineer", Mai 1970  * pages 52 à 57 *                                                                                                                                                                                                                                                                  | 1                                                          | Catégorie des documents cités<br>Kategorie der genannten Dokumente:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                        | "The Radio and Electronic Engineer" Avril 1969  * pages 213 à 223 *  ,                                                                                                                                                                                                                                                  | 1                                                          | X: particulièrement pertinent von besondere Bedeutung A: arrière-plan technologique technologischer Hintergrund O: divulgation non-écrite nichtschriftliche Offenbarung P: document intercalaire Zwischenliteratur T: théorie ou principe à la base de l'invention der Erfindung zugrunde liegende Theorien oder Grundsätze E: demande faisant interference kollidierende Anmeldung L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument &: membre de la même famille, document correspondant Mitglied der gleichen Patentfamilie; ubereinstimmendes Dokument |

|  | Etendue | de la | recherche/ | 'Umfang | der | Recherch |

|--|---------|-------|------------|---------|-----|----------|

|--|---------|-------|------------|---------|-----|----------|

Revendications ayant fait l'objet de recherches Recherchierte Patentansprüche:

Revendications n'ayant pas fait l'objet de recherches Nicht recherchierte Patentansprüche: Raison: Grund:

| Date d'achèvement de la recherche/Abschlussdatum der Recherche | Examinateur I.I.B./I.I.B Prüfer |

|----------------------------------------------------------------|---------------------------------|

|                                                                |                                 |

| 19 mars 1973                                                   |                                 |

#### REVENDICATIONS

- 1. Montre électronique comprenant un circuit de base de temps fournissant un signal à haute fréquence, un circuit diviseur de fréquence, un circuit de dispositif d'affichage commandé par le signal sortant du diviseur de fréquence et une source d'énergie qui excite lesdits circuits, montre dans laquelle le circuit diviseur de fréquence est formé d'étages de division (9, 10) comprenant chacun un nombre pair d'anneaux de division complémentaires (9A, 9B) dont chaque anneau comprend deux circuits logiques ET-NON positifs (11/13, 12/14) et deux circuits logiques ET-NON négatifs (15/18, 16/17), chaque circuit logique étant formé de deux transistors à effet de champ à électrode de commande isolée, branchés en série par une connexion sourcedrain, les transistors des circuits logiques négatifs (15/18, 16/17) étant à canal N et ceux des circuits logiques positifs (11/13, 12/14) étant à canal P, caractérisée en ce que les deux circuits logiques positifs ET-NON de chaque anneau sont connectés en parallèle pour former un circuit logique positif ET-NON-ET (ET-OU-NON) tandis que les deux circuits logiques négatifs sont également connectés en parallèle pour former un circuit logique négatif ET-NON-ET (ET-OU-NON), lesdits circuits ET-NON-ET étant connectés en série entre les bornes de la source d'énergie, en ce que, dans chaque anneau, une première borne de sortie (A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub>, A<sub>4</sub>) constituant un point de connexion entre lesdits circuits ET-NON-ET est reliée à un inverseur (19, 20) qui présente une deuxième borne de sortie (B1, B2, B3, B4) reliée, d'une part, aux électrodes de commande de deux transistors (14, 16) appartenant respectivement au premier circuit logique positif et au premier circuit logique négatif, et, d'autre part, à une entrée (D<sub>2</sub>, D<sub>3</sub>, D<sub>4</sub>) de l'anneau suivant, en ce qu'une connexion (21) est établie entre la première borne de sortie (A<sub>4</sub>) du dernier anneau de chaque étage et une entrée (D<sub>1</sub>) du premier anneau de l'étage, cette entrée étant reliée aux électrodes de commande de deux transistors (13, 15) du premier anneau, appartenant respectivement au deuxième circuit logique positif et au deuxième circuit logique négatif de cet anneau.

- 2. Montre selon la revendication 1, caractérisée en ce que, dans chaque étage, les électrodes de commande de deux transistors (11, 17) appartenant respectivement au premier circuit logique positif et au second circuit logique négatif sont reliées à une borne d'entrée (Ø1) qui reçoit un premier signal de commande, tandis que les électrodes de commande de deux transistors (12, 18) homologues de ceux qui sont connectés à ladite borne d'entrée et appartenant respectivement au deuxième circuit 45 court-circuit entre les bornes positives et négatives. logique positif et au premier circuit logique négatif sont reliées à une borne d'entrée (\$\overline{Q}\$1) qui reçoit un second signal de commande déphasé de 180° par rapport au premier.

- 3. Montre selon l'une des revendications 1 ou 2, caractérisée en ce que le circuit diviseur de fréquence comporte au moins une boucle constituée de quatre anneaux et constituant un diviseur par quatre.

- 4. Montre selon l'une des revendications 1 ou 2, caractérisée en ce que le circuit diviseur de fréquence comporte au moins une boucle constituée de six anneaux et constituant un diviseur par

- 5. Montre selon la revendication 1, caractérisée en ce que le dispositif d'affichage est du type numérique et en ce que son circuit comprend un décodeur qui comprend lui-même un étage de division à anneaux complémentaires pour chaque position d'affichage.

La présente invention a pour objet une montre électronique comprenant un circuit de base de temps fournissant un signal à

haute fréquence, un circuit diviseur de fréquence, un circuit de dispositif d'affichage commandé par le signal sortant du diviseur de fréquence et une source d'énergie qui excite lesdits circuits, montre dans laquelle le circuit diviseur de fréquence est formé d'étages de division comprenant chacun un nombre pair d'anneaux de division complémentaires dont chaque anneau comprend deux circuits logiques ET-NON positifs et deux circuits logiques ET-NON négatifs, chaque circuit logique étant formé de deux transistors à effet de champ à électrode de commande isolée, 10 branchés en série par une connexion source-drain, les transistors des circuits logiques négatifs étant à canal N et ceux des circuits logiques positifs étant à canal P.

On connaît déjà des montres électroniques de ce genre. En vue de la fabrication en grande série des modules électroniques de ces 15 montres, il est avantageux d'établir le schéma des circuits de comptage et des circuits diviseurs, de facon que leur réalisation soit aussi simple que possible tout en donnant un circuit intégré dont la fiabilité soit maximale. La production industrielle de ces montres électroniques pose donc le problème de l'établissement 20 des schémas des circuits.

Le brevet CH Nº 483754 décrit déjà un circuit diviseur de fréquence destiné notamment à être réalisé sous forme intégrée et susceptible d'être introduit dans une montre. Toutefois, la structure de ce circuit est telle que sa réalisation pratique n'atteint pas 25 les conditions optimales désirables.

Le brevet FR Nº 2018275 décrit une bascule binaire dynamique qui est également susceptible d'être réalisée en technologie intégrée, mais qui souffre du même inconvénient que le circuit diviseur de fréquence mentionné ci-dessus.

On connaît également des circuits formés de transistors MOS complémentaires connectés en étages et appelés compteurs Johnson. Ainsi, la revue «The Electronic Engineer» de mai 1970 a publié un article montrant une utilisation de ces compteurs comme compteurs décimaux. Toutefois, ce compteur connu ne 35 satisfait pas non plus dans toute la mesure désirable aux exigences spécifiées plus haut.

Partant de cet état de la technique, l'invention a pour but de créer une montre électronique dont tous les circuits, et notamment le circuit diviseur de fréquence, soient conçus de façon à 40 permettre une simplification maximale de la réalisation des masques de sérigraphie tout en garantissant un fonctionnement stable et fiable, même au cas où une des impulsions d'entrée serait légèrement déphasée. En outre, les circuits faisant partie de l'invention et réalisés en technologie intégrée évitent les risques de

Dans ce but, la montre électronique selon l'invention, du genre mentionné au début, est caractérisée en ce que les deux circuits logiques positifs ET-NON de chaque anneau sont connectés en parallèle pour former un circuit logique positif ET-NON-50 ET (ET-OU-NON) tandis que les deux circuits logiques négatifs sont également connectés en parallèle pour former un circuit logique négatif ET-NON-ET (ET-OU-NON), lesdits circuits ET-NON-ET étant connectés en série entre les bornes de la source d'énergie, en ce que, dans chaque anneau, une première borne de 55 sortie constituant un point de connexion entre lesdits circuits ET-NON-ET est reliée à un inverseur qui présente une deuxième borne de sortie reliée, d'une part, aux électrodes de commande de deux transistors appartenant respectivement au premier circuit logique positif et au premier circuit logique négatif, et, d'autre 60 part, à une entrée de l'anneau suivant, et en ce qu'une connexion est établie entre la première borne de sortie du dernier anneau de chaque étage et une entrée du premier anneau de l'étage, cette entrée étant reliée aux électrodes de commande de deux transistors du premier anneau, appartenant respectivement au deuxième 65 circuit logique positif et au deuxième circuit logique négatif de cet

Ainsi, une boucle formée d'un certain nombre de compteurs diviseurs par un nombre pair comprend n étages de circuits

618 577

compteurs binaires et cette boucle diviseuse par 2n divise une fréquence relativement élevée, par exemple un signal supérieur à 1 kHz fourni par un vibreur à cristal pour donner un signal à fréquence relativement basse, par exemple de 1 Hz. Ce signal entraîne, par exemple, un indicateur avançant par sauts à 1 s sous l'action d'un moteur à rotation par pas en assurant ainsi l'affichage de la seconde. En outre, l'invention peut s'appliquer à un affichage numérique en utilisant des étages de compteurs divisant par 6 et par 10 dans la partie relative à la minute, du système d'affichage et des étages de compteur divisant par 12 dans le système d'affichage de l'heure. On réalise ainsi facilement un affichage électronique utilisable dans une montre.

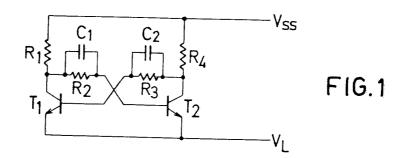

Les circuits électroniques utilisés jusqu'à maintenant dans les montres-bracelets à quartz, ainsi que dans d'autres pièces d'horlogerie, consistaient en circuits flip-flop qui produisent une division 15 par 2 à chaque étage, comme le montre la fig. 1. Dans ce flip-flop se produit une division de fréquence par asservissement rétroactif, lorsqu'on a un rapport de division de 1/6 ou 1/12, afin de sortir la division au rapport optimal, c'est-à-dire à un rapport (1/2)n. Cette méthode d'asservissement rétroactif permettait de transformer un 20 compteur diviseur par 16 en un diviseur décimal en utilisant deux diodes, du fait du retard du flip-flop dû aux éléments CR, comme le montre la fig. 1. Cependant, dans un circuit récemment développé et utilisant des MOST, la division de fréquence par asservissement rétroactif était obtenue en employant huit MOST dans le circuit NI et quatre MOST dans l'inverseur de la porte prévue pour l'asservissement; malgré ces résultats déjà acquis, on peut dire que, pour un produit tel qu'une montre, qui nécessite divers types de compteurs diviseurs par 6, des compteurs décimaux et des compteurs diviseurs par 24, qui ne peuvent pas être réalisés uniquement par des circuits décimaux, un compteur diviseur par 2n est bien supérieur à un compteur diviseur par 2n. Quand on utilise des éléments de circuits intégrés à haute densité, si le schéma est choisi de manière que les seuls conducteurs matériels à connecter soient les conducteurs d'asservissement de l'anneau, tous les autres éléments de circuits actifs peuvent être de type usuel et faits sur le même modèle.

On va décrire, ci-après, en se référant au dessin annexé, une forme de réalisation de l'invention:

- la fig. 1 montre un circuit constitué de résistances R<sub>1</sub>-R<sub>4</sub>, de condensateurs C<sub>1</sub>, C<sub>2</sub> et de transistors bipolaires T<sub>1</sub>, T<sub>2</sub>;

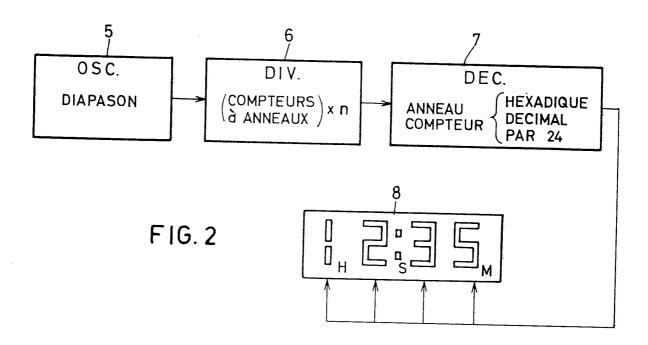

- la fig. 2 est un schéma-bloc d'une forme d'exécution de l'invention;

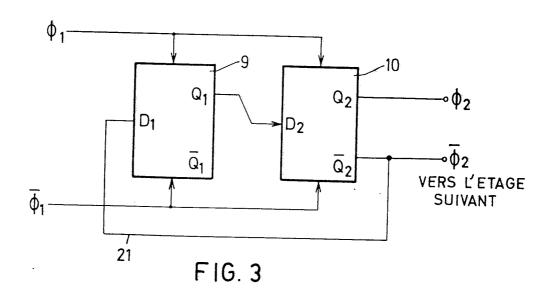

- la fig. 3 représente une boucle de division constituant un élément de la pièce d'horlogerie selon l'invention, et

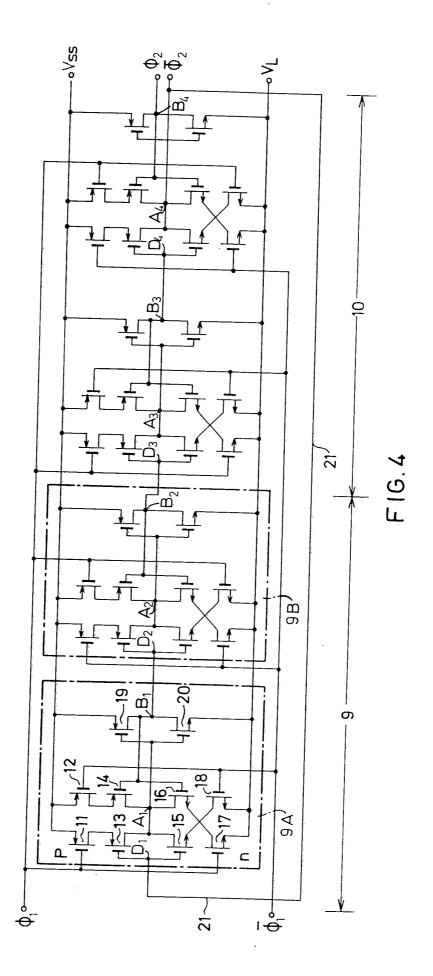

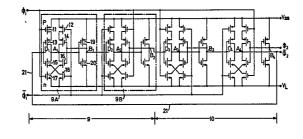

- la fig. 4 une construction générale de cette forme d'exécution.

L'oscillateur 5 forme la base de temps de la pièce d'horlogerie décrite. Sa fréquence, par exemple de 16384 kHz, si un oscillateur de quartz en forme de diapason est utilisé, est divisée par le diviseur 6 dans lequel, pour réduire la fréquence élevée du quartz (plusieurs dizaines de milliers de Hz) à 1 Hz, on a connecté en cascade sept étages de diviseurs par 4. Les compteurs à anneaux sont connectés successivement en une pluralité d'étages afin d'opérer une division de fréquence efficace. Ces anneaux ne

servent qu'à la réduction de fréquence. Le décodeur 7 pour l'affichage électronique est composé d'anneaux de comptage divisant par 6, par 12, et de type décimal. Les étages sont regroupés en boucles composées de trois étages dans le cas des diviseurs par 6, de cinq étages pour la partie décimale. Les boucles divisant par 4 ont deux étages et les boucles divisant par 6 en ont trois dans le cas de diviseurs par 24. En 8, on voit l'affichage qui s'effectue sur 24 h et comprend des chiffres formés par des segments.

A la fig. 3, on voit qu'en connectant deux circuits de retard 9 et 10 en deux étages successivement et en asservissant en retour l'entrée du premier à la sortie du second étage, de façon à former une boucle, on a un compteur qui provoque une division par 4 au moyen de circuits logiques NAND et OU. On voit l'exécution de ces circuits à la fig. 4.

Chacun des deux étages 9 et 10 comprend deux ensembles ou anneaux (9A, 9B) formés chacun de MOST à canal P 11 à 14 et de MOST à canal N 15 à 18. Le groupe de MOST de type P ou positif comprend deux portes ET-NON 11, 13 et 12, 14, connectées en parallèle, et le groupe de type N ou négatif comprend deux portes ET-NON 15, 18 et 16, 17 connectées en parallèle. Les deux groupes précités sont connectés en série entre les bornes Vss et VL de la source de puissance et la sortie de cet ensemble va à l'inverseur 19, 20. Les éléments 11, 17 sont commandés par un signal de temps Ø de la même phase, tandis que 12, 18 sont commandés par un signal de temps  $\overline{\mathcal{Q}}$  de phase inversée. La connexion 21 est une connexion pour l'asservissement en retour. Les deux étages 9 et 10, formés chacun de deux ensembles complémentaires tels que décrits ci-dessus, sont commandés par un signal de phase du compteur. Comme chaque étage tel que 9 ou 10 assure une divi-30 sion par 2, on peut brancher ces étages 9 et 10 en une série d'étages indépendants, ce qui donne un diviseur binaire de type usuel. Mais, pour diviser un signal de haute fréquence, de plusieurs dizaines de kHz, il est plus efficace de superposer les anneaux de comptage par paire d'étages ou par boucles. On 35 obtient ainsi un minimum d'étages et chaque boucle, telle que 9, 10 effectue alors une division de fréquence par 4. On peut connecter en suivant une série de telles boucles formées chacune de deux étages.

Pour obtenir un type d'éléments divisant par 6, il suffit de

de câbler un fil 21 pour l'asservissement en retour après superposition du demi-circuit de la fig. 4 par une boucle supplémentaire.

Pour la division par 24, un bloc de deux étages et un bloc de trois

étages sont prévus avec des asservissements rétroactifs successifs.

Dans la partie qui forme un compteur décimal, un fil d'asservissement en retour sur cinq étages est prévu, alors que, dans les autres

parties, il suffit de prévoir l'asservissement en retour sur deux ou

trois étages. On n'utilise ainsi aucun élément actif.

Les signaux de temps  $\emptyset$  et  $\overline{\emptyset}$  sont déphasés de 180° l'un par rapport à l'autre et Q, ainsi que  $\overline{Q}$ , sont les bornes de sortie de ces signaux.

Comme indiqué plus haut, comme l'invention crée des circuits de comptage divisant par un nombre pair, qui ont un très bon rendement, on peut réaliser un circuit actif de bon rendement, tel qu'un circuit électronique de montre avec une haute densité de 55 MOST intégrés.