### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 3 March 2005 (03.03.2005)

**PCT**

# (10) International Publication Number $WO\ 2005/020487\ A1$

(51) International Patent Classification<sup>7</sup>: H04J 3/06

(21) International Application Number:

PCT/US2004/025475

**(22) International Filing Date:** 6 August 2004 (06.08.2004)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/640,108 13 August 2003 (13.08.2003) U-

(71) Applicant (for all designated States except US): INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

- (72) Inventors: LIENHART, Rainer; 2727 Forbes Avenue, Santa Clara CA 95051 (US). KOZINTSEV, Igor; 4913 Anna Drive, San Jose, CA 95124 (US).

- (74) Agents: VINCENT, Lester, J. et al.; Blakely Sokoloff Tayor & Zafman, 7th floor, 12400 Wilshire Boulevard, Los Angeles, CA 90025 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: UNIVERSAL ADAPTIVE SYNCHRONIZATION SCHEME FOR DISTRIBUTED AUDIO-VIDEO CAPTURE ON HETEROGENEOUS COMPUTING PLATFORMS

(57) Abstract: According to one embodiment of the present invention, a novel apparatus is disclosed. The apparatus includes an analog to digital converter (406) to receive a predefined synchronization signal and a receiver clock; and an interpolation module (408) coupled to the analog to digital converter to receive an output of the analog to digital converter and to continuously estimate and adapt current delay and skew estimates to synchronize a signal.

## Universal Adaptive Synchronization Scheme for Distributed Audio-Video Capture on Heterogeneous Computing Platforms

#### **COPYRIGHT NOTICE**

Contained herein is material that is subject to copyright protection. The copyright owner has no objection to the facsimile reproduction of the patent disclosure by any person as it appears in the Patent and Trademark Office patent files or records, but otherwise reserves all rights to the copyright whatsoever.

#### 10 FIELD OF THE INVENTION

[0002] The present invention generally relates to the field of distributed multimedia synchronization. More particularly, an embodiment of the present invention relates to a universal adaptive synchronization scheme for distributed audio-video capture on heterogeneous computing platforms.

#### 15 BACKGROUND

20

[0003] One approach to provide additional computing power has been to utilize distributed computer environments. This approach enables several computers to collaboratively perform computational tasks within a reduced amount of time. Generally, the divide and conquer approach provided by such parallel computing approaches enables utilization of available personal computers, rather than purchasing of a high performance, server-based computer system for performing the computationally intensive tasks.

[0004] Distributed computing has generally, however, been applied to performing purely computational tasks and not to synchronized capture and/or processing of signals, especially audio/video signals (and data streams). Signal processing of audio/video signals (and data streams) are generally very sensitive to even very small differences in sampling rates (e.g., clock skew), jitter, and delays. Therefore, precise synchronization is very critical for high quality input/output processing, as well as for real-time performance and in general, robustness and reliability issues. But, precise capture and synchronized inputs are not guaranteed on current platforms.

5

10

15

20

arise when several input/output (I/O) devices are used to capture audio and visual information from video camera(s) and microphone(s). Due to the fact that the different I/O devices will be triggered by separate oscillators, resulting audio samples and video frames will not be aligned on an absolute time line (thus inducing some relative offsets). Moreover, due to differences in the oscillators' frequencies, audio and/or visual data will drift away across multiple channels/streams over time. Instabilities in the oscillators' frequencies will also not be perfectly correlated between each other.

[0006] Similarly, in the case of multiple PC platforms audio and visual I/O devices will not be synchronized in time scale inducing some relative offsets and data samples to drift relative to each other. The extent of the relative offset, drift, and jitter on the existing platforms depends on many hardware and software parameters and can be very significant, sometimes causing total degradation of the processed signals (from the non-synchronized input streams). Such drifts, delays, and jitters can cause significant performance degradation for instance for array signal processing algorithms.

between microphones, an error of only 0.01 percent in time can cause error of 20 degrees in the beam direction. Due to this fact, current implementations of audio array process algorithms may rely on dedicated circuitry for the synchronization between multiple I/O channels. Unfortunately, implementing such an approach with existing PC platforms would require a major overhaul of the current hardware utilized by the PC platforms. Therefore, there remains a need to overcome one or more of the limitations in the above-described existing art.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

- 10 [0008] The invention is illustrated by way of example and not limitation in the figures of the accompanying drawings, in which like references indicate similar or identical elements, and in which:

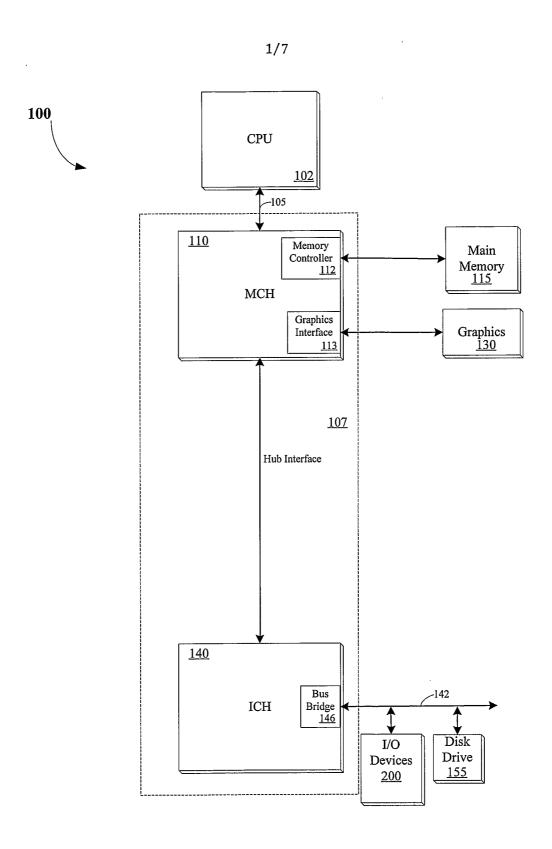

- [0009] Fig. 1 illustrates an exemplary block diagram of a computer system 100 in which one embodiment of the present invention may be implemented;

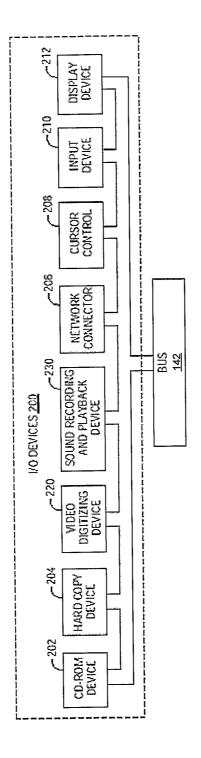

- 15 **[0010]** Fig. 2 further illustrates the I/O devices 200 of the computer system 100 as depicted in Fig. 1;

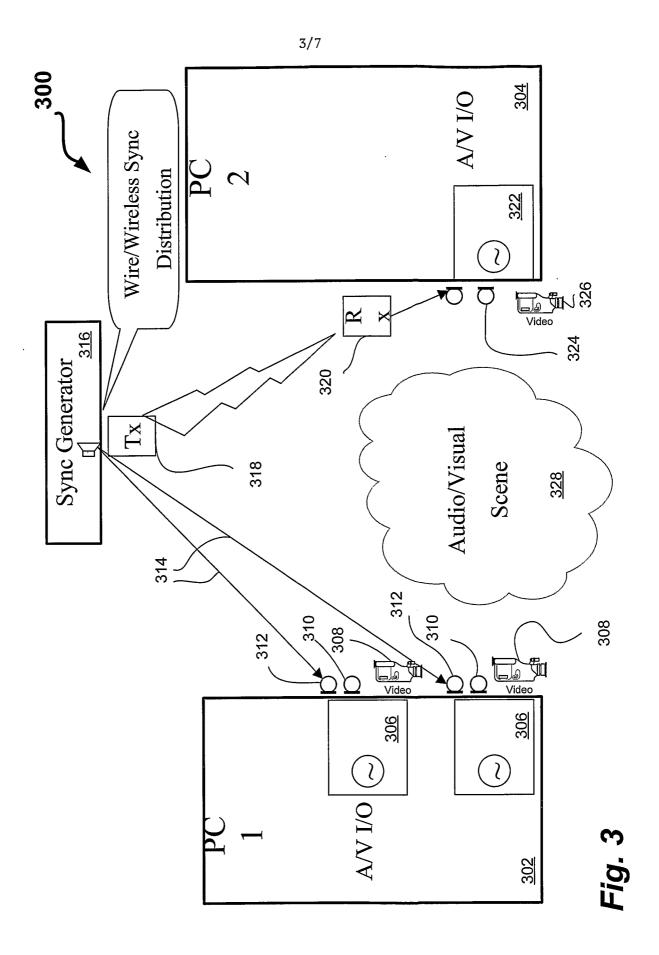

- [0011] Fig. 3 illustrates an exemplary synchronized, distributed multimedia data capture system 300 which may be utilized to implement an embodiment of the present invention;

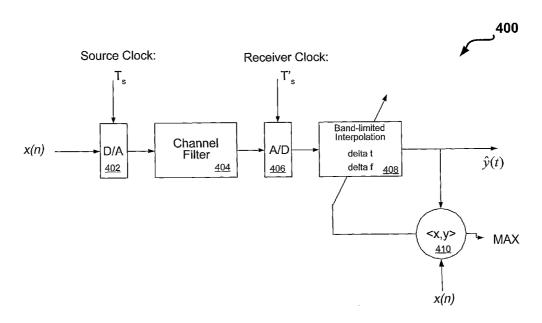

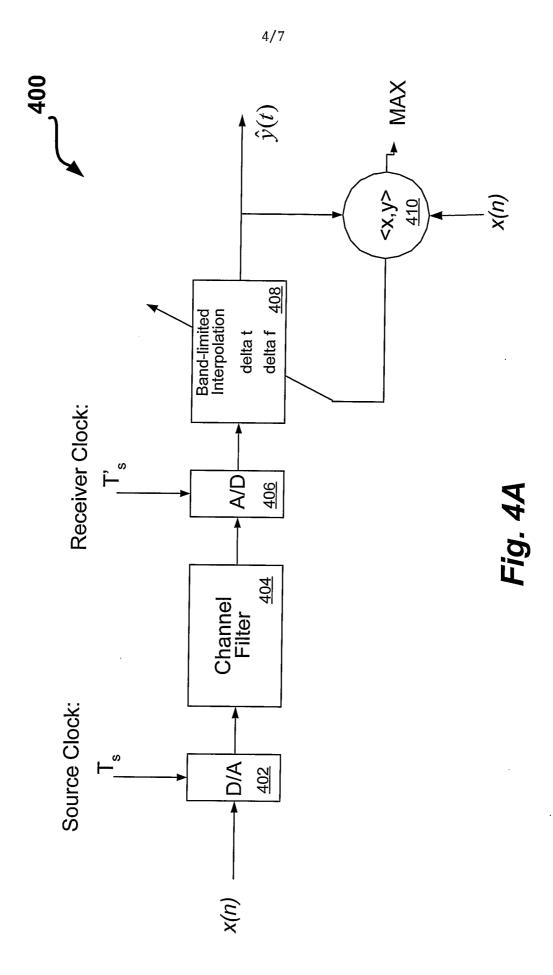

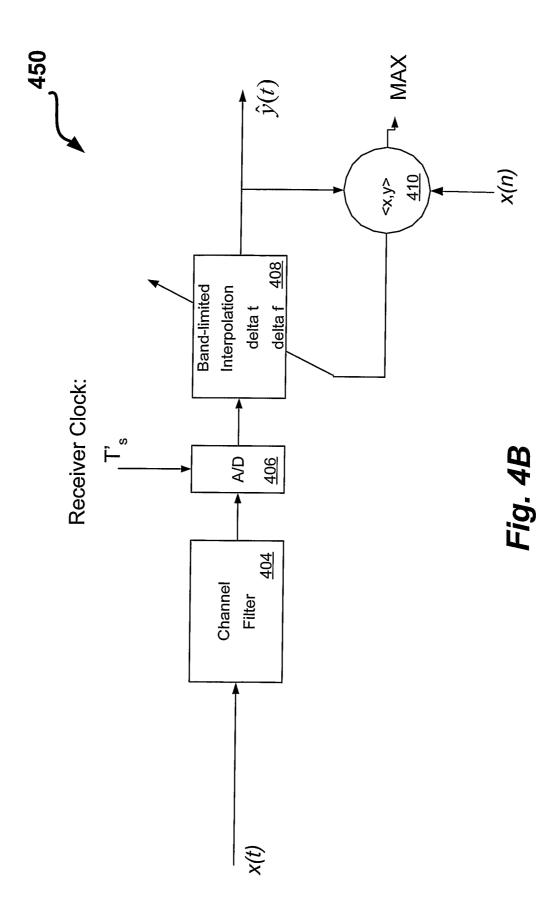

- 20 **[0012]** Figs. 4A and 4B illustrate exemplary adaptive filtering systems 400 and 450 in accordance with embodiments of the present invention;

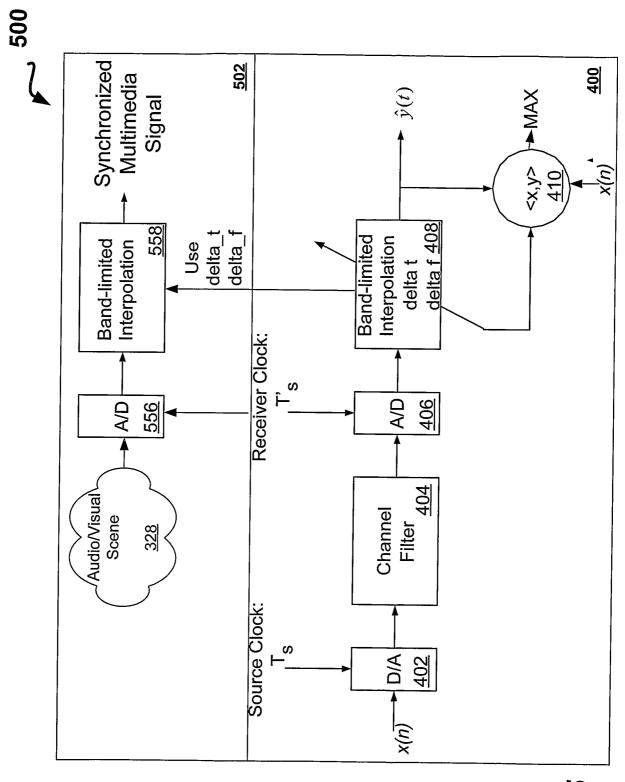

[0013] Fig. 5 illustrates an exemplary adaptive filtering system 500 in accordance with an embodiment of the present invention; and

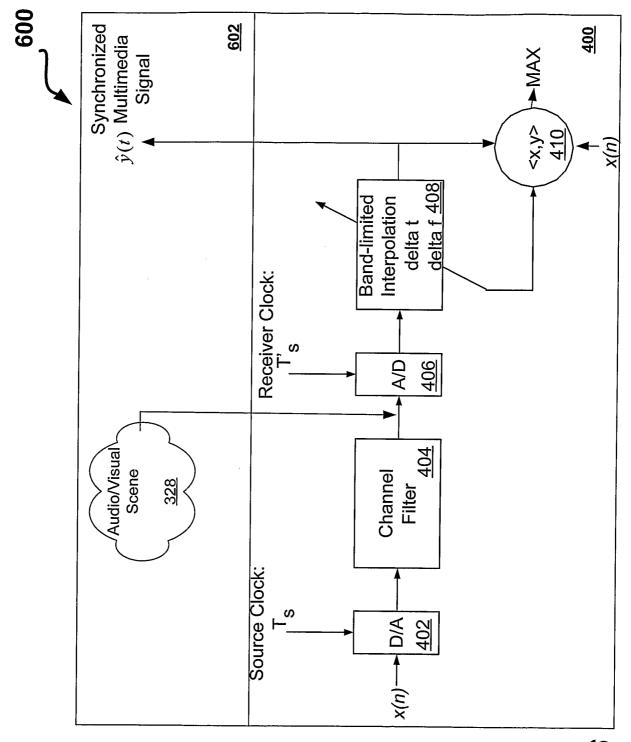

[0014] Fig. 6 illustrates an exemplary adaptive filtering system 600 in accordance with an embodiment of the present invention.

#### DETAILED DESCRIPTION

5

10

15

[0015] In the following detailed description of the present invention numerous specific details are set forth in order to provide a thorough understanding of the present invention. However, it will be apparent to one skilled in the art that the present invention may be practiced without these specific details. In other instances, well-known structures and devices are shown in block diagram form, rather than in detail, in order to avoid obscuring the present invention.

[0016] Reference in the specification to "one embodiment" or "an embodiment" means that a particular feature, structure, or characteristic described in connection with the embodiment is included in at least one embodiment of the invention. The appearances of the phrase "in one embodiment" in various places in the specification are not necessarily all referring to the same embodiment.

[0017] The following clock-related definitions are used herein:

- "stability" denotes how well a clock can maintain a constant frequency;

- "accuracy" denotes how well a clock's time compares to national standards:

- "precision" specifies the internal resolution of the clock;

• "offset" specifies the time difference between two clocks;

- "skew" characterizes the difference in frequency between two clocks and is defined as the ratio of the frequencies;

- "synchronizing two clocks" denotes the process of reconciling two

clocks with respect to frequency and time (i.e., correcting the offset to zero and making the skew equal to one).

- [0018] Also, the use of the term general purpose computer (GPC) herein is intended to denote laptops, PDAs, tablet PCs, mobile phones, and similar devices that can be a part of a distributed audio/visual system.

- 10 [0019] Fig. 1 illustrates an exemplary block diagram of a computer system 100 in which one embodiment of the present invention may be implemented. The computer system 100 includes a central processing unit (CPU) 102 coupled to a bus 105. In one embodiment, the CPU 102 is a processor in the Pentium® family of processors including the Pentium® II processor family, Pentium® III processors, Pentium® IV processors available from Intel Corporation of Santa Clara, California. Alternatively, other CPUs may be used, such as Intel's XScale processor, Intel's Pentium M Processors, ARM processors available from ARM Ltd. of Cambridge, the United Kingdom, or OMAP processor (an enhanced ARM-based processor) available from Texas Instruments, Inc., of Dallas, Texas.

- 20 **[0020]** A chipset 107 is also coupled to the bus 105. The chipset 107 includes a memory control hub (MCH) 110. The MCH 110 may include a memory controller 112 that is coupled to a main system memory 115. Main system memory 115 stores data and sequences of instructions that are executed by the CPU 102 or any other device included

in the system 100. In one embodiment, main system memory 115 includes dynamic random access memory (DRAM); however, main system memory 115 may be implemented using other memory types. Additional devices may also be coupled to the bus 105, such as multiple CPUs and/or multiple system memories.

- The MCH 110 may also include a graphics interface 113 coupled to a 5 [0021] graphics accelerator 130. In one embodiment, graphics interface 113 is coupled to graphics accelerator 130 via an accelerated graphics port (AGP) that operates according to an AGP Specification Revision 2.0 interface developed by Intel Corporation of Santa Clara, California. In an embodiment of the present invention, a flat panel display may be 10 coupled to the graphics interface 113 through, for example, a signal converter that translates a digital representation of an image stored in a storage device such as video memory or system memory into display signals that are interpreted and displayed by the flat-panel screen. It is envisioned that the display signals produced by the display device may pass through various control devices before being interpreted by and subsequently 15 displayed on the flat-panel display monitor. The display device may be an liquid crystal display (LCD), a flat panel display, a plasma screen, a thin film transistor (TFT) display, and the like.

- [0022] In addition, the hub interface couples the MCH 110 to an input/output control hub (ICH) 140 via a hub interface. The ICH 140 provides an interface to input/output (I/O) devices within the computer system 100. In one embodiment of the present invention, the ICH 140 may be coupled to a Peripheral Component Interconnect (PCI) bus adhering to a Specification Revision 2.1 bus developed by the PCI Special Interest Group of Portland, Oregon. Thus, the ICH 140 includes a bus bridge 146 that

provides an interface to a bus 142. In one embodiment of the present invention, the bus 142 is a PCI bus. Moreover, the bus bridge 146 provides a data path between the CPU 102 and peripheral devices.

[0023] The bus 142 includes I/O devices 200 (which are further discussed with reference to Fig. 2) and a disk drive 155. However, one of ordinary skill in the art will appreciate that other devices may be coupled to the PCI bus 142. In addition, one of ordinary skill in the art will recognize that the CPU 102 and MCH 110 may be combined to form a single chip. Furthermore, graphics accelerator 130 may be included within MCH 110 in other embodiments.

5

15

In addition, other peripherals may also be coupled to the ICH 140 in 10 [0024] various embodiments of the present invention. For example, such peripherals may include integrated drive electronics (IDE) or small computer system interface (SCSI) hard drive(s), universal serial bus (USB) port(s), a keyboard, a mouse, parallel port(s), serial port(s), floppy disk drive(s), digital output support (e.g., digital video interface (DVI)). and the like. Moreover, the computer system 100 is envisioned to receive electrical power from one or more of the following sources for its operation: a power source (such as a battery, fuel cell, and the like), alternating current (AC) outlet (e.g., through a transformer and/or adaptor), automotive power supplies, airplane power supplies, and the like.

Fig. 2 further illustrates I/O devices 200 of the computer system 100 as [0025] depicted in Fig. 1. As illustrated, the computer system 100 may include a display device 20 212 such as a monitor. The display device 212 may include an intermediate device such as a frame buffer. The computer system 100 also includes an input device 210 such as a keyboard and a cursor control 208 such as a mouse, trackball, or track pad. The display

device 212, the input device 210, and the cursor control 208 are coupled to bus 142. The computer system 100 may include a network connector 206 so that computer system 100 may be connected as part as a local area network (LAN) or a wide area network (WAN) such as, for example, the Internet.

Additionally, the computer system 100 can also be coupled to a device for sound recording and playback 230 such as an audio digitization device coupled to a microphone for recording voice input for speech recognition or for recording sound in general. The I/O devices 200 of computer system 100 may also include a video digitizing device 220 that can be used to capture video images alone or in conjunction with sound recording device 230 to capture audio information associated with the video images. Furthermore, the input devices 200 may also include a hard copy device 204 (such as a printer) and a CD-ROM device 202. The input devices 200 (202-212) are also coupled to bus 142.

to capture multimedia data including, for example, audio and/or video data from a selected scene, environment, or the like. Currently, many individuals utilize personal computers (PCs) such as depicted in Fig. 1 in order to capture live audio/video data (multimedia scene data) through, for example, a camera coupled to a port of computer system 100 (not shown) such as, for example, a USB port or a firewire port (IEEE 1394). This data is then provided as a streaming media format (Multimedia Stream Data) including, but not limited to, Microsoft® advanced steaming format (ASF) files, motion picture experts group (MPEG) standards such as MPEG-1/2/4, and audio layer-3 (MP3) files, Real Audio G2 files, QDesign2 files, or the like.

15

In one embodiment of the present invention, an audio capture device such as a microphone may be utilized by the computer system 100 to capture audio information associated with the captured multimedia scene data. Accordingly, as individuals attempt to utilize their personal computers in order to capture, for example, live audio/video data, it is generally recognized that audio/video data is most effectively captured utilizing one or more data capture devices.

5

15

[0029] With reference to Figs. 1 and 2, the I/O devices (except AGP display adapters) are generally connected to the ICH (I/O hub) via dedicated or shared buses. The PCI bus can be a way to connect various audio, video, and networking devices to the ICH.

These devices typically have their own crystal oscillators and clocks that are not synchronized to each other, and to the CPU clock. This means, for example, that if audio and video samples are captured using separate I/O cards, they can go out of sync as time passes by.

[0030] Unfortunately, the time it takes for a block of data to travel between I/O device, main memory, and CPU is variable and depends on many factors like the CPU load, cache state, activity of other I/O devices that share the bus, and the operating system behavior. Therefore, applications that process data have no way to know precisely the time the data enters or leaves the I/O devices. The propagation delay may range from nanoseconds to milliseconds depending on the conditions mentioned above.

20 [0031] In existing applications, multiple video and audio streams are usually captured using a single I/O device such as a multi-channel analog to digital (A/D) or audio/video (A/V) capture cards. Special methods are needed to use multiple I/O devices synchronously even on a single PC platform.

[0032] The situation becomes more complex when synchronization of I/O devices on separate platforms is desired. There, in addition to I/O-CPU latencies, network connection introduces additional delays, that are variable due to best-effort (and therefore variable transmission delay) type of Media Access Protocols used in existing wired and wireless Ethernet.

5

10

15

20

[0033] Fig. 3 illustrates an exemplary synchronized, distributed multimedia data capture system 300 which may be utilized to implement an embodiment of the present invention. As illustrated in Fig. 3, the data capture system 300 may include a plurality of multimedia platforms (302 and 304). However, Fig. 3 should not be construed in a limiting sense and is provided to illustration one embodiment of the present invention.

[0034] The multimedia platform 302, as well as multimedia platform 304 may be provided utilizing the computer system 100, as depicted in Fig. 1. As illustrated, the multimedia platform 302 includes a plurality of I/O cards 306 which may include a microphone 310, as well as a video capture device 308. Each audio/video card may include a wired link input 312, which is used to receive a multimedia synchronization signal 314, which is generated by sync generator 316.

[0035] In on embodiment of the present invention, the sync generator 316 is configured utilizing a computer system, such as the computer system 100, as depicted in Fig. 1. The sync generator 316 may generate the synchronization signal 314. In one embodiment of the present invention, the synchronization signal 314 is selected as a maximum length sequences (MLS) signal, which is generally comprised of white noise, to form an audio sync signal. Sequence numbers may be modulated onto the MLS signal.

However, in alternate embodiments, a different multimedia synchronization signal may be selected if desired based on the specific implementation.

[0036] The synchronization signal 314 may be provided via a wired link, for example, to multimedia platform 302 and/or may be transmitted wirelessly via a transmitter 318 and a receiver 320 to multimedia platform 304. An example of the wireless transmitter 318 and receiver 320 is a radio frequency (RF) based transmitter and receiver. In one embodiment of the present invention, a single multimedia synchronization signal is generated which is transmitted to each of the multimedia platforms via either a wired link or a wireless link. As such, the multimedia platform 304 includes an I/O card 322 with a video capture device 326, as well as an audio capture device 324.

5

10

15

20

[0037] Furthermore, in contrast to the multimedia platform 302, the multimedia platform 304 may include the wireless receiver (Rx) 320, which may be used to capture the received multimedia synchronization signal. In one embodiment of the present invention, the transmitter 318 modulates the synchronization signal 314 onto a multimedia signal (e.g., audio signal), which in turn is modulated onto some wireless carrier signal and the receiver 320 demodulates the received signal in order to generate the multimedia modulated synchronization signal used by the platform 304. The multimedia modulated synchronization signal (i.e., the synchronization signal modulated onto a multimedia signal) is then provided to the video capture device(s) and/or audio capture device(s) in order to enable synchronization of captured audio/visual scene data 328. In an embodiment of the present invention, the wireless transmission of the synchronization

signal may be provided using, for example, wireless audio transmission via a U.S. Robotics Sound Link Solution.

5

10

15

20

[0038] In accordance with one embodiment of the present invention, an audio synchronization signal is generated as the multimedia synchronization signal. In one embodiment of the present invention, the sync generator 316 produces special synchronization signals and modulates them using its own clock information. The synchronization signals are delivered to audio input devices using wired (as to 302) or wireless (as to 304) mechanism to a dedicated synchronization audio channel. As a result, the synchronization information becomes embedded in the audio/video streams as a separate audio track and is available to the application layer for the processing.

In accordance with an embodiment of the present invention, once errors are determined within generated multimedia stream data, each multimedia platform (e.g., 302 or 304) is responsible, for example, for resampling of generated multimedia stream data to synchronize the multimedia stream data generated by each I/O card of each multimedia platform. Consequently, once all generated multimedia stream data is synchronized, the captured stream data may be provided to an array signal-processing computer (not illustrated). The array signal processing computer may then perform, for example, beam forming, blind signal separation (BSS), multi-modal recognition, or the like, utilizing the synchronized multimedia stream data. Likewise, embodiments of the present invention may be performed within the multimedia data capture system 300 using, for example, camcorders, video capture devices, or the like, which may include multiple input channels.

[0040] Fig. 4A illustrates an exemplary adaptive filtering system 400 in accordance with an embodiment of the present invention. In one embodiment of the

present invention, the system 400 operates by utilizing band-limited signal interpolation to continuously estimate and adapt current delay and skew estimates to synchronize audio/visual signals collected from multiple devices. In an embodiment of the present invention, the system 400 of Fig. 4A may be embedded on a computer system (such as the computer system 100 of Fig. 1), a digital signal processor (DSP), a coder-decoder (codec) module, a CPU, and the like.

5

10

15

20

The system 400 includes a Digital to Analog (D/A) converter 402 which receives a source synchronization signal x(n) from a sender (clock master) and a source clock  $T_s$ . The digital to analog converter 402 may be provided at a sender location. The source synchronization signal may be a multimedia signal such as an audio or video signal. The D/A converter 402 then provides its output to a channel filter 404. It is envisioned that the channel filter 404 exemplifies characteristics of the signal transmission environment or medium coupling the sender and receivers (e.g., a copper wire, RF medium, frequency modulation (FM) medium, other wireless medium, and the like).

[0042] The system 400 further includes an analog to digital (A/D) converter 406 (e.g., at a receiver location), which converts the signal transmitted through the channel filter 404 into digital form. The A/D converter 406 further receives a receiver clock  $T'_s$  to sample the signal transmitted through the channel filter 404. In one embodiment of the present invention, the source clock may be used for the actual sample rate of the D/A converter 402, while the sync signal x(n) would be the signal that is used to determine the difference in the sample rate between the master D/A 402 and the client A/D converter(s) 406. In an embodiment of the present invention, the source clock  $T_s$  and the receiver clock  $T'_s$  are provided by a device such as a DSP, a codec module, a CPU, and the like.

[0043] As illustrated in Fig. 4A, the A/D converter 406 is coupled to a band-limited interpolation module 408, which is driven by maximizing some cost function between the source synchronization signal x(n) and the resampled output of the A/D converter 406 to generate the output signal of the system 400 ( $\hat{y}(t)$ ) and to determine the skew (delta\_f) and offset (delta\_t) values. In one embodiment of the present invention, all multimedia signal captured by some A/D converter driven with the same clock as 406 are re-sampled accordingly

[0044] The precise form of the synchronization signal may be a domain knowledge and thus known at the sender as well as all receivers. The estimation of the time delay and sampling skew between the actually recorded signal  $y(nT_s')$  at a receiver with a sampling rate of  $F_s' = 1/T_s'$  and the source signal  $x(nT_s)$  operating at sampling rate  $F_s = 1/T_s$  is based on the adaptive filtering approach shown in Fig. 4A. At the sender the sync signal  $x(nT_s)$  is sent out through the D/A converter 402 at sampling rate  $F_s$ . The signal is assumed to go through a filter formed by the D/A converter, transmission channel (e.g., wireless channel), and finally A/D converter with a sample rate of  $F_s'$  on the receiving side.

[0045] An adaptive filter based on band-limited interpolation of discrete-time signals (408) is then used to estimate offset  $\Delta t$  and the skew  $\Delta F = T_s'/T_s''$ . The band-limited interpolated signal  $\hat{y}(t)$  with estimated offset  $\Delta t$  and sampling period  $T_s''$  is given by:

$$\hat{y}(t) = \sum_{n=-\infty}^{\infty} y(nT_s') \cdot a \cdot \text{sinc}(b(t - nT_s'))$$

5

10

$$\hat{y}(t') = a \sum_{n=-\infty}^{\infty} y(nT_s') \cdot \frac{\sin(\widetilde{t} - \widetilde{b}n)}{\widetilde{t} - \widetilde{b}n}$$

where

$$a = \min\{1, \frac{F_s''}{F_s'}\}, \ \widetilde{b} = \pi T_s' \min\{F_s', F_s''\}, \ \widetilde{t} = bt\pi$$

[0046] In an embodiment of the present invention, for simplicity, the windowing function used in the implementation (e.g., Kaiser window) is omitted in this formulation.

5 Given the inner product as the performance criterion over a time window of size w, the optimization criterion becomes:

$$f(T_s'', \Delta t) = \langle x(nT_s), \hat{y}(\tilde{t}) \rangle \rightarrow \max$$

where t is evaluated at  $t = nT_s'' + \Delta t$ . Gradient decent can be applied for optimization in accordance with an embodiment of the present invention.

10 [0047] Although the adaptive time delay and sampling skew estimator of Fig. 4A can track fractional time delay and fractional sampling skew, it may be initialized by rough estimates for the time delay  $\Delta t$  and sampling skew factor  $\Delta F = T_s'/T_s''$  in one embodiment of the present invention.

[0048] In an embodiment of the present invention, to improve the precision of the MLS time offset estimation, two or more audio samples per MLS symbol may be utilized. Accordingly, there is going to be more than two samples per main lobe of MLS autocorrelation function and the precision of finding the position of the autocorrelation peak increases. The position may be found by fitting a curve (or its approximation) corresponding to the autocorrelation main lobe to the samples with highest values.

[0049] In an embodiment of the present invention, a novel method to initialize the skew estimate of the adaptive filter approach based on 'Autonomous Estimation

of Skew' (self-monitoring/self-sensing) is disclosed. As an alternative to (or in addition to) the MLS-based skew estimation, networking services may be utilized to calibrate individual audio clocks by running a dummy audio capture process counting the number of samples observed per measurement period. In one embodiment of the present invention, it is assumed that the current platform has a reasonable long-term sampling clock stability and that the Network Time Protocol (NTP) is providing a system clock with a clock error per day (CEPD) of hundreds of milliseconds, where:

T: Observation period (in seconds)

$\Delta T$ : Uncertainty in observation interval (in seconds)

$f^{target}$ : Target sampling rate (in Hertz)

$f^{actual}$ : Actual sampling rate (in Hertz)

$S^{t \operatorname{arge} t}$ : Number of samples produced in observation period T at sample

$S^{actual}$ : Number of samples produced in observation period T at sample

15 rate  $f^{actual}$

rate  $f^{t \operatorname{arg} et}$

5

10

20

$S^{measured}$  : Number of samples produced in observation period  $T\pm \Delta T$  at sample rate  $f^{actual}$

[0050] Assuming an accurate system clock at each distributed platform, the skew between the target sampling rate and actual sampling rate of a platform may be determined as follows:

$$skew = \frac{f^{target}}{f^{actual}} = \frac{T \cdot f^{target}}{T \cdot f^{actual}} = \frac{S^{target}}{S^{actual}}$$

[0051] In real world, however, the system clock may not be perfect or accurate enough. Given an uncertainty of  $\Delta T$  for an observation period of T, the measured skew may be determined as follows"

$$skew^{measured} = \frac{S^{target}}{S^{measuerd}} = \frac{T \cdot f^{target}}{(T \pm \Delta T) \cdot f^{actual}} = \frac{T}{(T \pm \Delta T)} skew$$

$$\Leftrightarrow skew = (1 \pm \frac{\Delta T}{T}) \cdot skew^{measured}$$

- In other words, the error in the estimated skew factor is  $1 \pm \Delta T/T$ . Given a clock accuracy of NTP of around 250 ms and an observation period of 1 day, the estimation error is less than  $3 \cdot 10^{-6}$ . Thus, a sample rate around 44.1 kHz may be correctly determined up to 0.13 samples per second.

- [0053] Fig. 4B illustrates an exemplary adaptive filtering system 450 in accordance with an embodiment of the present invention. In one embodiment of the present invention, the system 450 includes the channel filter 404, the A/D converter 406, the band-limited interpolation module 408, and the scalar product 410. As illustrated in Fig. 4B, the analog synch signal x(t) (where x(n) denotes the digital synch signal, while x(t) denotes the continuous analog signal) may be generated in the analog domain. It is also envisioned that the digital reference form x(n) of x(t) may be known in an embodiment of the present invention.

- [0054] Fig. 5 illustrates an exemplary adaptive filtering system 500 in accordance with an embodiment of the present invention. In one embodiment of the present invention, the system 500 includes the system 400 of Fig. 4A. The system 500 also includes a portion 502 to provide synchronized multimedia signals for additional channels. For example, additional audio/visual scene signals may be collected (by, for example, the

multimedia platforms 302 and 304 of Fig. 3) from the audio/visual scene 328 such as discussed with reference to Fig. 3 in one embodiment of the present invention.

[0055] As illustrated in Fig. 5, the captured signals may then be provided to one or more A/D converters 556 (e.g., one for each channel), which may also receive the receiver clock ( $T_s'$ ). The A/D converter 556 may be coupled to a respective band-limited interpolation module (558). The band-limited 558 may receive the estimated delta\_t and delta\_f values from the band-limited interpolation module 408, for example, to avoid having to recalculate these values. Accordingly, in accordance with an embodiment of the present invention, a single clock may drive multiple channels.

5

In one embodiment of the present invention, even though one additional channel per device may be assigned to perform synchronization (such as discussed with reference to Fig. 5), it is envisioned that the analog synchronization signal at the receiver can be mixed into the analog data channel at the receiver before the A/D conversion, provided the magnitude of the signal is maintained small enough to introduce no perceived distortion. Such an embodiment of the present invention is illustrated in Fig. 6.

[0057] Fig. 6 illustrates an exemplary adaptive filtering system 600 in accordance with an embodiment of the present invention. In one embodiment of the present invention, the system 600 includes the system 400 of Fig. 4A. The system 600 also includes a portion 602 to provide synchronized multimedia signals for additional channels.

For example, the analog synchronization signal may be mixed into the additional captured audio/visual scene signals from the audio/visual scene 328 (e.g., at the A/D converter 406). In turn, the output of the band-limited interpolation module 408 may provide synchronization for additional multimedia channels.

[0058] In accordance with an embodiment of the present invention, it is envisioned that the MLS-based synchronization indicates that the autocorrelation peaks are detected reliably even when the magnitude of the MLS signal is up to two orders below the magnitude of the audio signal for a length 1023 sequence (for longer MLS sequences this magnitude can be made even smaller).

5

10

[0059] Whereas many alterations and modifications of the present invention will no doubt become apparent to a person of ordinary skill in the art after having read the foregoing description, it is to be understood that any particular embodiment shown and described by way of illustration is in no way intended to be considered limiting. For example, even though embodiments of the present invention have been discussed with respect to a band-limited interpolation module, it is envisioned that other interpolation techniques may be utilized. Therefore, references to details of various embodiments are not intended to limit the scope of the claims which in themselves recite only those features regarded as essential to the invention.

#### WHAT IS CLAIMED IS:

1. An apparatus comprising:

an analog to digital converter to receive a predefined synchronization signal and a receiver clock; and

an interpolation module coupled to the analog to digital converter to

receive an output of the analog to digital converter and to continuously estimate and adapt

current delay and skew estimates to synchronize a signal.

- 2. The apparatus of claim 1 further including a digital to analog converter coupled to the analog to digital converter to receive the synchronization signal and a source clock and to provide its output to the analog to digital converter.

- 10 3. The apparatus of claim 1 wherein the apparatus is utilized to synchronize a plurality of multimedia signals captured by a plurality of devices.

- 4. The apparatus of claim 1 wherein the synchronization signal is embedded in another signal.

- 5. The apparatus of claim 1 wherein the signal includes data selected from one ormore items including an audio signal and a video signal.

- 6. The apparatus of claim 1 wherein the apparatus is embedded in a device selected from a group comprising a digital signal processor (DSP), a coder-decoder (codec) module, and a CPU.

- 7. The apparatus of claim 2 wherein the source clock is provided by a device selected from a group comprising a DSP, a codec module, and a CPU.

- 8. The apparatus of claim 1 further including a channel filter coupled to the analog to digital converter, the channel filter characterizing a signal transmission environment coupling a sender and a receiver.

9. The apparatus of claim 8 wherein the transmission environment is selected from a group comprising a wired medium and a wireless medium.

- 10. The apparatus of claim 1 wherein the apparatus is initialized by rough estimates for the time delay and sampling skew factor.

- 5 11. The apparatus of claim 10 wherein the initialization is based on autonomous estimation of skew.

- 12. The apparatus of claim 1 wherein the apparatus utilizes MLS to synchronize the signal.

- 13. The apparatus of claim 12 wherein at least two or more audio samples per MLS

symbol are utilized to improve a precision of finding a position of an autocorrelation peak.

- 14. The apparatus of claim 12 wherein to find the position, a curve is fitted corresponding to an autocorrelation main lobe to the audio samples with highest values.

- 15. The apparatus of claim 1 wherein a networking service is utilized to calibrate the receiver clock.

- 15 16. The apparatus of claim 15 wherein the calibrating is performed through running a audio capture process to count a number of samples observed per measurement period.

- 17. The apparatus of claim 15 wherein the networking service is Network Time Protocol (NTP).

- 18. The apparatus of claim 17 wherein the NTP has a clock error per day (CEPD) of about hundreds of milliseconds.

- 19. The apparatus of claim 1 wherein the interpolation module is band-limited.

#### 20. A method comprising:

5

10

providing a predefined synchronization signal;

providing an analog to digital converter to receive the synchronization signal and a receiver clock; and

- providing an interpolation module coupled to the analog to digital converter to receive an output of the analog to digital converter and to continuously estimate and adapt current delay and skew estimates to synchronize a signal.

- 21. The method of claim 20 further including providing a digital to analog converter coupled to the analog to digital converter to receive the synchronization signal and a source clock and to provide its output to the analog to digital converter.

- 22. The method of claim 20 further including synchronizing a plurality of multimedia signals collected from a plurality of sources.

- 23. The method of claim 20 wherein the signal includes data selected from one or more items including an audio signal and a video signal.

- 15 24. The method of claim 20 further including providing a channel filter coupled to the analog to digital converter, the channel filter characterizing a signal transmission environment coupling a sender and a receiver.

- 25. The method of claim 20 wherein the transmission environment is selected from a group comprising a wired medium and a wireless medium.

- 20 26. The method of claim 20 wherein the interpolation module is band-limited.

- 27. An article of manufacture comprising:

a machine readable medium that provides instructions that, if executed by a machine, will cause the machine to perform operations including:

providing a predefined synchronization signal;

providing an analog to digital converter to receive the synchronization signal and a receiver clock; and

providing an interpolation module coupled to the analog to digital converter to receive an output of the analog to digital converter and to continuously estimate and adapt current delay and skew estimates to synchronize a signal.

- 28. The article of claim 27 wherein the operations further include synchronizing a plurality of multimedia signals collected from a plurality of sources.

- 29. A computer system comprising:

5

10

15

a central processing unit (CPU);

a display device coupled to the CPU to display an image;

a memory coupled to the display device to store the image;

an analog to digital converter to receive a predefined synchronization signal and a receiver clock; and

an interpolation module coupled to the analog to digital converter to receive an output of the analog to digital converter and to continuously estimate and adapt current delay and skew estimates to synchronize a signal.

30. The computer system of claim 29 wherein the display device is selected from a group comprising an LCD, a flat panel display, a plasma screen, and a TFT display.

Fig. 1

Fig. 1

-ig. 5

71g. 6

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 H04J3/06

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, PAJ

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                    | Relevant to claim No.                         |

|------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| X          | US 2002/114354 A1 (ARVIV ELL ET AL)<br>22 August 2002 (2002-08-22)                                                    | 1,3-7,<br>10,11,<br>15,19,<br>20,22,          |

| Υ          | the whole document                                                                                                    | 23,25-28<br>2,8,9,<br>12-14,<br>21,24         |

| X          | WO 01/19005 A (BROADCOM CORP ; DENNEY LISA V (US); RABENKO THEODORE F (US)) 15 March 2001 (2001-03-15)                | 1,3-7,<br>10,11,<br>20,22,<br>23,25,<br>27-30 |

|            | page 1, paragraph 16 - paragraph 21 page 8, paragraph 23 - paragraph 26 page 230, paragraph 1 - page 235, paragraph 3 | 27 30                                         |

| X Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier document but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than the priority date claimed | <ul> <li>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combined with one or more other such documents, such combination being obvious to a person skilled in the art.</li> <li>"&amp;" document member of the same patent family</li> </ul> |

| Date of the actual completion of the international search  10 December 2004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Date of mailing of the international search report $27/12/2004$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Name and mailing address of the ISA  European Patent Office, P.B. 5818 Patentlaan 2  NL – 2280 HV Rijswijk  Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,  Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                | Authorized officer  Yvonnet, J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT  Category 2 Citation of document with indication, where appropriate of the relevant passages.  Relevant to claim No. |                                                                                                                                                               |                       |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Category °                                                                                                                                                                | Citation of document, with indication, where appropriate, of the relevant passages                                                                            | Relevant to claim No. |  |  |  |

| Υ                                                                                                                                                                         | US 2003/086515 A1 (NGOC THO L ET AL)<br>8 May 2003 (2003-05-08)<br>figures 29-32,39,90                                                                        | 2,8,9,<br>21,24       |  |  |  |

| Υ                                                                                                                                                                         | WO 02/30021 A (MUSHKIN MORDECHAI ; ITRAN COMM LTD (IL); RAPHAELI DAN (IL)) 11 April 2002 (2002-04-11) page 15, paragraph 11 - page 16, paragraph 19; figure 5 | 12-14                 |  |  |  |

| A                                                                                                                                                                         | US 2002/056133 A1 (FUNG DANNY ET AL) 9 May 2002 (2002-05-09)                                                                                                  |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

|                                                                                                                                                                           |                                                                                                                                                               |                       |  |  |  |

### INTERNATIONAL SEARCH REPORT

Information on patent family members

### International Application No PCT/US2004/025475

| Patent document cited in search report | Publication date | Patent family<br>member(s)                                                                                                                                                                                                                             | Publication<br>date                                                                                                                                                                                                          |

|----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| US 2002114354 A                        | 22-08-2002       | WO 02071666 A1                                                                                                                                                                                                                                         | 12-09-2002                                                                                                                                                                                                                   |

| WO 0119005 A                           | 15-03-2001       | AU 1187801 A<br>EP 1214807 A1<br>WO 0119005 A1<br>US 6819682 B1                                                                                                                                                                                        | 10-04-2001<br>19-06-2002<br>15-03-2001<br>16-11-2004                                                                                                                                                                         |

| US 2003086515 A                        | 1 08-05-2003     | US 2003016770 A1 US 6553085 B1 US 2001038674 A1 AU 3748900 A AU 4799000 A CA 2370040 A1 CA 2370634 A1 EP 1177618 A1 EP 1173949 A1 WO 0062415 A1 WO 0062470 A1 US 2003128781 A1 US 2002181633 A1 AU 8684098 A CA 2302466 A1 EP 1021884 A2 WO 9907077 A2 | 23-01-2003<br>22-04-2003<br>08-11-2001<br>14-11-2000<br>19-10-2000<br>19-10-2000<br>06-02-2002<br>23-01-2002<br>19-10-2000<br>19-10-2000<br>10-07-2003<br>05-12-2002<br>22-02-1999<br>11-02-1999<br>26-07-2000<br>11-02-1999 |

| WO 0230021 A                           | 11-04-2002       | AU 1086502 A<br>WO 0230021 A2                                                                                                                                                                                                                          | 15-04-2002<br>11-04-2002                                                                                                                                                                                                     |

| US 2002056133 A                        | 1 09-05-2002     | AU 4725701 A AU 5079701 A WO 0167744 A2 WO 0167745 A2 US 2001047325 A1 US 2001055354 A1                                                                                                                                                                | 17-09-2001<br>17-09-2001<br>13-09-2001<br>13-09-2001<br>29-11-2001<br>27-12-2001                                                                                                                                             |