## (12)发明专利

(10)授权公告号 CN 106408502 B

(45)授权公告日 2019.12.31

(21)申请号 201610990011.8

(51)Int.CI.

(22)申请日 2011.07.07

G06T 1/00(2006.01)

(65)同一申请的已公布的文献号

G06T 1/20(2006.01)

申请公布号 CN 106408502 A

H04N 5/232(2006.01)

(43)申请公布日 2017.02.15

H04N 5/335(2011.01)

(30)优先权数据

H04N 9/67(2006.01)

61/362,247 2010.07.07 US

(56)对比文件

12/959,281 2010.12.02 US

CN 101529473 A, 2009.09.09,

(62)分案原申请数据

CN 101425140 A, 2009.05.06,

201180042998.6 2011.07.07

CN 101540000 A, 2009.09.23,

(73)专利权人 快图有限公司

CN 101587189 A, 2009.11.25,

地址 爱尔兰戈尔韦

Griselda Saldana等. Real Time FPGA-

(72)发明人 P·比吉奥伊 C·弗洛雷亚

based Architecture for Video

P·科尔科朗

Applications.《Real Time FPGA-based

(74)专利代理机构 北京市金杜律师事务所

Architecture for Video Applications,

11256

Reconfigurable Computing and FPGA's,

代理人 王茂华 庞淑敏

2006. ReConFig 2006. IEEE International

Conference》.2006,

审查员 王璇

权利要求书3页 说明书13页 附图8页

## (54)发明名称

实时视频帧预处理硬件

## (57)摘要

一种动态可重配置异质脉动阵列被配置成处理第一图像帧，从该图像帧产生图像处理基元，以及在存储器存储装置中存储该基元和相应图像帧。确定图像帧的特性。基于该特性，将该阵列重配置成处理后续图像帧。

1. 一种用于图像处理的装置,所述装置包括:

一个或多个硬件处理器;

一个或多个存储器;

一个或多个硬件模块,所述硬件模块被配置为:

在动态可重配置异质脉动阵列中处理第一图像帧,以从所述第一图像帧产生多个图像处理基元,

其中所述多个图像处理基元包括至少一个图像图;

将所述多个图像处理基元和所述第一图像帧存储在存储器存储装置中;

至少部分基于所述多个图像处理基元,确定所述第一图像帧的一个或多个特性;

基于针对所述第一图像帧确定的所述一个或多个特性,重配置所述动态可重配置异质脉动阵列;以及

使用重配置的所述动态可重配置异质脉动阵列,基于所述一个或多个特性来处理第二图像帧。

2. 根据权利要求1所述的装置,其中所述多个图像处理基元中的图像处理基元是通过识别所述第一图像帧的子区域以及从所述子区域产生该图像处理基元而生成的。

3. 根据权利要求1所述的装置,其中所述第一图像帧和所述第二图像帧是视频帧。

4. 根据权利要求1所述的装置,其中所述多个图处理基元包括经过处理的图像图或者其他经过处理的硬件模块数据或者其两者。

5. 根据权利要求1所述的装置,其中所述装置还被配置为向存储器提供格式化的图像数据。

6. 根据权利要求4所述的装置,其中所述经过处理的图像图包括阈值图,或者积分图像图,或者其两者。

7. 根据权利要求1所述的装置,其中所述多个图像处理基元包括区域基元,或者帧数据基元,或者其两者。

8. 根据权利要求1所述的装置,其中所述装置还被配置接收来自存储器的格式化的图像数据。

9. 根据权利要求1所述的装置,其中所述装置还包括译码模块,被配置接收经过处理的图像数据,以及向存储器提供或者从存储器接收压缩的图像或者视频数据或者其两者。

10. 根据权利要求9所述的装置,其中所述译码模块还被配置为输出所选择的图像数据或者视频数据或者其两者的子集,以进行显示。

11. 根据权利要求1所述的装置,其中所述装置被配置为在单个时钟周期内处理图像数据。

12. 根据权利要求1所述的装置,其中所述装置还被配置为对硬件模块或者IPP模块或者其两者进行编程。

13. 一种使用动态可重配置异质脉动阵列的图像处理的方法,包括:

在动态可重配置异质脉动阵列中,处理第一图像帧,以从所述第一图像帧产生多个图像处理基元,

其中所述多个图像处理基元包括至少一个图像图;

将所述多个图像处理基元和所述第一图像帧存储在存储器存储装置中;

至少部分基于所述多个图像处理基元，确定所述第一图像帧的一个或多个特性；

基于针对所述第一图像帧确定的所述一个或多个特性，重配置所述动态可重配置异质脉动阵列；以及

使用重配置的所述动态异质脉动阵列，基于所述一个或多个特性来处理第二图像帧；其中所述方法是使用一个或多个计算设备执行的。

14. 根据权利要求13所述的方法，其中所述多个图像处理基元中的图像处理基元是通过识别所述第一图像帧的子区域以及从所述子区域产生该图像处理基元而生成的。

15. 根据权利要求13所述的方法，其中所述第一图像帧和所述第二图像帧是视频帧。

16. 根据权利要求13所述的方法，其中所述多个图处理基元包括经过处理的图像图或者其他经过处理的硬件模块数据或者其两者。

17. 根据权利要求13所述的方法，还包括从基于硬件的图像处理模块向存储器提供格式化的图像数据。

18. 根据权利要求17所述的方法，还包括处理图像图，其包括阈值图，或者积分图像图，或者其两者。

19. 根据权利要求13所述的方法，其中所述多个图像处理基元包括区域基元，或者帧数据基元，或者其两者。

20. 根据权利要求13所述的方法，还包括接收来自存储器的格式化的图像数据。

21. 根据权利要求13所述的方法，还包括将经过处理的图像数据传送到译码模块，从所述译码模块或者朝所述译码模块通信传送压缩的图像或者视频数据或者其两者。

22. 根据权利要求13所述的方法，还包括输出所选择的图像数据或者视频数据或者其两者的子集，以进行显示。

23. 根据权利要求13所述的方法，还包括利用基于硬件的图像处理模块在单个时钟周期内处理图像数据。

24. 根据权利要求13所述的方法，其中还包括对基于硬件的图像处理模块进行编程。

25. 一种用于图像处理的装置，所述装置包括：

一个或多个处理器；

一个或多个存储器，其上存储有指令，当所述指令被所述一个或更多处理器执行时，致使所述一个或多个处理器执行：

在动态可重配置异质脉动阵列中处理第一图像帧，以从所述第一图像帧产生多个图像处理基元，

其中所述多个图像处理基元包括至少一个图像图；

将所述多个图像处理基元和所述第一图像帧存储在存储器存储装置中；

至少部分基于所述多个图像处理基元，确定所述第一图像帧的一个或多个特性；

基于针对所述第一图像帧确定的所述一个或多个特性，重配置所述动态可重配置异质脉动阵列；以及

使用重配置的所述动态可重配置异质脉动阵列，基于所述一个或多个特性来处理第二图像帧。

26. 根据权利要求25所述的装置，其中所述多个图处理基元包括经过处理的图像图或者其他经过处理的硬件模块数据或者其两者。

27. 根据权利要求25所述的装置,其中所述一个或多个存储器其上存储有附加指令,当所述附加指令被所述一个或更多处理器执行时,致使所述一个或多个处理器执行向存储器提供格式化的图像数据。

28. 根据权利要求25所述的装置,其中所述一个或多个存储器其上存储有附加指令,当所述附加指令被所述一个或更多处理器执行时,致使所述处理器执行:处理图像图,所述图像图包括阈值图,或者积分图像图,或者其两者。

29. 根据权利要求25所述的装置,其中所述多个图像处理基元包括区域基元,或者帧数据基元,或者其两者。

30. 根据权利要求25所述的装置,其中所述一个或多个存储器其上存储有附加指令,当所述附加指令被所述一个或更多处理器执行时,致使所述处理器执行:接收并处理来自存储器的格式化的图像数据。

31. 根据权利要求25所述的装置,其中所述一个或多个存储器其上存储有附加指令,当所述附加指令被所述一个或更多处理器执行时,致使所述处理器执行:将经过处理的图像数据传送到译码模块,从所述译码模块或者朝所述译码模块通信传送压缩的图像或者视频数据或者其两者。

32. 根据权利要求25所述的装置,其中所述一个或多个存储器其上存储有附加指令,当所述附加指令被所述一个或更多处理器执行时,致使所述处理器执行:输出所选择的图像数据或者视频数据或者其两者的子集,以进行显示。

33. 根据权利要求25所述的装置,其中所述一个或多个存储器其上存储有附加指令,当所述附加指令被所述一个或更多处理器执行时,致使所述处理器执行:利用基于硬件的图像处理模块,在单个时钟周期内处理图像数据。

34. 根据权利要求33所述的装置,其中所述基于硬件的图像处理模块是可编程的。

## 实时视频帧预处理硬件

[0001] 本申请是申请号为201180042998.6、发明名称为“实时视频帧预处理硬件”的发明专利申请的分案申请。

[0002] 优先权

[0003] 本申请权利要求于2010年12月2日提交的美国专利申请序列号12/959,281和2010年7月7日提交的美国临时专利申请序列号61/362,247的优先权。

### 背景技术

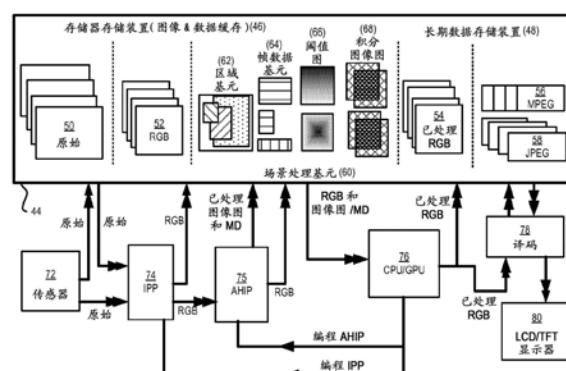

[0004] 在通过数字成像系统内的图像传感器获取图像之后，典型地在设备上显示或存储之前，对图像进行处理。图1中示出了典型的图像处理链或图像处理管线或IPP。图1中示出的示例IPP包括曝光和白平衡模块2、去马赛克块6、颜色校正块6、伽玛校正块8、颜色转换块10和下采样模块12。

[0005] 当希望实现实时视频成像系统时，通常在使用这种IIPP时存在明显的约束，因为图像数据典型地在IPP的每一级上从存储器读取且然后在一些操作之后被写回。对于HD视频，存储器带宽经受巨大挑战。因而，希望在视频获取设备的硬件实施例中直接实现IPP的元件。这将是有利的：IPP的元件避免了在每一级处理之后向存储器写入图像数据以及读回用于每个后续IPP操作的数据的挑战。然而，它暗示着在IPP的每一级应用的方法将具有较差适应性，因为整个IPP链将在从单个图像帧输入数据之前配置。

[0006] 与用在图1的一些示例块所示出的基本IPP可以提供的图像和场景分析相比，现代数字静态照相机(DSC)实现了更复杂的图像和场景分析。具体而言，图像获取设备可以检测且跟踪图像场景中的面部区域(见美国专利7,620,218、7,460,695、7,403,643、7,466,866和7,315,631以及美国公布的申请序列号2009/0263022、2010/0026833、2008/0013798、2009/0080713、2009/0196466和2009/0303342以及美国序列号12/374,040和12/572,930，它们全都转让给相同的受让人且此处通过引用而结合于此)，且这些设备可以分析和检测这些区域中的瑕疵和缺陷并动态地(on the fly)校正这些疵点(见上面的专利以及此处通过引用而结合的美国专利7,565,030和美国专利公布申请序列号2009/0179998)。诸如灰尘瑕疵或“小瑕疵”之类的全局缺陷可以被检测和校正(例如见美国专利序列号12/710,271和12/558,227以及美国专利7,206,461、7,702,236、7,295,233和7,551,800，它们全都转让给相同的受让人且此处通过引用结合于此)。可以应用面部增强。可以确定并补偿图像模糊和图像移动、平移和旋转(例如见此处通过引用而结合的7,660,478和美国专利公布申请序列号2009/0303343、2007/0296833、2008/0309769、2008/0231713和2007/0269108以及W0/2008/131438)。面部区域可以被识别且与已知人相关联(例如见此处通过引用而结合的美国专利7,567,068、7,515,740和7,715,597和US2010/0066822、US2008/0219517和US2009/0238419以及美国专利序列号12/437,464)。所有这些技术和其他技术(例如见美国专利6,407,777、7,587,085、7,599,577、7,469,071、7,336,821、7,606,417和2009/0273685、2007/0201725、2008/0292193、2008/0175481、2008/0309770、2009/0167893、2009/0080796、2009/0189998、2009/0189997、2009/0185753、2009/0244296、2009/0190803、2009/0179999

以及美国专利申请序列号12/636,647,它们全都转让给相同的受让人且此处通过引用而结合于此)依赖于对图像场景的分析。典型地,这涉及从存储器存储装置(memory store)读取图像数据块且接着是该数据的各种处理阶段。中间数据结构可以临时存储在图像存储装置中以方便每个场景分析算法。在一些情况中,这些数据专用于单个算法,而在其他情况中,数据结构可以在若干不同场景分析算法上保持。在这些情况中,图像数据在图像存储器存储装置和CPU之间移动以执行各种图像处理操作。在应用多个算法的情况下,图像数据典型地被读取若干次,以针对每个图像执行不同的图像和场景处理操作。

[0007] 对于大多数上述技术而言,分析可以涉及先前图像流,该先前图像流是通过大多数数码相机捕获的相对低分辨率的流且用于在照相机显示器上提供实时显示。因而,为了适当地分析主图像场景,使得基本相同的场景的至少两个图像可用是有用的。在一个或多个先前图像也被存储的情况下,在许多时候还典型地存在与主获取(全分辨率)图像的组合的读取。另外,处理可能涉及临时存储预览图像的未采样拷贝或主获取图像的下采样拷贝,以便于各种场景分析算法。

[0008] 在数字照相机内,图像典型地被分别获取且在用于场景分析的图像获取和各个图像的后处理之间有典型地一秒或更多秒量级的基本时间间隔可用。即使在时间十分靠近地获取多个图像的情况下,例如,在专业DSC的突发模式中,由于受限的存储器,可以获取有限数目的图像。再者,这些图像不能在突发获取期间被处理,而是通常一直等待直到它在可以实现更复杂的基于场景的处理之前完成。

[0009] 在现代视频设备中,数据通常以30fps或更快的帧速率处理,且由于存储器约束,数据被数字压缩且被或快或慢地立即写入到长期存储器存储装置。再者,在DSC的情况下,低分辨率预览流一般不可用。最后,处理全HD视频流的需求暗示着存储器带宽在这种设备中是挑战性的。

[0010] 为了获得诸如目前在用于HD视频获取设备的DSC内可用的现代场景分析技术的益处,我们因而可以意识到若干关键挑战。首先,难以在视频帧获取之间可用的时间内存储和执行关于完整HD的复杂场景分析。这并不简单地是CPU功率的问题,而更重要的可能是数据带宽的问题。完整HD图像的大小暗示着简单地通过IPP移动这种图像且移动到长期存储装置上的视频压缩单元是十分挑战性的。尽管通过向IPP添加硬件可以实现一些有限的场景分析,但是这将很可能涉及在开始视频流的实时获取之前固定的很多设置和配置,这使得它们将并不响应于进行的场景分析而动态调适。

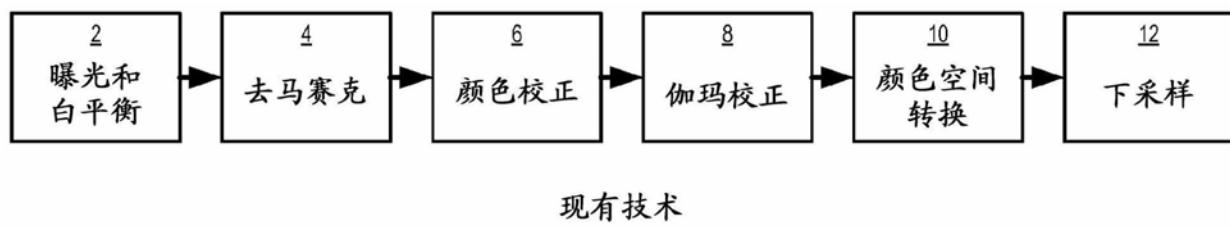

[0011] 其次,没有余地来在场景分析算法之间共享图像处理数据基元(primitive)而不向IPP引入极大的共享存储器缓冲器。这将导致不合理且有效模仿单个IC内(图2中示出)的现有技术的硬件设计需求。图2示出用于实现IPP和软件中的其他高级功能的常规硬件。存储器14被示出为包括图像和数据缓存器16以及长期数据存储装置18。缓存器16可以存储原始数据20、RGB格式化数据22和RGB处理数据24,而长期数据存储装置18可以保存MPEG图像26和/或JPEG图像28。传感器32向存储器14和IPP 34通信传送原始数据。IPP 34还从存储器14接收数据。IPP 34还向存储器14、16提供RGB数据22。RGB数据22、24也被CPU 36检索,该CPU 36向存储器14提供已处理RGB数据24,且向译码模块38提供RGB数据22。译码模块38向存储器14、18提供数据且从存储器14、18检索数据。译码模块还提供例如将在LCD/TFT显示器40上显示的数据。

[0012] 由于各种实际原因,这不提供最佳图像处理机制。备选方案是针对每个场景分析算法具有单独的硬件实施,但这还将导致极大的硬件尺寸,因为每个算法将缓冲完整图像帧以执行完整场景分析。

[0013] 在这些宽区域中的每一个中存在很多附加工程细微区别,但是可以认识到宽广范围的挑战,其中当前场景分析技术和所得的图像益处并未明显地应用于使用当前现有技术的实时视频。因此,下面提供一组有利的实施例。

## 附图说明

[0014] 图1示出常规图像处理管线(IPP)。

[0015] 图2示出用于实现IPP和软件中的其他高级功能的常规硬件。

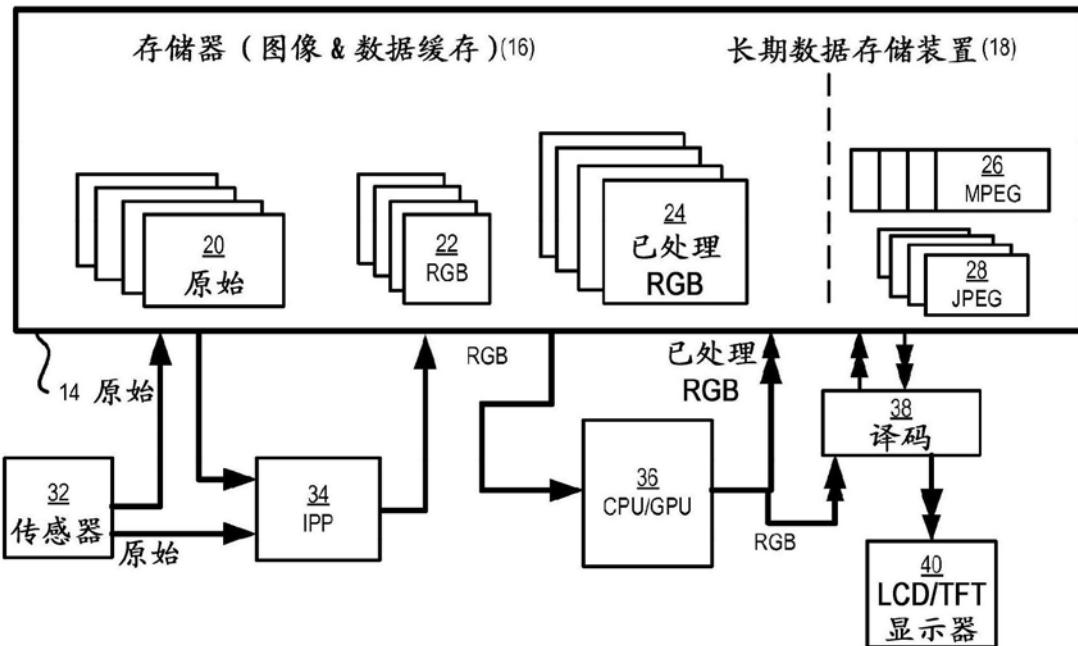

[0016] 图3示出同质脉动阵列架构。

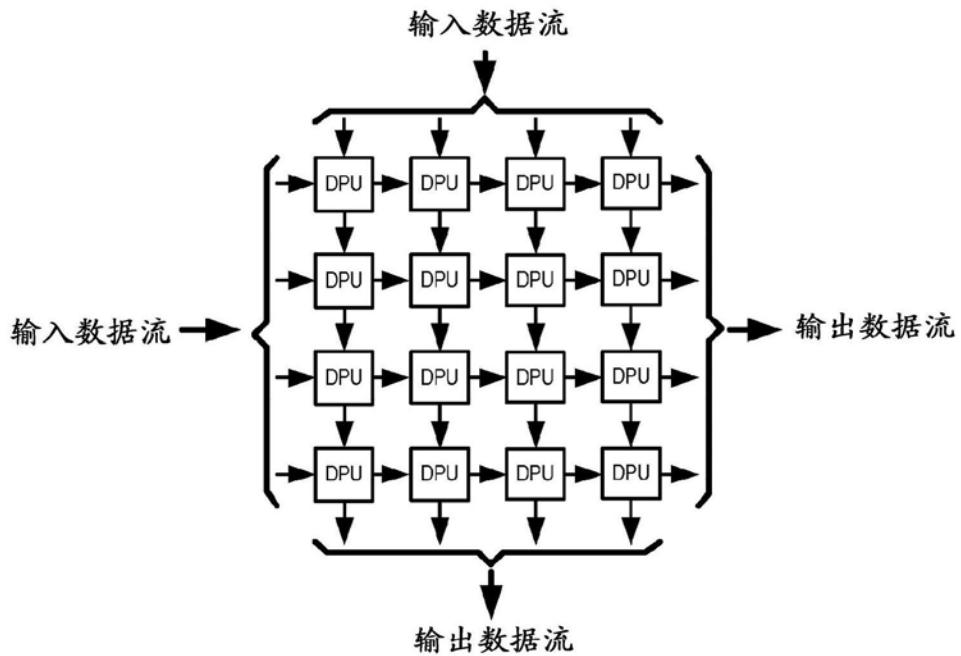

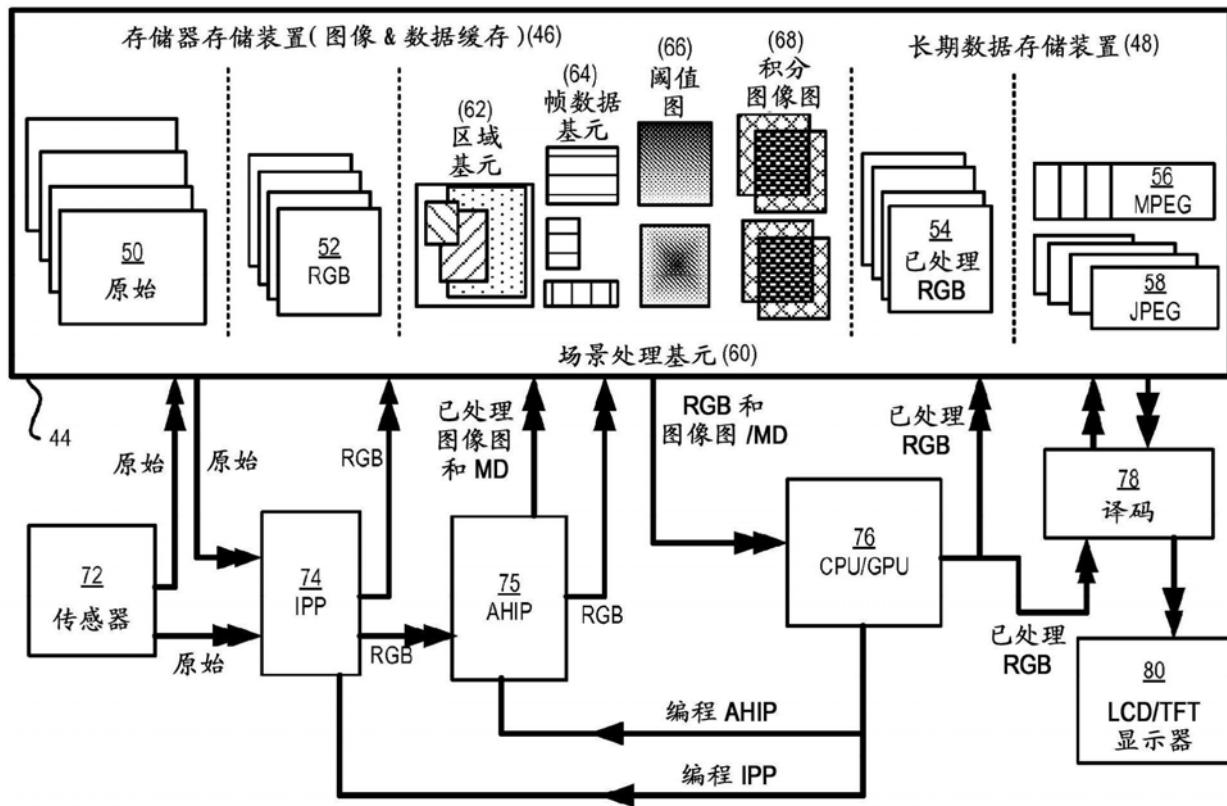

[0017] 图4示出根据某些实施例具有用于图像处理的高级硬件或包括穿过(pass-through)特性的AHIP的IPP硬件。

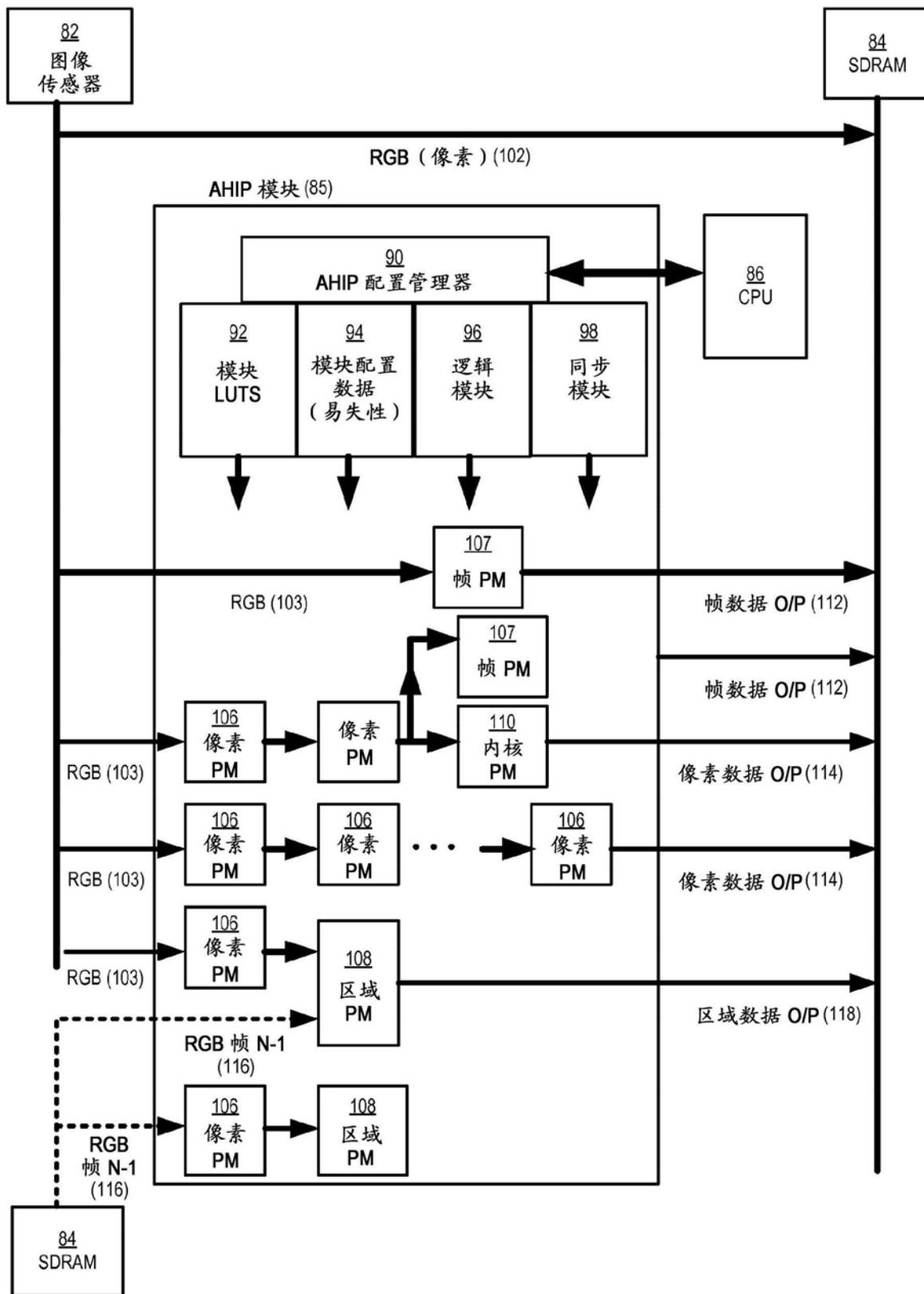

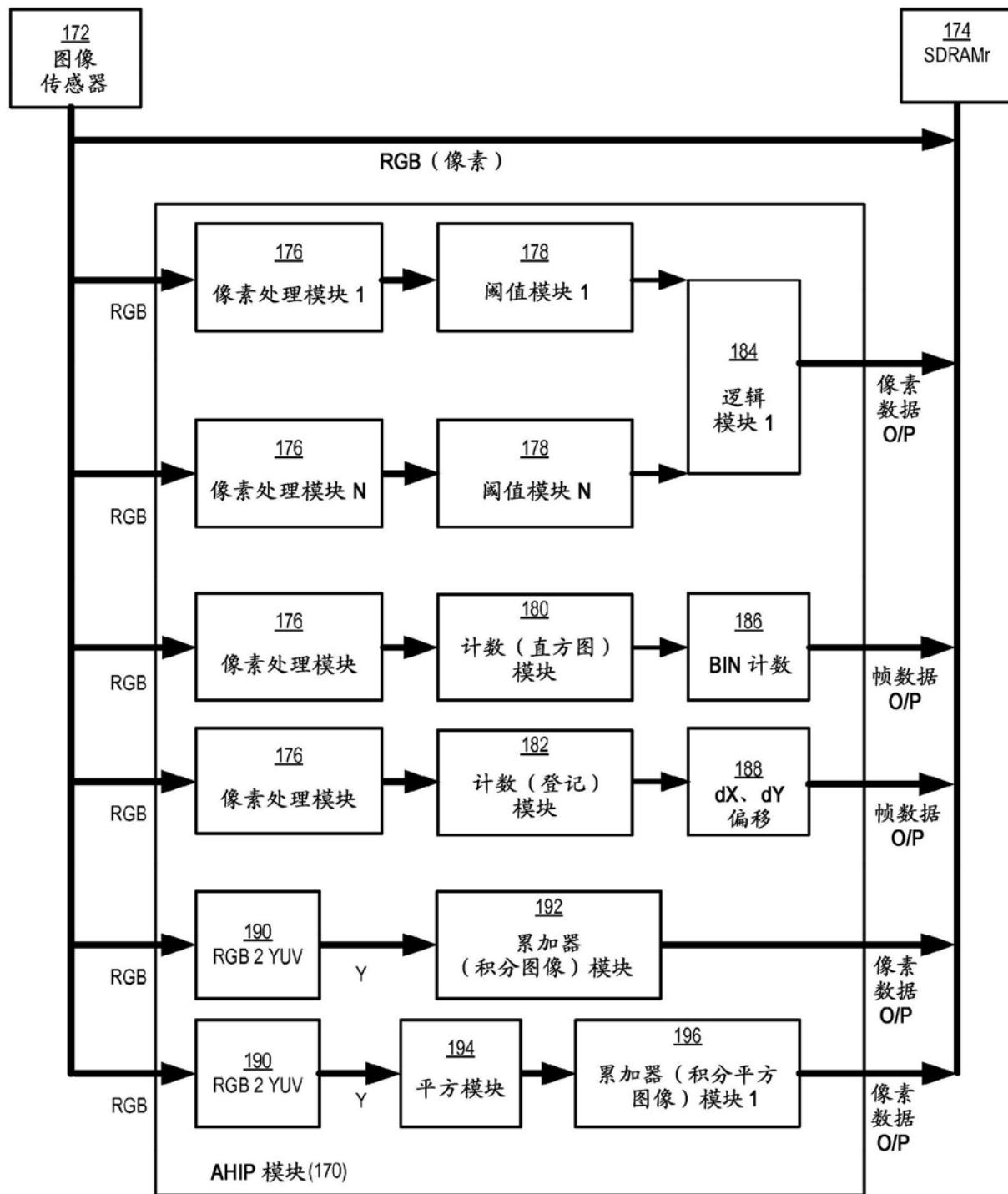

[0018] 图5示出根据某些实施例的AHIP模块,该AHIP模块包括布置到用于各种图像处理基元的处理链中的若干通用处理模块。

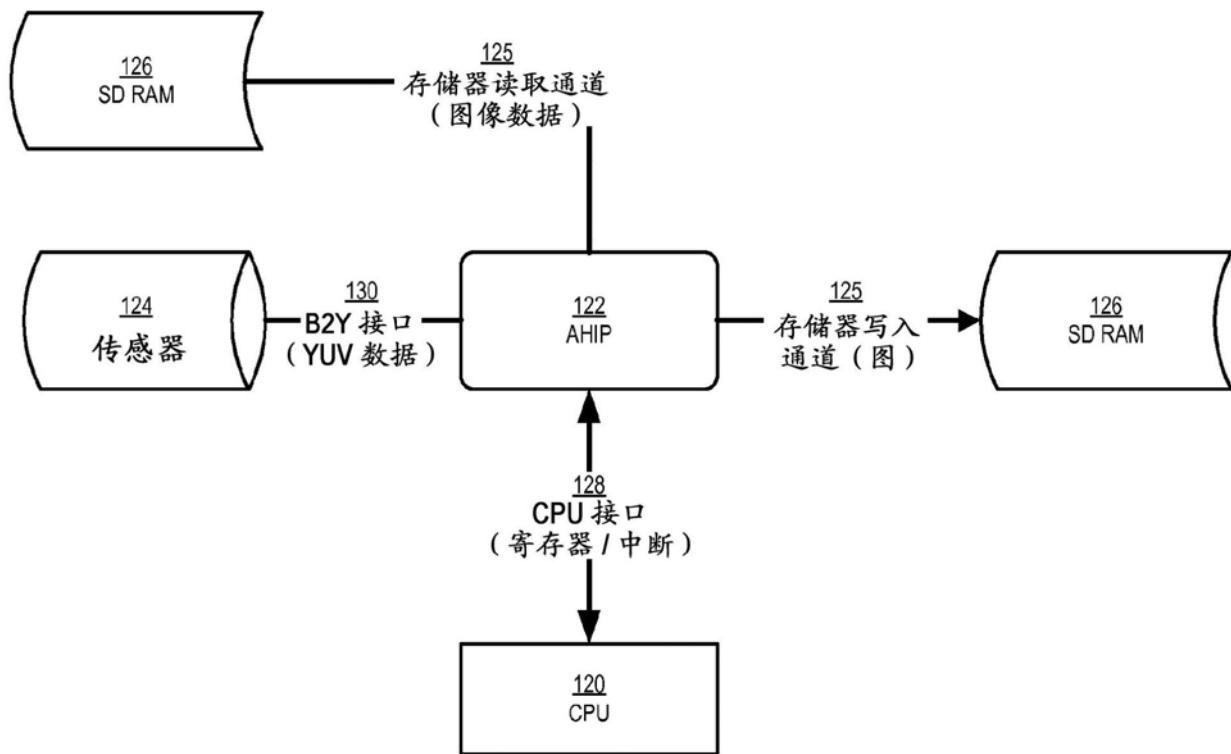

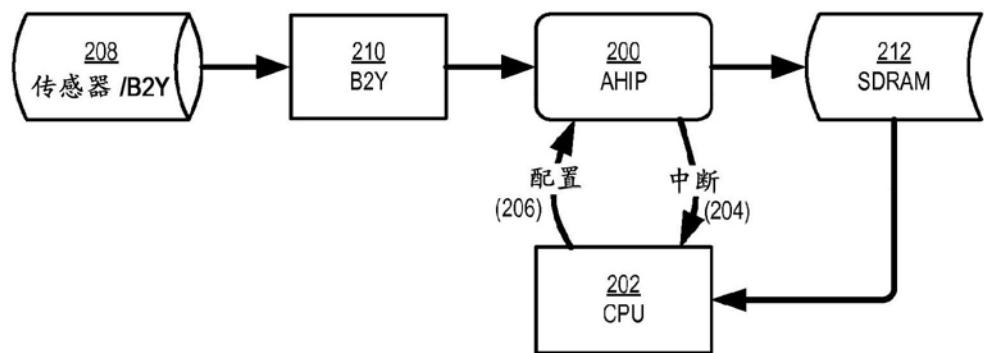

[0019] 图6示出根据某些实施例在主CPU、硬件模块、图像传感器和SDRAM读/写通道之间的相互关系。

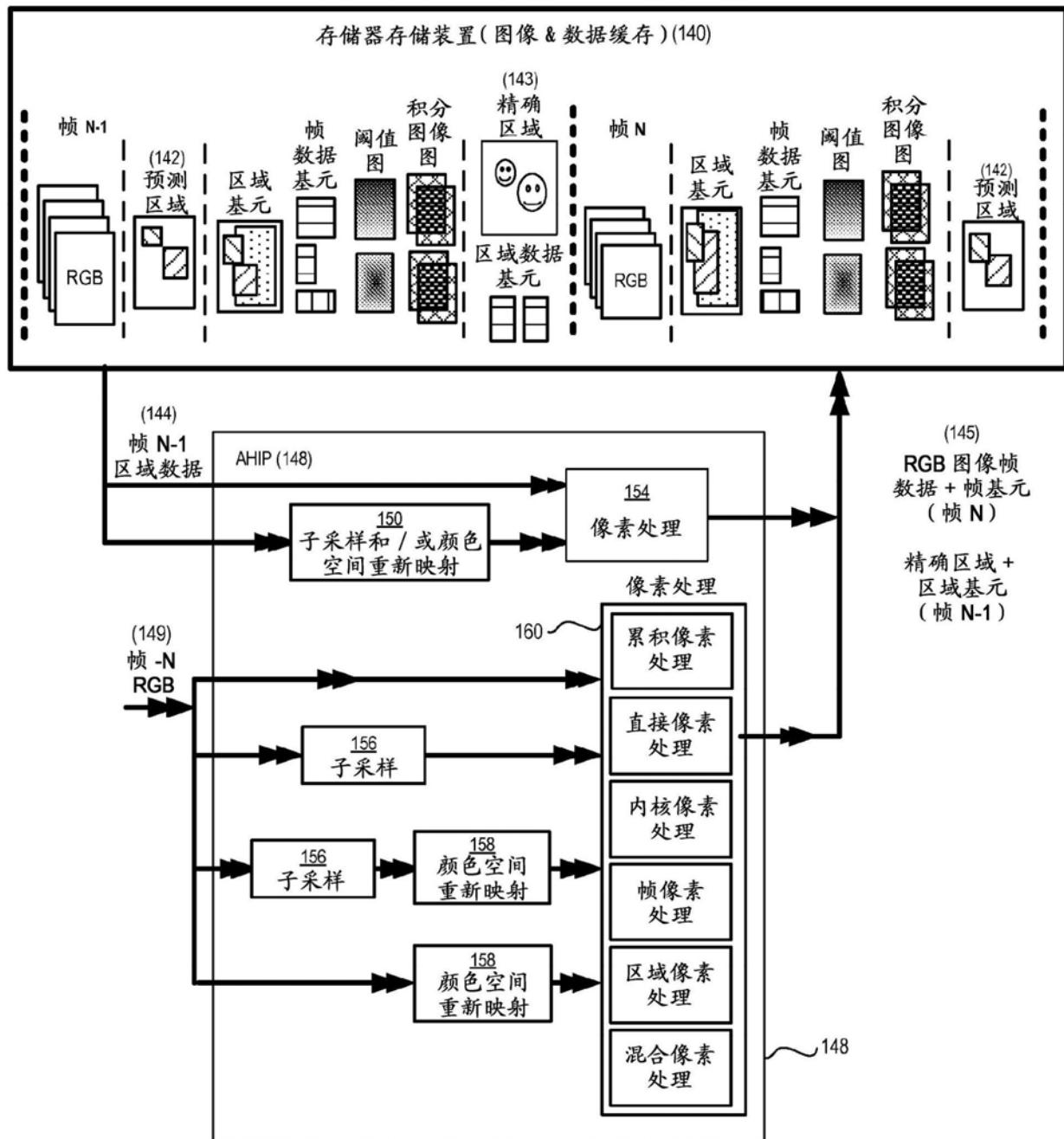

[0020] 图7示出根据某些实施例包括图像和数据缓存的存储器存储装置和AHIP模块之间的相互关系。

[0021] 图8示出根据某些实施例的颜色阈值处理模块。

[0022] 图9示出根据某些实施例的原始图像和具有16个阈值(4位)的肤色图(skin-color map)。

[0023] 图10示出根据某些实施例的AHIP模块,其输出颜色空间转换、颜色阈值处理、帧-帧配准、积分图像和/或积分平方图像基元和/或图像帧直方图数据。

[0024] 图11示出根据某些实施例在AHIP模块和其他图像处理组件之间的处理关系。

## 具体实施方式

[0025] 下面描述包括硬件子系统的实施例,该硬件子系统从连续地逐个像素输入的具有延时的图像帧而产生实时推导的图像处理基元范围,所述延时明显小于与获取完整图像帧相关的时间。这些基元在图像帧已获取之后极快地可用或甚至立即可用,且可以用于在获取下一图像帧时进一步处理该图像。

[0026] 另外,依次从先前图像帧的处理确定的数据可以变得可用,以用于与从当前图像帧推导的图像处理基元组合。这通过帧场景处理实现了细节帧而无需单独捕获图像的低分辨率预览流(尽管这在某些实施例中这可以可选地使用)。

[0027] 还描述了在每个时钟周期输入使用一个像素操作和/或产生提供关于当前图像/视频帧的有用知识的很多不同类型的图像处理基元的实施例。每个基元通过包括一个或多个像素处理块或模块的处理链产生。这些块或模块通过可以动态切换的多个内部数据总线链接在一起。在某些不那么复杂的实施例中,模块可能具有直接链接的数据路径,不过主输入模块可以从图像传感器/IPP来共享公共输入数据路径。多个模块可以共享相同的输入数

据。而且,各个处理块的输出可以逻辑地组合。来自多个处理链的各个输出典型地在被输出到外部存储器 (SDRAM) 之前组合到单个数据字中,因为这有利于存储器和外部存储器总线的优化使用。因为处理链之间处理时间的差异,同步模块与逻辑电路集成以确保输出数据的正确对准。

[0028] 在很多更加可应用的图像处理技术之中,产生的图像基元可以有利地用于促进一系列图像处理操作的性能,所述图像处理操作包括红眼检测、面部检测和识别、面部美化、帧-帧图像重合以及用于创建全景图像的多帧图像接合。而且,这些基元的可用性极大地简化了场景分析和处理算法的实现。这尤其可以有利地减小从内存存储装置 (memory store) 读取和写入完整图像帧以用于CPU或GPU上的后续处理的趋势。在大多数情况下,(多个) 相关图像基元和主图像仅被读取一次以使用特定算法分析和/或增强图像。还可以与主要获取图像的单次读取一起从多个算法加载基元,以基于单个图像读取执行这多个算法。这极大地减小了用于处理视频流的存储器带宽。在单独的读/写总线可用的情况下,还可以在主CPU/GPU上处理一个图像帧,同时在通过IPP和AHIP模块获取和预处理第二图像帧。

[0029] 而且,该系统配置使得从图像帧的分析推导的数据被CPU/GPU处理,以反馈回IPP或AHIP模块,以便调适后续图像帧的预处理。通过IPP应用的全局图像处理和通过AHIP应用的场景专用图像处理二者的详细调适实现了视频获取设备的更快或更具响应性的性能。在例如基于面部区域和皮肤的相关色图的分析而改变发光条件的情况下,这进而允许视频获取的更快的调适。根据某些实施例,这种技术现在可以有利地应用于视频获取。

[0030] 就这方面而言,在某些实施例中也可以使用帧计数器和相关逻辑。在每个帧处理周期的结尾,可以重配置内部像素处理链。这可能涉及加载新LUT、改变各个像素处理块的处理参数或在某些情况中重配置处理链中块的顺序或逻辑组合。在某些实施例中,模块被选择或者被旁路。在更复杂的实施例中,数据处理模块在一个或多个内部数据总线上共享I/O端口。在某些实施例中,可以使用双缓冲I/O来实现几乎同时的对模块的读/写操作。

[0031] 根据某些实施例中,动态可重配置异质脉动阵列被配置成处理第一图像帧,且从图像帧产生图像处理基元,且在存储器存储设备中存储基元和相应图像帧。基于图像帧的确定特性,动态可重配置异质脉动阵列可重配置为处理后续图像帧。

[0032] 图像帧的特性的确定可以在脉动阵列外部执行。至少一个特性的确定可以基于对图像帧的至少一部分的处理以及基于图像处理基元其中至少一个。

[0033] 根据某些实施例的图像获取和处理设备包括处理器、用于获取数字图像帧的透镜和图像传感器以及根据此处实施例其中任意一个描述而配置的动态可重配置异质结脉动阵列其中任意一个。

[0034] 根据某些实施例使用动态可重配置异质结脉动阵列的图像处理的方法包括获取和处理第一图像帧。从图像帧产生图像处理基元。将所述基元和相应图像帧存储在存储器存储装置中。确定图像帧的至少一个特性,且基于该至少一个特性,该方法包括重配置阵列以处理后续图像帧。

[0035] 该至少一个特性的确定可以在脉动阵列的外部执行。该至少一个特性的确定可以基于处理图像帧的至少一部分以及图像处理基元其中至少一个。

[0036] 根据某些实施例,提供又一数字图像获取和处理设备。该设备包括用于获取数字图像的透镜和图像传感器。该设备的图像处理管线 (IPP) 模块被配置成接收图像帧的原始

图像数据且向存储器和配置成执行图像处理的硬件模块分发相应的格式化图像数据。硬件模块从IPP模块接收图像帧的格式化图像数据且向存储器提供场景处理基元。处理单元被配置成基于从存储器接收且通过硬件模块提供的场景处理基元处理后续的图像帧。

[0037] 场景处理基元可以包括已处理图像图 (image map) 或其他已处理硬件模块数据, 或二者。硬件模块还可以配置成向存储器提供格式化图像数据。已处理图像TU可以包括阈值图 (threshold map) 或积分图像图 (integral image maps) 或二者。场景处理基元可以包括区域基元或帧数据基元, 或二者。处理单元还可以接收来自存储器的格式化图像数据。

[0038] 此设备可以包括译码模块, 该译码模块配置成从处理单元接收已处理图像数据, 且向存储器提供或从其接收压缩图像或视频数据或二者。译码模块可以配置成向显示器输出图像数据或视频数据或二者的所选子集。

[0039] 硬件模块可以配置成在单个时钟周期内处理图像数据。处理单元还可以配置成编程硬件模块或IPP模块或二者。

[0040] 根据某些实施例提供了获取和处理数字图像的另一方法, 其包括: 获取数字图像以及接收图像帧的原始图像数据且向存储器和基于硬件的图像处理模块分发相应的格式化图像数据。该方法还包括在基于硬件的图像处理模块处接收图像帧的格式化图像数据且向存储器提供场景处理基元, 以及在存储器中存储由基于硬件的图像处理模块所提供的场景处理基元。基于从存储器接收且通过基于硬件的图像处理模块提供的场景处理基元来处理后续图像帧。

[0041] 场景处理基元可以包括已处理图像图或其他已处理硬件模块数据或二者。格式化图像数据可以从基元硬件的图像处理模块提供到存储器。可以对包括阈值图或积分图像图或二者的图像图进行处理。场景处理基元可以包括区域基元或帧数据基元或二者。格式化图像数据可以从存储器接收。已处理图像数据可以被传输到译码模块, 且压缩图像或视频数据可以被通信传送到译码模块或从译码模块进行通信传送或其组合。图像数据或视频数据的所选子集或两者可以被输出到显示器。可以使用基于硬件的图像处理模块, 在单个时钟周期内处理图像数据。基于硬件的图像处理模块可以是可编程和/或可重配置的。

[0042] 基于硬件的图像处理模块被进一步提供以用于在图像获取和处理设备中操作, 该图像获取和处理设备获取原始图像数据且向基于硬件的图像处理模块分发给相应的格式化数据, 该基于硬件的图像处理模块配置成基于存储在存储器中的格式化图像数据产生且向存储器提供场景处理基元, 以用于基于从存储器接收且通过基于硬件的图像处理模块提供的场景处理基元来理后续图像帧。

[0043] 场景处理基元可以包括已处理图像图或其他已处理硬件模块数据或二者。该模块可以配置成向存储器提供格式化图像数据, 和/或处理包括阈值图和积分图像图或二者的图像图。场景处理基元可以包括区域基元或帧数据基元或二者。该模块可以配置成接收并处理来自存储器的格式化数据, 和/或向译码模块发射已处理图像数据, 且向译码模块或从译码模块通信传输压缩图像或视频数据或其结合。该模块还可以配置成向显示器输出图像数据或视频数据或二者的所选子集, 和/或使用基于硬件的图像处理模块在单个时钟周期内处理图像数据。该模块可以是可编程和/或可重配置的。

[0044] 根据某些实施例, 将动态可重配置异质脉动阵列被配置为处理第一图像数据; 从所述图像帧产生多个图像处理基元; 识别所述图像帧的至少一个子区域的位置且从所述子

区域产生至少一个图像处理基元;以及将所述基元与图像帧和子区域位置一起存储在存储器存储装置中。该动态可重配置异质脉动阵列可重配置为基于图像帧或子区域或二者的一个或多个确定的特性来处理后续图像帧。

[0045] 至少一个特性的确定可以在脉动阵列外部执行。至少一个特性的确定可以基于对图像帧的至少一部分的处理以及图像处理基元其中至少一个。

[0046] 根据某些实施例的图像获取和处理设备包括处理器;用于获取数字图像帧的透镜和图像传感器;以及根据此处描述的实施例其中任意一个而配置的动态可重配置异质结脉动阵列。

[0047] 还提供了一种使用动态可重配置异质脉动阵列进行图像处理的方法,该方法包括:获取和处理第一图像帧;从所述图像帧产生多个图像处理基元;识别所述图像帧的至少一个子区域的位置且从所述子区域产生至少一个图像处理基元;将所述基元与图像帧和子区域位置一起存储在存储器存储装置中,确定图像帧或子区域或二者的至少一个特性;以及基于所述特性,重配置所述阵列以处理后续图像帧。

[0048] 该至少一个特性的确定可以部分地在动态可重配置异质脉动阵列外部执行。该至少一个特性的确定可以基于对图像帧的至少一部分的处理和所述图像处理基元其中至少一个。

#### [0049] 脉动阵列

[0050] 脉动阵列范例,即由数据计数器驱动的数据流,是冯·诺依曼(von Neumann)范例,即程序计数器驱动的指令流。因为脉动阵列通常发送和接收多个数据流,且使用多个数据计数器来产生这些数据流,所以它支持数据并行。该名称因与心脏的规则血流泵浦的详细而得出。

[0051] 脉动阵列由被称为胞元(cell)数据处理单元的矩阵状行组成。数据处理单元或DPU类似于中央处理单元(CPU),只不过缺少程序计数器,因为操作是传输触发的,即由数据对象的到达而触发。每个胞元在处理之后立即与其相邻胞元共享信息。脉动阵列通常是矩形的,或者使其胞元成列和/或成行布置,其中数据跨越相邻DPU之间的阵列流动,通常不同数据在不同方向中流动。图3示出这种同质脉动阵列架构的示例。进入且离开阵列端口的数据流通过自排序存储器单元或ASM产生。每个ASM包括数据计数器。在嵌入式系统中,数据流还可以从外部源输入和/或向外部源输出。

[0052] 脉动阵列可以包括网状拓扑的DPU阵列,这些DPU连接到少量最近相邻的DPU。DPU对在其间流动的数据执行一系列操作。因为常规脉动阵列合成方法已经通过代数算法来实践,所以仅可以获得仅具有线性管线的均匀阵列,使得在所有DPU中架构都是相同的。结果是在典型脉冲阵列上通常仅实现具有规则数据依赖关系的应用。

[0053] 像SIMD(单指令/多数据)机器一样,钟控的脉动阵列在“锁步”中进行计算,每个处理器采取交替的计算/通信状态。然而,在DPU之间具有异步握手的脉动阵列通常被称为波前阵列。一个已知的脉动阵列是已经由Intel制造的卡内基梅隆大学的iWarp处理器。iWarp系统具有通过在两个方向中行进的数据总线而连接的线性阵列处理器。

#### [0054] AHIP(用于图像处理的高级硬件)

[0055] 图4示意性示出包括使用AHIP(用于图像处理的高级硬件)的IPP硬件的实施例。在图4示出的AHIP具有穿过(pass-through)属性。图4示出包括图像和数据缓存46以及长期数

据存储装置48的存储器存储装置44。缓存46包括原始数据50、RGB数据52和已处理RGB数据54，而长期数据存储装置可以包括MPEG图像56和/或JPEG图像58。在图4示出的实施例还有利地包括场景处理基元60，该场景处理基元例如包括区域基元62、帧数据基元64、阈值图66和/或积分图像图68。

[0056] 图4还示出向存储器44和IPP 74通信传送原始数据的传感器72。IPP 74还从存储器44接收原始数据。IPP 74还向存储器44、46提供RGB数据52。RGB数据通过IPP 74提供到有利的AHIP模块75。AHIP模块75向存储器44、46提供已处理图像图、AHIP模块数据和RGB数据。存储器44、46向CPU/GPU 76提供RGB数据、图像图和AHIP模块数据。CPU 76向存储器44和译码模块78提供已处理RGB数据54。如图4示意性所示，CPU 76还可以对IPP模块74和/或AHIP模块75进行编程。译码模块78向存储器44、48提供数据，且从存储器44、48检索数据。译码模块78还提供例如将在LCD/TFT显示器80上显示的数据。

[0057] 有利地，在某些实施例中，在每个时钟周期获取一个标准图像像素，且以各种方式中的一种或多种来处理该像素。若干不同类型的输出可以并行地从每个独立像素的处理而产生。每个输出类型的多于一个实例可以通过硬件元件的复制提供。因为该硬件子系统可以在每个时钟周期处理像素，它并不延时来自传感器的图像像素的传输，且因而它可以在任意IPP级插入。

[0058] 很多通用类型的图像处理基元可以通过AHIP模块识别和产生。为了使得下面的讨论清晰，图像数据可以被称为“像素”（图像元素）且输出基元中的数据值可以被称为“图像素（map pixel）”。典型地，图像素将明显地小于像素（24或32比特）。作为示例，用于皮肤图（skin map）的图像素的一种形式仅具有对应于作为皮肤像素的原始像素的4个概率的两个比特。另一图像素具有对应于16个阈值的4比特，该16个阈值描述它与预定颜色空间中的特定颜色有多相似。对应于16个相似度级别的颜色空间阈值被存储在LUT中，最终的输出数据基元图包括图像素。

[0059] 第一种基元包括直接像素到映射像素的映射。在某些实施例中，这可以包括颜色或亮度阈值，其确定特定像素与颜色空间中的预定值有多接近。在某些实施例中，该数据可以作为15个阈值的范围而被捕获且写入到4比特图像图中。这些阈值可以通过CPU/GPU随着图像帧不同而进行调节。

[0060] 在示例性实施例中，每个阈值的数据值被设置为测量图像像素与皮肤颜色有多接近。这种图像图可以有利地用于区分面部区域的不同皮肤区域且可以用于诸如面部跟踪和面部美化之类的应用。

[0061] 就时钟周期而言，这种形式的图像基元仅招致了小固定延时。在图像帧的最后像素被输入到AHIP之后，输出图像图典型地在几十个时钟周期内可用。

[0062] 像素到图像素处理的一种变型是当处理多个像素时，产生单个输出像素。这对应于对原始输入图像的子采样。在一些实施例中，像素块在被处理以产生相应的输出基元数据之前，临时存储在硬件线路缓冲器中。在备选实施例中，像素继续被单独处理，但是来自处理每个相应像素的输出以某一预定方式被组合，以产生单个图像素。

[0063] 第二种形式的基元是内核推导基元。用于这种基元的图像素从当前图像像素和该图像的至少一个先前像素的知识而推导得出。很多技术指定N×N内核，这暗示着对应于当前像素的输出值从在图像内在水平和垂直两个方向中的N个相邻的像素确定。因为像素数

据在某些实施例中典型地仅对于AHIP模块顺序可用,在某些实施例中它将通过IPP从图像传感器逐行(和/或逐列)被直接钟控。在这些实施例中图像数据的所有行将典型地被缓冲以支持内核推导基元。

[0064] 在某些实施例中,七(7)行图像数据被完整地存储且第8个图像行滚动。这使得模块能够产生从高达 $8 \times 8$ 个内核而推导的图像处理基元。在该实施例中,在完整内核基元图像图针对当前图像帧可用之前,存在8乘以图像的行大小(针对1080p, $8 \times 1920$ )的量级的延时。然而,这仍小于获取完图像帧(1000个像素行)花费的总时间的1%,所以图像帧基元数据在完成最终帧获取之后很快可用。

[0065] 内核推导图像处理基元的一个特定示例是红眼分段的基元。例如在通过引用结合的美国专利6,873,743中,描述了针对图像执行执行 $2 \times 2$ 分段的技术。这在LAB颜色空间上操作。内核推导基元的另一示例是在图像的亮度分量上执行的积分图像的计算。如将简要地解释的那样,在某些实施例中AHIP并入了颜色空间转变模块,该颜色空间转变模块实现了在若干常用颜色空间之间的输入图像数据的动态转换。因而单独RGB像素数据可以在AHIP内以可忽略的延时转换到YCC或Lab颜色空间。

[0066] 第三种形式的基元包括帧推导基元。这些基元是其中单个像素或像素块并未产生相应的单个图像输出的数据基元的示例。这种形式的图像处理基元的一个示例是使用很多组距(bin)预配置的直方图模块。针对一组阈值对输入像素数据进行分析,且基于其值将其分类到直方图。在图像帧的结尾,每个直方图组距包括满足其上阈值限制和下阈值限制的像素数目的计数。

[0067] 当与针对基元类型一种给定的示例组合时,可以测量特定图像帧中多少像素落在一组16个皮肤颜色直方图组距内。这进而可以在例如在跟踪的面部区域内检测到太多或太少的皮肤像素时提议需要针对下一图像帧调节皮肤颜色阈值。AHIP内的硬件架构被设计成使得处理块能够在处理图像帧之前动态重配置。根据某些实施例,附加并行处理块可以被添加到这种硬件架构中。

[0068] 在其他实施例中,颜色相关图或其他形式的直方图状数据可以通过AHIP确定。这种基元可以有利地从用于产生内核数据的相同一组行缓冲器确定,差异是直方图或相关图数据提供从多个像素确定的帧推导基元,而非由内核推导基元提供的输入到输出像素的一对一映射。

[0069] 另一种形式的帧推导基元包括执行像素行和像素列值的求和的基元。这实现了当前图像帧与一个或多个先前图像帧的关联。这种基元引入AHIP的另一方面,其中从当前帧确定的基元中的一个或多个可以被记录以用于一个或多个后续图像帧。这种基元可以明显小于全图像帧,或者实时处理的益处将并不被完全实现。在某些实施例中,针对这种基元的典型大小限制是它们不大于已处理图像的最大行大小。

[0070] 在某些实施例中,这种数据可以保留在AHIP模块中而不是被写入到外部存储装置。因而图像帧推导数据和/或像素推导数据可以在AHIP中累积,以有利于图像帧基元的更快处理。

[0071] 第四种形式的基元是从主图像帧的特定空间区域推导得到的。这些基元本质上可以更加复杂,且可以将区域的更复杂的硬件处理与从CPU/GPU推导且涉及一个或多个在前帧图像的外部数据和一些基本基元组合。

[0072] 硬件缓冲器可以用在涉及预测数字图像中面部区域的位置处理中(例如见上面通过引用而结合的美国专利7,315,631及其后续申请以及7,466,866)。在某些实施例中,在一个或多个先前帧中收集关于在当前图像帧内有望在何处检测到面部的知识。与在当前帧中执行面部检测相比,该方法具有更加快速的优点,且收集的信息甚至可以当前图像帧之前用于各种目的。

[0073] 具体而言,一般难以在图像帧的单一处理期间判断这种区域的高度精确的位置,因为这依赖于在GPU/CPU上的软件中执行的附加图像处理。因此,在AHIP的图像帧的第一硬件处理期间一般仅近似确定空间区域位于何处。然而,这些近似位置可以被有利地标记,且典型地明显小于主图像。在一个实施例中,若干这种预测区域可以存储在AHIP的缓冲器中,以用于下一帧周期上的进一步处理。在备选实施例中,这些区域与主图像一起被写入存储器中,但是通过专门配置成处理这种区域的第二AHIP模块加载回来。在该第二实施例中,优点在于存储器子系统是双端口的这一事实。因而当下一图像帧被主AHIP处理且被写入到存储器时,来自先前图像帧的一个或多个预测区域可以被读回到第二AHIP模块,以用于更加专用的处理。在该实施例中,典型地仅在下一图像帧被一般化处理时才处理特定图像区域。不过单个帧延时可以被容易地补偿且不折中实现接视频序列的实时处理的目标。

[0074] 一个非常常见的空间区域是预测的面部区域。其是当前图像帧中面部区域将很可能位于其中的区域。这种区域被频繁地用在面部跟踪算法(同样见上面通过引用结合的美国专利7,315,632以及其后续申请)。这种区域的一种通常用途是将诸如红眼检测的图像处理算法的应用限制到面部出现高概率的图像区域。

[0075] 图5示意性示出AHIP模块,所述AHIP模块具有布置到处理链中以用于各种图像处理基元的若干通用处理模块。图5中示出图像传感器82、SDRAM存储器84、AHIP模块85本身以及CPU 86。AHIP模块包括与CPU 86通信的AHIP配置管理器90。AHIP模块85还包括查找表(LUT)模块92、数据配置模块94、逻辑模块96和同步模块98。如前面图4所述,某一RGB数据102被直接存储到存储器84。然而,某些其他RGB数据103在一个或多个像素处理模块106、一个或多个帧处理模块107、一个或多个区域处理模块108以及一个或多个内核处理模块110处由AHIP模块85进行处理。某些RGB数据103可以在帧处理模块处被处理,且该帧数据112被存储在存储器84中。某些RGB数据103可以在一个或多个像素处理模块106被处理,且然后像素数据114被存储在存储器84中或者该数据在内核处理模块110和/或帧处理模块107和/或区域处理模块108被进一步处理。诸如先前帧(由N-1指示)的相邻帧的RGG数据116可以在区域处理模块108与RGB数据103一同处理。在区域处理模块108处已被处理的数据然后可以作为区域数据118存储在存储器84中。

[0076] 通常希望例如在甚至可以做出面部区域的精确位置的完全确认之前向图像的一些部分应用算法。这些预测面部区域可以从先前图像帧确定,且可以利用大量在前帧上的面部和照相机移动的历史。就这方面而言,帧-帧dX和dY位移可以通过AHIP模块确定,且在帧的最后像素被处理之后的短延时内可用。类似地,面部区域的位置和大小可以从面部跟踪器算法的一个或多个帧的最终数目获得,且这两个数据可以在AHIP开始新图像帧的处理之后极快地可用。这些数据可以有利地实现针对当前图像帧的预测面部区域的精确和动态估算(见美国公布的申请序列号US2009/0303342和US2009/0263022以及美国专利7,460,695、7,403,643和7,315,631以及US2009/00123063、US2009/0190803、US2009/0189998、

US2009-0179999和US专利申请序列号12/572,930、12/824,214和12/815,396,这些专利和专利申请均转让给相同的受让人,且通过引用而结合于此)。

[0077] 诸如眼睛区域和/或嘴部区域和/或半面部区域的面部区域或面部特征区域(见美国序列号12/790,594和12/825,280,它们与本申请均被转让给相同的受让人且此处通过引用结合于此)初始时可以被保存到本地存储器缓冲器。典型地,因为存储器在硬件核中是昂贵的,因此可能存在有限数目的“面部缓冲器”,且它们可以优化以使大小最小化。实际上,在一些实施例中,这种缓冲器可以在AHIP外部,且可以包括用于将这些区域写入到主外部存储器存储装置的带宽。在其他实施例中,其在主图像内的位置可以被记录,使得它们稍后可以从主存储器存储装置在主图像帧数据内可存取。在一个实施例中,这种区域将被内部存储在AHIP模块中。然而,因为AHIP缓冲器的大小对于全HD视频可能太大或者并不是太大,因此在备选实施例中,这些面部区域与主图像一起存储在主存储器中,且在下一主图像帧被处理且写入到主存储器的同时将这些面部区域再次加载到辅助AHIP模块中。

[0078] 在这些实施例中,因为很多面部检测和识别技术可以应用于固定大小的面部图像,这些存储器缓冲器可以足够大以容纳这种固定大小面部区域且具有一些附加容量。附加容量可以用于针对很多因素进行补偿:(1)图像数据被预测,并且因而高度精确的面部位置在图像的初始AHIP处理时是未知的;(i)面部区域可以并不正确地竖直且可能需要面内旋转以获得适当的竖直面部区域;该信息可以在面部区域的精确位置被确定且该面部区域内的眼睛区域的位置被确定之后在稍后可用;此时,面内校正角和尺寸缩放信息可以提供到AHIP,但是直到这时面部区域才可能处于面内角度,这涉及附加存储器空间以容纳对角取向的面部区域;(ii)面部区域可以以全局大小随着帧不同变化;在可以从过去的图像帧的历史获知一些趋势时,也可能存在来自这些趋势的变化。因而直到在主图像帧处理完成之后区域数据被CPU/GPU处理时,面部的精确大小可能是已知的或者是未知的。在下一原始图像帧被处理和写入的同时来加载和处理面部区域的备选实施例中,主图像及相关基元的一些附加处理可以从CPU/GPU获得。在这些情况中,面部区域位置的更精确的估算可能是可用的。

[0079] 在另一示例性实施例中,假设考虑最大尺寸 $32 \times 32$ 的最终固定大小的面部区域。存储器缓冲器可以用于 $64 \times 64$ 的面部区域以适应高达1.99的潜在部分尺寸缩放且高达46度的旋转。这定义了用于精确定位的面部区域的缓冲器大小,然而在当前帧首次被AHIP处理时,我们仅知道其中该图像帧中可能存在面部的预测区域。因此,存储较大区域可能是有用的,可以使用例如 $96 \times 96$ 或 $128 \times 128$ 个像素的缓冲器,以提供比期望的面部区域的尺寸大50%或100%的预测面部区域缓冲器。

[0080] 当关于预测面部区域的位置和尺寸的数据从先前图像帧的软件处理而传递到AHIP时,这些预测面部区域被整数缩小到 $96 \times 96$ 或 $128 \times 128$ 的相应AHIP缓冲器。典型地对于面部区域的处理,仅须保持亮度值,且因而这些缓冲器是单值的且典型地不保持全色数据。然而在一些实施例中,皮肤图的形式可以被产生且与面部区域的亮度图像一同存储。典型地,用于面部跟踪目的的皮肤图可以仅是2位的,代表皮肤像素的仅3或4个状态。

[0081] 这种基元的示例是面部分类器在被跟踪面部区域的应用。典型地,面部区域将并不是精确地水平且所以来自预测面部区域的数据可以在应用面部分类器之前首先被旋转到水平取向。这种操作需要用于图像数据的较大缓冲器且所以区域缓冲器的数目和每个缓

冲器的大小可能略微受限。在该示例中输出的基元是对应于特征向量组的一组数据值,该特征向量组可以用于确认和/或 (i) 该区域仍包括确认的面部; (ii) 特征向量组可以与一组已知面部匹配以指示相似的匹配。

[0082] 图6示出主CPU、AHIP硬件模块、图像传感器和SDRAM存储器126的读/写通道125之间的相互关系。AHIP/CPU接口128提供某些寄存器和/或中断。在图6中示出传感器124和AHIP块122之间的用于YUV数据的B2Y接口130。

[0083] 在AHP内实现若干原理类型的图像帧处理。下面将描述这些处理中的一些。

[0084] 帧到帧AHIP处理

[0085] 图7示出来自帧N-1的数据与当前帧N组合的使用。在图7的说明性示例中,存储器存储装置(图像数据和缓存)140被相应地分段成两个帧。一些特征已经参考图4描述且此处不重复。参考作为示例的面部跟踪,在存储器140中存储预测区域142以用于帧N-1和帧N二者。在存储器140的帧N-1部分内,存储精确区域和区域基元数据143。这些数据用于产生用于帧N的RGB图像帧数据和帧基元145。帧N-1区域数据144与帧N RGB数据149一起被输入到AHIP块148。在块150,AHIP块对帧N-1区域数据中的某一些进行子采样和/或颜色空间重新映射,且然后通过像素处理块154移动所有帧N-1区域数据144以在帧N部分向存储器140输出。在块160,帧N RGB数据149可以被子采样156和/或在被像素处理之前被颜色空间重新映射158。像素处理160可以包括累积、直接、内核、区域和/或混合像素处理。数据然后存储在存储器140的帧N部分。

[0086] 现在将简要描述根据某些实施例的AHIP模块的各种子元件中的某一些的描述。AHIP模块可以包括这些示例子元件其中的任意一个、所有元件或不包括这些元件。

[0087] 色图单元

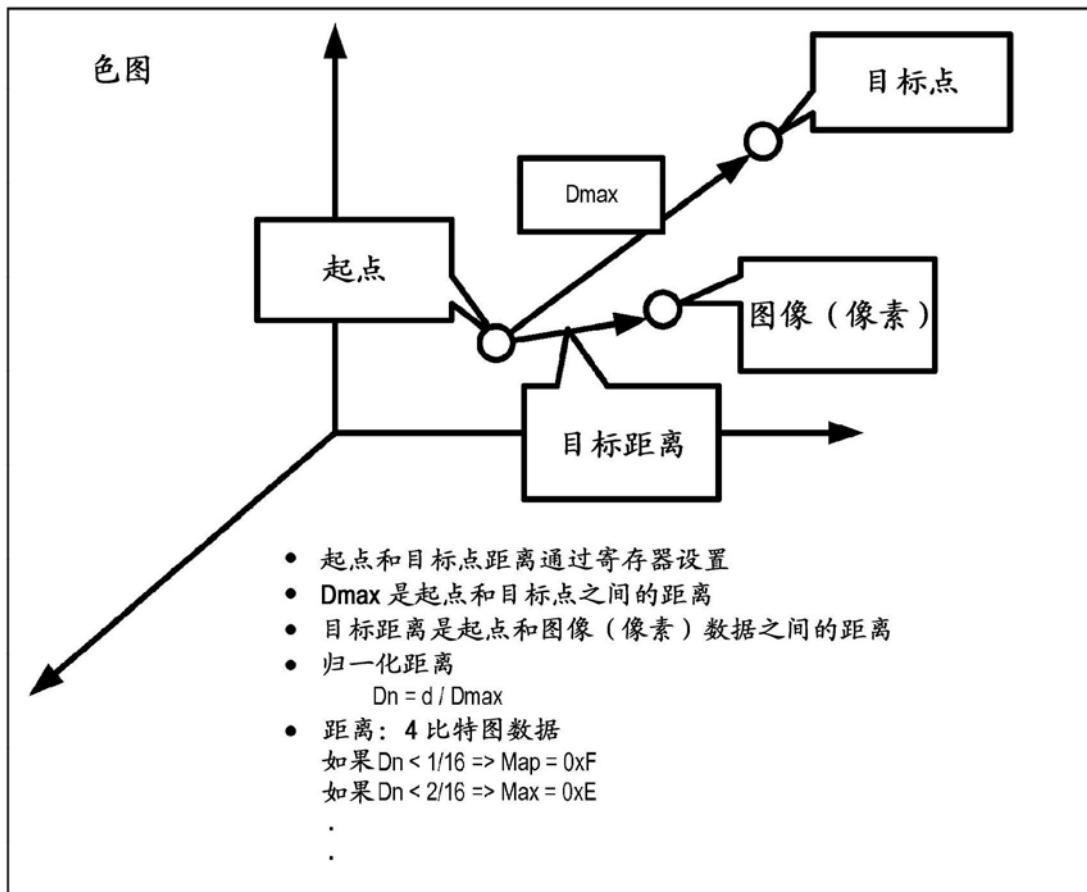

[0088] 色图单元模块产生具有相似颜色的像素的图。参考点R可以在输入颜色空间(例如RGB)中被预编程。然后,针对每个输入像素P,色图模块可以计算P和R之间的欧几里德距离d,且然后将它与15个可编程阈值(T1...15)进行比较。这些阈值可以被级联地评估,使得它们优选地以递增顺序设置(T1< T2...< T15-从非常严格到非常宽容)。如果d< Tn,则模块输出值16-n。如果没有阈值匹配,则0被送出。图8示出根据某些实施例的颜色阈值模块。

[0089] 色图的输出典型地可以由4位表示。在一些实施例中,例如可以仅使用8(3位)或4(2位)或2(1位)实现较小一组阈值。色图模块可以针对输入全分辨率图像操作。输出图可以具有与输入相同的分辨率且每个像素可以产生指示在3D颜色空间中它与预编程的参考像素有多匹配的匹配输出。

[0090] 在备选实施例中,附加并行颜色模块可以通过设置输入通道之一为零或中点值来实现像素与3个颜色通道中的2个有多相似的确定。其他实施例实现2D颜色模块,其中3个通道中仅2个用于比较。

[0091] 因为色图模块的功能性依赖于欧几里德距离,输入颜色空间将是距离有意义(接近度等于视觉相似度)的颜色空间。通常,此模块应当与RGB输入一起使用,但不限于此。

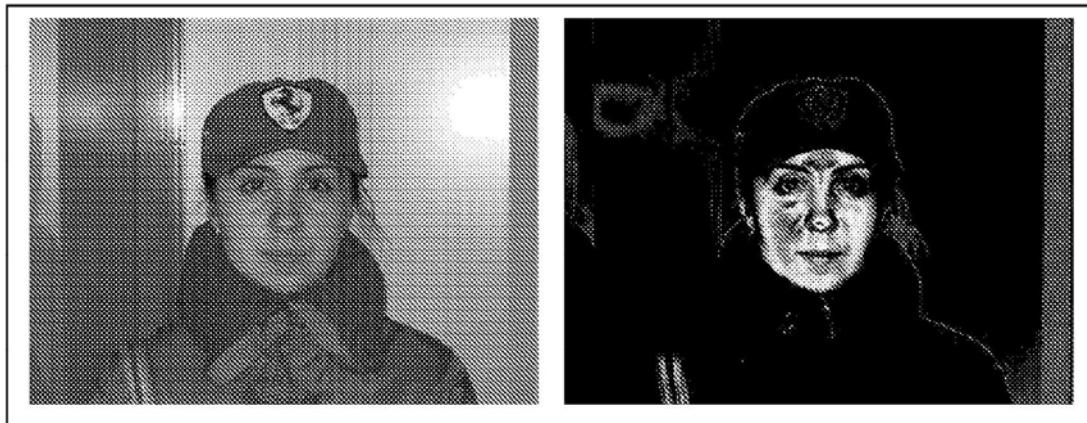

[0092] 在图9中,提供应用于图像的色图模块的示例。该示例中的参考点是在RGB坐标中给出的类似皮肤的颜色。在图9中的左侧,示出输入图像,而在右侧是色图(白色代表最大值,范围是0至15)。在图9的示例中,使用16个阈值(4位)。

[0093] 颜色空间转换(CSC)单元

[0094] CSC可以用于实现如下定义的可编程矩阵乘法器：

$$[0095] Ax + B = \begin{bmatrix} a_{11} & a_{12} & a_{13} \\ a_{21} & a_{22} & a_{23} \\ a_{31} & a_{32} & a_{33} \\ a_{41} & a_{42} & a_{43} \end{bmatrix} \times \begin{bmatrix} Y \\ U \\ V \end{bmatrix} + \begin{bmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \end{bmatrix} = \begin{bmatrix} a_{11} Y + a_{12} U + a_{13} V + b_1 \\ a_{21} Y + a_{22} U + a_{23} V + b_2 \\ a_{31} Y + a_{32} U + a_{33} V + b_3 \\ a_{41} Y + a_{42} U + a_{43} V + b_4 \end{bmatrix}$$

[0096]  $x = [Y, U, V]$  = 输入像素，A和B=具有可编程系数的矩阵。

[0097] 该结构可以执行像YUV-2-RGB或RGB-2-YUV这样的转换。还可以执行YUV和定制颜色空间之间的转换。这些转换可以结合其他模块使用以识别具有特殊属性的像素。

[0098] 可以在CSC的输出处执行饱和功能(以限制值为0…255的整数范围)。

[0099] 图10示出从图像传感器172接收RGB数据且向存储器174提供数据(包括像素数据和/或帧数据)的AHIP模块170。图10的示例AHIP模块170包括像素处理模块176。模块176中的两个馈入阈值化模块178，且模块176中的两个馈入计数模块：一个直方图180和其他登记182。逻辑模块184从阈值化模块178接收输入且向存储器174输出像素数据。组距计数器186从计数(直方图)模块180接收输入且向存储器174输出帧数据。dX、dY偏移块188从计数(登记)模块182接收输入且向存储器174输出帧数据。第一RGB-2-YUV块190向累加器(积分图像)模块192输出像素数据，该累加器模块进而向存储器174输出像素数据。第二RGB-2-YUV块190向平方模块194和累加器(积分平方图像)模块196输出像素数据，且该累加器模块进而向存储器174输出像素数据。

[0100] 图11示出与CPU 202通信的AHIP块200，所述通信包括向CPU 202提供中断204且从CPU 202接收配置命令206。AHIP块200经由B2Y块210从传感器/B2Y 208接收数据且向存储器212输出。

[0101] 阈值化 (THR)

[0102] 该模块包括 $8 \times 1$ LUT以用于对其他模块的输出进行阈值化并将它们转换成二进制值(1比特)。可以在AHIP中并入多个阈值单元。

[0103] 逻辑功能 (LF)

[0104] 该模块包括 $6 \times 6$ LUT，该LUT可以用于进一步组合THR或诸如色图模块之类的AHIP模块的结果。它可以使用来自THR和SKIN模块的输入来实现6个不同逻辑功能。可以在AHIP中并入多个逻辑单元。

[0105] 直方图 (HIST)

[0106] 计算直方图可以应用于原始输入数据(YUV)和/或CSC模块的输出。这些模块累积来自每个像素的计数值且其输出在图像帧的每个像素通过AHIP时进行钟控之后可用。直方图组距的数目典型地是16且用于每个组距的阈值可编程。

[0107] 积分图像累计器 (II)-AKA

[0108] 面积计算模块

[0109] 这些模块包括用于计算积分图像的块(允许矩形区域中的最快面积计算；例如见上面通过引用而结合的美国专利7,315,631以及通过引用而结合的美国专利申请US 2002/0102024)。它们通常用在实时对象检测算法中。可以存在可用的三个标准块其中任意一个：

[0110] II(原始Y通道的总和面积，用于面积计算)

- [0111] 112(Y平方之和,用于方差计算)

- [0112] 皮肤II(皮肤由上的积分图像,给出区域中的皮肤密度)。

- [0113] 这些模块可以用于在每个输入像素上累积它们值且输出当前累积值以提供积分图像的相应像素值、或者积分变量或皮肤积分图像图(例如见通过引用结合的美国公布的申请序列号no.2010/0053368)。

- [0114] 复杂下采样器(DS)

- [0115] 该下采样器对图像进行缩放以用于其他模块。该模块被设计成在具有低门计数的同时提供合适的质量水平。其可以编程为实现主图像的可变尺寸缩小。

- [0116] 固定下采样器(XDS)

- [0117] 使用最近相邻内差,较简单的下采样器实现是可用的。这允许以固定分辨率同时计算图。典型地,x2、x4和x8下采样器将是可用的。

- [0118] 工作流

- [0119] AHIP可以设计为在De-bayer模块(传感器接口)之后集成在图像管线的末端。尽管YUV被认为是AHIP的固有颜色空间,一些内部模块也可以处理其他颜色空间。除了传感器接口,AHIP提供用于从存储器读取数据的回放接口。在预览模式中,AHIP可以配置成以传感器时钟速率(每个像素一个时钟)处理数据。AHIP处理的数据可以被写入到目标系统的主存储器(SDRAM)中。模块中的一个或多个可以向寄存器输出值。AHIP可以或可以不配置成向其他模块提供流输出接口。

- [0120] 使用AHIP的典型工作流的示例如下:

- [0121] 来自传感器或来自存储器的实况数据被发送到AHIP(一次一个像素)。

- [0122] 在帧周期中,AHIP执行其计算:

- [0123] 一个或多个模块更新内部统计。

- [0124] 一个或多个其他模块向系统存储器写入数据(图)。这典型地可以相对于输入以最小延时完成(即数据随着像素进入而离开)。

- [0125] 在帧结束之后,AHIP触发对CPU的中断:

- [0126] 在正常条件下,中断告知CPU全新数据可用。

- [0127] 也可以存在告知错误条件的中断。

- [0128] CPU中断处理器被调用:

- [0129] 它读取AHIP寄存器以发现中断的原因。

- [0130] 它然后可选地重配置AHIP(例如基于这样做将有利的确定)且确认中断。

- [0131] 它还可以告知其他CPU线程来自硬件的数据可用(并且算法使用它开始)。

- [0132] 尽管已经描述和示出了本发明的示例性附图和特定实施例,应当理解本发明的范围不限于讨论的特定实施例。因而,这些实施例将被认为是说明性的而非限制性的,且应当理解本领域技术人员可以在不脱离本发明的范围的条件下在这些实施例中做出改变。

- [0133] 另外,在可以根据此处的优选实施例来执行且上面已经描述的方法中,以所选的拓扑序列描述了操作。然而,序列被选择为因此被排序是出于用于拓扑方便目的,且并非旨在暗示用于执行操作的任意特定顺序,除非可以明确设置特定顺序或者本领域技术人员可以断定特定顺序是必须的。

图1

图2

图3

图4

图5

图6

图8

图9

图10

图11