## (12) 发明专利申请

(10) 申请公布号 CN 120089649 A

(43) 申请公布日 2025.06.03

(21) 申请号 202510243037.5

(51) Int.Cl.

(22) 申请日 2019.02.25

H01L 23/488 (2006.01)

(30) 优先权数据

H01L 21/60 (2006.01)

15/903,677 2018.02.23 US

H01L 21/78 (2006.01)

(62) 分案原申请数据

201910137647.1 2019.02.25

(71) 申请人 半导体组件工业公司

地址 美国亚利桑那州

(72) 发明人 迈克尔·J·塞登 野间崇

和央冈田 英章吉见 四方田尚之

林育圣

(74) 专利代理机构 北京律盟知识产权代理有限

责任公司 11287

专利代理人 章蕾

权利要求书2页 说明书11页 附图22页

(54) 发明名称

半导体器件以及用于形成半导体器件的方法

(57) 摘要

本申请涉及半导体器件以及用于形成半导体器件的方法。本发明公开了半导体器件，所述半导体器件的实施方式可包括管芯，所述管芯具有第一侧和第二侧；接触接垫，所述接触接垫耦接到所述管芯的所述第一侧；以及金属层，所述金属层耦接到所述管芯的所述第二侧。所述管芯的厚度可不超过所述金属层的厚度的四倍。

## 1. 一种半导体器件,包括:

管芯,所述管芯包括第一侧和第二侧;

接触接垫,所述接触接垫耦接到所述管芯的所述第一侧;

金属层,所述金属层耦接到所述管芯的所述第二侧;和

模制化合物,所述模制化合物直接耦接到所述金属层;

其中所述模制化合物的外侧壁包括背向所述金属层的台阶;

其中所述管芯的厚度小于30微米;

其中所述接触接垫通过耦接在所述管芯上方的钝化层暴露;

其中所述管芯是经切割的管芯;

其中所述模制化合物覆盖并接触所述金属层的最外侧壁;

其中所述管芯的外侧壁与所述模制化合物的最外侧壁共面;且

其中整个所述金属层的周边小于所述管芯的周边并位于所述管芯的周边内。

## 2. 一种半导体器件,包括:

管芯,所述管芯包括第一侧和第二侧;

接触接垫,所述接触接垫耦接到所述管芯的所述第一侧;

金属层,所述金属层耦接到所述管芯的所述第二侧;和

模制化合物,所述模制化合物直接耦接到所述金属层的整个第一表面且位于所述金属层的整个第一表面上方,所述金属层的所述整个第一表面与面向所述管芯的所述第二侧的所述金属层的第二表面相对;

其中所述模制化合物的外侧壁包括台阶;

其中所述管芯是从晶圆中切割出来的;

其中所述模制化合物覆盖并接触所述金属层的最外侧壁;

其中所述管芯的外侧壁与所述模制化合物的最外侧壁共面;且

其中整个所述金属层的周边小于所述管芯的周边并位于所述管芯的周边内。

## 3. 一种用于形成半导体器件的方法,包括:

形成耦接到晶圆的第一侧的多个接触接垫;

通过背面研磨所述晶圆在所述晶圆的第二侧中形成凹槽,所述第二侧与所述晶圆的所述第一侧相对;

在所述凹槽内形成金属层;

对所述凹槽内的所述金属层进行图案化;

将模制化合物与所述凹槽内的所述金属层耦接;

移除所述晶圆的一部分,直到所述晶圆的所述部分与由所述模制化合物的一部分形成的平面共面;以及

将所述晶圆切割成多个半导体器件。

4. 根据权利要求3所述的方法,其中所述金属层通过所述模制化合物暴露。

5. 根据权利要求3所述的方法,其中所述模制化合物直接耦接在所述金属层上方。

6. 根据权利要求3所述的方法,还包括通过形成所述凹槽来减薄所述晶圆,其中所述晶圆的一部分被减薄到小于30微米。

## 7. 一种用于形成半导体器件的方法,包括:

- 形成耦接到晶圆的第一侧的多个接触接垫；

通过背面研磨所述晶圆的第二侧在所述晶圆的所述第二侧中形成凹槽，所述第二侧与所述第一侧相对；

在所述凹槽内形成金属层；

在所述金属层内形成多个开口；

将模制化合物形成到所述金属层的所述多个开口中；

移除所述晶圆的一部分，直到所述晶圆的所述部分与由所述模制化合物的一部分形成的平面共面；以及

将所述晶圆切割成多个半导体器件。

8. 根据权利要求7所述的方法，还包括将第二金属层耦接在所述金属层上方。

## 半导体器件以及用于形成半导体器件的方法

[0001] 分案申请的相关信息

[0002] 本申请是申请号为201910137647.1、申请日为2019年2月25日、发明名称为“半导体器件以及用于形成半导体器件的方法”的中国发明专利申请的分案申请。

### 技术领域

[0003] 本文档的各方面整体涉及半导体器件和半导体晶圆以及器件处理方法。

### 背景技术

[0004] 半导体制造工艺可涉及许多步骤。在一些工艺中，晶圆接纳一个或多个层，例如导电层。导电层可用于提供从晶圆切割的各个半导体器件的电接触区域。导电层通常使用溅射、蒸发或电镀操作来形成。

### 发明内容

[0005] 半导体器件的实施方式可包括管芯，该管芯具有第一侧和第二侧；接触接垫，该接触接垫耦接到管芯的第一侧；以及金属层，该金属层耦接到管芯的第二侧。管芯的厚度可不超过金属层的厚度的四倍。

[0006] 半导体器件的实施方式可包括以下各项中的一者、全部或任一者：

[0007] 管芯的厚度可小于30微米(μm)。

[0008] 管芯的厚度可与金属层的厚度基本上相同。

[0009] 器件可包括直接耦接到金属层的模制化合物。

[0010] 器件可包括直接耦接在金属层上方的模制化合物。

[0011] 半导体器件的实施方式可包括管芯，该管芯具有第一侧和第二侧；接触接垫，该接触接垫耦接到管芯的第一侧；金属层，该金属层耦接到管芯的第二侧；以及模制化合物，该模制化合物直接耦接到金属层。管芯的厚度可小于30μm。

[0012] 半导体器件的实施方式可包括以下各项中的一者、全部或任一者：

[0013] 管芯的厚度可与金属层的厚度基本上相同。

[0014] 模制化合物可直接耦接在金属层上方。

[0015] 用于形成半导体管芯的方法的实施方式可包括形成耦接到晶圆的第一侧的多个接触接垫；通过背面研磨晶圆在晶圆的与第一侧相对的第二侧中形成凹槽；在凹槽内形成金属层；对凹槽内的金属层进行图案化；以及将晶圆切割成多个半导体器件。

[0016] 用于形成半导体器件的方法的实施方式可包括以下各项中的一者、全部或任一者：

[0017] 该方法可包括将模制化合物与凹槽内的金属层耦接。

[0018] 金属层可通过模制化合物暴露。

[0019] 模制化合物可直接耦接在金属层上方。

[0020] 该方法可包括背面研磨晶圆的一部分，直到晶圆的该部分与由模制化合物的一部

分形成的平面共面。

- [0021] 该方法可包括通过形成凹槽来减薄晶圆,其中晶圆的一部分被减薄到小于30 $\mu\text{m}$ 。

- [0022] 该方法可包括用晶种层涂覆凹槽。

- [0023] 该方法可包括在金属层上方形成多个凸块。

- [0024] 该方法可包括将金属层、模制化合物以及多个凸块中的一者耦接到背面保护层,然后切割晶圆。

- [0025] 用于形成半导体管芯的方法的实施方式可包括形成耦接到晶圆的第一侧的多个接触接垫;通过背面研磨晶圆的第二侧在晶圆的与第一侧相对的第二侧中形成凹槽;在凹槽内形成金属层;在金属层内形成多个开口;将模制化合物形成到金属层的开口中;以及将晶圆切割成多个半导体器件。

- [0026] 用于形成半导体器件的方法的实施方式可包括以下各项中的一者、全部或任一者:

- [0027] 该方法还可包括在接触接垫与晶圆的第一侧之间形成金属层。

- [0028] 金属层的厚度可与晶圆的厚度基本上相同。

- [0029] 金属层的厚度可以基本上是晶圆的厚度的三倍。

- [0030] 该方法可包括将第二金属层耦接在金属层上方。

- [0031] 模制化合物可包封金属层。

- [0032] 对于本领域的普通技术人员而言,通过具体实施方式以及附图并通过权利要求书,上述以及其他方面、特征和优点将会显而易见。

## 附图说明

- [0033] 将在下文中结合附图来描述各实施方式,其中类似标号表示类似元件,并且:

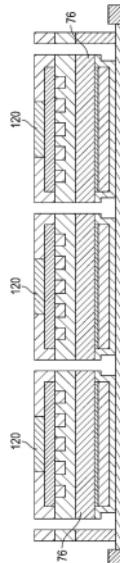

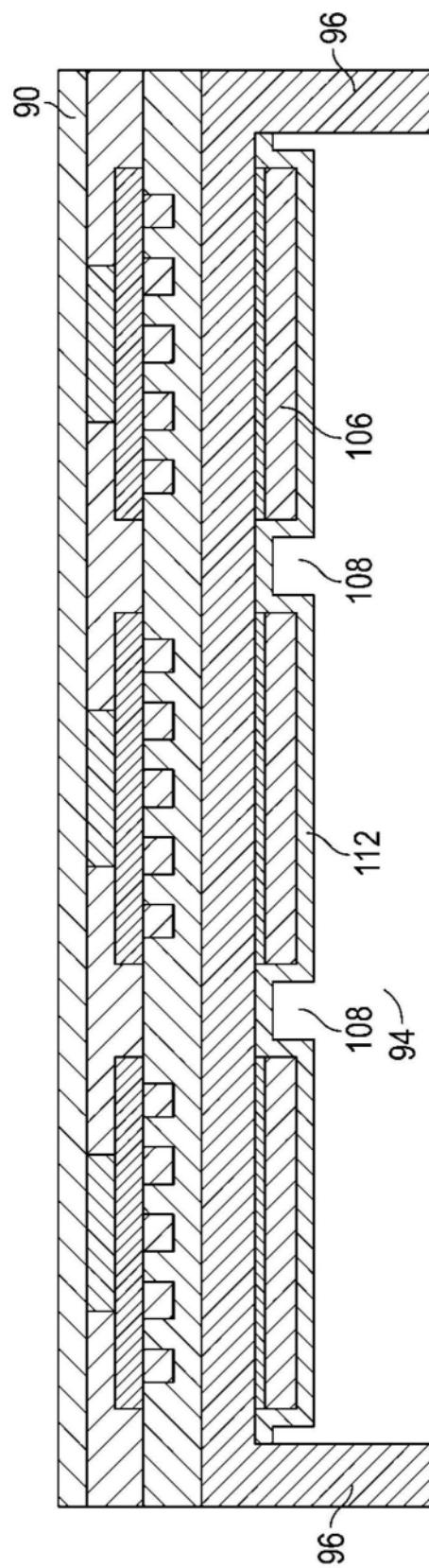

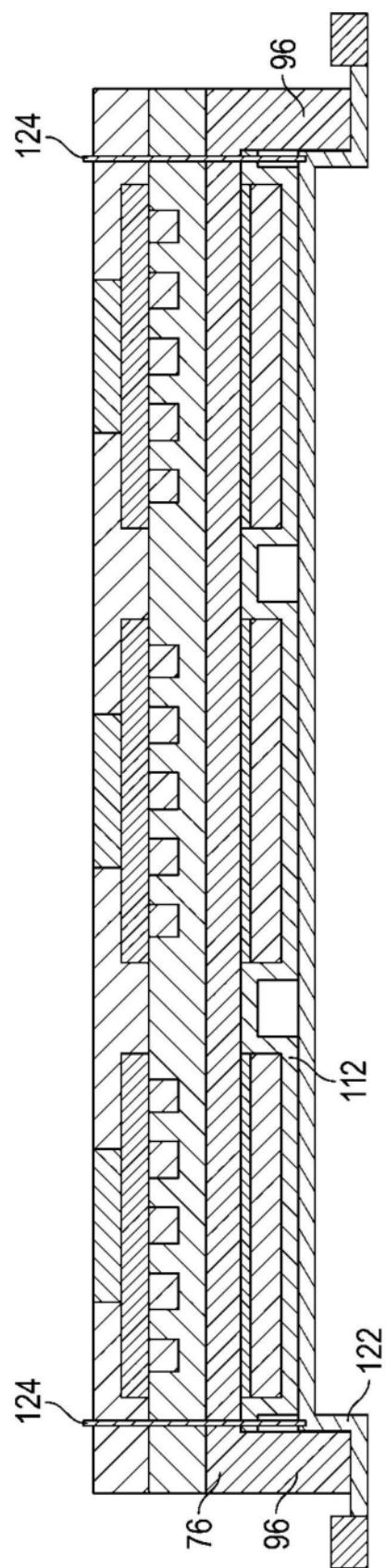

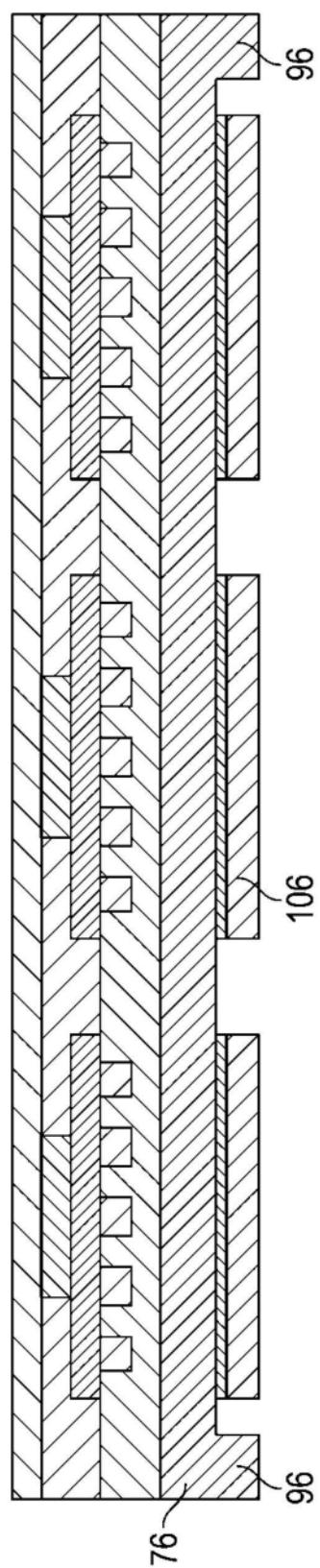

- [0034] 图1是半导体器件的第一实施方式的横截面侧视图;

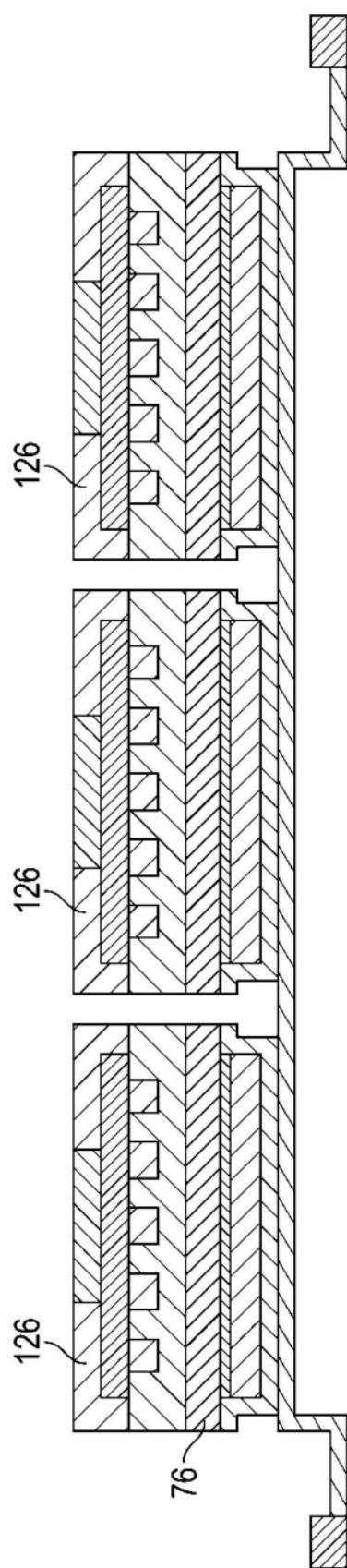

- [0035] 图2是半导体器件的第二实施方式的横截面侧视图;

- [0036] 图3是半导体器件的第三实施方式的横截面侧视图;

- [0037] 图4是半导体器件的第四实施方式的横截面侧视图;

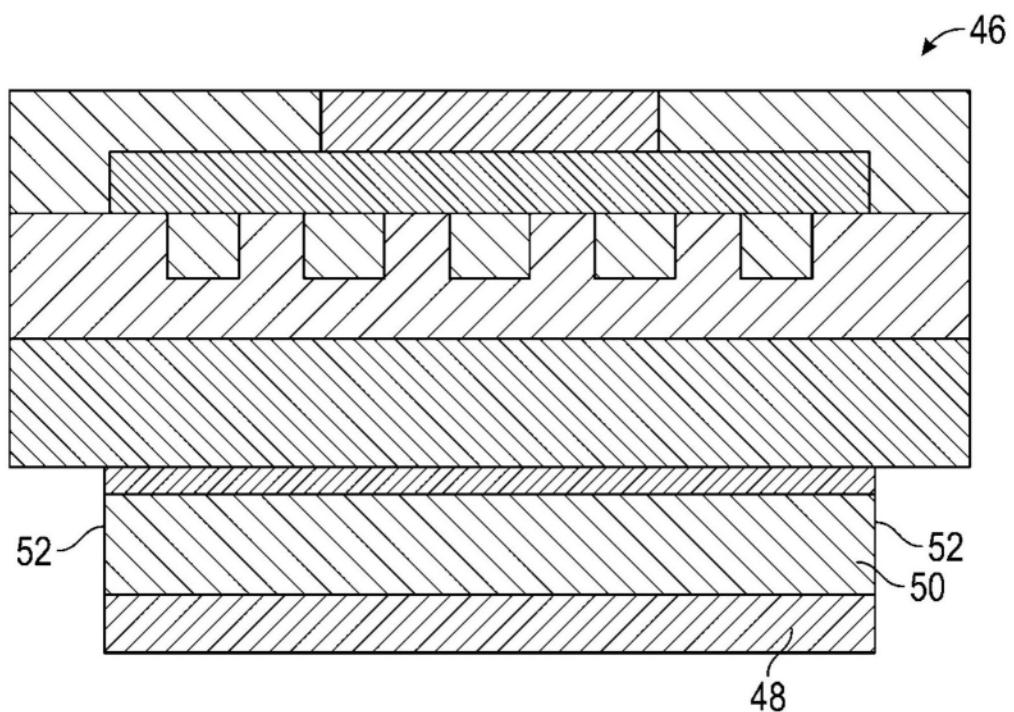

- [0038] 图5是半导体器件的第五实施方式的横截面侧视图;

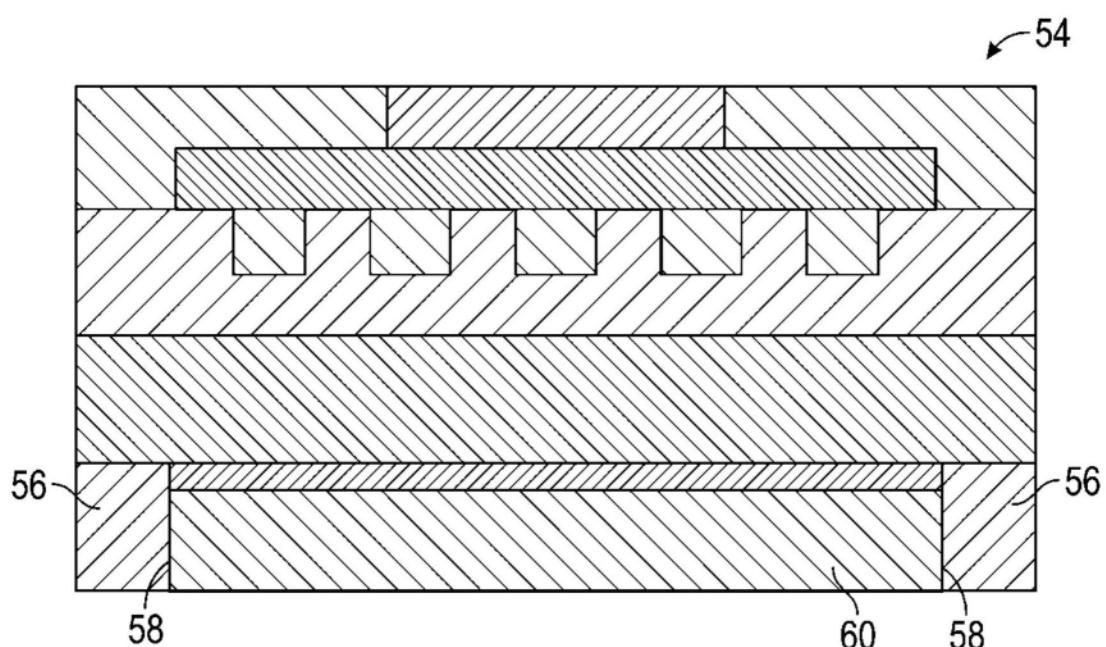

- [0039] 图6是半导体器件的第六实施方式的横截面侧视图;

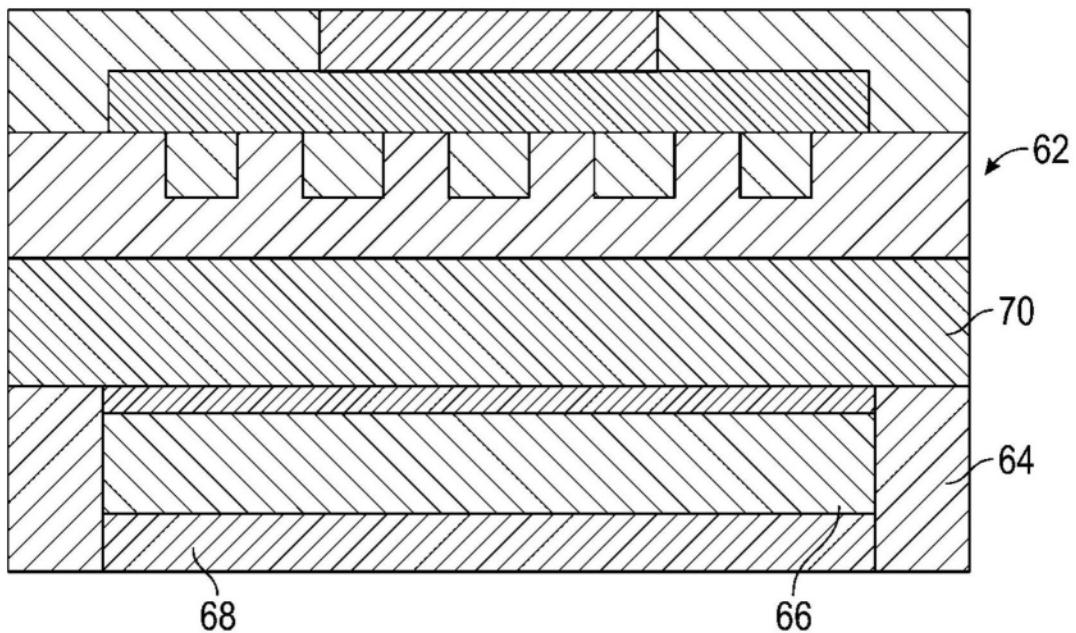

- [0040] 图7是半导体器件的第七实施方式的横截面侧视图;

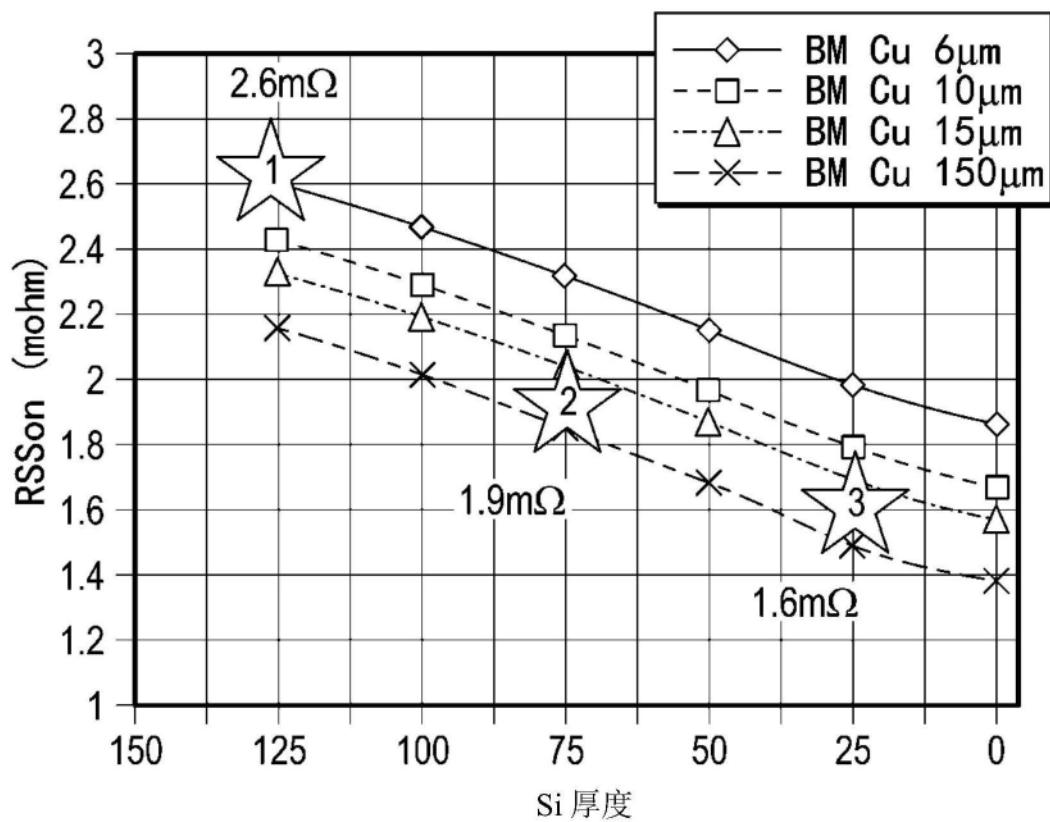

- [0041] 图8是示出半导体器件的各种实施方式的导通电阻的曲线图;

- [0042] 图9是晶圆的横截面侧视图;

- [0043] 图10是具有形成在其中的凹槽的图9的晶圆的横截面侧视图;

- [0044] 图11是图10的晶圆的横截面侧视图,其中掩膜形成在凹槽中;

- [0045] 图12是图10的晶圆的横截面侧视图,其中金属层形成在凹槽中;

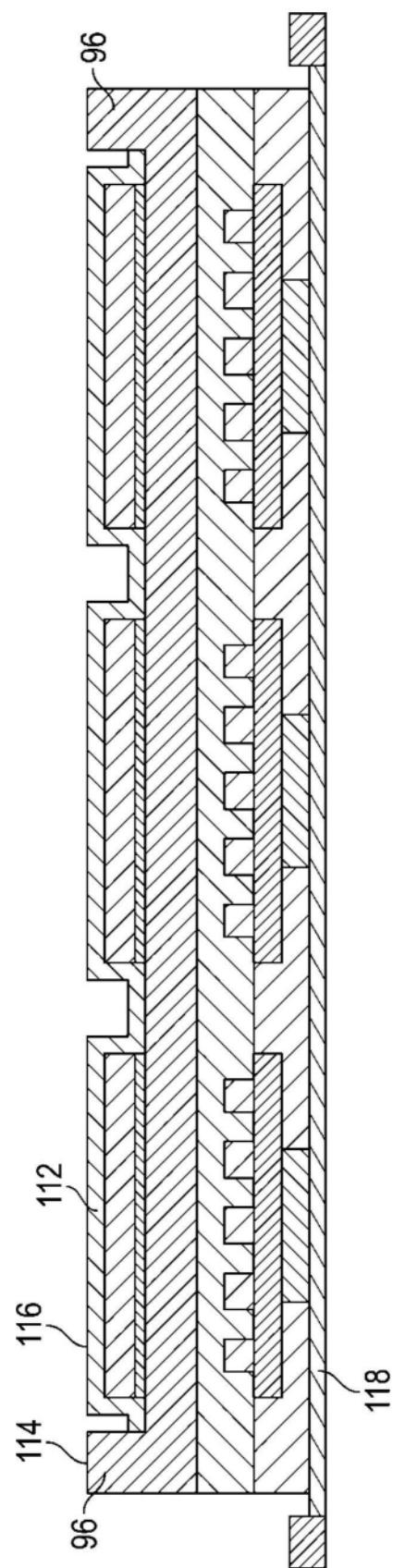

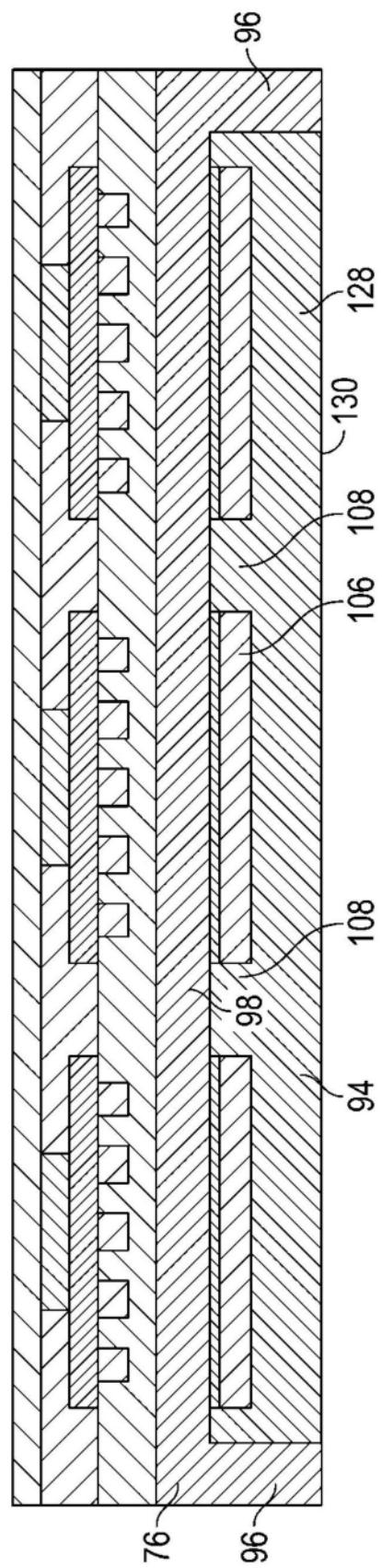

- [0046] 图13是图12的晶圆的横截面侧视图,其中模制化合物形成在金属层上方;

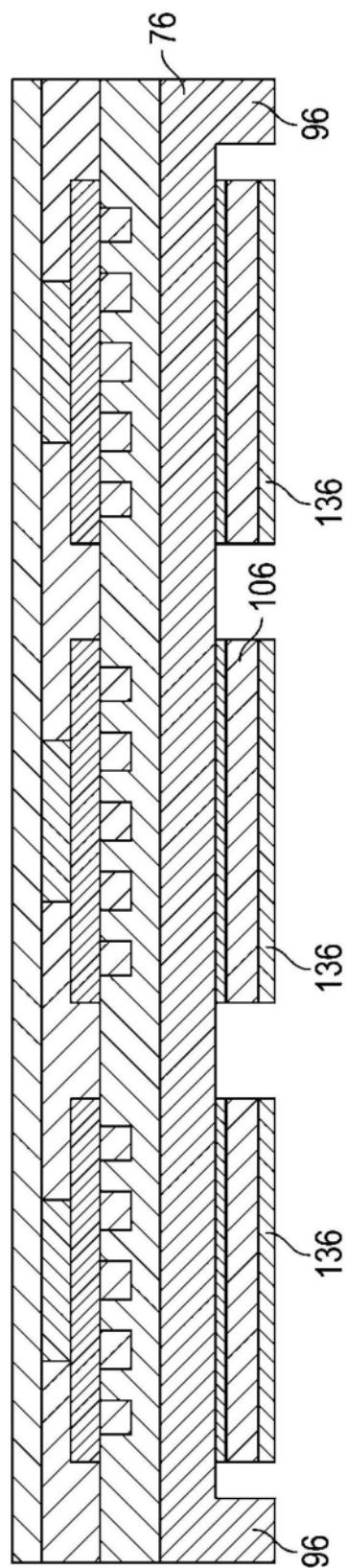

- [0047] 图14是图13的晶圆的横截面侧视图,其中移除晶圆的环的一部分;

- [0048] 图15是与施加到模制化合物的带一起旋转的图14的晶圆的横截面侧视图;

- [0049] 图16是切割的图15的晶圆的横截面侧视图;

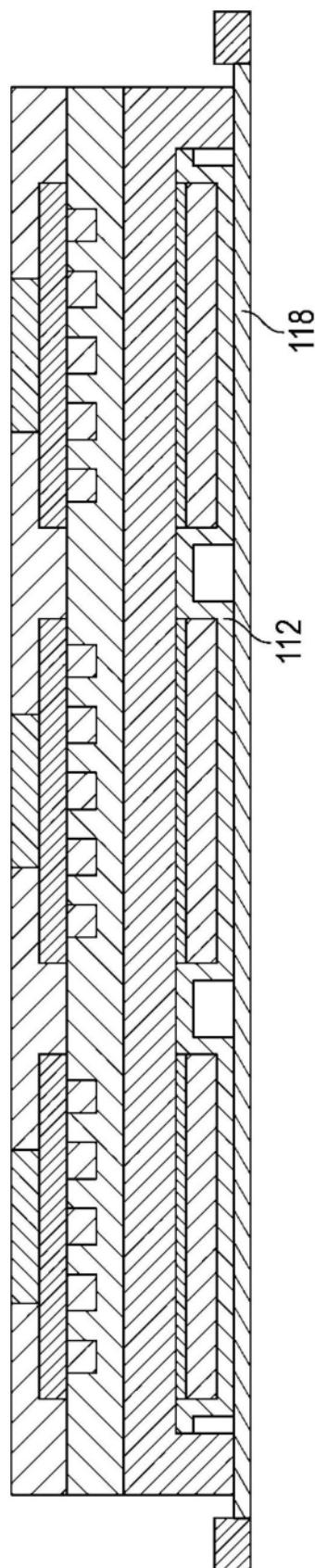

- [0050] 图17是图13的晶圆的横截面侧视图,其中带被施加到模制化合物;

- [0051] 图18是切割的图17的晶圆的横截面侧视图；

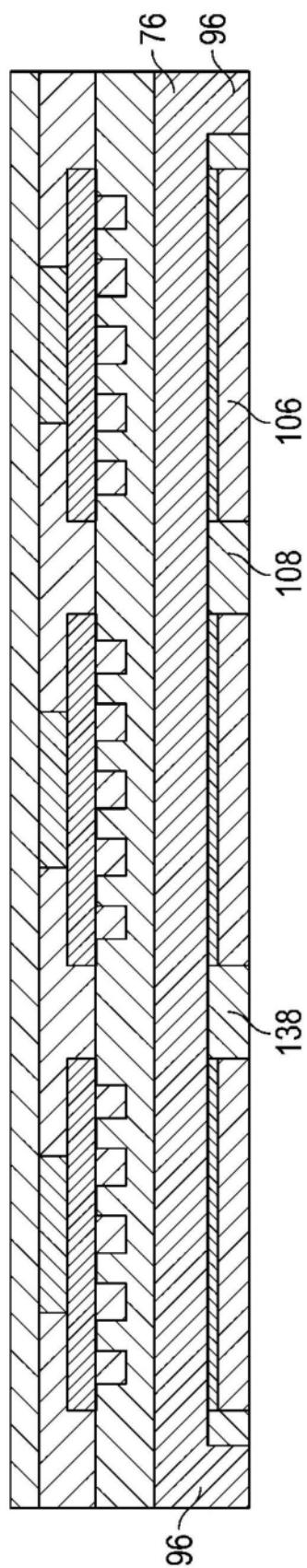

- [0052] 图19是图12的晶圆的横截面侧视图，其中模制化合物填充凹槽；

- [0053] 图20是图10的晶圆的横截面侧视图，其中非图案化金属层形成在凹槽内；

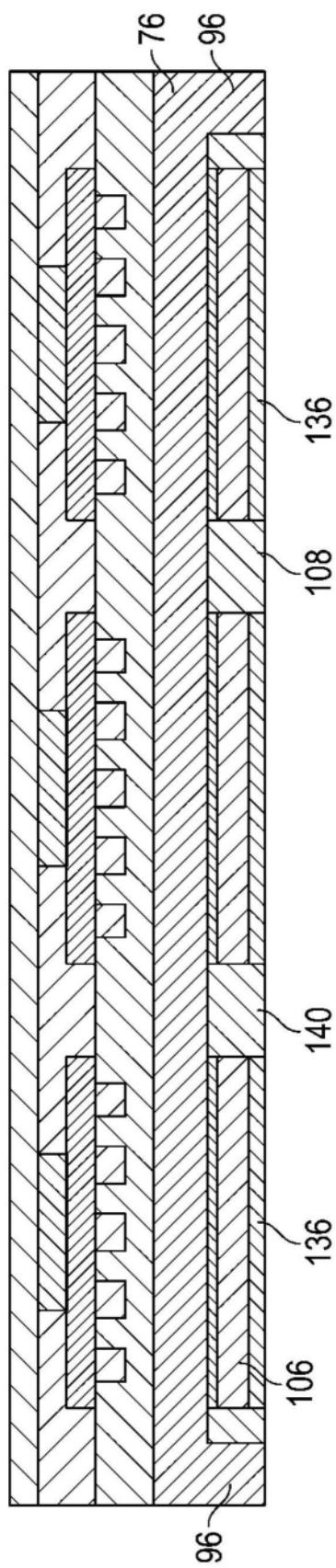

- [0054] 图21是图12的晶圆的横截面侧视图，其中移除晶圆的环的一部分；

- [0055] 图22是图21的晶圆的横截面侧视图，其中凸块形成在金属层上方；

- [0056] 图23是图21的晶圆的横截面侧视图，其中模制化合物形成在金属层中的开口之间；

- [0057] 图24是图22的晶圆的横截面侧视图，其中模制化合物形成在金属层中的开口之间；

- [0058] 图25A-图25B示出用于切割具有施加到其上的BSP层的晶圆的工艺；并且

- [0059] 图26A-图26B示出用于切割不具有施加到其上的BSP层的晶圆的工艺。

### 具体实施方式

[0060] 本公开、其各方面以及实施方式并不限于本文所公开的具体部件、组装工序或方法元素。本领域已知的符合预期半导体器件的许多另外的部件、组装工序和/或方法元素将显而易见地能与本公开的特定实施方式一起使用。因此，例如，尽管本发明公开了特定实施方式，但是此类实施方式和实施部件可包括符合预期操作和方法的本领域已知用于此类半导体器件以及实施部件和方法的任何形状、尺寸、样式、类型、模型、版本、量度、浓度、材料、数量、方法元素、步骤等。

[0061] 半导体器件以及实施部件和方法的特定实施方式可与以下专利中公开的半导体器件以及实施部件和方法相似或相同：授予Yusheng Lin的标题为“Semiconductor Copper Metallization Structure and Related Methods (半导体铜金属化结构和相关方法)”的美国专利No. 9905522, 2016年9月1日提交、2018年2月27日发布的申请序列号15254640 (‘522专利)，以及授予Yusheng Lin的标题为“Semiconductor Backmetal (BM) and Over Pad Metallization (OPM) Structures and Related Methods (半导体背金属(BM)和接垫上金属化(OPM)结构和相关方法)”的美国专利No. 9640497, 2016年6月30日提交、并于2017年5月2日发布的申请序列号15198859 (‘497专利)，这些专利中的每个的公开内容据此以引用方式全文并入本文。

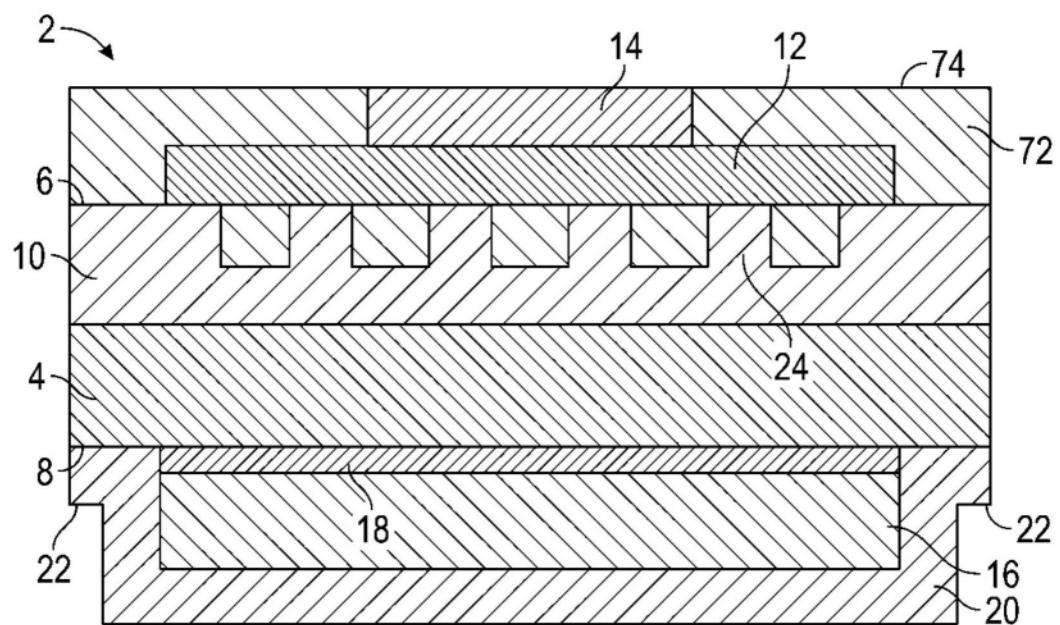

[0062] 在各种实施方式中，本文中公开的半导体器件可以是功率半导体器件，通过非限制性示例，诸如为金属氧化物半导体场效应晶体管 (MOSFET) 或绝缘栅双极晶体管 (IGBT)。在其他实施方式中，器件可以为其他类型的功率半导体器件，或者可以为不是功率半导体器件的半导体器件。参见图1，示出了半导体器件的第一实施方式的横截面侧视图。半导体器件2包括具有第一侧6和第二侧8的管芯4。管芯4可包括硅，并且在各种实施方式中，可包括外延部分10。应当理解，在本公开涉及硅管芯的情况下，硅管芯可以是任何类型的硅管芯，通过非限制性示例，包括外延硅管芯、绝缘体上硅、多晶硅、它们的任何组合、或任何其他含硅管芯材料。另外，还应当理解，在各种实施方式中，可以使用除含硅管芯之外的管芯，通过非限制性示例，诸如砷化镓或含金属的管芯。在图1所示的实施方式中，半导体器件可以是沟槽MOSFET器件，如管芯4的外延部分10中的图案化部分24所指示，示出沟槽的位置，然而，其他实施方式可以不包括沟槽MOSFET结构，但是可包括可以是或可以不是功率半导

体器件的不同半导体器件。在各种实施方式中,管芯4的厚度可为约25微米(μm),约40μm,约75μm,大于约75μm,介于约25μm和约75μm之间,小于约30μm,并且小于约25μm。

[0063] 在各种实施方式中,半导体器件2可包括耦接到管芯4的第一侧6的导电层12。导电层可以是金属或金属合金,并且在此类实施方式中,通过非限制性示例,可包括铝、铜、金、银、钛、镍、任何其他金属、以及它们的任何组合。在各种实施方式中,导电层12的长度和宽度可与管芯4一样,然而,在其他实施方式中,诸如图1所示,导电层的长度或宽度可小于管芯4的长度或宽度。

[0064] 在各种实施方式中,半导体器件2可包括耦接到导电层的接触接垫14。接触接垫14可以是本文所公开的任何类型的金属或金属合金。在特定实施方式中,接触接垫可以是SnAg或NiAu。接触接垫14的长度和宽度可与导电层12一样,然而,在其他实施方式中,诸如图1所示,接触接垫的长度或宽度可小于导电层12的长度或宽度。在各种实施方式中,除了导电层12之外,半导体器件2可以不包括接触接垫14,但是可使用导电层作为接触接垫。类似地,在特定实施方式中,半导体器件2可以不包括导电层12,但是可包括直接耦接到管芯4的第一侧6的接触接垫14。

[0065] 在各种实施方式中,中间接垫可耦接在导电层12和接触接垫14之间。中间接垫可以是使用电镀沉积的金属,并且在特定实施方式中,可以是电镀铜。在特定实施方式中,中间接垫可包括金属合金,并且通过非限制性示例,可包括Ni、Au、Pd、Cu、或它们的任何组合。在各种实施方式中,中间接垫可具有不同的宽度,其中中间接垫的直接耦接到导电层12的第一部分的横截面宽度小于中间接垫的直接耦接到接触接垫14的第二部分。在其他实施方式中,中间接垫的第一部分的横截面宽度可与中间接垫的第二部分相同。

[0066] 在各种实施方式中,如图1所示,半导体器件可包括耦接在管芯4上方的钝化材料72。钝化材料的表面74可与由接触接垫14的暴露表面形成的平面共面。在包括中间接垫的实施方式中,钝化层可仅覆盖中间接垫的一部分,使整个接触接垫14不直接耦接到钝化层。在特定实施方式中,钝化材料可至少部分地包封导电层12。通过非限制性示例,钝化材料可以是SiN、SiO<sub>2</sub>、或任何其他类型的钝化材料。

[0067] 仍然参见图1,半导体器件2包括耦接到管芯4的第二侧8的金属层/背金属层16。在各种实施方式中,通过非限制性示例,金属层可包括铜、金、银、铝、钛、镍、任何其他金属、以及它们的任何组合。在特定实施方式中,金属层16可与‘522专利和‘497专利中公开的背金属层相同或相似,这两个专利之前以引用方式并入本文。在各种实施方式中,金属层16可包括单一类型的金属或金属合金,而在其他实施方式中,金属层可包括相同或不同金属和/或金属合金的多个金属层。在各种实施方式中,金属层16的厚度可为约10μm,约25μm,约40μm,小于约10μm,介于约10-40μm之间,并且大于约40μm,包括与约200μm一样大的厚度。与管芯4相比,在各种实施方式中,管芯的厚度可不超过金属层16的厚度的约四倍。在更特定的实施方式中,管芯4的厚度可以是金属层16的厚度的约三倍,金属层的厚度的约二点五倍,金属层的厚度的约两倍,或与金属层16的厚度大致相同。在其他实施方式中,管芯4的厚度可大于金属层16的厚度的约四倍,或者小于金属层16的厚度。

[0068] 在各种实施方式中,半导体器件2可包括在管芯4的第二侧8与金属层16之间的晶种层18。晶种层18可被配置为促进金属层16和管芯4之间的接合并且/或者在电镀操作期间提供电沉积开始的位置。晶种层18可包括金属或金属合金,并且在特定实施方式中,可包括

TiCu或TiWCu。在其他实施方式中,晶种层18可包括本文先前公开的任何金属。

[0069] 在各种实施方式中,半导体器件2可包括耦接到金属层16的模制化合物/树脂/保护涂层(下文中称为“模制化合物”20)。尽管本文中使用术语“模制化合物”来描述金属层上方的材料,但应当理解,如本文所用,该术语包括许多类型的树脂、环氧树脂和其他种类的保护涂层。在特定实施方式中,模制化合物20可直接耦接到金属层16,并且在甚至更特定的实施方式中,模制化合物可直接耦接在金属层上方。如图1所示,模制化合物20可包封金属层16。在其他实施方式中,如本文稍后所示和所讨论的,金属层16可通过模制化合物20暴露。模制化合物20的侧壁22可以是阶梯状的,然而,在其他实施方式中,侧壁22可以不包括台阶。

[0070] 图1的半导体器件连同本文公开的其他半导体器件可耦接到其他半导体器件或与其他半导体器件配对,其他半导体器件可以是相同类型或不同类型的半导体器件。在各种实施方式中,半导体器件可通过金属层16配对和/或电/热耦接在一起。通过非限制性示例,器件也可以使用引线接合、导电迹线或任何其他耦接方式配对在一起。

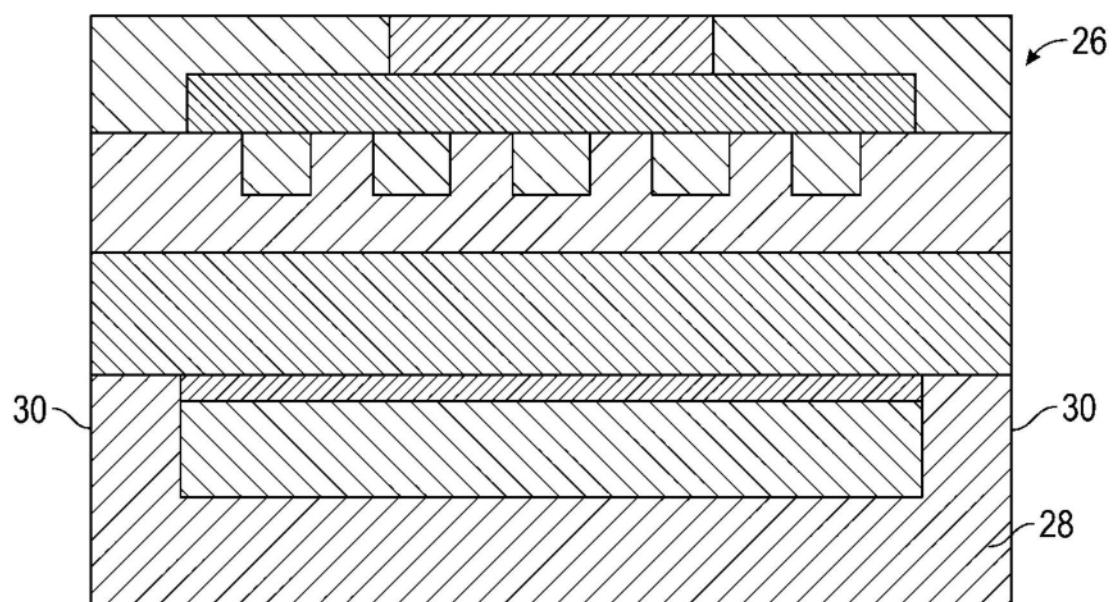

[0071] 参见图2,示出了半导体器件的第二实施方式的剖视图。半导体器件26类似于图1的半导体器件2,不同之处在于模制化合物28比图1的模制化合物20更厚。然而,在各种实施方式中,模制化合物可比图1所示的模制化合物的厚度更薄。另外,在各种实施方式中,模制化合物28的侧壁30不是阶梯状的。

[0072] 参见图3,示出了半导体器件的第三实施方式的横截面侧视图。半导体器件32类似于图1的半导体器件2,不同之处在于金属层34的长度和宽度与管芯4的长度和宽度相同。通过与管芯的长度和宽度相同,金属层暴露在半导体器件的侧壁上。半导体器件32还可包括耦接到金属层34的模制化合物36。如图3所示,模制化合物可直接耦接到金属层,而不直接耦接到金属层34的任何侧壁38。在各种实施方式中,图3的半导体器件可与任何数量的其他半导体器件配对。其他半导体器件可与图3所示的器件相同。在此类实施方式中,器件可并排定位,使得金属层16直接接触另一个半导体器件的金属层,从而允许半导体器件通过半导体器件背面上的金属层电配对。

[0073] 在其他实施方式中,半导体器件可具有耦接在金属层34上方的导电层来代替模制化合物36。导电层可以是本文所公开的任何类型的导电层。这样的实施方式类似于本文的图5所示的实施方式,不同之处在于导电层和金属层的侧壁可与管芯的侧壁共同延伸。

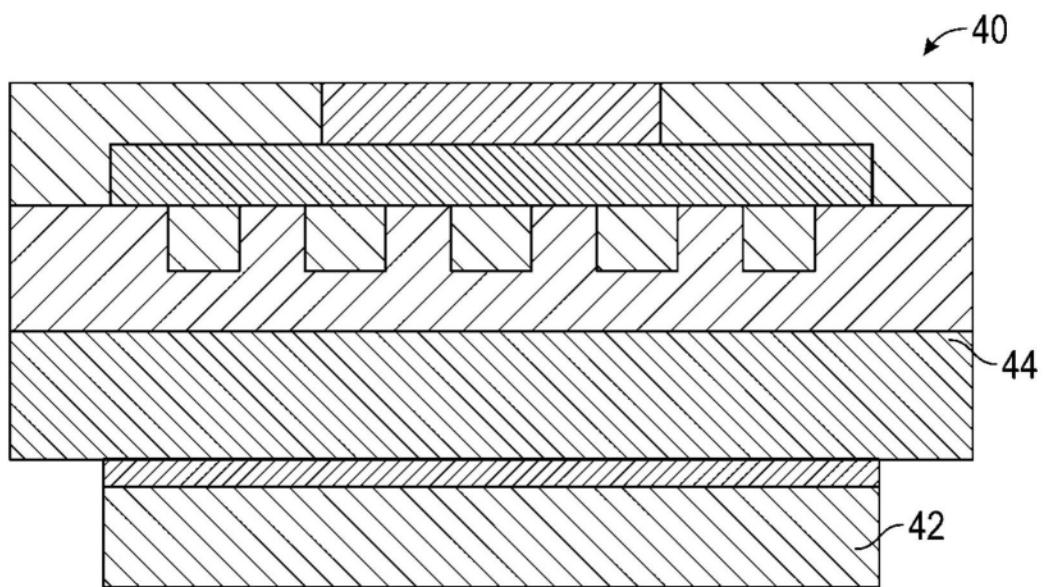

[0074] 参见图4,示出了半导体器件的第四实施方式的横截面侧视图。半导体器件40可类似于图1的半导体器件,不同之处在于没有耦接到金属层42的模制化合物。在此类实施方式中,金属层的周边可与管芯44的侧面共同延伸,如图3的金属层所示,或者金属层42的周边可从管芯的侧面设置,如图4所示。

[0075] 参见图5,示出了半导体器件的第五实施方式的剖视图。半导体器件46可类似于图4的半导体器件,不同之处在于导电层48形成在金属层50上方。在各种实施方式中,层可以是导热的和/或导电的。在各种实施方式中,导电层可以是第二金属层并且可包括本文所公开的任何金属或金属合金,通过非限制性示例,包括Ni、SnAg和NiAu。在特定实施方式中,导电层48可以是凸块或接垫。导电层、凸块或接垫可以与金属层50的侧面52共同延伸或者可以不与其共同延伸。

[0076] 参见图6,示出了半导体器件的第六实施方式的剖视图。半导体器件54可类似于图

4的半导体器件,不同之处在于模制化合物56直接耦接到金属层60的侧壁58。因为模制化合物56仅耦接到金属层60的侧壁,所以金属层的与由管芯的最大表面形成的平面平行的表面通过模制层56暴露。

[0077] 参见图7,示出了半导体器件的第七实施方式的剖视图。半导体器件62可类似于图5的半导体器件,不同之处在于模制化合物64直接耦接到金属层66和耦接在金属层上方的导电层68两者的侧壁。在图7所示的实施方式中,模制化合物不在导电层68上方,因此导电层可通过模制化合物64暴露。导电层可与图5的导电层相同或相似。

[0078] 贯穿本公开,术语“上方”相对于各种层和元件使用。该术语不意味着表达在附图中向上或向下的位置,而是意在表达相对外部位置。例如,使用图7的上(之上)和下(之下)方向,放置在管芯70之上的层将在管芯“上方”,并且放置在金属层66之下的层将类似地在金属层“上方”。

[0079] 参见图8,示出了示出半导体器件的各种实施方式的导通电阻的曲线图。图表的Y轴示出导通电阻,以毫欧( $\text{m}\Omega$ )计。图表的X轴示出硅管芯的厚度,以微米计。具有不同厚度的背金属的管芯的电阻由曲线图中的四条线示出。如曲线图所示,随着硅层厚度的减小,导通电阻减小,并且随着背金属的厚度增加,导通电阻也减小。第一个星形表示第一半导体器件,其具有厚度为 $125\mu\text{m}$ 的硅管芯以及厚度为 $6\mu\text{m}$ 的背金属层。其具有 $2.6\text{m}\Omega$ 的导通电阻。第二个星形表示第二半导体器件,其具有厚度为 $75\mu\text{m}$ 的硅管芯以及厚度为 $15\mu\text{m}$ 的背金属层。第二半导体器件的导通电阻为 $1.9\text{m}\Omega$ 。第三个星形表示第三半导体器件,其具有厚度为 $25\mu\text{m}$ 的硅管芯以及厚度为 $15\mu\text{m}$ 的背金属层。第三半导体器件具有 $1.6\text{m}\Omega$ 的导通电阻。如曲线图所示,随着硅层厚度的减小,导通电阻减小,并且随着背金属的厚度增加,导通电阻也减小。这种低导通电阻对于在各种应用(包括快速充电系统)中使用的半导体器件可能是有益的。另外,通过显著减小管芯的厚度,半导体封装的整体尺寸可减小。

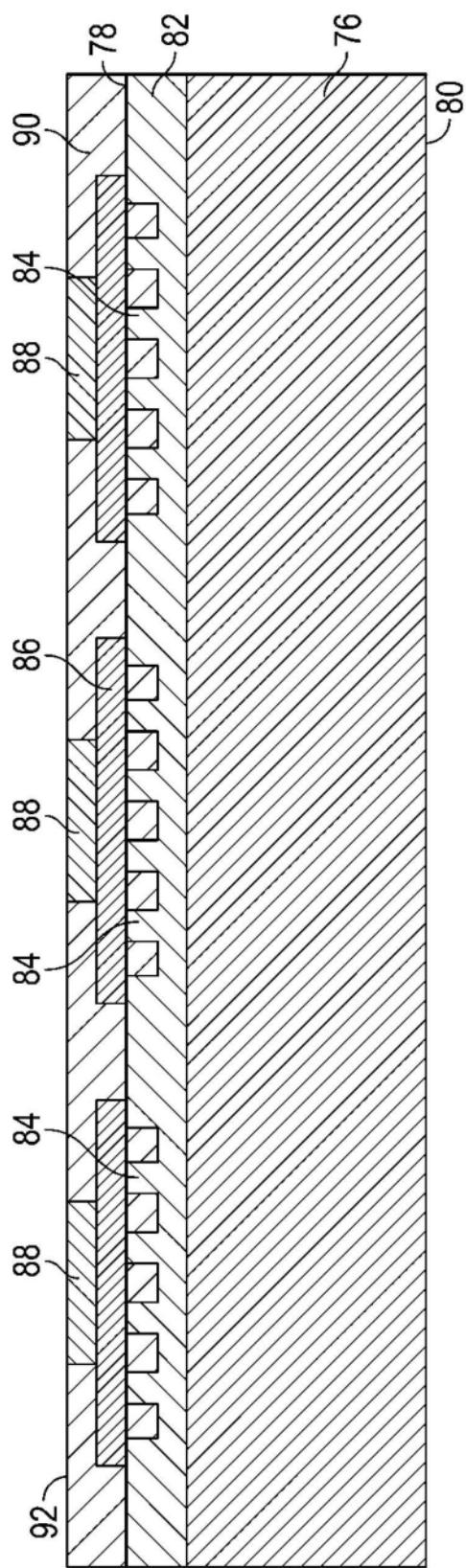

[0080] 参见图9-图24,示出了用于形成图1-图7中所示的各种半导体器件的各种方法。具体参见图9,示出了晶圆的剖视图。在各种实施方式中,形成半导体器件的方法包括提供具有第一侧78和第二侧80的晶圆76。在各种实施方式中,晶圆76可以是硅。应当理解,在本公开涉及硅层的情况下,硅层可以是任何类型的硅层,通过非限制性示例,包括外延硅层、绝缘体上硅、多晶硅、它们的任何组合、或任何其他含硅衬底材料。如图9所示,晶圆76可包括外延硅部分82。另外,还应当理解,在各种实施方式中,可以使用除含硅衬底之外的衬底,通过非限制性示例,诸如砷化镓或含金属的衬底。在各种实施方式中,该方法可包括在晶圆76内部分/完全地形成多个半导体器件。在特定实施方式中,多个功率半导体器件可部分/完全地形成在外延硅部分82内,通过非限制性示例,包括MOSFET、IGBT、或任何其他功率半导体器件。在图9所示的实施方式中,多个沟槽MOSFET 84部分地形成在外延硅部分82内。形成在晶圆76内的功率半导体器件的部分可包括接线/布线,以允许半导体器件在使用时连接到其他封装部件和/或电路。在此类实施方式中,接线可以是铝或本文所公开的任何其他导电材料。

[0081] 在各种实施方式中,用于形成半导体器件的方法可包括在晶圆76的第一侧78上方形成导电层86。在各种实施方式中,并且如图9所示,导电层可被图案化,然而,在其他实施方式中,导电层可以不被图案化。导电层可以是金属或金属合金,并且在此类实施方式中,通过非限制性示例,可包括铝、铜、金、银、钛、镍、任何其他金属、以及它们的任何组合,包括

本文所公开的那些。

[0082] 在各种实施方式中,用于形成半导体器件的方法可包括形成耦接晶圆76的第一侧78的多个接触接垫88。如图9所示,导电层86可将接触接垫88与晶圆76分离。在其他实施方式中,该方法可包括将接触接垫直接形成到晶圆,以及从形成半导体器件的过程中省略导电层。在各种实施方式中,多个接触接垫88可形成焊料顶部金属(STM),并且可由任何金属或金属合金制成。在特定实施方式中,多个接触接垫可以是NiAu。在此类实施方式中,NiAu接触接垫可通过化学镀形成到导电层86或晶圆76上。多个接触接垫88可被认为是在晶圆76的源极侧上。

[0083] 仍然参见图9,形成半导体器件的方法可包括将钝化层90施加到晶圆76、导电层86和/或多个接触接垫88。钝化层90可以是本文先前公开的任何类型的钝化层。钝化层90可至少部分地包封导电层86。另外,多个接触接垫88可通过钝化层90暴露。在特定实施方式中,钝化层90最初可覆盖多个接触接垫88,并且多个接触接垫88可通过背面研磨或化学机械抛光(CMP)钝化层而通过钝化层暴露。另外,如图9所示,钝化层90的表面92可与由多个接触接垫88的暴露部分形成的平面共面。通过非限制性示例,可使用CMP技术来平坦化钝化层90和多个接触接垫88。

[0084] 在其他实施方式中,用于形成半导体封装的方法可包括在导电层86和接触接垫88之间形成中间层。中间层可以是电镀金属层,并且在特定实施方式中,可以是电镀铜。中间层可包括合金,通过非限制性示例,包括Ni、Au、Pd、Cu、以及它们的任何组合。在其他实施方式中,中间层可溅射到导电层86上。在各种实施方式中,形成中间层的方法可包括在中间层内形成多个层。在此类实施方式中,多个层中的一个可以是晶种层,该晶种层可包括Ti或Cu。在特定实施方式中,形成半导体封装的方法可包括将中间层图案化成多个中间接垫。在形成中间层的方法包括在中间层内形成多个层的情况下,中间层内的每个层可以具有不同的图案,这些图案形成具有阶梯状侧壁的中间接垫。在形成中间层的过程期间,可在形成接垫88的材料形成之后蚀刻晶种层。作为示例,中间层可被图案化以形成多个中间接垫,该中间接垫具有直接耦接到导电层的第一部分,该第一部分的横截面宽度小于多个中间接垫的直接耦接到接触接垫88的第二部分。在其中形成中间接垫的实施方式中,钝化层可完全或部分地覆盖中间接垫的侧壁。

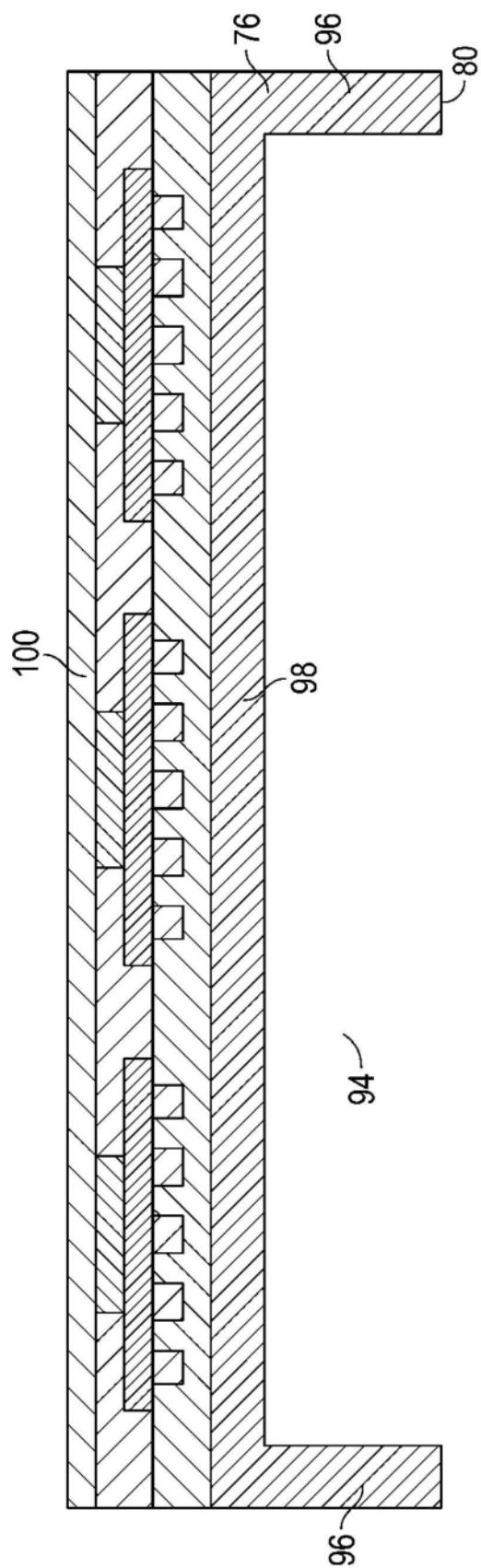

[0085] 参见图10,示出了具有形成在其中的凹槽的图9的晶圆的横截面侧视图。在各种实施方式中,形成半导体器件的方法包括在晶圆76的第二侧80中形成凹槽94。通过形成凹槽94,可以减薄晶圆76。在各种实施方式中,凹槽94可通过背面研磨晶圆76的第二侧80来形成。在此类实施方式中,背面研磨带100可耦接到接触接垫。在特定实施方式中,凹槽94可使用由日本东京的DISCO公司(DISCO, Tokyo, Japan)以商品名TAIKO销售的工艺通过背面研磨而形成。背面研磨留下未移除材料的环96(TAIKO环),这有助于防止晶圆在处理期间卷曲、翘曲或以其他方式弯曲,同时移除第二侧80或晶圆76的背面的大部分厚度和材料。在形成半导体器件的方法的其他实施方式中,可以不使用TAIKO工艺,但是可使用一些其他背面研磨或其他材料移除技术,诸如通过湿法蚀刻移除材料。在各种实施方式中,晶圆76的减薄部分98的厚度可被减薄到约25 $\mu\text{m}$ ,约40 $\mu\text{m}$ ,约75 $\mu\text{m}$ ,大于约75 $\mu\text{m}$ ,介于约25 $\mu\text{m}$ 和约75 $\mu\text{m}$ 之间,小于约30 $\mu\text{m}$ ,并且小于约25 $\mu\text{m}$ 。

[0086] 参见图11,示出了图10的晶圆的横截面侧视图,其中掩膜形成在凹槽中。掩模可使

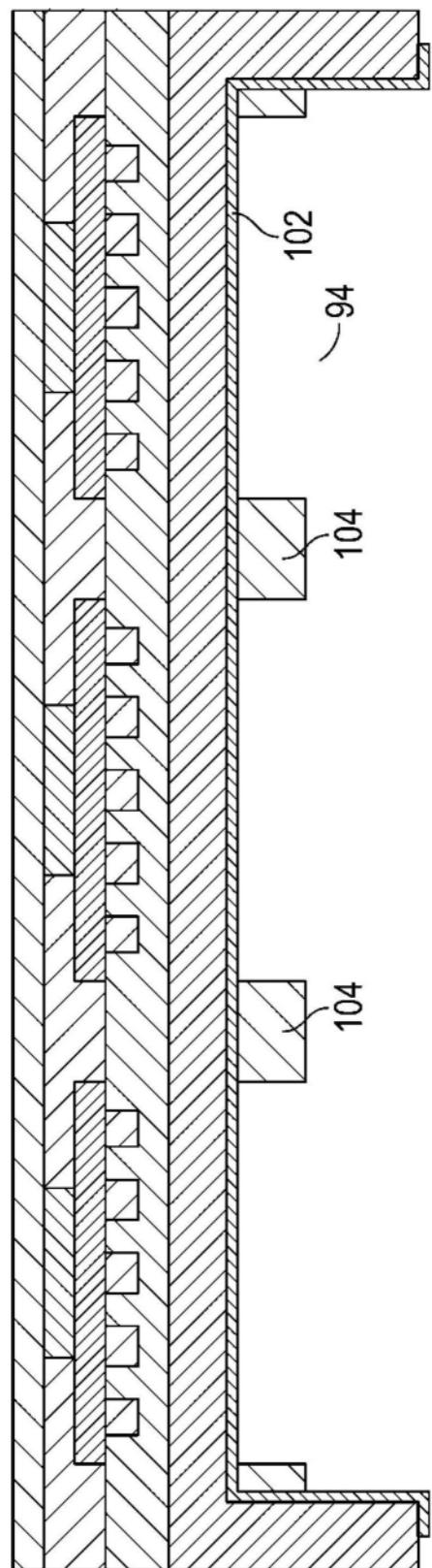

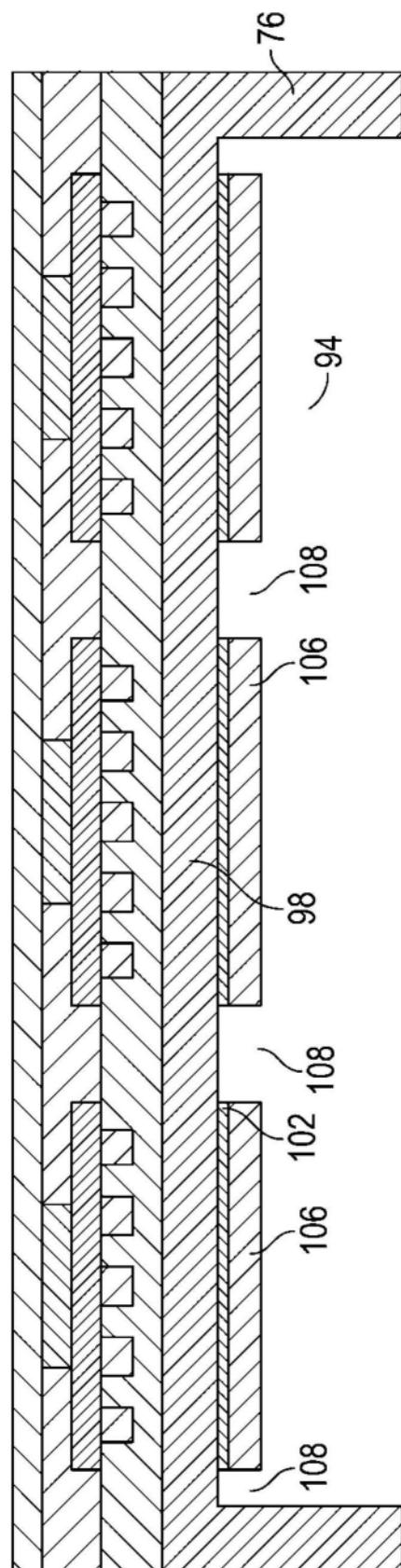

用各种工艺形成,通过非限制性示例,包括光刻法、膜附接以及在凹槽中形成图案的其他方法。该方法还可包括在凹槽94内形成图案化的光致抗蚀剂层104。在各种实施方式中,形成半导体器件的方法还包括在形成掩模之前或之后用晶种层102涂覆凹槽94。晶种层102可以是金属或金属合金。在特定实施方式中,晶种层可以是TiCu或TiWCu。在各种实施方式中,凹槽的内部可通过溅射用晶种层102涂覆。参见图12,示出了图10的晶圆的横截面侧视图,其中金属层形成在凹槽中。在各种实施方式中,形成半导体器件的方法可包括在凹槽94内形成金属层106或背金属。金属层106可包括铜、铝、金、银、镍、钛、任何其他金属、以及它们的任何组合。在晶种层102耦接到凹槽94内的晶圆76的实施方式中,金属层106可通过晶种层102耦接到晶圆76。在一些实施方式中,金属层可通过镀铜或其他金属镀覆工艺施加。在其他实施方式中,金属层可使用溅射或蒸发工艺来施加。

[0087] 在各种实施方式中,金属层106可包括多层相同或不同的金属,而在其他实施方式中,金属层可仅包括单层金属。在各种实施方式中,金属层106的厚度可为约10 $\mu\text{m}$ ,约25 $\mu\text{m}$ ,约40 $\mu\text{m}$ ,小于约10 $\mu\text{m}$ ,介于约10-40 $\mu\text{m}$ 之间,并且大于约40 $\mu\text{m}$ ,包括与约200 $\mu\text{m}$ 一样大的厚度。与晶圆76的减薄部分98相比,在各种实施方式中,晶圆的减薄部分的厚度不超过金属层106的厚度的约四倍。在更特定的实施方式中,晶圆76的减薄部分98的厚度可以基本上是金属层106的厚度的三倍,金属层的厚度的二点五倍,金属层的厚度的两倍,或与金属层106的厚度大致相同。在其他实施方式中,晶圆76的减薄部分98的厚度可大于金属层106的厚度的约四倍,或者小于金属层106的厚度。

[0088] 在特定实施方式中,并且如图12所示,该方法可包括在金属层106内图案化或形成开口108。图11的光致抗蚀剂层104可用于形成开口108或金属层106的图案。在凹槽94内形成金属层106之后,光致抗蚀剂层104以及晶种层102的部分可被剥离。在各种实施方式中,金属层106可以不包括切割道,当要切割晶圆时,该切割道可减少晶圆76(以及因此,经切割的管芯)的碎屑。

[0089] 参见图13,示出了图12的晶圆的剖视图,其中模制化合物形成在金属层上方。形成半导体器件的方法可包括将模制化合物112与凹槽94内的金属层106耦接。可以施加模制化合物112以防止金属层106的氧化以及保护金属层免受物理损坏。在各种实施方式中,模制化合物112可直接耦接在金属层106上方,如图13所示。在其中金属层106被图案化的实施方式中,模制化合物112还可在金属层106内的开口108内。在各种实施方式中,模制化合物112可具有基本上恒定的厚度,因此开口108并未完全用模制化合物112填充。通过非限制性示例,可使用液体分配技术、传递模制技术、打印机模制技术、压缩模制技术或层压技术来将模制化合物112施加到金属层106。在各种实施方式中,通过非限制性示例,模制化合物112可以是环氧树脂模制化合物、丙烯酸模制化合物或任何其他类型的模制化合物或保护性覆盖物。

[0090] 参见图14,示出了图13的晶圆的横截面侧视图,其中移除晶圆的环的一部分。在各种实施方式中,用于形成半导体器件的方法可包括移除环96的一部分。在特定实施方式中,环96的部分可通过背面研磨环96来移除。在其他实施方式中,可使用其他去除技术或方法至少部分地移除环,诸如围绕晶圆的边缘循环地锯切掉环。在各种实施方式中,移除足够的环96,使得环96或晶圆76的表面114与模制化合物112的表面116共面。在其他实施方式中,环部分可被部分地移除,但是不会到使环96的表面114与模制化合物112的表面116平坦化

的程度。在各种实施方式中,该方法可包括从晶圆76的源极侧移除背面研磨带90,以及将新的背面研磨/切割带118施加到接触接垫,如图14所示。

[0091] 参见图15,示出了与施加到模制化合物的带一起旋转的图14的晶圆的横截面侧视图。用于形成半导体器件的方法可包括将带施加到晶圆76的背面,或者施加到模制化合物112。在各种实施方式中,并且如图15所示,晶圆76可从背面研磨/切割带118移除,如图14所示,并且晶圆可与晶圆和/或模制化合物112的背面一起旋转,重新施加到背面研磨带118(或者最初施加到锯切带以用于切割),如图15所示。

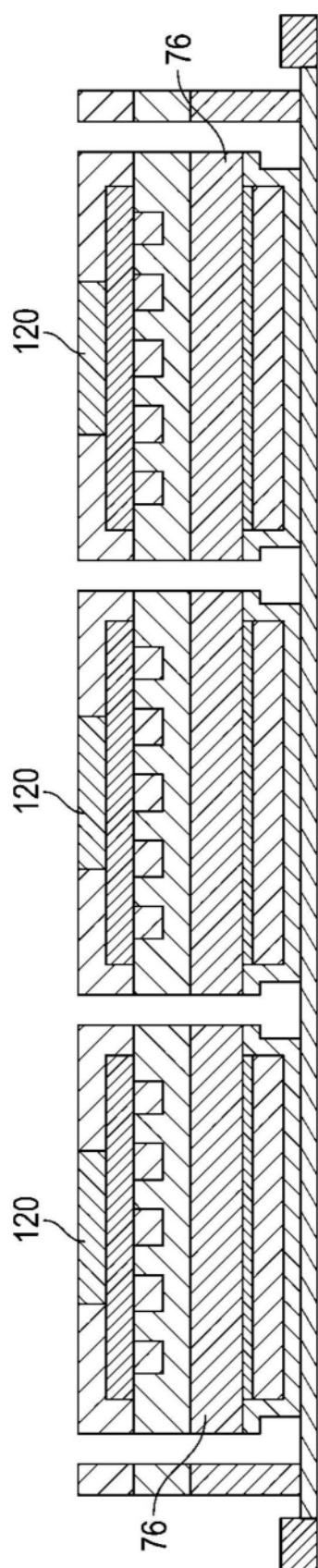

[0092] 参见图16,示出了切割的图15的晶圆的横截面侧视图。用于形成半导体器件的方法包括将晶圆76切割成多个半导体器件120。通过非限制性示例,可以通过刀片切割、激光切割、水射流切割、蚀刻或任何其他切割方法来切割晶圆76。如图16所示,半导体器件120中的每个与图1所示的半导体器件2相同。

[0093] 参见图17-图18,示出了形成图1的半导体器件的替代方法。具体参见图17,示出了图13的晶圆的横截面侧视图,其中带被施加到模制化合物。图17示出该方法可包括将带122施加到模制化合物112并且施加到晶圆76的环96,而不是背面研磨环96,如图14所示。然后,如切口124所指示,可通过切穿钝化层90、晶圆76和模制化合物112从金属层移除环96。参见图18,示出了切割后的图17的晶圆的横截面侧视图。该方法可包括将晶圆76切割成多个半导体器件126。可使用本文所公开的任何切割方法来切割晶圆。图18所示的多个半导体器件126可与图1所示的半导体器件2相同。

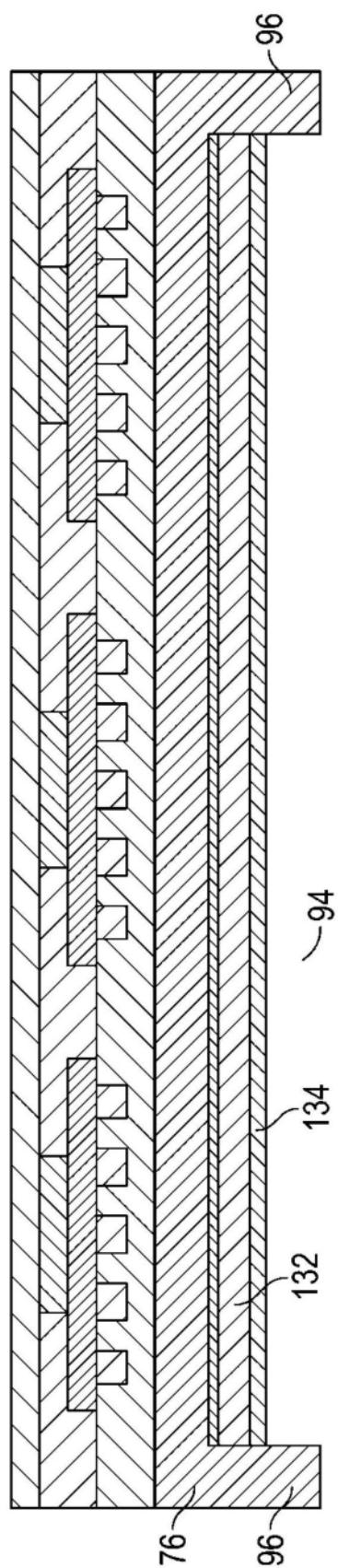

[0094] 参见图19,示出了图12的晶圆的横截面侧视图,其中模制化合物填充凹槽。图19示出了用于形成半导体器件的替代方法。图19所示的方法可包括用模制化合物128完全填充凹槽94,而不是形成在覆盖金属层106的保护涂层的整个长度上具有一致厚度的模制化合物112,如图13所示。模制化合物128可使用本文所公开的任何技术施加到凹槽,并且可以是本文所公开的任何类型的模制化合物或其他保护涂层。如图19所示,与图13相反,模制化合物128的外表面130具有不遵循图案化金属层106的轮廓的平滑表面,因此模制化合物128可具有不同的厚度。换句话讲,模制化合物128可完全填充金属层106内的开口108。模制化合物128可增加芯片强度,并且在其中晶圆76的减薄部分98的厚度小于约30 $\mu\text{m}$ 的实施方式中可尤其有用。

[0095] 在其他实施方式中,模制化合物可仅部分地填充凹槽,而不是使模制化合物128完全填充凹槽94。在此类实施方式中,模制化合物128的外表面130仍然可具有不遵循图案化金属层106的轮廓的平滑表面,然而,外表面130可以不与环96的端部共面。

[0096] 仍然参见图19,在各种实施方式中,用于形成半导体器件的方法可包括背面研磨环96、模制化合物128,或环和模制化合物两者。然后可使用本文先前公开的任何切割方法将晶圆76切割成多个半导体器件。多个切割的半导体器件可与图2中所示的半导体器件26相同。因为模制化合物128完全填充金属层106内的开口108,所以切割的半导体器件可以具有模制化合物28,该模制化合物具有不是阶梯状的侧壁30,如图2所示。

[0097] 参见图20,示出了图10的晶圆的横截面侧视图,其中非图案化金属层形成在凹槽内。图20示出了用于形成半导体器件的替代方法。该方法可包括形成耦接到晶圆76的固体金属层132,而不是形成图案化金属层106,如图11-图12所示。在各种实施方式中,晶种层102可在金属层132和晶圆76之间。该方法可包括用可为模制化合物134的保护涂层涂覆金

属层132。模制化合物134可部分地填充凹槽94,而在其他实施方式中,其可完全填充凹槽94。在各种实施方式中,用于形成半导体器件的方法可包括背面研磨环96、模制化合物134,或环和模制化合物两者。然后可使用本文先前公开的任何切割方法将晶圆76切割成多个半导体器件。多个切割的半导体器件可与图3中所示的半导体器件32相同。通过不对金属层132进行图案化,与图11-图12所示的方法相比,该方法可潜在地节省成本。

**[0098]** 在其他实施方式中,用于形成半导体器件的方法可包括将导电层形成到金属层132,而不是用模制化合物134涂覆金属层132。导电层可以是本文所公开的任何类型的导电层,包括Ni、NiAu、SnAg。在各种实施方式中,该方法可包括将导电层镀覆到金属层上,而在其他实施方式中,通过溅射、蒸发或其他沉积技术将导电层施加到金属层。用于形成半导体器件的方法可包括背面研磨环96。然后可使用本文先前公开的任何切割方法将晶圆76切割成多个半导体器件。多个切割的半导体器件可类似于图3中所示的半导体器件32,不同之处在于代替金属层上方的模制化合物,半导体器件具有金属层上方的导电层。

**[0099]** 参见图21,示出了图12的晶圆的横截面侧视图,其中移除晶圆的环的一部分。图21示出了用于形成半导体器件的替代方法。该方法可包括不用任何种类的模制化合物或保护性覆盖物覆盖金属层106,而不是在金属层106上方形成模制化合物,如图13和图19所示。在各种实施方式中,用于形成半导体器件的方法可包括背面研磨环96。然后可使用本文先前公开的任何切割方法将晶圆76切割成多个半导体器件。多个切割的半导体器件可与图4中所示的半导体器件40相同。

**[0100]** 参见图22,示出了图21的晶圆的横截面侧视图,其中凸块形成在金属层上方。图22示出了用于形成半导体器件的替代方法。该方法可包括在金属层106上方形成多个凸块/接垫136,而不是使金属层106未被覆盖,如图21所示。在各种实施方式中,多个凸块136可被认为是金属层106上方的第二金属层。多个凸块136可以是本文所公开的任何类型的材料。在各种实施方式中,用于形成半导体器件的方法可包括背面研磨环96。然后可使用本文先前公开的任何切割方法将晶圆76切割成多个半导体器件。多个切割的半导体器件可与图5中所示的半导体器件46相同。

**[0101]** 参见图23,示出了图21的晶圆的横截面侧视图,其中模制化合物形成在金属层中的开口之间。图23示出了用于形成半导体器件的替代方法。与图21中所示相反,图23所示的方法包括将模制化合物138耦接在金属层106的开口108内,同时使金属层通过模制化合物138暴露。模制化合物138的外表面可与金属层106的外表面共面或基本上共面。在各种实施方式中,模制化合物138最初可覆盖金属层106,如图19所示,但是然后可被背面研磨以通过模制化合物138暴露金属层106。在各种实施方式中,用于形成半导体器件的方法可包括背面研磨环96、模制化合物138,或环和模制化合物两者。然后可使用本文先前公开的任何切割方法将晶圆76切割成多个半导体器件。多个切割的半导体器件可与图6中所示的半导体器件54相同。

**[0102]** 参见图24,示出了图22的晶圆的横截面侧视图,其中模制化合物形成在金属层中的开口之间。图24示出了用于形成半导体器件的替代方法。与图22中所示相反,图24所示的方法包括将模制化合物140耦接在金属层106的开口108内,同时使多个凸块136、或第二金属层通过模制化合物140暴露。模制化合物140的外表面可与多个凸块136的外表面共面。在各种实施方式中,模制化合物140最初可覆盖多个凸块136,但是然后可被背面研磨以通过

模制化合物140暴露多个凸块。在各种实施方式中,用于形成半导体器件的方法可包括背面研磨环96、模制化合物140,或环和模制化合物两者。然后可使用本文先前公开的任何切割方法将晶圆76切割成多个半导体器件。多个切割的半导体器件可与图7中所示的半导体器件62相同。

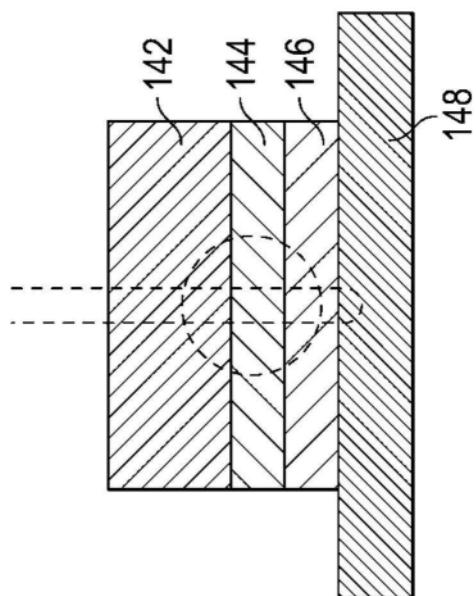

[0103] 参见图25A-图25B,示出了用于切割具有施加到其上的背面保护(BSP)层的工艺。图25A-图25B所示的方法可被并入本文先前公开的任何方法实施方式中。如图25A所示,晶圆142可耦接到金属层144。在各种实施方式中,金属层可耦接到BSP层146。在各种实施方式中,BSP层可以是包括环氧树脂的带,并且可包括玻璃填料。在特定实施方式中,BSP层可以是由日本东京的琳得科公司(LINTEC Corporation, Tokyo, Japan)以商品名ADWILL<sup>®</sup>销售的晶圆背面涂覆带。BSP层可耦接到用于在晶圆的切割期间保持晶圆的带148。

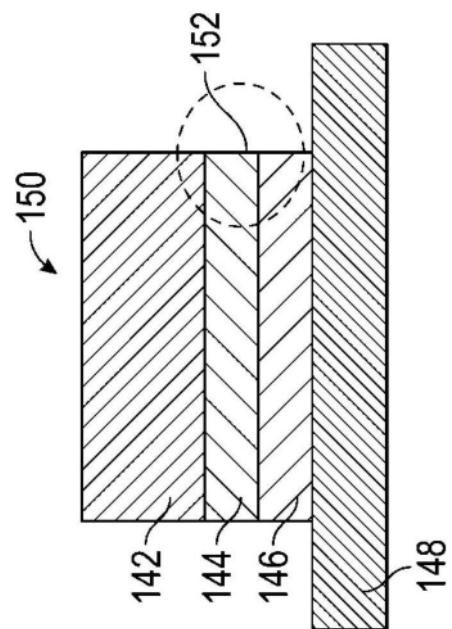

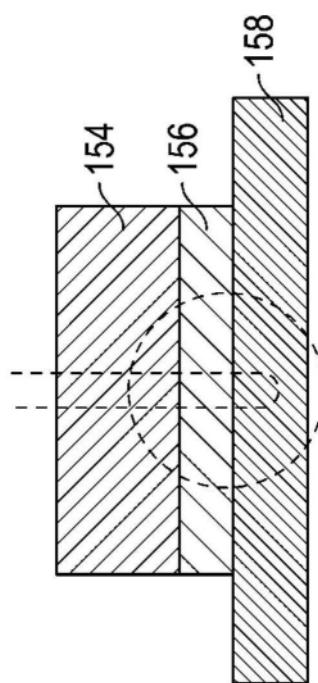

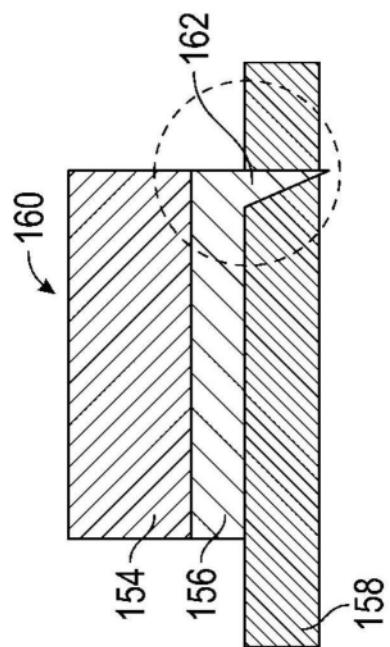

[0104] 图25B示出在切割以形成半导体器件150之后的晶圆142、金属层144和BSP层146。如图25B所示,其中晶圆、金属层和BSP被切割的侧壁152形成清洁切口,意味着不同的层不延伸到相邻层中,包括带148。与此相反,并且参见图26A-图26B,示出了用于切割不具有施加到其上的BSP层的工艺。图26A示出耦接到金属层156的晶圆154,该金属层直接耦接到用于在切割期间保持晶圆的带158。如图26B所示,其示出切割成半导体器件160的图26A的晶圆和金属层,由切割金属层156产生的材料毛刺162可延伸到带158中。在各种实施方式中,切割直接耦接到非BSP带的金属层可产生类似于毛刺162的毛刺,这可妨碍在管芯拾取操作期间从带158移除半导体器件160。

- [0105] 在本文所公开的半导体器件的各种实施方式中,管芯的厚度可小于30微米。

- [0106] 在其他实施方式中,管芯基本上与金属层的厚度一样厚。

- [0107] 在各种实施方式中,模制化合物可直接耦接到器件的金属层。

- [0108] 在各种实施方式中,模制化合物可直接耦接在金属层上方。

- [0109] 在如同本文所公开的那些的形成半导体器件的方法的各种实施方式中,该方法可包括在接触接垫与晶圆的第一侧之间形成导电层。

- [0110] 在各种方法实施方式中,金属层的厚度与晶圆的厚度基本上相同。

- [0111] 在各种方法实施方式中,金属层的厚度基本上是晶圆的厚度的三倍。

- [0112] 在方法的各种实施方式中,模制化合物可包封金属层。

- [0113] 在各种方法实施方式中,该方法还包括用晶种层涂覆凹槽。

- [0114] 在各种方法实施方式中,该方法包括在金属层上方形成多个凸块。

- [0115] 在各种方法实施方式中,该方法可包括将金属层、模制化合物或多个凸块耦接到背面保护层,然后切割晶圆。

- [0116] 在以上描述中提到半导体器件的具体实施方式以及实施部件、子部件、方法和子方法的地方,应当易于显而易见的是,可在不脱离其实质的情况下作出多种修改,并且这些实施方式、实施部件、子部件、方法和子方法可应用于其他半导体器件。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21

图22

图23

图24

图25A

图25B

图26A

图26B