### CORRECTED VERSION

## (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 15 November 2007 (15.11.2007) PCT

# (10) International Publication Number WO 2007/131127 A3

(51) **International Patent Classification:** *GUC* 16/12 (2006 01) *GHC* 11/56 (2006 01)

(21) International Application Number:

PCT/US2007/068172

(22) International Filing Date: 3 May 2007 (03 05 2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

11/381,996 5 May 2006 (05 05 2006) US 11/382,000 5 May 2006 (05 05 2006) US

- (71) **Applicant** (for all designated States except US): **SAN- DISK CORPORATION** [US/US], 601 McCarthy Blvd ,

Milpitas, CA 95035 (US)

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): LI, Yan [US/US], 695 Kevenaire Drive, Milpitas, CA 95035 (US)

- (74) Agent: PARSONS, Gerald, P., Davis Wπght Tremane LLP, 505 Montgomery Street, Suite 800, San Francisco, CA 9411 1 (US)

- (81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL,

[Continued on next page]

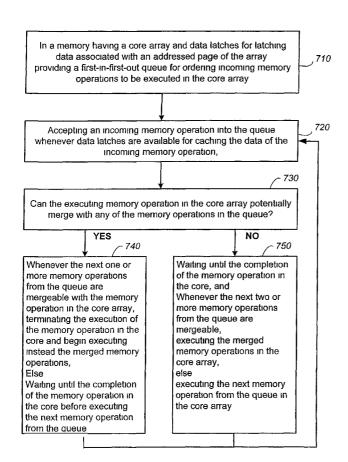

#### (54) Title: MERGING QUEUED MEMORY OPERATION IN A NON-VOLATILE MEMORY

(57) Abstract: Methods and circuitry are present for executing current memory operation while other multiple pending memory operations are queued Furthermore, when certain conditions are satisfied, some of these memory operations are combinable or mergeable for improved efficiency and other benefits The management of the multiple memory operations is accomplished by the provision of a memory operation queue controlled by a memory operation queue manager. The memory operation queue manager is preferably implemented as a module in the state machine that controls the execution of a memory operation in the memory array

## WO 2007/131127 A3

PT, RO, SE, SI, SK, TR), OAPI (BF, **BJ**, CF, CG, CI, CM, **GA**, **GN**, **GQ**, **GW**, **ML**, **MR**, **NE**, **SN**, **TD**, **TG**).

(48) Date of publication of this corrected version:

5 June 2008

#### **Published:**

- with international search report

- (88) Date of publication of the international search report:

3 April 2008

$(15) \ \ Information \ about \ \ Correction:$

see Notice of 5 June 2008