(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4451189号

(P4451189)

(45) 発行日 平成22年4月14日(2010.4.14)

(24) 登録日 平成22年2月5日(2010.2.5)

(51) Int.Cl.

G 11 C 29/56 (2006.01)

F 1

G 11 C 29/00 651 T

請求項の数 14 (全 21 頁)

(21) 出願番号 特願2004-1111494 (P2004-1111494)

(22) 出願日 平成16年4月5日 (2004.4.5)

(65) 公開番号 特開2005-293808 (P2005-293808A)

(43) 公開日 平成17年10月20日 (2005.10.20)

審査請求日 平成19年1月5日 (2007.1.5)

(73) 特許権者 390005175

株式会社アドバンテスト

東京都練馬区旭町1丁目32番1号

(74) 代理人 100104156

弁理士 龍華 明裕

(72) 発明者 佐藤 新哉

東京都練馬区旭町1丁目32番1号 株式

会社アドバンテスト内

審査官 堀江 義隆

最終頁に続く

(54) 【発明の名称】試験装置、位相調整方法、及びメモリコントローラ

## (57) 【特許請求の範囲】

## 【請求項 1】

被試験メモリを試験する試験装置であって、

前記被試験メモリの試験実行前に、前記被試験メモリを実装した状態で、前記被試験メモリの複数の端子のそれぞれについて、前記被試験メモリから出力された、予め書き込まれた試験パターンに対応した出力信号の出力値を、ストローブ信号のタイミングで取得するタイミングコンパレータと、

前記タイミングコンパレータが取得した前記出力値を予め生成された期待値と比較して、比較結果を出力する論理比較器と、

前記論理比較器が出力した前記比較結果に基づいて、前記被試験メモリの複数の端子のそれぞれについて、前記ストローブ信号のタイミングを調整する位相調整制御回路とを備える試験装置。

## 【請求項 2】

前記ストローブ信号を遅延させて前記タイミングコンパレータに供給する第1可変遅延回路をさらに備え、

前記位相調整制御回路は、前記論理比較器が出力した前記比較結果に基づいて、前記第1可変遅延回路による遅延量を設定する請求項1に記載の試験装置。

## 【請求項 3】

前記論理比較器が前記比較結果として出力した、前記出力値と前記期待値とが一致しないことを示すフェイルデータの数を計数するフェイルカウンタと、

前記フェイルカウンタが計数した前記フェイルデータの数を、予め定められた判定値と比較して、判定結果を出力する判定回路とをさらに備え、

前記位相調整制御回路は、前記判定回路が出力した前記判定結果に基づいて、前記第1可変遅延回路による遅延量を設定する請求項2に記載の試験装置。

#### 【請求項4】

前記位相調整制御回路は、2進数データで示される前記第1可変遅延回路による前記遅延量を、前記判定回路が出力した前記判定結果に基づいてバイナリサーチにより上位ビットから順に決定していく請求項3に記載の試験装置。

#### 【請求項5】

セット信号のタイミングで試験パターン信号を立ち上げ、リセット信号のタイミングで前記試験パターン信号を立ち下げて、前記試験パターン信号を前記被試験メモリに供給するS R ラッチと、10

前記セット信号を遅延させて前記S R ラッチに供給する第2可変遅延回路と、

前記リセット信号を遅延させて前記S R ラッチに供給する第3可変遅延回路とをさらに備え、

前記タイミングコンパレータは、前記試験パターン信号に対応して前記被試験メモリから出力された出力信号の出力値を、前記被試験メモリの内部クロックと同期した前記ストローブ信号のタイミングで取得し、

前記論理比較器は、前記タイミングコンパレータが取得した前記出力値を前記期待値と比較して、比較結果を出力し、20

前記位相調整制御回路は、前記論理比較器が出力した前記比較結果に基づいて、前記被試験メモリの複数の端子のそれぞれについて、前記第2可変遅延回路及び前記3可変遅延回路による遅延量を設定する請求項1に記載の試験装置。

#### 【請求項6】

前記被試験メモリの温度又は前記被試験メモリの周囲の温度の変化を検出する温度検出部と、

前記温度検出部が検出した温度変化が予め定められた温度変化以上である場合に、前記被試験メモリの複数の端子のそれぞれについて、前記ストローブ信号のタイミングを再度調整させるリキャリブレーション制御部とをさらに備える請求項1に記載の試験装置。

#### 【請求項7】

前記被試験メモリに対するデータの書き込み又は読み出しを連続して行った場合に、前記論理比較器が経過時間毎に出力した前記比較結果に基づいて、前記被試験メモリの複数の端子のそれぞれについて、前記ストローブ信号のタイミングを再調整すべき時間間隔を測定するリキャリブレーション間隔制御部をさらに備える請求項1に記載の試験装置。30

#### 【請求項8】

被試験メモリの試験実行前に、前記被試験メモリを実装した状態で、前記被試験メモリの複数の端子のそれぞれについて、前記被試験メモリから出力された、予め書き込まれた試験パターンに対応した出力信号とストローブ信号とのタイミングを調整する位相調整方法であって、

前記被試験メモリから出力された前記出力信号の出力値を、前記ストローブ信号のタイミングで取得する出力値取得段階と、40

取得された前記出力値を予め生成された期待値と比較して、比較結果を出力する段階と、

前記比較結果に基づいて、前記被試験メモリの複数の端子のそれぞれについて、前記ストローブ信号のタイミングを調整する段階とを備える位相調整方法。

#### 【請求項9】

前記被試験メモリに試験パターン信号を低速で書き込む低速書込段階と、

前記試験パターン信号に対応した前記出力信号を前記被試験メモリから高速で読み出す第1高速読出段階とをさらに備え、

前記出力値取得段階は、前記第1高速読出段階において読み出された前記出力信号の前50

記出力値を、前記ストローブ信号のタイミングで取得する段階を有する請求項 8 に記載の位相調整方法。

**【請求項 10】**

前記低速書込段階は、前記被試験メモリのスキャン入出力端子から前記試験パターン信号を書き込む段階を有し、

前記第1高速読出段階は、前記被試験メモリのデータ入出力端子から前記試験パターン信号を読み出す段階を有する請求項 9 に記載の位相調整方法。

**【請求項 11】**

セット信号のタイミングで試験パターン信号を立ち上げ、リセット信号のタイミングで前記試験パターン信号を立ち下げて、前記試験パターン信号を前記被試験メモリに高速で書き込む高速書込段階と、

前記試験パターン信号に対応した前記出力信号を前記被試験メモリから高速で読み出す第2高速読出段階と、

前記第2高速読出段階において読み出された前記出力信号の出力値を、前記ストローブ信号のタイミングで取得する段階と、

取得された前記出力値を予め生成された前記期待値と比較して、比較結果を出力する段階と、

前記比較結果に基づいて、前記被試験メモリの複数の端子のそれについて、前記セット信号及び前記リセット信号のタイミングを調整する段階とをさらに備える請求項 8 に記載の位相調整方法。

10

20

**【請求項 12】**

前記高速書込段階は、前記被試験メモリのデータ入出力端子から前記試験パターン信号を書き込む段階を有し、

前記第2高速読出段階は、前記被試験メモリのデータ入出力端子から前記試験パターン信号を読み出す段階を有する請求項 11 に記載の位相調整方法。

**【請求項 13】**

メモリのデータの書き込み及び読み出しを制御するメモリコントローラであって、

前記メモリの使用前に、前記メモリを実装した状態で、前記メモリの複数の端子のそれについて、前記メモリから読み出された、予め書き込まれたデータパターンに対応した出力信号の出力値を、ストローブ信号のタイミングで取得するタイミングコンパレータと、

30

前記タイミングコンパレータが取得した前記出力値を予め生成された期待値と比較して、比較結果を出力する論理比較器と、

前記論理比較器が出力した前記比較結果に基づいて、前記ストローブ信号のタイミングを前記メモリの複数の端子に対して調整する位相調整制御回路と、

前記メモリの温度又は前記メモリの周囲の温度の変化を検出する温度検出部と、

前記温度検出部が検出した温度変化が予め定められた温度変化以上である場合に、前記メモリの複数の端子のそれについて、前記ストローブ信号のタイミングを再度調整させるリキャリブレーション制御部とを備えるメモリコントローラ。

**【請求項 14】**

40

メモリのデータの書き込み及び読み出しを制御するメモリコントローラであって、

前記メモリの使用前に、前記メモリを実装した状態で、前記メモリの複数の端子のそれについて、前記メモリから読み出された、予め書き込まれたデータパターンに対応した出力信号の出力値を、ストローブ信号のタイミングで取得するタイミングコンパレータと、

前記タイミングコンパレータが取得した前記出力値を予め生成された期待値と比較して、比較結果を出力する論理比較器と、

前記論理比較器が出力した前記比較結果に基づいて、前記メモリの複数の端子のそれについて、前記ストローブ信号のタイミングを調整する位相調整制御回路と、

前記メモリに対するデータの書き込み又は読み出しを連続して行った場合に、前記論理

50

比較器が経過時間毎に出力した前記比較結果に基づいて、前記メモリの複数の端子のそれぞれについて、前記ストローブ信号のタイミングを再調整すべき時間間隔を測定するリキヤリブレーキション間隔制御部とを備えるメモリコントローラ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、試験装置、位相調整方法、及びメモリコントローラに関する。特に本発明は、被試験メモリを試験する試験装置、被試験メモリから出力された出力信号とストローブ信号とのタイミングを調整する位相調整方法、及びメモリのデータの書き込み及び読み出しを制御するメモリコントローラに関する。

10

【背景技術】

【0002】

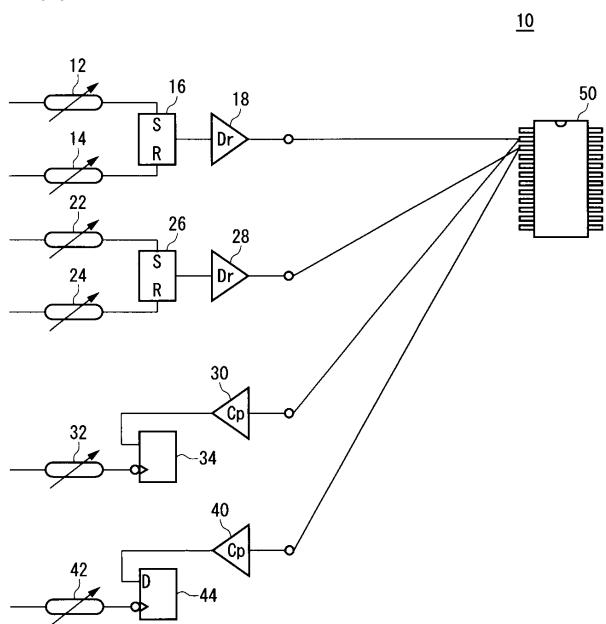

図12は、従来技術に係る試験装置10の構成を示す。試験装置10は、可変遅延回路12、14、22、24、32、及び42、SRラッチ16及び26、ドライバ18及び28、レベルコンパレータ30及び40、並びにタイミングコンパレータ34及び44を備える。

【0003】

SRラッチ16は、可変遅延回路12によって遅延されたセット信号及び可変遅延回路14によって遅延されたリセット信号に基づいて試験パターン信号を発生出力し、ドライバ18を介して被試験メモリ50に供給する。SRラッチ26は、可変遅延回路22によって遅延されたセット信号及び可変遅延回路24によって遅延されたリセット信号に基づいて試験パターン信号を発生出力し、ドライバ28を介して被試験メモリ50に供給する。また、タイミングコンパレータ34は、レベルコンパレータ30を介して被試験メモリ50から出力された出力信号を受け取り、可変遅延回路32により遅延されたストローブ信号に基づいて出力値をサンプリングする。タイミングコンパレータ44は、レベルコンパレータ40を介して被試験メモリ50から出力された出力信号を受け取り、可変遅延回路42により遅延されたストローブ信号に基づいて出力値をサンプリングする。

20

【0004】

そして、タイミングコンパレータ34又は44によってサンプリングされた出力値は、論理比較器によって、予め生成された期待値と比較される。そして、試験装置10は、論理比較器による比較結果に基づいて、被試験メモリ50の良否を判定する。

30

【0005】

試験装置10では、被試験メモリ50の試験を実行する前に次のような位相調整を行う。まず、ドライバ18及び28から出力される試験パターン信号の位相が、被試験メモリ50の端子において同位相になるように、可変遅延回路12及び14の遅延量を設定する。また、被試験メモリ50から同位相で出力される出力信号が、タイミングコンパレータ34及び44において正確にサンプリングされるように、可変遅延回路32及び42の遅延量を設定する。

【0006】

本出願に対応する外国の特許出願においては下記の文献が発見または提出されている。

40

【特許文献1】特開2002-181899号公報

【特許文献2】特開2001-222897号公報

【特許文献3】特開2001-4712号公報

【特許文献4】特開2003-98235号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

従来の試験装置10における位相調整では、ドライバ18及び28から出力された試験パターン信号の位相が、被試験メモリ50の端子において同位相になるように可変遅延回路12及び14の遅延量を設定する。そのため、非常に高い周波数で動作する被試験メモリ

50

リ 5 0 を試験する場合においては、被試験メモリ 5 0 の出力信号の出力タイミングのばらつき、タイミングコンパレータ 3 4 及び 4 4 によるストローブ信号の受け取りタイミングのばらつきにより、被試験メモリ 5 0 から出力された出力信号を正しくサンプリングすることが困難である。また、タイミングコンパレータ 3 4 及び 4 4 によるストローブ信号の受け取りタイミングのばらつきを抑えるため、被試験メモリ 5 0 を実装するたびにストローブ信号の位相調整を行うと、膨大な時間がかかり試験のスループットを低下させてしまう。

#### 【 0 0 0 8 】

そこで本発明は、上記の課題を解決することができる試験装置、位相調整方法、及びメモリコントローラを提供することを目的とする。この目的は特許請求の範囲における独立項に記載の特徴の組み合わせにより達成される。また從属項は本発明の更なる有利な具体例を規定する。10

#### 【課題を解決するための手段】

#### 【 0 0 0 9 】

本発明の第 1 の形態によると、被試験メモリを試験する試験装置であって、被試験メモリから出力された出力信号の出力値を、ストローブ信号のタイミングで取得するタイミングコンパレータと、タイミングコンパレータが取得した出力値を予め生成された期待値と比較して、比較結果を出力する論理比較器と、論理比較器が出力した比較結果に基づいて、ストローブ信号のタイミングを調整する位相調整制御回路とを備える。

#### 【 0 0 1 0 】

ストローブ信号を遅延させてタイミングコンパレータに供給する第 1 可変遅延回路をさらに備え、位相調整制御回路は、論理比較器が出力した比較結果に基づいて、第 1 可変遅延回路による遅延量を設定してもよい。20

#### 【 0 0 1 1 】

論理比較器が比較結果として出力した、出力値と期待値とが一致しないことを示すフェイルデータの数を計数するフェイルカウンタと、フェイルカウンタが計数したフェイルデータの数を、予め定められた判定値と比較して、判定結果を出力する判定回路とをさらに備え、位相調整制御回路は、判定回路が出力した判定結果に基づいて、第 1 可変遅延回路による遅延量を設定してもよい。

#### 【 0 0 1 2 】

位相調整制御回路は、2進数データで示される第 1 可変遅延回路による遅延量を、判定回路が出力した判定結果に基づいてバイナリサーチにより上位ビットから順に決定していくてもよい。30

#### 【 0 0 1 3 】

セット信号のタイミングで試験パターン信号を立ち上げ、リセット信号のタイミングで試験パターン信号を立ち下げて、試験パターン信号を被試験メモリに供給する S R ラッチと、セット信号を遅延させて S R ラッチに供給する第 2 可変遅延回路と、リセット信号を遅延させて S R ラッチに供給する第 3 可変遅延回路とをさらに備え、タイミングコンパレータは、試験パターン信号に対応して被試験メモリから出力された出力信号の出力値を、被試験メモリの内部クロックと同期したストローブ信号のタイミングで取得し、論理比較器は、タイミングコンパレータが取得した出力値を期待値と比較して、比較結果を出力し、位相調整制御回路は、論理比較器が出力した比較結果に基づいて、第 2 可変遅延回路及び第 3 可変遅延回路による遅延量を設定してもよい。40

#### 【 0 0 1 4 】

被試験メモリの温度又は被試験メモリの周囲の温度の変化を検出する温度検出部と、温度検出部が検出した温度変化が予め定められた温度変化以上である場合に、ストローブ信号のタイミングを再度調整させるリキャリブレーション制御部とをさらに備えてもよい。

#### 【 0 0 1 5 】

被試験メモリに対するデータの書き込み又は読み出しを連続して行った場合に、論理比較器が経過時間毎に出力した比較結果に基づいて、ストローブ信号のタイミングを再調整50

すべき時間間隔を測定するリキャリプレーション間隔制御部をさらに備えてよい。

【0016】

本発明の第2の形態によると、被試験メモリから出力された出力信号とストローブ信号とのタイミングを調整する位相調整方法であって、被試験メモリから出力された出力信号の出力値を、ストローブ信号のタイミングで取得する出力値取得段階と、取得された出力値を予め生成された期待値と比較して、比較結果を出力する段階と、比較結果に基づいて、ストローブ信号のタイミングを調整する段階とを備える。

【0017】

被試験メモリに試験パターン信号を低速で書き込む低速書込段階と、試験パターン信号に対応した出力信号を被試験メモリから高速で読み出す第1高速読出段階とをさらに備え、出力値取得段階は、第1高速読出段階において読み出された出力信号の出力値を、ストローブ信号のタイミングで取得する段階を有してもよい。10

【0018】

低速書込段階は、被試験メモリのスキャン入出力端子から試験パターン信号を書き込む段階を有し、第1高速読出段階は、被試験メモリのデータ入出力端子から試験パターン信号を読み出す段階を有してもよい。

【0019】

セット信号のタイミングで試験パターン信号を立ち上げ、リセット信号のタイミングで試験パターン信号を立ち下げて、試験パターン信号を被試験メモリに高速で書き込む高速書込段階と、試験パターン信号に対応した出力信号を被試験メモリから高速で読み出す第2高速読出段階と、第2高速読出段階において読み出された出力信号の出力値を、ストローブ信号のタイミングで取得する段階と、取得された出力値を予め生成された期待値と比較して、比較結果を出力する段階と、比較結果に基づいて、セット信号及びリセット信号のタイミングを調整する段階とをさらに備えてよい。20

【0020】

高速書込段階は、被試験メモリのデータ入出力端子から試験パターン信号を書き込む段階を有し、第2高速読出段階は、被試験メモリのデータ入出力端子から試験パターン信号を読み出す段階を有してもよい。

【0021】

本発明の第3の形態によると、メモリのデータの書き込み及び読み出しを制御するメモリコントローラであって、メモリから読み出された出力信号の出力値を、ストローブ信号のタイミングで取得するタイミングコンパレータと、タイミングコンパレータが取得した出力値を予め生成された期待値と比較して、比較結果を出力する論理比較器と、論理比較器が出力した比較結果に基づいて、ストローブ信号のタイミングを調整する位相調整制御回路と、メモリの温度又はメモリの周囲の温度の変化を検出する温度検出部と、温度検出部が検出した温度変化が予め定められた温度変化以上である場合に、ストローブ信号のタイミングを再度調整させるリキャリプレーション制御部とを備える。30

【0022】

本発明の第4の形態によると、メモリのデータの書き込み及び読み出しを制御するメモリコントローラであって、メモリから読み出された出力信号の出力値を、ストローブ信号のタイミングで取得するタイミングコンパレータと、タイミングコンパレータが取得した出力値を予め生成された期待値と比較して、比較結果を出力する論理比較器と、論理比較器が出力した比較結果に基づいて、ストローブ信号のタイミングを調整する位相調整制御回路と、メモリに対するデータの書き込み又は読み出しを連続して行った場合に、論理比較器が経過時間毎に出力した比較結果に基づいて、ストローブ信号のタイミングを再調整すべき時間間隔を測定するリキャリプレーション間隔制御部とを備える。40

【0023】

なお上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではなく、これらの特徴群のサブコンビネーションもまた発明となりうる。

【発明の効果】

50

## 【0024】

本発明に係る試験装置によれば、高速なデータの送受信を行う被試験メモリを正確に試験することができる。

## 【発明を実施するための最良の形態】

## 【0025】

以下、発明の実施形態を通じて本発明を説明するが、以下の実施形態は特許請求の範囲に係る発明を限定するものではなく、また実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

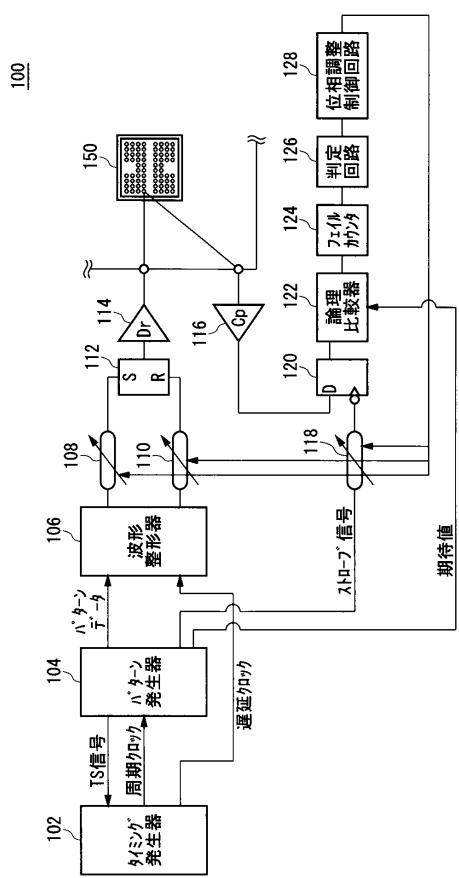

## 【0026】

図1は、本発明の第1実施形態に係る試験装置100の構成の一例を示す。試験装置100は、タイミング発生器102、パターン発生器104、波形整形器106、可変遅延回路108、可変遅延回路110、SRラッチ112、ドライバ114、レベルコンパレータ116、可変遅延回路118、タイミングコンパレータ120、論理比較器122、フェイルカウンタ124、判定回路126、及び位相調整制御回路128を備える。10

## 【0027】

本実施形態に係る試験装置100では、被試験メモリ150に印加する試験データ信号の位相、及び被試験メモリ150から出力される出力信号の出力値を取得するためのストローブ信号の位相を、被試験メモリ150の端子毎に調整することにより、試験装置100と被試験メモリ150との高速なデータの送受信を実現することを目的とする。20

## 【0028】

まず、試験装置100による被試験メモリ150の試験動作について説明する。パターン発生器104は、タイミングセット信号（以下、「TS信号」という。）を出力して、タイミング発生器102に供給する。タイミング発生器102は、TS信号により指定されたタイミングデータに基づいて周期クロック及び遅延クロックを発生して、遅延クロックをパターン発生器104に供給し、遅延クロックを波形整形器106に供給する。そして、パターン発生器104は、タイミング発生器102から供給された周期クロックに基づいて被試験メモリ150に供給すべきパターンデータを発生して、波形整形器106に供給する。

## 【0029】

波形整形器106は、タイミング発生器102から供給された遅延クロックに基づいて、パターン発生器104が発生したパターンデータが示す試験パターン信号を必要なタイミングの波形にすべく、セット信号及びリセット信号を出力する。可変遅延回路108は、位相調整制御回路128により予め設定された遅延量により、波形整形器106が出力したセット信号を遅延させてSRラッチ112に供給する。また、可変遅延回路110は、位相調整制御回路128により予め設定された遅延量により、波形整形器106が出力したリセット信号を遅延させてSRラッチ112に供給する。そして、SRラッチ112は、可変遅延回路108から供給されたセット信号のタイミングで試験パターン信号を立ち上げ、可変遅延回路110から供給されたリセット信号のタイミングで試験パターン信号を立ち下げ、ドライバ114を介して被試験メモリ150に供給する。30

## 【0030】

また、パターン発生器104は、被試験メモリ150から出力された出力信号をタイミングコンパレータ120がサンプリングするタイミングを指定するストローブ信号を発生する。可変遅延回路118は、位相調整制御回路128により予め設定された遅延量により、パターン発生器104が発生したストローブ信号を遅延させてタイミングコンパレータ120に供給する。タイミングコンパレータ120は、被試験メモリ150から出力されレベルコンパレータ116によって2値データに変換された被試験メモリ150の出力信号の出力値を、可変遅延回路118から供給されたストローブ信号のタイミングで取得する。40

## 【0031】

また、パターン発生器104は、被試験メモリ150が試験パターン信号に対応して出50

力すべき出力信号の出力値である期待値を生成して、論理比較器 122 に供給する。そして、論理比較器 122 は、タイミングコンパレータ 120 が取得した出力値を、パターン発生器 104 によって予め生成された期待値と比較して、比較結果を出力する。そして、論理比較器 122 が出力する比較結果に基づいて、被試験メモリ 150 の良否判定を行う。

#### 【0032】

次に、試験装置 100 による試験データ信号及びストローブ信号の位相調整動作について説明する。上述の試験動作と同様に、タイミングコンパレータ 120 は、被試験メモリ 150 から出力された出力信号の出力値を、可変遅延回路 118 から供給されたストローブ信号のタイミングで取得する。そして、論理比較器 122 は、タイミングコンパレータ 120 が取得した出力値を期待値と比較して、比較結果を出力する。具体的には、論理比較器 122 は、出力値と期待値とは一致する場合にフェイルデータを出力し、フェイルカウンタ 124 に供給する。そして、フェイルカウンタ 124 は、論理比較器 122 が比較結果として出力した、出力値と期待値とが一致しないことを示すフェイルデータの数を計数する。そして、判定回路 126 は、フェイルカウンタ 124 が計数したフェイルデータの数を、予め定められた判定値と比較して、判定結果を出力する。位相調整制御回路 128 は、判定回路 126 が output した判定結果に基づいて、可変遅延回路 118 による遅延量を設定する。即ち、位相調整制御回路 128 は、論理比較器 122 が出力した比較結果に基づいて、可変遅延回路 118 による遅延量を設定することにより、タイミングコンパレータ 120 に供給されるストローブ信号のタイミングを調整する。具体的には、位相調整制御回路 128 は、可変遅延回路 118 の位相調整レジスタの設定値を設定する。10

#### 【0033】

また、タイミングコンパレータ 120 は、試験パターン信号に対応して被試験メモリ 150 から出力された出力信号の出力値を、被試験メモリ 150 の内部クロックと同期したストローブ信号のタイミングで取得する。そして、論理比較器 122 は、タイミングコンパレータ 120 が取得した出力値を期待値と比較して、比較結果を出力する。具体的には、論理比較器 122 は、出力値と期待値とは一致する場合にフェイルデータを出力し、フェイルカウンタ 124 に供給する。そして、フェイルカウンタ 124 は、論理比較器 122 が比較結果として出力した、出力値と期待値とが一致しないことを示すフェイルデータの数を計数する。そして、判定回路 126 は、フェイルカウンタ 124 が計数したフェイルデータの数を、予め定められた判定値と比較して、判定結果を出力する。位相調整制御回路 128 は、判定回路 126 が output した判定結果に基づいて、可変遅延回路 108 及び可変遅延回路 110 による遅延量を設定する。即ち、位相調整制御回路 128 は、論理比較器 122 が出力した比較結果に基づいて、可変遅延回路 108 及び 110 による遅延量を設定することにより、S R ラッチ 112 に供給されるセット信号及びリセット信号のタイミングを調整する。具体的には、位相調整制御回路 128 は、可変遅延回路 108 の位相調整レジスタの設定値、及び可変遅延回路 110 の位相調整レジスタの設定値を設定する。20

#### 【0034】

以上のように、位相調整段階において、被試験メモリ 150 から実際に出力される出力信号を利用してストローブ信号、並びにセット信号及びリセット信号の位相を調整することで、試験段階において、被試験メモリ 150 から出力される出力信号の出力値を精度よくサンプリングすることができる。したがって、高速なデータの送受信を行う被試験メモリ 150 を正確に試験することができる。40

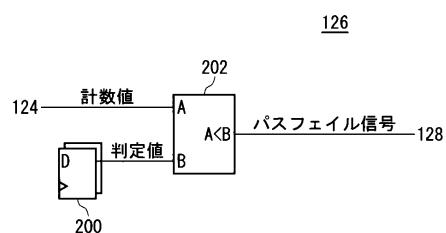

#### 【0035】

図 2 は、第 1 実施形態に係る判定回路 126 の構成の一例を示す。判定回路 126 は、判定値レジスタ 200 及び計数値比較器 202 を有する。判定値レジスタ 200 は、予め定められた判定値を格納し、計数値比較器 202 に供給する。例えば、判定値は、位相調整段階において論理比較器 122 により行われる比較回数の半値である。計数値比較器 202 は、フェイルカウンタ 124 が計数したフェイルデータの数である計数値をフェイル50

カウンタ124から取得し、判定値レジスタ200から供給された判定値と大小比較する。そして、計数値比較器202は、判定結果としてバスフェイル信号を出力し、位相調整制御回路128に供給する。例えば、計数値比較器202は、計数値が判定値より小さい場合にバスデータとして”1”を出力し、計数値が判定値以上の場合にフェイルデータとして”0”を出力する。なお、計数値比較器202は、計数値が判定値より小さい場合にフェイルデータとして”0”を出力し、計数値が判定値以上の場合にバスデータとして”1”を出力してもよい。

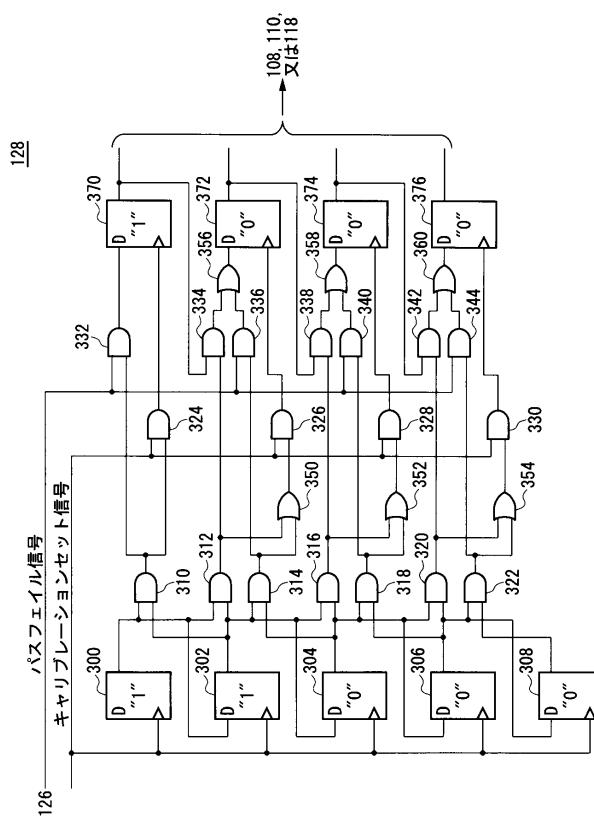

#### 【0036】

図3は、第1実施形態に係る位相調整制御回路128の構成の一例を示す。なお、図3では、可変遅延回路108、110、118の位相調整レジスタが4ビットの場合の例を説明する。なお、位相調整制御回路128は、可変遅延回路108、110、及び118のそれぞれに対応して、図3に示す構成要素をそれぞれ有する。また、本例においては、位相調整制御回路128をハードウェハ回路により実現する例を説明するが、ソフトウェアにより同様の機能を実現してもよい。

10

#### 【0037】

位相調整制御回路128は、ビット選択レジスタ300、302、304、306、及び308、論理積回路310、312、314、316、318、320、322、324、326、328、330、332、334、336、338、340、342、及び344、論理和回路350、352、354、356、358、及び360、並びに位相調整レジスタ370、372、374、及び376を有する。

20

#### 【0038】

ビット選択レジスタ300、302、304、306、及び308、並びに位相調整レジスタ370、372、374、及び376は、初期設定値を保持する。具体的には、ビット選択レジスタ300及び302は、”1”を保持する。また、ビット選択レジスタ304、306、及び308は、”0”を保持する。また、位相調整レジスタ370は、”1”を保持する。また、位相調整レジスタ372、374、及び306は、”0”を保持する。

#### 【0039】

ビット選択レジスタ300は、キャリブレーションセット信号に基づいて、保持しているビットデータを論理積回路310及び312、並びにビット選択レジスタ302に供給する。ビット選択レジスタ302は、キャリブレーションセット信号に基づいて、保持しているビットデータを論理積回路310、312、314、及び316、並びにビット選択レジスタ304に供給する。ビット選択レジスタ304は、キャリブレーションセット信号に基づいて、保持しているビットデータを論理積回路314、316、318、及び320、並びにビット選択レジスタ306に供給する。ビット選択レジスタ306は、キャリブレーションセット信号に基づいて、保持しているビットデータを論理積回路318、320、及び322、並びにビット選択レジスタ308に供給する。ビット選択レジスタ308は、キャリブレーションセット信号に基づいて、保持しているビットデータを論理積回路322、並びにビット選択レジスタ308に供給する。

30

#### 【0040】

ビット選択レジスタ300、302、304、306、及び308は、キャリブレーションセット信号が供給される毎に、保持しているビットデータを順にシフトさせて保持する。即ち、ビット選択レジスタ300、302、304、306、及び308は、初期設定において”1”、“1”、“0”、“0”、及び”0”をそれぞれ保持し、キャリブレーションセット信号が供給されると”0”、“1”、“1”、“0”、及び”0”をそれぞれ保持し、さらにキャリブレーションセット信号が供給されると”0”、“0”、“1”、“1”、及び”0”をそれぞれ保持し、さらにキャリブレーションセット信号が供給されると”0”、“0”、“0”、“1”、及び”1”をそれぞれ保持する。ビット選択レジスタ300、302、304、306、及び308が保持するビットデータをシフトさせることによって、位相調整レジスタ370、372、374、及び376を順に選択

40

50

して設定値を決定する。

**【0041】**

論理積回路310は、ビット選択レジスタ300から供給されたビットデータと、ビット選択レジスタ302から出力されたビットデータとの論理積演算を行い、演算結果を論理積回路332及び論理積回路324に出力する。論理積回路312は、ビット選択レジスタ300から供給されたビットデータと、ビット選択レジスタ302から出力されたビットデータとの論理積演算を行い、演算結果を論理積回路334及び論理和回路350に出力する。論理積回路314は、ビット選択レジスタ302から供給されたビットデータと、ビット選択レジスタ304から出力されたビットデータとの論理積演算を行い、演算結果を論理積回路336及び論理和回路350に出力する。論理積回路316は、ビット選択レジスタ302から供給されたビットデータと、ビット選択レジスタ304から出力されたビットデータとの論理積演算を行い、演算結果を論理積回路338及び論理和回路352に出力する。10

**【0042】**

論理積回路318は、ビット選択レジスタ304から供給されたビットデータと、ビット選択レジスタ306から出力されたビットデータとの論理積演算を行い、演算結果を論理積回路340及び論理和回路352に出力する。論理積回路320は、ビット選択レジスタ304から供給されたビットデータと、ビット選択レジスタ306から出力されたビットデータとの論理積演算を行い、演算結果を論理積回路342及び論理和回路354に出力する。論理積回路322は、ビット選択レジスタ306から供給されたビットデータと、ビット選択レジスタ308から出力されたビットデータとの論理積演算を行い、演算結果を論理積回路344及び論理和回路354に出力する。20

**【0043】**

論理和回路350は、論理積回路312の出力と論理積回路314の出力との論理和演算を行い、演算結果を論理積回路326に出力する。論理和回路352は、論理積回路316の出力と論理積回路318の出力との論理和演算を行い、演算結果を論理積回路328に出力する。論理和回路354は、論理積回路320の出力と論理積回路322の出力との論理和演算を行い、演算結果を論理積回路330に出力する。

**【0044】**

論理積回路324は、論理積回路310の出力とキャリブレーションセット信号との論理積演算を行い、演算結果を位相調整レジスタ370に出力する。論理積回路326は、論理和回路350の出力とキャリブレーションセット信号との論理積演算を行い、演算結果を位相調整レジスタ372に出力する。論理積回路328は、論理和回路352の出力とキャリブレーションセット信号との論理積演算を行い、演算結果を位相調整レジスタ374に出力する。論理積回路330は、論理和回路354の出力とキャリブレーションセット信号との論理積演算を行い、演算結果を位相調整レジスタ376に出力する。即ち、論理積回路324、326、328、及び330は、キャリブレーションセット信号が”1”にセットされている場合に、ビット選択レジスタ300、302、304、306、及び308によって選択されている位相調整レジスタ370、372、374、又は376にクロック信号を供給する。30

**【0045】**

論理積回路332は、判定回路126から供給されたパスフェイル信号と論理積回路310の出力との論理積演算を行い、演算結果を位相調整レジスタ370に出力する。そして、位相調整レジスタ370は、論理積回路324の出力に基づいて、保持しているビットデータを出力し、また論理積回路332の出力を保持する。

**【0046】**

論理積回路334は、判定回路126から供給されたパスフェイル信号と位相調整レジスタ370が保持していたビットデータとの論理積演算を行い、演算結果を論理和回路356に出力する。論理積回路336は、判定回路126から供給されたパスフェイル信号と論理積回路314の出力との論理積演算を行い、演算結果を論理和回路356に出力す4050

る。論理和回路 356 は、論理積回路 334 の出力と論理積回路 336 の出力との論理和演算を行い、演算結果を位相調整レジスタ 372 に出力する。そして、位相調整レジスタ 372 は、論理積回路 326 の出力に基づいて、保持しているビットデータを出力し、また論理和回路 356 の出力を保持する。

#### 【0047】

論理積回路 338 は、判定回路 126 から供給されたパスフェイル信号と位相調整レジスタ 372 が保持していたビットデータとの論理積演算を行い、演算結果を論理和回路 358 に出力する。論理積回路 340 は、判定回路 126 から供給されたパスフェイル信号と論理積回路 318 の出力との論理積演算を行い、演算結果を論理和回路 358 に出力する。論理和回路 358 は、論理積回路 338 の出力と論理積回路 340 の出力との論理和演算を行い、演算結果を位相調整レジスタ 374 に出力する。そして、位相調整レジスタ 374 は、論理積回路 328 の出力に基づいて、保持しているビットデータを出力し、また論理和回路 358 の出力を保持する。10

#### 【0048】

論理積回路 342 は、判定回路 126 から供給されたパスフェイル信号と位相調整レジスタ 374 が保持していたビットデータとの論理積演算を行い、演算結果を論理和回路 360 に出力する。論理積回路 344 は、判定回路 126 から供給されたパスフェイル信号と論理積回路 322 の出力との論理積演算を行い、演算結果を論理和回路 360 に出力する。論理和回路 360 は、論理積回路 342 の出力と論理積回路 344 の出力との論理和演算を行い、演算結果を位相調整レジスタ 376 に出力する。そして、位相調整レジスタ 376 は、論理積回路 330 の出力に基づいて、保持しているビットデータを出力し、また論理和回路 358 の出力を保持する。20

#### 【0049】

以上のように位相調整段階において、位相調整レジスタ 370、372、374、及び 376 は、判定回路 126 から供給されたパスフェイル信号及びキャリブレーションセット信号に基づいて、それぞれ 1 ビットの設定値を保持する。そして、被試験メモリ 150 の試験段階において、可変遅延回路 108、110、又は 118 に設定値を供給することにより、可変遅延回路 108、110、又は 118 によるストローブ信号の遅延量を調整する。

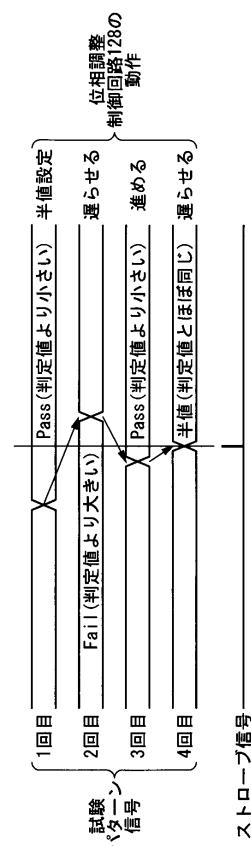

#### 【0050】

図 4 は、第 1 実施形態に係る位相調整制御回路 128 の動作の一例を示す。図 4 では、図 2 に示した判定回路 126、及び図 3 に示した位相調整制御回路 128 により可変遅延回路 108 及び 110 の遅延量を設定して、試験パターン信号の位相を調整する方法の一例を説明する。30

#### 【0051】

まず、1 回目の試験パターン信号を被試験メモリ 150 に印加しながら、論理比較器 122 が複数回に渡って出力値と期待値との比較を行い、フェイルカウンタ 124 がフェイルデータの数を計数する。そして、フェイルカウンタ 124 による計数値が判定値より小さい場合、即ちパスフェイル信号がパスデータとして "1" を出力する場合、位相調整制御回路 128 は、可変遅延回路 108 及び 110 の遅延量を増加させることにより試験パターン信号の位相を遅らせる。40

#### 【0052】

次に、2 回目の試験パターン信号を被試験メモリ 150 に印加しながら、論理比較器 122 が複数回に渡って出力値と期待値との比較を行い、フェイルカウンタ 124 がフェイルデータの数を計数する。そして、フェイルカウンタ 124 による計数値が判定値より大きい場合、即ちパスフェイル信号がフェイルデータとして "0" を出力する場合、位相調整制御回路 128 は、可変遅延回路 108 及び 110 の遅延量を減少させることにより試験パターン信号の位相を進める。

#### 【0053】

次に、3 回目の試験パターン信号を被試験メモリ 150 に印加しながら、論理比較器 1

50

22が複数回に渡って出力値と期待値との比較を行い、フェイルカウンタ124がフェイルデータの数を計数する。そして、フェイルカウンタ124による計数値が判定値より小さい場合、即ちパスフェイル信号がバスデータとして”1”を出力する場合、位相調整制御回路128は、可変遅延回路108及び110の遅延量を増加させることにより試験パターン信号の位相を遅らせる。

#### 【0054】

次に、4回目の試験パターン信号を被試験メモリ150に印加しながら、論理比較器122が複数回に渡って出力値と期待値との比較を行い、フェイルカウンタ124がフェイルデータの数を計数する。そして、フェイルカウンタ124による計数値と、判定値レジスタ200が保持する判定値とがほぼ同じになり、位相調整制御回路128による位相調整が終了する。10

#### 【0055】

即ち、本例においては、位相調整制御回路128は、2進数データで示される可変遅延回路108、110、又は118による遅延量を、判定回路126が出力した判定結果に基づいてバイナリサーチにより上位ビットから順に探索して決定していく。また、他の例においては、位相調整制御回路128は、シーケンシャルサーチによって可変遅延回路108、110、及び118の適切な遅延量を探索してもよいし、バイナリサーチとシーケンシャルサーチとの組み合わせによって可変遅延回路108、110、及び118の適切な遅延量を探索してもよい。20

#### 【0056】

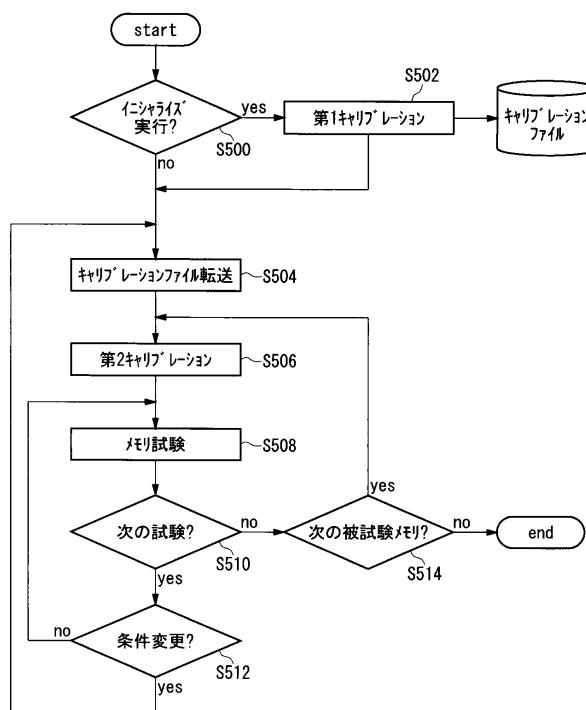

図5は、第1実施形態に係る試験方法のフローの一例を示す。本実施形態に係る位相調整は、被試験メモリ150を試験装置100のソケットに実装した状態で行い、被試験メモリ150のすべての端子について第1キャリブレーション(S502)による位相調整を行い、高速データ通信を行う端子については、第2キャリブレーション(S506)による位相調整を行う。

#### 【0057】

まず、タイミング発生器102、電圧電流発生器、電圧電流測定器等を所定の状態に初期化するイニシャライズが実行されたか否かを判断する(S500)。イニシャライズが実行された場合には(S500-y)、試験条件毎に第1キャリブレーションを行う(S502)。第1キャリブレーション(S502)では、イニシャライズに発生した各端子に対する信号の位相のずれを可変遅延回路108及び110により調整するため、可変遅延回路108及び110の設定値をファイル化してキャリブレーションファイルとして保存する。イニシャライズが実行されなかった場合には(S500-n)、第1キャリブレーションを行わない。30

#### 【0058】

次に、試験条件に対応したキャリブレーションファイルを可変遅延回路108及び110の位相調整レジスタに転送して(S504)、第2キャリブレーションを行う(S506)。第2キャリブレーション(S506)では、被試験メモリ150の端子のうち、高速に動作する端子であるデータ入出力端子等に対してのみ位相調整が行われる。例えば、被試験メモリ150がXDR-DRAMである場合、RQ0-11、CFM/CFMN、RST、CMD、SCK、SDI、SDO等の端子に対しては第1キャリブレーション(S502)のみを行い、DQ/DQN0-15の端子に対して第1キャリブレーション(S502)に加え第2キャリブレーション(S506)を行う。40

#### 【0059】

第2キャリブレーション(S506)が完了すると被試験メモリ150の試験を実行する(S508)。そして、同一の被試験メモリ150に対してさらに他の試験を実行するか否かを判断する(S510)。

#### 【0060】

同一の被試験メモリ150に対してさらに他の試験を実行する場合には(S510-y)、試験条件を変更するか否かを判断する(S512)。試験条件を変更しない場合には50

(S512-n)、続けて被試験メモリ150の試験を実行する(S508)。試験条件を変更する場合には(S512-y)、試験条件に対応したキャリブレーションファイルを可変遅延回路108及び110の位相調整レジスタに転送して(S504)、第2キャリブレーションを行う(S506)。

#### 【0061】

同一の被試験メモリ150に対してさらに他の試験を実行しない場合には(S510-n)、次の被試験メモリ150の試験を実行するか否かを判断する(S514)。次の被試験メモリ150の試験を実行する場合には(S514-y)、第2キャリブレーションを行う(S506)。そして、第2キャリブレーション(S506)が完了すると次の被試験メモリ150の試験を実行する(S508)。次の被試験メモリ150の試験を実行しない場合には(S514-n)、本試験フローを終了する。10

#### 【0062】

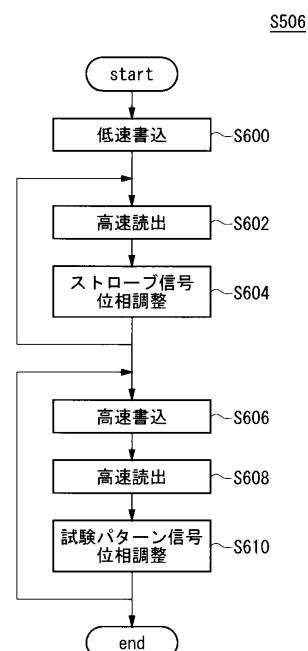

図6は、第1実施形態に係る位相調整方法のフローの一例を示す。図6では、第2キャリブレーション(S506)における位相調整方法のフローを説明する。まず、低速書き込段階(S600)において、被試験メモリ150に試験パターン信号を低速で書き込む。低速書き込段階(S600)では、シリアルバスを介して被試験メモリ150のスキャン入出力端子から試験パターン信号を書き込む。

#### 【0063】

次に、高速読出段階(S602)において、試験パターン信号に対応した出力信号を被試験メモリ150から高速で読み出す。高速読出段階(S602)では、被試験メモリ150のデータ入出力端子から試験パターン信号を読み出す。20

#### 【0064】

次に、ストローブ信号位相調整段階(S604)において、タイミングコンパレータ120は、高速読出段階(S602)において被試験メモリ150から読み出された出力信号の出力値を、ストローブ信号のタイミングで取得する。そして、論理比較器122は、出力値を予め生成された期待値と比較して、比較結果を出力する。そして、図1から図4において説明したように、位相調整制御回路128は、論理比較器122の比較結果に基づいて、可変遅延回路118の位相調整用レジスタを設定し、タイミングコンパレータ120に供給されるストローブ信号のタイミングを調整することにより、タイミングコンパレータ120による出力信号のサンプリングのタイミングを調整する。30

#### 【0065】

次に、高速書き込段階(S606)において、SRラッチ112は、可変遅延回路108から供給されるセット信号のタイミングで試験パターン信号を立ち上げ、可変遅延回路110から供給されるリセット信号のタイミングで試験パターン信号を立ち下げて、試験パターン信号を被試験メモリ150に高速で書き込む。高速書き込段階(S606)では、被試験メモリ150のデータ入出力端子から試験パターン信号を書き込む。

#### 【0066】

次に、高速読出段階(S608)において、試験パターン信号に対応した出力信号を被試験メモリ150から高速で読み出す。高速読出段階(S608)では、被試験メモリ150のデータ入出力端子から試験パターン信号を読み出す。40

#### 【0067】

次に、試験パターン信号位相調整段階(S610)において、タイミングコンパレータ120は、高速読出段階(S608)において被試験メモリ150から読み出された出力信号の出力値を、ストローブ信号のタイミングで取得する。そして、論理比較器122は、出力値を予め生成された期待値と比較して、比較結果を出力する。そして、図1から図4において説明したように、位相調整制御回路128は、論理比較器122の比較結果に基づいて、可変遅延回路108及び110の位相調整用レジスタを設定し、SRラッチ112に供給されるセット信号及びリセット信号のタイミングを調整することにより、被試験メモリ150に供給される試験パターン信号のタイミングを調整する。

#### 【0068】

10

20

30

40

50

以上のように、低速書き込み段階（S600）において試験パターン信号を被試験メモリ150に低速で書き込み、試験パターン信号を被試験メモリ150に正確に保持させることによって、ストローブ信号位相調整段階（S604）においてタイミングコンパレータ120に供給されるストローブ信号の遅延量を精度よく設定することができる。また、ストローブ信号位相調整段階（S604）の後に試験パターン信号位相調整段階（S610）を実行することによって、試験パターン信号位相調整段階（S610）においてセット信号及びリセット信号の遅延量を精度よく設定することができる。

#### 【0069】

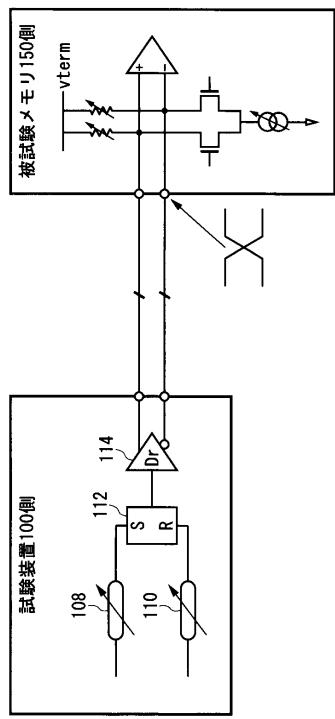

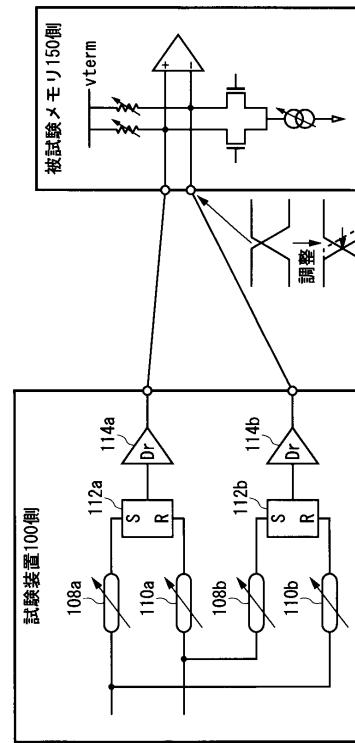

図7及び図8は、第1実施形態に係るドライバ114の一例を示す。また、図9は、第1実施形態に位相調整レジスタの構成の変形例を示す。ドライバ114は、差動ドライバであり、図7に示すように、被試験メモリ150の差動端子において差動信号が正しくクロスすること、また、差動信号の線路が等長であることが前提とされている。しかしながら、実際にはこのような前提に基づいて構成されることはなく、図8に示すように、シングルドライバ114a及び114bを用いて差動信号の位相を調整している。

#### 【0070】

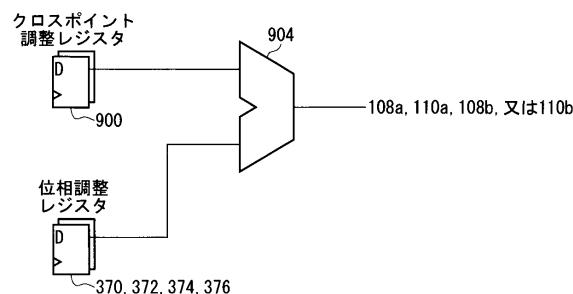

即ち、試験装置100は、図8に示すように、可変遅延回路108及び110に換えて可変遅延回路108a、108b、110a、及び110bを備え、SRラッチ112に換えてSRラッチ112a及び112bを備え、ドライバ114に換えてドライバ114a及び114bを備える。また、試験装置100は、図9に示すように、位相調整レジスタ370、372、374、及び376に加え、クロスポイント調整レジスタ900、及び加算器904をさらに備える。

#### 【0071】

SRラッチ112aは、可変遅延回路108aによって遅延されたセット信号により試験パターン信号を立ち上げ、可変遅延回路110aによって遅延されたリセット信号により試験パターン信号を立ち下げ、ドライバ114aを介して被試験メモリ150に供給する。また、SRラッチ112bは、可変遲延回路108bによって遅延されたセット信号により試験パターン信号を立ち上げ、可変遲延回路110bによって遲延されたリセット信号により試験パターン信号を立ち下げ、ドライバ114bを介して被試験メモリ150に供給する。

#### 【0072】

第1キャリブレーション（S502）において、被試験メモリ150の差動端子において差動信号のクロスポイントがハイレベルとロウレベルとの中心になるように調整する。そして、クロスポイント調整レジスタ900に調整した設定値を保持する。次に、第2キャリブレーション（S506）において、クロスポイントが中心からずれないように、可変遲延回路108a及び110bの位相を同時に調整し、また可変遲延回路108b及び110aの位相を同時に調整する。そして、位相調整レジスタ370、372、374、及び376に調整した設定値を保持する。次に、加算器904は、クロスポイント調整用レジスタ900に設定された設定値と、位相調整レジスタ370、372、374、及び376に設定された設定値とを加算して、可変遲延回路108a、110a、108b、又は110bに供給する。これにより、差動信号のクロスポイント調整と、試験パターン信号の位相調整とを同時に行うことができる。

#### 【0073】

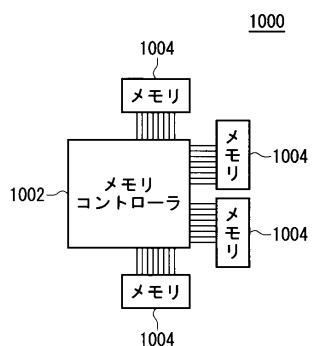

図10は、本発明の第2実施形態に係るメモリ制御システム1000の構成の一例を示す。メモリ制御システム1000は、メモリコントローラ1002、及び複数のメモリ1004を備える。メモリ制御システム1000は、データ転送を行う信号ラインに小振幅信号（200mV振幅）及び双方向差動インターフェースを最小し、複数のメモリ1004とメモリコントローラ1002との間を一対一接続する。また、メモリコントローラ1002のデータ入出力端子毎に、入力信号及び出力信号の位相調整機能が組み込まれている。

#### 【0074】

10

20

30

40

50

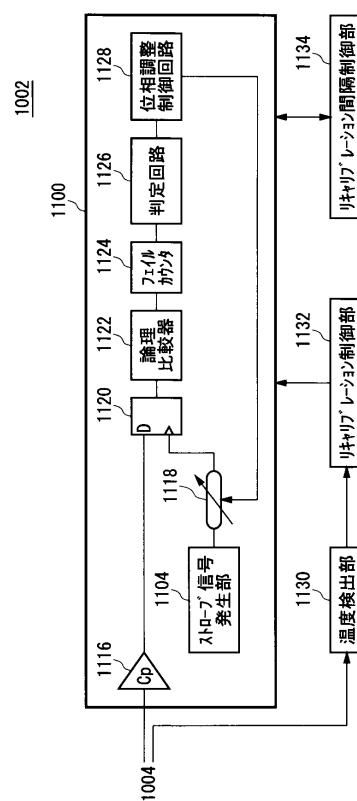

図11は、第2実施形態に係るメモリコントローラ1002の構成の一例を示す。メモリコントローラ1002は、送受信制御部1100、温度検出部1130、リキャリブレーション制御部1132、及びリキャリブレーション間隔制御部1134を備える。送受信制御部1100は、ストローブ信号発生器1104、レベルコンパレータ1116、可変遅延回路1118、タイミングコンパレータ1120、論理比較器1122、フェイルカウンタ1124、判定回路1126、及び位相調整制御回路1128を有する。

#### 【0075】

ストローブ信号発生器1104は、被試験メモリ150から出力された出力信号をタイミングコンパレータ1120がサンプリングするタイミングを指定するストローブ信号を発生する。可変遅延回路1118は、位相調整制御回路1128により予め設定された遅延量により、ストローブ信号発生器1104が発生したストローブ信号を遅延させてタイミングコンパレータ1120に供給する。また、レベルコンパレータ1116、可変遅延回路1118、タイミングコンパレータ1120、論理比較器1122、フェイルカウンタ1124、判定回路1126、及び位相調整制御回路1128のそれぞれは、図1に示した試験装置100が備えるレベルコンパレータ1116、可変遅延回路1118、タイミングコンパレータ1120、論理比較器1122、フェイルカウンタ1124、判定回路1126、及び位相調整制御回路1128のそれと同一の機能を有するので説明を省略する。また、メモリコントローラ1002は、図1に示した試験装置100が備えるその他の構成部材を備えてもよい。

#### 【0076】

温度検出部1130は、メモリ1004の温度又はメモリ1004の周囲の温度の変化を検出する。そして、リキャリブレーション制御部1132は、温度検出部1130が検出した温度変化が予め定められた温度変化以上である場合に、送受信制御部1100に対して、可変遅延回路1118による遅延量を再度設定することにより、タイミングコンパレータ1120に供給されるストローブ信号のタイミングを再度調整させる。即ち、メモリ1004の温度変化に起因して生じる出力信号の位相の変化に対して、ストローブ信号の位相を追従させることができる。そのため、メモリ1004が動作することによって温度が上昇する場合であっても、メモリ1004とメモリコントローラ1002との間のデータ通信を正確に行うことができる。

#### 【0077】

また、リキャリブレーション間隔制御部1134は、メモリ1004に対するデータの書き込み又は読み出しを連続して行った場合に、論理比較器1122が経過時間毎に出力した比較結果に基づいて、タイミングコンパレータ1120に供給されるストローブ信号のタイミングを再調整すべき時間間隔を測定する。具体的には、フェイルカウンタ1124は、論理比較器1122が出力したフェイルデータの数を単位時間毎に計数する。そして、判定回路1126は、予め定められた判定値と、フェイルカウンタ1124が計数した計数値とを大小比較する。これにより、リキャリブレーション間隔制御部1134は、計数値が判定値より大きくなる時間を測定する。即ち、メモリ1004に対するデータの書き込み又は読み出しを連続して行うことによって、メモリ1004の温度変化に起因して出力信号の位相の変化により、メモリコントローラ1002とメモリ1004との間のデータ通信が正確に行われなくなる時間を測定する。そして、リキャリブレーション間隔制御部1134は、測定した時間間隔毎に、送受信制御部1100に対して、タイミングコンパレータ1120に供給されるストローブ信号のタイミングを再調整させる。これにより、メモリ1004が動作することによって温度が上昇する場合であっても、常にメモリ1004とメモリコントローラ1002との間のデータ通信を正確に行うことができる。

#### 【0078】

なお、試験装置100は、図11に示したメモリコントローラ1002が備える温度検出部1130、リキャリブレーション制御部1132、及びリキャリブレーション間隔測定部1134をさらに備えてよい。そして、被試験メモリ150の温度上昇に追従させ

10

20

30

40

50

てタイミングコンパレータ 120 に供給するストローブ信号のタイミングを調整してもよい。また、タイミングコンパレータ 120 に供給するストローブ信号のタイミングを再調整すべき時間間隔を測定して、メモリ 1004 に書き込んでもよい。メモリコントローラ 1002 は、試験装置 100 によって書き込まれた時間間隔にしたがってストローブ信号のタイミングを再調整することにより、常にメモリ 1004 とメモリコントローラ 1002 との間のデータ通信を正確に行うことができる。

#### 【0079】

以上、実施形態を用いて本発明を説明したが、本発明の技術的範囲は上記実施形態に記載の範囲には限定されない。上記実施形態に、多様な変更又は改良を加えることができる。そのような変更又は改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。10

#### 【図面の簡単な説明】

#### 【0080】

【図 1】試験装置 100 の構成の一例を示す図である。

【図 2】判定回路 126 の構成の一例を示す図である。

【図 3】位相調整制御回路 128 の構成の一例を示す図である。

【図 4】位相調整制御回路 128 の動作の一例を示す図である。

【図 5】試験方法のフローの一例を示す図である。

【図 6】位相調整方法のフローの一例を示す図である。

【図 7】ドライバ 114 の一例を示す図である。20

【図 8】ドライバ 114 の一例を示す図である。

【図 9】位相調整レジスタの構成の変形例を示す図である。

【図 10】メモリ制御システム 1000 の構成の一例を示す図である。

【図 11】メモリコントローラ 1002 の構成の一例を示す図である。

【図 12】従来技術に係る試験装置 10 の構成を示す図である。

#### 【符号の説明】

#### 【0081】

100 試験装置

102 タイミング発生器

104 パターン発生器

106 波形整形器

108 可変遅延回路

110 可変遅延回路

112 S R ラッチ

114 ドライバ

116 レベルコンパレータ

118 可変遅延回路

120 タイミングコンパレータ

122 論理比較器

124 フェイルカウンタ

126 判定回路

128 位相調整制御回路

200 判定値レジスタ

202 計数値比較器

900 クロスポイント調整レジスタ

904 加算器

1000 メモリ制御システム

1002 メモリコントローラ

1004 メモリ

1100 送受信制御部

20

30

40

50

1 1 0 4 ストローブ信号発生器

1 1 1 6 レベルコンパレータ

1 1 1 8 可変遅延回路

1 1 2 0 タイミングコンパレータ

1 1 2 2 論理比較器

1 1 2 4 フェイルカウンタ

1 1 2 6 判定回路

1 1 2 8 位相調整制御回路

1 1 3 0 溫度検出部

1 1 3 2 リキャリブレーション制御部

1 1 3 4 リキャリブレーション間隔制御部

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図 1 2】

---

フロントページの続き

(56)参考文献 特開2002-181899(JP,A)

特開2001-013217(JP,A)

特開2003-344507(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 29/00 - 29/56

G 01 R 31/28