(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5105160号

(P5105160)

(45) 発行日 平成24年12月19日(2012.12.19)

(24) 登録日 平成24年10月12日(2012.10.12)

(51) Int.Cl.

F 1

H01L 21/338 (2006.01)

H01L 29/778 (2006.01)

H

H01L 29/812 (2006.01)

き回され、それぞれの前記経路は、前記活性領域の外で引き回され、前記フィールドプレートと前記ソース電極とを電気的に接続することを特徴とする請求項1に記載のトランジスタ。

【請求項3】

前記少なくとも1つの導電性経路は、前記フィールドプレートとゲートとの間に引き回され、それぞれの前記経路は、前記活性領域の外で引き回され、前記フィールドプレートと前記ゲートとを電気的に接続することを特徴とする請求項1に記載のトランジスタ。

【請求項4】

前記少なくとも1つの導電性経路は、前記フィールドプレートと前記ゲートとの間に引き回されている導電性ビアを備えることを特徴とする請求項1に記載のトランジスタ。 10

【請求項5】

前記第1のスペーサ層は、誘電体またはいくつかの誘電体層を備えることを特徴とする請求項1に記載のトランジスタ。

【請求項6】

前記ゲートは、前記活性領域内で少なくとも部分的にリセス化されていることを特徴とする請求項1に記載のトランジスタ。

【請求項7】

前記フィールドプレートは、ゲート-ソース間容量およびゲート-ドレイン間容量を低減することを特徴とする請求項1に記載のトランジスタ。

【請求項8】

前記拡大された頂部は、ゲートコンダクタンスを高めることを特徴とする請求項1に記載のトランジスタ。 20

【請求項9】

前記第1のスペーサ上に第2のフィールドプレートをさらに備えることを特徴とする請求項1に記載のトランジスタ。

【請求項10】

前記第2のフィールドプレートは、前記ゲートの前記拡大された頂部の下と接触することを特徴とする請求項9に記載のトランジスタ。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、トランジスタに関し、より詳細には、性能を改善するためにフィールドプレートを使用するトランジスタに関する。

【背景技術】

【0002】

$\text{AlGaN}/\text{GaN}$ 半導体材料の製造における改良により、高周波、高温、および高出力用途の高電子移動度トランジスタ(HEMT)などの $\text{AlGaN}/\text{GaN}$ トランジスタの開発が進展した。 $\text{AlGaN}/\text{GaN}$ は、大きなバンドギャップ、高いピーク電子速度値および高い飽和電子速度値を有する(非特許文献1参照)。 $\text{AlGaN}/\text{GaN}$ HEMTは、さらに、 $10^{13} \text{ cm}^{-2}$ を超える2DEGシート密度および比較的高い電子移動度(最大 $20^{19} \text{ cm}^2/\text{Vs}$ まで)を有することができる(非特許文献2参照)。これらの特性により $\text{AlGaN}/\text{GaN}$ HEMTは、非常に高い電圧を発生し、RF、マイクロ波、およびミリメートル波周波数における高出力動作を行うことができる。 40

【0003】

$\text{AlGaN}/\text{GaN}$ HEMTは、サファイヤ基板上に成長され、電力密度4.6W/mmおよび全出力電力7.6Wを示した(非特許文献3参照)。 $\text{AlGaN}/\text{GaN}$ HEMTは、SiC上に成長され、8GHzで電力密度9.8W/mm(非特許文献4参照)、および9GHzで全出力電力22.9W(非特許文献5参照)を示した。

【0004】

特許文献1には、緩衝層および基板上に成長された $\text{GaN}/\text{AlGaN}$ ベースのHEM 50

Tが開示されている。非特許文献6および7には、他のAlGaN/GaN HEMTおよび電界効果トランジスタ(FET)が説明されている。これらのデバイスのいくつかは、100ギガヘルツと高い利得帯域幅積( $f_T$ ) (非特許文献8参照)、およびX帯域で最大10W/mmと高い電力密度 (非特許文献9参照および非特許文献10参照)を示した。

【0005】

電子トラップおよびその結果であるDC特性とRF特性との差は、これらのデバイスの性能における制限要因となりうる。窒化ケイ素(SiN)パッシベーションを使用してこのトラップ問題を緩和し、その結果として電力密度が10GHzで10W/mmを超える高性能デバイスを実現した。特許文献2では、GaNベースのトランジスタにおけるトラップ効果を低減する方法および構造が開示されている。しかし、これらの構造内には高い電界が存在するため、電荷トラップが依然として問題になりうる。

【0006】

- 【特許文献1】米国特許第5,192,987号明細書

- 【特許文献2】米国特許第6,586,781号明細書

- 【特許文献3】米国特許第Re.34,861号明細書

- 【特許文献4】米国特許第4,946,547号明細書

- 【特許文献5】米国特許第5,200,022号明細書

- 【特許文献6】米国特許第5,290,393号明細書

- 【特許文献7】米国特許第5,686,738号明細書

- 【特許文献8】米国特許第5,393,993号明細書

- 【特許文献9】米国特許第5,523,589号明細書

- 【特許文献10】米国特許第5,739,554号明細書

- 【特許文献11】米国特許第6,316,793号明細書

- 【特許文献12】米国特許第6,548,333号明細書

- 【特許文献13】米国特許出願公開第2002/0167023号明細書

- 【特許文献14】米国特許出願公開第2003/0020092号明細書

- 【特許文献15】米国特許第5,296,395号明細書

- 【特許文献16】米国特許第7,170,111号明細書

- 【非特許文献1】B. Gelmont, K. Kim and M. Shur, "Monte Carlo Simulation of Electron Transport in Gallium Nitride," *J. Appl. Phys.* 74, (1993), pp. 1818-1821

- 【非特許文献2】R. Gaska et al., "Electron Transport in AlGaN-GaN Heterostructures Grown on 6H-SiC Substrates," *Appl. Phys. Lett.* 72, (1998), pp. 707-709

- 【非特許文献3】Y. F. Wu et al., "GaN-Based FETs for Microwave Power Amplification," *IEICE Trans. Electron. E-82-C*, (1999), pp. 1895-1905

- 【非特許文献4】Y. F. Wu et al., "Very-High Power Density AlGaN/GaN HEMTs," *IEEE Trans. Electron. Dev.* 48, (2001), pp. 586-590

- 【非特許文献5】M. Micovic et al., "AlGaN/GaN Heterojunction Field Effect Transistors Grown by Nitrogen Plasma Assisted Molecular Beam Epitaxy," *IEEE Trans. Electron. Dev.* 48, (2001), pp. 591-596

- 【非特許文献6】Gaska et al., "High-Temperature Performance of AlGaN/GaN HFET's on SiC Substrates," *IEEE Electron Device Letters*, 18, (1997), pp. 492-494

- 【非特許文献7】Wu et al., "High Al-content AlGaN/GaN HEMTs With Very High Performance," *IEDM-1999 Digest*, pp. 925-927, Washington DC, Dec. 1999

- 【非特許文献8】Lu et al., "AlGaN/GaN HEMTs on SiC With Over 100 GHz ft and Low Microwave Noise," *IEEE Transactions on Electron Devices*, Vol. 48, No. 3, March 2001, pp. 581-585

- 【非特許文献9】Wu et al., "Bias-dependent Performance of High-Power AlGaN/GaN HEMTs," *IEDM-2001*, Washington DC, Dec. 2-6, 2001

- 【非特許文献10】Wu et al., "High Al-Content AlGaN/GaN MODFETs for Ultrahigh Pe

10

20

30

40

50

rfomance," IEEE Electron Device Letters 19, (1998), pp. 50-53

【非特許文献 11】S Kamalkar and U. K. Mishra, "Very High Voltage AlGaN/GaN High Electron Mobility Transistors Using a Field Plate Deposited on a Stepped Insulator," Solid State Electronics 45, (2001), pp. 1645-1662

【発明の開示】

【発明が解決しようとする課題】

【0007】

これまで、マイクロ波周波数域におけるGaNベースのHEMTの性能を高めるためにフィールドプレートが使用されており、フィールドプレートのないデバイスに対する性能の改善が示された（非特許文献 11 参照）。多くのフィールドプレートアプローチでは、トランジスタのゲートに接続されたフィールドプレートを必要とし、フィールドプレートはチャネルのドレイン側の上にあった。この結果、トランジスタのゲート - ドレイン側の電界が減少し、これにより絶縁破壊電圧を高め、高電界トラップ効果を低減させることができる。しかし、ゲート - ドレインフィールドプレートを有するトランジスタは、特にゲートのソース側の電界が顕著になるC級（またそれ以上の級の）動作においては比較的低い信頼性性能を示す可能性がある。

【0008】

さらに他のフィールドプレートアプローチでは、フィールドプレートをソースに接続する必要があった。ソース接続フィールドプレートでは、ゲート - ドレイン間容量が低くなり、その結果、利得が増大する。しかしこの配置では、フィールドプレートがソースに接続されているため、ゲート - フィールドプレート間容量、またはゲート - ソース間容量が増大する。フィールドプレートがゲートの上にある状態では、ゲートの断面積を増やすことが困難であり、したがってゲートコンダクタンスが制限される。ゲート - ソース間容量を加えることで、デバイス帯域幅を低減することができるが、制限されたゲートコンダクタンスにより、電力利得遮断周波数が制限される。

【課題を解決するための手段】

【0009】

本発明は、低いゲート - ソース間容量およびゲート - ドレイン間容量ならびに高いゲートコンダクタンスで動作し、それによりデバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。本発明によるトランジスタの一実施形態は、トランジスタであって、活性領域と、活性領域と接触しているソースおよびドレイン電極と、ソース電極とドレイン電極との間にあり、活性領域と接触しているゲートであって、拡大された頂部を有するゲートと、ゲートの拡大された頂部の少なくとも一部の下にある少なくとも1つのフィールドプレートと、少なくとも1つのフィールドプレートをソース電極またはゲートに電気的に接続する少なくとも1つの導電性経路と、ゲートとドレイン電極との間、およびゲートとソース電極との間の、活性領域の表面の少なくとも一部の上の第1のスペーサ層であって、少なくとも1つのフィールドプレートは、第1のスペーサ層の上ある第1のスペーサ層と、第1のスペーサ層の表面の少なくとも一部の上にあり、フィールドプレートの少なくとも一部を覆う第2のスペーサ層と、拡大された部分の底部と拡大された部分の下にある層との間に空隙とを備える。ゲートは、ゲートコンダクタンスを高めるオーバーハングを有する一般的にT字型の頂部（top portion）を備える。ソース接続フィールドプレートが、ゲートのT字型部分の少なくとも一部の下の第1のスペーサ層上にある。

【0010】

本発明による高電子移動度トランジスタ（HEMT）の一実施形態は、基板上に連続的に配置されている緩衝層および障壁層を備え、二次元電子ガス（2DEG）層が前記緩衝層と前記障壁層との間のヘテロ界面に存在する。ソース電極およびドレイン電極が備えられ、共に前記2DEG層と接触し、ゲートが、前記ソース電極と前記ドレイン電極との間の前記障壁層上に備えられる。前記ゲートは、前記ゲートと一体化され、ゲートコンダクタンスを高める一般的にT字型の頂部を備える。第1の誘電体層が、前記ゲート電極と前

10

20

30

40

50

記ドレイン電極との間、および前記ゲート電極と前記ソース電極との間の前記障壁層の表面の少なくとも一部の上にあり、前記ゲートは、前記第1の誘電体層の開口部を通して前記障壁層と接触している。ソース接続フィールドプレートが、前記ゲートの前記T字型部分の少なくとも一部の下の前記第1の誘電体層上にある。第2の誘電体層が、前記第1の誘電体層の上にあり、前記フィールドプレートの少なくとも一部を覆う。

【0011】

本発明による高電子移動度トランジスタ(HEMT)の一実施形態は、基板上に連続的に配置されているGaN層および障壁層を備え、二次元電子ガス(2DEG)層が前記GaN層と前記障壁層との間のヘテロ界面に存在する。ソース電極およびドレイン電極が備えられ、共に前記2DEGと接触し、ゲートが、前記ソース電極と前記ドレイン電極との間の前記障壁層上に備えられる。前記ゲートは、前記ゲートと一体化され、ゲートコンダクタンスを高めるT字型の頂部を備える。第1のスペーサ層が、前記ゲート電極と前記ドレイン電極との間、および前記ゲート電極と前記ソース電極との間の前記障壁層の表面の少なくとも一部の上にあり、ゲート開口部が、前記障壁層内のリセスと接触している。ソース接続フィールドプレートが、前記ゲートの前記T字型部分の少なくとも一部の下の前記第1のスペーサ層上にある。第2のスペーサ層が、前記第1のスペーサ層の上にあり、前記フィールドプレートの少なくとも一部を覆う。

【0012】

本発明による高電子移動度トランジスタ(HEMT)の一実施形態は、基板上の緩衝層と前記緩衝層上の障壁層とを備え、二次元電子ガス(2DEG)層が、前記緩衝層と前記障壁層との間のヘテロ界面に存在する。In<sub>x</sub>Ga<sub>1-x</sub>N層が、前記緩衝層内に挿入される。ソース電極およびドレイン電極が備えられ、共に前記2DEGと接触し、ゲートが、前記ソース電極と前記ドレイン電極との間の前記障壁層上に備えられる。前記ゲートは、前記ゲートと一体化され、ゲートコンダクタンスを高める一般的にT字型の頂部を備える。第1の誘電体層が、前記ゲート電極と前記ドレイン電極との間、および前記ゲート電極と前記ソース電極との間の前記障壁層の表面の少なくとも一部の上にある。ソース接続フィールドプレートが、前記ゲートの前記T字型部分の少なくとも一部の下の前記第1の誘電体層上にある。第2の誘電体層が、前記第1の誘電体層の上にあり、前記フィールドプレートの少なくとも一部を覆う。

【0013】

本発明のこれら及びさらなる特徴および利点は、添付図面と併せて以下の詳細な説明を読むことで当業者に明らかになるであろう。

【発明を実施するための最良の形態】

【0014】

本出願は、2006年11月13日に出願したYifeng Wuの仮特許出願第60/858,851号の利益を主張するものである。

【0015】

本発明は、低いゲート-ソース間およびゲート-ドレイン間容量とともに高いゲートコンダクタンスを与える高電子移動度トランジスタ(HEMT)等のトランジスタのための構造を提供する。この結果、デバイス利得、帯域幅、および動作周波数を高めたデバイスが得られる。本発明は一般的に、「T字型」ゲートを有するトランジスタであって、ゲートのT字型部分のオーバーハングの一方または両方の下にあるか、または下に「埋設」されたフィールドプレートを備えるものを対象とする。

【0016】

この配置は、ワイドバンドギャップ材料で作られたトランジスタ構造等の多くの異なるトランジスタ構造とともに使用することができる。トランジスタは一般的に、複数の半導体層を有する活性領域を備え、複数の半導体層のうちの1つがチャネル層である。チャネル層は、多くの場合、二次元電子ガス(2DEG)により構成される。金属のソース電極およびドレイン電極が、活性領域と接触するように形成され、ゲートが、活性領域内の電界を変調するために、ソース電極とドレイン電極との間の活性領域上に形成される。

10

20

30

40

50

## 【0017】

第1のスペーサ層が、ゲートとドレインとの間の活性領域の表面の少なくとも一部と、ゲートとソースとの間の表面の少なくとも一部とを覆う形で、活性領域の上側に形成される。第2のスペーサ層が、ゲートとドレインとの間の第1のスペーサ層領域の表面の少なくとも一部と、ゲートとソースとの間の表面の少なくとも一部とを覆う形で、第1のスペーサ層の上側に形成される。第1および第2のスペーサ層は、誘電体層またはいくつかの誘電体層の組合せを備えることができ、いくつかの実施形態ではエピタキシャル成長層等の他の材料を備えることができる。

## 【0018】

一実施形態では、第1のスペーサ層は、ゲート電極とドレイン電極との間、およびゲート電極とソース電極との間の活性領域の最上面 (topmost surface) を覆う。後述のように他の実施形態では、スペーサ層は活性領域の表面のより少ない部分を覆うことができる。

10

## 【0019】

導電性の第1のフィールドプレートが第1のスペーサ層上に形成され、第1のスペーサ層は、フィールドプレートと下の活性領域との間の絶縁を行う。第1のフィールドプレートは、ゲートのドレイン側上のT字型部分の下からドレイン電極に向かって、スペーサ層上に距離  $L_{t_d}$  だけ延在している。第1のフィールドプレートは、ソース電極またはゲートのいずれかに電気的に接続することができる。本発明による異なる実施形態では、追加のスペーサ層フィールドおよびフィールドプレートの対も備えることができる。例えば、フィールドプレートは代替的に、ゲートのソース側上のT字型部分の下からソース電極に向かって、スペーサ層上に距離  $L_{t_s}$  だけ延在するようにすることもできる。好ましい実施形態では、ゲートのT字型部分の下面とその下の層との間に、ゲートとソースとの間の容量を最小にするための間隔がある。

20

## 【0020】

一実施形態では、第2のスペーサ層は、フィールドプレート全体をそれが実質的に埋設されるように覆うとともに、ゲート電極とドレイン電極との間、およびゲート電極とソース電極との間の第1のスペーサ層領域の最上面を覆う。後述のように他の実施形態では、第2のスペーサ層は、第1のスペーサ層の表面のより少ない部分を覆うか、あるいはフィールドプレートの一部を覆うことができる。さらに他の実施形態では、第2のスペーサ層は、ゲートとソースおよびドレインとの間の第2のスペーサ層領域の最上面のみを覆い、フィールドプレートを覆わない。

30

## 【0021】

このフィールドプレート配置では、ピーク電界、ゲート-ソース間容量、およびゲート-ドレイン間容量を低減できるが、さらにゲートコンダクタンスを高めることもできる。静電容量を低くし、ゲートコンダクタンスを高くすることで、デバイス利得、帯域幅、および動作周波数が上がるとともに、絶縁破壊電圧が高くなり、トラッピングが低減される。電界を低くすることは、漏れ電流の低減や信頼性の向上等の他の利点もたらす。ソース接続フィールドプレートは、ゲートのソース側の容量が低減されるように配置され、これにより、負バイアスがより大きいゲート条件を必要とする用途に対する性能およびロバスト性が高まる。これは、C級および他の上級（例えば、E、F）の動作を含む。フィールドプレートをソースに接続しておくことで、トランジスタのドレイン側に生じるピーク電界が低減するので、ドレイン側の容量も低減される。

40

## 【0022】

本発明による埋設されたソース接続フィールドプレート配置を利用することができますトランジスタの一種に、緩衝層と緩衝層上の障壁層とを一般的には備える高電子移動度トランジスタ（HEMT）がある。二次元電子ガス（2DEG）チャネル層が、緩衝層と障壁層との間のヘテロ界面に配置されている。ソース電極とドレイン電極との間の障壁層上に、ゲート電極が形成される。HEMTはさらに、上述のいくつかのスペーサ層およびフィールドプレート配置も備える。

50

## 【0023】

本発明によるゲート・ソース間フィールドプレート配置を利用することができるトランジスタの別の種類として、電界効果トランジスタ、および特に、緩衝層と緩衝層上のチャネル層とを一般的には備える金属半導体電界効果トランジスタ(MESFET)がある。ゲートが、ソース電極とドレイン電極との間のチャネル層上に形成され、MESFETはさらに、上述のいくつかのスペーサ層およびフィールドプレート配置を備える。

## 【0024】

要素または層が、別の要素または層の「上にある」、「に接続されている」、「に結合されている」、または「接触している」と言及される場合、その要素または層は、直接に他の要素または層の上にあるか、接続されているか、結合されているか、もしくは接触しているか、または介在する要素または層が存在することができることが理解されるであろう。対照的に、ある要素が、別の要素または層の「上に直接にある」、「に直接に接続されている」、「に直接に結合されている」、または「直接に接触している」と言及される場合、介在する要素または層は存在しない。同様に、第1の要素または層が、第2の要素または層に「電気的に接続している」または「電気的に結合されている」と言及される場合、第1の要素または層と第2の要素または層との間に電流の流れを許す電気的経路があるということである。電気的経路は、コンデンサ、結合インダクタ、および/または導体素子の間に直接の接触がなくても電流の流れを許す他の要素とすることができます。

10

## 【0025】

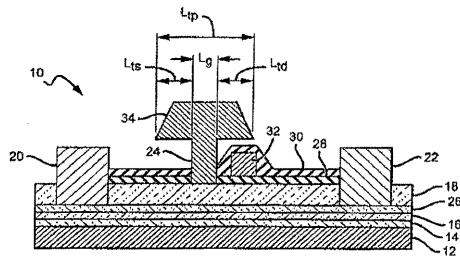

図1および2は、好ましくはIII族窒化物ベースの本発明によるHEMT 10の一実施形態を示しているが、他の材料系を使用することもできる。「III族窒化物」は、窒素と、周期表のIII族に属する元素、通常はアルミニウム(Al)、ガリウム(Ga)、およびインジウム(In)との間に形成される半導体化合物を指す。この用語は、Al<sub>1</sub>GaNおよびAl<sub>1</sub>InGaNなどの三元および四元化合物も指す。

20

## 【0026】

HEMT 10は、炭化ケイ素、サファイヤ、スピネット、ZnO、シリコン、窒化ガリウム、窒化アルミニウム、またはIII族窒化物材料の成長を支えられる材料またはこれらの材料の組合せから形成することができる基板12を備える。核形成層14を基板12上に形成することができ、これにより、基板12とHEMT 10内の次の層との間の格子不整合を低減することができる。核形成層14は、厚さを約1000オングストローム(㎚)とすべきであるが、他の厚さとすることもできる。核形成層14は、多くの異なる材料を含むことができ、好適な材料としてはAl<sub>z</sub>Ga<sub>1-z</sub>N(0<z<1)があり、有機金属化学気相堆積法(MOCVD)、ハイドライド気相エピタキシー法(HVPE)、または分子線エピタキシー法(MBE)等の既知の半導体成長技術を使用して基板12上に形成することができる。

30

## 【0027】

基板12は、多くの異なる材料により構成することができ、好適な基板は炭化ケイ素の4Hポリタイプであるが、3C、6H、および15Rポリタイプを含む他の炭化ケイ素ポリタイプも使用できる。炭化ケイ素は、サファイヤよりもIII族窒化物に大幅に近い結晶格子整合を有し、その結果、品質のより高いIII族窒化物膜が得られる。炭化ケイ素はさらに、非常に高い熱伝導性を有し、炭化ケイ素上のIII族窒化物デバイスの全出力が基板の熱散逸により制限されない(サファイヤ上に形成されたいくつかのデバイスの場合にそうであるように)。また、炭化ケイ素基板が利用できると、商用デバイスを可能にするデバイス絶縁および寄生容量の低減の可能性となる。SiC基板は、ノースカロライナ州ダラムのCree, Inc.から入手可能であり、その生産方法は、科学文献ならびに特許文献3、4および5に説明されている。

40

## 【0028】

核形成層14の形成は、基板12に使用される材料に依存しうる。例えば、様々な基板上に核形成層14を形成する方法は、特許文献6および7で説明されている。これらは共に、本明細書に完全に記載されたかのように参照により組み込む。炭化ケイ素基板上に核

50

形成層を形成する方法は、特許文献8、9および10で説明されている。これらは共に、本明細書に完全に記載されたかのように参照により組み込む。

【0029】

HEMT 10は、核形成層14上に形成された高抵抗緩衝層16をさらに備える。緩衝層16は、III族窒化物材料のドープまたはアンドープ層を備えることができ、好ましい緩衝層16は、 $Al_xGa_yIn_{(1-x-y)}N(0 \leq x \leq 1, 0 \leq y \leq 1, x+y \leq 1)$ などのIII族窒化物材料により構成される。緩衝層16には、その一部がFeでドープされた厚さ約0.5~20μmのGaN等の他の材料も使用することができる。

【0030】

障壁層18が、緩衝層16上に形成され、緩衝層16は障壁層18と核形成層14との間にサンドイッチ状に挟まれる。緩衝層16のように、障壁層18はIII族窒化物材料のドープまたはアンドープ層を備えることができる。障壁層は、 $Al_xGa_{1-x}N$ または $Al_xIn_yGa_{1-x-y}N$ (xは0~1)の1つ又はいくつかの層でにより構成することができ、xは、障壁層18が傾斜層となるように深さの関数とすることができます。2DEGチャネル層26は、緩衝層16と障壁層18との間のヘテロ界面のところに生じ、緩衝層16、2DEGチャネル層26、および障壁層18は一般的にHEMT活性領域を形成する。

【0031】

例示的HEMT構造は、特許文献2および11~14に説明されている。これらの文献は、本明細書に完全に記載されたかのように参照により組み込む。他の窒化物ベースのHEMT構造が特許文献1および15に説明されている。これらの文献は、本明細書に完全に記載されたかのように参照により組み込む。緩衝層16および障壁層18は、核形成層14を成長させるために使用される方法と同じ方法を使用して作製することができる。デバイス間の電気的分離は、活性HEMTの外でメサエッティングまたはイオン注入を行うことにより達成される。

【0032】

金属のソース電極20およびドレイン電極22は、障壁層18と接触するように形成され、ゲート24は、ソース電極20とドレイン電極22との間に、第1の非導電性スペーサ層28内の開口部を通して障壁層18上に形成される。ゲート24が適切なレベルにバイアスされたときに、緩衝層16と障壁層18との間の2DEGチャネル層26を通りソース電極20とドレイン電極22との間に電流が流れることができる。ソース電極20およびドレイン電極22の形成については、上記の特許文献および非特許文献に詳述されている。

【0033】

ソース電極20およびドレイン電極22は、これらに限定されないが、チタン、アルミニウム、金、またはニッケルの合金を含む異なる材料で作製することができる。ゲート24も、これらに限定されないが、金、ニッケル、白金、チタン、クロム、チタンとタングステンの合金、または白金シリサイドを含む異なる材料で作製することができる。ゲート24は、多くの異なる長さ( $L_g$ )を有することができ、好適なゲート長は10nmから1000nmまでの範囲であるが、他のゲート長も使用できる。

【0034】

第1の非導電性スペーサ層28は、ゲート24の周りと、ゲート24とソースおよびドレイン電極20、22との間の障壁層18の表面の少なくとも一部の周りに形成される。図1に示されているように、スペーサ層28は、ゲート24とソースおよびドレイン電極20、22との間の障壁層18全体を覆う。第1のスペーサ層28は、誘電体層、またはいくつかの誘電体層の組合せを備えることができる。SiN、SiO<sub>2</sub>、Si、Ge、MgO<sub>x</sub>、MgN<sub>x</sub>、ZnO、SiNx、SiOx、それらの合金または層配列等の異なる誘電体材料を使用することができる。第1のスペーサ層は、厚さがさまざまであってよく、厚さの好適な範囲は約50nmから500nmまでである。図2に最もよく示されているように、ゲート24は、ゲートコンタクト36のところで接触する。

10

20

30

40

50

## 【0035】

ゲート24は、ゲート24よりも大きく、ゲート24と一体化された、一般的にT字型の頂部34も備える。大きな頂部34は、張り出し、ゲートよりも大きな断面を有し、その結果、抵抗が低くなり、ゲートコンダクタンスが高くなる。頂部34およびゲートは、一般的にT字型であるが、これらは多くの異なる形状をとりうることが理解されるだろう。目的は、ゲート24上に、導電性を高めて高周波動作に対応できるようにする区域を備えることであり、この区域は、この目的を達成するように拡大されている。拡大された頂部に対し特定の形状を持たせることは、重要でない。

## 【0036】

頂部34は、さらに、さまざまな材料から作製することができ、その一部は、上記のゲート24の材料と同じか、または類似のものとすることができます。頂部34のオーバーハンプは、多くの異なる長さ( $L_{tp}$ )を有することができ、好適な長さは、0.2μmから2μmまでの範囲であるが、他の長さも使用できる。さらに、頂部34は、その下の層に接しているか、またはその層の上方にあり、図示されている実施形態では、第2のスペーサ層30に接しているか、またはその上方にある。一実施形態では、頂部34とスペーサ層30との間に間隔が設けられ、これにより、ゲートとソースとの間の容量を低くすることができる。頂部34およびゲートは、既知のフォトレジスト技術を使用して作製することができ、一実施形態では、フォトレジスト層をスペーサ層30上に備え、頂部をフォトレジスト層上に形成することができる。フォトレジスト層をその後に取り除くと、スペーサ層と頂部との間に間隔が残る。

10

20

## 【0037】

第2のスペーサ層30は、ゲート24とソースおよびドレイン電極20、22との間にある第1のスペーサ層28の表面の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。図1に示されているように、第2のスペーサ層30は、ゲート24とソースおよびドレイン電極20、22との間の第1のスペーサ層28全体を覆う。第2のスペーサ層30は、誘電体層、またはいくつかの誘電体層の組合せを含むことができる。SiN、SiO<sub>2</sub>、Si、Ge、MgOx、MgNx、ZnO、SiNx、SiOx、それらの合金または層配列等の異なる誘電体材料を使用することができる。第2のスペーサ層30は、厚さがさまざまあってよく、厚さの好適な範囲は約50nmから500nmまでである。

30

## 【0038】

フィールドプレート32は、ゲート頂部34のオーバーハンプの下のスペーサ層28上に形成され、フィールドプレートは、図1に示されているようにスペーサ層28上で距離 $L_{td}$ にわたりドレイン電極22に向かって延在するか、またはそれとは別に距離 $L_{ts}$ にわたりソース電極20に向かって延在する。スペーサ層28は、フィールドプレート32と障壁層18との間を絶縁するように配置され、したがって、スペーサ層28は第1のフィールドプレート32の下の障壁層18を覆うだけでよい。しかしながら、製造しやすくするために、スペーサ層28は、典型的には、障壁層18全体を覆う。 $L_{td}$ は、さまざまな距離とすることができます、距離の好適な範囲は0.05~0.5μmである。同様に、 $L_{ts}$ は、さまざまな距離とすることができます、距離の好適な範囲は0.05~0.5μmである。他の実施形態では、フィールドプレートは連続的でなくてよいが、必要に応じて穴または中断部を備えることができる。第2のスペーサ層30は、フィールドプレート32を覆うこともできる。

40

## 【0039】

フィールドプレート32は、多くの異なる導電性材料を用いることができ、好適な材料は、標準的な金属化法を使用して堆積された金属または金属積層である。本発明による一実施形態では、フィールドプレート32は、後述のようにそれが電気的に接続される形態と同じ金属により構成される。

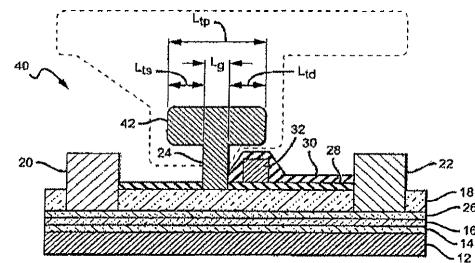

## 【0040】

フィールドプレート32は、ソース電極20またはゲート24のいずれかに電気的に接

50

続することができる。図2は、HEMT 10の活性領域の外で引き回され(runs outside the active area)、ソース電極20に接続されている第1の導電性経路38を通して第1のフィールドプレート32をソース電極20に電気的に接続することができる一実施形態を示している。図2に示されているように、経路38は、ゲートコンタクト36と反対側の縁でHEMTの活性領域の外に引き回される。本発明による代替実施形態では、導電性経路は、ゲートコンタクト36側でHEMT 10の活性領域の外に引き回すか、またはHEMT 10は、HEMT 10の片側または両側に引き回される2つまたはそれ以上の導電性経路を備えることができる(図示せず)。一実施形態では、導電性経路は、ソース電極20と同じ材料で構成することができ、他の実施形態では、異なる材料で構成することができ、ソース電極20の形成の後に作製プロセスの異なる工程で形成することができる。これは、本発明によりフィールドプレートをソースに接続できる様々な方法のうちの1つのみを説明していることが理解されるだろう。

#### 【0041】

あるいは、フィールドプレート32は多くの異なる方法によりゲート24に電気的に接続することもでき、そのうちの2つの好適な方法が本明細書で説明される。第1に、フィールドプレートは、HEMT 10の活性領域の外でフィールドプレート32とゲート24との間に引き回されている第2の導電性経路40によりゲート24に接続することができる。導電性経路40は、ゲートコンタクト36、またはゲート24のゲートコンタクト36と反対側の一部等のゲート24のHEMTの活性領域の外の部分に接続することができる。あるいは、複数の導電性経路を使用して、フィールドプレート32とゲート24とを接続することができる。

#### 【0042】

代替的接続構造は、導電性ビア(図示せず)の形態の導電性経路を備え、この経路は、第1のフィールドプレート32からゲート24へ、第1または第2のスペーサ層28、30を通して引き回されるように形成されうる。これらのビアは、ゲート24とフィールドプレート32との間を電気的に接続するものであり、ビアは、まずエッチングなどによりスペーサ層28、30に穴を形成し、次いで、別個の工程またはフィールドプレート32の形成時に穴に導電性材料を充填することにより形成することができる。ビアは、ゲート24からフィールドプレート32へ電流拡散が効果的に進むようにフィールドプレート32の下に周期的に配置することができる。

#### 【0043】

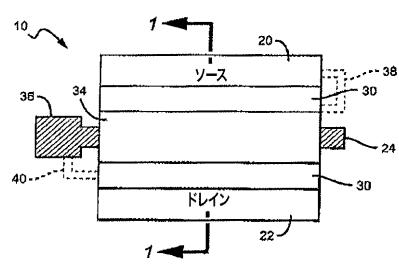

図3は、図1および2のHEMT 10と同じであり、HEMT 10と似た多くの形態を有するHEMT 40を示しており、類似の形態については、この図およびこれ以降の図を説明する際に同じ参照番号が使用されている。HEMT 40では、第2の非導電性スペーサ層30を、フィールドプレート32と、第1のスペーサ28のゲート24とドレイン22との間の部分とに被さるように形成されているものとして示しており、ゲート24とソース20との間にある第1のスペーサ28は第2のスペーサ層30により覆われていない状態にある。第2のスペーサ層30が、ゲート24とソース20との間、およびゲート24とドレイン22との間の第1のスペーサ層28全体の一部しか覆うことができない様々な実施形態があることが理解されるだろう。

#### 【0044】

加えて、図3のゲート24の一般的にT字型の頂部42は、図1および2の頂部34と異なる形状である。頂部34、42は、ゲートコンダクタンスを高めるために、さまざまな形状およびサイズを有しうることが理解されるだろう。頂部42がソース20およびドレイン22に向かって延在する程度は様々であり、典型的なゲート-ソース間間隔は0.05 μmから2 μm、典型的なゲート-ドレイン間間隔は0 μmから3 μmである。

#### 【0045】

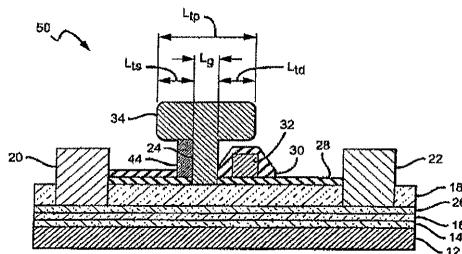

図4は、HEMT 10と類似の多くの形態を有する本発明によるHEMT 50の別の実施形態を示しており、類似の形態については、同じ参照番号が使用される。HEMT 50は、基板12と、核形成層14と、緩衝層16と、障壁層18と、ソース電極20

10

20

30

40

50

と、ドレイン電極 22 と、ゲート 24 と、2DEG 26 のチャネル層と、第 1 のスペーサ層 28 と、第 2 のスペーサ層 30 と、ゲート頂部 34 とを備える。

【0046】

しかしながら、頂部 34 のドレイン側のオーバーハングの下に 1 つのフィールドプレート 32 を有するだけではなく、第 2 のフィールドプレート部分 44 を第 1 のスペーサ層 28 または第 2 のスペーサ層 30 上に堆積させることができ（図示せず）。本発明による異なる第 2 のフィールドプレートは、異なった形で覆うことができ、第 2 のフィールドプレート 44 は、図示されているようにソース 20 とゲート 24 との間の頂部 34 のオーバーハングの下にあり、ゲート 24 および頂部 34 と一体化されている。多くの異なるフィールドプレート配置を含むことができ、第 1 のスペーサ層 28 は活性層全体の全部または一部を覆い、第 2 のスペーサ層 30 は第 1 もしくは第 2 のフィールドプレート 32、44 の全部もしくは一部、または第 1 のスペーサ層 28 の全部もしくは一部を覆うことが理解されるだろう。第 2 のスペーサ層 30 が、第 1 もしくは第 2 のフィールドプレート 32、44 および / またはスペーサ層 28 全体の一部しか覆わない実施形態では、第 2 のスペーサ層 30 は、第 1 のフィールドプレート 32 と第 2 のフィールドプレート 44 との間を電気的に絶縁する程度には、第 1 または第 2 のフィールドプレート 32、44 を覆っていかなければならない。

【0047】

第 2 のフィールドプレート 44 は、ソース電極 20 またはゲート 24 に接続することができ、多くの異なる接続構造を使用することができる。第 2 の導電性バスを第 2 のスペーサ層 30 上に形成し、第 2 のフィールドプレート 44 とソース電極 20 との間に延在させることができ。望ましくない静電容量が入り込むほど活性領域を覆いすぎないようにしながら、異なる数のバスを使用して、電流がソース電極 20 から第 2 のフィールドプレート 44 内に効果的に拡散するようにできる。第 1 のフィールドプレート 32 は、さらに、HEMT 40 の活性領域の外で引き回され、ソース電極 20 に接続されている第 3 の導電性経路を通してソース電極 20 に電気的に接続することもできる。

【0048】

第 2 のフィールドプレート 44 を堆積し、それをソース電極 20 に接続した後、窒化ケイ素等の誘電体パッシベーション層（図示せず）により活性構造を覆うことができる。誘電体パッシベーション層を形成する方法については、上記の特許文献および非特許文献において詳述されている。図 1 および 2 の HEMT 10 および後述のトランジスタも、（1つ又は複数の）スペーサ層および（1つ又は複数の）フィールドプレートの形成の後、誘電体パッシベーション層により覆うことができる。

【0049】

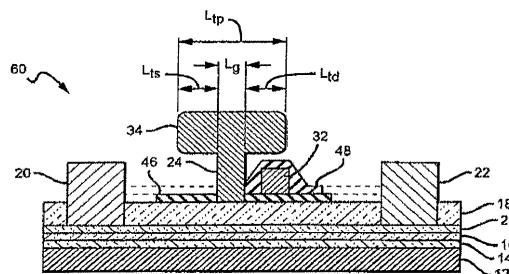

図 5 は、HEMT 10 と類似の多くの形態を有する本発明による HEMT 60 の他の実施形態を示しており、類似の形態については、同じ参照番号が使用される。HEMT 60 は、基板 12 と、核形成層 14 と、緩衝層 16 と、障壁層 18 と、ソース電極 20 と、ドレイン電極 22 と、ゲート 24 と、2DEG 26 のチャネル層と、フィールドプレート 32 と、ゲート頂部 34 とを備える。

【0050】

しかしながら、HEMT 60 は、ゲート 24 とソース 20 との間、および / またはゲート 24 とドレイン 22 との間の障壁層 18 の全表面の一部しか覆うことができない第 1 のスペーサ層 46 を備える。この覆う範囲は、フィールドプレート 32 と障壁層 18 との間を電気的に絶縁するのに十分なものでなければならない。加えて、第 2 のスペーサ層 48 は、ゲート 24 とソース 20 との間、および / またはゲート 24 とドレイン 22 との間の第 1 のスペーサ層 46 の全表面の一部しか覆わない可能性がある。

【0051】

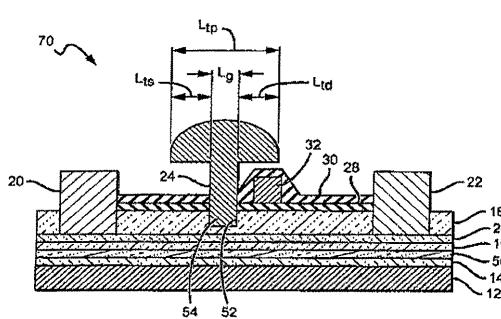

図 6 は、HEMT 10 と類似の多くの形態を有する本発明による HEMT 70 の他の実施形態を示している。HEMT 70 は、基板 12 と、核形成層 14 と、緩衝層 16 と、障壁層 18 と、ソース電極 20 と、ドレイン電極 22 と、ゲート 24 と、2DEG 50

26のチャネル層と、第1のスペーサ層28と、第2のスペーサ層30と、フィールドプレート32と、ゲート頂部34とを備える。

#### 【0052】

しかしながら、HEMT 70は、障壁層18のリセス52がゲート24の下側部分54を受容する代替実施形態を示している。さらに、 $1n_x Ga_{1-x}N$ 層56を、エネルギー障壁として用いるためにGaN緩衝層等に含めることができる。この層は、他の材料により構成することもでき、この配置は特許文献18において説明されている。この文献は、本明細書に完全に記載されたかのように参照により本明細書に取り込む。

#### 【0053】

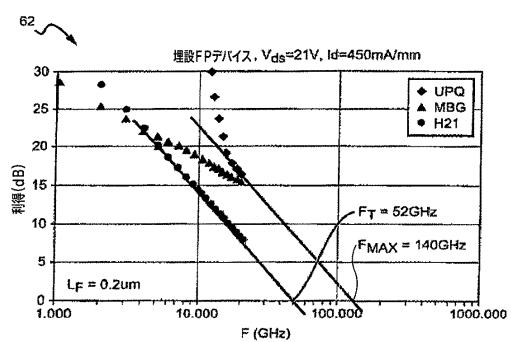

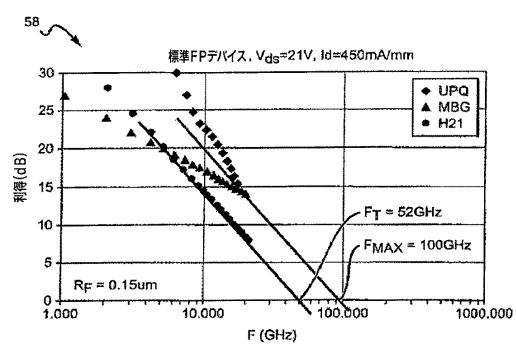

図7は、表58および62を示しており、これは、標準ゲート接続され、かつ埋設されたソース接続のフィールドプレートを有する2つのGaN HEMTの電流利得遮断周波数(Ft)および電力利得遮断周波数(Fmax)の利得をプロットしたものである。表58および62は、GaNベースのHEMTの動作特性を比較しており、表58の標準FPデバイスと比較したときに、表62の埋設されたFPデバイスが50%高いFmaxを示していることがわかる。

10

#### 【0054】

このフィールドプレート配置は、MESFETおよび金属酸化膜半導体ヘテロ構造電界効果トランジスタ(MOSFET)を含むHEMT以外のトランジスタに応用することができる。このフィールドプレート配置は、通信、計装、軍事用途等を目的とするマイクロ波およびミリメートル波電力増幅器にも応用することができる。

20

#### 【0055】

本発明は、いくつかの好ましい構成を参照して詳説されているが、他の形態も考えられる。埋設フィールドプレートおよびゲート配置は、多くの異なるデバイスにおいて使用することができる。フィールドプレートおよびゲートは、多くの異なる形状をとることもでき、様々な方法でソースコンタクトに接続することができる。したがって、本発明の精神および範囲は、上述の本発明の好ましい形態に限定されるべきではない。

#### 【図面の簡単な説明】

#### 【0056】

【図1】本発明によるHEMTの一実施形態の断面図である。

30

【図2】図1に示されている実施形態の平面図である。

【図3】本発明によるHEMTの別の実施形態の断面図である。

【図4】いくつかのフィールドプレートを有する本発明によるHEMTの別の実施形態の断面図である。

【図5】いくつかのフィールドプレートを有する本発明によるHEMTの別の実施形態の断面図である。

【図6】いくつかのフィールドプレートを有する本発明によるHEMTの別の実施形態の断面図である。

【図7】フィールドゲート-ソースフィールドプレートを有しないHEMTと比べた本発明によるHEMTの動作特性を比較した表を示す図である。

40

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

審査官 村岡 一磨

(56)参考文献 国際公開第2006/025971 (WO, A1)

特開平07-176544 (JP, A)

特表2008-511172 (JP, A)

特開平07-273128 (JP, A)

特開2000-315804 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/338

H01L 29/778

H01L 29/812