## (12) 发明专利

(10) 授权公告号 CN 110268517 B

(45) 授权公告日 2023.03.21

(21) 申请号 201880009810.X

(74) 专利代理机构 北京市汉坤律师事务所

(22) 申请日 2018.02.01

11602

(65) 同一申请的已公布的文献号

专利代理人 王其文 张涛

申请公布号 CN 110268517 A

(51) Int.CI.

(43) 申请公布日 2019.09.20

H01L 23/051 (2006.01)

(30) 优先权数据

H01L 23/535 (2006.01)

17154197.2 2017.02.01 EP

H01L 23/62 (2006.01)

(85) PCT国际申请进入国家阶段日

H01L 25/07 (2006.01)

2019.08.01

H01L 29/16 (2006.01)

H01L 23/00 (2006.01)

(86) PCT国际申请的申请数据

(56) 对比文件

PCT/EP2018/052559 2018.02.01

EP 2530711 A1, 2012.12.05

(87) PCT国际申请的公布数据

EP 2528092 A1, 2012.11.28

W02018/141867 EN 2018.08.09

EP 2729964 A1, 2014.05.14

(73) 专利权人 日立能源瑞士股份公司

CN 104241372 A, 2014.12.24

地址 瑞士巴登

WO 2015176985 A1, 2015.11.26

(72) 发明人 柳春雷 J.舒德雷尔 F.布雷姆

CN 104040715 A, 2014.09.10

M.拉希莫 P.K.施泰默 F.杜加尔

审查员 李艳红

权利要求书2页 说明书8页 附图2页

## (54) 发明名称

具有短路失效模式的功率半导体模块

## (57) 摘要

功率半导体模块(10)包括：基板(12)；包括Si衬底的Si芯片(16a)，该Si芯片(16a)附接到基板(12)；利用第一压销(24a)紧压Si芯片(16a)的第一金属预制件(22a)；宽带隙材料芯片(16b)，其包括宽带隙衬底和在该宽带隙衬底中提供的半导体开关(28b)，该宽带隙材料芯片(16b)附接到基板(12)；以及利用第二压销(24b)紧压宽带隙材料芯片(16b)的第二金属预制件(22b)；其中Si芯片(16a)和宽带隙材料芯片(16b)经由基板(12)并且经由第一压销(24a)和第二压销(24b)并联连接；其中第一金属预制件(22a)适合于在被过电流加热时形成通过Si芯片(16a)的传导路径；并且其中第二金属预制件(22b)适合于在被过电流加热时形成通过宽带隙材料芯片(16b)的暂时的传导路径或开路。

1. 一种功率半导体模块(10)，包括：

基板(12)；

包括Si衬底的Si芯片(16a)，所述Si芯片(16a)附接到所述基板(12)；

第一金属预制件(22a)，所述第一金属预制件(22a)被第一压销(24a)紧压抵靠所述Si芯片(16a)的一侧；

宽带隙材料芯片(16b)，所述宽带隙材料芯片(16b)包括宽带隙衬底和所述宽带隙衬底中提供的半导体开关(28b)，所述宽带隙材料芯片(16b)附接到所述基板(12)；

第二金属预制件(22b)，所述第二金属预制件(22b)被第二压销(24b)紧压抵靠所述宽带隙材料芯片(16b)的一侧；

其中所述Si芯片(16a)和所述宽带隙材料芯片(16b)经由所述基板(12)并且经由所述第一压销(24a)和所述第二压销(24b)并联连接；

其中所述第一金属预制件(22a)适合于在被过电流加热时通过与所述Si衬底形成合金而形成通过所述Si芯片(16a)的传导路径；

其中由具有比所述第一金属预制件(22a)的材料更高的熔点的材料制成的所述第二金属预制件(22b)适合于在被过电流加热时形成通过所述宽带隙材料芯片(16b)的至少暂时的传导路径。

2. 如权利要求1所述的功率半导体模块(10)，

其中所述第二金属预制件(22b)适合于通过至少部分被所述过电流熔化来形成通过所述宽带隙材料芯片(16b)的至少暂时的传导路径。

3. 如权利要求1或2所述的功率半导体模块(10)，

其中所述第一金属预制件(22a)由Al、Cu、Ag、Mg或其合金制成。

4. 如权利要求1或2所述的功率半导体模块(10)，

其中所述第二金属预制件(22b)由Mo、W或其合金制成。

5. 如权利要求1或2所述的功率半导体模块(10)，

其中所述基板(12)由Mo制成。

6. 如权利要求1或2所述的功率半导体模块(10)，

其中所述宽带隙材料芯片(16b)的所述宽带隙材料是SiC。

7. 如权利要求1或2所述的功率半导体模块(10)，

其中所述Si芯片(16a)包括在所述Si衬底中提供的半导体开关(28a)。

8. 如权利要求7所述的功率半导体模块(10)，

其中所述Si芯片(16a)的所述半导体开关(28a)的栅极(30a)在所述半导体模块(10)中与所述宽带隙材料芯片(16b)的所述半导体开关(28b)的栅极(30b)电连接。

9. 如权利要求7所述的功率半导体模块(10)，

其中所述Si芯片(16a)的所述半导体开关(28a)的栅极(30a)电连接到所述半导体模块(10)的第一栅极端子(34a)并且所述宽带隙材料芯片(16b)的所述半导体开关(28b)的栅极(30b)电连接到所述半导体模块(10)的第二栅极端子(34b)，使得所述Si芯片(16a)的所述半导体开关(28a)独立于所述宽带隙材料芯片(16b)的所述半导体开关(28b)而可开关。

10. 如权利要求7所述的功率半导体模块(10)，

其中所述Si芯片(16a)的所述半导体开关(28a)的栅极(30a)未连接到由所述半导体模

块(10)提供的栅极端子。

11. 如权利要求1或2所述的功率半导体模块(10)，

其中所述Si芯片(16a)不包括有源可开关的开关。

12. 如权利要求1或2所述的功率半导体模块(10)，其中所述Si芯片(16a)是无源Si层。

13. 如权利要求1至2以及8至10中任一项所述的功率半导体模块(10)，

其中所述功率半导体模块(10)包括与所述Si芯片(16a)并联连接的至少两个宽带隙材料芯片(16b)。

14. 如权利要求1至2以及8至10中任一项所述的功率半导体模块(10)进一步包括：

连接到所述第一压销(24a)和所述第二压销(24b)的导电顶板(14)。

15. 如权利要求1至2以及8至10中任一项所述的功率半导体模块(10)，

其中所述第一压销(24a)和所述第二压销(24b)中的至少一个包括弹簧元件(26a、

26b)。

## 具有短路失效模式的功率半导体模块

### 技术领域

[0001] 本发明涉及功率半导体器件的领域。特别地，本方面涉及用于这种器件的功率半导体模块。

### 背景技术

[0002] 诸如转换器、电驱动器、STATCOMS之类的功率半导体器件通常由多个功率半导体模块组装而成，所述多个功率半导体模块中的每个机械且电连接一个或多个功率半导体元件。在高压DC应用中，通常需要多个功率半导体模块串联连接来满足高压和高电流要求。在失效(failure)情况下变成永久传导的功率半导体模块在这种串联连接中可具有很大优势。

[0003] 在具有基于Si(硅)的半导体元件的半导体模块中，可以在Si芯片的电极上提供金属预制件(preform)，该金属预制件适合于与芯片的Si材料形成低熔点共晶合金并且创建传导路径来运输全电流负载通过失效点。例如，在相对低的温度(577°C)，Si与Al(铝)之间的共晶反应实现这样的固有失效补偿。

[0004] 例如，EP 0989611 A2和EP 2 503 595 A1涉及具有基于Si的半导体芯片的功率半导体模块，该半导体芯片是在能够与芯片的Si材料形成共晶合金的两个层之间提供。

[0005] 具有基于SiC(碳化硅)和其他宽带隙衬底的半导体元件的半导体模块由于它们的高阻断能力而越来越多地在高压应用中被采用。

[0006] WO 2016/062 426 A1示出了具有并联连接的Si芯片12和SiC芯片的半导体模块。按压器件用于压到Si芯片上。提到了这促进短路失效模式的预备。

[0007] WO 2013/004 297 A1示出了具有诸如IGBT的若干半导体器件的半导体模块，通过弹性元件将金属层压到半导体器件上。在熔化时，该金属层适合于与半导体器件的材料形成合金。

[0008] WO2012/107 482 A2示出了具有多个基于硅的半导体芯片的半导体模块，在该半导体芯片中的每个之上提供由Al制成的第一预制件和由Mo制成的第二预制件。提到了第一金属预制件与芯片之间的共晶合金的形成。

### 发明内容

[0009] 本发明的目的是提供基于宽带隙半导体元件的紧凑、稳固且不太复杂的功率半导体器件。

[0010] 该目的由独立权利要求的主题来实现。另外的示范性实施例从从属权利要求和下面的描述显而易见。

[0011] 本发明涉及功率半导体模块。在此以及在下面，术语“功率”可涉及处理超过10A和/或超过1.000V的电流的能力。功率半导体模块一般可以是机械支承诸如晶体管、晶闸管、二极管之类的一个或多个功率半导体元件且为其提供端子的器件。一般来说，功率半导体模块可包括提供端子的壳体，其中容纳一个或多个功率半导体元件。

[0012] 根据本发明的实施例，功率半导体模块包括基板，其可以完全导电或至少包括导电层。

[0013] 此外，功率半导体模块包括：包括Si衬底的Si芯片，该Si芯片附接到基板；以及利用第一压销紧压Si芯片的一侧的第一金属预制件。例如，Si芯片可以熔接、烧结或焊接到基板。第一金属预制件可以直接紧压Si芯片。必须注意，用于将第一金属预制件接合到Si芯片和/或Si芯片上的电极层的接合层可以视为Si芯片的一部分。第一压销可以具有与第一金属预制件不同的材料。

[0014] 功率半导体模块还包括：宽带隙材料芯片，其包括宽带隙衬底和在该宽带隙衬底中提供的半导体开关，宽带隙材料芯片附接到基板；以及利用第二压销紧压宽带隙材料芯片的一侧的第二金属预制件。例如，Si芯片可以熔接、烧结或焊接到基板。第二金属预制件可以直接紧压宽带隙材料芯片。必须注意，用于将第二金属预制件接合到宽带隙材料芯片和/或宽带隙芯片上的电极层的接合层可以视为宽带隙材料芯片的一部分。第二压销可以具有与第二金属预制件不同的材料。

[0015] 宽带隙材料可以是SiC、GaN等。它可以用至少2eV的半导体带隙来表征。

[0016] 半导体开关可以是具有适合于控制半导体开关的两个另外的电极之间的电阻的栅极的开关元件。半导体开关可以是晶体管或晶闸管。例如，宽带隙材料开关的宽带隙材料可以是SiC。例如，半导体开关可以是SiC MOSFET、SiC JFET、SiC IGBT、SiC BJT或SiC GT0。

[0017] 第一金属预制件和/或第二金属预制件可以是具有两个平坦表面的板状体。第一金属预制件和/或第二金属预制件可以比对应芯片更厚。

[0018] Si芯片和/或宽带隙材料芯片可以都具有其中两侧上提供扁平电极的大致板状体。在面对和/或邻接金属预制件的那侧上，还可以存在由相应芯片提供的开关的栅电极。

[0019] Si芯片和宽带隙材料芯片经由基板并且经由第一压销和第二压销并联电连接。特别地，它们在功率半导体模块内并联连接。可能的是，顶板用第一压销和第二压销将电路闭合。必须注意，Si芯片可以是完全无源元件和/或为沿第一金属预制件和第一压销的电流路径仅提供相当高的电阻的层。也就是说，可能的是在正常操作期间完全没有电流流过Si芯片。

[0020] 第一金属预制件适合于在被过电流(overcurrent)加热时，可选地与Si衬底一起形成通过Si芯片的传导路径。该传导路径可以用合金形成，该合金由Si衬底和第一金属预制件的材料形成。除Al之外，其他金属也可以适合于与Si形成共晶合金。在此，过电流可以是使得Si芯片和/或例如第一金属预制件熔化或开始熔化的这样高的电流。

[0021] 第二金属预制件适合于在被过电流加热时与宽带隙衬底形成通过宽带隙材料芯片的至少暂时的传导路径。在该上下文中，过电流可以是使得第二金属预制件和/或宽带隙材料开始熔化的这样高的电流。第二金属预制件由具有比第一金属预制件的材料更高的熔点的材料制成。采用这样的方式，与Si芯片的Si材料的熔点相比，第二金属预制件可以导致宽带隙材料的更高熔点。

[0022] 利用该构造，Si芯片和第一金属预制件可以提供永久SCFM(短路失效模式)，而宽带隙材料芯片和第二金属预制件可以提供暂时的传导路径或甚至开路。

[0023] 半导体模块可以例如通过堆叠而与其他半导体模块串联连接，这些其他半导体模块可以具有与其中所描述的半导体模块相同的类型。在该情况下，宽带隙材料芯片失效，它

可能变为阻断或可能至少具有比其他半导体模块高得多的电阻。因此，跨串联连接的半导体模块的电压可以完全或大致应用于具有失效芯片的半导体模块，这可能引起通过宽带隙材料芯片的电弧和过电流。

[0024] 形成通过宽带隙材料芯片的暂时的传导路径，然而该暂时的传导路径可能由于为传导路径形成的材料而退化。例如，SiC衬底和金属预制件可以形成导电物质，其不稳定并且一段时间后消失。术语“暂时”可以涉及比“永久”时间跨度小得多的时间跨度。例如，暂时的时间跨度可以比1秒更短。

[0025] 根据本发明的实施例，第二金属预制件适合于通过被过电流熔化来形成通过宽带隙材料芯片的至少暂时的传导路径。第二金属预制件可以被过电流加热到使得它自身和/或宽带隙材料熔化并且通过宽带隙材料芯片形成传导材料的传导路径的这种高温度。Si芯片和第一金属预制件可以形成永久导电路径。必须注意，术语“永久”指的是比“暂时”时间跨度长得多的时间跨度，其例如是“暂时”时间跨度的100倍或以上。通过Si芯片的永久导电路径的形成可以是由于仅仅跨Si芯片的电压引起，如关于宽带隙材料芯片所描述的那样。然而，还可以有可能的是，Si芯片中的开关被提供有栅电压，该栅电压引起Si芯片的内部电阻，从而导致加热到用于形成传导路径的适合的温度。

[0026] 总之，在宽带隙材料芯片中有故障的情况下，Si芯片和它的金属预制件可以比宽带隙材料芯片更容易进入安全的短路失效模式。Si芯片可以视为牺牲器件，其提供功率半导体模块的固有安全特征。

[0027] 所得的宽带隙-Si半导体模块可以具有在正常操作期间使用低损耗宽带隙材料芯片的优势，并且可以具有由Si芯片提供的固有、可靠的SCFM能力的优势。

[0028] 采用这样的方式，基于宽带隙材料的功率半导体模块可以可靠地被用于其中多个功率半导体模块串联连接的高压应用，诸如HVDC应用、STATCOM应用等。利用该类型的功率半导体模块，实现更好的功率系统设计与更低的系统成本和更高的系统效率。例如，可以省略机械旁路和防爆壳体。

[0029] 一般来说，第一和第二金属预制件可以由Al(铝)、Cu(铜)、Ag(银)、Mg(镁)、Mo(钼)、W(钨)或它们的组合(诸如其合金)制成。如已经提到的，第二金属预制件由具有比第一金属预制件的材料更高的熔点的材料制成。在该情况下，第二金属预制件将在更接近宽带隙衬底的熔化温度的温度熔化，这可以支持形成通过宽带隙材料的传导路径。具有较低熔点的金属预制件(例如Al、Cu、Ag、Mg等)优选地被定向在Si芯片顶部并且具有较高熔点的金属预制件(Mo、W等)优选地在宽带隙材料(例如SiC)芯片的顶部。

[0030] 根据本发明的实施例，第一金属预制件由Al、Cu、Ag、Mg或其合金制成。例如，Al可以在相当低的温度与Si形成共晶合金。

[0031] 根据本发明的实施例，第二金属预制件由Mo、W或其合金制成。有益组合可以是：用于第一金属预制件的Al和用于第二金属预制件的Mo，这是因为Mo除了相当高的熔点外还具有诸如SiC的适合于宽带隙材料的机械性质(诸如它的热膨胀系数)。

[0032] 根据本发明的实施例，基板由Mo制成。Mo可以是有益的，因为它具有与Si、SiC或其他宽带隙材料相似的热膨胀系数。此外，Mo还可以在更高的温度下与宽带隙材料芯片的宽带隙衬底形成至少暂时的传导路径。在该情况下，第二金属预制件也可以由Mo制成。

[0033] Si芯片可以是虚设(dummy)Si芯片或功能Si芯片。虚设Si芯片可以是不被开关或

仅在失效情况下被开关的芯片。功能Si芯片可以是与宽带隙材料芯片一起被开关的Si芯片。

[0034] 在功能Si芯片的情况下,Si芯片与宽带隙材料芯片的传导电流的比率可以根据系统设计要求而变化。功能Si芯片可以被单独控制并且它仅在需要时起作用。针对Si芯片和宽带隙材料芯片的栅极单元可以是相同的或者Si芯片和宽带隙材料芯片可以具有不同的栅极单元。

[0035] 根据本发明的实施例,Si芯片包括Si衬底中提供的半导体开关。例如,开关可以是晶体管、晶闸管,例如IGBT或IGCT,或它们在一个衬底中的组合。在该情况下,Si芯片可以是功能或虚设的。它可以具有到外部端子的栅极连接或它的栅极可以与功率半导体模块的电路断开连接。

[0036] 根据本发明的实施例,Si芯片的半导体开关的栅极在半导体模块中与宽带隙材料芯片的半导体开关的栅极电连接。可能的是,两个开关都连接到相同的栅极控制单元。在该情况下,在正常操作模式中,Si开关和宽带隙开关都可以用于对通过模块的电流进行开关。

[0037] 根据本发明的实施例,Si芯片的半导体开关的栅极电连接到半导体模块的第一栅极端子并且宽带隙材料芯片的半导体开关的栅极电连接到半导体模块的第二栅极端子,使得Si芯片的半导体开关独立于宽带隙材料芯片的半导体开关而可开关。在该情况下,在正常操作期间,两个开关都可以用类似的方式开关。在失效模式操作期间,Si开关可以被开关来产生导电路径。可能的是,开关Si仅在失效模式操作期间进行开关。

[0038] 根据本发明的实施例,Si芯片的半导体开关的栅极未连接到由半导体模块提供的栅极端子。在该情况下,Si芯片可以是虚设的,在正常操作或失效模式操作中都不用于对通过半导体模块的电流进行开关。

[0039] 根据本发明的实施例,Si芯片不包括有源可开关的开关。有源开关或有源可开关的开关可以是具有在设置为不同电势时可以阻断且允许电流通过开关的栅极的开关。例如,Si芯片可以包括二极管。与宽带隙材料芯片的开关反并联连接的续流二极管可以用作功率半导体模块的SCFM元件。

[0040] 根据本发明的实施例,Si芯片是无源Si层。无源Si层可以是无掺杂Si层和/或在半导体模块的正常操作条件期间在两个方向上都不传导电流的Si层。Si芯片可以不包括半导体器件。还可以有可能的是,存在Si芯片只为提供Si材料以用于连同第一金属预制件一起形成传导路径。

[0041] 必须注意,在通过Si芯片的传导路径仅仅是被动形成(Si芯片中没有存在或不存在的开关的任何开关)的情况下,Si芯片的厚度可能必须适应于电压,这引起通过Si芯片的电弧。Si芯片的抗弧性(arcing resistance)可能必须低于串联连接的功率半导体模块所能提供的电压。

[0042] 根据本发明的实施例,功率半导体模块包括与Si芯片并联连接的至少两个宽带隙材料芯片。可能的是,功率半导体模块包括不止一个宽带隙材料芯片和/或不止一个Si芯片。可能的是,Si芯片的SCFM能力用于多个宽带隙材料芯片。

[0043] 根据本发明的实施例,功率半导体模块进一步包括连接到第一压销和第二压销的导电顶板。该顶板可以由Cu或Al制成。

[0044] 根据本发明的实施例,第一压销和/或第二压销包括弹簧元件。例如,该弹簧元件

可以包括一个或多个碟形弹簧(disc spring),其可以由导电材料制成。

[0045] 本发明的这些和其他方面将从下文描述的实施例显而易见并且参考这些实施例来阐明。

## 附图说明

[0046] 本发明的主题将在下面的文本中参考附图中图示的示范性实施例来更详细地解释。

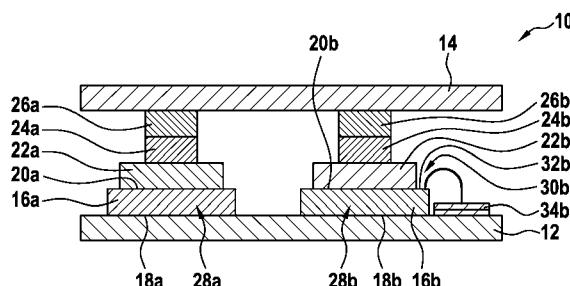

[0047] 图1示意地示出根据本发明的实施例通过功率半导体模块的横截面。

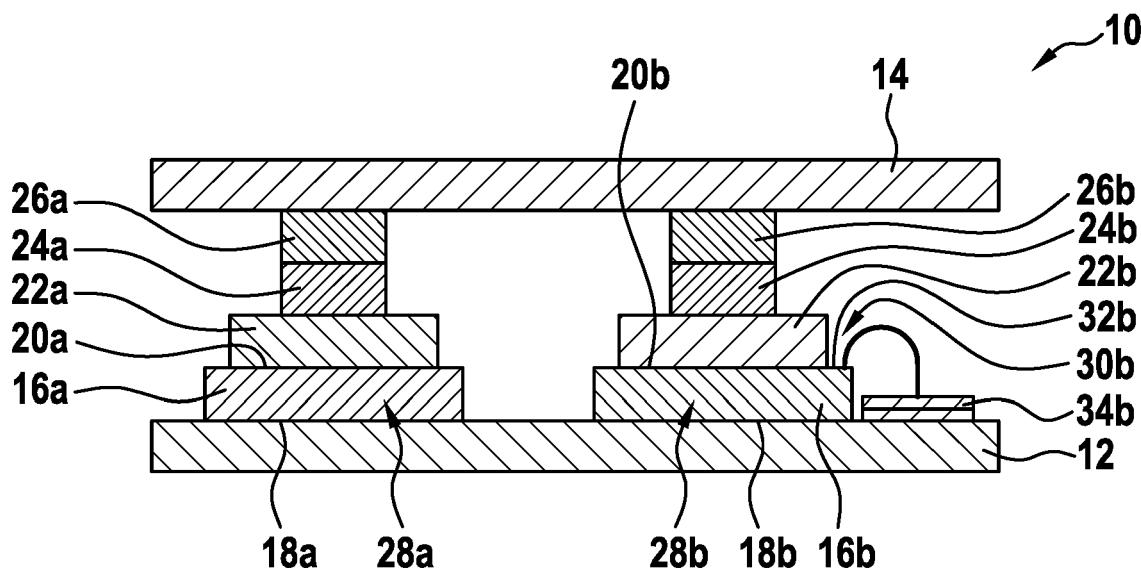

[0048] 图2示意地示出根据本发明的另外的实施例通过功率半导体模块的横截面。

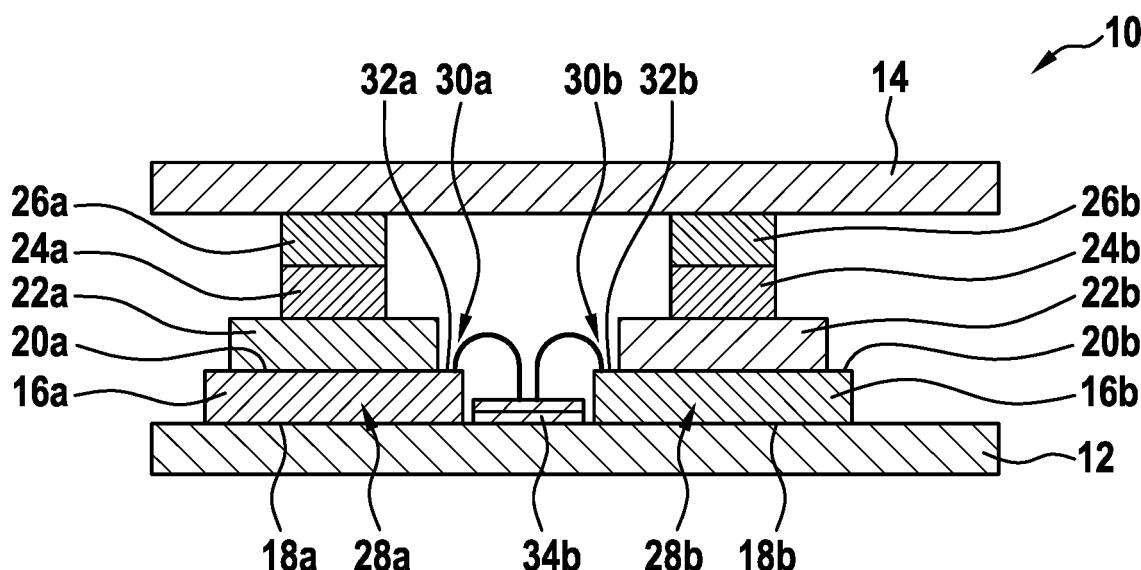

[0049] 图3示意地示出根据本发明的另外的实施例通过功率半导体模块的横截面。

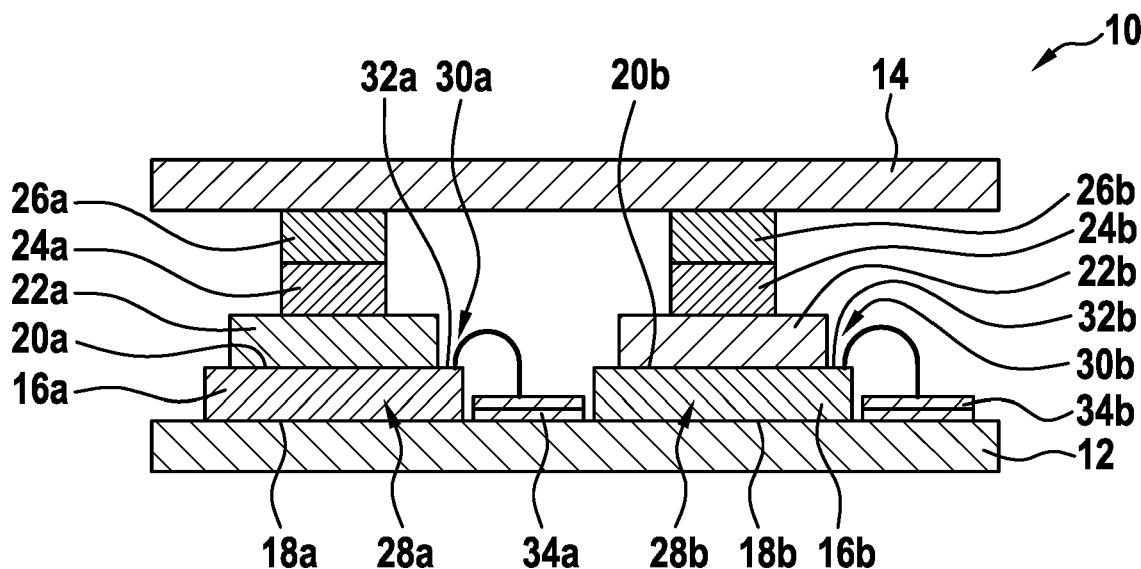

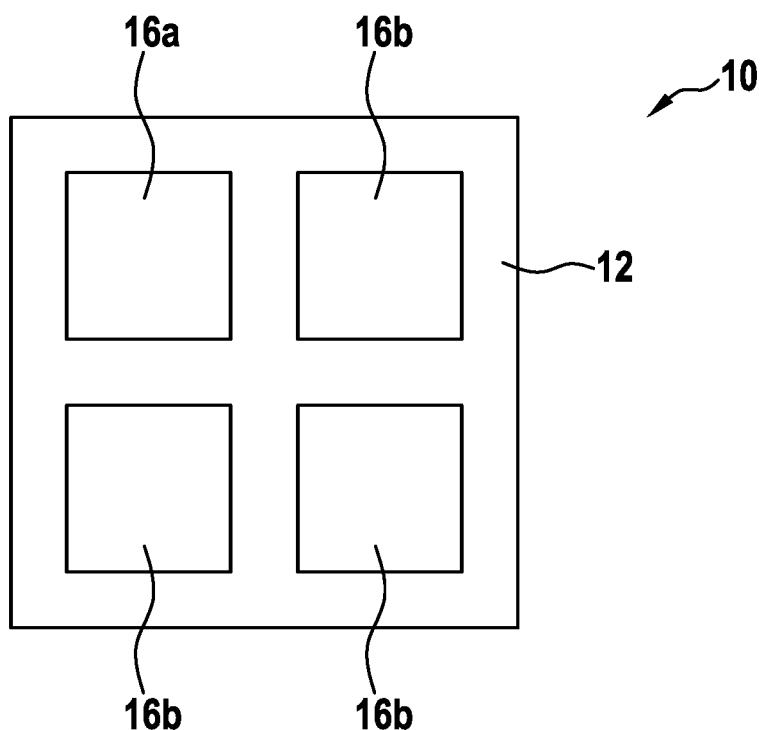

[0050] 图4示意地示出根据本发明的另外的实施例的功率半导体模块的顶视图。

[0051] 图中使用的参考符号和它们的含义以总结形式在参考符号列表中列出。原则上,相同的部件在图中提供有相同的参考符号。

## 具体实施方式

[0052] 图1示意示出通过功率半导体模块10的横截面,该功率半导体模块10包括基板12、顶板14和夹在它们之间的两个半导体芯片16a、16b。

[0053] 基板12可以是导电板,其例如由Mo制成。顶板也可以是导电板,其例如由Cu或Al制成。

[0054] 第一半导体芯片16a是基于Si衬底作为半导体的Si芯片。第二半导体芯片16b是基于诸如SiC的宽带隙半导体衬底的宽带隙材料芯片。

[0055] 第一和第二半导体芯片16a、16b可以包括第一和第二底部电极18a、18b以及第一和第二顶部电极20a、20b。术语“顶部”和“底部”不是绝对地理位置,而是仅用于区分两个相对放置的电极。每个电极可以由金属层提供,该金属层比对应芯片16a、16b的厚度薄得多。两个半导体芯片16a、16b可以例如通过烧结、焊接或熔接来附接到基板12。

[0056] 第一金属预制件22a直接在Si芯片16a顶部并且第二金属预制件22b直接在芯片16b顶部。如上文指示的,金属预制件22a、22b可以由相同材料或不同材料制成。一个或两个金属预制件22a、22b可以附接到相应芯片16a、16b(通过烧结、焊接或熔接)和/或可以紧压相应芯片16a、16b,例如紧压相应的电极20a、20b。

[0057] 可以通过导电压销24a、24b施加压力,该导电压销紧压相应的金属预制件22a、22b。例如,第一和/或第二压销24a、24b可以包括弹簧元件26a、26b,其例如可以包括碟形弹簧。金属预制件22a、22b、压销24a、24b和/或弹簧元件26a、26b可以被容纳在基板12与顶板14之间。

[0058] 例如经由压销24a、24b和/或经由弹簧元件26a、26b,金属预制件22a、22b可以与顶板电接触。采用这样的方式,两个芯片16a、16b互相并联连接,其中在每个电流路径中存在金属预制件22a、22b。

[0059] 金属预制件22a适合于在被过电流加热时形成通过Si芯片16a的传导路径。采用这样的方式,提供短路失效模式,其形成到Si芯片16a的永久传导路径。

[0060] 金属预制件22b适合于在被过电流加热时形成通过宽带隙材料芯片16b的至少暂

时的传导路径。采用这样的方式,提供短路失效模式,其形成到宽带隙材料芯片16b的暂时的传导路径。

[0061] 采用组合的方式,当功率半导体模块10中发生失效时,通过宽带隙材料芯片16b的电流可以形成暂时的传导路径或甚至开路。同时或在那之后,可以通过Si芯片16a形成传导路径,其可以为半导体模块10提供永久短路失效模式。采用这样的方式,对于宽带隙材料芯片16b的不那么可靠的短路失效模式可以得到由Si芯片16a提供的更加可靠的短路失效模式的支持。

[0062] 因为Si的熔点可能低于宽带隙材料的熔点(这是针对SiC和大部分其他宽带隙材料的情况),第一金属预制件22a可以由具有比第二金属预制件22b的金属材料更低的熔点的金属材料制成。例如,金属预制件22a可以由Al制成并且金属预制件22b可以由Mo制成。

[0063] 在Al的情况下,因为Al可以与Si芯片16a的Si材料形成共晶合金,因此可以提供非常可靠的短路失效模式。

[0064] 宽带隙材料芯片16b包括半导体开关28b,其能够用栅极30b来控制。宽带隙材料芯片16b可以包括与电极20b在相同侧上的栅电极32b,其可以例如经由线接合(wire bond)与半导体模块10的栅极端子34b电连接。例如,半导体开关28b可以是SiC MOSFET。在正常操作模式期间,半导体开关28b可以用来自经由端子34b连接的栅极单元的栅极信号接通和断开。

[0065] Si芯片16a可以是功能或虚设芯片。如图1中所示,Si芯片16a可以完全不包含半导体元件或可以包含没有栅极的半导体元件,诸如二极管。还可能的是,Si芯片16a包括没有栅极连接的开关。

[0066] 如图2和3中所示,Si芯片16a可以包括半导体开关28a,其能用栅极30a来控制。Si芯片16a可以包括与电极20a在相同侧上的栅电极32a,其可以例如经由线接合与半导体模块10的第一和/或第二栅极端子34a、34b电连接。例如,开关28a可以是IGBT或IGCT。

[0067] 如图2中所示,Si芯片16a的栅极30a可以与宽带隙芯片16b的栅极30b连接到相同的栅极端子。采用这样的方式,开关28a、28b都可以用相同的栅极信号来控制,该栅极信号可以由相同的栅极单元来提供。在正常操作模式期间,半导体开关28b都可以用来自相同栅极单元的栅极信号接通和断开。在失效操作模式期间,该栅极单元还可以提供迫使Si芯片16a加热并且与第一金属预制件22a形成传导路径的栅极信号。

[0068] 如图3中所示,Si芯片16a的栅极30a可以与宽带隙芯片16b的栅极30b连接到不同的栅极端子,使得开关28a、28b可以彼此独立地被控制。例如可以从相同或从两个不同的栅极单元向开关28a、28b提供两个独立的栅极信号。

[0069] 在正常操作模式期间,开关28b以及可选地开关28a可以被开关以控制通过半导体模块10的电流。

[0070] 在失效操作模式期间,可以控制开关28a使得Si芯片16a加热并且与第一金属预制件22a形成传导路径。例如,栅极信号可以使得Si芯片16a具有电阻,这导致足够的功率被转换成热以便使第一金属预制件22a熔化。

[0071] 一般来说,例如对于高压应用中的AC到DC转换,图1至3中所示的半导体模块10可以与等同设计的半导体模块10堆叠来形成高压开关。

[0072] 当作为与其他半导体模块10串联连接的半导体模块10的一部分的芯片16a、16b中

的一个中存在失效时,可能发生下面的情形。

[0073] 如果首先在Si芯片16a中发生失效,则Si衬底将在失效之后立即与第一金属预制件22a形成传导路径,因为可以存在跨芯片16a的足够高的电压,这时其他半导体模块正在传导。

[0074] 如果失效首先在宽带隙芯片16b中发生,则可以发生至少暂时的SCFM(短路失效模式)形成。通过使宽带隙材料和第二金属预制件22b熔化并且起反应来形成传导路径。

[0075] 例如因为宽带隙芯片16b中的传导路径尚未形成或具有太高的电阻,在宽带隙芯片16b已经失效之后的高电阻或开路可以导致被动迫使Si SCFM形成。随后的电压尖峰将形成通过如上面描述的Si芯片16a的安全传导路径。

[0076] 此外,从通过宽带隙芯片16b提供的SCFM传导路径到通过Si芯片16a的Si SCFM传导路径的转变可以是有可能的。通过宽带隙材料形成的传导路径可能仅在短时段承受全电流负载,电阻可以增加或可以导致开路。然后,如上面描述的,可以形成到通过Si芯片16a的传导路径的转变。这可以延长半导体模块10的SCFM模式的寿命。

[0077] 另外,对于图3中示出的实施例,单独的栅极单元可以接通开关28a以在失效之后立即传导全负载电流和/或主动迫使SCFM形成。

[0078] 图4示出一个Si芯片16a与超过一个宽带隙材料芯片16b在一个半导体模块10中组合。采用这样的方式,仅一个Si芯片16a可以为超过一个宽带隙材料芯片16b提供短路失效模式。图4中的所有芯片16a、16b可以被提供有如图1至3中所示的金属预制件22a、22b和压销24a、24b。此外,栅极30a、30b可以按图1至图3中示出的那样连接,其中由宽带隙材料芯片16b提供的开关28b的栅极30b可以与相同的第二端子34b并联连接。

[0079] 虽然已经在附图和前述描述中详细地图示和描述本发明,但这样的图示和描述要被认为是说明性或示范性的而不是限制性的;本发明不限于所公开的实施例。根据附图、公开以及所附的权利要求的研究,实践所要求保护的发明的以及本领域技术人员能够理解和实现对于所公开的实施例的其它变化。在权利要求中,词语“包括”不排除其它元件或步骤,并且不定冠词“一”或“一个”不排除复数个。单个处理器或控制器或其他单元可以实现权利要求中所记载的若干项目的功能。在相互不同的从属权利要求中记载某些措施的这一事实不表明这些措施的组合不能够有利地被使用。在权利要求中的任何参考标记不应解释为限制范围。

[0080] 参考符号列表

[0081] 10 功率半导体模块

[0082] 12 基板

[0083] 14 顶板

[0084] 16a 第一Si芯片

[0085] 16b 第二宽带隙材料芯片

[0086] 18a 第一底部电极

[0087] 18b 第二底部电极

[0088] 20a 第一顶部电极

[0089] 20b 第二顶部电极

[0090] 22a 第一金属预制件

- [0091] 22b 第二金属预制件

- [0092] 24a 第一压销

- [0093] 24b 第二压销

- [0094] 26a 第一弹簧元件

- [0095] 26b 第二弹簧元件

- [0096] 28a 第一半导体开关

- [0097] 28b 第二半导体开关

- [0098] 30a 第一栅极

- [0099] 30b 第二栅极

- [0100] 32a 第一栅电极

- [0101] 32b 第二栅电极

- [0102] 34a 第一栅极端子

- [0103] 34b 第二栅极端子。

图 1

图 2

图 3

图 4