【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成26年1月30日(2014.1.30)

【公開番号】特開2013-93448(P2013-93448A)

【公開日】平成25年5月16日(2013.5.16)

【年通号数】公開・登録公報2013-024

【出願番号】特願2011-234814(P2011-234814)

【国際特許分類】

H 01 L 21/822 (2006.01)

H 01 L 27/04 (2006.01)

H 01 L 21/8234 (2006.01)

H 01 L 27/06 (2006.01)

H 01 L 27/08 (2006.01)

【F I】

H 01 L 27/04 H

H 01 L 27/06 1 0 2 A

H 01 L 27/08 3 3 1 G

H 01 L 27/06 3 1 1 B

H 01 L 27/06 3 1 1 C

【手続補正書】

【提出日】平成25年12月6日(2013.12.6)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0046

【補正方法】変更

【補正の内容】

【0046】

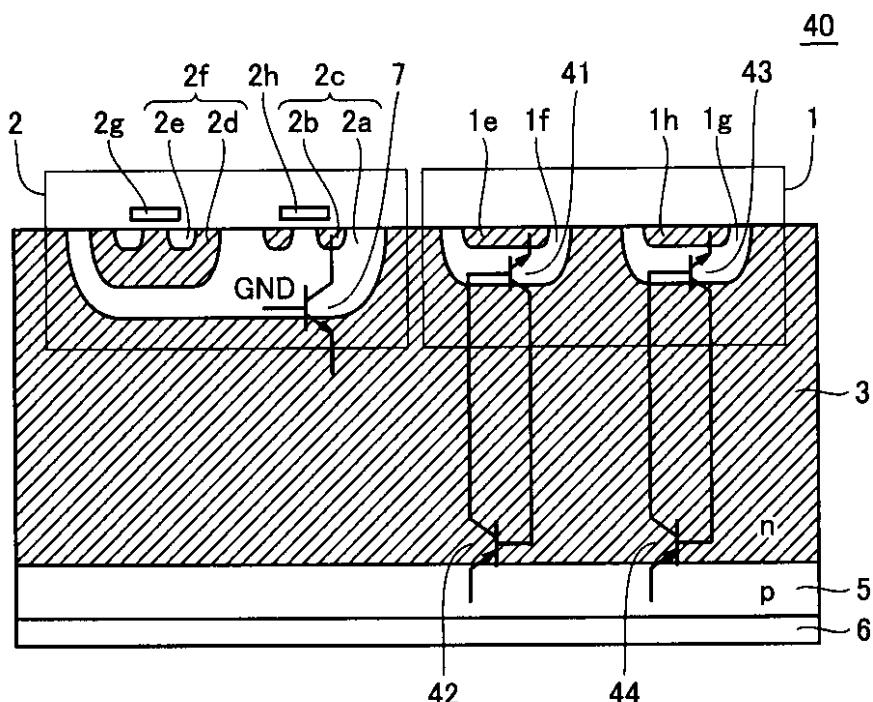

電力素子1には、p型の半導体層1\_fと、p型の半導体層1\_f内に形成したn型の半導体層1\_eとが形成してある。そのため、電力素子1には、n型の半導体層1\_eと、p型の半導体層1\_fと、n型の半導体基板3とで構成されるNPNトランジスタ4\_1が形成される。さらに、p型の半導体層1\_fと、n型の半導体基板3と、p型の半導体層5とで構成するPNPトランジスタ4\_2が半導体基板3に形成される。同様に、電力素子1には、p型の半導体層1\_g内に、n型の半導体層1\_hを形成してある。そのため、電力素子1には、n型の半導体層1\_hと、p型の半導体層1\_gと、n型の半導体基板3とで構成されるNPNトランジスタ4\_3が形成される。さらに、p型の半導体層1\_gと、n型の半導体基板3と、p型の半導体層5とで構成するPNPトランジスタ4\_4が半導体基板3に形成される。なお、NPNトランジスタ4\_1のコレクタ電極と、NPNトランジスタ4\_3のコレクタ電極とは、p型の半導体層5を介して電気的に接続している。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0048

【補正方法】変更

【補正の内容】

【0048】

図6には図示していないが、半導体装置4\_0には、半導体基板3および半導体層1\_fと接続する外部回路を備えている。外部回路を含めた半導体装置4\_0の等価回路を説明する。図7は、本発明の実施の形態4に係る半導体装置4\_0の回路構成を示す回路図である。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0049

【補正方法】変更

【補正の内容】

【0049】

図7に示す外部回路9は、電源9aと、電源9aに一端を接続する抵抗素子9bと、抵抗素子9bの他端にアノード電極を接続するダイオード9cと、ダイオード9cのカソード電極にアノード電極を接続し、カソード電極をGND接地するダイオード9dとを有している。また、抵抗素子9bの他端は、NPNトランジスタ41のベース電極（半導体層1f）と電気的に接続してある。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0052

【補正方法】変更

【補正の内容】

【0052】

半導体装置40は、半導体装置40に負電流が流れた場合、NPNトランジスタ41のベース電極（p型の半導体層1f）とn型の半導体基板3とで構成されるpn結合によって、半導体基板3の電位がNPNトランジスタ41のベース電極の電位（1.4V程度（常温））から0.7V程度（常温）に低下した電位を維持しようとする。そのため、半導体装置40は、p型の半導体層2aとn型の半導体基板3とが逆バイアス状態となり、半導体層2aから半導体基板3へ寄生電流が流れないため、寄生NPNトランジスタ7が作動しない。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0062

【補正方法】変更

【補正の内容】

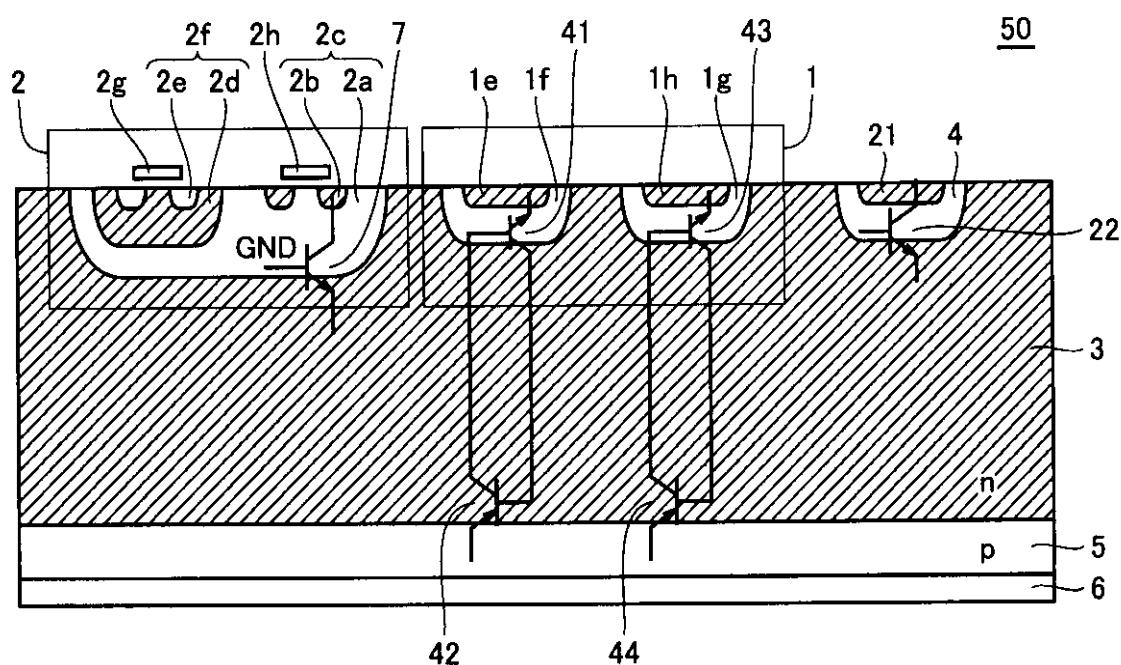

【0062】

図8には図示していないが、半導体装置50には、半導体基板3および半導体層1f, 4と接続する外部回路を備えている。外部回路を含めた半導体装置50の等価回路を説明する。図9は、本発明の実施の形態5に係る半導体装置50の回路構成を示す回路図である。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0063

【補正方法】変更

【補正の内容】

【0063】

図9に示す外部回路9は、電源9aと、電源9aに一端を接続する抵抗素子9bと、抵抗素子9bの他端にアノード電極を接続するダイオード9cと、ダイオード9cのカソード電極にアノード電極を接続し、カソード電極をGND接地するダイオード9dとを有している。また、抵抗素子9bの他端は、NPNトランジスタ41のベース電極（半導体層1f）と電気的に接続してある。さらに、抵抗素子9bの一端は、NPNトランジスタ22のコレクタ電極（半導体層21）と電気的に接続し、抵抗素子9bの他端は、NPNトランジスタ22のベース電極（半導体層4）と電気的に接続してある。

【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0070

【補正方法】変更

## 【補正の内容】

## 【0070】

抵抗素子 9 b の他端は、NPNトランジスタ 41 のベース電極（半導体層 1\_f）と電気的に接続してある。さらに、抵抗素子 9 b の一端は、NPNトランジスタ 22 のコレクタ電極（半導体層 2\_1）と電気的に接続し、抵抗素子 9 b の他端は、NPNトランジスタ 22 のベース電極（半導体層 4）と電気的に接続してある。

## 【手続補正8】

## 【補正対象書類名】図面

## 【補正対象項目名】図 6

## 【補正方法】変更

## 【補正の内容】

## 【図 6】

## 【手続補正9】

## 【補正対象書類名】図面

## 【補正対象項目名】図 8

## 【補正方法】変更

## 【補正の内容】

【図8】