(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4190798号

(P4190798)

(45) 発行日 平成20年12月3日(2008.12.3)

(24) 登録日 平成20年9月26日(2008.9.26)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/78 29/78

627G

H01L 29/786 (2006.01)

H01L 29/78

618D

H01L 21/20 (2006.01)

H01L 29/78

618Z

H01L 21/20

請求項の数 11 (全 11 頁)

(21) 出願番号

特願2002-132310 (P2002-132310)

(22) 出願日

平成14年5月8日(2002.5.8)

(65) 公開番号

特開2003-332346 (P2003-332346A)

(43) 公開日

平成15年11月21日(2003.11.21)

審査請求日

平成17年4月7日(2005.4.7)

(73) 特許権者 303018827

NEC液晶テクノロジー株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100079164

弁理士 高橋 勇

(72) 発明者 奥村 展

東京都港区芝五丁目7番1号 日本電気株式会社内

審査官 河本 充雄

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

薄膜部と厚膜部とを有する多結晶シリコン膜からなり、前記薄膜部が少なくともチャネル部として用いられ、

前記多結晶シリコン膜は、前記薄膜部が完全溶融するとともに前記厚膜部が完全溶融しないエネルギー密度のレーザアニールによって形成され、

前記薄膜部は、チャネル長方向が8μm以下であり、チャネル長方向に二列の結晶粒が形成され、かつ当該二列の結晶粒の間に微結晶化組織が形成されていない、

薄膜トランジスタ。

## 【請求項2】

前記薄膜部が完全溶融するエネルギー密度とは当該薄膜部の微結晶化しきい値以上のエネルギー密度であり、

前記厚膜部が完全溶融しないエネルギー密度とは当該厚膜部の微結晶化しきい値未満のエネルギー密度である、

請求項1記載の薄膜トランジスタ。

## 【請求項3】

前記薄膜部が完全溶融するエネルギー密度とは当該薄膜部の微結晶化しきい値以上かつアブレーションしきい値未満のエネルギー密度であり、

前記厚膜部が完全溶融しないエネルギー密度とは当該厚膜部の多結晶化しきい値以上かつ微結晶化しきい値未満のエネルギー密度である、

請求項 1 記載の薄膜トランジスタ。

【請求項 4】

前記チャネル部の他に L D D 領域とソース・ドレイン領域の一部とが、前記薄膜部に形成されている、

請求項 1 乃至 3 のいずれか一項に記載の薄膜トランジスタ。

【請求項 5】

前記二列の結晶粒の間の結晶粒界がチャネル長方向に対して垂直である、

請求項 1 乃至 4 のいずれか一項に記載の薄膜トランジスタ。

【請求項 6】

前記二列の結晶粒の一方にのみチャネル部が形成された、

請求項 1 乃至 5 のいずれか一項に記載の薄膜トランジスタ。

【請求項 7】

基板上にアモーファスシリコン膜の薄膜部及び厚膜部を形成する工程であって、当該薄膜部のチャネル長方向を  $8 \mu m$  以下にする工程と、

前記薄膜部が完全溶融するとともに前記厚膜部が完全溶融しないエネルギー密度で前記アモーファスシリコン膜をレーザアニールすることにより、当該薄膜部のチャネル長方向に二列の結晶粒を形成するとともに当該二列の結晶粒の間に微結晶化組織を形成しないように、当該薄膜部及び当該厚膜部を多結晶化する工程と、

前記薄膜部を少なくともチャネル部とする薄膜トランジスタを形成する工程と、

を備えた薄膜トランジスタの製造方法。

10

【請求項 8】

基板上にアモーファスシリコン膜の薄膜部及び厚膜部を形成する前記工程は、前記基板上にアモーファスシリコン膜を形成する工程と、このアモーファスシリコン膜の一部を途中までエッチングする工程とからなる、

請求項 7 記載の薄膜トランジスタの製造方法。

【請求項 9】

基板上にアモーファスシリコン膜の薄膜部及び厚膜部を形成する前記工程は、前記基板上に第一のアモーファスシリコン膜を形成する工程と、この第一のアモーファスシリコン膜の一部をエッチングする工程と、このエッチングされた第一のアモーファスシリコン膜を含む前記基板上に第二のアモーファスシリコン膜を形成する工程とからなる、

30

請求項 7 記載の薄膜トランジスタの製造方法。

【請求項 10】

前記薄膜部が完全溶融するエネルギー密度とは当該薄膜部の微結晶化しきい値以上のエネルギー密度であり、

前記厚膜部が完全溶融しないエネルギー密度とは当該厚膜部の微結晶化しきい値未満のエネルギー密度である、

請求項 7 乃至 9 のいずれか一項に記載の薄膜トランジスタの製造方法。

【請求項 11】

前記薄膜部が完全溶融するエネルギー密度とは当該薄膜部の微結晶化しきい値以上かつアブレーションしきい値未満のエネルギー密度であり、

40

前記厚膜部が完全溶融しないエネルギー密度とは当該厚膜部の多結晶化しきい値以上かつ微結晶化しきい値未満のエネルギー密度である、

請求項 7 乃至 9 のいずれか一項に記載の薄膜トランジスタの製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、アクティブマトリックス型ディスプレイなどに用いられる薄膜トランジスタ及びその製造方法に関する。以下、薄膜トランジスタを「TFT (thin film transistor)」、シリコンを「Si」という。

【0002】

50

### 【従来の技術】

近年、ガラス基板上に集積回路を形成する薄膜素子として、多結晶Si TFTの開発が盛んに行われている。多結晶Si薄膜の形成法としては、一旦アモーファスSi膜を形成した後にエキシマレーザ光を照射することにより、アモーファスSi膜を溶融及び再結晶化させて多結晶Si膜を得る、エキシマレーザ法が一般的である。エキシマレーザ法で使われるレーザアニール装置としては、照射口径が $300\text{ mm} \times 0.4\text{ mm}$ 程度のレーザ光を短軸方向に数十 $\mu\text{m}$ ピッチでスキャン照射する装置が市販されている。この装置を用いれば、サブ $\mu\text{m}$ オーダの結晶粒がランダムに配置された多結晶Si膜が形成可能であるため、移動度 $150\text{ cm}^2/\text{Vs}$ 程度のTFTを歩留まり良く量産可能となる。また、今後のTFTの高性能化には、結晶粒径の拡大と結晶粒の位置制御とが必要である。

10

### 【0003】

多結晶Si膜の大粒径化技術として、例えば特許第2689596号公報には、二層のアモーファスSi膜を利用して、薄膜部を大粒径化する技術が開示されている。しかし、この公報には、レーザ照射条件に基づく膜の溶融状態及び膜厚以外の膜構造に関しては、何ら記載も示唆も無い。また、結晶粒の位置制御に関する記載も示唆も無い。

### 【0004】

一方、エキシマレーザアニール法を改良し、TFTのチャネル長に匹敵する数 $\mu\text{m}$ もの結晶粒を、その発生位置を制御しながら形成することにより、擬似単結晶Si TFTの開発も進められている。例えば、MRS Bulletin 21巻(1996年)、3月号、39頁にImlaにより開示されているように、島状に形成したアモーファスSi薄膜に、幅 $5\text{ }\mu\text{m}$ の極めて微細な線状ビームを $0.75\text{ }\mu\text{m}$ ピッチで照射することにより、結晶粒界がほぼ平行に整列している一方向成長多結晶Si薄膜が形成可能となる。また、第61回応用物理学会学術講演予稿集(2000年)、No.2、759頁、5p-ZD-4及び5p-ZD-5に中田らにより開示されているように、位相シフトマスクを用い $\mu\text{m}$ オーダの強度周期を有するレーザ光を作成することにより、 $3\text{ }\mu\text{m}$ 程度に成長したSi結晶粒を位置制御して形成することが可能となる。これらの方により、TFTチャネル位置に均一な大粒径多結晶Si薄膜を、制御性良く形成できるようになる。

20

### 【0005】

#### 【発明が解決しようとする課題】

これらレーザ光の強度プロファイルを $\mu\text{m}$ オーダで制御する方法を用いる場合、光学系の分解能をサブ $\mu\text{m}$ オーダに向上させる必要がある。しかし、光学系のコストが増大するという問題、レーザ光の利用効率が低下するという問題、及び光学系の焦点深度が狭くなるという問題が生じる。光学系の焦点深度が基板のそり量やたわみ量より狭くなると、基板ステージに高さ調整機能を設ける必要が生じる。また、基板ステージ動作もサブ $\mu\text{m}$ オーダで制御することが必要となる。更に、位相シフトマスクを用いる場合では、マスクをアモーファスSi表面にほぼ密着させる必要があるため、レーザアニール中にアモーファスSi膜表面から遊離するSi原子がマスクを汚染するので、高価なマスクを頻繁に交換しなければならない。したがって、生産設備としてのレーザアニール装置が複雑になるので、値段が高価になるとともに、稼働率が低下するという問題が発生する。

30

### 【0006】

#### 【発明の目的】

そこで、本発明の目的は、高キャリア移動度及び低リーク電流等の性能を簡単に実現できるTFT及びその製造方法を提供することにある。

40

### 【0007】

#### 【課題を解決するための手段】

本発明に係るTFTは、薄膜部と厚膜部とを有する多結晶Si膜からなり、薄膜部が少なくともチャネル部として用いられるものである。そして、多結晶Si膜は、薄膜部が完全溶融するとともに厚膜部が完全溶融しないエネルギー密度のレーザアニールによって形成され、薄膜部は、チャネル長方向が $8\text{ }\mu\text{m}$ 以下であり、チャネル長方向に二列の結晶粒が形成され、かつ当該二列の結晶粒の間に微結晶化組織が形成されていない(請求項1)。

50

## 【0008】

ここで、完全溶融するエネルギー密度とは、微結晶化しきい値以上のエネルギー密度であることを意味する。アモーファスSi膜のレーザアニールによって形成される多結晶Si膜の結晶粒径は、レーザのエネルギー密度に依存する。そして、エネルギー密度が増加するに従い結晶粒径は増加するが、ある特定のエネルギー密度を越えると粒径が20nm以下と極めて微細になることが知られている（ただし、膜厚によっては、レーザ照射による溶融後に結晶化することなくアモーファス化する。）。このときのエネルギー密度を、微結晶化しきい値という。

## 【0009】

微結晶化は、アモーファスSi膜の溶融状態が非完全溶融から完全溶融へと変化することにより、再結晶化時の核発生機構が、基板／アモーファスSi膜界面を核発生サイトとした不均一核発生から、特異な核発生サイトの無い均一核発生へと変化することにより発生すると考えられている。この核発生機構の変化は、基板／アモーファスSi膜界面の到達温度、膜厚方向の温度分布、膜の冷却速度等に依存する。したがって、微結晶化しきい値は、アモーファスSi膜の膜厚、アモーファスSi膜の構造、アモーファスSi膜の光学定数、パルスレーザ光の波長及びパルス幅、などに依存して変化する。例えば、一旦レーザアニールした多結晶Si膜の微結晶化しきい値は、レーザ照射前のアモーファスSi膜よりも約14%大きな値を示す。また、更にエネルギー密度が増大すると、アブレーションにより膜剥れが発生する。

## 【0010】

薄膜部が完全溶融するとともに厚膜部が完全溶融しないエネルギー密度によるレーザアニールでは、厚膜部では微結晶化しきい値以下の温度になる。そのため、厚膜部では、基板／アモーファスSi膜界面が主たる核発生サイトになり、基板／アモーファスSi膜界面からアモーファスSi膜表面方向へと結晶が成長する。一方、薄膜部では、完全溶融していることにより、基板／アモーファスSi膜界面での核発生が抑制されているため、厚膜部で形成された結晶粒が種結晶となって、横方向（膜面方向）に成長した粗大結晶粒が得られる。したがって、この粗大結晶粒は一次元で位置制御されていると言える。

## 【0011】

ここで、エネルギー密度が高すぎて薄膜部だけでなく厚膜部も完全溶融してしまうと、薄膜部及び厚膜部の両方で微結晶化した組織が形成される。逆に、エネルギー密度が低過ぎて厚膜部の溶融が不十分であると、基板／アモーファスSi膜界面近傍にアモーファスSi膜領域が残存することになる。すると、種結晶は薄膜部／厚膜部境界よりも薄膜部側に形成されてしまうため、粗大結晶粒の粒径は小さくなってしまう。更に、エネルギー密度が低過ぎて薄膜部が完全溶融しない場合は、基板／アモーファスSi膜界面で核発生が起こるため、厚膜部とともに薄膜部においてもランダムに発生した不均質な1μmに満たない結晶粒が形成される。

## 【0012】

したがって、照射エネルギー密度は、薄膜部で微結晶化しきい値以上かつアブレーションしきい値未満であり、厚膜部で膜厚方向にアモーファスSi膜が全て多結晶化する値以上かつ微結晶化しきい値未満である、となる条件を選定する。

## 【0013】

請求項2記載のTFTは、請求項1記載のTFTにおいて、薄膜部が完全溶融するエネルギー密度とは薄膜部の微結晶化しきい値以上のエネルギー密度であり、厚膜部が完全溶融しないエネルギー密度とは厚膜部の微結晶化しきい値未満のエネルギー密度である、としたものである。請求項3記載のTFTは、請求項1記載のTFTにおいて、薄膜部が完全溶融するエネルギー密度とは薄膜部の微結晶化しきい値以上かつアブレーションしきい値未満のエネルギー密度であり、厚膜部が完全溶融しないエネルギー密度とは厚膜部の多結晶化しきい値以上かつ微結晶化しきい値未満のエネルギー密度である、としたものである。これらの請求項は、エネルギー密度をより具体化したものである。

## 【0014】

10

20

30

40

50

請求項 4 記載の TFT は、請求項 1 乃至 3 のいずれかに記載の TFT において、チャネル部の他に LDD (lightly doped drain) 領域とソース・ドレイン領域の一部とが、薄膜部に形成されている、というものである。LDD 領域及びソース・ドレイン領域の一部も、粗大結晶粒を有する薄膜部に形成されているので、LDD 領域での低リーク電流化、ソース・ドレイン領域での低抵抗化が図れる。

【 0 0 1 5 】

また、本発明に係る TFT は、薄膜部のチャネル長方向に二列の結晶粒が形成されている。ソース・ドレイン領域に薄膜部と厚膜部との界面がある場合、これらの界面から結晶粒が成長するので、薄膜部ではチャネル長方向に二列の結晶粒が形成される。すなわち、薄膜部ではチャネル長方向と交差する結晶粒界が概ね一面となるので、キャリア移動度が向上する。請求項 5 記載の TFT は、請求項 1 乃至 4 のいずれかに記載の TFT において、二列の結晶粒の間の結晶粒界がチャネル長方向に対して垂直である、というものである。

【 0 0 1 6 】

請求項 6 記載の TFT は、請求項 5 記載の TFT において、二列の結晶粒の一方にのみチャネル部が形成された、というものである。この場合は、チャネル長方向と交差する結晶粒界が概ね無くなるので、キャリア移動度がより向上する。

【 0 0 1 7 】

また、本発明に係る TFT は、薄膜部のチャネル長方向が  $8 \mu m$  以下である。粗大結晶粒の粒径は  $4 \mu m$  までが比較的容易に形成できる。薄膜部のチャネル長方向が  $8 \mu m$  以下とすると、薄膜部のチャネル長方向に二列の結晶粒を容易に形成できる。

【 0 0 1 8 】

本発明に係る TFT の製造方法は、本発明に係る TFT を製造する方法である（請求項 7 乃至 11）。

【 0 0 1 9 】

換言すると、本発明は次の構成を採り得る。

(1) 薄膜部及び厚膜部を有する多結晶 Si 膜を活性層に用いた TFT において、チャネル部と LDD 領域とソース・ドレイン領域の一部とが薄膜部に形成されている TFT。

(2) 薄膜部が二列の結晶粒で構成されている上記(1)。

(3) 薄膜部及び厚膜部を有する多結晶 Si 膜を活性層に用いた TFT を作製するにあたり、薄膜部は完全溶融しかつ厚膜部は完全溶融しないエネルギー密度でエキシマレーザ二光子する、TFT の製造方法。

(4) 薄膜部の領域幅が  $8 \mu m$  以下である上記(3)。

【 0 0 2 0 】

アモーファス Si 薄膜にエキシマレーザ光を照射する、多結晶 Si 薄膜の製造方法において、アモーファス Si 薄膜は二種類の膜厚を有し、エキシマレーザ光の照射強度が、当該アモーファス Si 薄膜の薄膜部を完全に溶融する強度であり、かつ当該アモーファス Si 薄膜の厚膜部を完全には溶融しないこと、を特徴とする。また、チャネル領域と LDD 領域とを当該薄膜部に有する TFT を提供する。

【 0 0 2 1 】

【発明の実施の形態】

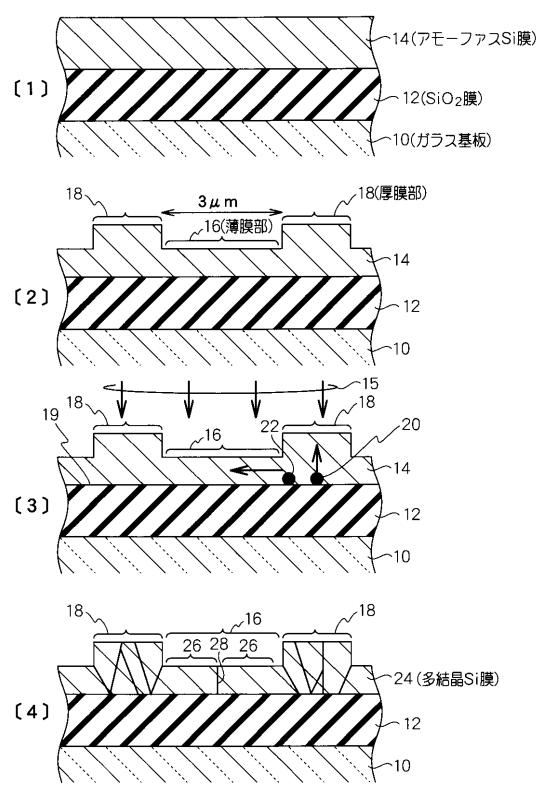

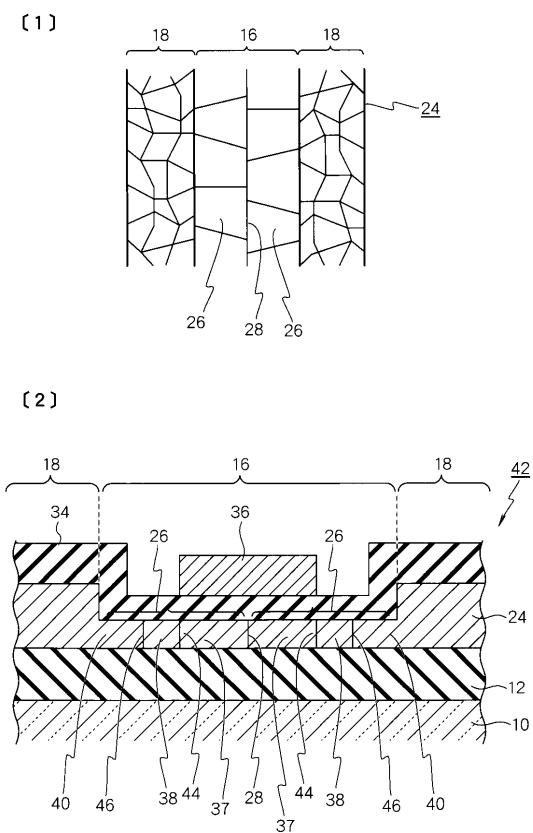

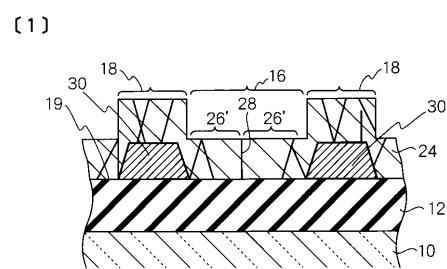

図 1 は、本発明に係る TFT の第一実施形態を示す断面図であり、図 1 [1] ~ 図 1 [4] の順に製造工程が進行する。図 2 [1] は図 1 [4] の平面図であり、図 2 [2] は図 1 [4] の次の製造工程を示す断面図である。図 3 [1] は第一比較例を示す断面図であり、図 3 [2] は第二比較例を示す平面図である。以下、これらの図面に基づき説明する。

【 0 0 2 2 】

まず、PECVD (plasma enhanced CVD) 法を用いて、ガラス基板 10 上に下地用の SiO<sub>2</sub> 膜 12 をとアモーファス Si 膜 14 とを連続して成膜した（図 1 [1]）。膜厚は、両者とも  $100 \text{ nm}$  とした。続いて、ガラス基板 10 等に対して  $500$  かつ  $5$  分の脱

10

20

30

40

50

水素処理を行い、通常のフォトリソグラフィ法及びドライエッティング法を用いて、アモーファスSi膜14に薄膜部16及び厚膜部18を形成した(図1[2])。薄膜部16は、膜厚が40nm、領域幅が3μmとした。厚膜部18の膜厚は、変わらずに100nmである。続いて、アモーファスSi膜14表面にエキシマレーザ光15を照射した(図1[3])。このレーザアニール装置は、200mm×0.4mm光学系を有する一般的な量産品を用いた。その照射条件として、エネルギー密度は薄膜部16が完全溶融する430mJ/cm<sup>2</sup>とし、スキャンピッチは40μmとした。

#### 【0023】

ここで、完全溶融するエネルギー密度とは、微結晶化しきい値以上のエネルギー密度であることを意味する。例えば特開平11-274095号公報に開示されているように、アモーファスSi膜14のレーザアニールにおいて、形成される多結晶Si膜24の結晶粒径は、レーザエネルギー密度に依存する。エネルギー密度が増加するに従い粒径は増加するが、ある特定のエネルギー密度を越えると粒径が20nm以下と極めて微細になることが知られている(膜厚によっては、レーザ照射による溶融後に結晶化することなくアモーファス化する。)。このときのエネルギー密度を、微結晶化しきい値という。

#### 【0024】

微結晶化は、アモーファスSi膜14の溶融状態が非完全溶融から完全溶融へと変化することにより、再結晶化時の核発生機構が、基板/Si界面19を核発生サイトとした不均一核発生から、特異な核発生サイトの無い均一核発生へと変化することにより発生すると考えられている。この核発生機構の変化は、基板/Si界面19の到達温度、アモーファスSi膜14の膜厚方向の温度分布、アモーファスSi膜14の冷却速度等に依存する。したがって、微結晶化しきい値は、アモーファスSi膜14の膜厚、アモーファスSi膜14の構造、アモーファスSi膜14の光学定数、パルスレーザ光の波長及びパルス幅、などに依存して変化する。例えば、一旦レーザアニールした多結晶Si膜24の微結晶化しきい値は、レーザ照射前のアモーファスSi膜14より約14%大きな値を示す。また、更にエネルギー密度が増大すると、アブレーションにより膜剥れが発生する。

#### 【0025】

膜厚40nmのアモーファスSi膜の微結晶化しきい値は、410mJ/cm<sup>2</sup>であった。そのため、膜厚が同じアモーファスSi膜の場合、430mJ/cm<sup>2</sup>で照射すると微結晶化組織になるはずである。しかしながら、本実施形態において430mJ/cm<sup>2</sup>で照射後の薄膜部18には、薄膜部18の幅の1/2程度の長さである1.5μm程度の粒径の粗大結晶粒26が形成された(図1[4])。この粗大結晶粒26の生成は、薄膜部16の両脇に厚膜部18を有していることに起因する。

#### 【0026】

厚膜部18においては、430mJ/cm<sup>2</sup>は微結晶化しきい値(約570mJ/cm<sup>2</sup>)以下の値であるため、基板/Si界面19が主たる核発生サイト20になり、基板/Si界面19からアモーファスSi膜14表面方向へと結晶が成長する。一方、薄膜部16では、完全溶融していることにより、基板/Si界面19での核発生が抑制されるため、厚膜部18で形成された結晶粒が種結晶22となって、横方向(膜面方向)に成長した粗大結晶粒26が得られる。したがって、この粗大結晶粒26は一次元で位置制御されていると言える。図2[1]の平面図にも示すように、薄膜部16の両端から粗大結晶粒26が成長するため、薄膜部16を二分するかの如くに結晶粒界28が形成される。

#### 【0027】

ここで、厚膜部18も完全溶融してしまう過度のエネルギー密度では、薄膜部16及び厚膜部18の両方とも微結晶化した組織が形成される。一方、図3[1]に示すように、エネルギー密度が低いために、厚膜部18において溶融が不十分である場合は、基板/Si界面19近傍にアモーファスSi領域30が残存することになる。この場合、種結晶は薄膜部16と厚膜部18との境界よりも薄膜部16側に形成されてしまうため、粗大結晶粒26の粒径は小さくなってしまう。更に、薄膜部16が完全溶融しない場合では、基板/Si界面19で核発生が起こるため、厚膜部18とともに薄膜部16においてもランダムに

10

20

30

40

50

発生した不均質な  $1 \mu m$  に満たない結晶粒が形成される。

【0028】

したがって、照射エネルギー密度は、薄膜部 16 で微結晶化しきい値以上かつアブレーションしきい値未満であり、厚膜部 18 で膜厚方向に膜が全て結晶化する値以上かつ微結晶化しきい値未満である、となる条件を選定する。本実施形態では、上記の値はそれぞれ、 $410 \text{ mJ/cm}^2$ 、 $600 \text{ mJ/cm}^2$  以上、 $250 \text{ mJ/cm}^2$ 、 $570 \text{ mJ/cm}^2$  であることから、 $410 \sim 570 \text{ mJ/cm}^2$  が、位置制御された均質な粗大結晶粒 26 からなる多結晶 Si 膜 24 を得る照射条件となる。

【0029】

粗大結晶粒 26 の粒径は、照射エネルギー密度や薄膜部 16 と厚膜部 18 との膜厚差にも依存するが、主として基板温度等に依存しているので基板温度が室温のとき、約  $2 \mu m$  が限度であった。また、領域幅が  $5 \mu m$  の薄膜部 16' としたとき、図 3 [2] に示すように、薄膜部 16' の両脇部には  $2 \mu m$  ずつの粗大結晶粒 26 が形成されたが、中央部  $1 \mu m$  の領域には微結晶化組織 32 が形成された。更に、基板温度を 400 としたとき、粗大結晶粒 26 の粒径は約  $4 \mu m$  まで増加した。

【0030】

以上の一次元に位置制御された粗大結晶粒 26 からなる多結晶 Si 膜 24 を用いて、図 2 [2] に示すようにゲート絶縁膜 34、ゲート電極 36、ゲート電極 36 の両側に LDD 領域 38、ソース・ドレイン領域 40 を形成した。ここでゲート電極幅 (TFT チャネル長) は  $1.5 \mu m$ 、LDD 長は  $0.5 \mu m$  とした。その後、図示しないが、層間絶縁膜及びソース・ドレイン電極配線を形成して、TFT 42 が完成する。つまり、TFT 42 は、薄膜部 16 と厚膜部 18 とを有する多結晶 Si 膜 24 からなり、薄膜部 16 が少なくともチャネル部 37 として用いられる。そして、多結晶 Si 膜は、薄膜部 16 が完全溶融するとともに厚膜部 18 が完全溶融しないエネルギー密度のレーザアニールによって形成されている。

【0031】

このように作製された TFT 42 は、キャリアの移動を著しく妨げるチャネル長方向に対して概略垂直な結晶粒界 28 が一面と制御されているため、高移動度であり、素子間のバラツキも小さい。また、チャネル / LDD 境界 44 と LDD / ソース・ドレイン境界 46 とがチャネル長方向において同一の粗大結晶粒 26 内に形成されているため、リーク電流も、単結晶 Si 基板上の TFT 並みに極めて低い値を示す。

【0032】

また、ソース・ドレイン領域 40 には厚膜部 18 を含む方が、シート抵抗の低減、不純物導入時のプロファイル制御性、コンタクトホール形成時のエッティング制御性等に有利である。LDD 領域 38 が無いセルフアライント TFT の場合、リーク電流は高くなるが、それでもチャネル / ソース・ドレイン端がチャネル長方向において同一の結晶粒内に形成されているため、通常のセルフアライント TFT に比べれば低い値を示す。

【0033】

なおアモーファス Si 膜厚差を形成する場合、特許第 2689596 号公報に見られるように、アモーファス Si 膜を 2 回成膜することもできるが、このとき両アモーファス Si 膜の界面に自然酸化膜が残存してしまう。このような膜内に自然酸化膜が残存した厚膜部を TFT のソース・ドレイン領域に利用すると、ソース・ドレイン抵抗が増大するので、望ましいものではない。

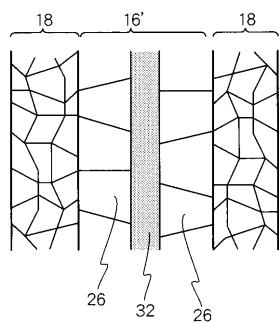

【0034】

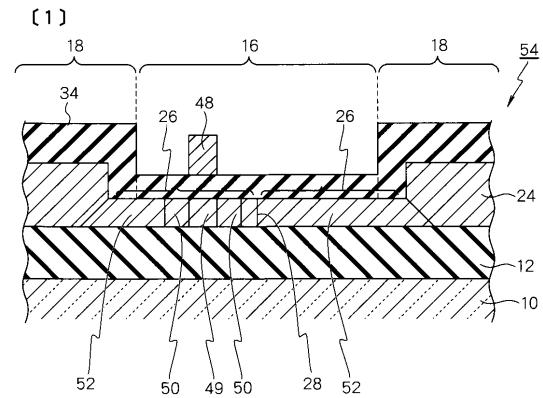

図 4 [1] は、本発明に係る TFT の第二実施形態を示す断面図である。以下、この図面に基づき説明する。ただし、図 2 [2] と同じ部分は同じ符号を付すことにより説明を省略する。

【0035】

第一実施形態と同様にして、400 でレーザアニールを行い、 $3 \mu m$  の 2 列に配列した粗大結晶粒 26 からなる多結晶 Si 膜 24 を形成した。この多結晶 Si 膜 24 を利用し、

10

20

30

40

50

ゲート絶縁膜34、ゲート電極48、ゲート電極48の両側にLDD領域50、ソース・ドレイン領域52を形成した。これにより、チャネル長0.8μm、LDD長0.5μmの両側LDD構造のTFT54を作製した。ここでチャネル部49は、一方の粗大結晶粒26内に形成することにより、薄膜部16を二分する結晶粒界28を含まないようにしてある。結晶粒界28は、ソース・ドレイン領域52にあることが望ましいが、ゲート長やLDD長及びフォトリソグラフィ目合わせ精度によっては、ソース側又はドレイン側のLDD領域50のどちらかに含まれてしまう可能性がある。低リーケ電流の観点からは、ソース側のLDD領域50に結晶粒界28が有ることが望ましい。

#### 【0036】

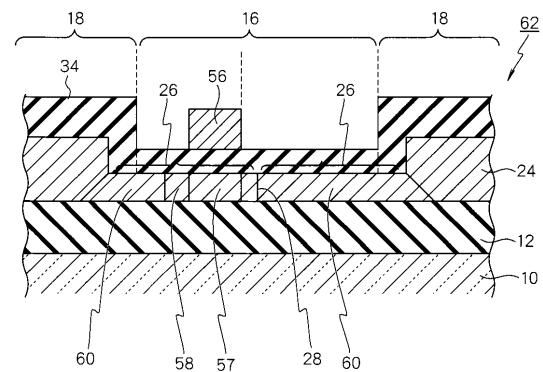

図4[2]は、本発明に係るTFTの第三実施形態を示す断面図である。以下、この図面に基づき説明する。ただし、図2[2]と同じ部分は同じ符号を付すことにより説明を省略する。

#### 【0037】

第一実施形態と同様にして、1.5μmの2列に配列した粗大結晶粒26からなる多結晶Si膜24を形成した。この多結晶Si膜24を利用し、ゲート絶縁膜34、ゲート電極56、ゲート電極56の片側にLDD領域58、ソース・ドレイン領域60を形成した。これにより、チャネル長0.8μm、LDD長0.2μmの片側LDD構造のTFT62を作製した。ここでチャネル部57は、一方の粗大結晶粒26内に形成されている。薄膜部16を二分する結晶粒界28は、チャネル部57及びLDD領域58には位置しない。

#### 【0038】

なお、本発明は、言うまでもなく、上記実施形態に限定されるものではない。例えば、基板上に第一のアモーファスシリコン膜を形成し、第一のアモーファスシリコン膜の一部をエッチングし、エッチングされた第一のアモーファスシリコン膜を含む基板上に第二のアモーファスシリコン膜を形成することにより、薄膜部と厚膜部とを形成してもよい。

#### 【0039】

#### 【発明の効果】

本発明によれば、薄膜部が完全溶融するとともに厚膜部が完全溶融しないエネルギー密度のレーザアニールによって多結晶Si膜を形成することにより、薄膜部と厚膜部との界面から成長した粗大結晶粒によってチャネル部が構成されるので、一般的なレーザアニール装置を用いて高キャリア移動度及び低リーケ電流等の性能を簡単に実現できる。

#### 【0040】

チャネル部の他にLDD領域とソース・ドレイン領域の一部とを、薄膜部に形成することにより、LDD領域及びソース・ドレイン領域の一部も粗大結晶粒に形成されるので、LDD領域での低リーケ電流化、ソース・ドレイン領域での低抵抗化が図れる。

#### 【0041】

チャネル長方向の二列の結晶粒で薄膜部を構成することにより、薄膜部ではチャネル長方向と交差する結晶粒界が概ね一面となるので、キャリア移動度がより向上する。

#### 【0042】

二列の結晶粒の一方にのみチャネル部が形成することにより、チャネル長方向と交差する結晶粒界が概ね無くなるので、キャリア移動度がより向上する。

#### 【0043】

薄膜部のチャネル長方向を8μm以下とすることにより、4μm以下の粒径の粗大結晶粒は比較的容易に形成できるので、薄膜部のチャネル長方向に二列の結晶粒を容易に形成できる。

#### 【図面の簡単な説明】

【図1】本発明に係るTFTの第一実施形態を示す断面図であり、図1[1]～図1[4]の順に製造工程が進行する。

【図2】図2[1]は図1[4]の平面図である。図2[2]は図1[4]の次の製造工程を示す断面図である。

【図3】図3[1]は第一比較例を示す断面図である。図3[2]は第二比較例を示す平

10

20

30

40

50

面図である。

【図4】図4[1]は本発明に係るTFTの第二実施形態を示す断面図である。図4[2]は本発明に係るTFTの第三実施形態を示す断面図である。

【符号の説明】

- 16 薄膜部

- 18 厚膜部

- 24 多結晶Si膜

- 26 粗大結晶粒

- 37, 49, 57 チャネル部

- 42, 54, 62 TFT

10

【図1】

【図2】

【図3】

[2]

【図4】

[2]

---

フロントページの続き

(56)参考文献 特開平10-321870(JP,A)

特開平02-283073(JP,A)

特開平09-036041(JP,A)

特開平10-055979(JP,A)

特開2003-282586(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 21/20

H01L 29/786