(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4962993号

(P4962993)

(45) 発行日 平成24年6月27日(2012.6.27)

(24) 登録日 平成24年4月6日(2012.4.6)

(51) Int.Cl.

G06F 21/22 (2006.01)

G06F 11/22 (2006.01)

F 1

G06F 21/22 114D

G06F 11/22 340A

請求項の数 10 (全 16 頁)

(21) 出願番号 特願2009-519507 (P2009-519507)

(86) (22) 出願日 平成19年7月11日 (2007.7.11)

(65) 公表番号 特表2009-544069 (P2009-544069A)

(43) 公表日 平成21年12月10日 (2009.12.10)

(86) 國際出願番号 PCT/US2007/015775

(87) 國際公開番号 WO2008/008367

(87) 國際公開日 平成20年1月17日 (2008.1.17)

審査請求日 平成22年7月9日 (2010.7.9)

(31) 優先権主張番号 60/831,022

(32) 優先日 平成18年7月14日 (2006.7.14)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/820,287

(32) 優先日 平成18年7月25日 (2006.7.25)

(33) 優先権主張国 米国(US)

(73) 特許権者 502188642

マーベル ワールド トレード リミテッド

バルバドス国 ビービー14027, セントマイケル、ブリトンズ ヒル、ガンサイ

トロード、エル ホライズン

(74) 代理人 100104156

弁理士 龍華 明裕

(74) 代理人 100118005

弁理士 飯山 和俊

(74) 代理人 100143502

弁理士 明石 英也

(74) 代理人 100138128

弁理士 東山 忠義

最終頁に続く

(54) 【発明の名称】システムオンチップ (S o C) 試験インターフェースセキュリティ

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサと、

イネーブルされている場合にだけ、前記プロセッサと通信する試験インターフェースと、

前記プロセッサ用のファームウェアを記憶する第1メモリと、前記プロセッサ用の、前記プロセッサがブートした場合に前記第1メモリ内の予め定められた位置から前記ファームウェアの一部を前記プロセッサに読み込ませるブートコードを記憶する第2メモリとレジスタ、前記予め定められた値を記憶する第3メモリ、および前記レジスタと前記第3メモリとの間の比較に基づいて、前記試験インターフェースをイネーブルするロジックを有する特定用途向け回路と

を備え、

前記試験インターフェースは、前記ファームウェアの前記一部が予め定められた値を有する場合にだけイネーブルされ、

前記ブートコードは、前記プロセッサに、前記ファームウェアの前記一部を前記レジスタに書き込ませる装置。

## 【請求項 2】

前記試験インターフェースは、Joint Test Action Group (JTAG) インタフェースを有する

請求項1に記載の装置。

## 【請求項 3】

前記プロセッサは、前記ファームウェアの前記一部が前記予め定められた値を有するか否かを決定し、

前記プロセッサは、前記ファームウェアの前記一部が前記予め定められた値を有する場合に、前記試験インターフェースをイネーブルする請求項 1 または 2 に記載の装置。

## 【請求項 4】

前記試験インターフェースは、イネーブルされている場合にだけ、前記特定用途向け回路と通信する請求項 1 から 3 の何れか 1 項に記載の装置。

## 【請求項 5】

前記第 1 メモリ内の前記予め定められた位置に記憶された前記ファームウェアの前記一部はスクランブルされており、10

前記装置は、

前記プロセッサが前記第 1 メモリ内の前記予め定められた位置から前記ファームウェアの前記一部を読み込んだ場合に、前記ファームウェアの前記一部をデスクランブルするデスクランブル

をさらに備える請求項 1 から 4 の何れか 1 項に記載の装置。

## 【請求項 6】

前記デスクランブルは、

Advanced Encryption Standard (AES) プロセス、20

Data Encryption Standard (DES) プロセス、および

共有鍵プロセス

の少なくとも 1 つに従って実行される請求項 5 に記載の装置。

## 【請求項 7】

前記第 1 メモリは、

ファームウェアメモリ

を有する請求項 1 から 6 の何れか 1 項に記載の装置。

## 【請求項 8】

前記第 2 メモリは、

リードオンリーメモリ

を有する請求項 1 から 7 の何れか 1 項に記載の装置。30

## 【請求項 9】

請求項 1 から 8 の何れか 1 項に記載の装置を有する集積回路。

## 【請求項 10】

請求項 9 に記載の集積回路を備えるディスクプレーヤ。

## 【発明の詳細な説明】

## 【関連出願】

## 【0001】

本出願は、2007年1月18日に出願された米国特許出願番号第 11/654841 号、2006年7月14日に出願された米国仮特許出願番号第 60/831022 号、および、2006年7月25日に出願された米国仮特許出願番号第 60/820287 号の利益を主張し、その開示は、全てがここに参照として組み込まれる。40

## 【技術分野】

## 【0002】

本発明は、概して集積回路に関する。特に、本発明はシステムオンチップ (SOC) 試験インターフェースセキュリティに関する。

## 【背景技術】

## 【0003】

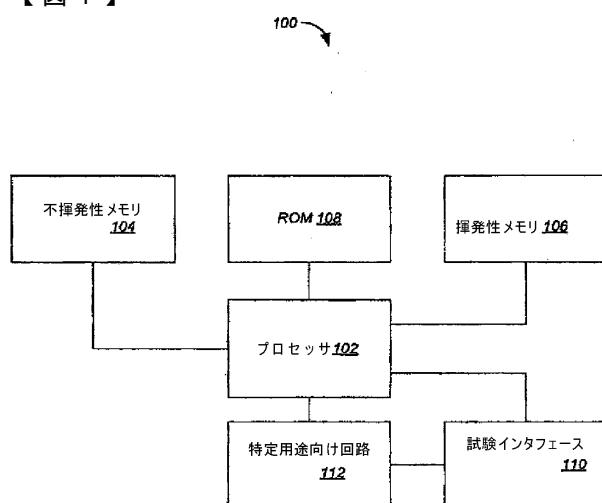

集積回路技術の最近の進歩は、いわゆるシステムオンチップ (SOC) 集積回路を普及させた。そこでは、メモリ、および、単一の集積回路チップ上の特定用途向け回路のような他のハードウェアブロックとともに、プロセッサが組み込まれる。図 1 は、プロセッサ

102、不揮発性メモリ104、揮発性メモリ106、リードオンリーメモリ(ROM)108、試験インターフェース110、および、特定用途向け回路112を備える従来技術としてのS0C100を示す。

#### 【0004】

S0C100は、Joint Test Action Group (JTAG)インターフェースのような、S0C100をデバッギングおよび試験するのに用いる1つの試験インターフェース110を通常備える。試験インターフェース110は、一般にプロセッサ102および特定用途向け回路112に接続される。試験インターフェース110は、S0C100内の他の回路にも接続されることができる。例えば、S0C100は、不揮発性メモリ104に記憶されたファームウェアのプロセッサ102による実行をトレースするために用いることができる。10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、試験インターフェース110は、開発中には有用な一方で、ひとたび実地で実用されると、アタッカがS0C100に入り込む隙をも提供する。例えば、アタッカは、S0C100が内部に設けられたシステムのセキュリティを破るべくファームウェアをコピーまたは変更するために試験インターフェース110を使用することができる。S0C100は、いくつかのリソースへの不正アクセスを防ぐための秘密鍵のようなシークレットを用いることもできる。例えば、デジタルビデオディスク(DVD)プレーヤ/バーナ内に設けられたS0C100は、コピー保護されたDVDのコピーをユーザが作成することを防ぐための秘密鍵を用いることができる。アタッカは、試験インターフェース110を用いて秘密鍵を取得して、コピー保護されたDVDのコピーをDVDプレーヤ/バーナを用いて作成することができる。20

#### 【課題を解決するための手段】

#### 【0006】

概して、一側面において、この発明は、プロセッサと、イネーブルされている場合にだけ、プロセッサと通信する試験インターフェースと、プロセッサ用のファームウェアを記憶する第1メモリと、プロセッサ用のブートコードを記憶する第2メモリとを備え、プロセッサがブートした場合に、ブートコードはプロセッサに、第1メモリ内の予め定められた位置からファームウェアの一部を読み込ませ、試験インターフェースは、ファームウェアの一部が予め定められた値を有する場合にイネーブルされる装置、を特徴とする。30

#### 【0007】

いくつかの実施態様において、試験インターフェースは、Joint Test Action Group (JTAG)インターフェースを有する。いくつかの実施態様において、プロセッサはファームウェアの一部が予め定められた値を有するか否かを決定し、ファームウェアの一部が予め定められた値を有する場合に、プロセッサは試験インターフェースをイネーブルする。いくつかの実施態様は、レジスタと、予め定められた値を記憶する第3メモリと、レジスタと第3メモリとの間の比較に基づいて、試験インターフェースをイネーブルするロジックとを有する特定用途向け回路を備え、ブートコードは、プロセッサに、ファームウェアの一部をレジスタに書き込ませる。いくつかの実施態様において、試験インターフェースは、イネーブルされている場合にだけ、特定用途向け回路と通信する。いくつかの実施態様において、第1メモリ内の予め定められた位置に記憶されたファームウェアの一部はスクランブルされており、装置は、プロセッサが第1メモリ内の予め定められた位置からファームウェアの一部を読み込んだ場合に、ファームウェアの一部をデスクランブルするデスクランブルをさらに備える。いくつかの実施態様において、デスクランブルは、Advanced Encryption Standard (AES)プロセス、Data Encryption Standard (DES)プロセス、および共有鍵プロセスの少なくとも1つに従って実行される。いくつかの実施態様において、第1メモリは、ファームウェアメモリを有する。いくつかの実施態様において、第2メモリ4050

リは、リードオンリーメモリを有する。いくつかの実施態様は、上記装置を有する集積回路を備える。いくつかの実施態様は、上記集積回路を備えるディスクプレーヤを備える。

#### 【0008】

概して、一側面において、この発明は、プロセッシング手段と、イネーブルされている場合にだけプロセッシング手段と通信する試験インターフェース手段と、プロセッシング手段用のファームウェアを記憶する第1メモリ手段と、プロセッシング手段用のブートコードを記憶する第2メモリ手段とを備え、プロセッシング手段がブートした場合に、ブートコードは、第1メモリ内の予め定められた位置からファームウェアの一部をプロセッシング手段に読み込ませ、試験インターフェース手段は、ファームウェアの一部が予め定められた値を有する場合にだけイネーブルされる装置、を特徴とする。

10

#### 【0009】

いくつかの実施態様において、試験インターフェースは、Joint Test Action Group (JTAG) を有する。いくつかの実施態様において、プロセッシング手段は、ファームウェアの一部が予め定められた値を有するか否かを決定して、プロセッシング手段は、ファームウェアの一部が予め定められた値を有する場合に、試験インターフェース手段をイネーブルする。いくつかの実施態様は、データを記憶する第3メモリ手段と、予め定められた値を記憶する第4メモリ手段と、第3および第4メモリ手段の間の比較に基づいて、試験インターフェースをイネーブルするロジック手段とを備え、ブートコードは、プロセッシング手段に、ファームウェアの一部を第3メモリ手段に書き込ませる。いくつかの実施態様において、試験インターフェース手段は、試験インターフェースがイネーブルされている場合にだけ、ロジック手段と通信する。いくつかの実施態様において、第1メモリ手段内の予め定められた位置に記憶されたファームウェアの一部はスクランブルされており、装置は、プロセッシング手段が第1メモリ手段内の予め定められた位置からファームウェアの一部を読み込んだ場合に、ファームウェアの一部をデスクランブルするデスクランブル手段をさらに備える。いくつかの実施態様において、デスクランブルは、Advanced Encryption Standard (AES) プロセス、Data Encryption Standard (DES) プロセス、および共有鍵プロセスの少なくとも1つに従って実行される。いくつかの実施態様は、上記装置を有する集積回路を備える。いくつかの実施態様は、上記集積回路を備えるディスクプレーヤを備える。

20

#### 【0010】

概して、一側面において、この発明は、プロセッサ、試験インターフェース、プロセッサ用のファームウェアを記憶する第1メモリ、および、プロセッサ用のブートコードを記憶する第2メモリを有する装置をオペレートする方法であって、ブートコードに従って、プロセッサがブートした場合に第1メモリ内の予め定められた位置からファームウェアの一部を読み込む段階と、ファームウェアの一部が予め定められた値を有するか否かを決定する段階と、ファームウェアの一部が予め定められた値を有する場合にだけ、試験インターフェースをイネーブルする段階とを備え、試験インターフェースは、イネーブルされている場合にだけプロセッサと通信する方法、を特徴とする。

30

#### 【0011】

いくつかの実施態様において、装置は、レジスタ、および、予め定められた値を記憶する第3メモリを有し、方法は、ブートコードに従って、ファームウェアの一部をレジスタに書き込む段階と、レジスタと第3メモリとの間の比較に基づいて、試験インターフェースをイネーブルする段階とをさらに備える。いくつかの実施態様において、装置は、レジスタおよび第3メモリを有する特定用途向け回路をさらに有し、記試験インターフェースは、イネーブルされている場合にだけ、特定用途向け回路と通信する。いくつかの実施態様において、第1メモリ内の予め定められた位置に記憶されたファームウェアの一部はスクランブルされており、方法は、第1メモリ内の予め定められた位置からファームウェアの一部を読み込んだ場合に、ファームウェアの一部をデスクランブルする段階をさらに備える。いくつかの実施態様において、デスクランブルする段階は、Advanced Enc

40

50

ryption Standard (AES) プロセス、Data Encryption Standard (DES) プロセス、および共有鍵プロセスの少なくとも 1 つに従って実行される。

#### 【0012】

概して、一側面において、この発明は、プロセッサ、試験インターフェース、プロセッサ用のファームウェアを記憶する第 1 メモリ、および、プロセッサ用のブートコードを記憶する第 2 メモリを有する装置をオペレートするためのプロセッサ上で実行可能なコンピュータプログラムであって、ブートコードに従って、プロセッサがブートした場合に第 1 メモリ内の予め定められた位置からファームウェアの一部を読み込むための命令と、ファームウェアの一部が予め定められた値を有するか否かを決定するための命令と、ファームウェアの一部が予め定められた値を有する場合にだけ、試験インターフェースをイネーブルするための命令とを備え、試験インターフェースは、イネーブルされている場合にだけプロセッサと通信するコンピュータプログラム、を特徴とする。いくつかの実施態様において、装置は、レジスタ、および、予め定められた値を記憶する第 3 メモリを有しており、コンピュータプログラムは、ブートコードに従って、ファームウェアの一部をレジスタに書き込むための命令と、レジスタと第 3 メモリとの間の比較に基づいて、試験インターフェースをイネーブルするための命令とを備える。いくつかの実施態様において、装置は、レジスタおよび第 3 メモリを有する特定用途向け回路をさらに有し、試験インターフェースは、イネーブルされている場合にだけ、特定用途向け回路と通信する。いくつかの実施態様において、第 1 メモリ内の予め定められた位置に記憶されたファームウェアの一部はスクランブルされており、コンピュータプログラムは、第 1 メモリ内の予め定められた位置からファームウェアの一部を読み込んだ場合に、ファームウェアの一部をデスクランブルするための命令をさらに備える。いくつかの実施態様において、デスクランブルは、Advanced Encryption Standard (AES) プロセス、Data Encryption Standard (DES) プロセス、および共有鍵プロセスの少なくとも 1 つに従って実行される。

#### 【0013】

1 以上の実施の詳細が、添付の図および以下の説明に記載される。他の特徴は、その説明および図から、そして請求項から明らかである。

#### 【図面の簡単な説明】

#### 【0014】

【図 1】従来技術のシステムオンアチップ (SoC) を示す図である。

【図 2】この発明のいくつかの実施形態において、プロセッサが認証コードをチェックする SoC を示す図である。

【図 3】この発明のいくつかの実施形態において、図 3 の SoC のためのプロセスを示す図である。

【図 4】この発明のいくつかの実施形態において、特定用途向け回路が認証コードをチェックする SoC を示す図である。

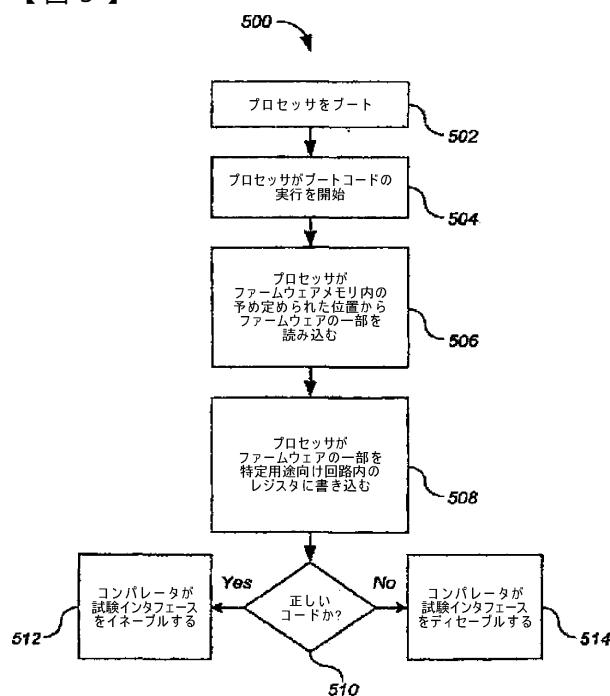

【図 5】この発明のいくつかの実施形態において、図 5 の SoC のためのプロセスを示す図である。

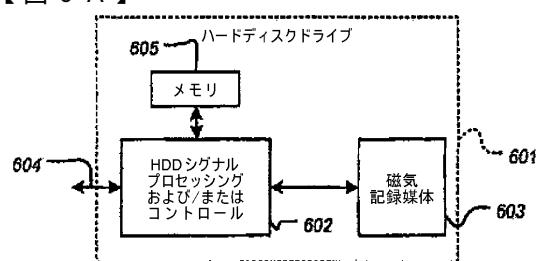

【図 6 A】この発明の様々な典型的な実装を示す図である。

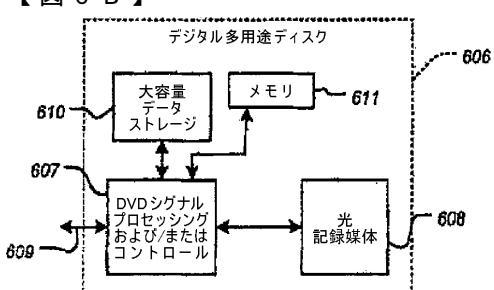

【図 6 B】この発明の様々な典型的な実装を示す図である。

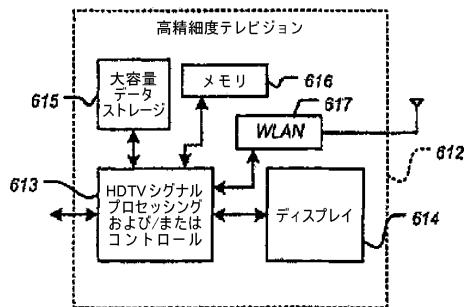

【図 6 C】この発明の様々な典型的な実装を示す図である。

【図 6 D】この発明の様々な典型的な実装を示す図である。

【図 6 E】この発明の様々な典型的な実装を示す図である。

【図 6 F】この発明の様々な典型的な実装を示す図である。

【図 6 G】この発明の様々な典型的な実装を示す図である。

#### 【発明を実施するための形態】

#### 【0015】

本明細書で用いられる各参照番号の桁は、参照番号が最初に現れる図の番号を示す。

10

20

30

40

50

この発明の実施形態は、複数のシステムオンチップ（S o C）集積回路用の複数の試験インターフェースに対するセキュリティを提供する。S o Cは、試験インターフェース、1つのプロセッサ、プロセッサ用のファームウェアを記憶する1つのファームウェアメモリ、および、プロセッサ用のブートコードを記憶する1つのリードオンリーメモリを有する。試験インターフェースは、試験インターフェースがイネーブルされている場合にだけプロセッサと通信する。試験インターフェースは、Joint Test Action Group（JTAG）インターフェースとして実装されてよい。プロセッサがブートした場合に、ブートコードは、プロセッサに、ファームウェアメモリ内の予め定められた位置からファームウェアの一部を読み込ませる。試験インターフェースは、プロセッサに読み込まれたファームウェアの一部が予め定められた認証コードを含む場合にだけ、イネーブルされる。

10

#### 【 0 0 1 6 】

この発明の実施形態に従って実装された複数のS o Cにおいて、認証コードは、S o Cの開発フェーズの間においてファームウェアメモリ内に記憶されることができる。それにより、S o Cの試験およびデバッグのために試験インターフェースがイネーブルにされる。その後、製造のためにファームウェアから認証コードが削除されることができ、それにより試験インターフェースがディセーブルされる。

#### 【 0 0 1 7 】

いくつかの実施形態において、プロセッサは、ファームウェアの一部が認証コードを含むか否かを決定して、ファームウェアの一部が認証コードを含む場合に、試験インターフェースをイネーブルする。他の実施形態においては、ファームウェアの一部が認証コードを含むか否かを、特定用途向け回路が決定する。特定用途向け回路は、例えばデジタルビデオディスク（DVD）プレーヤ／バーナなどをコントロールする、デバイスコントローラおよび類似のものであってよい。特定用途向け回路は、1つのレジスタ、認証コードを記憶する1つのメモリ、および1つのコンパレータを有する。ブートコードは、プロセッサに、ファームウェアの一部をレジスタに書き込ませる。コンパレータは、レジスタと異なるメモリとの間の比較に基づき、試験インターフェースをイネーブルする。

20

#### 【 0 0 1 8 】

特定用途向け回路が認証コードをチェックする実施形態においては、S o Cの製造者は認証コードを知る必要がなく、このため、製造するS o Cのための認証コードを保守セキュアにする責務から解放される。これらの実施形態において、顧客（例えば、S o Cを含む電子デバイスの製造者）は、認証コードを含んでいない複数のS o Cを購入することができ、その後、試験およびデバッグするために試験インターフェースをイネーブルすべく、認証コードを複数のS o Cに入力することができる。例えば、特定用途向け回路内のメモリは、1つのワンタイムプログラマブルメモリとして実装されてよい。顧客は、メモリに認証コードを焼き、認証コードをファームウェアに記録もする。顧客が複数のS o Cを出荷する場合に、顧客は認証コードをファームウェアから単に削除し、それにより試験インターフェースをディセーブルする。

30

#### 【 0 0 1 9 】

いくつかの実施形態において、ファームウェアメモリに記憶されたファームウェアのいくつかまたは全てが、1つのスクランブリングプロセスに従ってスクランブルされる。これらの実施形態は、プロセッサがファームウェアメモリからファームウェアを読み込んだ場合に1つのデスクランブリングプロセスに従ってファームウェアをデスクランブルする、1つのデスクランブラーを含む。スクランブリングおよびデスクランブリングプロセスは、Advanced Encryption Standard（AES）プロセス、Data Encryption Standard（DES）プロセス、共有鍵プロセス、および類似のものを含むことができる。これらの実施形態において、アタッカが試験インターフェースを通じてどうにかしてS o Cにアクセスすることができたとしても、アタッカはファームウェアをデスクランブルするという問題にさらに直面するだろう。

40

#### 【 0 0 2 0 】

50

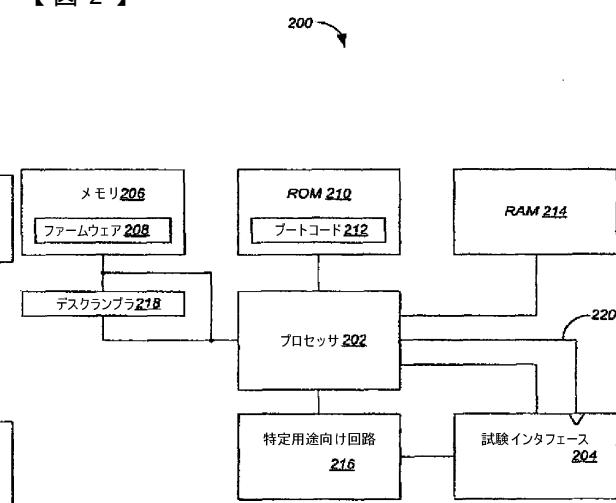

図2は、この発明の実施形態において、S o C 2 0 0 内のプロセッサ2 0 2 が認証コードをチェックするS o C 2 0 0 を示す。S o C 2 0 0 は、プロセッサ2 0 2 と、試験インタフェース2 0 4 がイネーブルされている場合にだけプロセッサ2 0 2 と通信する試験インタフェース2 0 4 と、プロセッサ2 0 2 用のファームウェア2 0 8 を記憶するファームウェアメモリ2 0 6 と、プロセッサ2 0 2 用のブートコード2 1 2 を記憶するリードオンリメモリ(ROM)2 1 0 とを有する。以下に詳細に説明されるように、試験インタフェース2 0 4 がイネーブルされている場合に、試験インタフェース2 0 4 は、プロセッサ2 0 2 および特定用途向け回路2 1 6 に接続され、また、S o C 2 0 0 内の他の複数の回路にも接続されてよい。試験インタフェース2 0 4 は、Joint Test Action Group (JTAG) インタフェースまたは類似のものとして実装されてよい。ファームウェアメモリ2 0 6 は、不揮発性メモリまたは類似のものとして実装されてよい。 10

#### 【0021】

S o C 2 0 0 は概して、1つのランダムアクセスメモリ(RAM)2 1 4 および1つの特定用途向け回路2 1 6 を有してもよい。例えば、S o C 2 0 0 がDVDプレーヤのようなディスクプレーヤをコントロールすることを目的とする場合、特定用途向け回路2 1 6 は1つのディスクコントローラおよび1つの読み込みチャネルを含むことができる。当然に、他の実装では、他の種類の複数の特定用途向け回路を含むことができる。

#### 【0022】

いくつかの実施形態において、例えば上述したように、ファームウェア2 0 8 はスクランブルがかけられており、S o C 2 0 0 は、ファームウェア2 0 8 がファームウェアメモリ2 0 6 から読み込まれた場合にファームウェア2 0 8 の全てまたは一部をデスクランブルする1つのデスクランブル2 1 8 を含む。説明される複数の実施形態においてS o C 2 0 0 の複数の要素がある構成で表されるが、他の実施形態では他の構成をとることができることが、本明細書で提供された開示および教示に基づいて当業者に明らかであろう。例えば、S o C 2 0 0 の複数の要素は、ハードウェア、ソフトウェア、またはそれらのコンビネーションで実装することができる。 20

#### 【0023】

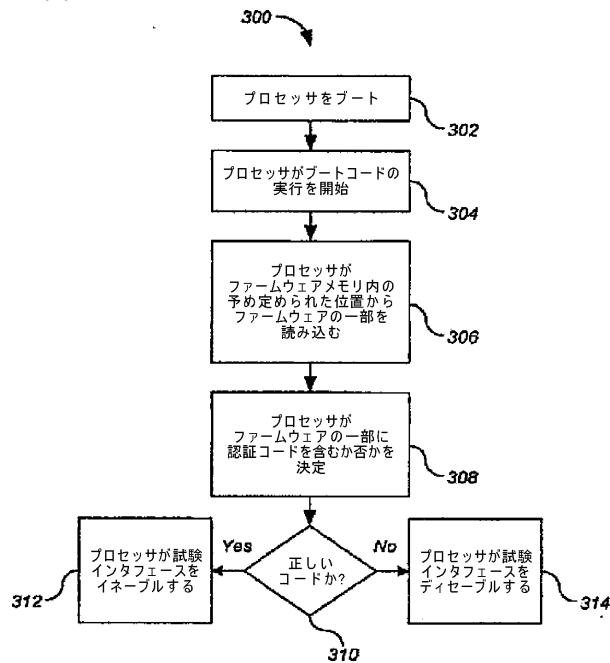

図3は、この発明の実施形態に係る、図3のS o C 2 0 0 のプロセスを示す。説明される複数の実施形態においてプロセス3 0 0 の複数の要素がある構成で表されるが、他の実施形態では他の構成をとることができることが、本明細書で提供された開示および教示に基づいて当業者に明らかであろう。 30

#### 【0024】

関連技術分野でよく知られているように、例えばS o C 2 0 0 への電力を切断して投入したり、プロセッサ2 0 2 にリセット信号を加えたり、同様のことをすることで、プロセッサ2 0 2 がブートされる(ステップ3 0 2)。ブートされたとき、プロセッサ2 0 2 は、ROM2 1 0 に記憶されているブートコード2 1 2 の実行を開始する(ステップ3 0 4)。ブートコード2 1 2 は、プロセッサ2 0 2 に、ファームウェアメモリ2 0 6 内の予め定められた位置からファームウェア2 0 8 の一部を読み込ませ(ステップ3 0 6)、ファームウェア2 0 8 の一部が適正な認証コードを含むか否かを決定させる(ステップ3 0 8)。例えば、認証コードはROM2 1 0 に記憶されることができ、プロセッサ2 0 2 は、その認証コードを、ファームウェアメモリ2 0 6 内の予め定められた位置から読み込まれたファームウェア2 0 8 の一部と比較する。 40

#### 【0025】

ファームウェア2 0 8 が適正な認証コードを含む場合(ステップ3 1 0)には、プロセッサ2 0 2 は、例えばイネーブル信号2 2 0 をアサートすることにより、試験インタフェース2 0 4 をイネーブルする(ステップ3 1 2)。そうでない場合には、プロセッサ2 0 2 は、例えばイネーブル信号2 2 0 を無効にすることにより、試験インタフェース2 0 4 をディセーブルする(ステップ3 1 4)。イネーブルされた場合、試験インタフェース2 0 4 は、試験デバイスのような外部デバイスと、プロセッサ2 0 2 との間の通信、いくつかの実施形態では特定用途向け回路2 1 6 のようなS o C 2 0 0 内の他の複数の回路との 50

通信を、許可する。

【0026】

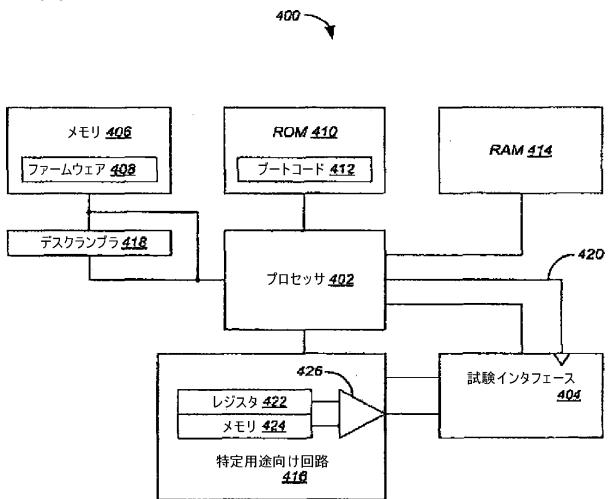

図4は、この発明の実施形態に従って、S o C 4 0 0 内の特定用途向け回路4 1 6が認証コードをチェックするS o C 4 0 0を示す。S o C 4 0 0は、プロセッサ4 0 2と、試験インタフェース4 0 4がイネーブルされている場合にだけプロセッサ4 0 2と通信する試験インタフェース4 0 4と、プロセッサ4 0 2用のファームウェア4 0 8を記憶するファームウェアメモリ4 0 6と、プロセッサ用のブートコード4 1 2を記憶するリードオンリメモリ(ROM)4 1 0とを有する。試験インタフェース4 0 4は、以下に説明するよう、試験インタフェース4 0 4がイネーブルされた場合に、プロセッサ4 0 2および特定用途向け回路4 1 6と接続されてよく、S o C 4 0 0内の他の複数の回路とも接続されてよい。試験インタフェース4 0 4は、Joint Test Action Group (JTAG)インタフェースまたは類似のものとして実装されてよい。ファームウェアメモリ4 0 6は、不揮発性メモリまたは類似のものとして実装されてよい。S o C 4 0 0は概して、1つのランダムアクセスメモリ(RAM)4 1 4を有してもよい。

【0027】

S o C 4 0 0は、特定用途向け回路4 1 6も有する。例えば、S o C 4 0 0がDVDプレーヤーのようなディスクプレーヤーをコントロールすることを目的とする場合、特定用途向け回路4 1 6は1つのディスクコントローラおよび1つの読み込みチャネルを含むことができる。当然に、他の実装では、他の種類の複数の特定用途向け回路を含むことができる。特定用途向け回路4 1 6は、レジスタ4 2 2、メモリ4 2 4、およびコンパレータ4 2 6を有する。メモリ4 2 4は、1つのワンタイムプログラマブルメモリとして実装されてよい。

【0028】

いくつかの実施形態において、例えば上述したように、ファームウェア4 0 8はスクランブルがかけられており、S o C 4 0 0は、ファームウェア4 0 8がファームウェアメモリ4 0 6から読み込まれた場合にファームウェア4 0 8の全てまたは一部をデスクランブルする1つのデスクランブル4 1 8を含む。説明される複数の実施形態においてS o C 4 0 0の複数の要素がある構成で表されるが、他の実施形態では他の構成をとることができることが、本明細書で提供された開示および教示に基づいて当業者に明らかであろう。例えば、S o C 4 0 0の複数の要素は、ハードウェア、ソフトウェア、またはそれらのコンビネーションで実装することができる。

【0029】

図5は、この発明の実施形態において、図5のS o C 4 0 0のための処理を示す。説明される複数の実施形態においてS o C 5 0 0の複数の要素がある構成で表されるが、他の実施形態では他の構成をとることができることが、本明細書で提供された開示および教示に基づいて当業者に明らかであろう。

【0030】

関連技術分野でよく知られているように、例えばS o C 4 0 0への電力を切断して投入したり、プロセッサ4 0 2にリセット信号を加えたり、同様のことをすることで、プロセッサ4 0 2がブートされる(ステップ5 0 2)。ブートされたとき、プロセッサ4 0 2は、ROM4 1 0に記憶されているブートコード4 1 2の実行を開始する(ステップ5 0 4)。ブートコード4 1 2は、プロセッサ4 0 2に、ファームウェアメモリ4 0 6内の予め定められた位置からファームウェア4 0 8の一部を読み込ませ(ステップ5 0 6)、ファームウェア4 0 8のその一部を特定用途向け回路4 1 6内のレジスタ4 2 2に書き込ませる(ステップ5 0 8)。

【0031】

これらの実施形態において、認証コードはメモリ4 2 4に記憶される。コンパレータ4 2 6は、レジスタ4 2 2とメモリ4 2 4との間の比較に基づき、試験インタフェース4 0 4をイネーブルする。具体的には、メモリ4 2 4が適正な認証コードを格納している場合(ステップ5 1 0)には、コンパレータ4 2 6は、例えばイネーブル信号4 2 0をアサー

トすることにより、試験インターフェース 404 をイネーブルする（ステップ 512）。そうでない場合には、コンパレータ 426 は、例えイネーブル信号 420 を無効にすることにより、試験インターフェース 404 をディセーブルする（ステップ 514）。イネーブルされた場合、試験インターフェース 404 は、試験デバイスのような外部デバイスと、ブロセッサ 402 との間の通信、いくつかの実施形態では特定用途向け回路 416 のような S o C 400 内の他の複数の回路との通信を、許可する。

【0032】

図 6 A - 6 G は、この発明の様々な典型的な実装を示す図である。図 6 A を参照すると、この発明は、ハードディスクドライブ 601 に実装することができる。この発明は、図 6 A において 602 で一般に識別されるシグナルプロセッシングおよび / またはコントロール回路のいずれかまたは双方を実装することができる。いくつかの実施態様において、HDD 601 内のシグナルプロセッシングおよび / またはコントロール回路 602 および / または他の複数の回路（図示せず）は、データ処理、コーディングおよび / または暗号化、演算、および / または、磁気記録媒体 603 に出力される、および / または磁気記録媒体 603 から受信されたデータのフォーマットを実行することができる。

10

【0033】

HDD 601 は、ホストデバイス（図示せず）（例えば、コンピュータ、携帯情報端末のようなモバイルコンピューティングデバイス、セルラフォン、メディアまたはMP3 プレーヤなど）、および / または他のデバイスと、1 以上の有線または無線の通信リンク 604 を介して通信することができる。HDD 601 は、メモリ 605（例えば、ランダムアクセスメモリ（RAM）、フラッシュメモリのような低レイテンシの不揮発性メモリ、リードオンリメモリ（ROM）、および / または他の適切な電子データストレージ）に接続されることができる。

20

【0034】

図 6 B を参照すると、この発明は、デジタル多目的ディスク（DVD）ドライブ 606 に実装することができる。この発明は、図 6 B において 607 で一般に識別されるシグナルプロセッシングおよび / またはコントロール回路のいずれかまたは双方、および / または DVD ドライブ 606 の大容量データストレージを実装することができる。DVD 606 内のシグナルプロセッシングおよび / またはコントロール回路 607 または他の複数の回路（図示せず）は、データ処理、コーディングおよび / または暗号化、演算、および / または、光記録媒体 608 に出力される、および / または光記録媒体 608 から受信されたデータのフォーマットを実行することができる。いくつかの実施形態において、シグナルプロセッシングおよび / またはコントロール回路 607、および / または DVD 606 の複数の回路（図示せず）は、エンコーディングおよび / またはデコーディングおよび / または DVD ドライブに関連する他のいかなる信号処理機能のような他の機能を実行することができる。

30

【0035】

DVD ドライブ 606 は、出力デバイス（図示せず）（例えばコンピュータ、テレビジョンまたは他のデバイス）と、1 以上の有線または無線の通信リンク 609 を介して通信することができる。DVD 606 は、不揮発式でデータを記憶する大容量データストレージ 610 と通信することができる。大容量データストレージ 610 は、ハードディスクドライブ（HDD）を含むことができる。HDD は、図 6 A で示された構成を有することができる。HDD は、およそ 1.8 インチより小さい径の 1 以上のプラッタを持つ小型 HDD であつてよい。DVD 606 は、メモリ 611（例えば、RAM、ROM、フラッシュメモリのような低レイテンシの不揮発性メモリ、および / または他の適切な電子データストレージ）に接続されることがある。

40

【0036】

図 6 C を参照すると、この発明は、高精細テレビジョン（HDTV）612 に実装されることがある。この発明は、図 6 C において 613 で一般に識別されるシグナルプロセッシングおよび / またはコントロール回路のいずれかまたは双方、HDTV 612 の WL

50

A N インタフェースおよび／または大容量データストレージを実装することができる。H D T V 6 1 2 は、有線または無線フォーマットでH D T V 入力信号を受け取って、ディスプレイ6 1 4 用のH D T V 出力信号を生成する。いくつかの実施形態において、H D T V 6 1 2 のシグナルプロセッシング回路および／またはコントロール回路6 1 3、および／または他の複数の回路（図示せず）は、データ処理、コーディングおよび／または暗号化、演算、データのフォーマット、および／または、要求される他のタイプのいかなるH D T V 处理を実行することができる。

【 0 0 3 7 】

H D T V 6 1 2 は、光および／または磁気記録媒体のように、不揮発式でデータを記憶する大容量データストレージ6 1 5 と通信することができる。少なくとも1つのH D D は図6 A で示した構成を有してよく、少なくとも1つのD V D は図6 B で示した構成を有してよい。H D D は、およそ1.8インチより小さい径の1以上のプラッタを持つ小型H D D であってよい。H D T V 6 1 2 は、メモリ6 1 6（例えば、R A M、R O M、フラッシュメモリのような低レイテンシの不揮発性メモリ、および／または他の適切な電子データストレージ）に接続されることができる。H D T V 6 1 2 は、W L A N ネットワークインターフェース6 1 7 を通じたW L A N 接続をサポートすることもできる。

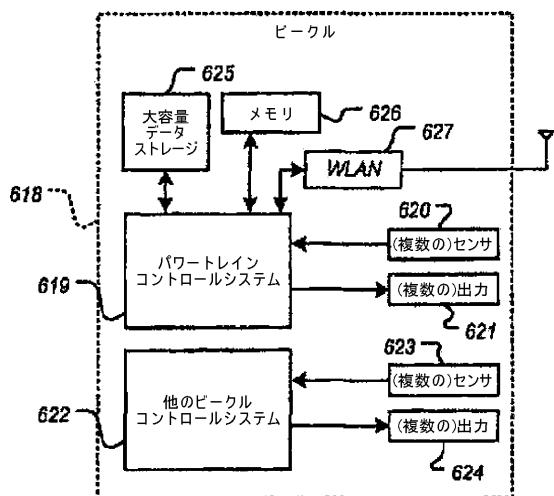

【 0 0 3 8 】

図6 D を参照すると、この発明は、ビーカル6 1 8 のコントロールシステム、W L A N インタフェース、および／またはビーカルコントロールシステムの大容量データストレージを実装する。いくつかの実施形態において、この発明は、パワートレインコントロールシステム6 1 9 を実装する。パワートレインコントロールシステム6 1 9 は、1以上のセンサ（例えば、温度センサ、圧力センサ、回転センサ、気流センサ、および／または他のいかなる適切なセンサ）から入力を受け取り、および／または、1以上の出力コントロール信号（例えば、エンジンオペレーティングパラメータ、トランスマッショナリオペレーティングパラメータ、および／または他のコントロール信号）を生成する。

【 0 0 3 9 】

この発明は、ビーカル6 1 8 の他のコントロールシステム6 2 2 にもまた実装されてよい。コントロールシステム6 2 2 は、同様に入力センサ6 2 3 から信号を受け取ることができ、コントロール信号を1以上の出力デバイス6 2 4 に出力できてよい。いくつかの実施形態において、コントロールシステム6 2 2 は、アンチロックブレーキングシステム（A B S）、ナビゲーションシステム、テレマチクスシステム、ビーカルテレマチクスシステム、レーンデパーチャシステム、アダプティブクルーズコントロールシステム、ビーカルエンターテイメントシステム（ステレオ、D V D、コンパクトディスクなど）の一部であってよい。さらに他の実施形態が考えられる。

【 0 0 4 0 】

パワートレインコントロールシステム6 1 9 は、不揮発式でデータを記憶する大容量データストレージ6 2 5 と通信することができる。大容量データストレージ6 2 5 は、光／磁気ストレージデバイス（例えばハードディスクドライブ（H D D）および／またはD V D ドライブ）を含むことができる。少なくとも1つのH D D は図6 A で示された構成を有することができ、少なくとも1つのD V D は図6 B で示された構成を有することができる。H D D は、およそ1.8インチより小さい径の1以上のプラッタを持つ小型H D D であってよい。パワートレインコントロールシステム6 1 9 は、メモリ6 2 6（例えば、R A M、R O M、フラッシュメモリのような低レイテンシの不揮発性メモリ、および／または他の適切な電子データストレージ）に接続されることができる。パワートレインコントロールシステム6 1 9 は、W L A N ネットワークインターフェース6 2 7 を通じたW L A N 接続をサポートすることもできる。コントロールシステム6 2 2 は、大容量データストレージ、メモリ、および／またはW L A N インタフェース（いずれも図示せず）を含むこともできる。

【 0 0 4 1 】

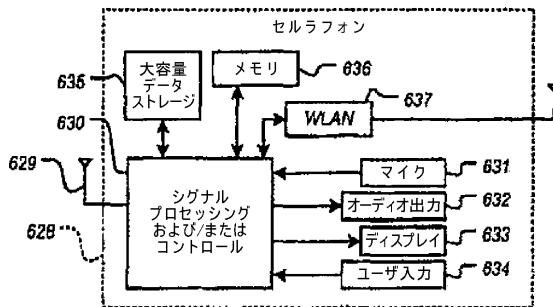

図6 E を参照すると、この発明は、セルラアンテナ6 2 9 を含むセルラフォン6 2 8 に

10

20

30

40

50

実装される。この発明は、図 6 Eにおいて 630 で一般に識別されるシグナルプロセッシングおよび / またはコントロール回路のいずれかまたは双方、セルラフォン 628 の WLAN インタフェースおよび / または大容量データストレージを実装することができる。いくつかの実施態様において、セルラフォン 628 は、マイクロホン 631、オーディオ出力 632 ( 例えばスピーカおよび / またはオーディオ出力ジャック ) 、ディスプレイ 633 および / または入力デバイス 634 ( 例えばキーパッド、ポインティングデバイス、ボイスアクチュエーション、および / または他の入力デバイス ) を含むことができる。セルラフォン 628 内のシグナルプロセッシングおよび / またはコントロール回路 630 、および / または他の複数の回路 ( 図示せず ) は、データ処理、コーディングおよび / または暗号化、演算、および / または、他のセルラフォン機能を実行することができる。 10

#### 【 0042 】

セルラフォン 628 は、光および / または磁気記録媒体 ( 例えば、ハードディスクドライブ ( HDD ) および / または DVD ドライブ ) のように、不揮発式でデータを記憶する大容量データストレージ 635 と通信することができる。少なくとも 1 つの HDD は図 6 A で示した構成を有してよく、少なくとも 1 つの DVD は図 6 B で示した構成を有してよい。 HDD は、およそ 1.8 インチより小さい径の 1 以上のプラッタを持つ小型 HDD であってよい。セルラフォン 628 は、メモリ 636 ( 例えば、RAM 、 ROM 、フラッシュメモリのような低レイテンシの不揮発性メモリ、および / または他の適切な電子データストレージ ) に接続されることができる。セルラフォン 628 は、 WLAN ネットワークインターフェース 637 を通じた WLAN 接続をサポートすることもできる。 20

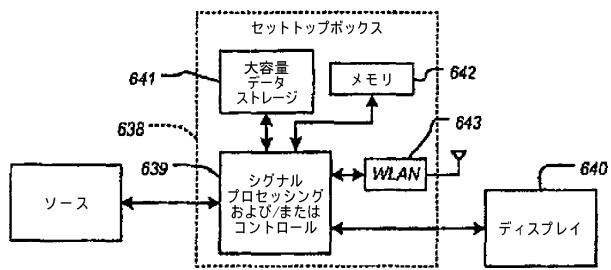

#### 【 0043 】

図 6 F を参照すると、この発明は、セットトップボックス 638 に実装されることがある。この発明は、図 6 F において 639 で一般に識別されるシグナルプロセッシングおよび / またはコントロール回路のいずれかまたは双方、セットトップボックス 638 の WLAN インタフェースおよび / または大容量データストレージを実装することができる。セットトップボックス 638 は、プロードバンドソースのようなソースから信号を受け取って、テレビジョンおよび / またはモニタのようなディスプレイ 640 、および / または他のビデオおよび / またはオーディオ出力デバイスに適した、スタンダードおよび / またはハイディフィニション・オーディオ / ビデオ信号を出力する。セットトップボックス 638 のシグナルプロセッシングおよび / またはコントロール回路 639 および / または他の複数の回路 ( 図示せず ) は、データ処理、コーディングおよび / または暗号化、演算、および / または、他のいかなるセットトップボックス機能を実行することができる。 30

#### 【 0044 】

セットトップボックス 638 は、不揮発式でデータを記憶する大容量データストレージ 643 と通信することができる。大容量データストレージ 643 は、光および / または磁気ストレージデバイス ( 例えば、ハードディスクドライブ ( HDD ) および / または DVD ドライブ ) を含むことができる。少なくとも 1 つの HDD は図 6 A で示した構成を有してよく、少なくとも 1 つの DVD は図 6 B で示した構成を有してよい。 HDD は、およそ 1.8 インチより小さい径の 1 以上のプラッタを持つ小型 HDD であってよい。セットトップボックス 638 は、メモリ 642 ( 例えば、RAM 、 ROM 、フラッシュメモリのような低レイテンシの不揮発性メモリ、および / または他の適切な電子データストレージ ) に接続されることができる。セットトップボックス 638 は、 WLAN ネットワークインターフェース 643 を通じた WLAN 接続をサポートすることもできる。 40

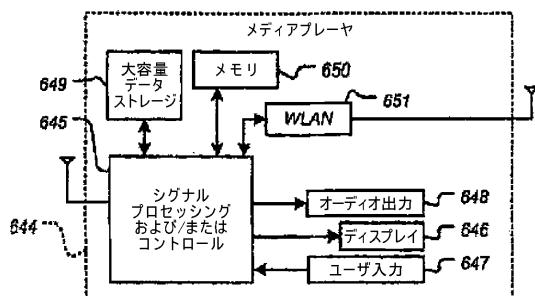

#### 【 0045 】

図 6 G を参照すると、この発明は、メディアプレーヤ 644 に実装されることがある。この発明は、図 6 G において 645 で一般に識別されるシグナルプロセッシングおよび / またはコントロール回路のいずれかまたは双方、メディアプレーヤ 644 の WLAN インタフェースおよび / または大容量データストレージを実装することができる。いくつかの実施形態において、メディアプレーヤ 644 はディスプレイ 646 、および / または、キーパッド、タッチパッドなどのようなユーザ入力 647 を有してよい。いくつかの実施 50

形態において、メディアプレーヤ 644 は、メニュー、ドロップダウンメニュー、アイコン、および／またはディスプレイ 646 および／またはユーザ入力 647 を通じたポイントアンドクリックインターフェースを典型的に利用するグラフィカルユーザインタフェース (G U I) を用いることができる。メディアプレーヤ 644 は、スピーカおよび／またはオーディオ出力ジャックのようなオーディオ出力 648 を有することができる。メディアプレーヤ 644 内のシグナルプロセッシングおよび／またはコントロール回路 645 および／または他の複数の回路 (図示せず) は、データ処理、コーディングおよび／または暗号化、演算、および／または、他のいかなるメディアプレーヤ機能を実行することができる。

## 【 0046 】

10

メディアプレーヤ 644 は、圧縮されたオーディオおよび／またはビデオコンテンツのようなデータを不揮発式で記憶する大容量データストレージ 649 と通信することができる。いくつかの実施形態において、圧縮されたオーディオファイルは、M P E フォーマットまたは他の適切な圧縮オーディオおよび／またはビデオフォーマットに準拠したファイルを含む。大容量データストレージは、光／磁気ストレージデバイス (例えばハードディスクドライブ (H D D) および／またはD V D ドライブ) を含むことができる。少なくとも 1 つのH D D は図 6 A で示された構成を有することができ、少なくとも 1 つのD V D は図 6 B で示された構成を有することができる。H D D は、およそ 1 . 8 インチより小さい径の 1 以上のプラッタを持つ小型H D D であってよい。メディアプレーヤ 644 は、メモリ 650 (例えば、R A M、R O M、フラッシュメモリのような低レイテンシの不揮発性メモリ、および／または他の適切な電子データストレージ) に接続されることができる。メディアプレーヤ 644 は、W L A N ネットワークインターフェース 651 を通じたW L A N 接続をサポートすることもできる。上記に説明した実施形態に加えて、さらに他の実施形態が考えられる。

## 【 0047 】

20

この発明の実施形態は、デジタル電子回路で、またはコンピュータハードウェア、ファームウェア、ソフトウェア、またはそれらのコンビネーションで実装することができる。この発明の装置は、プログラマブルプロセッサによる実行のための機械読み込み可能な記録媒体内に実体的に実現されたコンピュータプログラムプロダクト内に実装することができる。この発明の方法ステップは、この発明の機能を実行する命令のプログラムを実行しているプログラマブルプロセッサによって、入力データに対してオペレートし出力を生成することで実行されることができる。この発明は、プログラマブルシステム上で実行可能な、1 以上のコンピュータプログラムに有利に実装されることができる。このプログラマブルシステムは、データおよび命令をデータストレージシステムから受け取り、データおよび命令をデータストレージシステムに送信する、データストレージシステムに結合された少なくとも 1 つのプログラマブルプロセッサ、少なくとも 1 つの入力デバイス、および、少なくとも 1 つの出力デバイスを有することができる。それぞれのコンピュータプログラムは、高レベル手続き型またはオブジェクト指向型のプログラミング言語、若しくは必要であればアッセンブラーまたはマシン語で実装されることができる。いずれの場合でも、言語はコンパイル型またはインタープリタ型言語であってよい。適切なプロセッサは、一例として汎用および専用マイクロプロセッサの双方を含む。概してプロセッサは、リードオンリーメモリおよび／またはランダムアクセスメモリから命令およびデータを受け取るだろう。概してコンピュータは、データファイルを記憶する 1 以上の大容量ストレージデバイスを含むだろう。そのようなデバイスは、内部ハードディスクおよびリムーバブルディスクのような磁気ディスク、光磁気ディスク、および光ディスクを含むだろう。コンピュータプログラム命令およびデータを実体的に実現するのに適したストレージデバイスは、全ての形式の不揮発性メモリ (一例として、E P R O M、E E P R O M、およびフラッシュメモリデバイスのような半導体メモリデバイスを含む)、内部ハードディスクおよびリムーバブルハードディスクのような磁気ディスク、光磁気ディスク、およびC D - R O M ディスクを含むことができる。上記はいずれもA S I C (特定用途向け集積回路) によ

30

40

50

り補完されるか A S I C に組み込まれることができる。

【 0 0 4 8 】

この発明の数々の実施形態が説明された。それにもかかわらず、この発明の要旨と範囲から逸脱することなく、さまざまな変更がなされ得ることが理解される。したがって、他の実施形態が、以下の請求項の範囲内にある。

【 図 1 】

【 図 2 】

従来技術

【図3】

【図4】

【図5】

【図6 A】

【図6 B】

【図 6 C】

【図 6 E】

【図 6 D】

【図 6 F】

【図 6 G】

---

フロントページの続き

(31)優先権主張番号 11/654,841

(32)優先日 平成19年1月18日(2007.1.18)

(33)優先権主張国 米国(US)

(74)代理人 100112520

弁理士 林 茂則

(74)代理人 100156591

弁理士 高田 学

(72)発明者 フェン、ウェイシ

アメリカ合衆国、95054 カリフォルニア州、サンタ クララ、マーベル レーン 5488

マーベル セミコンダクター インコーポレイテッド内

審査官 後藤 彰

(56)参考文献 特開2006-107040 (JP, A)

特開2006-11987 (JP, A)

特開2002-358137 (JP, A)

特開2002-341956 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 21/22

G06F 11/22