(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-12938

(P2007-12938A)

(43) 公開日 平成19年1月18日(2007.1.18)

| (51) Int.CI.                 | F 1        |   | テーマコード (参考) |

|------------------------------|------------|---|-------------|

| <b>H01L 21/822</b> (2006.01) | H01L 27/04 | D | 5C006       |

| <b>H01L 27/04</b> (2006.01)  | H01L 27/04 | E | 5C080       |

| <b>H01L 21/82</b> (2006.01)  | H01L 27/04 | A | 5F038       |

| <b>G09G 3/20</b> (2006.01)   | H01L 27/04 | H | 5F064       |

| <b>G09G 3/36</b> (2006.01)   | H01L 21/82 | L |             |

審査請求 未請求 請求項の数 15 O L (全 26 頁) 最終頁に続く

|           |                              |          |                                                |

|-----------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号 | 特願2005-193021 (P2005-193021) | (71) 出願人 | 000002369<br>セイコーホーリング株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日  | 平成17年6月30日 (2005.6.30)       | (74) 代理人 | 100090479<br>弁理士 井上 一                          |

|           |                              | (74) 代理人 | 100124626<br>弁理士 榎並 智和                         |

|           |                              | (74) 代理人 | 100124682<br>弁理士 黒田 泰                          |

|           |                              | (74) 代理人 | 100090387<br>弁理士 布施 行夫                         |

|           |                              | (74) 代理人 | 100090398<br>弁理士 大渕 美千栄                        |

|           |                              | (74) 代理人 | 100101649<br>弁理士 伊奈 達也                         |

最終頁に続く

(54) 【発明の名称】集積回路装置

(57) 【要約】 (修正有)

【課題】高速シリアル転送の信号品質を維持できる集積回路装置を提供すること。

【解決手段】回路装置に含まれるインターフェース回路ブロック120の短辺から対向する短辺へと向かう方向を第1の方向D R 1とし、当該回路ブロック120の長辺から対向する長辺へと向かう方向を第2の方向D R 2とした場合、当該回路ブロック120は、所与の処理を行う回路が形成される回路形成領域と、回路形成領域の第2の方向D R 2側に配置され、長辺側に第1の方向D R 1に沿って複数の入力端子が設けられる入力端子形成領域124と、入力端子形成領域124において、複数の入力端子P A Dが形成される配線層の下層の配線層に、第1の方向D R 1に沿って延在形成される集積回路装置用の複数の電源供給線D R V S S、D R V D D 1～D R V D D 3とを含む。

【選択図】図19

(A)

(B)

**【特許請求の範囲】****【請求項 1】**

差動信号を用いたシリアルバスを介してデータ転送を行うインターフェース回路ブロックを含む集積回路装置であって、

前記インターフェース回路ブロックの短辺である第1の辺から対向する第3の辺へと向かう方向を第1の方向とし、前記インターフェース回路ブロックの長辺である第4の辺から対向する第2の辺へと向かう方向を第2の方向とした場合に、

前記インターフェース回路ブロックは、

所与の処理を行う回路が形成される回路形成領域と、

前記回路形成領域の前記第2の方向側に配置され、前記第2の辺側に前記第1の方向に沿って複数の入力端子が設けられる入力端子形成領域と、

前記入力端子形成領域において、前記複数の入力端子が形成される配線層の下層の配線層に、前記第1の方向に沿って延在形成される前記集積回路装置用の複数の電源供給線と、

、

を含むことを特徴とする集積回路装置。

**【請求項 2】**

請求項1において、

前記複数の入力端子は、

前記インターフェース回路ブロックに前記差動信号を供給するための複数の差動信号入力端子と、

前記インターフェース回路ブロックに電源を供給するための複数の電源入力端子と、

を含み、

前記入力端子形成領域は、前記複数の差動信号入力端子が形成される差動信号入力端子形成領域と、前記複数の電源入力端子が形成される第1及び第2の電源入力端子形成領域を含み、

前記差動信号入力端子形成領域は、前記第1の電源入力端子形成領域と前記第2の電源入力端子形成領域との間に設けられていることを特徴とする集積回路装置。

**【請求項 3】**

請求項2において、

前記差動信号入力端子形成領域には、前記第2の辺側に前記第1の方向に沿って前記複数の差動信号入力端子が配置され、

前記第1及び第2の電源入力端子形成領域には、前記第2の辺側に前記第1の方向に沿って前記複数の電源入力端子が形成されていることを特徴とする集積回路装置。

**【請求項 4】**

請求項2又は3において、

前記複数の電源入力端子は、第1の電源電圧を供給するための複数の第1の電源入力端子と、前記第1の電源電圧よりも電圧の高い第2の電源電圧を供給するための複数の第2の電源入力端子と、を含み、

前記集積回路装置用の複数の電源供給線は、前記第1の電源電圧を供給するための第1の電源供給線を含むことを特徴とする集積回路装置。

**【請求項 5】**

請求項4において、

前記第1の辺側及び前記第3の辺側の少なくとも一方側の入力端子は、前記複数の第1の電源入力端子の少なくとも一つとして設定されていることを特徴とする集積回路装置。

**【請求項 6】**

請求項5において、

前記複数の第1の電源入力端子のうちの前記第1の辺側及び前記第3の辺側の少なくとも一方側に設けられた第1の電源入力端子は、第1の保護回路を介して前記第1の電源供給線と接続されていることを特徴とする集積回路装置。

**【請求項 7】**

10

20

30

40

50

請求項 6 において、

前記第 1 の保護回路はダイオードで構成されていることを特徴とする集積回路装置。

**【請求項 8】**

請求項 4 又は 5 において、

前記複数の第 1 の電源入力端子の少なくとも一つは、第 1 の保護回路を介して前記第 1 の電源供給線に接続され、

前記第 1 の保護回路は、前記回路形成領域内の前記入力端子形成領域側であって前記第 1 の辺側及び前記第 3 の辺側の少なくとも一方側に配置されていることを特徴とする集積回路装置。

**【請求項 9】**

10

請求項 4 乃至 8 のいずれかにおいて、

前記複数の第 2 の電源入力端子の少なくとも一つは、デカップリングコンデンサを介して前記第 1 の電源供給線と接続され、

前記デカップリングコンデンサは、前記回路形成領域であって前記第 1 の辺側及び前記第 3 の辺側の少なくとも一方側に配置されていることを特徴とする集積回路装置。

**【請求項 10】**

20

請求項 4 乃至 9 のいずれかにおいて、

前記複数の第 1 の電源入力端子の少なくとも一つは、第 2 の保護回路を介して前記第 1 の電源供給線に接続され、

前記第 2 の保護回路は、前記入力端子形成領域であって、前記差動信号入力端子形成領域に形成されている差動信号入力端子と、前記第 1 及び第 2 の電源入力端子形成領域の少なくとも一方に形成されている第 1 の電源入力端子と、の間の入力端子が形成されない領域の下層の半導体層に形成されていることを特徴とする集積回路装置。

**【請求項 11】**

請求項 10 において、

前記第 2 の保護回路は、前記複数の入力端子が形成される領域の下層の半導体層の領域には形成されないことを特徴とする集積回路装置。

**【請求項 12】**

30

請求項 11 において、

前記第 2 の保護回路はダイオードで構成されていることを特徴とする集積回路装置。

**【請求項 13】**

請求項 2 乃至 12 のいずれかにおいて、

その各々が差動信号を受信する第 1 ~ 第 S の受信回路と、

前記第 1 ~ 第 S の受信回路に定電圧を供給するためのバイアス回路と、

を含み、

前記回路形成領域において前記第 1 の方向に沿って、第 1 ~ 第 [ S / 2 ] ( [ X ] は X を越えない最大の整数) の受信回路、前記バイアス回路、第 ( [ S / 2 ] + 1 ) ~ 第 S の受信回路の順に配置されていることを特徴とする集積回路装置。

**【請求項 14】**

40

請求項 13 において、

前記差動信号入力端子形成領域が、前記第 1 ~ 第 S の受信回路及び前記バイアス回路に対して前記第 2 の方向側に配置されていることを特徴とする集積回路装置。

**【請求項 15】**

請求項 13 又は 14 において、

前記第 1 ~ 第 S の受信回路からの信号を処理するロジック回路を含み、

前記ロジック回路の前記第 2 の方向側には、前記第 1 ~ 第 S の受信回路が配置されていることを特徴とする集積回路装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

50

本発明は、集積回路装置に関する。

【背景技術】

【0002】

近年、EMIノイズの低減などを目的としたインターフェースとしてLVDS (Low Voltage Differential Signaling)などの高速シリアル転送のインターフェースが脚光を浴びている。この高速シリアル転送では、トランスミッタ回路がシリアル化されたデータを差動信号により送信し、レシーバ回路が差動信号を差動増幅することでデータ転送を実現する。

【0003】

一般的な携帯電話は、電話番号入力や文字入力のためのボタンが設けられる第1の機器部分と、表示パネルやカメラが設けられる第2の機器部分と、第1、第2の機器部分を接続するヒンジなどの接続部分により構成される。従って、第1の機器部分に設けられる第1の基板と、第2の機器部分に設けられる第2の基板との間のデータ転送を、差動信号を用いたシリアル転送により行えば、接続部分を通る配線の本数を減らすことができ、好都合である。

【0004】

ところで、液晶パネルなどの表示パネルを駆動する集積回路装置として表示ドライバ (LCDドライバ)がある。そして、上述した第1、第2の機器部分の間での高速シリアル転送を実現するためには、シリアルバスを介してデータ転送を行う高速インターフェース回路を表示ドライバに組み込む必要がある。

【0005】

しかしながら、表示ドライバの集積回路装置を例えばCOG (Chip On Glass) 実装した場合に、外部接続端子であるバンプでの接触抵抗が原因となって、高速シリアル転送の信号品質が劣化するという問題が判明した。

【0006】

また、表示ドライバでは、低コスト化のためにチップサイズの縮小が要求される。しかしながら、携帯電話機などに組み込まれる表示パネルの大きさはほぼ一定である。従って、微細プロセスを採用し、表示ドライバの集積回路装置を単純にシュリンクしてチップサイズを縮小しようとすると、実装が困難になるなどの問題を招く。

【特許文献1】特開2001-222249号公報

30

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、高速シリアル転送の信号品質を維持できる集積回路装置を提供することにある。

【課題を解決するための手段】

【0008】

本発明は、差動信号を用いたシリアルバスを介してデータ転送を行うインターフェース回路ブロックを含む集積回路装置であって、前記インターフェース回路ブロックの短辺である第1の辺から対向する第3の辺へと向かう方向を第1の方向とし、前記インターフェース回路ブロックの長辺である第4の辺から対向する第2の辺へと向かう方向を第2の方向とした場合に、前記インターフェース回路ブロックは、所与の処理を行う回路が形成される回路形成領域と、前記回路形成領域の前記第2の方向側に配置され、前記第2の辺側に前記第1の方向に沿って複数の入力端子が設けられる入力端子形成領域と、前記入力端子形成領域において、前記複数の入力端子が形成される配線層の下層の配線層に、前記第1の方向に沿って延在形成される前記集積回路装置用の複数の電源供給線と、を含む集積回路装置に関する。

【0009】

このように、入力端子形成領域に電源供給線を形成することで、表示ドライバの回路のレイアウトの自由度が拡大される。これにより、表示ドライバのレイアウト規模の縮小が

40

50

可能となる。また、入力端子形成領域に電源供給線を形成することで、各入力端子と電源供給線との間に保護回路を接続することが容易となり、インターフェース回路ブロック内で効率のよいレイアウトが可能となる。

【0010】

また、本発明では、前記複数の入力端子は、前記インターフェース回路ブロックに前記差動信号を供給するための複数の差動信号入力端子と、前記インターフェース回路ブロックに電源を供給するための複数の電源入力端子と、を含み、前記入力端子形成領域は、前記複数の差動信号入力端子が形成される差動信号入力端子形成領域と、前記複数の電源入力端子が形成される第1及び第2の電源入力端子形成領域を含み、前記差動信号入力端子形成領域は、前記第1の電源入力端子形成領域と前記第2の電源入力端子形成領域との間に設けられてもよい。10

【0011】

このように、複数の差動信号用入力端子を第1の電源用入力端子で挟むことにより、外部からのノイズ対策が可能となる。

【0012】

また、本発明では、前記差動信号入力端子形成領域には、前記第2の辺側に前記第1の方向に沿って前記複数の差動信号入力端子が配置され、前記第1及び第2の電源入力端子形成領域には、前記第2の辺側に前記第1の方向に沿って前記複数の電源入力端子が形成されてもよい。20

【0013】

また、本発明では、前記複数の電源入力端子は、第1の電源電圧を供給するための複数の第1の電源入力端子と、前記第1の電源電圧よりも電圧の高い第2の電源電圧を供給するための複数の第2の電源入力端子と、を含み、前記表示ドライバ用の複数の電源供給線は、前記第1の電源電圧を供給するための第1の電源供給線を含むようにしてもよい。20

【0014】

また、本発明では、前記第1の辺側及び前記第3の辺側の少なくとも一方側の入力端子は、前記複数の第1の電源入力端子の少なくとも一つとして設定されてもよい。

【0015】

また、本発明では、前記複数の第1の電源入力端子のうちの前記第1の辺側及び前記第3の辺側の少なくとも一方側に設けられた第1の電源入力端子は、第1の保護回路を介して前記第1の電源供給線と接続されてもよい。30

【0016】

これにより、第1の電源入力端子は短い配線で第1の保護回路と接続することができる。30

【0017】

また、本発明では、前記第1の保護回路はダイオードで構成されてもよい。

【0018】

また、本発明では、前記複数の第1の電源入力端子の少なくとも一つは、第1の保護回路を介して前記第1の電源供給線に接続され、前記第1の保護回路は、前記回路形成領域内の前記入力端子形成領域側であって前記第1の辺側及び前記第3の辺側の少なくとも一方側に配置されてもよい。40

【0019】

これにより、第1の保護回路は短い配線で第1の電源供給線と接続することができる。

【0020】

また、本発明では、前記複数の第2の電源入力端子の少なくとも一つは、デカップリングコンデンサを介して前記第1の電源供給線と接続され、前記デカップリングコンデンサは、前記回路形成領域であって前記第1の辺側及び前記第3の辺側の少なくとも一方側に配置されてもよい。

【0021】

このように第2の電源入力端子がデカップリングコンデンサを介して第1の電源供給線50

と接続されることで、インターフェース回路ブロック内の電源の安定化を図ることができる。また、インターフェース回路ブロック内にデカップリングコンデンサを効率よく配置することができるため、ガラス基板などのコンデンサの形成が難しい基板にインターフェース回路ブロックを実装した場合であっても、回路内の電源の安定化が可能である。

【0022】

また、本発明では、前記複数の第1の電源入力端子の少なくとも一つは、第2の保護回路を介して前記第1の電源供給線に接続され、前記第2の保護回路は、前記入力端子形成領域であって、前記差動信号入力端子形成領域に形成されている差動信号入力端子と、前記第1及び第2の電源入力端子形成領域の少なくとも一方に形成されている第1の電源入力端子と、の間の入力端子が形成されない領域の下層の半導体層に形成されてもよい。

10

【0023】

このように第2の保護回路を形成することで、回路形成領域に保護回路を設けるスペースを用意しなくても良くなり、インターフェース回路ブロックのレイアウト規模の縮小に寄与できる。また、第1の電源供給線との接続も容易となる。

【0024】

また、本発明では、前記第2の保護回路は、前記複数の入力端子が形成される領域の下層の半導体層の領域には形成されないようにしてもよい。

【0025】

このように第2の保護回路を複数の入力端子が形成されている領域の下層の半導体層に形成しないことで、インターフェース回路ブロックのレイアウトを実装形態によらずに用いることができ、設計コストの削減が可能となる。

20

【0026】

また、本発明では、前記第2の保護回路はダイオードで構成されてもよい。

【0027】

また、本発明では、その各々が差動信号を受信する第1～第Sの受信回路と、前記第1～第Sの受信回路に定電圧を供給するためのバイアス回路と、を含み、前記回路形成領域において前記第1の方向に沿って、第1～第[S/2]([X]はXを越えない最大の整数)の受信回路、前記バイアス回路、第([S/2]+1)～第Sの受信回路の順に配置されてもよい。

30

【0028】

このように、受信回路とバイアス回路を配置することで、バイアス回路は各受信回路に均等に定電圧を供給することができる。

【0029】

また、本発明では、前記差動信号入力端子形成領域が、前記第1～第Sの受信回路及び前記バイアス回路に対して前記第2の方向側に配置されてもよい。

【0030】

このようにレイアウトすることで、差動信号用入力端子から短い配線で受信回路に差動信号を供給できるため、信号劣化の少ない高速データ転送が可能となる。

【0031】

また、本発明では、前記第1～第Sの受信回路からの信号を処理するロジック回路を含み、前記ロジック回路の前記第2の方向側には、前記第1～第Sの受信回路が配置されてもよい。

40

【0032】

このようにレイアウトすることで、各入力端子から供給される信号が直線的に自然にロジック回路へ流れるため、特性の良いインターフェース回路ブロックを得ることができる。

【発明を実施するための最良の形態】

【0033】

以下、本発明の一実施形態について、図面を参照して説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない

50

。また以下で説明される構成のすべてが本発明の必須構成要件であるとは限らない。なお、以下の図において同符号のものは同様の意味を表す。

#### 【0034】

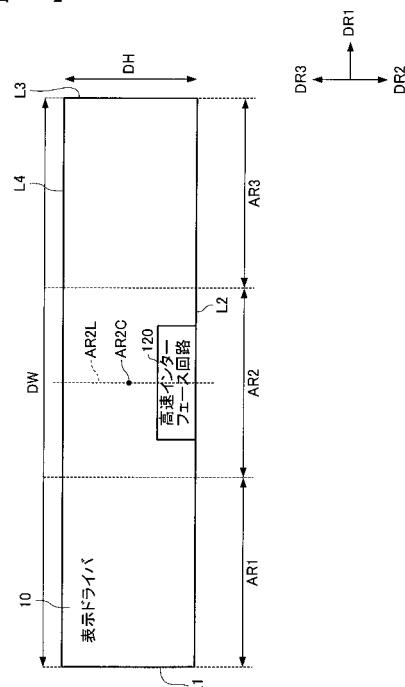

##### 1. 表示ドライバ

###### 1.1. 高速インターフェース回路の配置

図1は、表示ドライバ10（広義には集積回路装置）を示す図である。表示ドライバ10は、その短辺D Hが、その長辺D Wよりも十分に短い短辺スリムな形状の集積回路である。各第1～第3の領域A R 1～A R 3は、表示ドライバ10の長辺D Wを方向D R 1において3分割することで得られる。また、各第1～第3の領域A R 1～A R 3は、表示ドライバ10の長辆D Wを方向D R 1において3等分するようにもよい。高速インターフェース回路120（広義にはインターフェース回路ブロック）は、表示ドライバ10の第2の領域A R 2の第2の辺L 2側に配置されている。さらに、高速インターフェース回路120は、第2の領域A R 2の中心点A R 2 C通り、方向D R 2に平行な中心線A R 2 Lと平面視で重なるように表示ドライバ10に配置されている。

10

#### 【0035】

なお、方向D R 1（広義には第1の方向）は表示ドライバ10の第1の辺L 1から第3の辺L 3へ向かう方向であり、方向D R 2（広義には第2の方向）は表示ドライバ10の第4の辺L 4から第2の辺L 2へ向かう方向であり、方向D R 3（広義には第3の方向）は表示ドライバ10の第2の辺L 2から第4の辺L 4へ向かう方向である。

#### 【0036】

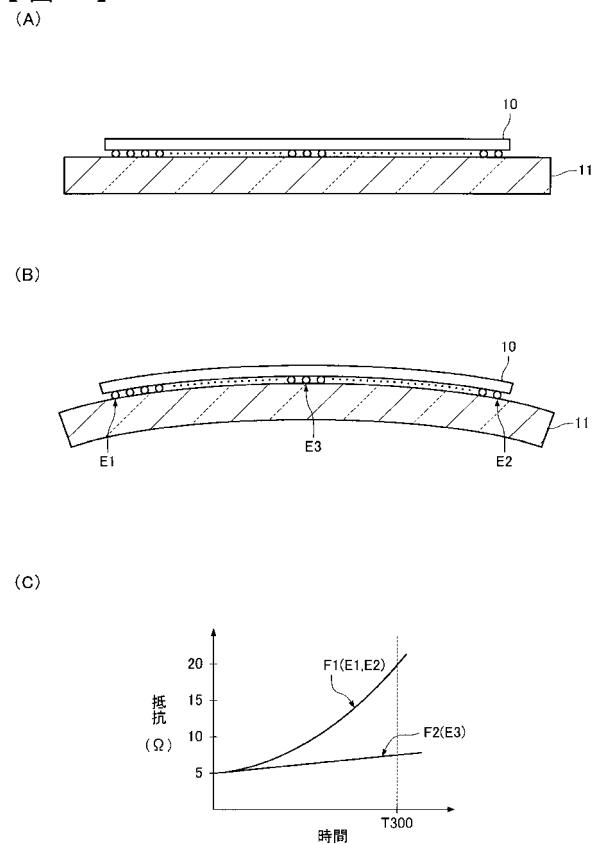

図2（A）は、表示ドライバ10をガラス基板11にCOG（Chip On Glass）実装した時の様子を示している。COG実装では、金パンプ等が形成された表示ドライバ10のチップが、表示パネルのガラス基板11に直接フェースダウンで実装される。こうすることで、LCDモジュールの厚さをLCDガラスの厚さまで薄くすることができる。

20

#### 【0037】

ところが、このようなCOG実装等を行った場合に、表示ドライバ10の両端部のパンプでの接触抵抗が上昇してしまうという問題が判明した。即ち表示ドライバ10とガラス基板11の熱膨張係数は異なる。従って、熱膨張係数の差によって生じる応力（熱ストレス）は、E 1、E 2に示す表示ドライバ10の両端部の方が、E 3に示す中央部よりも大きくなる。このため、E 1、E 2に示す両端部では、パンプでの接触抵抗が時間経過につれて上昇してしまう。例えば図2（C）に示すように10年の経時変化に相当する300サイクルの温度サイクル試験を行った場合に、図2（B）のE 3に示す中央部での接触抵抗は、図2（C）のF 2に示すように5オームから7オーム程度にしか上昇しない。これに対し、図2（B）のE 1、E 2に示す両端部での接触抵抗は、図2（C）のF 1に示すように20オーム程度に上昇してしまう。特に図1に示すように表示ドライバ10がスリムで細長になるほど、両端部と中央部の応力の差は大きくなり、両端部のパンプでの接触抵抗の上昇も大きくなる。

30

#### 【0038】

ところで、高速インターフェース回路では、信号の反射を防止するために送信側と受信側とでインピーダンス整合をとっている。しかしながら、高速インターフェース回路のパッド（DATA+、DATA-等）として、例えば表示ドライバ10の両端部のパンプに接続されるパッドを使用すると、F 1に示すパンプでの接触抵抗の上昇によって、インピーダンス整合が崩れてしまう。この結果、高速シリアル転送の信号品質が劣化する問題が生じる。

40

#### 【0039】

本実施形態は、図1に示すように高速インターフェース回路120が表示ドライバ10の第2の領域A R 2に配置されているため、上記のような問題点を解決することができる。このようにすれば、高速インターフェース回路120は、表示ドライバ10の両端に配置されないようになる。従って図2（C）のF 1に示すような接触抵抗の上昇を原因とするインピーダンス不整合を低減でき、高速シリアル転送の信号品質の劣化を低減できる。

50

## 【0040】

そして接触抵抗の上昇を最小限に抑え、信号品質の向上を図るためには、高速インターフェース回路120は、図1に示すように中心線A R 2 Lに平面視で重なるように配置されることが望ましい。こうすれば、高速インターフェース回路120が、表示ドライバ10の中央付近に配置されるようになる。従って、バンプ等での接触抵抗が図2(C)のF2に示すような特性になり、接触抵抗の上昇を原因とするインピーダンス不整合を更に抑えることができる。

## 【0041】

なお、高速インターフェース回路120側でインピーダンス整合の調整可能な場合や、バンプ接触点の抵抗値の変化に基づくインピーダンス不整合の影響をあまり考慮しなくても良い場合には、高速インターフェース回路120は、表示ドライバ10の第1又は第3の領域A R 1、A R 3に配置されても良い。

10

## 【0042】

なお高速インターフェース回路120に接続される入力端子(DATA+/-、STB+/-、CLK+/-、電源等のパッド)は、表示ドライバ10の第2の辺L2側の領域に配置できる。これらの入力端子(パッド)のパッド間の空き領域には、保護回路(保護トランジスタ)などを配置できる。

## 【0043】

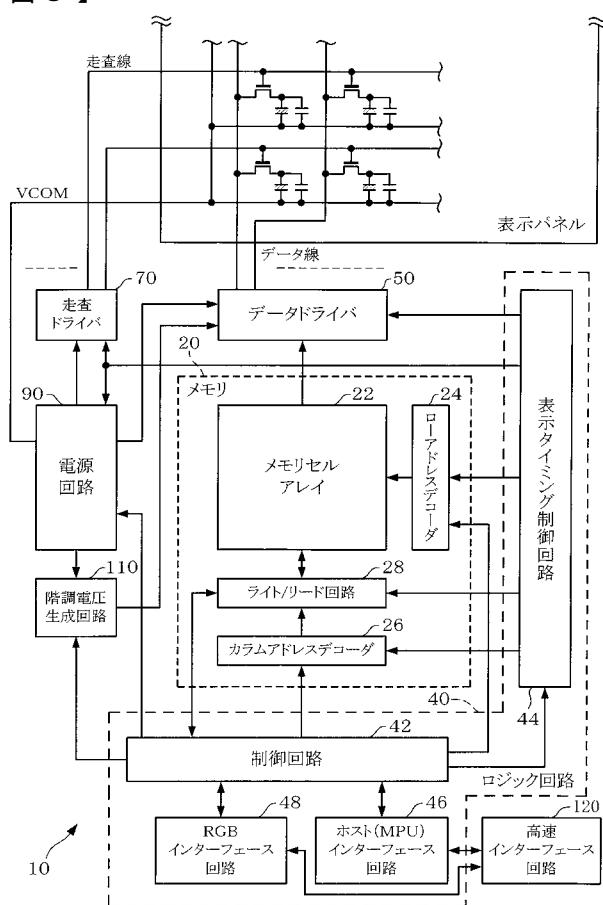

## 1.2. 表示ドライバの回路構成

図3に表示ドライバ10の回路構成例を示す。なお表示ドライバ10の回路構成は図3に限定されるものではなく、種々の変形実施が可能である。メモリ20(表示データRA M)は画像データを記憶する。メモリセルアレイ22は複数のメモリセルを含み、少なくとも1フレーム(1画面)分の画像データ(表示データ)を記憶する。この場合、1画素は例えばR、G、Bの3サブピクセル(3ドット)で構成され、各サブピクセルについて例えば6ビット(kビット)の画像データが記憶される。ロードレスデコーダ24(MPU/LCDロードレスデコーダ)はロードレスについてのデコード処理を行い、メモリセルアレイ22のワード線の選択処理を行う。カラムアドレスデコーダ26(MPUカラムアドレスデコーダ)はカラムアドレスについてのデコード処理を行い、メモリセルアレイ22のビット線の選択処理を行う。ライト/リード回路28(MPUライト/リード回路)はメモリセルアレイ22への画像データのライト処理や、メモリセルアレイ22からの画像データのリード処理を行う。なおメモリセルアレイ22のアクセス領域は、例えばスタートアドレスとエンドアドレスを対頂点とする矩形で定義される。即ちスタートアドレスのカラムアドレス及びロードレスと、エンドアドレスのカラムアドレス及びロードレスでアクセス領域が定義され、メモリアクセスが行われる。

20

30

40

## 【0044】

ロジック回路40(自動配置配線回路)は、表示タイミングを制御するための制御信号やデータ処理タイミングを制御するための制御信号などを生成する。このロジック回路40はゲートアレイ(G/A)などの自動配置配線により形成できる。制御回路42は各種制御信号を生成したり、装置全体の制御を行う。具体的には階調電圧生成回路110に階調特性(特性)の調整データ(補正データ)を出力したり、電源回路90の電圧生成を制御する。またロードレスデコーダ24、カラムアドレスデコーダ26、ライト/リード回路28を用いたメモリへのライト/リード処理を制御する。表示タイミング制御回路44は表示タイミングを制御するための各種の制御信号を生成し、メモリから表示パネル側への画像データの読み出しを制御する。ホスト(MPU)インターフェース回路46は、ホストからのアクセス毎に内部パルスを発生してメモリにアクセスするホストインターフェースを実現する。RGBインターフェース回路48は、ドットクロックにより動画のRGBデータをメモリに書き込むRGBインターフェースを実現する。なおホストインターフェース回路46、RGBインターフェース回路48のいずれか一方のみを設ける構成としてもよい。

## 【0045】

50

高速インターフェース回路 120 は、シリアルバスを介した高速シリアル転送を実現する。具体的には、シリアルバスの差動信号線を電流駆動又は電圧駆動することにより、ホスト（ホストデバイス）との間で高速シリアル転送が実現される。

#### 【0046】

図3において、高速インターフェース回路120、ホストインターフェース回路46、RGBインターフェース回路48からは1画素単位でメモリ20へのアクセスが行われる。一方、データドライバ50へは、高速インターフェース回路120、ホストインターフェース回路46、RGBインターフェース回路48とは独立した内部表示タイミングにより、ライン周期毎に、ラインアドレスで指定されライン単位で読み出された画像データが送られる。

10

#### 【0047】

データドライバ50は表示パネルのデータ線を駆動するための回路である。具体的には階調電圧生成回路110から複数（例えば64段階）の階調電圧（基準電圧）を受け、これらの複数の階調電圧の中から、デジタルの画像データに対応する電圧を選択して、データ電圧として出力する。

#### 【0048】

走査ドライバ70は表示パネルの走査線を駆動するための回路である。電源回路90は各種の電源電圧を生成する回路である。階調電圧生成回路（補正回路）110は階調電圧を生成する回路である。

#### 【0049】

##### 1.3. 高速インターフェース回路の回路構成

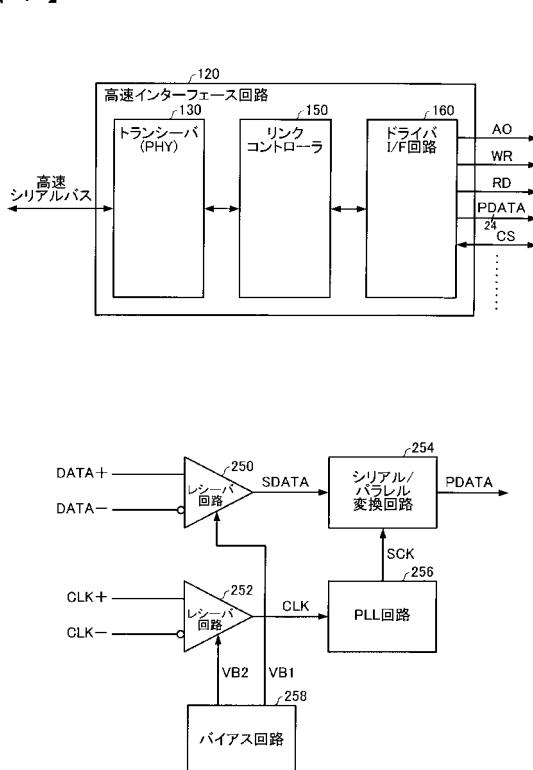

図3の高速インターフェース回路（シリアルインターフェース回路）120は、差動信号を用いたシリアルバス（高速シリアルバス）を介してデータ転送を行う回路であり、図4（A）にその構成例を示す。

20

#### 【0050】

トランシーバ130は、差動信号（差動データ信号、差動ストローブ信号、差動クロック信号）を用いてシリアルバスを介してパケット（コマンド、データ）を受信したり、送信するための回路である。具体的にはシリアルバスの差動信号線を電流駆動又は電圧駆動することによりパケットの送受信が行われる。このトランシーバ130は、差動信号線を駆動する物理層回路（アナログフロントエンド回路）や高速ロジック回路（シリアル／パラレル変換回路、パラレル／シリアル変換回路）などを含むことができる。またシリアルバスのインターフェース規格としては、例えばMDI（Mobile Display Digital Interface）規格などを採用できる。なおシリアルバスの差動信号線は多チャンネル構成であってもよい。またトランシーバ130は、レシーバ回路とトランスミッタ回路の少なくとも一方を含むものであり、例えばトランスミッタ回路を含まない構成としてもよい。

30

#### 【0051】

リンクコントローラ150は、物理層の上層であるリンク層やトランザクション層の処理を行う。具体的には、シリアルバスを介してホスト（ホストデバイス）からトランシーバ130がパケットを受信した場合には、受信したパケットを解析する。即ち受信したパケットのヘッダとデータを分離して、ヘッダを抽出する。またリンクコントローラ150は、シリアルバスを介してホストにパケットを送信する場合には、そのパケットの生成処理を行う。具体的には、送信するパケットのヘッダを生成し、ヘッダとデータを結合してパケットを組み立てる。そして生成したパケットの送信を、トランシーバ130に指示する。

40

#### 【0052】

ドライバI/F回路160は、高速インターフェース回路120と表示ドライバの内部回路との間のインターフェース処理を行う。具体的にはドライバI/F回路160は、アドレス0信号A0、ライト信号WR、リード信号RD、パラレルデータ信号PDATA、チップセレクト信号CSなどを含むホストインターフェース信号を生成して、表示ドライバの内部回路（ホストインターフェース回路46）に出力する。

50

## 【0053】

具体的には図4(A)の高速インターフェース回路120のうち、物理層の回路であるトランシーバ130を高速インターフェース回路120に含ませ、物理層の上層（リンク層、トランザクション層、アプリケーション層）の回路であるリンクコントローラ150やドライバI/F回路160をロジック回路40に含ませる。即ち、高速インターフェース回路120にはトランシーバ130だけ設け、リンクコントローラ150及びドライバI/F回路160を外部の回路に設ける。このようにすれば、リンクコントローラ150やドライバI/F回路160を、例えばゲートアレイなどの自動配置配線手法によりインプリメントすることができ、設計を効率化できる。なおトランシーバ130が含む高速ロジック回路（シリアル／パラレル変換回路等）の一部又は全部をロジック回路40に含ませてもよい。

10

## 【0054】

図4(B)にトランシーバ130の構成例を示す。データ用のレシーバ回路250は差動データ信号DATA+、DATA-を受信する。そしてレシーバ回路250は、DATA+、DATA-の信号線間に設けられた図示しない抵抗素子の両端に生じる電圧を増幅し、得られたシリアルデータSDATAを後段のシリアル／パラレル変換回路254に出力する。クロック用のレシーバ回路252は差動クロック信号CLK+、CLK-を受信する。そしてレシーバ回路252は、CLK+、CLK-の信号線間に設けられた図示しない抵抗素子の両端に生じる電圧を増幅し、得られたクロックCLKを後段のPLL回路256に出力する。シリアル／パラレル変換回路254は、データ用レシーバ回路250からのシリアルデータSDATAをサンプリングし、パラレルデータPDATAに変換して出力する。PLL(Phase Locked Loop)回路256は、クロック用レシーバ回路252により受信されたクロックCLKに基づいて、データ用レシーバ回路250で受信されたデータをサンプリングするためのサンプリングクロックSCKを生成する。具体的にはPLL回路256は、サンプリングクロックSCKとして、周波数が同一で位相が互いに異なる多相のサンプリングクロックを、シリアル／パラレル変換回路254に出力する。そしてシリアル／パラレル変換回路254は、この多相のサンプリングクロックを用いて、シリアルデータSDATAをサンプリングし、パラレルデータPDATAを出力する。バイアス回路258は、バイアス電流を制御するためのバイアス電圧VB1、VB2を生成してレシーバ回路250、252に供給する。

20

30

## 【0055】

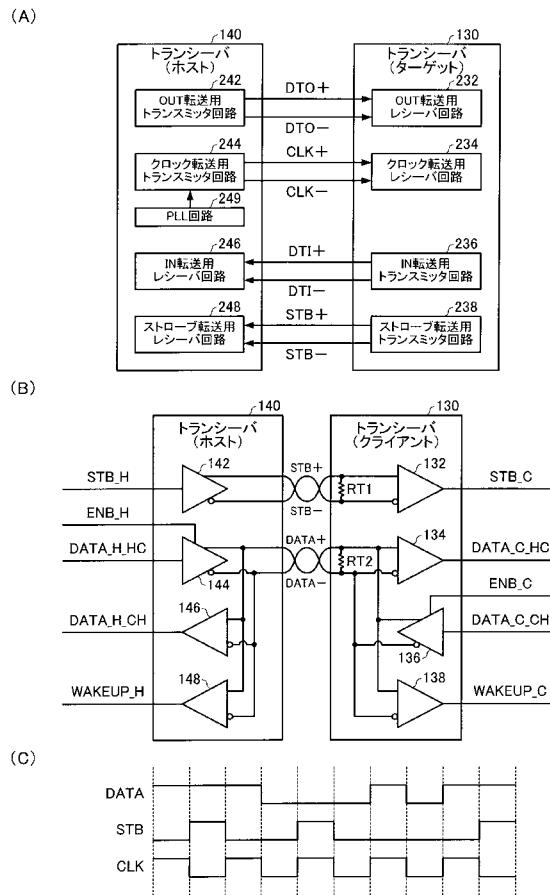

なおトランシーバの構成は図4(B)に限定されず、例えば図5(A)、図5(B)に示すような種々の変形実施が可能である。

## 【0056】

例えば図5(A)の第1の変形例において、DTO+、DTO-は、ホスト側のトランスマッタ回路242がターゲット側のレシーバ回路232に出力する差動データ信号(OUITデータ)である。CLK+、CLK-は、ホスト側のトランスマッタ回路244がターゲット側のレシーバ回路234に出力する差動クロック信号である。ホスト側はCLK+/ -のエッジに同期してDTO+/-を出力する。従ってターゲット側は、CLK+/ -を用いてDTO+/-をサンプリングして取り込むことができる。更に図5(A)では、ターゲット側はホスト側から供給されたクロックCLK+/ -に基づいて動作する。即ちCLK+/ -はターゲット側のシステムクロックになる。このためPLL回路249はホスト側に設けられ、ターゲット側には設けられていない。

40

## 【0057】

DTI+、DTI-はターゲット側のトランスマッタ回路236がホスト側のレシーバ回路246に出力する差動データ信号(INデータ)である。STB+、STB-は、ターゲット側のトランスマッタ回路238がホスト側のレシーバ回路248に出力する差動ストローブ信号である。ターゲット側はホスト側から供給されたCLK+/ -に基づいてSTB+/-を生成して出力する。そしてターゲット側はSTB+/-のエッジに同期してDTI+/-を出力する。従ってホスト側は、STB+/-を用いてDTI+/-をサ

50

ンプリングして取り込むことができる。

#### 【0058】

また図5(B)の第2の変形例はMDDI規格に準拠したトランシーバの例である。図5(B)において、トランシーバ140はホストデバイスに内蔵され、トランシーバ130は表示ドライバに内蔵される。また136、142、144はトランスミッタ回路であり、132、134、146はレシーバ回路である。また138、148はウェイクアップ検出回路である。ホスト側のトランスミッタ回路142は差動ストローブ信号STB+/-を駆動する。そしてクライアント側のレシーバ回路132は、駆動により抵抗RT1の両端に発生した電圧を増幅し、ストローブ信号STB\_Cを後段の回路に出力する。またホスト側のトランスミッタ回路144はデータ信号DATA+/-を駆動する。そしてクライアント側のレシーバ回路134は、駆動により抵抗RT2の両端に発生した電圧を増幅し、データ信号DATA\_C\_HCを後段の回路に出力する。図5(C)に示すように送信側は、データ信号DATAとクロック信号CLKの排他的論理和をとることで、ストローブ信号STBを生成し、このSTBを高速シリアルバスを介して受信側に送信する。そして受信側は、受信したデータ信号DATAとストローブ信号STBの排他的論理和をとることで、クロック信号CLKを再生する。

#### 【0059】

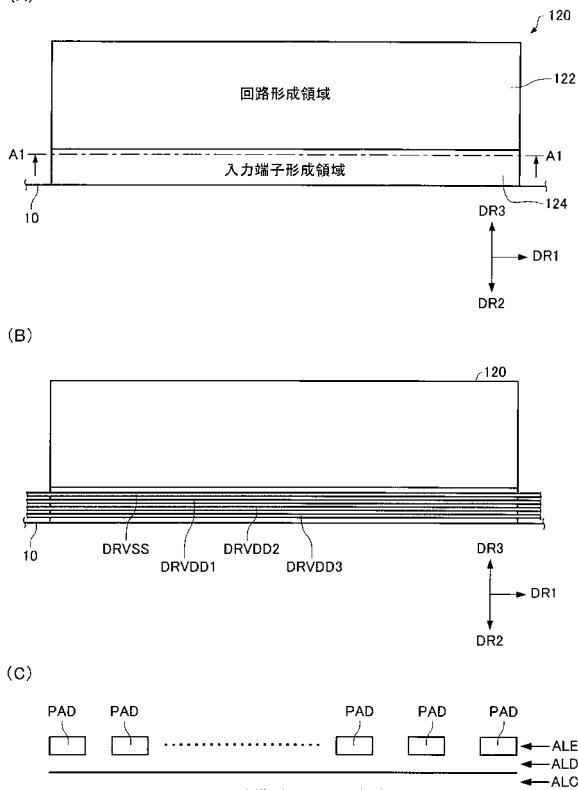

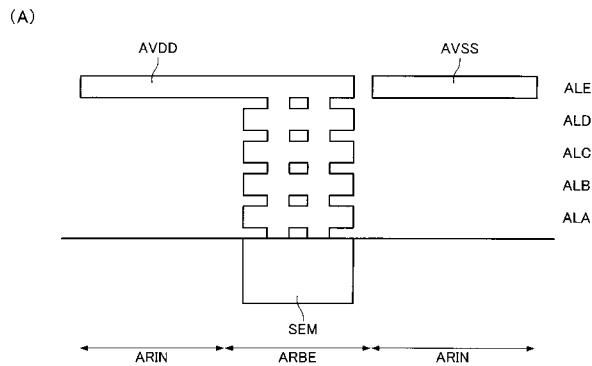

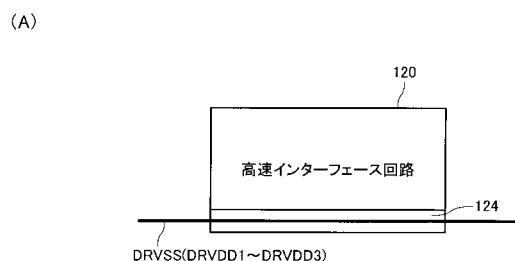

##### 2. 高速インターフェース回路のレイアウト構成

###### 2.1. 入力端子形成領域及び回路形成領域

図6(A)～図6(C)は、高速インターフェース回路120の入力端子形成領域124を示す図である。図6(A)に示すように高速インターフェース回路120において、表示ドライバ10の第2の辺L2側に入力端子形成領域124が設けられ、入力端子形成領域124の方向DR3側に回路形成領域122が設けられている。

#### 【0060】

入力端子形成領域124には、高速インターフェース回路120の内部回路に接続される複数の入力端子が方向DR1に沿って配置される。回路形成領域122には、後述する差動信号を受信する受信回路や、受信回路に定電圧を供給するバイアス回路や、受信回路からの信号処理を行うロジック回路などが形成される。

#### 【0061】

本実施形態において高速インターフェース回路120は、例えば5層の金属配線層で形成される。この場合、複数の入力端子は、最上層の第5金属配線層ALEに形成される。

#### 【0062】

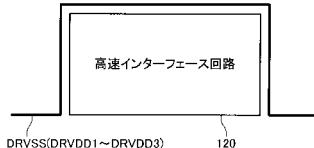

また、図6(B)に示すように、入力端子形成領域124には、例えば4本の表示ドライバ10用の電源供給線DRVSS(広義には第1の電源供給線)、DRVDD1～DRVDD3が形成されている。電源供給線DRVSSは表示ドライバ10用の電源電圧VSS(広義には第1の電源電圧)を表示ドライバ10内で供給するための電源供給線である。同様に、電源供給線DRVDD1～DRVDD3は、それぞれ表示ドライバ10に必要な電源電圧(電源電圧VSSよりも高い電圧)を供給するための電源供給線である。

#### 【0063】

これらの電源供給線DRVSS、DRVDD1～DRVDD3は、方向DR1に沿って延在形成され、特に電源供給線DRVSSは入力端子形成領域124内の回路形成領域122側に形成されている。このように電源供給線DRVSSを回路形成領域122に形成することで、電源供給線DRVSSと、後述するデカップリングコンデンサ、保護回路等との接続を簡素化することができるため、効率の良いレイアウトが可能となる。

#### 【0064】

また、これらの電源供給線DRVSS、DRVDD1～DRVDD3は、複数の入力端子PADの下層に形成される。電源供給線DRVSS、DRVDD1～DRVDD3は、例えば図6(C)に示すように第3金属配線層ALCに形成されるが、これに限定されない。電源供給線DRVSS、DRVDD1～DRVDD3は例えば第2金属配線層ALBに形成されても良い。

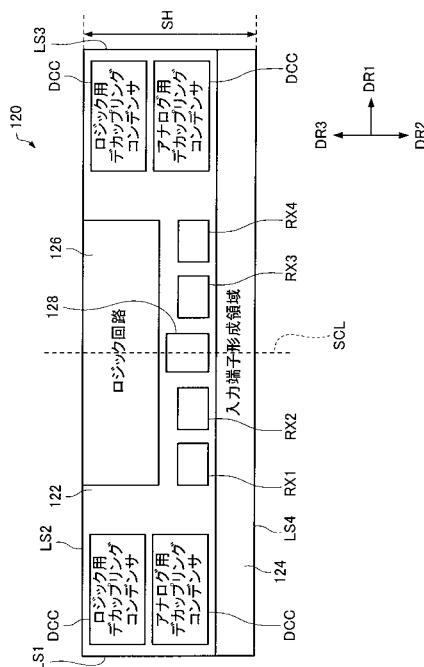

## 【0065】

## 2.2. 各回路のレイアウト

図7は、高速インターフェース回路120の各回路のレイアウトを示す図である。図7に示すように、デカップリングコンデンサDCCが高速インターフェース回路120の第1の辺LS1側及び第3の辺LS3側に設けられている。このデカップリングコンデンサDCCは、後述するが電源供給線DRVSSに接続され、高速インターフェース回路120の電源系が例えば表示ドライバ10の電源供給線DRVDD1～DRVDD3からノイズ等の影響を受けても、高速インターフェース回路120の電源電圧を安定させることができる。また、デカップリングコンデンサDCCを、アナログ用デカップリングコンデンサと、ロジック用デカップリングコンデンサとのそれぞれ設けることが望ましい。デカップリングコンデンサをアナログ用とロジック用（デジタル用）とで分けることで、アナログ回路とロジック回路（デジタル回路）との間でのノイズ伝搬を減少させることができる。なお、デカップリングコンデンサDCCは、図7に限定されず、回路形成領域122内の空いている領域に設けるようにすることができる。このデカップリングコンデンサDCCは、容量が大きい程、高速インターフェース回路120内の電源が安定する。

10

## 【0066】

また、回路形成領域122には、中心線SCLと平面視で重なるようにバイアス回路128が設けられている。バイアス回路128は、受信回路RX1～RX4（広義には第1～第5の受信回路）に定電圧を供給する回路であり、例えば図4（B）のバイアス回路258に相当する。

20

## 【0067】

また、バイアス回路128の両側には、方向DR1に沿って受信回路RX1～RX4が配置されている。各受信回路RX1、RX3、RX4は例えば図4（B）のレシーバ回路250に相当し、受信回路RX2は図4（B）のレシーバ回路252に相当する。

20

## 【0068】

なお、中心線SCLは方向DR2に平行で、且つ、高速インターフェース回路120の第2の辺LS2（又は、第4の辺LS4）の中点を通る高速インターフェース回路120の中心線である。このように、バイアス回路128を高速インターフェース回路120の中心に配置することで、複数の受信回路RX1～RX4に均等に定電圧を供給することができる。これにより、受信回路RX1～RX4とバイアス回路128との配線長の違いが緩和され、配線長の違いに起因する信号の遅延や、配線抵抗の違いによって生じる供給電圧のバラツキ等を緩和することができる。即ち、信号特性の良い高速インターフェース回路120を実現できる。

30

## 【0069】

また、受信回路RX1～RX4、バイアス回路128の方向DR3側には、ロジック回路126が設けられている。ロジック回路126は、各受信回路RX1～RX4からの信号を処理し、上層の回路（例えばリンクコントローラ150等）に処理した信号を供給する。

40

## 【0070】

図7のように、各回路をレイアウトすることで、高速インターフェース回路120の短辺の長さSHを短くすることができる。

## 【0071】

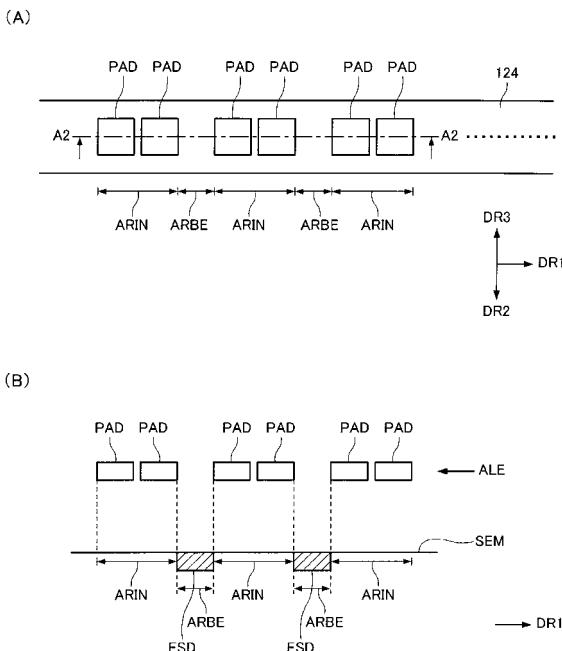

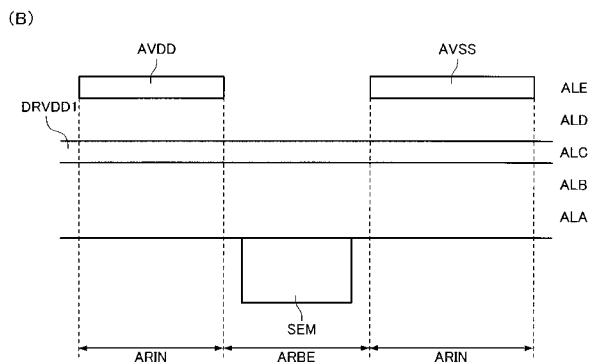

## 2.3. 入力端子形成領域と保護回路

図8（A）は、入力端子形成領域124の一部を示す。複数の入力端子PADが方向DR1に沿って配置されている。本実施形態では例えば1つの信号を受けるために2つの入力端子PADを用いている。このように2つの入力端子PADで1つの信号を受ける構造（ダブルパッド）によって、2つの入力端子PADが配置される入力端子配置領域ARINの方向DR1での幅が広くなる。これにより、製品の検査等においてプローブカードの接触が容易になり、検査効率の向上を期待できる。また、入力端子配置領域ARINの方向DR1での幅が広いため、製品の検査において、複数の検査針を接触させることができ

50

るので、例えば四端子測定法などを用いて測定精度を高めることができる。

#### 【0072】

入力端子配置領域 A R I N と入力端子配置領域 A R I N の間には、入力端子間領域 A R B E が設けられている。この入力端子間領域 A R B E は、入力端子 P A D が形成されない領域である。この入力端子間領域 A R B E の下層の半導体層には、保護回路 E S D (広義には保護回路) が形成されている。

#### 【0073】

このように入力端子形成領域 124 に保護回路 E S D を形成することができるため、回路形成領域 122 を有効に利用することができ、高速インターフェース回路 120 のレイアウト面積の縮小に寄与できる。

#### 【0074】

図 8 (B) に図 8 (A) の A2-A2 断面を示す。各入力端子 P A D は例えば第 5 金属配線層 A L E に形成される。その下層の半導体層 S E M において、入力端子 P A D の下層の領域 (即ち、入力端子配置領域 A R I N の下層の半導体層 S E M ) には保護回路 E S D は形成されない。

#### 【0075】

図 8 (B) に示すように、半導体層 S E M において、入力端子間領域 A R B E の下層の領域 (即ち、入力端子 P A D が形成されていない領域) に保護回路 E S D が形成されている。

#### 【0076】

例えば、表示ドライバ 10 をバンプ用いて COG 実装する場合 (バンプ品とも言う) には、入力端子 P A D の下層の配線層が空くため、その配線層を自由に使える。即ち、入力端子 P A D の下層の半導体層 S E M にも保護回路 E S D を形成できる。

#### 【0077】

これに対して、表示ドライバ 10 をワイヤボンディング等で基板に実装する場合 (パッド品とも言う) には、入力端子 P A D の下層も入力端子 P A D の構造の一部として含まれるため、入力端子 P A D の下層の配線層を使うことができない。このため、入力端子配置領域 A R I N の下層の半導体層 S E M には保護回路 E S D を形成することができない。

#### 【0078】

一方、本実施形態では、入力端子間領域 A R B E の下層の半導体層 S E M に保護回路 E S D が形成され、入力端子配置領域 A R I N の下層の半導体層 S E M には形成されない。このような回路レイアウトを採用することによって、本実施形態の高速インターフェース回路 120 を形成するための高速インターフェース回路マクロをバンプ品の表示ドライバ 10 やパッド品の表示ドライバ 10 に適用できる。即ち、表示ドライバ 10 の実装形態のそれぞれに対して高速インターフェース回路 120 の設計を行わずに、高速インターフェース回路マクロを供給できるため、設計コストの削減が可能となる。

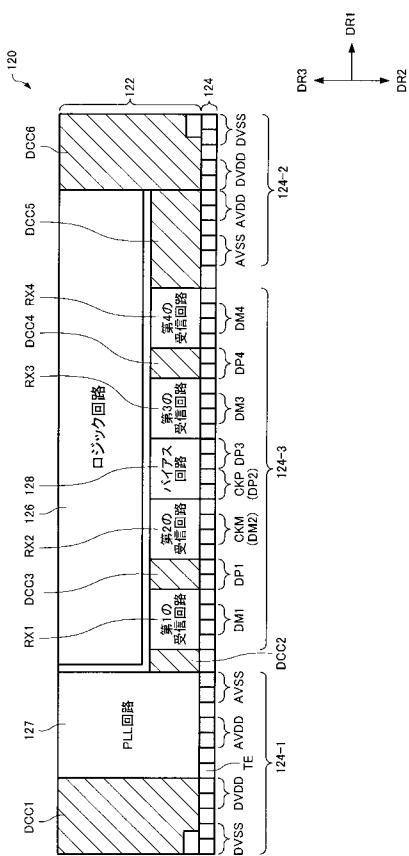

#### 【0079】

##### 2.4. 入力端子の種類とその配列

図 9 は、高速インターフェース回路 120 の詳細なレイアウトを示す図である。作図の都合上、各入力端子間には隙間がないように見えるが、実際は各入力端子間には多少の幅が存在する。図 10 においても同様である。入力端子形成領域 124 は、電源電圧 V D D (広義には第 2 の電源電圧)、V S S (広義には第 1 の電源電圧) を高速インターフェース回路 120 に供給するためのロジック用電源電圧入力端子 D V S S (広義には第 1 の電源用入力端子)、D V D D (広義には第 2 の電源用入力端子)、アナログ用電源電圧入力端子 A V D D (広義には第 2 の電源用入力端子)、A V S S (広義には第 1 の電源用入力端子) が配置される第 1、第 2 の電源入力端子形成領域 124-1、124-2 を含む。

#### 【0080】

第 1、第 2 の電源入力端子形成領域 124-1、124-2 では、方向 D R 1 に沿って、ロジック用電源電圧入力端子 D V S S、D V D D、アナログ用電源電圧入力端子 A V D D、A V S S の順に配置されている。

10

20

30

40

50

**【0081】**

また、入力端子形成領域124は、差動信号を高速インターフェース回路120に供給するための差動信号用入力端子D M 1～D M 4、D P 1～D P 4が配置される差動信号入力端子形成領域124-3を含む。

**【0082】**

差動信号用入力端子D M 1、D P 1は受信回路R X 1に接続され、差動信号用入力端子C K M ( D M 2 )、C K P ( D P 2 )は受信回路R X 2に接続される。受信回路R X 2は、差動信号で供給されるクロックを受けるが、これに限定されない。他の受信回路でクロックを受けても良い。

**【0083】**

同様にして、差動信号用入力端子D M 3、D P 3は受信回路R X 3に対応し、差動信号用入力端子D M 4、D P 4は受信回路R X 4に対応する。

**【0084】**

図9に示すように、差動信号入力端子形成領域124-3は、方向D R 1において、第1及び第2の電源入力端子形成領域124-1、124-2の間に設けられている。

**【0085】**

ロジック用電源電圧入力端子D V S S、D V D Dに供給される電圧は、例えばロジック回路126に供給される。なお、ロジック用電源電圧入力端子D V S Sには例えば電圧V S Sが供給され、ロジック用電源電圧入力端子D V D Dには例えば電圧V D Dが供給される。

**【0086】**

アナログ用電源電圧入力端子A V D D、A V S Sに供給される電圧は例えばバイアス回路128やP L L回路127に供給される。なお、アナログ用電源電圧入力端子A V D Dには例えば電圧V D Dが供給され、アナログ用電源電圧入力端子A V S Sには例えば電圧V S Sが供給される。

**【0087】**

P L L回路127は、高速インターフェース回路120に差動信号で供給されるクロックの周波数に対して例えば倍倍処理を行い、例えば図4( B )のP L L回路256に相当する。

**【0088】**

また、回路形成領域122において、受信回路R X 1～R X 4、ロジック回路126、P L L回路127、バイアス回路128が配置されることで、D C C 1～D C C 6に示すように空き領域を生じる。この領域を利用して、デカップリングコンデンサD C Cが形成される。このようにスペースを有効利用することで、効率の良いレイアウトが可能となる。また、この空きスペースを用いてデカップリングコンデンサD C Cの容量を稼ぐことができるため、高速インターフェース回路120内の電源を安定化させることができる。

**【0089】**

なお、テスト端子T Eは、高速インターフェース回路120のテストを行う場合に用いられ、高速インターフェース回路120から省略されても良い。

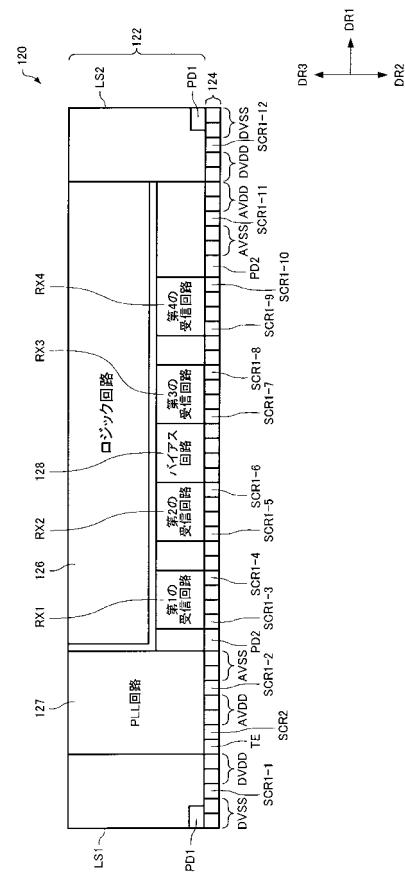

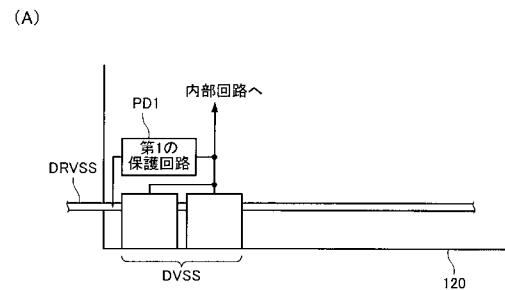

**【0090】****2.5.保護回路の配置**

図10は、保護回路P D 1(広義には第1の保護回路)、P D 2(広義には第2の保護回路)、保護回路S C R 1-1～S C R 1-12、S C R 2の配置を示す図である。なお、保護回路P D 2、保護回路S C R 1-1～S C R 1-12、S C R 2は保護回路E S Dに相当する。

**【0091】**

保護回路P D 1は、高速インターフェース回路120の第1の辺L S 1側及び第3の辺L S 3側であって、ロジック用電源電圧入力端子D V S Sの方向D R 3側の回路形成領域122に設けられている。

**【0092】**

10

20

30

40

50

保護回路 P D 2 は入力端子形成領域 1 2 4 であって、アナログ用電源電圧入力端子 A V S S に隣接する入力端子間領域 A R B E の半導体層に形成されている。

#### 【 0 0 9 3 】

保護回路 S C R 1 - 1 、 S C R 1 - 1 2 はロジック用電源電圧入力端子 D V D D に隣接する入力端子間領域 A R B E の半導体層に形成されている。保護回路 S C R 1 - 2 、 S C R 1 - 1 1 はアナログ用電源電圧入力端子 A V D D に隣接する入力端子間領域 A R B E の半導体層に形成されている。保護回路 S C R 1 - 3 ~ S C R 1 - 1 0 は各差動信号用入力端子 D M 1 ~ D M 4 、 D P 1 ~ D P 4 に隣接する入力端子間領域 A R B E の半導体層に形成されている。保護回路 S C R 2 は、テスト端子 T E に隣接する入力端子間領域 A R B E の半導体層に形成されている。

10

#### 【 0 0 9 4 】

なお、入力端子形成領域 1 2 4 の例えば第 3 金属配線層 A L C には表示ドライバ 1 0 用の電源供給線 D R V S S が形成されているため、各保護回路との接続が容易である。

#### 【 0 0 9 5 】

##### 3 . 保 護 回 路

###### 3 . 1 . サイリスタ

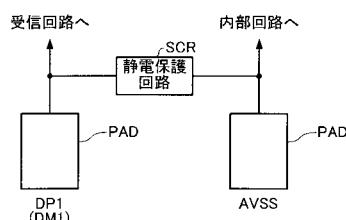

図 1 1 ( A ) ~ 図 1 1 ( C ) は、図 1 0 の各保護回路 S C R 1 - 1 ~ S C R 1 - 1 2 、 S C R 2 に相当する保護回路 S C R と各入力端子との接続関係を示す図である。保護回路 S C R は例えばサイリスタで構成することができる。

20

#### 【 0 0 9 6 】

図 1 1 ( A ) に示すように、保護回路 S C R は、アナログ用電源電圧入力端子 A V D D ( 又はロジック用電源電圧入力端子 D V D D ) とアナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) を接続する。なお、アナログ用電源電圧入力端子 A V D D ( 又はロジック用電源電圧入力端子 D V D D ) とアナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) は内部回路へ接続される。

#### 【 0 0 9 7 】

例えば、アナログ用電源電圧入力端子 A V D D ( 又はロジック用電源電圧入力端子 D V D D ) に予期せぬ高電圧が供給された場合、保護回路 S C R がオン状態となり、その高電圧がアナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) に供給される。このため、高電圧から内部回路を保護することができる。

30

#### 【 0 0 9 8 】

なお、図 1 1 ( A ) の保護回路 S C R は、例えば図 1 0 の保護回路 S C R 1 - 1 、 S C R 1 - 2 、 S C R 1 - 1 1 、 S C R 1 - 1 2 に相当する。また、保護回路 S C R を、アナログ用電源電圧入力端子 A V D D ( 又はロジック用電源電圧入力端子 D V D D ) とアナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) の近傍に設けることで、内部回路への予期せぬ高電圧の伝搬を防止する効果が高くなる。

#### 【 0 0 9 9 】

また、図 1 1 ( B ) に示すように、保護回路 S C R は、差動信号用入力端子 D M 1 ( 又は D M 2 ~ 4 、 D P 1 ~ D P 4 ) とアナログ用電源電圧入力端子 A V S S を接続する。なお、差動信号用入力端子 D M 1 は受信回路 R X 1 に接続され、アナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) は内部回路へ接続される。

40

#### 【 0 1 0 0 】

例えば、差動信号用入力端子 D M 1 ( 又は D M 2 ~ 4 、 D P 1 ~ D P 4 ) に予期せぬ高電圧が供給された場合、保護回路 S C R がオン状態となり、その高電圧がアナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) に供給される。このため、高電圧から受信回路を保護することができる。

#### 【 0 1 0 1 】

なお、図 1 1 ( B ) の保護回路 S C R は、例えば図 1 0 の保護回路 S C R 1 - 3 ~ S C R 1 - 1 0 に相当する。また、保護回路 S C R を、差動信号用入力端子 D M 1 ( 又は D M 2 ~ 4 、 D P 1 ~ D P 4 ) とアナログ用電源電圧入力端子 A V S S の近傍に設けること

50

、内部回路への予期せぬ高電圧の伝搬を防止する効果が高くなる。

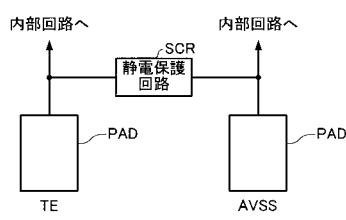

#### 【0102】

また、図11(C)に示すように、保護回路SCRは、テスト端子TEとアナログ用電源電圧入力端子AVSSを接続する。なお、テスト端子TEとアナログ用電源電圧入力端子AVSS(又はロジック用電源電圧入力端子DVSS)は内部回路へ接続される。

#### 【0103】

例えば、テスト端子TEに予期せぬ高電圧が供給された場合、保護回路SCRがオン状態となり、その高電圧がアナログ用電源電圧入力端子AVSS(又はロジック用電源電圧入力端子DVSS)に供給される。このため、高電圧から内部回路を保護することができる。

10

#### 【0104】

なお、図11(C)の保護回路SCRは、例えば図10の保護回路SCR2に相当する。また、テスト端子TEとアナログ用電源電圧入力端子AVSS(又はロジック用電源電圧入力端子DVSS)の近傍に設けることで、内部回路への高電圧の伝搬を防止する効果が高くなる。

#### 【0105】

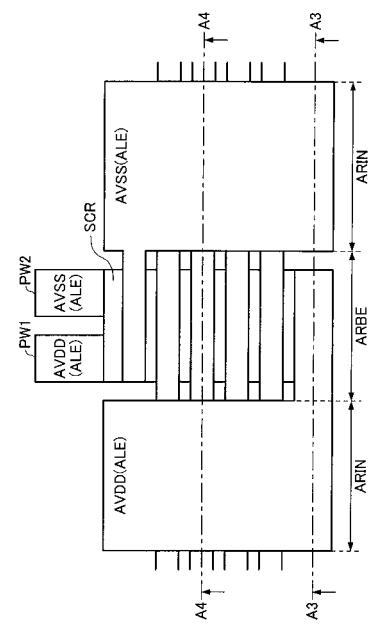

図12は、アナログ用電源電圧入力端子AVDDとアナログ用電源電圧入力端子AVSを拡大した図である。各入力端子AVDD、AVSSは例えば第5金属配線層ALEに形成されている。その下層の例えば第3金属配線層ALCには表示ドライバ10用の電源供給線DRVSS、DRVDD1～DRVDD3が形成されている。

20

#### 【0106】

また、入力端子間領域ARB Eの半導体層には保護回路SCRが形成されている。アナログ用電源電圧入力端子AVDDは保護回路SCRに接続され、保護回路SCRを介してアナログ用電源電圧入力端子AVSSに接続される。また、アナログ用電源電圧入力端子AVDDは入力端子間領域ARB Eの半導体層に接続され、保護回路SCRを介さずに電圧供給端子PW1に接続される。電圧供給端子PW1は例えば第5金属配線層ALEに形成される。こうすることで、保護回路SCRがオン状態とならない場合には、アナログ用電源電圧入力端子AVDDに供給される例えば電圧VDDを電圧供給端子PW1に供給することができる。

30

#### 【0107】

同様にして、アナログ用電源電圧入力端子AVSSは保護回路SCRに接続され、保護回路SCRを介してアナログ用電源電圧入力端子AVDDに接続される。また、アナログ用電源電圧入力端子AVSSは入力端子間領域ARB Eの半導体層に接続され、保護回路SCRを介さずに電圧供給端子PW2に接続される。電圧接続端子PW2は例えば第5金属配線層ALEに形成される。こうすることで、保護回路SCRがオン状態とならない場合には、アナログ用電源電圧入力端子AVSSに供給される例えば電圧VSSを電圧供給端子PW2に供給することができる。

#### 【0108】

図13(A)は、図12のA3-A3断面を示す図である。アナログ用電源電圧入力端子AVDDは、入力端子間領域ARB Eの下層の金属配線層ALE～ALAを用いて入力端子間領域ARB Eの下層の半導体層SEMに接続される。

40

#### 【0109】

図13(B)は、図12のA4-A4断面を示す図である。各入力端子AVDD、AVSSの下層の第3金属配線層ALCには表示ドライバ10用の電源供給線DRVDD1が形成されている。

#### 【0110】

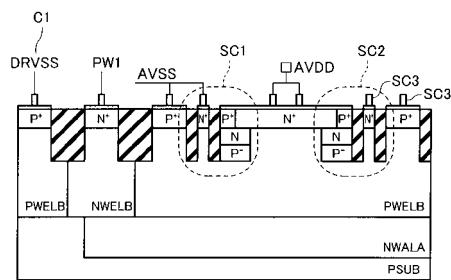

図14(A)は、本実施形態の高速インターフェース回路120に用いられる保護回路SCRの一例を示す断面図である。図14(A)のSC1、SC2に示すように二つのサイリスタが形成されているが、これに限定されない。どちらか一方だけ形成されるようにしても良い。図14(A)に示すように二つのサイリスタを作りこんでおけば、金属配線

50

をするときにサイリスタをいくつ使うかを決めることができる。例えば、耐圧を稼ぎたい場合には、S C 3 に示す部分を配線し、サイリスタを並列に接続することで実現できる。

#### 【0111】

例えば、アナログ用電源電圧入力端子 A V D D は S C 1 に示すサイリスタを介してアナログ用電源電圧入力端子 A V S S に接続される。また、アナログ用電源電圧入力端子 A V D D はサイリスタを介さず半導体層を介して、電圧供給端子 P W 1 と接続される。なお、C 1 に示すように表示ドライバ 1 0 用の電源供給線 D R V S S と拡散領域 P W E L B が接続されている。

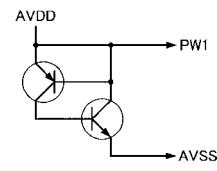

#### 【0112】

図 14 (B) に保護回路 S C R を説明するための簡略化された回路図を示す。アナログ用電源電圧入力端子 A V D D に高電圧が供給されるとサイリスタがオンとなり、高電圧は電圧供給端子 P W 1 には供給されず、アナログ用電源電圧入力端子 A V S S 側に供給される。これにより、高電圧から内部回路を保護することができる。

#### 【0113】

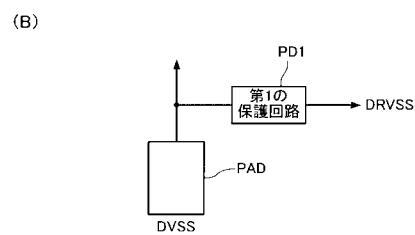

3 . 2 . 双方向ダイオード

3 . 2 . 1 . 第 1 の保護回路

図 10 に示すように保護回路 P D 1 は、高速インターフェース回路 1 2 0 の第 1 の辺 L S 1 側及び第 3 の辺 L S 3 側であって、ロジック用電源電圧入力端子 D V S S の方向 D R 3 側の回路形成領域 1 2 2 に設けられている。そのうちの第 1 の辺 L S 1 側に設けられている保護回路 P D 1 を図 15 (A) に示す。

#### 【0114】

図 15 (A) に示すように、保護回路 P D 1 は入力端子 D V S S に非常に近い領域に設けられているため、入力端子 D V S S と接続しやすい。また、保護回路 P D 1 は第 1 の辺 L S 側であって、回路形成領域 1 2 2 内の入力端子形成領域 1 2 4 側に設けられているため、電源供給線 D R V S S と非常に近い。このため、保護回路 P D 1 は電源供給線 D R V S S とも接続しやすい。なお、図 15 (B) に示すように、第 1 の保護回路 P D 1 は、ロジック用電源電圧入力端子 D V S S と表示ドライバ 1 0 用の電源供給線 D R V S S とを接続する。また、ロジック用電源電圧入力端子 D V S S は内部回路へ接続される。

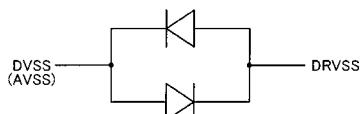

#### 【0115】

以上のことから、本実施形態では、効率よく保護回路 P D 1 をレイアウトすることができる。即ち、高速インターフェース回路 1 2 0 の方向 D R 3 での幅 S H を短くすることができる。

#### 【0116】

図 15 (C) に示すように保護回路 P D 1 は双方向ダイオードで構成することができる。

#### 【0117】

なお、図 15 (A) では高速インターフェース回路 1 2 0 の第 1 の辺 L S 1 側の保護回路 P D 1 について示されているが、第 3 の辺 L S 3 側の保護回路 P D 1 も同様の効果を発揮できる。

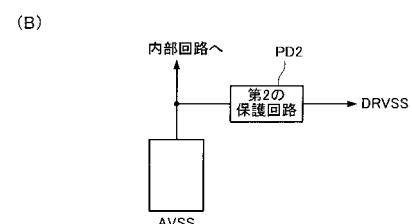

#### 【0118】

3 . 2 . 2 . 第 2 の保護回路

図 10 に示すように保護回路 P D 2 は入力端子形成領域 1 2 4 であって、アナログ用電源電圧入力端子 A V S S に隣接する入力端子間領域 A R B E の半導体層に形成されている。一例としてそのうちの 1 つ第 2 の保護回路 P D 2 を図 16 (A) に示す。

#### 【0119】

図 16 (A) に示すように、保護回路 P D 2 は入力端子 A V S S に隣接する入力端子間領域 A R B E に設けられているため、入力端子 A V S S と接続しやすい。また、保護回路 P D 2 は入力端子形成領域 1 2 4 に形成されているため、その下層に形成されている電源供給線 D R V S S と非常に近い。このため、保護回路 P D 2 は電源供給線 D R V S S とも接続しやすい。なお、図 16 (B) に示すように、第 2 の保護回路 P D 2 は、アナログ用

10

20

30

40

50

電源電圧入力端子 A V S S と表示ドライバ 10 用の電源供給線 D R V S S とを接続する。また、アナログ用電源電圧入力端子 A V S S は内部回路へ接続される。

#### 【 0 1 2 0 】

以上のことから、本実施形態では、効率よく保護回路 P D 1 をレイアウトすることができる。即ち、高速インターフェース回路 120 の方向 D R 3 での幅 S H を短くすることができる。

#### 【 0 1 2 1 】

保護回路 P D 2 は保護回路 P D 1 と同様に図 15 ( C ) に示す双方向ダイオードで構成することができる。

#### 【 0 1 2 2 】

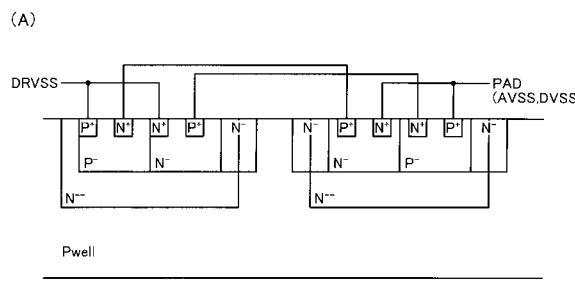

##### 3 . 2 . 3 . 第 1 、第 2 の保護回路の断面

図 17 ( A ) は、第 1 、第 2 の保護回路 P D 1 、 P D 2 の断面を示す図である。保護回路 P D 1 、 P D 2 は、図 17 ( B ) に示すように直列接続された 2 つのダイオードと、直列接続された 2 つのダイオードとを並列に接続する構成でもよい。

#### 【 0 1 2 3 】

図 17 ( A ) に示すように、ダイオードの配線は、例えば第 1 金属配線層 A L A だけ可能である。このため、例えば第 3 金属配線層 A L C に形成されている電源供給線 D R V S S 、 D R V D D 1 ~ D R V D D 3 と干渉しない。即ち、入力端子形成領域 124 のスペースを生かして配線が可能であるため、回路形成領域 122 の自由度が増し、高速インターフェース回路 120 のレイアウト縮小が可能となる。

#### 【 0 1 2 4 】

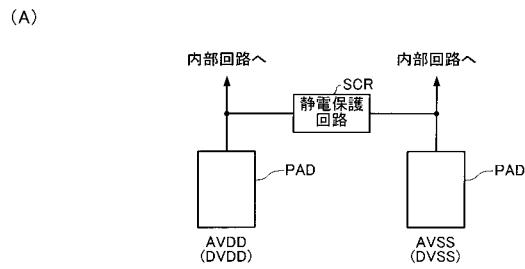

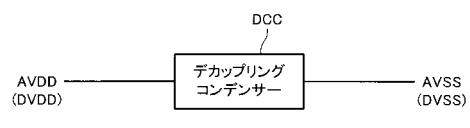

##### 3 . 3 . デカップリングコンデンサ

デカップリングコンデンサ D C C は、図 18 ( A ) に示すようにアナログ用電源電圧入力端子 A V D D ( 又はロジック用電源電圧入力端子 D V D D ) と、 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) を接続する。こうすることにより、入力端子 A V D D 、 A V S S 、 D V S S 、 D V D D に供給される電圧が一時的に不安定化したとしても、デカップリングコンデンサ D C C の働きにより安定した電源を内部回路に供給することができる。また、前述のように、デカップリングコンデンサ D C C をアナログ用とロジック用 ( デジタル用 ) とで分けることができる。

#### 【 0 1 2 5 】

また、デカップリングコンデンサ D C C は、図 9 に示すように他の回路の隙間にも設けることができるため、電源を安定化するために十分な容量を高速インターフェース回路 120 内で確保できる。

#### 【 0 1 2 6 】

例えば、表示ドライバ 10 を C O G 実装する場合、表示ドライバ 10 の外部のガラス基板上には、容量の大きなデカップリングコンデンサ D C C を形成することは困難である。また、表示ドライバ 10 においても、回路規模の縮小のため、高速インターフェース回路 120 のためのデカップリングコンデンサ D C C はほとんどの場合省略される。

#### 【 0 1 2 7 】

このような場合に対しても、本実施形態では、高速インターフェース回路 120 内に容量の大きなデカップリングコンデンサ D C C を含むため、 C O G 実装に対しても高速インターフェース回路 120 の電源の安定化を保証できる。

#### 【 0 1 2 8 】

デカップリングコンデンサ D C C は、図 18 ( B ) に示すように表示ドライバ 10 用の電源供給線 D R V S S とアナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) とを接続する。こうすることにより、入力端子 A V S S 、 D V S S に供給される電圧が一時的に不安定化したとしても、デカップリングコンデンサ D C C の働きにより安定した電源を内部回路に供給することができる。また、静電気の耐量が増えるため、電源供給線 D R V S S とアナログ用電源電圧入力端子 A V S S ( 又はロジック用電源電圧入力端子 D V S S ) との間の静電気保護素子としても機能する。そのため、図 15

10

20

30

40

50

(C)の双方向ダイオードだけを静電気保護素子として用いた場合と比べて、静電気保護機能を高くすることができます。

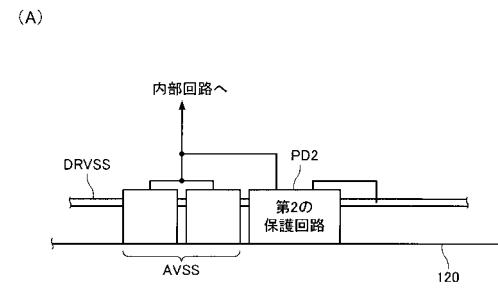

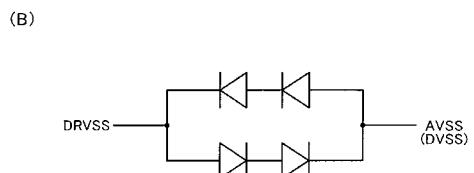

#### 【0129】

##### 4. その他の効果

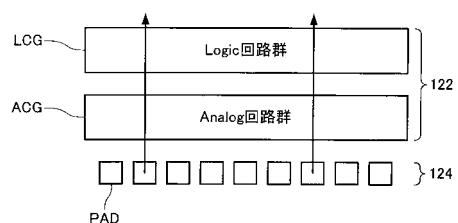

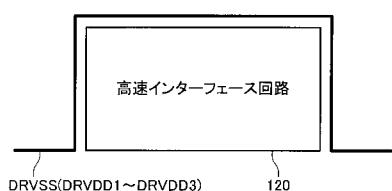

本実施形態では、図19(A)に示すように表示ドライバ10用の電源供給線DRVSS、DRVDD1～DRVDD3が入力端子形成領域124に形成されている。このため、表示ドライバ10内では、電源供給線DRVSS、DRVDD1～DRVDD3を直線的に、且つ、高速インターフェース回路120内に設けることができる。これに対して、図19(B)に示す比較例では、高速インターフェース回路120を回り込むように電源供給線DRVSS、DRVDD1～DRVDD3がレイアウトされている。このような場合、電源供給線DRVSS、DRVDD1～DRVDD3の配線長が長くなるばかりか、電源供給線DRVSS、DRVDD1～DRVDD3用に必要な配線面積を表示ドライバ10内に設けなくてはならない。このため、比較例では、図1の表示ドライバ10の短辺の幅DHを短くすることが難しくなる。

10

#### 【0130】

即ち、本実施形態では、比較例に比べて、無駄なく電源供給線DRVSS、DRVDD1～DRVDD3を配置できるため、表示ドライバ10の短辺の幅DHを短くすることが可能となる。

#### 【0131】

また、図20に示すように、本実施形態では、各入力端子PADからの信号が、回路形成領域122のアナログ回路群ACGを通り、そして、ロジック回路群LCGに流れる。即ち、信号の流れが、アナログからロジックへと直線的に自然に流れるため、特性のよい高速インターフェース回路120を得ることができる。

20

#### 【0132】

上記のように、本発明の実施例について詳細に説明したが、本発明の新規事項及び効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。したがって、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書または図面において、少なくとも一度、より広義又は同義な異なる用語と共に記載された用語は、明細書または図面のいかなる箇所においても、その異なる用語に置き換えることができる。

30

#### 【図面の簡単な説明】

##### 【0133】

【図1】本実施形態に係る表示ドライバを示す図である。

【図2】図2(A)～図2(C)は、接触抵抗の変化を説明するための図である。

【図3】本実施形態に係る表示ドライバの回路ブロック図である。

【図4】図4(A)～図4(B)は、本実施形態に係るインターフェース回路ブロックの構成例を示す図である。

【図5】図5(A)～図5(C)は、本実施形態に係るインターフェース回路ブロックの他の構成例を示す図である。

40

【図6】図6(A)～図6(C)は、入力端子形成領域と電源供給線を示す図である。

【図7】図7は、本実施形態に係るインターフェース回路ブロックの回路レイアウトの一例を示す図である。

【図8】図8(A)～図8(B)は、本実施形態に係るインターフェース回路ブロックの入力端子間領域と入力端子配置領域を示す図である。

【図9】本実施形態に係るインターフェース回路ブロックの各入力端子の配置例を示す図である。

【図10】本実施形態に係るインターフェース回路ブロックに設けられる保護回路の配置例を示す図である。

【図11】図11(A)～図11(C)は、各入力端子と保護回路との接続を示す図である。

50

【図12】本実施形態に係るインターフェース回路ブロックの入力端子と電源供給線を示す図である。

【図13】図13(A)は図12のA3-A3断面を示す断面図であり、図13(B)は図12のA4-A4断面を示す断面図である。

【図14】図14(A)～図14(B)は、保護回路の構成例を示す図である。

【図15】図15(A)～図15(C)は、各入力端子と保護回路との接続を示す他の図である。

【図16】図16(A)～図16(C)は、各入力端子と保護回路との接続を示す他の図である。

【図17】図17(A)～図17(B)は、保護回路の構成例を示す他の図である。 10

【図18】図18(A)～図18(B)は、本実施形態に係るデカップリングコンデンサの接続例を示す図である。

【図19】図19(A)は本実施形態に係るインターフェース回路ブロックを示す図であり、図19(B)は本実施形態に係る比較例を示す図である。

【図20】本実施形態に係るインターフェース回路ブロックの信号の流れを説明するための図である。

#### 【符号の説明】

##### 【0134】

10 10 表示ドライバ、120 インターフェース回路ブロック、122 回路形成領域、

124 入力端子形成領域、124-1 第1の電源入力端子形成領域、

124-2 第2の電源入力端子形成領域、124-3 差動信号入力端子形成領域、

126 ロジック回路、128 バイアス回路、DCC デカップリングコンデンサ、

D RVSS 第1の電源供給線、DRVDD1～DRVDD3 電源供給線、

D VDD、AVDD 第2の電源用入力端子、

D VSS、AVSS 第1の電源用入力端子、

DR1 第1の方向、DR2 第2の方向、DR3 第3の方向、

DM1～DM4、DP1～DP4 差動信号用入力端子、ESD 保護回路、

LS1～LS4 インターフェース回路ブロックの第1～第4の辺、

PAD 入力端子、PD1 第1の保護回路、PD2 第2の保護回路、

RX1～RX4 第1～第Sの受信回路、

SEM 半導体層、SCR、SCR1-1～SCR1-12、SCR2 保護回路

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

(B)

(C)

【図12】

【図13】

【図14】

(B)

【図15】

(C)

【図16】

【図17】

【図18】

(B)

【図19】

【図20】

(B)

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|        |       |         |

|--------|-------|---------|

| H 01 L | 21/82 | P       |

| G 09 G | 3/20  | 6 3 3 B |

| G 09 G | 3/36  |         |

| G 09 G | 3/20  | 6 1 1 J |

(74)代理人 100104710

弁理士 竹腰 昇

(72)発明者 小松 史和

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 降矢 安成

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 5C006 AA16 AA22 AF25 AF72 AF83 BB16 BC02 BC12 BF02 BF25

BF26 BF32 BF36 BF37 BF43 EB01 EB05 FA13 FA20 FA26

FA31 FA37 FA41 FA51

5C080 AA10 BB05 CC03 DD05 DD08 DD12 DD15 DD19 DD25 DD28

EE29 FF11 GG12 JJ02 JJ03 JJ04 JJ06

5F038 BE07 BH05 BH06 BH13 CA03 CA10 CD02 CD04 CD14 DF01

EZ08 EZ20

5F064 DD03 DD05 DD18 DD32 DD34 DD43 EE03 EE08 EE22 EE52

EE53