(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년11월21일

(11) 등록번호 10-0869659

(24) 등록일자 2008년11월14일

(51) Int. Cl.

*G11C 11/15* (2006.01)

(21) 출원번호 10-2003-7010125

(22) 출원일자 2003년07월31일

심사청구일자 2007년01월11일

번역문제출일자 2003년07월31일

(65) 공개번호 10-2003-0072617

(43) 공개일자 2003년09월15일

(86) 국제출원번호 PCT/US2002/000786

국제출원일자 2002년01월11일

(87) 국제공개번호 WO 2002/61755

국제공개일자 2002년08월08일

(30) 우선권주장

09/774,934 2001년01월31일 미국(US)

(56) 선행기술조사문헌

"A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell" - 2000 IEEE INTERNATIONAL SOLID-STATE CIRCUITS CONFERENCE

전체 청구항 수 : 총 4 항

심사관 : 윤진훈

(54) 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리

**(57) 요약**

컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리 셀은 차동 연결된 쌍의 MTJ들 및 MTJ들에 연결된 비교 및 매치 검출 회로를 포함하고, 차동적인 태그 비트라인들, 차동적인 태그 프로그램 비트라인들, 인에이블 라인, 워드 라인, 디지트 라인, 및 매치 라인을 포함한다. 이 매치 라인은 상기 차동적인 태그 비트라인들 상에 위치되는 입력 데이터와 상기 셀 내에 저장된 데이터 사이의 매치의 표시를 제공한다.

**대 표 도** - 도1

## 특허청구의 범위

### 청구항 1

자기 랜덤 액세스 메모리 어레이 셀에 있어서,

자기 터널 접합들의 차동 연결된 쌍; 및

상기 차동 연결된 쌍에 연결되고, 차동적인 비트라인들, 차동적인 프로그램 비트라인들, 인에이블 라인, 워드 라인, 디지트 라인 및 매치 라인을 포함하는 프로그래밍 및 검출 회로를 포함하는, 자기 랜덤 액세스 메모리 어레이 셀.

### 청구항 2

컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리 셀(content addressable magnetic random access memory cell)에 있어서,

차동 연결된 제 1 및 제 2 자기 터널 접합들; 및

상기 제 1 자기 터널 접합에 연결된 태그 비트라인 및 태그 프로그램 비트라인과, 상기 제 2 자기 터널 접합에 연결된 태그 비트라인-낫(tag bitline-not) 및 태그 프로그램 비트라인-낫(tag program bitline-not)과, 상기 제 1 및 제 2 자기 터널 접합들 둘 다에 각각 연결된 인에이블 라인, 워드 라인, 디지트 라인 및 매치 라인을 포함하는 비교 및 매치 검출 회로로서, 상기 매치 라인은 상기 제 1 및 제 2 태그 비트라인들 상에 배치된 입력 데이터와 상기 셀에 저장된 데이터 사이의 매치의 표시를 제공하는, 상기 비교 및 매치 검출 회로를 포함하는, 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리 셀.

### 청구항 3

삭제

### 청구항 4

삭제

### 청구항 5

삭제

### 청구항 6

컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리 셀에 있어서,

트랜지스터들의 제 1 직렬 연결된 쌍을 통해 제 1 접합에 연결된 제 1 사이드(side)를 갖는 제 1 자기 터널 접합 및 트랜지스터들의 제 2 직렬 연결된 쌍을 통해 제 2 접합에 연결된 제 1 사이드를 갖는 제 2 자기 터널 접합으로서, 상기 제 1 자기 터널 접합의 제 2 사이드가 프로그래밍 비트라인에 연결되고 상기 제 2 자기 터널 접합의 제 2 사이드가 프로그래밍 비트라인-낫에 연결되며, 트랜지스터들의 상기 제 1 직렬 연결된 쌍의 제 1의 제어 단자가 인에이블 라인에 연결되고 트랜지스터들의 상기 제 2 직렬 연결된 쌍의 제 1의 제어 단자가 상기 인에이블 라인에 연결되고,

상기 제 1 접합은 제 1 트랜지스터의 제어 단자가 워드 라인에 연결된 상기 제 1 트랜지스터를 통해 비트라인에 연결되고, 상기 제 2 접합은 제 2 트랜지스터의 제어 단자가 상기 워드 라인에 연결된 상기 제 2 트랜지스터를 통해 비트라인-낫에 연결되고,

상기 제 1 접합은 제 1 인에이블 트랜지스터의 제어 단자가 상기 인에이블 라인에 연결된 상기 제 1 인에이블 트랜지스터를 통해 전력 입력 단자에 연결되고, 상기 제 2 접합은 제 2 인에이블 트랜지스터의 제어 단자가 상기 인에이블 라인에 연결된 상기 제 2 인에이블 트랜지스터를 통해 전력 입력 단자에 결합되고,

상기 제 1 접합은 제 1 차동 트랜지스터의 제어 단자가 트랜지스터들의 상기 제 1 직렬 연결된 쌍의 제 2의 제어 단자와 상기 제 2 접합에 연결된 상기 제 1 차동 트랜지스터를 통해 상기 전력 입력 단자에 연결되고, 상기 제 2 접합은 제 2 차동 트랜지스터의 제어 단자가 트랜지스터들의 상기 제 2 직렬 연결된 쌍의 제 2의 제어 단

자와 상기 제 1 접합에 연결된 상기 제 2 차동 트랜지스터를 통해 상기 전력 입력 단자에 결합되는, 상기 제 1 자기 터널 접합 및 상기 제 2 자기 터널 접합; 및

상기 전력 입력 단자와 매치 라인 사이에 연결된 매치 트랜지스터들의 제 1 직렬 연결된 쌍으로서, 매치 트랜지스터들의 제 1 쌍의 제 1의 제어 단자가 상기 비트 라인에 연결되고 매치 트랜지스터들의 제 1 쌍의 제 2의 제어 단자가 제 2 접합에 연결되고,

매치 트랜지스터들의 상기 제 1 쌍의 제 1의 제어 단자가 상기 비트라인에 연결되고 매치 트랜지스터들의 상기 제 1 쌍의 제 2의 제어 단자가 상기 제 2 접합에 연결된 상기 전력 입력 단자와 매치 라인 사이에 연결된 매치 트랜지스터들의 제 1 직렬 연결된 쌍과, 매치 트랜지스터들의 제 2 쌍의 제 1의 제어 단자가 상기 비트라인-낫에 연결되고 매치 트랜지스터들의 제 2 쌍의 제 2의 제어 단자가 상기 제 1 접합에 연결된 상기 전력 입력 단자와 상기 매치 라인 사이에 연결된 매치 트랜지스터들의 제 2 직렬 연결된 쌍을 포함하는, 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리 셀.

#### 청구항 7

삭제

#### 청구항 8

삭제

#### 청구항 9

컨텐트 어드레스 가능한 비휘발성 메모리를 형성하기 위해 연결된 메모리 셀들의 어레이에 있어서,

행들과 열들로 배열된 복수의 메모리 셀들로서,

각각의 메모리 셀은 차동 연결된 쌍의 자기 터널 접합들, 태그 비트라인, 태그 비트라인-낫, 태그 프로그램 비트라인, 태그 프로그램 비트라인-낫, 인에이블 라인, 워드 라인, 디지트 라인, 및 매치 라인을 포함하고, 상기 매치 라인은 상기 태그 비트라인 및 상기 태그 비트라인-낫 상에 위치되는 입력 데이터와 상기 셀내에 저장된 데이터 사이의 매치의 표시를 제공하며,

열에서 각 메모리 셀에 대한 상기 태그 비트라인, 태그 비트라인-낫, 태그 프로그램 비트라인, 태그 프로그램 비트라인-낫, 및 인에이블 라인은 각각 상기 열에서 각각 다른 메모리 셀에 대한 상기 태그 비트라인, 태그 비트라인-낫, 태그 프로그램 비트라인, 태그 프로그램 비트라인-낫, 및 인에이블 라인에 결합되고,

행에서 각 메모리 셀에 대한 상기 워드 라인, 디지트 라인, 및 매치 라인은 상기 행에서 각각 다른 메모리 셀에 대한 상기 워드 라인, 디지트 라인, 및 매치 라인에 결합되는, 상기 복수의 메모리 셀들; 및

각 행에서의 상기 매치 라인들에 결합된 매치 검출 회로를 포함하는, 메모리 셀들의 어레이.

#### 청구항 10

삭제

#### 청구항 11

삭제

### 명세서

#### 기술분야

<1> 본 발명은 컴퓨터 메모리들에 관한 것이며, 보다 상세하게는 캐시 메모리들 및 이와 유사한 메모리들에 관한 것이다.

#### 배경기술

<2> 컴퓨터들에서, 캐시 메모리는 가장 최근에 액세스된 코드 또는 데이터를 유지하는 CPU에 인접하여 위치된 빠른 메모리이다. 데이터가 캐시에서 발견되지 않을 때 캐시 미스(miss)가 발생하고 데이터는 메인 메모리로부터 검

색되어 캐시 내에 넣어진다. 이 시간 동안 CPU는 인터럽트되고 데이터는 활용 가능할 때까지 대기 상태에 놓인다.

<3> CPU는 캐시에 저장된 워드들을 포함하는, 캐시를 검사하기 위해 캐시 내에 어드레스를 보낸다. 각 셀에 저장된 데이터는 통상 "태그(tag)"로 불리고, 태그 워드는 태그들 또는 메모리 셀들의 행(row)에 의해 형성된다. CPU에 의해 어드레싱되는 워드가 캐시에서 발견되면, 그것은 캐시로부터 판독된다. 발견되지 않으면, 메인 메모리는 워드를 읽기 위해 어드레싱된다. 막 액세스된 워드를 포함하는 워드들의 블록은 그후 메인 메모리로부터 캐시로 옮겨진다.

<4> 캐시 메모리는 CPU로부터 어드레스들을 수신하고 캐시 내에 저장된 어드레스들을 찾아 비교를 수행한다. 고속으로 이러한 비교를 병렬로 수행하기 위해, 연관(associative) 또는 컨텐트 어드레스 가능한 메모리(CAM)가 요구된다. 메모리 내의 정보를 액세스하기 위한 시간은, 저장된 데이터가 어드레스보다는 컨텐츠에 의해 식별될 수 있다면, 격감될 수 있다. CAM들 또는 연관 메모리들은 캐시 메모리들 및 변환 참조 버퍼들(translation look-asides buffers ; TLB)에서 확장적으로 사용된다. 일반적으로, CAM들은 물리적 어드레스들을 데이터로 변환하기 위해 캐시들에 사용되고, TLB들에서는 가상 어드레스들을 물리적 어드레스들로 변환하기 위해 사용된다. CAM들은 연관 데이터 처리에 대한 매우 강력한 도구이다.

<5> 일반적으로, 캐시 메모리는 메인 메모리보다 5-10 인자(factor) 더 빨라야 하기 때문에 속도가 캐시 메모리들에서 중요하다. 지금까지, 단지 SRAM들만이 캐시 메모리를 등에 필요한 속도를 가지고 있다.

### 발명의 상세한 설명

<6> 종래 기술에서, 대부분의 캐시 메모리들은 SRAM들의 어레이로 구성된다. 메모리 셀들의 SRAM 타입은 요구되는 속도를 가지지만 이들은 휘발성 메모리들이다. 종래의 기술에서, SRAM 셀들은 주변 또는 그렇지 않으면 어레이의 외부에 위치된 모든 비교 및 매치 검출 회로를 갖는 어레이에 형성된다. 또한 SRAM 기반의 CAM들은 SRAM은 셀에서 턴오프(turn off)될 수 없지만 마스킹이 주변에 배치되어야하며, 이것은 전력 낭비의 결과가 된다. 또한, 상이한 메모리 셀들은 일반적으로 메인 메모리에 사용되어 캐시 메모리 및 메인 메모리가 상이한 처리 및 제조 단계들을 요구하도록 한다.

<7> 따라서, 이러한 문제들을 극복하는 캐시 메모리를 제공하는 것이 매우 바람직하다.

### 실시 예

#### 양호한 실시예의 상세한 설명

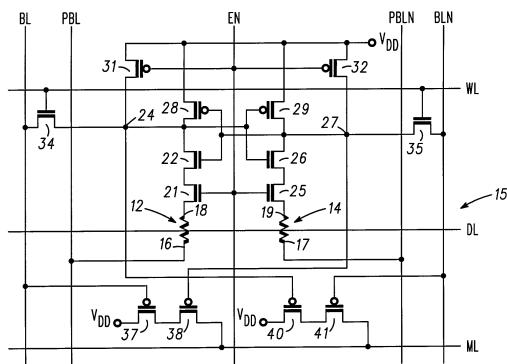

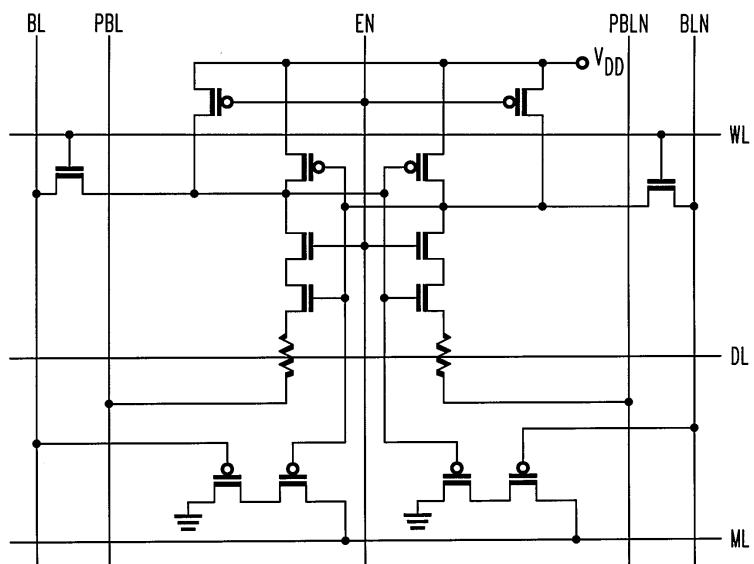

<14> 이제 도 1로 돌아가서, 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리 셀(10)이 본 발명에 따라 도시된다. 셀(10)은 자기 터널 접합들(magnetic tunnel junctions: MTJs)(12 및 14)의 차동 연결된 쌍을 포함한다. MTJ는 이것을 회로 내에 연결함으로써 사용되어 전기가 하나의 자기층으로부터 다른 층으로 MTJ를 형성하는 층들의 스택을 통해 수직적으로 흐르도록 한다. MTJ는 저항기로서 전기적으로 나타낼 수 있고 저항의 크기는 두 개의 안정된 상태들 중 어느 상태의 두 자기 벡터들의 방위에 따른다. 당업자에 의해 이해되는 바와 같이, MTJ는 자기 벡터들이 잘못 정렬될 때(반대 방향들의 포인트) 상대적으로 높은 저항을 갖고 자기 벡터들이 정렬될 때 상대적으로 낮은 저항을 갖는다. MTJ들은 당 기술분야에 잘 알려져 있으며, 여기서는 상세히 논하지 않을 것이다. 그러나, MTJ들의 제조 및 동작에 관한 부가적인 정보는 본 명세서에 참조로서 통합된 1998년 3월 31일 발행된 발명의 명칭이 "다층 자기 터널링 접합 메모리 셀들"인 특허 번호 5,702,831에서 발견될 수 있다.

<15> 또한, 셀(10)은 MTJ들(12 및 14)의 차동 연결된 쌍에 연결된 비교 및 매치 검출 회로(15)를 포함한다. 회로(15)는 BL 및 BLN(비트라인-낫; bitline-not)으로 지정된 차동 태그 비트라인들, PBL 및 PBLN으로 지정된 차동 태그 프로그램 비트라인들, EN으로 지정된 인에이블 라인, WL로 지정된 워드 라인, DL로 지정된 디지트 라인, 및 ML로 지정된 매치 라인을 포함하고, 매치 라인은 차동 태그 비트라인들 상에 위치된 입력 데이터 및 셀 내에 저장된 데이터 사이의 매치의 지시를 제공한다.

<16> 보다 상세하게는, MTJ(12)의 하부 단자(16)(도 1)는 태그 프로그램 비트라인(PBL)에 직접 연결되고 MTJ(14)의 하부 단자(17)(도 1)는 태그 프로그램 비트라인-낫(PBLN)에 직접 연결된다. 곧 더욱 상세히 설명될 이유들 때문에, MTJ들(12 및 14)의 하부 단자들(16 및 17)은 MTJ들을 형성하는 층들의 스택들의 꼭대기에 있고 상부 단자들(18 및 19)은 각각 스택의 바닥에 있다. MTJ(12)의 상부 단자(18)는 제 1 스위칭 트랜지스터(21) 및 제 2 스위칭 트랜지스터(22)를 통해 접합(24)에 연결된다. MTJ(14)의 상부 단자(19)는 제 1 스위칭 트랜지스터(25) 및 제

2 스위칭 트랜지스터(26)를 통해 접합(27)에 연결된다. 스위칭 트랜지스터들(21 및 25)의 제어 단자들 또는 게이트들은 인에이블 라인(EN)에 직접 연결된다. 스위칭 트랜지스터(22)의 게이트는 접합(27)에 직접 연결되고, 스위칭 트랜지스터(26)의 게이트는 접합(24)에 직접 연결된다.

<18> 스위칭 트랜지스터(28)는 Vdd로 지정된 전원과 접합(24) 사이에 연결되고 스위칭 트랜지스터(29)는 전원(Vdd)과 접합(27) 사이에 연결된다. 스위칭 트랜지스터(28)의 제어 단자 또는 게이트는 접합(27)에 직접 연결되고, 스위칭 트랜지스터(29)의 제어 단자 또는 게이트는 접합(24)에 직접 연결된다. 한쌍의 스위칭 트랜지스터(31 및 32)는 전원(Vdd)과 접합들(24 및 27) 사이에 각각 연결된다. 스위칭 트랜지스터(31 및 32)의 제어 단자들 또는 게이트들 모두는 인에이블 라인(EN)에 직접 연결된다.

<19> 제어 단자 또는 게이트가 워드라인(WL)에 직접 연결되면서 스위칭 트랜지스터(34)는 태그 비트라인(BL)과 접점(24) 사이에 연결된다. 제어 단자 또는 게이트가 워드라인(WL)에 직접 연결되면서 스위칭 트랜지스터(35)는 태그 비트라인-낫(BLN)과 접합(27) 사이에 연결된다. 한쌍의 직렬로 연결된 스위칭 트랜지스터들(37 및 38)은 전원(Vdd)과 매치 라인(ML) 사이에 연결된다. 트랜지스터(37)의 제어 단자 또는 게이트는 태그 비트라인(BL)에 직접 연결되고 트랜지스터(38)의 제어 단자 또는 게이트는 접합(27)에 직접 연결된다. 또 다른 한쌍의 직렬로 연결된 스위칭 트랜지스터들(40 및 41)은 전원(Vdd)과 매치 라인(ML) 사이에 연결된다. 트랜지스터(40)의 제어 단자 또는 게이트는 접합(24)에 직접 연결되고 트랜지스터(41)의 제어 단자 또는 게이트는 태그 비트라인-낫(BLN)에 직접 연결된다.

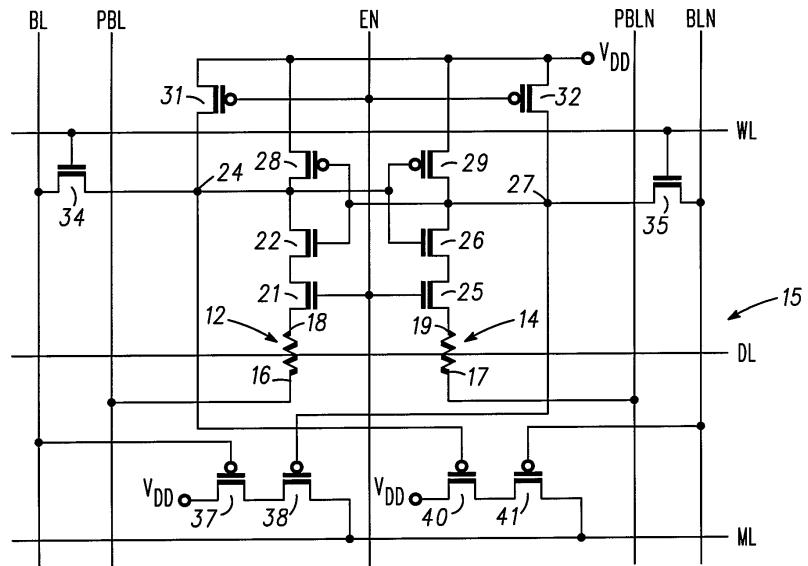

<20> 부가적으로 도 2를 참조하면, MTJ들(12 및 14)은 잘 알려진 방식으로 조립된 자기 물질의 층들의 스택들, 절연물질, 및 비-자기 전도체들로서 도시된다. 비교 및 매치 검출 회로(15)는 일반적으로 MTJ들(12 및 14) 아래에 지원 반도체 기판(도시되지 않음)의 표면 상에 그리고 그 안에 형성된다. MTJ(12)는 회로(15) 위의 층에 위치되고 비아(46)를 통해 스위칭 트랜지스터(21)에 연결되는 전도성 물질(45)의 바닥층을 포함한다. MTJ(14)는 회로(15) 위의 층에 위치되고 비아(48)를 통해 스위칭 트랜지스터(25)에 연결되는 전도성 물질(47)의 바닥층(일반적으로 물질(45)과 같은 층으로부터 형성됨)을 포함한다.

<21> 디지트 라인(DL)은 두 MTJ들(12 및 14)의 아래에 확장하도록 형성되고 충분히 접(close)하여 MTJ들(12 및 14)에 부분적 프로그래밍 자기 필드를 생성하도록 한다. 태그 프로그래밍 비트라인(PBL)은 MTJ(12)위에 위치되고, 충분히 접하여 MTJ(12)내에 부분적 프로그래밍 자기 필드를 생성하도록 하고, 디지트 라인(DL)에 수직으로 방위를 맞춘다. 유사하게, 태그 프로그래밍 비트라인-낫(PBLN)은 MTJ(14)위에 위치되고, 충분히 접촉하여 MTJ(12)에 부분적 프로그래밍 자기 필드를 생성하고, 디지트 라인(DL)에 수직으로 방위를 맞춘다. 그러므로, 디지트 라인(DL), 태그 프로그래밍 비트라인(PBL) 및 태그 프로그래밍 비트라인-낫(PBLN)은 메모리의 프로그래밍 동안 각각의 개별 셀을 어드레싱하도록 사용된다.

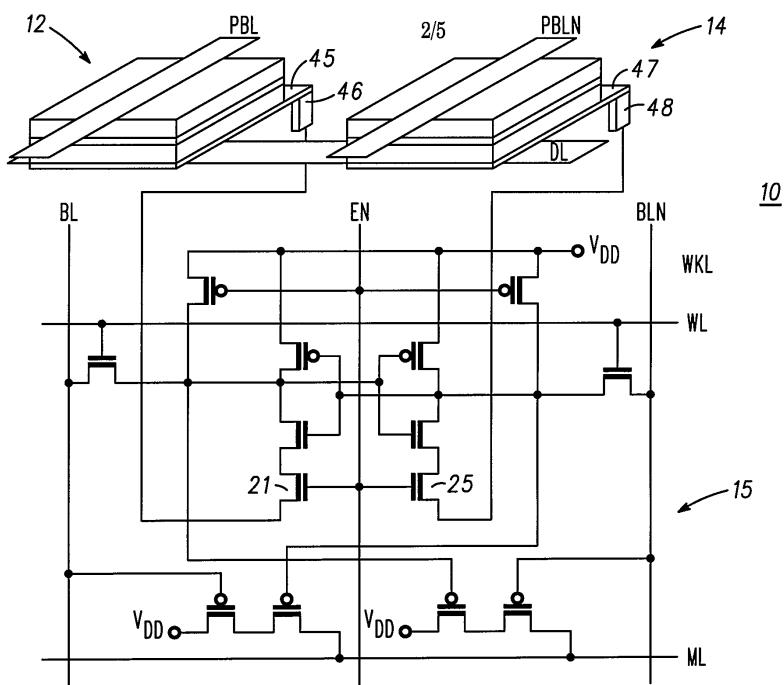

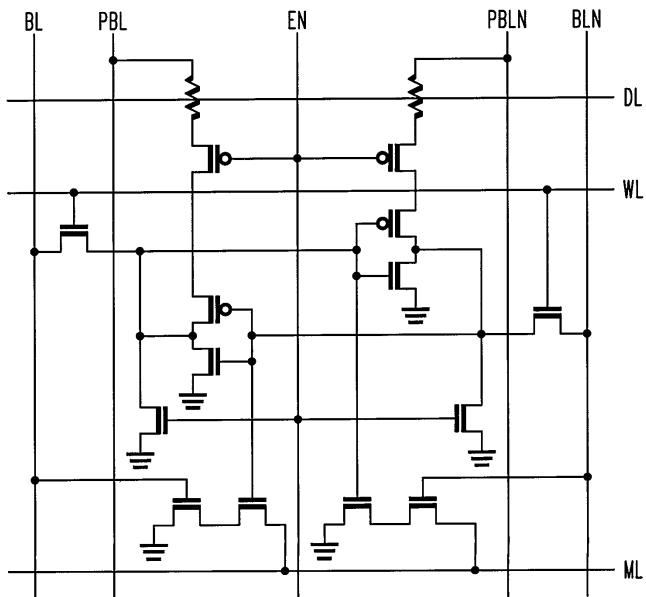

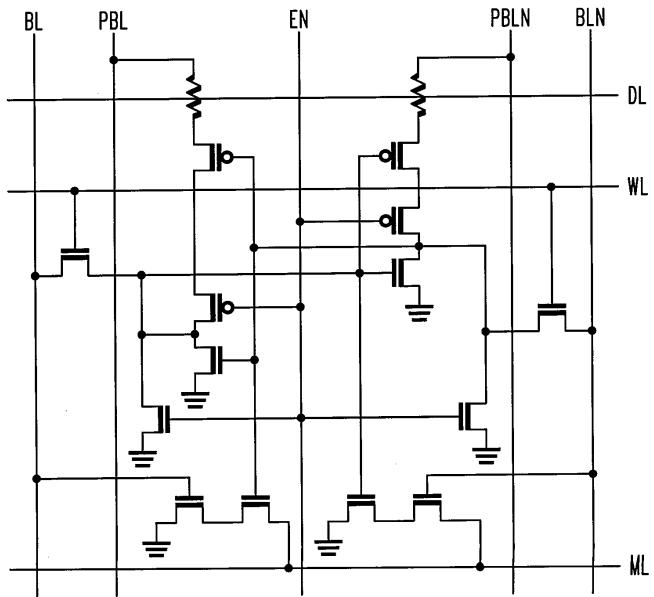

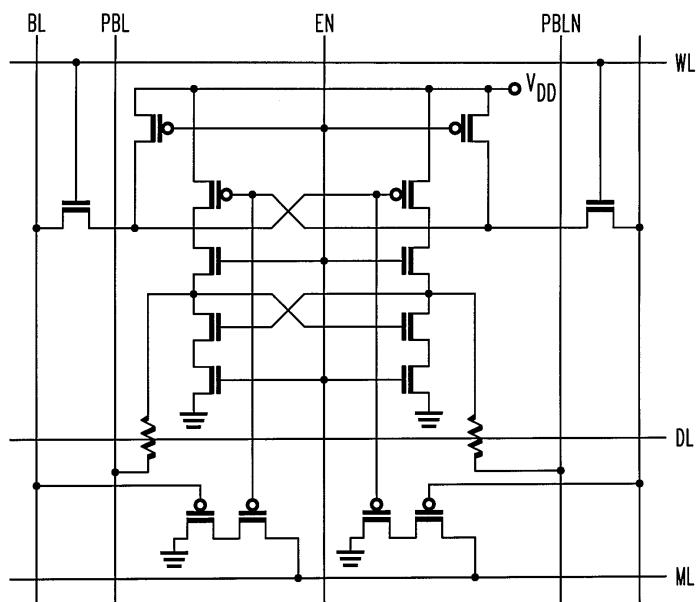

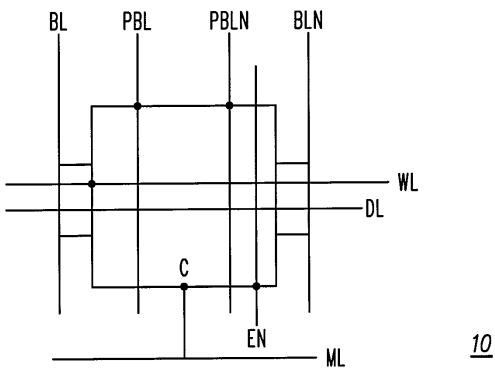

<22> 도 3, 4, 5 및 6을 참조하면, 몇몇의 부가적인 실시예들이 본 발명에 따른 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리들(CAMRAM들)에 대해 도시된다. 다양한 실시예들은 상이한 전도 트랜지스터들(예를 들어, N-전도와 P-전도) 및 다양한 구성 요소들의 상이한 위치들과 같은, 연결 회로에서의 전위 변화들을 도시한다. CAMRAM 셀(10)의 매크로 뷰 또는 다른 셀 실시예들 중 임의의 것이 다양한 I/O 연결들을 보여주는 도 7에 도시된다.

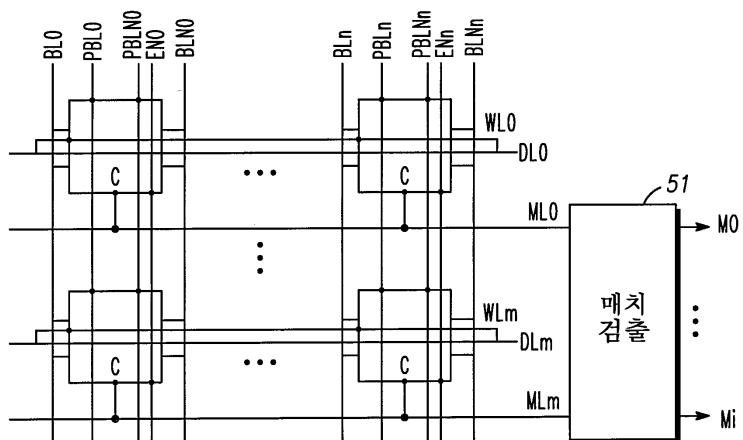

<23> 이제 도 8로 돌아가면, 도 7의 셀(10)과 각각 유사한 CAMRAM 셀들의 어레이(50)가 도시된다. 어레이의 CAMRAM 셀들은 행들과 열들로 배열되는데, 각 행에는 n 셀들이 그리고 각 열에는 m 셀들이 있고, 여기서 n과 m은 임의의 전체 정수를 나타낸다. 어레이 내의 셀들의 각각은 열들을 따라 확장하는 태그 비트라인들 및 태그 비트라인들-낫(각각 BL0-BLn 및 BLN0-BLNn으로 지정됨), 및 인에이블 라인들(EN0-ENn으로 지정됨)과, 행들을 따라 확장하는 워드 라인들(WL0-WLm으로 지정됨), 디지트 라인들(DL0-DLm으로 지정됨) 및 매치 라인들(ML0-MLm으로 지정됨)에 의해 연결된다. 매치 라인들(ML0-MLm)은 매치 라인들 중 임의의 것에 대한 매치를 검출하고 매치 신호(M0-Mi로 지정됨)를 출력하는 매치 검출 회로(51)에 결합된다.

<24> 보완 정보(complementary information)가 도 1을 다시 참조하여 다음의 처리에 의해 어레이(50)의 셀들의 각각으로 프로그램된다. 인에이블 라인에 논리(0)를 인가하여(EN=0) 셀이 프로그램되는 것을 디스에이블한다. 디스에이블되는 시간동안, 접합들(24 및 27)은 Vdd에서 유지될 것이고, 이것은 프로그램 동작 직후에 발생하는 팬독 및 검색 모드들로의 빠른 전이(transition)에 중요하다. 동시에, 워드 라인은 논리(0)를 인가함으로써(WL=0) 디스에이블 된다. 고속 프로그래밍을 위해 프로그램 비트라인들의 쌍(PBL 및 PBLN) 또는 프로그램 비트라인들의 모든 쌍들을 선택하고 하나의 디지트 라인(DL)을 선택한다. 선택된 프로그램 비트라인들(PBL 및 PBLN) 및 선택된 디지트 라인(DL)을 통해 적절한 전류를 통과시킴으로써, 특정 행을 따르는 선택된 셀이 프로그램될 것이다. 예를 들어, PBL0 및 PBLN0을 선택하는 것은 셀들의 제 1 열을 선택한다. DL0을 선택하는 것은 제 1 열에서의 제

1 셀을 선택한다. 라인들(PBL0, PBLN0, 및 DL0)에 인가된 적절한 전류들은 그후 원하는 보완 정보로 제 1 열 내의 제 1 셀을 프로그램한다.

<25> 검색 모드에서, 다음의 처리가 수행된다. 선택된 인에이블 라인에 논리(1)를 인가함으로써(EN=1) 디스에이블 상태(EN=0)로부터 인에이블 라인을 올리면서, 어레이(50)에서의 셀들의 선택된 열을 인에이블한다. 동시에, 워드 라인을 디스에이블 한다(WL=0). 셀이 디스에이블될 때(EN=0), 매치 라인(ML)은 접지까지 미리 충전되어야 한다. 태그 비트라인들(PBL 및 PBLN)을 접지시킨다. 일단 셀이 인에이블되고 태그 비트라인들이 접지되면, 트랜지스터들(28, 22, 21) 및 MTJ(12)와 트랜지스터들(29, 26, 25) 및 MTJ(14)에 의해 전개되는 재생적인 +Vc 피드백은 Vdd에서의 접합(24)을 유지할 것이고, 접지에 가까운 전압으로 접합(27)을 끌어당길 것이다, 또는 그 역으로, 이것은 접합(27)을 Vdd에 유지시킬 것이고 접합(24)을 그라운드에 가까운 전압으로 끌어당길 것이다. 접합들(24 및 27)에서의 전압들은 각각 트랜지스터들(40 및 38)의 게이트들에 나타난다. 그러므로, 트랜지스터들(40 및 41) 또는 트랜지스터들(37 및 38)의 어느 하나가 태그 비트라인(BL 및 BLN) 상의 입력 어드레스에 따라 매치 라인(ML)을 풀업할 것이다.

<26> 이제 어레이(50)가 검색을 시작할 준비가 된다. 결과로서, 인에이블 라인은 하이(high)로 설정되고 고속 병렬 검색이 시작될 수 있다. 입력 워드(BL<sub>0</sub>...BL<sub>n</sub>)가 어레이(50)의 하나의 행의 어레이에 저장된 데이터와 비교된다.

각 CAMRAM 셀(10)에 저장된 데이터는 "태그"로 알려져 있으며, 태그 워드는 하나의 행의 CAMRAM 셀들(10)에 의해 형성된다. CAMRAM 셀들(10)의 각 행 또는 각 태그 워드는 매치 라인(ML<sub>0</sub>...ML<sub>n</sub>)에 연결된다. 태그 워드의 임의의 비트 내에 미스매치가 있다면, 대응하는 매치 라인은 내려진다. 태그 워드에서의 모든 비트들이 입력 워드와 매치되면, 대응하는 매치 라인은 하이로 유지한다. 매치 검출 회로(51)는 매치 라인들의 전이들을 검출하고 그 결과를 레지스터에 저장한다. 여기서 "마스킹된 문의 비트 포지션(masked interrogate bit position)"으로 인용되는, 어레이(50)에서의 하나 이상의 비트들의 마스킹은 원하는 비트들의 인에이블 라인을 로우(low)로 끌어당김으로써 쉽게 성취된다. 로우 인에이블 라인을 갖는 비트들은 대응하는 열을 따라 CAMRAM 셀들을 턴오프할 것이고, 따라서 로컬 마스킹과 전력 절약을 제공한다.

<27> 판독 모드의 동작에서, CAMRAM은 랜덤 액세스 메모리로 사용될 수 있거나, 또는 순차적으로 액세스되도록 설계될 수 있다. 판독 모드 동작은 다음과 같다. 인에이블 라인이 디스에이블될 때(EN=0), 태그 비트라인들(BL 및 BLN)을 Vdd로 미리 충전한다. 접합(24 및 27) 및 비트라인들(BL 및 BLN)은 Vdd에 있을 것이다. 프로그래밍 비트 라인들(PBL 및 PBLN)을 접지시킨다. 매치 검출 회로(51)를 디스에이블하는 것은 판독 동작 동안 태그 비트라인들(BL 및 BLN)이 트랜지스터들(37 및 41)을 턴온 또는 턴오프할 논리 하이 또는 논리 로우를 가정하기 때문에, 따라서 매치 라인(ML)을 움직이게 한다. 랜덤 액세스 동안 매치 검출 회로(51)를 디스에이블하는 것은 매치 검출 회로(51)의 불필요한 전이를 방지할 것이다. 워드 라인(WL)을 인에이블하고(WL=1) 선택된 셀을 인에이블(EN=1) 한다. MTJ들(12 및 14)의 상태에 따라, 접합들(24 및 27)은 Vdd에 있거나 그라운드 보다 약간 높은 전압에 있을 것이다. 접합(24 또는 27)이 Vdd에 있다면, 태그 비트라인(BL 또는 BLN)은 각각 Vdd에 머무를 것이다. 그러나, 접합(24 또는 27)이 그라운드보다 약간 위의 전압에 있다면, 태그 비트라인(BL 또는 BLN)은 각각 그라운드쪽으로 풀 다운될 것이며, 이 때 고속 센스 증폭기(도시되지 않음)가 고속에서 차동적으로 태그 비트라인들(BL 및 BLN)에서의 전압을 감지하고, 감지된 데이터를 출력할 것이다. 여기서 스캐닝 메커니즘이 전압 또는 전류 모드의 하나에 있을 수 있다는 것이 이해될 것이다.

<28> 양호하게는, 트랜지스터들(21, 22 및 28) 및 트랜지스터들(25, 26 및 29)과 MTJ들(12 및 14)의 저항들은 MTJ들(12 및 14) 전역의 전압이 약 10mV 내지 400mV의 범위에 있도록 선택된다. 이 범위에서 최대 MR(최대 저항과 최소 저항 사이의 비율)이 이루어질 수 있다. 일반적으로, MTJ들(12 및 14)에서의 전압이 더 낮아질수록 MR은 더 높아지고 전류 소비는 더 낮아진다.

<29> 단일 MTJ 셀들이 처리, 바이어스 전압 변화들, 온도 등에 기인하여 저항 변화들을 겪기 때문에, 이를 변화들을 계산하는 것은 속도 저하를 초래할 것이다. 그러나, 여기에 설명된 CAMRAM 셀에서와 같은 차동 방식으로 프로그램된 이중 MTJ 셀에서, 그러한 모든 변화들은 공통 모드이며 자동적으로 제거된다. 또한, 활용 가능한 출력 신호가 이중 MTJ들과 차동 동작에 의해 두배가 된다. 또한, 단일 MTJ 셀들이 메모리 어레이의 끝들에서 데이터 감지 및 처리를 하는 메인 메모리 내에 사용되는 경우(예를 들어, 일련 번호를 갖고, 동일한 양수인에게 양도된 2000년에 출원된 발명의 명칭이 "HIGH DENSITY MRAM CELL ARRAY(고밀도 엠패 셀 어레이)"인 공동 계류 중인 출원을 참조), CAMRAM은 메인 메모리보다 훨씬 더 빠르다.

<30> 또한 여기서, CAMRAM 셀들이 셀에서 정보의 분실없이 셀에 국부적으로 마스킹될 수 있는 반면, SRAM들에 기초한 CAM 셀들은 그것들이 셀에서 턴오프될 수 없고, 마스킹이 어레이의 주변에서 발생해야 하기 때문에 마스킹될 수

없다는 것을 유념해야 한다. CAMRAM 셀들의 국부적 마스킹은 실질적인 전력 절약의 결과가 될 것이다. CAMRAM 셀들은 셀들의 열을 연결하는 인에이블 라인(EN)에 연결된 셀의 인에이블 라인(EN) 입력을 통해 마스킹된다. 또한, CAMRAM 셀들은 고밀도 MRAM들에 사용된 표준 MTJ 구조로부터 임의의 이탈을 요구하지 않는다(위에 보이는 공동 계류중인 출원을 보라).

- <31> 그러므로, 적어도 SRAM 기반 메모리만큼 빠르고 비휘발성인 새롭고 개선된 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리 셀이 개시된다. 또한, 비트라인 전압은 검색동안 매치들 또는 미스매치들이 발견되든지 상대적으로 일정하게 남는다. 각 셀의 차동적 동작 때문에, 처리, 바이어스 전압 변화들, 온도 등에 기인하는 저항 변화들이 자동적으로 제거될 것이고 동작 동안 속도가 희생되지 않는다. 또한, 차동적인 동작은 더욱 효율적인 감지 및 동작을 위해 더 큰 출력 신호들을 제공한다.

- <32> CAMRAM 셀들의 비휘발성 때문에, 새로운 캐시 설계들이 발생할 것이고 새로운 CPU 구조가 나올 것이다. 고속 검색 엔진들이 새로운 CAMRAM 셀들을 사용하여 설계될 수 있어서, 연관 데이터 처리를 위한 수많은 시스템들 및 애플리케이션들이 나올 것이다.

- <33> 비트라인이 일반적으로 MTJ 셀들의 어레이의 각 열과 관련되고 디지트 라인이 그 어레이의 각 행과 관련된다는 것이 이 기술분야의 당업자들에게 이해될 것이다. 비트라인들 및 디지트 라인들은 어레이에서의 정보를 저장하거나 판독 및 프로그래밍 모두를 위해 어레이 내의 개별 셀들을 어드레싱하는데 사용된다. 당업자들에 의해 이해될 수 있는 바와 같이, 열들과 행들은 쉽게 상호 변경될 수 있고 그러한 용어들이 상호 변경될 수 있음을 본원의 공개에서 의도된다. 또한, 예를 들어 비트라인, 워드 라인, 디지트 라인, 선택 라인, 등의 다양한 라인들의 특정 이름들은 단지 설명을 용이하게 하기 위해서 사용되는 총칭적인 이름들인 것으로 의도되며 본 발명을 제한하기 위한 어떤 방식으로 의도된 것이 아니다.

- <34> 본인이 본 발명의 특정 실시예들을 도시하고 설명하는 동안, 추가적인 변경들과 개선들이 당업자들에게 발생할 것이다. 그러므로, 본 발명은 도시된 특정 형식들에 제한되지 않음을 이해하기 바라며, 첨부된 청구항들에서 본 발명의 사상과 범위를 벗어나지 않는 모든 변경들을 커버하도록 의도한다.

### 도면의 간단한 설명

- <8> 도면들을 참조하면,

- <9> 도 1은 본 발명에 따른 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리(CAMRAM)의 개략도이다.

- <10> 도 2는 도 1의 CAMRAM의 부분적인 같은 크기의 부분 개략도이다.

- <11> 도 3,4,5, 및 6은 본 발명에 따른 컨텐트 어드레스 가능한 자기 랜덤 액세스 메모리(CAMRAM)의 부가적인 실시예들을 도시한다.

- <12> 도 7은 다양한 I/O 연결들을 도시하는 CAMRAM 셀 매크로 뷰이다.

- <13> 도 8은 CAMRAM 셀들의 어레이를 도시한다.

## 도면

## 도면1

10

## 도면2

도면3

도면4

도면5

도면6

## 도면7

## 도면8

50