**【特許請求の範囲】****【請求項 1】**

複数の端子を有する半導体素子と、この半導体素子の1つの端子にバイアス電圧を供給するバイアス電源回路とを具備した半導体素子用バイアス回路において、前記1つの端子と前記バイアス電源回路とを結ぶ中間点の電圧が所定値を越えた場合に、前記中間点の電圧の上昇を停止させる保護回路を設けたことを特徴とする半導体素子用バイアス回路。

**【請求項 2】**

複数の端子を有する半導体素子と、この半導体素子の1つの端子にバイアス電圧を供給するバイアス電源回路とを具備した半導体素子用バイアス回路において、前記1つの端子と前記バイアス電源回路とを結ぶ中間点の電圧が所定値よりも低下した場合に、前記中間点の電圧の降下を停止させる保護回路を設けたことを特徴とする半導体素子用バイアス回路。

10

**【請求項 3】**

複数の端子を有する半導体素子と、この半導体素子の1つの端子にバイアス電圧を供給するバイアス電源回路とを具備した半導体素子用バイアス回路において、前記1つの端子と前記バイアス電源回路とを結ぶ中間点に接続し、前記中間点の電圧が所定値よりも大きい場合に導通状態となる回路素子を有する保護回路を設けたことを特徴とする半導体素子用バイアス回路。

**【請求項 4】**

複数の端子を有する半導体素子と、この半導体素子の1つの端子にバイアス電圧を供給するバイアス電源回路とを具備した半導体素子用バイアス回路において、前記1つの端子と前記バイアス電源回路とを結ぶ中間点に接続し、前記中間点の電圧が所定値よりも小さい場合に導通状態となる回路素子を有する保護回路を設けたことを特徴とする半導体素子用バイアス回路。

20

**【請求項 5】**

複数の端子を有する半導体素子と、この半導体素子の1つの端子にバイアス電圧を供給するバイアス電源回路とを具備した半導体素子用バイアス回路において、前記1つの端子と前記負電圧供給回路とを結ぶ中間点に接続し、かつ、前記中間点の電圧が第1所定値よりも大きい場合に導通状態となる第1回路素子および前記中間点の電圧が第2所定値よりも小さい場合に導通状態となる第2回路素子を有する保護回路を設けたことを特徴とする半導体素子用バイアス回路。

30

**【請求項 6】**

半導体素子が電界効果トランジスタで、1つの端子がゲート端子である請求項1ないし請求項5のいずれか1つに記載の半導体素子用バイアス回路。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は半導体素子にバイアス電圧を供給する半導体素子用バイアス回路に関する。

**【0002】****【従来の技術】**

半導体素子たとえば電界効果トランジスタ（以下FETという）は高周波信号を増幅する増幅素子などとして使用され、動作時、バイアス回路から出力されるバイアス電圧がゲート端子などに印加される。

40

**【0003】**

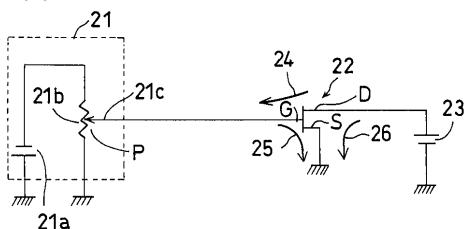

ここで、従来の半導体素子用バイアス回路について、半導体素子がFETの場合を例にとり図2のDC等価回路図を参照して説明する。バイアス電源回路21は、負電圧を出力する定電圧電源21aおよび出力抵抗21b、出力抵抗21b上を移動する出力端子21cなどから構成されている。バイアス電源回路21の一端たとえば定電圧電源21aの正側端子は接地され、出力端子21cはFET22のゲート端子Gに接続されている。FET22はゲート端子Gおよびドレイン端子D、ソース端子Sを有し、ドレイン端子Dは定電

50

圧電源 2 3 の正側端子に接続され、ソース端子 S は接地に接続されている。

【 0 0 0 4 】

上記した構成において、F E T の動作時、バイアス電源回路 2 1 から F E T 2 のゲート端子 G に所定大きさの負のバイアス電圧が供給され、また、定電圧電源 2 3 から F E T 2 2 のドレイン端子 D に正のバイアス電圧が供給される。

【 0 0 0 5 】

上記した半導体素子用バイアス回路に関する技術は特許文献 1 などにも記載されている。

【 0 0 0 6 】

【 特許文献 1 】

特開平 8 - 2 2 2 9 6 7 号公報

10

【 0 0 0 7 】

【 発明が解決しようとする課題 】

F E T 2 2 の動作時、ゲート端子 G に入力する交流信号のレベルが F E T 2 2 の飽和出力よりも十分に小さい場合、F E T 2 2 のゲート・ソース間の電圧はほとんど問題にならない。しかし、ゲート端子 G に入力する交流信号のレベルが F E T 2 2 の飽和出力に近づくと、F E T 2 2 のゲート・ドレイン間に矢印で示す逆方向の整流電流 2 4 が流れる。また、ゲート・ソース間に矢印で示す順方向の整流電流 2 5 が流れる。

【 0 0 0 8 】

ゲート・ドレイン間に逆方向の整流電流 2 4 が流れると、その整流電流 2 4 が出力抵抗 2 1 b に流れ、出力抵抗 2 1 b と出力端子 2 1 c との接触点 P の電位が上昇する。このとき、ゲート・ソース間電圧はたとえば 0 V に近くなり、ドレイン・ソース間に矢印方向に流れるドレイン・ソース間電流 2 6 が増加する。その結果、F E T 2 2 が熱的に焼損し破壊する場合がある。

【 0 0 0 9 】

また、ゲート・ソース間に順方向の整流電流 2 5 が流れると、接触点 P の電位が低下し、ゲート・ドレイン間の電圧が大きくなり、ゲート・ドレイン間に耐圧破壊が発生する場合がある。

【 0 0 1 0 】

上記した問題を解決するために、出力抵抗 2 1 b の抵抗値を小さくし、ゲート・ドレイン間やゲート・ソース間の電圧変動を小さくする方法がある。しかし、この方法は、F E T 2 2 のゲート端子 G の入力抵抗が高いため、ゲート端子 G に入力する交流信号のレベルが F E T 2 2 の飽和出力よりも十分に小さい場合でも、出力抵抗 2 1 b に流れる電流が大きくなり、バイアス電源回路 2 1 の電源効率が低下するという問題がある。

【 0 0 1 1 】

本発明は、上記した欠点を解決し、半導体素子の破壊を防止する半導体素子用バイアス回路を提供することを目的とする。

【 0 0 1 2 】

【 課題を解決するための手段 】

本発明は、複数の端子を有する半導体素子と、この半導体素子の 1 つの端子にバイアス電圧を供給するバイアス電源回路とを具備した半導体素子用バイアス回路において、前記 1 つの端子と前記バイアス電源回路とを結ぶ中間点の電圧が所定値を越えた場合に、前記中間点の電圧の上昇を停止させる保護回路を設けたことを特徴とする。

【 0 0 1 3 】

【 発明の実施の形態 】

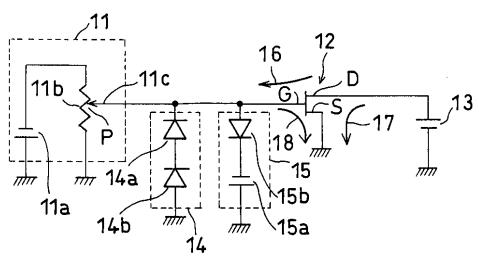

本発明の実施形態について図 1 の D C 等価回路図を参照して説明する。

【 0 0 1 4 】

バイアス電源回路 1 1 は、負電圧を出力する定電圧電源 1 1 a および出力抵抗 1 1 b 、出力抵抗 1 1 b 上を移動する出力端子 1 1 c などから構成されている。バイアス電源回路 1 1 の一端たとえば定電圧電源 1 1 a の正側端子は接地され、他端たとえば出力端子 1 1 c

40

50

は F E T 1 2 のゲート端子 G に接続されている。F E T 1 2 はゲート端子 G およびドレイン端子 D、ソース端子 S を有し、ドレイン端子 D は定電圧電源 1 3 の正側端子に接続され、ソース端子 S は接地に接続されている。

【 0 0 1 5 】

バイアス電源回路 1 1 と F E T 1 2 のゲート端子 G とを結ぶ線路の中間点、たとえば第 1 中間点 C 1 に第 1 保護回路 1 4 が接続され、もう 1 つのたとえば第 2 中間点 C 2 に第 2 保護回路 1 5 が接続されている。

【 0 0 1 6 】

第 1 保護回路 1 4 は、たとえば直列に接続する 2 つのダイオード 1 4 a、1 4 b から構成されている。中間点 C 1 側に位置するダイオード 1 4 a のカソード端子が中間点 C 1 接続され、中間点 C 1 から遠い側に位置するダイオード 1 4 b のアノード端子が所定の第 1 電位点たとえば接地に接続されている。

【 0 0 1 7 】

第 2 保護回路 1 5 は、所定の第 2 電位点を形成するたとえば - 1 V の負の電圧を発生する定電圧電源 1 5 a およびダイオード 1 5 b から構成されている。中間点 C 2 側に位置するダイオード 1 5 b のアノード端子は中間点 C 2 に接続され、カソード端子は所定の第 2 電位点を形成している定電圧電源 1 5 a の負側端子に接続されている。定電圧電源 1 5 a の正側端子は接地に接続されている。

【 0 0 1 8 】

F E T 1 2 の動作時、バイアス電源回路 1 1 から F E T 1 2 のゲート端子 G に所定大きさの負のバイアス電圧が供給され、また、定電圧電源 1 3 から F E T 2 のドレイン端子 D に正のバイアス電圧が供給される。

【 0 0 1 9 】

上記した構成において、F E T 1 2 のゲート・ドレイン間に矢印の向きに逆方向の整流電流 1 6 が流れると、その整流電流 1 6 が出力抵抗 1 1 b に流れる。このとき、出力抵抗 1 1 b と出力端子 1 1 c との接触点 P の電位が上昇し、たとえば第 2 中間点 C 2 の電位が上昇する。そして、ゲート・ソース間電圧がたとえば - 0 . 4 V 程度に浅くなると、第 2 保護回路 1 5 のダイオード 1 5 b が導通状態となり、その直流抵抗値が急激に小さくなる。この場合、ゲート端子 G の電位たとえば第 2 中間点 C 2 の電位は定電圧電源 1 5 a で規定される第 2 電位とほぼ同じ値になり、電位の上昇が停止する。したがって、ゲート・ソース間電圧はそれ以上 0 V に近づかず、矢印で示すドレイン・ソース間電流 1 7 の増大が抑えられ、F E T 1 2 の熱的な焼損による破壊が防止される。

【 0 0 2 0 】

また、F E T 1 2 のゲート・ソース間に矢印の向きに順方向の整流電流 1 8 が流れると、出力抵抗 1 1 b と出力端子 1 1 c との接触点 P の電位が降下し、第 1 中間点 C 1 やゲート端子 G の電位が降下する。このとき、ゲート・ドレイン間電圧が大きくなる。そして、ゲート・ソース間電圧がたとえば - 1 . 2 V より深くなると、第 1 保護回路 1 4 のダイオード 1 4 a およびダイオード 1 4 b が導通状態となり、第 1 保護回路 1 4 の直流抵抗値が急激に小さくなる。この場合、第 1 中間点 C 1 の電位はほぼ接地状態となり、電位の降下が停止する。したがって、ゲート・ソース間電圧はそれ以上深くならず、ゲート・ドレイン間の耐圧破壊が抑えられる。

【 0 0 2 1 】

上記した構成によれば、F E T 1 2 のゲート端子 G に入力する交流信号のレベルが F E T 1 2 の飽和出力よりも十分に小さい場合、第 1 保護回路 1 4 の 2 つのダイオード 1 4 a、1 4 b、および第 2 保護回路 1 5 のダイオード 1 5 b は非導通状態になっている。したがって、第 1 および第 2 の保護回路 1 4、1 5 は切り離された形となり、電源効率が低下するようなことはない。

【 0 0 2 2 】

また、F E T のゲート・ドレイン間あるいはゲート・ソース間に流れる整流電流によるゲート・ソース間電圧の変動が抑えられ、F E T の破壊が防止される。さらに、バイアス電

10

20

30

40

50

源回路の出力抵抗として大きな抵抗値をもつ抵抗を利用するため、電源効率が低下しないFET用バイアス回路が実現される。

【0023】

上記の実施形態では、第1および第2の2つの保護回路14、15が使用されている。この場合、2つの保護回路14、15のいずれか一方だけを用いる構成にすることもできる。しかし、2つの保護回路14、15を用いると、バイアス電源回路11の出力電圧が上昇した場合、および低下した場合の両方に対応でき、より効果的である。また2つの保護回路14、15は中間点の相違する位置に接続してもよく、共通する位置に接続してもよい。

【0024】

また、2つの保護回路において、導通状態および非導通状態となる回路素子としてダイオードが使用されているが、他の回路素子たとえばスイッチ作用をもつトランジスタなどを使用することもできる。

【0025】

また、上記の実施形態では、FETのゲート電極用のバイアス回路の例で説明している。しかし、この発明はFETに限らず、バイポーラトランジスタなどの他の半導体素子にも適用できる。また、バイアス電圧も負の場合に限らず、正のバイアス電圧を印加する回路に対しても適用できる。

【0026】

【発明の効果】

本発明によれば、半導体素子の破壊を防止できる半導体素子用バイアス回路を実現できる。

【図面の簡単な説明】

【図1】本発明の実施形態を説明するためのDC等価回路図である。

【図2】従来例を説明するためのDC等価回路図である。

【符号の説明】

11 … バイアス電源回路

11 a … 負の定電圧電源

11 b … 出力抵抗

11 c … 出力端子

12 … FET

13 … 正の定電圧電源

14 … 第1保護回路

14 a、14 b … 第1保護回路のダイオード

15 … 第2保護回路

15 a … 第2保護回路の定電圧電源

15 b … 第2保護回路のダイオード

16 … ゲート・ドレイン間の逆方向整流電流

17 … ドレイン・ソース間電流

18 … ゲート・ソース間の順方向整流電流

G … ゲート端子

D … ドレイン端子

S … ソース端子

C1、C2 … 中間点

10

20

30

40

【図1】

【図2】

---

フロントページの続き

F ターム(参考) 5J092 AA01 CA57 FA00 FA20 HA09 HA19 HA25 KA00 KA12

5J500 AA01 AC57 AF00 AF20 AH09 AH19 AH25 AK00 AK12 PF06

PG01