(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6029989号

(P6029989)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年10月28日(2016.10.28)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 21/8247 (2006.01) | HO 1 L 27/10 4 3 4 |

| HO 1 L 27/115 (2006.01)  | HO 1 L 29/78 3 7 1 |

| HO 1 L 21/336 (2006.01)  | HO 1 L 27/10 4 8 1 |

| HO 1 L 29/788 (2006.01)  | HO 1 L 29/58 G     |

| HO 1 L 29/792 (2006.01)  |                    |

請求項の数 10 (全 29 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-11820 (P2013-11820)    |

| (22) 出願日  | 平成25年1月25日 (2013.1.25)        |

| (65) 公開番号 | 特開2014-143339 (P2014-143339A) |

| (43) 公開日  | 平成26年8月7日 (2014.8.7)          |

| 審査請求日     | 平成27年8月21日 (2015.8.21)        |

|           |                                                    |

|-----------|----------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>東京都江東区豊洲三丁目2番24号  |

| (74) 代理人  | 110001195<br>特許業務法人深見特許事務所                         |

| (72) 発明者  | 佃 栄次<br>神奈川県川崎市中原区下沼部1753番地<br>ルネサスエレクトロニクス株式会社内   |

| (72) 発明者  | 片山 弘造<br>神奈川県川崎市中原区下沼部1753番地<br>ルネサスエレクトロニクス株式会社内  |

| (72) 発明者  | 園田 賢一郎<br>神奈川県川崎市中原区下沼部1753番地<br>ルネサスエレクトロニクス株式会社内 |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板の主表面に形成されるメモリセルと周辺トランジスタとを含む半導体装置の製造方法であって、

前記半導体基板を準備する工程と、

前記メモリセルが形成されるメモリセル形成領域における前記主表面に、第1の絶縁膜と、前記第1の絶縁膜の上面に接する第1のダミー電極とが積層された第1の積層構造を形成する工程と、

前記メモリセル形成領域における前記主表面に、前記第1の積層構造の側面に接するとともに前記半導体基板の前記主表面上にまで延びる延長部を有するように形成された第2の絶縁膜と、前記第2の絶縁膜の前記延長部の上面を含めて前記第2の絶縁膜に接する第2のダミー電極とが積層された第2の積層構造を形成する工程と、

前記周辺トランジスタが形成される周辺トランジスタ形成領域における前記主表面に、第3の絶縁膜と、前記第3の絶縁膜の上面に接する第3のダミー電極とが積層された第3の積層構造を形成する工程と、

前記第1、第2および第3の積層構造を覆うように層間絶縁層を形成する工程と、

前記第1、第2および第3のダミー電極の上面が前記層間絶縁層から露出し、前記層間絶縁層の上面と、露出した前記第1、第2および第3のダミー電極の上面とが平坦になるように、前記層間絶縁層の一部と前記第1、第2および第3のダミー電極の上面とを研磨する工程と、

10

20

露出した前記第1、第2および第3のダミー電極を除去して第1の開口部、第2の開口部および第3の開口部のそれぞれを形成する工程と、

前記第1の開口部と前記第2の開口部と前記第3の開口部とのそれぞれに、金属含有膜および他の膜を含む金属含有積層膜を埋設することにより、第1の金属含有膜と、第2の金属含有膜と、第3の金属含有膜とを形成する工程とを備え、

前記第1および第2の積層構造の高さは前記第3の積層構造の高さよりも高くなるように形成され、

前記第2の絶縁膜には電荷を蓄積する電荷蓄積膜を含み、

前記電荷蓄積膜はシリコン窒化膜である、半導体装置の製造方法。

【請求項2】

10

前記第2の絶縁膜は、第1のシリコン酸化膜と、前記シリコン窒化膜と、第2のシリコン酸化膜とがこの順に積層された構成を有する、請求項1に記載の半導体装置の製造方法。

【請求項3】

前記シリコン窒化膜の端部は、前記第2の金属含有膜の端部よりも内側に配置される、請求項1または2に記載の半導体装置の製造方法。

【請求項4】

20

前記第1および第2の積層構造を形成する工程の後、前記メモリセル形成領域における前記主表面に前記メモリセルのソース領域およびドレイン領域を形成する工程と、

前記ソース領域および前記ドレイン領域にシリサイドを形成する工程とをさらに備える、請求項1に記載の半導体装置の製造方法。

【請求項5】

前記第3の積層構造を形成する工程の後、前記周辺トランジスタ形成領域における前記主表面に前記周辺トランジスタのソース領域およびドレイン領域を形成する工程と、

前記ソース領域および前記ドレイン領域にシリサイドを形成する工程とをさらに備える、請求項1に記載の半導体装置の製造方法。

【請求項6】

前記第1、第2および第3の金属含有膜を形成する工程は、前記層間絶縁層の上面と、前記第1、第2および第3の開口部とに前記金属含有積層膜を堆積する工程と、前記層間絶縁層が露出するように前記金属含有積層膜を研磨する工程とを含み、

30

前記金属含有積層膜を研磨する工程では、前記第1の金属含有膜の上面と、前記第2の金属含有膜の上面と、前記第3の金属含有膜の上面とが同一の高さの平坦な面を形成するように研磨される、請求項1に記載の半導体装置の製造方法。

【請求項7】

前記金属含有膜は窒化チタンの薄膜のみを含む、請求項1に記載の半導体装置の製造方法。

【請求項8】

前記金属含有膜は、窒化チタンの薄膜と、多結晶シリコンの薄膜とがこの順に積層された構成を有する、請求項1に記載の半導体装置の製造方法。

【請求項9】

40

前記第1の金属含有膜は前記第1の絶縁膜の上面に形成され、前記第1の金属含有膜は前記第1の絶縁膜より誘電率が高い誘電体膜と、前記誘電体膜の仕事関数を調整する調整膜と、前記金属含有膜とがこの順に積層された構造を有し、

前記第2の金属含有膜は前記第2の絶縁膜の上面に形成され、前記第2の金属含有膜は前記誘電体膜と、前記調整膜と、前記金属含有膜とがこの順に積層された構造を有し、

前記第3の金属含有膜は前記第3の絶縁膜の上面に形成され、前記第3の金属含有膜は前記誘電体膜と、前記調整膜と、前記金属含有膜とがこの順に積層された構造を有し、

前記他の膜は前記誘電体膜と前記調整膜とを含む、請求項1に記載の半導体装置の製造方法。

【請求項10】

50

前記主表面には、前記メモリセルおよび前記周辺トランジスタが形成される素子形成領域と、前記素子形成領域の周囲に形成されるダイシング領域とを有し、

前記第1または第2の積層構造を形成する工程と同時に、前記ダイシング領域に、前記第1および第2の積層構造と同じ厚みを有する構造体が形成される工程をさらに備える、請求項1に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法に関し、特に、複数のゲートを含むメモリセルを有する半導体装置の製造方法に関するものである。

10

【背景技術】

【0002】

フラッシュメモリやC P U (Central Processing Unit)を内蔵する半導体装置として、たとえばマイクロコンピュータ(Microcomputer)が考えられる。たとえばフラッシュメモリには、電源を切っても記録情報が残る素子である不揮発性メモリが用いられることが好ましい。不揮発性メモリと論理用半導体装置とを同一の半導体基板上に混載することにより、高機能を有するマイクロコンピュータを形成することができる。不揮発性メモリと論理用半導体装置とが配置された当該マイクロコンピュータは、産業用機械、家電製品、自動車搭載装置などに広く用いられている。

【0003】

20

一般的にマイクロコンピュータに含まれる不揮発性メモリは、当該マイクロコンピュータが必要とするプログラムを格納し、隨時読み出して使用する。このため不揮発性メモリと論理用半導体装置とが混載したマイクロコンピュータが用いられることが好ましい。このような論理用半導体装置との混載に適した不揮発性メモリのメモリセル構造としては、制御用M I S (Metal Insulator Semiconductor)トランジスタと記憶用M I Sトランジスタとが一体として形成されたスプリットゲート構造のメモリセルが挙げられる。

【0004】

スプリットゲート構造のメモリセルのうち、記憶用M I SトランジスタにM O N O S (Metal Oxide Nitride Oxide Silicon)を用いたM O N O S型メモリセルが、たとえば特開2011-29631号公報(特許文献1)に開示されている。

30

【0005】

一方、近年のM I Sトランジスタのゲート絶縁膜の薄膜化の限界に伴い、ゲート絶縁膜として高誘電率絶縁膜(いわゆるH i g h - k膜)を用い、ゲート電極を金属膜とした構造が、たとえば特開2011-49282号公報(特許文献2)に開示されている。

【0006】

なお、M O N O S型メモリセルのうち、記憶用M I Sトランジスタを、制御用M I Sトランジスタの側壁部に形成した構造が、たとえば特開2010-282987号公報(特許文献3)に開示されている。

【先行技術文献】

【特許文献】

40

【0007】

【特許文献1】特開2011-29631号公報

【特許文献2】特開2011-49282号公報

【特許文献3】特開2010-282987号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

M O N O S型メモリセルの周りには、メモリセルの制御やメモリセルと接続されるマイクロコントローラ等の、周辺回路用のM I Sトランジスタが形成されている。周辺回路用M I Sトランジスタを高性能化するため、ゲート絶縁膜を高誘電率絶縁膜としゲート電極

50

を金属膜とした場合、特許文献 2 に開示されるように、ゲートラストプロセスを適用する必要がある。

【0009】

ゲートラストプロセスでは、一旦、多結晶シリコンでダミーのゲート電極を形成し、ゲート電極に接する側壁構造を形成後、ダミーのゲート電極を除去する。そして、除去した部分に、高誘電率絶縁膜と、金属膜を埋め込むことで、ゲート構造を形成する。

【0010】

一方、特許文献 3 に示す MONOS 型メモリセルの記憶用 MIS トランジスタは制御用 MIS トランジスタの側壁に形成されており、ダミーのゲート電極を用いないゲートファーストプロセスにより形成される。

10

【0011】

そのため、特許文献 3 に示す MONOS 型メモリセルと、高誘電率絶縁膜のゲート絶縁膜及び金属ゲート電極を有する周辺回路用 MIS トランジスタとを、一緒に形成しようとすると、ゲートファーストプロセスとゲートラストプロセスとを行うことになり、工程数が増加し、信頼性が低下してしまう。

【0012】

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0013】

20

一実施の形態によれば、メモリセル形成領域の第 1 および第 2 の積層構造が、周辺トランジスタ形成領域の第 3 の積層構造の高さよりも高くなるように形成された後、これらを覆うように層間絶縁層が形成され、研磨される。第 2 の積層構造に含まれる第 2 の絶縁膜には電荷を蓄積する電荷蓄積膜を含む。上記電荷蓄積膜はシリコン窒化膜である。

【発明の効果】

【0014】

一実施の形態の製造方法によれば、信頼性の高い半導体装置を製造することができる。

【図面の簡単な説明】

【0015】

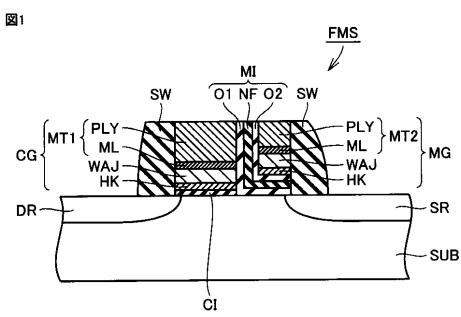

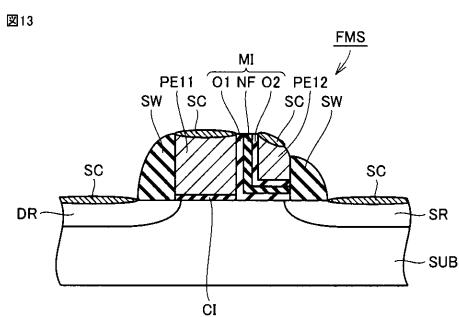

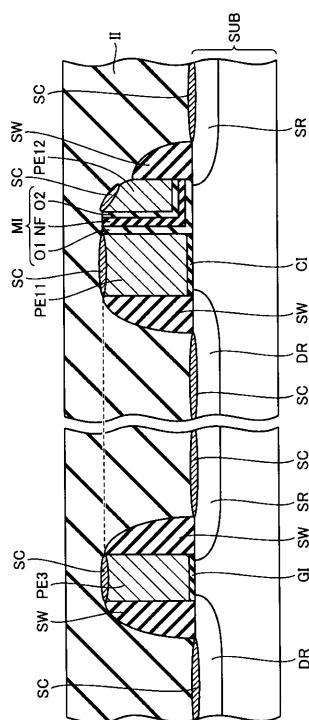

【図 1】一実施の形態の半導体装置を構成するメモリセルの概略断面図である。

30

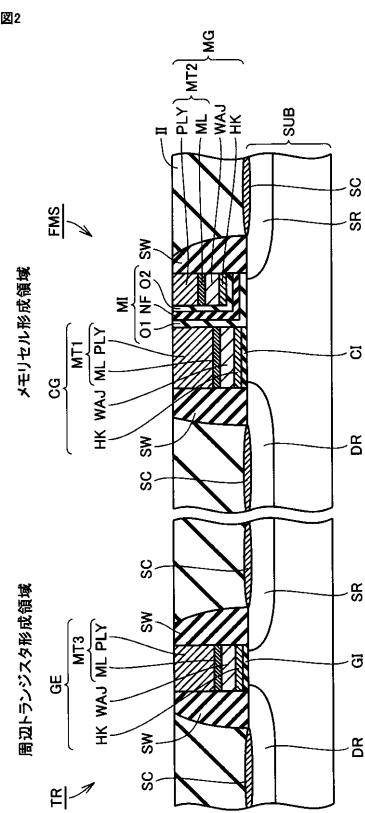

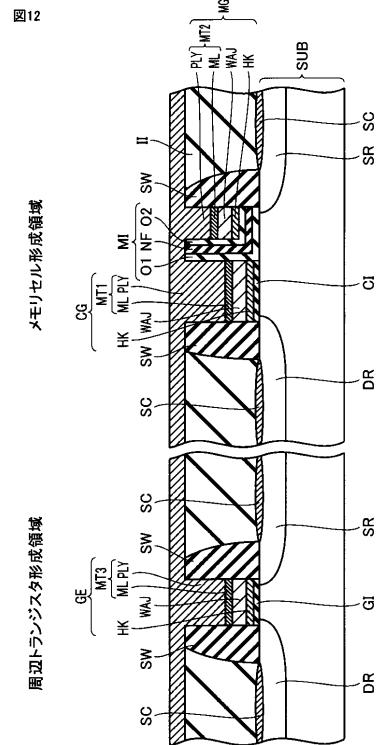

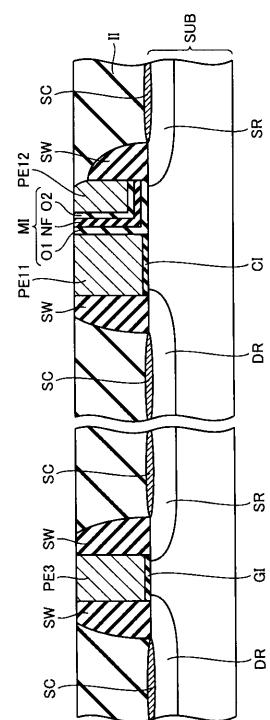

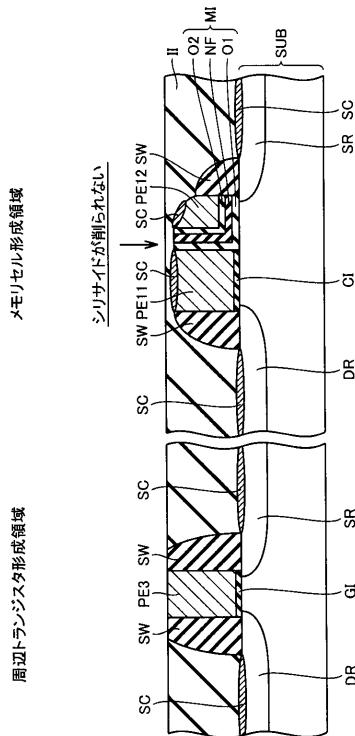

【図 2】図 1 のメモリセルと、その周辺回路としての周辺トランジスタとの概略断面図である。

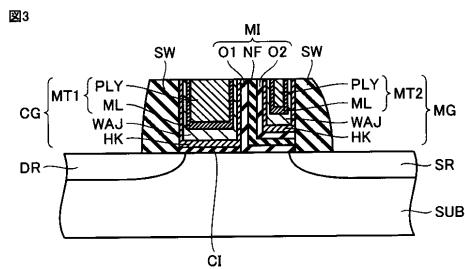

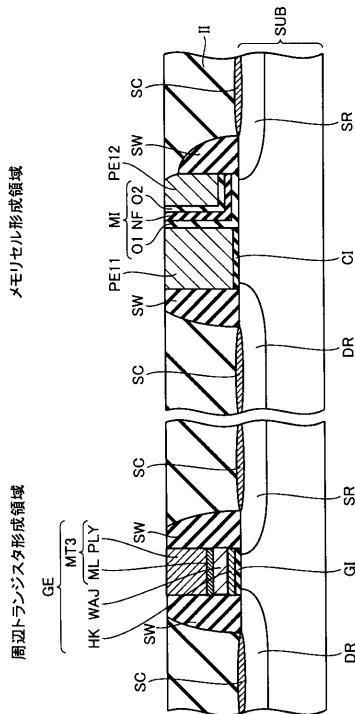

【図 3】図 1 のメモリセルのコントロールゲート膜およびメモリゲート膜の他の形状を示す概略断面図である。

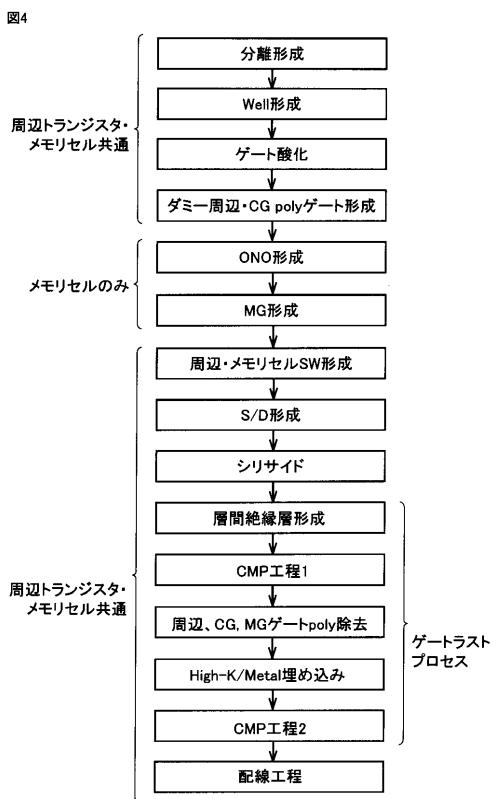

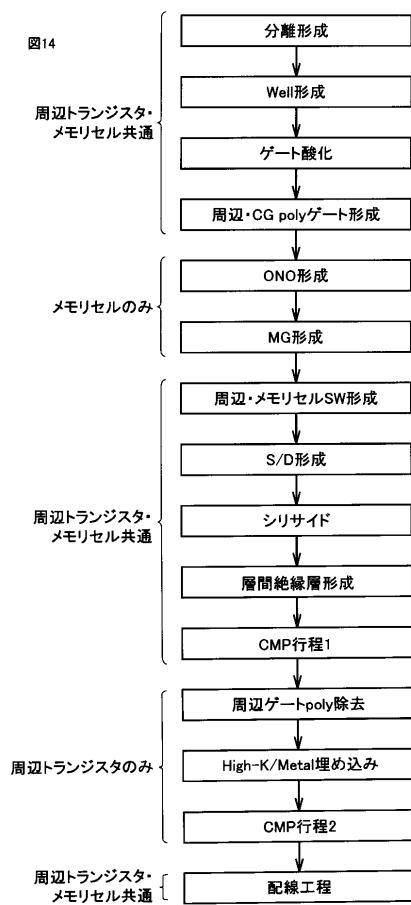

【図 4】一実施の形態の半導体装置の製造方法を説明するフローチャートである。

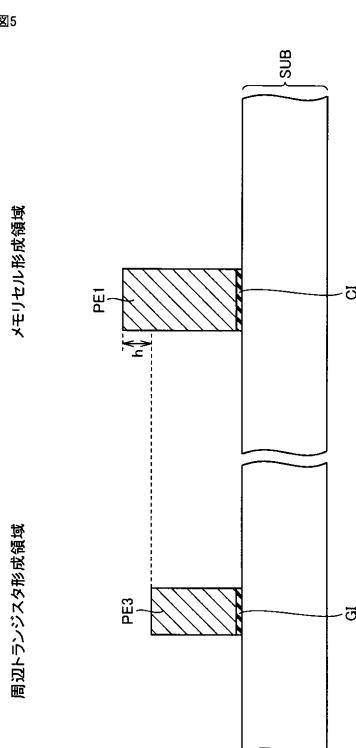

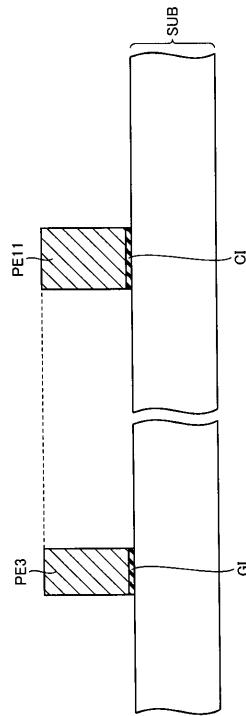

【図 5】一実施の形態の半導体装置の製造方法の第 1 工程を示す概略断面図である。

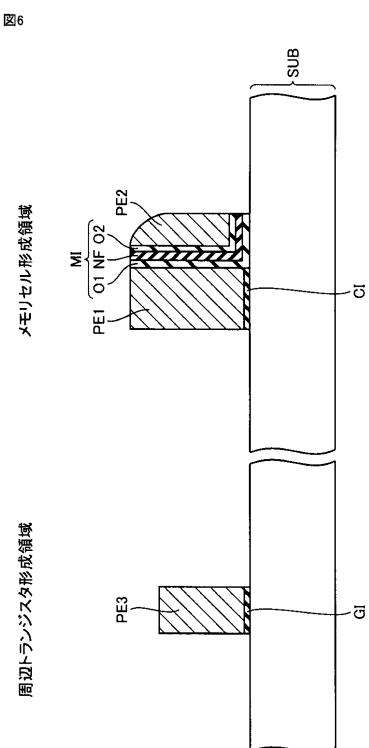

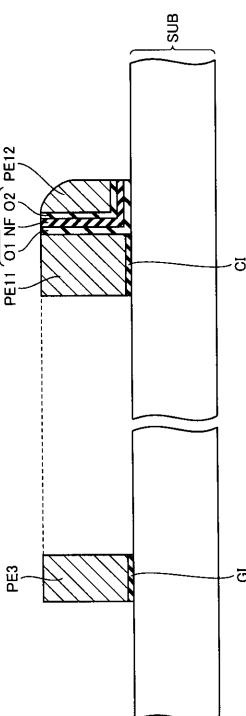

【図 6】一実施の形態の半導体装置の製造方法の第 2 工程を示す概略断面図である。

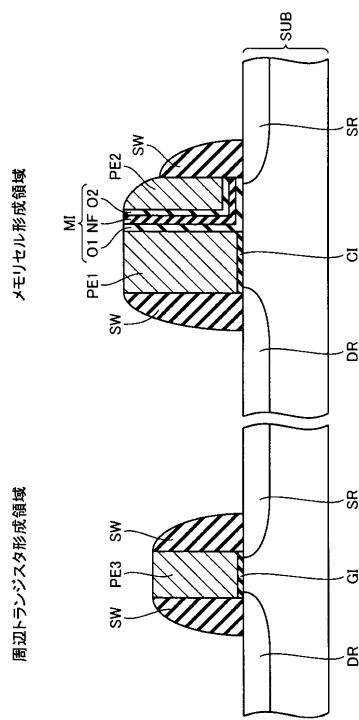

【図 7】一実施の形態の半導体装置の製造方法の第 3 工程を示す概略断面図である。

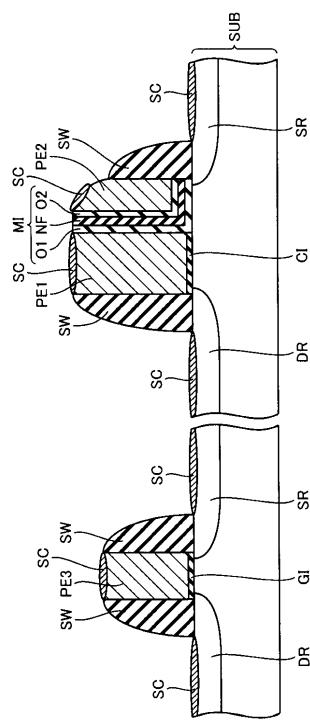

【図 8】一実施の形態の半導体装置の製造方法の第 4 工程を示す概略断面図である。

【図 9】一実施の形態の半導体装置の製造方法の第 5 工程を示す概略断面図である。

40

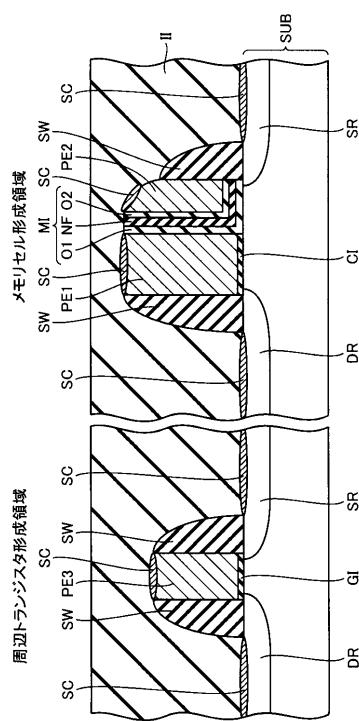

【図 10】一実施の形態の半導体装置の製造方法の第 6 工程を示す概略断面図である。

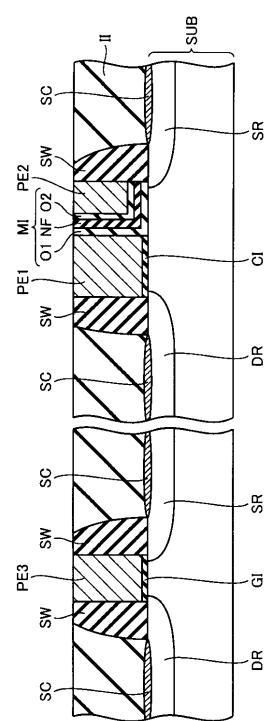

【図 11】一実施の形態の半導体装置の製造方法の第 7 工程を示す概略断面図である。

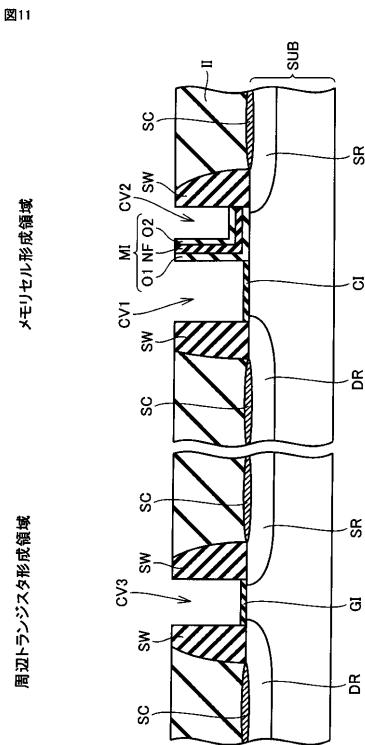

【図 12】一実施の形態の半導体装置の製造方法の第 8 工程を示す概略断面図である。

【図 13】比較例の半導体装置を構成するメモリセルの概略断面図である。

【図 14】比較例の半導体装置の製造方法を説明するフローチャートである。

【図 15】比較例の半導体装置の製造方法の第 1 工程を示す概略断面図である。

【図 16】比較例の半導体装置の製造方法の第 2 工程を示す概略断面図である。

【図 17】比較例の半導体装置の製造方法の第 3 工程を示す概略断面図である。

【図 18】比較例の半導体装置の製造方法の第 4 工程を示す概略断面図である。

【図 19】比較例の半導体装置の製造方法の第 5 工程を示す概略断面図である。

50

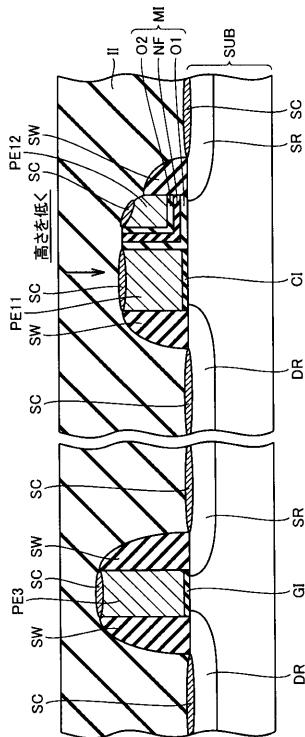

【図20】他の比較例として、図18のメモリセルがより薄く形成された態様を示す概略断面図である。

【図21】図20の周辺トランジスタの上面が研磨された態様を示す概略断面図である。

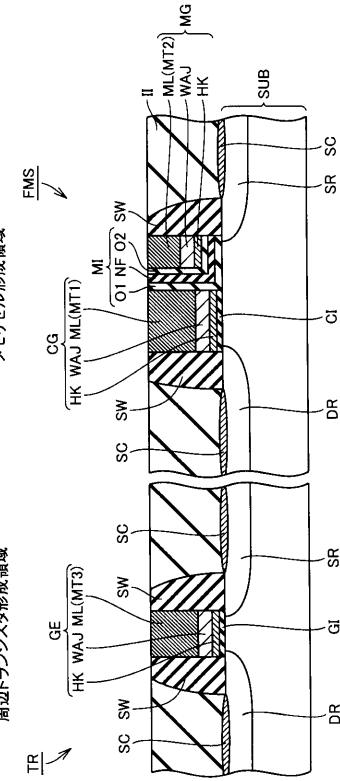

【図22】実施の形態2のメモリセルと、その周回路としての周辺トランジスタとの概略断面図である。

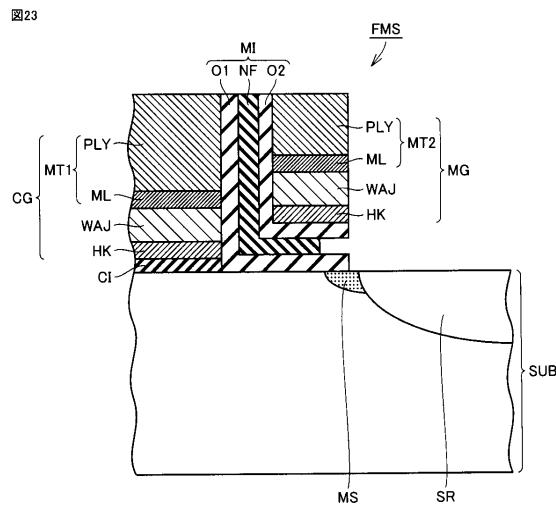

【図23】実施の形態3のメモリセルの構成を部分的に拡大して示す概略断面図である。

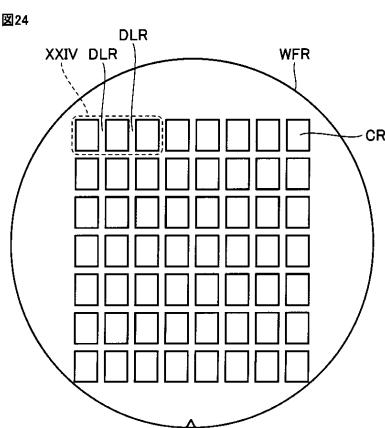

【図24】実施の形態4の半導体ウェハの概略平面図である。

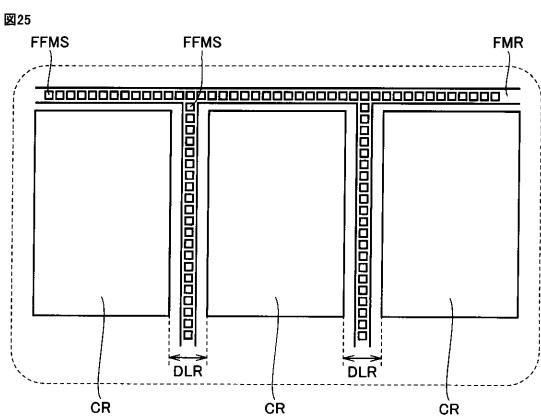

【図25】図24中の点線で囲まれた領域XXIVの構成を拡大して示す概略平面図である。

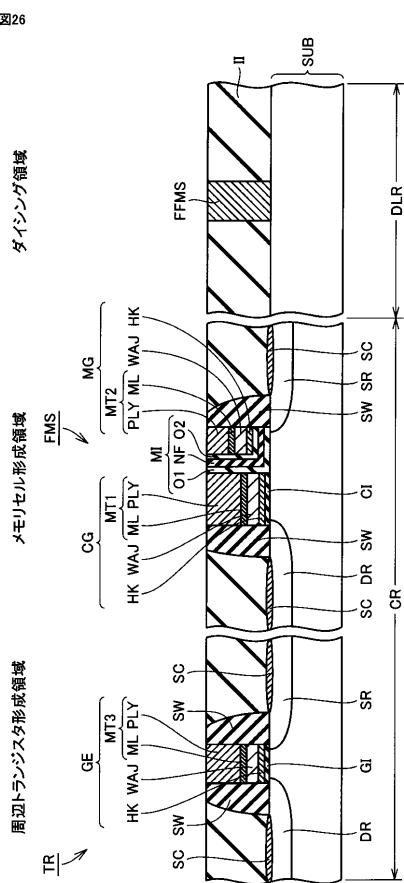

【図26】実施の形態4のメモリセルと、その周回路としての周辺トランジスタと、ダイシング領域との概略断面図である。 10

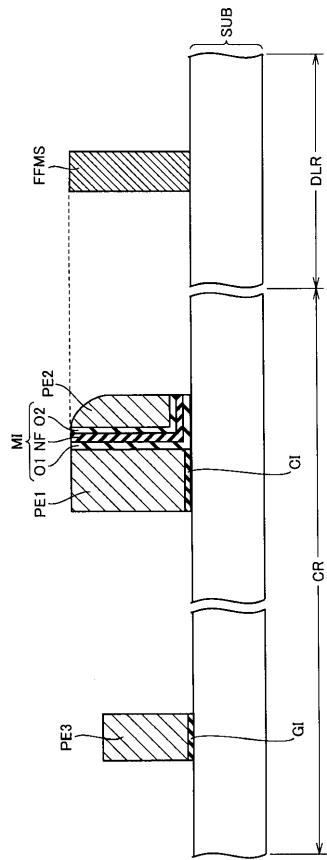

【図27】実施の形態4の半導体装置の製造方法の一工程を示す概略断面図である。

【発明を実施するための形態】

【0016】

以下、一実施の形態について図に基づいて説明する。

(実施の形態1)

まず一実施の形態の半導体装置に含まれるメモリセルの構成について、図1～図3を用いて説明する。

【0017】

図1を参照して、一実施の形態の半導体装置には、メモリセルとしてのFMONOS型メモリセルFMS(以下「メモリセルFMS」と記す)を有している。メモリセルFMSは、主表面を有する半導体基板SUBに形成されている。 20

【0018】

半導体基板SUBはたとえばシリコンの単結晶により形成されている。半導体基板SUB内の主表面(図1の半導体基板SUBの最上面としての左右方向に延びる面)にはドレイン領域DRおよびソース領域SRが互いに間隔をあけて形成されている。ドレイン領域DRおよびソース領域SRは、いわゆるn型またはp型の不純物が拡散されることにより形成されており、後述するコントロールゲート(第1のゲート)およびメモリゲート(第2のゲート)を挟むように配置されている。

【0019】

なおドレイン領域DRおよびソース領域SRの上面には通常、後述するシリサイド膜が形成されるが、ここではその図示が省略されている。 30

【0020】

半導体基板SUBの主表面上にはコントロールゲート絶縁膜CI(第1の絶縁膜)が形成されており、コントロールゲート絶縁膜CIの上面に接するようにコントロールゲート膜CG(第1の金属含有膜)が形成されている。コントロールゲート膜CGは読み込み・書き込み・消去動作を行なうものであり、ここではコントロールゲート膜CGとは電圧が印加される金属含有膜MT1としての金属膜MLおよび多結晶シリコン膜PLYに加え、高誘電率絶縁膜HKおよび調整膜WAJを含むものと定義する。コントロールゲート膜CGは、コントロールゲート絶縁膜CIより誘電率が高い高誘電率絶縁膜HK(誘電体膜)と、調整膜WAJと、金属膜MLと、多結晶シリコン膜PLYとがこの順に積層された構成を有している。このようにして、コントロールゲート絶縁膜CIとコントロールゲート膜CGとが積層されたコントロールゲート(第1のゲート)が形成されている。 40

【0021】

コントロールゲート絶縁膜CIはたとえばシリコン酸化膜など、通常のMOS型トランジスタにおけるゲート絶縁膜と同様の材質により形成される。このゲート絶縁膜CIは、半導体基板SUBとコントロールゲート膜CGとの密着性を高めるため、および界面準位の抑制のために形成される。

【0022】

高誘電率絶縁膜HKとはコントロールゲート絶縁膜CIのシリコン酸化膜に比べて誘電

10

20

30

40

50

率が有意に高い材質からなる絶縁膜であり、たとえばハフニウム系酸化膜が用いられる。通常のゲート絶縁膜C Iと高誘電率絶縁膜H Kとを直列に形成することにより、これら両者を合わせた全体の誘電率が高くなるため、MOS容量部の容量値を高くすることができます。

【0023】

調整膜W A Jとは、高誘電率絶縁膜H Kを含むコントロールゲート膜C G全体の仕事関数を調整し（低下させ）、結果的にコントロールゲート膜C Gの閾値電圧を調整する（低下させる）ために形成される薄膜であり、たとえばランタノイド系の酸化膜が用いられる。

【0024】

高誘電率絶縁膜H Kは上記のようにMOS容量を増加するために用いられるが、高誘電率絶縁膜H Kを用いるとコントロールゲート膜C Gの仕事関数が低下しなくなるなど、その制御が困難になる場合がある。調整膜W A Jはこの仕事関数の制御を容易にする（低下させる）ために形成される。

【0025】

金属含有膜M T 1は金属膜M Lと多結晶シリコン膜P L Yとにより形成される。金属膜M Lとしては他の材質との密着性が良好な窒化チタンまたは窒化タンタルの薄膜が用いられる。

【0026】

コントロールゲート絶縁膜C Iとコントロールゲート膜C Gとの側面の一部（図1では右側の側面）に接して、半導体基板S U Bの主表面上にまで延びる延長部を有するように、メモリゲート絶縁膜M I（第2の絶縁膜）が形成されている。

【0027】

メモリゲート絶縁膜M Iの側面部と延長部の上面との双方に接するように、メモリゲート膜M G（第2の金属抵抗膜）が形成されている。メモリゲート膜M Gは書き込み／消去のフラッシュ動作を行なうものであり、ここではメモリゲート膜M Gとは電圧が印加される金属含有膜M T 2としての金属膜M Lおよび多結晶シリコン膜P L Yに加え、高誘電率絶縁膜H Kおよび調整膜W A Jを含むものと定義する。すなわちメモリゲート膜M Gは、メモリゲート絶縁膜M Iの側面部と延長部の上面との双方に接するように形成され、コントロールゲート膜C Gと同様に、高誘電率絶縁膜H Kと、調整膜W A Jと、金属膜M Lと、多結晶シリコン膜P L Yとがこの順に積層された構成を有している。メモリゲート膜M Gにおける高誘電率絶縁膜H Kおよび調整膜W A Jのそれぞれの機能は、上記のコントロールゲート膜C Gにおける高誘電率絶縁膜H Kおよび調整膜W A Jと同様である。このようにして、メモリゲート絶縁膜M Iとメモリゲート膜M Gとが積層されたメモリゲート（第2のゲート）が形成されている。

【0028】

メモリゲート絶縁膜M Iは、通常のMONOS型メモリセルと同様に、（第1の）シリコン酸化膜O 1（SiO<sub>2</sub>など）と、シリコン窒化膜N F（SiNなど）と、（第2の）シリコン酸化膜O 2（SiO<sub>2</sub>など）との3層がこの順に積層された構成を有している。このうちの特にシリコン窒化膜N Fへの電子の注入によりメモリセルF M Sのデータの書き込みがなされ、シリコン窒化膜N Fへの正孔の注入によりメモリセルF M Sのデータの消去がなされる。データの書き込みの際にはメモリセルF M Sの閾値電圧が上昇し、データの消去の際にはメモリセルF M Sの閾値電圧が低下する。

【0029】

このようにメモリゲート絶縁膜M Iは、データを書き込んだり消去したりするための電荷である電子や正孔を蓄積する電荷蓄積膜を含んでおり、ここではシリコン窒化膜N Fが電荷蓄積膜に該当する。シリコン窒化膜N Fを含むメモリゲート絶縁膜M Iは、MONOS型メモリセルF M Sの通常の機能を発揮するために必須の構成要素である。

【0030】

以上のようにメモリセルF M Sは、コントロールゲート膜C Gとメモリゲート膜M Gと

の 2 つのゲート電極を有しており、これらにより書き込み / 消去のフラッシュ動作と読み込み動作との 2 つの動作を別個に行なうことが可能となっている。コントロールゲート膜 CG とメモリゲート膜 MG とは、上記のドレイン領域 DR およびソース領域 SR の一部の真上に重畠するように形成される。

【 0 0 3 1 】

図 1 のメモリセル FMS は、コントロールゲート膜 CG とメモリゲート膜 MG とは平坦な表面（上面）を有しており、かつコントロールゲート膜 CG とメモリゲート膜 MG と同一高さ（厚み）となるように表面がいわゆるツライチとなっている。言い換えればコントロールゲートとメモリゲートとの高さが同一となっている。これは上面を CMP (Chemical Mechanical Polishing) により研磨するためであるが、開口部が確保できるのであればツライチである必要はない。またここでの平坦とは、凹凸がほとんど存在せず、かつ表面が半導体基板 SUB の主表面とほぼ平行となる状態を意味する。

【 0 0 3 2 】

また同様に、図 1 のメモリゲート絶縁膜 MI の側面部も、コントロールゲート膜 CG とメモリゲート膜 MG と同一高さ（厚み）となるように表面がいわゆるツライチとなっており、メモリゲート絶縁膜 MI の延長部の端部（図 1 の右側の端部）は、メモリゲート膜 MG の端部と同一平面を有するいわゆるツライチとなっている。

【 0 0 3 3 】

なお図 1 においてはドレイン領域 DR とソース領域 SR とを単純に図示しているが、実際にはこれらの各領域 DR, SR には通常のドレイン領域 DR (ソース領域 SR) に加え、これよりも n 型または p 型の不純物の濃度が低い LDD (Light Doped Drain) と呼ばれる領域を有していてもよいし、いわゆる Extension や Halo と呼ばれる不純物の拡散領域を含んでいてもよい。

【 0 0 3 4 】

またメモリセル FMS は、コントロールゲート膜 CG およびメモリゲート膜 MG の側面を覆うように側壁絶縁膜 SW を有している。側壁絶縁膜 SW は、たとえばシリコン酸化膜とシリコン窒化膜との積層構造によりなることが好ましいが、ここではそのような積層構造の図示が省略されている。

【 0 0 3 5 】

図 2 を参照して、半導体基板 SUB の主表面にはメモリセル FMS のほかに、たとえば MOS 型トランジスタなどのトランジスタ TR を有している。このトランジスタ TR はメモリセル FMS の周辺回路として、メモリセル FMS と間隔をあけて形成されたいわゆる周辺トランジスタである。

【 0 0 3 6 】

トランジスタ TR においては、通常の MOS 型トランジスタと同様に、半導体基板 SUB 内の主表面に互いに間隔をあけて（後述する第 3 のゲートを挟むように）形成されたドレイン領域 DR およびソース領域 SR を有している。また半導体基板 SUB の主表面上にはゲート絶縁膜 GI (第 3 の絶縁膜) と、ゲート絶縁膜 GI の上面に接するゲート膜 GE (第 3 の金属含有膜) とが形成されている。ここではゲート膜 GE とは電圧が印加される金属含有膜 MT3 としての金属膜 ML および多結晶シリコン膜 PLY に加え、高誘電率絶縁膜 HK および調整膜 WAJ を含むものとする。このようにして、ゲート絶縁膜 GI とゲート膜 GE とが積層されたゲート（第 3 のゲート）が形成されている。

【 0 0 3 7 】

すなわちゲート膜 GE は、コントロールゲート膜 CG などと同様に、高誘電率絶縁膜 HK と、調整膜 WAJ と、金属膜 ML と、多結晶シリコン膜 PLY とがこの順に積層された構成を有している。ゲート膜 GE における高誘電率絶縁膜 HK および調整膜 WAJ のそれぞれの機能は、上記のコントロールゲート膜 CG およびメモリゲート膜 MG における高誘電率絶縁膜 HK および調整膜 WAJ と同様である。

【 0 0 3 8 】

また図 2 のトランジスタ TR は、ゲート膜 GE が平坦な表面（上面）を有しており、か

10

20

30

40

50

つゲート膜 G E がコントロールゲート膜 C G とメモリゲート膜 M G と同一高さ（厚み）となるように表面がいわゆるツライチとなっている。言い換えればコントロールゲートとメモリゲートとゲートとの高さがすべて同一となっている。

【 0 0 3 9 】

図 2 においてメモリセル F M S とトランジスタ T R との間で共通の構成要素については同一の参照符号を付しているが、これらは同様の構成であり、同一の層として形成されている。

【 0 0 4 0 】

図 1 においては省略されているが、実際には図 2 に示すように、メモリセル F M S とトランジスタ T R とが形成される領域においては、各ゲート電極を取り囲むように層間絶縁層 I I が形成されている。この層間絶縁層 I I はたとえばシリコン酸化膜により形成されている。

10

【 0 0 4 1 】

さらに、図 2 においてはメモリセル F M S およびトランジスタ T R の双方のドレイン領域 D R およびソース領域 S R の上面に、シリサイド膜 S C が形成されている。シリサイド膜 S C は、ドレイン領域 D R などを構成するシリコンの原子が、その上に形成されたコバルトやニッケルなどの原子と反応することにより、ドレイン領域 D R およびソース領域 S R の最上面近傍において形成される薄膜である。

【 0 0 4 2 】

なおトランジスタ T R およびメモリセル F M S は半導体基板 S U B に複数形成され、隣り合う 1 対のトランジスタ T R (メモリセル F M S ) の間には通常、それらを電気的に分離するための分離絶縁膜が形成されるが、ここではその図示が省略されている。

20

【 0 0 4 3 】

ここで、後述するように図 1 および図 2 におけるコントロールゲート膜 C G 、メモリゲート膜 M G などを構成する高誘電率絶縁膜 H K や金属膜 M L などは、ダミーとしてのゲート電極が除去された開口部を埋め込むように形成される。このとき、スパッタ法などでコントロールゲート膜 C G およびメモリゲート膜 M G を成膜すれば、図 1 および図 2 のように形成される。しかしながら、有機原料ガスを用いた M O C V D (Metal Organic Chemical Vapor Deposition) 法などの C V D 法を用いてコントロール膜 C G およびメモリゲート膜 M G を成膜すれば、図 3 に示すように開口部の底面および側面を覆うように、カップ状の断面形状を有するように形成される。以降においては、図 1 および図 2 のコントロールゲート膜 C G およびメモリゲート膜 M G を用いて説明するが、コントロールゲート膜 C G およびメモリゲート膜 M G は、図 3 のような形状となっていてもよい。

30

【 0 0 4 4 】

次に、図 4 ~ 図 1 2 を参照しながら、上記の一実施の形態の半導体装置の製造方法について説明する。

【 0 0 4 5 】

まずたとえばシリコンの単結晶からなる半導体基板 S U B (図 1 ~ 図 3 参照) が準備される。図 4 を参照して、当該半導体基板 S U B の主表面に、たとえば通常の L O C O S ( L O C a l Oxidation of Silicon) 法または S T I (Shallow Trench Isolation) 法により、互いに間隔をあけて複数の素子分離絶縁膜が形成される (図 4 中の「分離形成」に相当)。また半導体基板 S U B 内の主表面には、互いに隣接する素子分離絶縁膜に挟まれた領域に、必要に応じて不純物が拡散された Well 領域が形成される (図 4 中の「Well 形成」に相当)。これらについては図示が省略される。

40

【 0 0 4 6 】

さらに図 4 および図 5 を参照して、半導体基板 S U B の主表面の、メモリセルが形成されるメモリセル形成領域に、コントロールゲート絶縁膜 C I (第 1 の絶縁膜) と、周辺トランジスタが形成される周辺トランジスタ形成領域におけるゲート絶縁膜 G I (第 3 の絶縁膜) とが同時に形成される (図 4 中の「ゲート酸化」に相当)。これらはたとえば通常の熱酸化法により形成されたシリコン酸化膜であり、通常の写真製版およびエッチングに

50

より所望のパターンに形成される。

【0047】

引き続き図4および図5を参照して、コントロールゲート絶縁膜CIの上面に接する第1のダミー電極PE1と、ゲート絶縁膜GIの上面に接する第3のダミー電極PE3とが同時に形成される(図4中の「ダミー周辺・CG polyゲート形成」に相当)。これらのダミー電極PE1、PE3はたとえばCVD(Chemical Vapor Deposition)法による多結晶シリコンの薄膜により形成されている。このようにして、コントロールゲート絶縁膜CIと第1のダミー電極PE1とが積層された第1の積層構造と、ゲート絶縁膜GIと第3のダミー電極PE3とが積層された第3の積層構造とが形成される。第1のダミー電極PE1はメモリセルを形成するためのダミーのコントロールゲートであり、第3のダミー電極PE3は周辺トランジスタを形成するためのダミーのゲートである。 10

【0048】

ここで第1のダミー電極PE1を含む第1の積層構造は、第3のダミー電極PE3を含む第3の積層構造に比べてその高さが図5のhだけ高くなるように形成される。ここで高さとは、半導体基板SUBの主表面に対する、図の上下方向の距離を意味する。

【0049】

具体的にはまず第1のダミー電極PE1と第3のダミー電極PE3とが同時に成膜されることにより、同じ厚みになるように形成された後、第1のダミー電極PE1を覆うフォトレジストが形成された状態で、第3のダミー電極PE3がエッチングにより除去される。このようにすれば、第1のダミー電極PE1より第3のダミー電極PE3を厚くすることができる。 20

【0050】

第1のダミー電極PE1と第3のダミー電極PE3との厚みが異なるように形成される点を除き、以上の各工程は周辺トランジスタの形成領域およびメモリセルの形成領域の双方に共通である。

【0051】

図4および図6を参照して、メモリセルの形成領域において、半導体基板SUBの主表面上にメモリゲート絶縁膜MIが形成される(図4中の「ONO形成」に相当)。メモリゲート絶縁膜MIは、第1の積層構造の側面に接するとともに、そこから半導体基板SUBの主表面上にまで延びる延長部を有するように形成される。メモリゲート絶縁膜MIとして具体的には、シリコン酸化膜O1と、シリコン窒化膜NFと、シリコン酸化膜O2との3層がこの順に積層される。これらの絶縁膜O1, NF, O2が、たとえば通常のCVD法により形成される。 30

【0052】

このとき、第1の積層構造の側面および上面を覆うように、半導体基板SUBの主表面上に、シリコン酸化膜O1と、シリコン窒化膜NFと、シリコン酸化膜O2との3層がこの順に積層される。

【0053】

次に、メモリゲート絶縁膜の延長部の上面を含めてメモリゲート絶縁膜MIに接する第2のダミー電極PE2が形成される(図4中の「MG形成」に相当)。第2のダミー電極PE2はたとえばCVD法により形成された多結晶シリコンの薄膜である。具体的には、図6の第1の積層構造の上面、ならびにメモリゲート絶縁膜MIの側面部および延長部の上面を覆うように、多結晶シリコンの薄膜が形成された後、異方性エッチングにより、多結晶シリコンおよびメモリゲート絶縁膜MIがエッチバックされる。その結果、図6に示すように、多結晶シリコンからなるダミー電極PE2およびメモリゲート絶縁膜MIが第1の積層構造の側壁として形成される。その後通常の写真製版およびエッチングにより不要な部分が除去されることにより、図6の構造が形成される。このようにして、メモリゲート絶縁膜MIと第2のダミー電極PE2とが積層された第2の積層構造が形成される。第2のダミー電極PE2はメモリセルを形成するためのダミーのメモリゲート膜である。 40

【0054】

ここで第2のダミー電極P E 2を含む第2の積層構造は、第3のダミー電極P E 3を含む第3の積層構造に比べてその高さが高くなるように形成される。第1のダミー電極P E 1が第3のダミー電極P E 3に比べてその高さが高くなるように形成されるため、第2のダミー電極P E 2を含む第2の積層構造についても第1の積層構造と同様に、第3の積層構造よりも高くなるように形成される。

#### 【0055】

ただし第2のダミー電極P E 2はその上面が平坦ではなく図6に示すようにやや右肩下がりの形状を有するように形成される。このため第2のダミー電極P E 2は少なくとも最大の高さを有する（シリコン酸化膜O 2などと接する）領域の高さが第1の積層構造よりも高く形成され、最小の高さを有する（右肩下がりになり最も高さが低い）領域についても第3の積層構造よりも高くなるように形成されることがより好ましい。

10

#### 【0056】

以上の各工程はメモリセルの形成領域のみに対して行なわれるが、これ以降の各工程は周辺トランジスタの形成領域およびメモリセルの形成領域の双方に共通である。

#### 【0057】

図4および図7を参照して、周辺トランジスタの形成領域およびメモリセルの形成領域において、第1、第2および第3の積層構造の側面を覆うように側壁絶縁膜S Wが形成される（図4中の「周辺・メモリセルS W形成」に相当）。側壁絶縁膜S Wは、第1、第2および第3の積層構造の上面および側面を覆うように絶縁膜が形成された後、異方性ドライエッティングにより絶縁膜がエッチバックされることにより、形成される。側壁絶縁膜は、シリコン酸化膜またはシリコン窒化膜のいずれか1層のみから形成されてもよいが、シリコン酸化膜とシリコン窒化膜との積層構造から形成されてもよい。

20

#### 【0058】

図4および図7を参照して、第1および第2の積層構造および側壁絶縁膜S Wによる構造体を用いた自己整合技術により、半導体基板S U Bの主表面から不純物をイオン注入することにより、メモリセル形成領域における半導体基板S U Bの主表面にメモリセルのソース領域S Rおよびドレイン領域D Rが形成される（図4中の「S / D形成」に相当）。同様に、第3の積層構造および側壁絶縁膜S Wによる構造体を用いた自己整合技術により、周辺トランジスタ形成領域における半導体基板S U Bの主表面に周辺トランジスタのソース領域S Rおよびドレイン領域D Rが形成される。

30

#### 【0059】

その後、ドレイン領域D Rおよびソース領域S Rが形成された領域の結晶状態を修復するために、たとえばいわゆるR T A（Rapid Thermal Anneal）により、半導体基板S U Bの熱処理がなされる。

#### 【0060】

ところで図7においては側壁絶縁膜S Wより内側の第1のダミー電極P E 1および第3のダミー電極P E 3の真下の領域の一部にまで広がるようにドレイン領域D Rおよびソース領域S Rが形成される。このようにするためには、たとえば第1～第3の積層構造の形成後、側壁絶縁膜S Wの形成前に一度、第1～第3の積層構造を用いた自己整合技術により、半導体基板S U Bの主表面から不純物をイオン注入することにより、上記のドレイン領域D Rおよびソース領域S Rよりも不純物濃度の低いいわゆるL D D領域が形成されることが好ましい。すなわちこの場合は、第1～第3の積層構造の形成後、L D D領域が形成され、その後側壁絶縁膜S Wが形成される。さらにその後、ドレイン領域D Rおよびソース領域S Rが形成される。

40

#### 【0061】

図4および図8を参照して、第1のダミー電極P E 1、第2のダミー電極P E 2、第3のダミー電極P E 3、ドレイン領域D Rおよびソース領域S Rの上面にシリサイド膜S Cが形成される（図4中の「シリサイド」に相当）。具体的には、第1、第2、第3のダミー電極P E 1, P E 2, P E 3の上面を覆うように、半導体基板S U Bの主表面上にたとえばコバルトまたはニッケルの金属膜が、たとえばスパッタリング法などの一般的な金属

50

薄膜形成方法により形成される。

【0062】

次に、図示されないがこの状態で半導体基板SUBが熱処理される。具体的には、たとえば半導体基板SUBが、たとえばニッケルの場合500以上600以下の温度で20秒以上3分以下の時間加熱される。するとドレイン領域DRおよびソース領域SRを構成するシリコンの原子と、その上に形成されたコバルトの原子とが反応してシリサイド膜SCが形成される。ただしコバルトの場合は700以上800以下の温度で加熱される。ダミー電極PE1～PE3とその上に形成されたコバルトやニッケルの原子とも同様に反応してシリサイド膜SCが形成される。

【0063】

図4および図9を参照して、第1のダミー電極PE1、第2のダミー電極PE2、第3のダミー電極PE3を含む第1～第3の積層構造の上面などを覆うように、半導体基板SUBの主表面に層間絶縁層IIが形成される(図4中の「層間絶縁層形成」)。層間絶縁層IIは、たとえばシリコン酸化膜であり、たとえばCVD法により形成される。

【0064】

図4および図10を参照して、層間絶縁層IIに覆われた第1のダミー電極PE1、第2のダミー電極PE2の上面が露出するように、層間絶縁層IIの一部を含む第1および第2の積層構造の上面が研磨される(図4中の「CMP工程1」に相当)。このとき第1のダミー電極PE1および第2のダミー電極PE2は、その上面が露出し、かつその上面に開口部を形成するように一部が研磨される。この開口部は、第1のダミー電極PE1および第2のダミー電極PE2の、半導体基板SUBの主表面に沿う方向に関する幅に比べて小さすぎないように、後の工程において当該開口部から第1のダミー電極PE1および第2のダミー電極PE2を抜き取り除去することが可能な程度に十分に広いことが好ましい。

【0065】

このとき、第1および第2のダミー電極PE1, PE2に加えて第3のダミー電極PE3の上面が露出するように、層間絶縁層IIの一部を含む第3の積層構造の上面が研磨される。第3の積層構造の上面は、第1および第2の積層構造の上面と同時に研磨される。すなわち、ここでは第3の積層構造は第1および第2の積層構造よりもその高さが低くなるように形成されているため、第1および第2の積層構造(ダミー電極PE1, PE2)の上面が露出した後も引き続き、第3のダミー電極PE3の上面が露出するまで、研磨が続けられる。

【0066】

ここで研磨は、たとえば通常のCMPによりなされることが好ましい。また研磨の後には層間絶縁層IIの上面およびダミー電極PE1, PE2, PE3の上面が平坦になるように処理がなされる。

【0067】

図4および図11を参照して、第1のダミー電極PE1および第2のダミー電極PE2が、通常の写真製版およびエッチングにより除去される(図4の「周辺、CG、MGゲートpolly除去」に相当)。この処理により、第1のダミー電極PE1が形成されていた領域には第1の開口部CV1が、第2のダミー電極PE2が形成されていた領域には第2の開口部CV2が、それぞれ形成される。

【0068】

このとき、第1および第2のダミー電極PE1, PE2に加えて第3のダミー電極PE3が、第1および第2のダミー電極PE1, PE2とともに除去され、第3のダミー電極PE3が形成されていた領域には第3の開口部CV3が形成される。

【0069】

図4および図12を参照して、メモリセルの形成領域において、第1の開口部CV1(コントロールゲート絶縁膜CIの上面)に、高誘電率絶縁膜HK(誘電体膜)と、調整膜WAJとがこの順に形成され、さらにその上に、金属含有膜MT1としての金属膜MLと

10

20

30

40

50

多結晶シリコン膜 P L Y とがこの順に形成される。これにより、層間絶縁層 I I の上面と第 1 の開口部 C V 1 とに金属含有積層膜が堆積（埋設）され、その結果、第 1 の金属含有膜（コントロールゲート膜 C G ）を構成する積層構造が形成される。すなわち金属含有膜 M T 1 ならびに高誘電率絶縁膜 H K および調整膜 W A J が第 1 の開口部 C V 1 に埋め込まれることにより、コントロールゲート膜 C G が形成される。

#### 【 0 0 7 0 】

なおここでは金属膜 M L と多結晶シリコン膜 P L Y とを合わせた積層膜を「金属含有膜（M T 1 ）」と、高誘電率絶縁膜 H K と調整膜 W A J とを合わせた積層膜を「他の膜」と、金属含有膜と他の膜とを合わせた積層膜を「金属含有積層膜」と定義する。金属含有積層膜を構成する各膜の厚みと開口部 C V 1 の深さとの関係により、図 1 2 に示すように層間絶縁層 I I の上面には金属含有積層膜のうち多結晶シリコン膜 P L Y のみが堆積する様となつてもよい。

10

#### 【 0 0 7 1 】

高誘電率絶縁膜 H K は、コントロールゲート絶縁膜 C I （第 1 の絶縁膜）よりも誘電率が高い。高誘電率絶縁膜 H K としては、たとえばハフニウム系の酸化膜が、C V D 法などにより形成される。調整膜 W A J としては、たとえばランタノイド系の酸化膜が、C V D 法などにより形成される。また金属膜 M L としてはたとえば窒化チタンまたはタンタルチタンの薄膜が、たとえばスパッタリング法により形成される。さらに多結晶シリコン膜 P L Y が、たとえば C V D 法により形成される。

20

#### 【 0 0 7 2 】

上記のコントロールゲート膜 C G と同時に、第 2 の開口部 C V 2 （メモリゲート絶縁膜 M I の延長部の上面）に、メモリゲート絶縁膜 M I の側面部に接するように、高誘電率絶縁膜 H K と調整膜 W A J と（他の膜）が形成され、さらにその上に、金属膜 M L と多結晶シリコン膜 P L Y と（金属含有膜 M T 2 ）がこの順に形成される。これにより、金属含有積層膜としての第 2 の金属含有膜（メモリゲート膜 M G ）を構成する積層構造が形成される。すなわち金属含有膜 M T 2 ならびに高誘電率絶縁膜 H K および調整膜 W A J が第 2 の開口部 C V 2 に埋め込まれることにより、メモリゲート膜 M G が形成される。

#### 【 0 0 7 3 】

さらにコントロール膜 C G 、メモリゲート膜 M G と同時に、第 3 の開口部 C V 3 （ゲート絶縁膜 G I の上面）に、高誘電率絶縁膜 H K と、調整膜 W A J と（他の膜）が形成され、さらにその上に、金属膜 M L と多結晶シリコン膜 P L Y と（金属含有膜 M T 3 ）がこの順に形成される。これにより、金属含有積層膜としての第 3 の金属含有膜（ゲート膜 G E ）を構成する積層構造が形成される。すなわち金属含有膜 M T 3 ならびに高誘電率絶縁膜 H K および調整膜 W A J が第 3 の開口部 C V 3 に埋め込まれることにより、ゲート膜 G E が形成される。以上の工程は、図 4 の「H i g h - K / M e t a l 埋め込み」に相当する。

30

#### 【 0 0 7 4 】

この高誘電率絶縁膜 H K と調整膜 W A J とを形成する工程は、上記のシリサイド膜 S C を形成するための熱処理がなされた後に行なわれる。より具体的には、高誘電率絶縁膜 H K と調整膜 W A J とを形成する工程の後、半導体装置が完成するまでの間には、熱処理がなされないことが好ましい。なおここでの熱処理とは、ドレイン領域 D R やシリサイド層 S C などを形成した後に（たとえば 500 や 800 などの）高温でなされるアニールなどの処理（高温熱処理）を指すものとする。たとえばこの後においても配線の形成のための成膜などの工程があり、当該成膜時にも半導体基板 S U B の温度が上がる。このためこのような成膜工程なども厳密には熱処理に含まれ得るが、このような温度の上昇はここでは熱処理に含まれないものとし、高誘電率絶縁膜 H K と調整膜 W A J とを形成する工程の後にこのような温度の上昇がなされてもよい。

40

#### 【 0 0 7 5 】

図 4、図 1 2 および図 2 を参照して、その後、「C M P 工程 2 」により、図 1 2 に示す層間絶縁層 I I の上面に接するように形成された多結晶シリコン膜 P L Y が除去され、図

50

2 に示すように層間絶縁層 II が露出するまで層間絶縁層 II の上面が研磨される。層間絶縁層 II が露出した結果、開口部 CV 1 ~ CV 3 に埋め込まれた多結晶シリコン膜 PL Yなどを含むコントロールゲート膜 CG、メモリゲート膜 MG およびゲート膜 GE の上面が露出し、これらの上面は同一の高さの平坦な面となる。以上により、コントロールゲート膜 CG、メモリゲート膜 MG およびゲート膜 GE が形成される。

【0076】

その後、層間絶縁層 II と同一の層および / またはそれより上層に各種の配線などが形成され (図 4 の「配線工程」に相当)、たとえば図 1 に示すような一実施の形態のメモリセルおよび周辺トランジスタを有する半導体装置が形成される。

【0077】

次に、図 13 ~ 図 21 の比較例を参照しながら、一実施の形態の作用効果について説明する。

10

【0078】

図 13 を参照して、比較例の半導体装置のメモリセル FMS は、一実施の形態の半導体装置のメモリセル FMS と大筋で同様の構成を備えている。このため図 13 において図 1 と同様の構成を有する要素については図 1 と同一の符号を付し、その説明を繰り返さない。

【0079】

図 13 のメモリセル FMS は、コントロールゲート膜が (ダミー電極 PE 1 と同様に) 多結晶シリコン膜 PE 11 により形成されており、メモリゲート膜が (ダミー電極 PE 2 と同様に) 多結晶シリコン膜 PE 12 により形成されている点において、図 1 に示す一実施の形態のメモリセル FMS と異なっている。多結晶シリコン膜 PE 11, PE 12 の上面にはシリサイド膜 SC が形成される。

20

【0080】

図 14 を参照して、比較例の半導体装置の製造方法は、図 4 の一実施の形態の製造方法の「ダミー周辺・CG pol y ゲート形成」において形成される多結晶シリコンのダミー電極 PE 3 は一実施の形態と同様にダミーとして形成されるため除去されるが、多結晶シリコン膜 PE 11 は除去されることなくそのままメモリセル FMS の電極として用いられる。つまり、周辺回路としてのトランジスタ TR はダミー電極を用いるゲートラストプロセスにより形成されるが、メモリセル FMS はダミー電極を用いないゲートファーストプロセスにより形成される。以下、図 14 ~ 図 18 を参照しながら、比較例の半導体装置の製造方法について説明する。

30

【0081】

図 14 を参照して、一実施の形態と同様に、半導体基板 SUB が準備され、「分離形成」「Well形成」がなされる。次に図 14 および図 15 を参照して、半導体基板 SUB の主表面上に、コントロールゲート絶縁膜 CI とゲート絶縁膜 GI とが同時に形成される。さらにコントロールゲート絶縁膜 CI の上面に接するコントロールゲート膜として機能する多結晶シリコン膜 PE 11 と、ゲート絶縁膜 GI の上面に接する第 3 のダミー電極 PE 3 とが同時に形成される。なおここでは、多結晶シリコン膜 PE 11 と第 3 のダミー電極 PE 3 とがほぼ同じ厚みとなるように形成される。以上は図 14 の「ゲート酸化」「周辺・CG pol y ゲート形成」に相当する。

40

【0082】

図 14 および図 16 を参照して、図 6 と同様にメモリゲート絶縁膜 MI が形成され (図 14 中の「ONO形成」に相当)、その後、メモリゲート膜として機能する多結晶シリコン膜 PE 12 が形成される (図 14 中の「MG形成」に相当)。

【0083】

図 14 および図 17 を参照して、図 7 と同様に側壁絶縁膜 SW が形成され (図 14 中の「周辺・メモリセル SW 形成」に相当)、ドレイン領域 DR およびソース領域 SR が形成され (図 14 中の「S/D 形成」に相当)、シリサイド膜 SC が形成される (図 14 中の「シリサイド」に相当)。さらに図示されないが熱処理がなされ、図 9 と同様に層間絶縁

50

層ⅠⅠが形成される（図14中の「層間絶縁層形成」に相当）。

【0084】

図14および図18を参照して、図10と同様に多結晶シリコン膜PE11, PE12, PE3の上面が露出するまで層間絶縁層ⅠⅠを研磨する（図14中の「CMP工程1」に相当）。

【0085】

ところが、図18の工程においては本来、周辺トランジスタの形成領域の第3のダミー電極PE3のみ上面が露出すれば十分であるが、第3のダミー電極PE3と多結晶シリコン膜PE11, PE12との上面がともに研磨される。このため多結晶シリコン膜PE11, PE12の上面のシリサイド膜SCが削り取られてしまう。多結晶シリコン膜PE11, PE12は多結晶シリコンで形成されるため、その上面のシリサイド膜SCが存在しなければゲート抵抗が高くなってしまう。このような問題は、多結晶シリコン膜PE11と第3のダミー電極PE3とがほぼ同じ厚みとなるように形成されるために起こり得る。

【0086】

図14および図19を参照して、多結晶シリコン膜PE11, PE12の上面のシリサイド膜SCが露出された状態で、周辺トランジスタの形成領域のみに対して第3のダミー電極PE3が除去され（図14の「周辺ゲートpolyl除去」に相当）、第3のダミー電極PE3が除去された領域に対して、ゲート絶縁膜GIの上面に、高誘電率絶縁膜HKと、調整膜WAJとが形成され、さらにその上に、金属含有膜MT3としての金属膜MLと、多結晶シリコン膜PLYとがこの順に形成されることにより、ゲート膜GEが形成される（図14の「High-K/Metal埋め込み」に相当）。その後は一実施の形態と同様に図14の「配線工程」に相当する処理がなされる。

【0087】

上記のように多結晶シリコンPE11, PE12の上面にシリサイド膜SCが存在しないために高抵抗になるという問題を解決するためには、図20および図21に示すように、ゲートファーストプロセスにより形成されるメモリセルの形成領域の多結晶シリコン膜PE11, PE12およびその上面のシリサイド膜SCが研磨されることを抑制すればよい。つまり多結晶シリコン膜PE11, PE12が第3のダミー電極PE3よりも低く（薄く）なるように形成すればよい。このようにすれば、周辺トランジスタの形成領域の第3のダミー電極PE3のシリサイド膜SCが研磨されても、メモリセルの形成領域の多結晶シリコン膜PE11, PE12のシリサイド膜SCは研磨されないので、ゲート抵抗を低く保つことができる。

【0088】

ところが実際にはメモリセルの多結晶シリコン膜PE12は、側壁絶縁膜SWのような右肩下がりの断面形状を有するため、これの高さを低く（薄く）形成すれば型崩れする可能性がある。また多結晶シリコン膜PE12が薄ければ、多結晶シリコン膜PE12にイオン注入しようとする不純物が多結晶シリコン膜PE12を貫通するため、多結晶シリコン膜PE12に適正な量の不純物を注入することが困難になる可能性がある。

【0089】

図20および図21のようにメモリセルを周辺トランジスタよりも低く形成するのではなく、反対に周辺トランジスタを低く、メモリセルを高く（厚く）形成する方が好ましい。周辺トランジスタは素子の動作速度を高めるため微細化がすすめられており、微細化に伴いゲートの高さが低くなっている。仮に周辺トランジスタのゲートが高く形成されれば、ゲートの断面のアスペクト比が大きくなりそのバランスを確保できなくなる。このため周辺トランジスタはメモリセルよりもゲートが低く形成される方が好ましい。

【0090】

しかしこのようにすれば、上記の図14～図19の工程と同様に、メモリセルにおける多結晶シリコン膜PE11, PE12のシリサイド膜SCが除去される問題が再び発生する。

【0091】

10

20

30

40

50

すなわちメモリセルFMSがゲートファーストプロセスにより形成され、周辺トランジスタTRがゲートラストプロセスにより形成されれば、メモリセルFMSの多結晶シリコン膜PE11, PE12が周辺トランジスタの第3のダミー電極PE3に対してどのような厚み(高さ)の大小関係となるように形成されようとも、上記のような問題が生じ得るため、最終製品の信頼性が低下する可能性がある。

【0092】

そもそも、メモリセルFMSがゲートファーストプロセスにより形成され、周辺トランジスタTRがゲートラストプロセスにより形成されるという製造方法は、一部の領域にゲートラストプロセスを施すだけのために工程数を増加する必要があるため、非常に煩雑である。

10

【0093】

そこで一実施の形態のように、メモリセルFMSと周辺トランジスタTRとの双方をゲートラストプロセスにより形成することにより、周辺トランジスタTRがゲートラストプロセスにより形成される比較例の工程に比べて工程数を増加することなく、より信頼性の高い半導体装置を提供することができるという知見が得られた。

【0094】

具体的には、一実施の形態のように、第1, 第2のダミー電極PE1, PE2が第3のダミー電極PE3に比べて厚く形成されることが好ましい。このようにすれば、メモリセルの電極の型崩れを抑制し、かつ周辺トランジスタの微細化により周辺トランジスタを薄くすることができる。また、第2のダミー電極PE2は、第1のダミー電極PE1の側壁部に形成されているため、第2のダミー電極PE2の上面は斜めになっている。そのため、図10に示す工程において、第2のダミー電極PE2が第3のダミー電極PE3よりも高くないと、第2のダミー電極PE2の露出部が狭くなってしまい、図11の工程で、第2の電極を除去するのが困難になってしまふ。また、図12の工程で、開口部に金属膜を埋め込むのも困難になる。そのため、一実施の形態では、第2のダミー電極PE2が第3のダミー電極PE3よりも高くなるようにしている。

20

【0095】

第1, 第2のダミー電極PE1, PE2が第3のダミー電極PE3に比べて厚く形成される場合、第3のダミー電極PE3の上面が研磨されることにより第1, 第2の電極の上面も研磨される。このように第1, 第2のダミー電極PE1, PE2の上面が研磨されて開口部が形成されることにより、後の工程において当該開口部を通じて第1, 第2のダミー電極PE1, PE2を確実に除去することができる。

30

【0096】

このように、一実施の形態では、メモリセルFMSのダミーのコントロールゲートである第1のダミー電極PE1と、ダミーのメモリゲートである第2のダミー電極PE2とが、周辺トランジスタTRのダミーのゲートである第3のダミー電極PE3よりも高く形成される。このため、CMPによる平坦化工程後に、ダミーのコントロールゲートとダミーのメモリゲートとダミーのゲートとを確実に除去し、その除去後の開口部に金属膜を埋め込むことができる。そして、メモリセルFMSと周辺トランジスタTRとをともに容易にゲートラストプロセスで形成することができる。

40

【0097】

この結果、図14～図19に示す工程のように周辺トランジスタはゲートラストプロセスとしメモリセルはゲートファーストプロセスとする作り分けをする必要がなくなり、プロセス工程数を大幅に削減することが可能となる。その結果、工程数が削減したことにより特性ばらつきの影響も小さくなり、半導体装置としての信頼性が向上する。

【0098】

なお、第1, 第2のダミー電極PE1, PE2が第3のダミー電極PE3に比べて厚く形成されることは、第1, 第2のダミー電極PE1, PE2は後工程において除去される電極であるためまったく問題はない。第1, 第2のダミー電極PE1, PE2が第3のダミー電極PE3に比べて厚く形成されることにより、メモリセルの側壁絶縁膜SWおよび

50

メモリゲート絶縁膜M Iの高さ(厚み)が最終的に周辺トランジスタとほぼ等しい高さ(厚み)を有するものとすることができます。

【0099】

次に一実施の形態においては、いったん形成された多結晶シリコンからなるダミー電極P E 1～P E 3が除去され、その後にコントロールゲート膜C G、メモリゲート膜M Gおよびゲート膜G Eが形成される。これらは金属含有膜M T 1～M T 3を含むために、多結晶シリコンのダミー電極P E 1～P E 3よりも抵抗が小さくなる。このため、周辺トランジスタおよびメモリセルの微細化に伴う抵抗の増加を抑制することができる。金属含有膜M T 1～M T 3は多結晶シリコン膜P L Yを含んでいるが、金属膜M Lを含むことにより、十分に抵抗値を下げることができる。

10

【0100】

またコントロールゲート膜C Gおよびメモリゲート膜M Gなどが金属膜M Lを含むことにより、ゲート空乏化が抑制される。そのため反転ゲート容量が大きくなり短チャネル特性を改善することが可能となる。

【0101】

メモリゲート膜M Gなどが金属膜M Lを含むことにより、メモリゲート膜M Gの仕事関数の変化を通じてメモリゲート膜M Gからシリコン窒化膜N Fへの電子の注入を抑制することができ、結果的にメモリセルF M Sをより深く(確実に)データ消去することができる。

20

【0102】

またコントロールゲート膜C Gなどが高誘電率絶縁膜H Kを有することにより、コントロールゲート絶縁膜C Iなどの薄膜化が困難となっても高い容量性を維持することができる。

【0103】

ところが高誘電率絶縁膜H Kを用いた場合、メモリゲート膜M Gの仕事関数の制御が困難になる可能性がある。そこで仕事関数の調整膜W A Jを形成することにより、メモリゲート膜M Gの仕事関数が調整できる。ただし調整膜W A Jは熱に弱いため、たとえば調整膜W A Jを含むメモリゲート膜M Gの形成後にソース領域S Rやドレイン領域D Rのアニールなどの熱処理がなされると、仕事関数の調整が不可になる可能性がある。

【0104】

30

そこでメモリセルF M Sを構成するコントロールゲート膜C Gおよびメモリゲート膜M Gを形成する前に、ダミー電極P E 1, P E 2を形成し、上記の(高温)熱処理を含む通常のトランジスタのプロセスの後にダミー電極P E 1, P E 2を除去したうえで、調整膜W A Jを含むコントロールゲート膜C Gおよびメモリゲート膜M Gが形成される、いわゆるゲートラストプロセスがなされる。このようにすれば、調整膜W A Jが熱による悪影響を被ることが抑制され、仕事関数の調整がより容易になれる。その結果、メモリゲート膜M Gのデータの消去などをより確実に(より深く)行なうことができる。

【0105】

コントロールゲート膜C Gおよびメモリゲート膜M Gはダミー電極P E 1, P E 2に比べて低抵抗であるため、コントロールゲート膜C Gおよびメモリゲート膜M Gの形成後はこの上面にシリサイド膜S Cを形成する必要がない。このためコントロールゲート膜C Gおよびメモリゲート膜M Gの形成後には上記のようにアニールなど高温の熱処理の必要がなくなり、上記の効果を奏すことができる。さらにコントロールゲート膜C Gおよびメモリゲート膜M Gの上面にシリサイド膜S Cが形成されないため、これらの電極上のシリサイド膜S C同士が接触することに起因する両者の短絡を抑制することもできる。

40

【0106】

なお上記のように、図10のC M P工程1においてダミー電極P E 1, P E 2などの上面が完全に露出するように研磨がなされることが好ましい。このようにすれば、図11の工程においてダミー電極P E 1, P E 2などを確実に除去することができる。

【0107】

50

さらに周辺トランジスタのゲート膜 G E についてもメモリセルのコントロールゲート膜 C G およびメモリゲート膜 M G と同様の構成を有することにより、周辺トランジスタ T R をより高容量化、低抵抗化することができる。また周辺トランジスタのゲート膜 G E とメモリセルのコントロールゲート膜 C G およびメモリゲート膜 M G とを同時に形成することができるので、工程数の増加を抑制することができる。

#### 【0108】

##### (実施の形態2)

図22を参照して、本実施の形態の半導体装置は、図2に示す実施の形態1の半導体装置と大筋で同様の構成を備えている。しかし本実施の形態においては、金属含有膜 M T 1 ~ M T 3 が多結晶シリコン P L Y を含まず金属膜 M L のみになっている点で、実施の形態1と相違する。金属膜 M L はたとえば窒化チタンの薄膜である。

10

#### 【0109】

本実施の形態の金属含有膜 M T 1 ~ M T 3 は、実施の形態1の金属含有膜 M T 1 ~ M T 3 とほぼ同じ厚みを有する。本実施の形態の金属膜 M L の膜厚は、実施の形態1の金属膜 M L と多結晶シリコン膜 P L Y との厚みの和にほぼ等しい。

#### 【0110】

本実施の形態は上記の点においてのみ実施の形態1と異なっており、他の点においては実施の形態1と同様であるため、実施の形態1と同一の構成要素については図22においても実施の形態1と同一の符号を付し、その説明を繰り返さない。このことは以降の各実施の形態においても同様である。

20

#### 【0111】

実施の形態1においては、金属含有膜 M T 1 ~ M T 3 を形成するために金属膜 M L と多結晶シリコン膜 P L Y との2層を形成する必要があるが、本実施の形態においては金属膜 M L の1層のみを形成すればよい。このためプロセスがより簡略化される。

#### 【0112】

また多結晶シリコン膜 P L Y の代わりに金属である窒化チタンの薄膜が配置されることにより、金属含有膜 M T 1 ~ M T 3 全体の抵抗を減少させることができる。

#### 【0113】

##### (実施の形態3)

図23を参照して、本実施の形態においては、メモリゲート絶縁膜 M I を構成するシリコン窒化膜 N F の延長部において、その端部がシリコン酸化膜 O 1 , O 2 の延長部の端部よりも内側に形成されている。その結果、シリコン窒化膜 N F の延長部の端部はメモリゲート膜 M G の端部(図23の右側の側面)よりも内側に形成されている。なおここで内側とは図23の左側(コントロールゲート膜 C G の配置される側)である。

30

#### 【0114】

シリコン窒化膜 N F は、下記のようにオーバーエッチングされることにより、その端部がメモリゲート膜 M G の端部よりも内側に形成され、その後の側壁絶縁膜 S W が形成される際に、当該絶縁膜によりシリコン窒化膜 N F の端部の外側が埋め込まれる。ただし他の実施の形態と同様に、メモリゲート絶縁膜 M I のシリコン酸化膜 O 1 , O 2 の端部は、メモリゲート膜 M G の端部と同一平面を有する(ツライチとなる)ように形成されている。

40

#### 【0115】

図23の構成は、以下に述べる方法により形成される。

図6と同様にメモリセルの形成領域にメモリゲート絶縁膜 M I と第2のダミー電極 P E 2 とが形成された後、半導体基板 S U B の主表面の、ソース領域 S R よりも内側(図23における左側)に高濃度注入ソース M S が形成される。この高濃度注入ソース M S はソース領域 S R などと同様にイオン注入により形成される。高濃度注入ソース M S における不純物濃度は、ソース領域 S R と位置的に連続するように形成される。

#### 【0116】

当該メモリセルがホットホール消去型である場合には、高濃度注入ソース M S は、高濃度注入による急峻なプロファイルが必要なため L D D としないことが好ましい。しかし当

50

該メモリセルがトンネル消去型である場合には、高濃度注入ソースM Sは高濃度である必要はなく、通常のM I Sトランジスタと同様に短チャネル特性が良くなるように低濃度化してもよい。

【0117】

高濃度注入ソースM Sの形成後、メモリゲート絶縁膜M Iのシリコン窒化膜N Fのみが、選択的に延長部の端部からオーバーエッティングされる。この処理により、メモリゲート絶縁膜M Iの中でもシリコン窒化膜N Fのみ、その端部がメモリゲート膜M Gの端部よりも内側に形成される。

【0118】

本実施の形態の構成は、以上の構成を有するために、メモリセルF M Sのデータの消去の効率を高めることができる。このことについて以下に説明する。 10

【0119】

高濃度注入ソースM Sは、シリコン窒化膜N Fに正孔を注入してメモリセルF M Sのデータを消去する際に、高濃度注入ソースM Sの端部の近傍における半導体基板S U Bのシリコンに正孔を形成させ、当該正孔を電界により加速させてシリコン窒化膜N F中に注入させるために配置される。

【0120】

しかしながら、シリコン窒化膜N Fが配置されていれば、当該領域においては正孔を加速させる電界が弱くなるために、高濃度注入ソースM Sの真上のシリコン窒化膜N Fには正孔が注入されにくくなる。その結果、データの消去が遅くなる可能性がある。 20

【0121】

具体的には、仮に高濃度注入ソースM Sの真上にメモリゲート膜M Gがオーバーラップすれば、高濃度注入ソースM Sの真上にあるシリコン窒化膜N Fには通常は正孔は注入されない。特にいわゆるE x t e n s i o nと呼ばれる不純物の拡散領域が形成された場合にはそのようになる。この場合にはメモリゲート膜M Gと高濃度注入ソースM Sとの間の電界強度は変化せず、データの消去は通常通りになされる。しかしながら仮に高濃度注入ソースM Sの真上のシリコン窒化膜N Fに正孔が注入されれば、注入された正孔はオーバーラップされたメモリゲート膜M Gにまで移動できる。そのようになれば、メモリゲート膜M Gと高濃度注入ソースM Sとの間の電界強度が弱くなり、データの消去が遅くなる。 30

【0122】

そこで図23のように、高濃度注入ソースM Sの真上にはシリコン窒化膜N Fが配置されない様とすることにより、正孔を加速させる電界が弱くなることが抑制され、より高効率に正孔がシリコン窒化膜N F中に注入される。したがってメモリセルF M Sのデータの消去の効率をより高めることができる。

【0123】

(実施の形態4)

図24を参照して、本実施の形態、および以上に述べた各実施の形態のメモリセルF M Sおよび周辺トランジスタT Rは、たとえばシリコンの単結晶により形成された半導体ウェハW F Rに形成されている。具体的には、半導体ウェハW F Rの主表面には互いに間隔をあけて複数のチップ領域C R(素子形成領域)が行列状に配置されている。このチップ領域C Rに、上記のメモリセルF M Sおよび周辺トランジスタT Rなどの半導体素子が形成される。なお上記の半導体基板S U Bとは半導体ウェハW F Rの土台としての基板を意味し、実質的に半導体ウェハW F Rと半導体基板S U Bとは同義である。 40

【0124】

隣り合う1対のチップ領域C Rに挟まれた領域、言い換えればチップ領域C Rの周囲に形成された領域はダイシング領域D L Rであり、ダイシング領域D L Rにおいて1枚の半導体ウェハW F Rがチップ領域C Rごとに分割された半導体チップとして形成される。

【0125】

図25を参照して、ダイシング領域D L Rは半導体ウェハW F Rが切断される領域であるため、ここにはメモリセルF M Sなどを形成するための位置合わせ用マークなどが形成 50

される。ただしこのダイシング領域 D L R には、少なくともその一部に、構造体形成領域 F M R が形成されており、構造体形成領域 F M R には複数の構造体 F F M S が形成されている。

【 0 1 2 6 】

図 2 6 を参照して、ダイシング領域 D L R の構造体 F F M S は、ダミーとして形成されるものであるため、たとえば多結晶シリコンの薄膜により形成されるなど、メモリセル F M S およびトランジスタ T R の電極とは異なる構成や材質であってもよい。

【 0 1 2 7 】

図 2 7 を参照して、ダイシング領域 D L R の構造体 F F M S は、図 5 に示す第 1 の積層構造を形成する工程、または図 6 に示す第 2 の積層構造を形成する工程と同時に、ダイシング領域に対して形成されることが好ましい。上記のとおり構造体 F F M S の構成や材質は第 1 および第 2 の積層構造の電極などとは異なっていてもよい。

【 0 1 2 8 】

構造体 F F M S は、第 1 または第 2 の積層構造の厚み（高さ）とほぼ同じ厚みとなるように形成されることが好ましい。なお第 2 の積層構造を構成する第 2 のダミー電極 P E 2 は、エッチバックされることによりその断面形状が右肩下がりになるためその厚み（高さ）が一定にならない。ここでは第 2 の積層構造の厚み（高さ）とはその最大の厚みであり、第 1 の積層構造の上面と同一平面をなす上面部（ツライチとなった部分）の厚みを意味するものとする。

【 0 1 2 9 】

上記の各実施の形態において形成される第 1 のダミー電極 P E 1 と第 2 のダミー電極 P E 2 とほぼ同じ高さの構造体 F F M S が形成されれば、たとえば図 1 0 に示す工程のようにダミー電極 P E 1 , P E 2 の上面が研磨される C M P がなされる場合に、構造体 F F M S が C M P の際に半導体基板 S U B 側に加わる力を支えることができる。このため、たとえばダミー電極 P E 1 , P E 2 とダミー電極 P E 3 との厚みが異なる場合においても、半導体基板 S U B の位置に対する C M P の加工量のばらつきなどを低減し、より均一に C M P の研磨がなされる。

【 0 1 3 0 】

構造体 F F M S の支持の下でダミー電極 P E 1 ~ P E 3 が C M P により、構造体 F F M S と高さが同一となるように研磨されれば、図 2 6 に示すように、その後形成されるコントロールゲート膜 C G 、メモリゲート膜 M G およびゲート膜 G E と、構造体 F F M S との高さがほぼ同一となるようにすることができる。

【 0 1 3 1 】

上記の C M P は、ゲートラストプロセスを行なう際にメモリセル F M S およびトランジスタ T R のダミー電極 P E 1 , P E 2 などを効果的に除去するために極めて重要な工程であり、 C M P の加工量にばらつきが生じれば、最終的に形成されるメモリセル F M S などの電極の形状に異常を来たす可能性がある。しかしながら上記のようにダイシング領域 D L R にダミーの構造体 F F M S を形成することにより、 C M P の加工精度を高めることができるために、最終的に形成されるメモリセル F M S などの信頼性を高めることができる。

【 0 1 3 2 】

その他、実施の形態に記載された内容の一部を以下に記載する。

( 1 ) 半導体装置は、半導体基板の主表面に形成されるメモリセルと周辺トランジスタとを備える半導体装置である。上記メモリセルは、主表面に形成される第 1 の絶縁膜と、第 1 の絶縁膜の上面に接する第 1 の金属含有膜とが積層された第 1 のゲートを含む。上記メモリセルは、主表面に形成される、第 1 のゲートの側面に接するとともに半導体基板の主表面上にまで延びる延長部を有するように形成された第 2 の絶縁膜と、第 2 の絶縁膜の延長部の上面を含めて第 2 の絶縁膜に接する第 2 の金属含有膜とが積層された第 2 のゲートを含む。上記周辺トランジスタは、主表面に形成される第 3 の絶縁膜と、第 3 の絶縁膜の上面に接する第 3 の金属含有膜とが積層された第 3 のゲートを含む。上記第 1 、第 2 および第 3 の金属含有膜の上面は平坦な面である。

10

20

30

40

50

## 【0133】

(2)(1)の半導体装置において、上記第1、第2および第3のゲートの高さが同一である。

## 【0134】

(3)(1)の半導体装置において、上記第2の絶縁膜には電荷を蓄積する電荷蓄積膜を含む。

## 【0135】

(4)(1)の半導体装置において、上記電荷蓄積膜はシリコン窒化膜である。

(5)(1)の半導体装置において、上記第2の絶縁膜は、第1のシリコン酸化膜と、シリコン窒化膜と、第2のシリコン酸化膜とがこの順に積層された構成を有する。

10

## 【0136】

(6)(4)または(5)の半導体装置において、上記シリコン窒化膜の端部は、第2の金属含有膜の端部よりも内側に配置される。

## 【0137】

(7)(1)の半導体装置において、上記メモリセルは、主表面に形成され、第1および第2のゲートを挟むように配置されるドレイン領域およびソース領域を有する。上記ドレイン領域およびソース領域にはシリサイドが形成されている。

## 【0138】

(8)(1)の半導体装置において、上記周辺トランジスタは、主表面に形成され、第3のゲートを挟むように配置されるドレイン領域およびソース領域を有する。

20

## 【0139】

(9)(1)の半導体装置において、上記第1、第2および第3の金属含有膜は金属含有膜（他の膜を含んでもよい）を含む。上記金属含有膜は窒化チタンの薄膜のみから構成される。

## 【0140】

(10)(1)の半導体装置において、上記第1、第2および第3の金属含有膜は金属含有膜（他の膜を含んでもよい）を含む。上記金属含有膜は、窒化チタンの薄膜と、多結晶シリコンの薄膜とがこの順に積層された構成を有する。

## 【0141】

(11)(9)または(10)の半導体装置において、上記第1、第2および第3の金属含有膜は、第1、第2および第3の絶縁膜より誘電率が高い誘電体膜と、高誘電率絶縁膜の仕事関数を調整する調整膜と、金属含有膜とがこの順に積層された構成を有する。

30

## 【0142】

(12)(1)の半導体装置において、上記主表面には、メモリセルおよび周辺トランジスタが形成される素子形成領域と、素子形成領域の周囲に形成されるダイシング領域とを有する。上記ダイシング領域には、第1、第2および第3のゲートと同じ厚みを有する構造体が形成される工程をさらに備える。

## 【0143】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

40

## 【符号の説明】

## 【0144】

C G コントロールゲート膜、C I コントロールゲート絶縁膜、C R チップ領域、C V 1 , C V 2 , C V 3 開口部、D L R ダイシング領域、D R ドレイン領域、F F M S 構造体、F M R 構造体形成領域、F M S メモリセル、G E ゲート膜、G I ゲート絶縁膜、H K 高誘電率絶縁膜、I I 層間絶縁層、M G メモリゲート膜、M I メモリゲート絶縁膜、M L 金属膜、M S 高濃度注入ソース、M T 1 , M T 2 , M T 3 金属含有膜、N F シリコン窒化膜、O 1 , O 2 シリコン酸化膜、P E 1 第1のダミー電極、P E 2 第2のダミー電極、P E 3 第3のダミー電極、P L Y 多結晶シ

50

リコン膜、S C シリサイド膜、S R ソース領域、S U B 半導体基板、S W 側壁絶縁膜、T R トランジスタ、W A J 調整膜、W F R 半導体ウェハ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

【 図 1 2 】

### 【 図 1 3 】

### 【図14】

【図15】

図15

メモリセル形成領域

【図16】

図16

【図17】

図17

メモリセル形成領域

【図18】

図18

メモリセル形成領域

【図19】

図19

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

【図24】

【図25】

【図26】

【図27】

図27

ダイシング領域

メモリセル形成領域

周辺トランジスタ形成領域

---

フロントページの続き

(51)Int.Cl. F I

H 01L 27/10 (2006.01)

H 01L 29/423 (2006.01)

H 01L 29/49 (2006.01)

(72)発明者 國清 辰也

神奈川県川崎市中原区下沼部1753番地 ルネサスエレクトロニクス株式会社内

審査官 小山 满

(56)参考文献 特開2011-049282 (JP, A)

特開2003-318290 (JP, A)

米国特許出願公開第2011/0309434 (US, A1)

特開2009-059927 (JP, A)

特開2010-245345 (JP, A)

特開2004-303918 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/8247

H 01L 21/336

H 01L 27/10

H 01L 27/115

H 01L 29/423

H 01L 29/49

H 01L 29/788

H 01L 29/792