(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4602112号

(P4602112)

(45) 発行日 平成22年12月22日(2010.12.22)

(24) 登録日 平成22年10月8日(2010.10.8)

|                        |                  |

|------------------------|------------------|

| (51) Int.Cl.           | F 1              |

| H01L 21/82 (2006.01)   | H01L 21/82 C     |

| H01L 21/3205 (2006.01) | H01L 21/88 Z     |

| H01L 23/52 (2006.01)   | H01L 21/90 A     |

| H01L 21/768 (2006.01)  | G06F 17/50 658 J |

| G06F 17/50 (2006.01)   |                  |

請求項の数 4 (全 22 頁)

(21) 出願番号 特願2005-41158 (P2005-41158)

(22) 出願日 平成17年2月17日 (2005.2.17)

(65) 公開番号 特開2006-228987 (P2006-228987A)

(43) 公開日 平成18年8月31日 (2006.8.31)

審査請求日 平成19年12月11日 (2007.12.11)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100083806

弁理士 三好 秀和

(74) 代理人 100100712

弁理士 岩▲崎▼ 幸邦

(74) 代理人 100100929

弁理士 川又 澄雄

(74) 代理人 100108707

弁理士 中村 友之

(74) 代理人 100095500

弁理士 伊藤 正和

(74) 代理人 100101247

弁理士 高橋 俊一

最終頁に続く

(54) 【発明の名称】半導体集積回路の製造方法及び半導体集積回路

## (57) 【特許請求の範囲】

## 【請求項1】

ビアセル作成部が、設計データ記憶装置に記憶された設計情報に基づいて、チップ領域上に下層配線パターン及び前記下層配線パターンの上層に前記下層配線パターンに直交する上層配線パターンをそれぞれ配置するステップと、

前記上層配線パターンの長手方向に直交する方向に前記上層配線パターンと接続される第1迂回パターン及び前記第1迂回パターンの長手方向に直交する方向に前記第1迂回パターンと接続される第2迂回パターンとを含む迂回パターンを前記下層及び上層配線パターンのいずれかに設定するステップと、

前記下層及び上層配線パターン間を接続する複数のビアパターンを前記下層及び上層配線パターンとの交点及び前記迂回パターン上に設定するステップと、

前記迂回パターン及び前記ビアパターンによりビアセルパターンを作成し、該ビアセルパターンの情報をビアセル記憶装置に記憶させるステップと、

前記設計情報に基づいて、前記迂回パターンの終端部に該終端部が配置された前記下層配線パターン及び上層配線パターンのいずれかの優先方向に平行な方向に終端補正パターンを配置するステップ

を含む工程により作成される設計データを用いることを特徴とする半導体集積回路の製造方法。

## 【請求項2】

前記工程は、レイアウト設計部が、フロアプラン記憶装置に記憶されたフロアプランの

10

20

情報に基づいて、前記チップ領域上に前記下層及び上層配線パターンを配置し、前記上層及び前記下層配線パターンが平面パターン上で交わる前記交点の周囲の環境に適合するビアセルパターンを前記ビアセル記憶装置の中から抽出し、前記交点に配置するステップとを更に含むことを特徴とする請求項 1 に記載の半導体集積回路の製造方法。

### 【請求項 3】

下層配線と、

前記下層配線上に配置された層間絶縁膜と、

前記層間絶縁膜の中に埋め込まれ、前記下層配線に接続された第 1 及び第 2 ビアと、

前記層間絶縁膜上に配置され、前記下層配線の長手方向に対して垂直に延伸し、平面パターン上、前記下層配線と前記第 1 ビアの位置で交わる上層配線と、

前記層間絶縁膜上において前記上層配線に接続され、前記上層配線の長手方向に直交する方向に形成された第 1 迂回配線と、

前記層間絶縁膜上において第 1 迂回配線に接続され、前記第 1 迂回配線に直交する方向に延伸し、平面パターン上、前記下層配線と前記第 2 ビアの位置で交わる第 2 迂回配線と、

前記層間絶縁膜上において前記第 2 迂回配線に接続され、前記第 2 迂回配線に直交する方向に形成された第 3 迂回配線と、

前記層間絶縁膜上において前記第 3 迂回配線に接続され、前記第 3 迂回配線に直交する方向に形成された第 4 迂回配線と、

前記層間絶縁膜の中に埋め込まれ、前記下層配線及び前記第 4 迂回配線が平面パターン上で交わる交点で前記下層配線及び前記第 4 迂回配線にそれぞれ接続された第 3 のビアとを備えることを特徴とする半導体集積回路。

### 【請求項 4】

下層配線と、

前記下層配線と同一配線層上において前記下層配線から離間し、前記下層配線の長手方向に対して並行に配置された第 1 迂回配線と、

前記下層配線及び前記第 1 迂回配線の上に配置された層間絶縁膜と、

前記層間絶縁膜に埋め込まれ、前記下層配線に接続された第 1 及び第 2 ビアと、

前記層間絶縁膜に埋め込まれ、前記第 1 迂回配線に接続された第 3 及び第 4 ビアと、

前記層間絶縁膜上に配置され、前記下層配線の長手方向に対して垂直に延伸し、平面パターン上、前記下層配線と第 1 ビアの位置で、前記第 1 迂回配線と前記第 3 ビアの位置でそれぞれ交わる上層配線と、

前記上層配線と同一配線層上において前記上層配線から離間し、前記上層配線の長手方向に対して並行に配置され、前記第 4 ビアを介して前記第 1 迂回配線に接続され、前記第 2 ビアを介して前記下層配線に接続された第 2 迂回配線

とを備えることを特徴とする半導体集積回路。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は半導体集積回路に係り、特に、上下層の配線を複数のビアを用いて接続するための半導体集積回路の製造方法及び半導体集積回路に関する。

#### 【背景技術】

#### 【0002】

半導体集積回路の微細化要求に伴い、素子間を接続する配線の形状を設計通りに形成することが困難になってきている。特に、多層配線化が進む半導体集積回路においては、光近接効果( O P E )等により多層配線層内の一層における配線の終端部が予め設定された形状より短く形成される場合がある。この結果、ビアホールの位置まで配線が達しない現象(ショートニング)が発生し、接続不良を生じる。

#### 【0003】

配線の微細化要求によるビアの高アスペクト化も進んでおり、ビアプラグをビアホール

10

20

30

40

50

に埋め込むことがより困難になってきている。所望の位置にビアが形成されないと、信頼性や歩留まりの低下を招く。このため、ビアの欠損を抑制し、信頼性及び歩留まりの向上を図るための手法が検討されている。

#### 【0004】

配線のショートニングの発生を抑制する方法として、ビアの配置される配線領域を予め延長・拡大しておく方法が用いられている。ビアの欠損による信頼性低下を抑制する方法としては、1つのビア（シングルカットビア）を配置する代わりに2つのビア（ダブルカットビア）を配置することにより、上下の配線層の接続を確実にする方法が提案されている（例えば、特許文献1参照）。

#### 【0005】

10

しかし、配線の優先方向が縦横方向に交互に設定される多層配線層内においては、上下の配線層を接続する2つのビアを配置するために、各配線層において優先方向とは異なる向きに配線を延長させている。このため、配線を延長させた部分の周囲には、優先方向に延伸する他の配線を隣接させて配置することができず、配線効率の低下を招く。特に、グリッドを基準として配線設計する設計装置においては、優先方向に反する延長部分の配線の敷設により、本来敷設可能であった優先方向のグリッドを多く消費することになるため、配線効率が低下する。この結果、高密度化が困難となり、チップサイズの増大を招く。

#### 【0006】

【特許文献1】特開平10-125775号公報

#### 【発明の開示】

20

#### 【発明が解決しようとする課題】

#### 【0007】

本発明は、上下の配線層を複数のビアを用いて接続する場合に、複数のビアの周辺に隣接する配線を敷設可能とし、信頼度及び歩留まりを向上可能な半導体集積回路の製造方法及び半導体集積回路を提供する。

#### 【課題を解決するための手段】

#### 【0008】

上記目的を達成するために、本発明の第1の特徴は、（イ）ビアセル作成部が、設計データ記憶装置に記憶された設計情報に基づいて、チップ領域上に下層配線パターン及び下層配線パターンの上層に下層配線パターンに直交する上層配線パターンをそれぞれ配置するステップと、（ロ）上層配線パターンの長手方向に直交する方向に上層配線パターンと接続される第1迂回パターン及び第1迂回パターンの長手方向に直交する方向に第1迂回パターンと接続される第2迂回パターンとを含む迂回パターンを下層及び上層配線パターンのいずれかに設定するステップと、（ハ）下層及び上層配線パターン間を接続する複数のビアパターンを下層及び上層配線パターンとの交点及び迂回パターン上に設定するステップと、（ニ）迂回パターン及びビアパターンによりビアセルパターンを作成し、ビアセルパターンの情報をビアセル記憶装置に記憶させるステップと、（ホ）設計情報に基づいて、迂回パターンの終端部に終端部が配置された下層配線パターン及び上層配線パターンのいずれかの優先方向に平行な方向に終端補正パターンを配置するステップを含む工程により作成される設計データを用いる半導体集積回路の製造方法であることを要旨とする。

30

#### 【0009】

第2の特徴は、（イ）下層配線と、（ロ）下層配線上に配置された層間絶縁膜と、（ハ）層間絶縁膜の中に埋め込まれ、下層配線に接続された第1及び第2ビアと、（ニ）層間絶縁膜上に配置され、下層配線の長手方向に対して垂直に延伸し、平面パターン上、下層配線と第1ビアの位置で交わる上層配線と、（ホ）層間絶縁膜上において上層配線に接続され、上層配線の長手方向に直交する方向に形成された第1迂回配線と、（ヘ）層間絶縁膜上において第1迂回配線に接続され、第1迂回配線に直交する方向に延伸し、平面パターン上、下層配線と第2ビアの位置で交わる第2迂回配線と、（ト）層間絶縁膜上において第2迂回配線に接続され、第2迂回配線に直交する方向に形成された第3迂回配線と、（チ）層間絶縁膜上において第3迂回配線に接続され、第3迂回配線に直交する方向に形

40

50

成された第4迂回配線と、(リ)層間絶縁膜の中に埋め込まれ、下層配線及び第4迂回配線が平面パターン上で交わる交点で下層配線及び第4迂回配線にそれぞれ接続された第3のビアとを備える半導体集積回路であることを要旨とする。

#### 【0010】

第3の特徴は、(イ)下層配線と、(ロ)下層配線と同一配線層上において下層配線から離間し、下層配線の長手方向に対して並行に配置された第1迂回配線と、(ハ)下層配線及び第1迂回配線の上に配置された層間絶縁膜と、(ニ)層間絶縁膜に埋め込まれ、下層配線に接続された第1及び第2ビアと、(ホ)層間絶縁膜に埋め込まれ、第1迂回配線に接続された第3及び第4ビアと、(ヘ)層間絶縁膜上に配置され、下層配線の長手方向に対して垂直に延伸し、平面パターン上、下層配線と第1ビアの位置で、第1迂回配線と第3ビアの位置でそれぞれ交わる上層配線と、(ト)上層配線と同一配線層上において上層配線から離間し、上層配線の長手方向に対して並行に配置され、第4ビアを介して第1迂回配線に接続され、第2ビアを介して下層配線に接続された第2迂回配線とを備える半導体集積回路であることを要旨とする。10

#### 【発明の効果】

#### 【0011】

本発明によれば、上下の配線層を複数のビアを用いて接続する場合に、複数のビアの周辺に隣接する配線を敷設可能とし、信頼度及び歩留まりを向上可能な半導体集積回路の製造方法及び半導体集積回路が提供できる。

#### 【発明を実施するための最良の形態】

#### 【0012】

次に、図面を参照して、本発明の実施の形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。また、図面は模式的なものであり、厚みと平均寸法の関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることは勿論である。以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の技術的思想は構成部品の材質、形状、構造、配置等を下記のものに特定するものではない。この発明の技術的思想は、特許請求の範囲において種々の変更を加えることができる。20

#### 【0013】

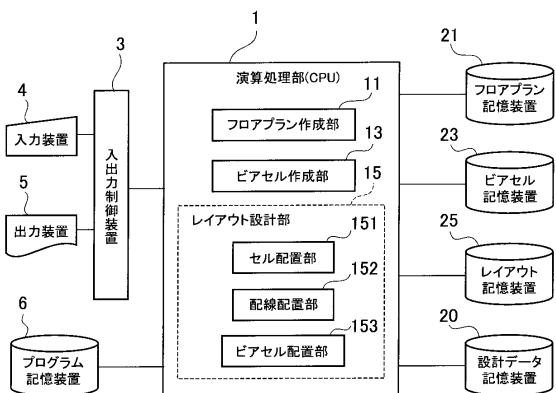

本発明の実施の形態に係る半導体集積回路の設計装置は、図1に示すように、レイアウト設計等の種々の演算を実行する演算処理部(CPU)1、CPU1に接続された入出力制御装置3、半導体集積回路のレイアウトプログラム等を記憶したプログラム記憶装置6、半導体集積回路のレイアウト設計に必要な設計データを記憶した設計データ記憶装置20、フロアプラン記憶装置21、ビアセル記憶装置23及びレイアウト記憶装置25を備える。入出力制御装置3には、入力装置4及び出力装置5が接続されている。30

#### 【0014】

CPU1は、フロアプラン作成部11、ビアセル作成部13及びレイアウト設計部15を備える。フロアプラン作成部11は、設計装置のメモリ空間内に設定されたチップ領域上に、論理セルや配線等を配置するためのフロアプランを作成する。フロアプラン記憶装置21は、フロアプラン作成部11が作成したフロアプランの情報を記憶する。40

#### 【0015】

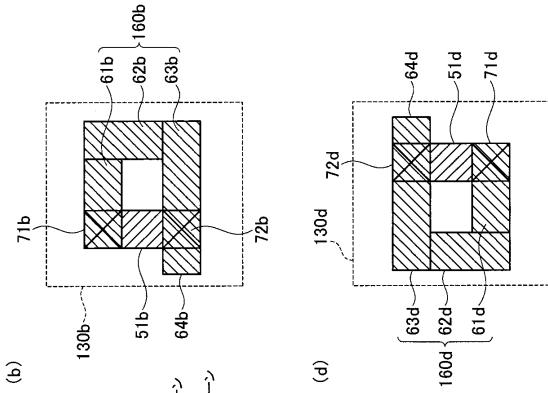

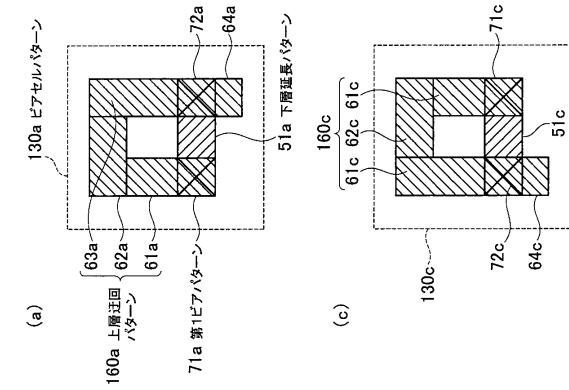

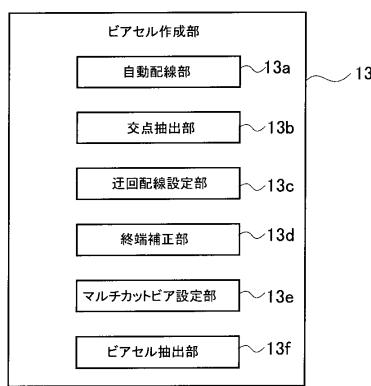

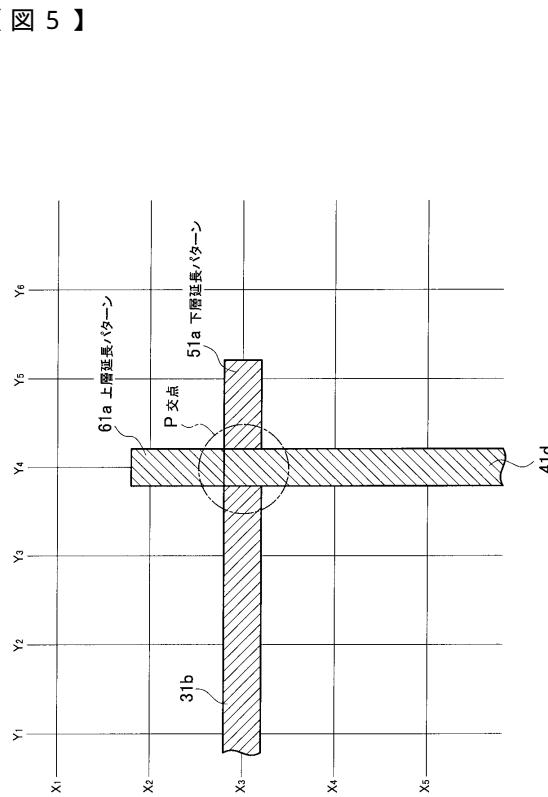

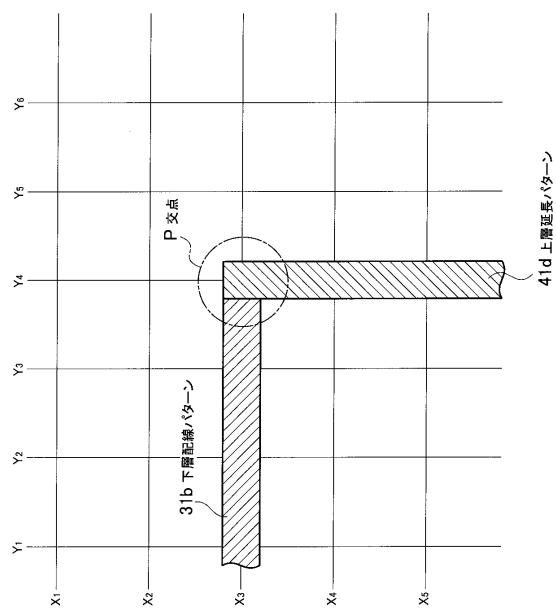

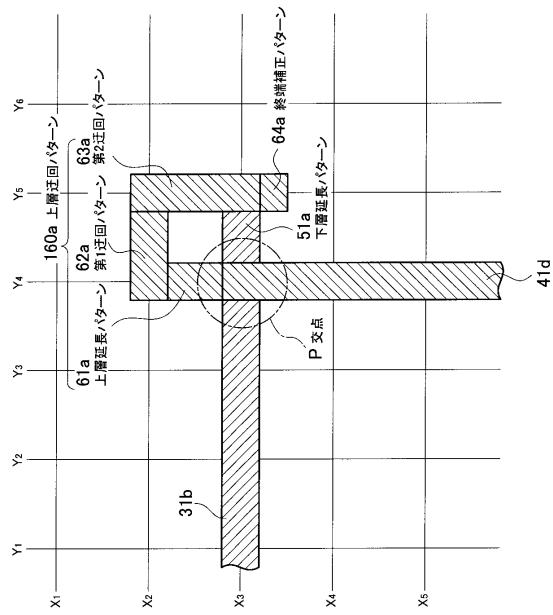

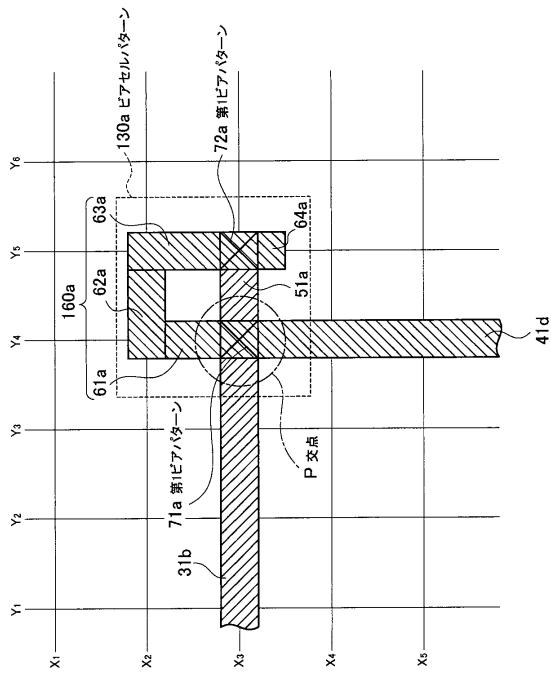

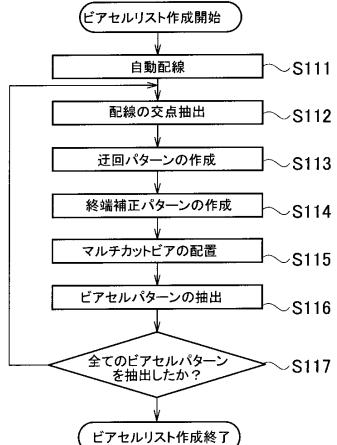

ビアセル作成部13は、チップ領域上の上下の配線層間を接続するビアとして、例えば、図3(a)～図3(d)に示すようなビアセルパターン130a～130dのリストを作成する。このため、ビアセル作成部13は、図2に示すように、自動配線部13a、交点抽出部13b、迂回配線設定部13c、終端補正部13d、マルチカットビア設定部13e及びビアセル抽出部13fを有する。

#### 【0016】

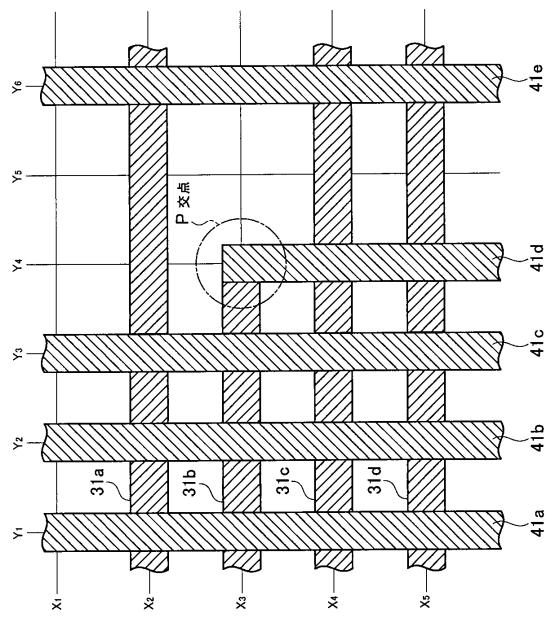

自動配線部13aは、図4に示すように、チップ領域上に設定されたグリッド $X_1, X_2, \dots, X_5$ 及びグリッド $X_1, X_2, \dots, X_5$ に直交するグリッド $Y_1, Y_2, \dots, Y_5$ を有する。50

<sub>6</sub>を基礎として、下層配線パターン31b及び上層配線パターン41dを配置する。図4においては、下層配線パターン31bは、下層配線パターン31bが配線される配線層の優先方向に平行なグリッドX<sub>3</sub>上に配置されている。上層配線パターン41dは、上層配線パターン41dが配線される配線層の優先方向に平行なグリッドY<sub>4</sub>上に配置されている。

#### 【0017】

図2の交点抽出部13bは、下層配線パターン31bと上層配線パターン41dとの平面パターン上の交点Pを抽出する。迂回配線設定部13cは、下層配線パターン31bと上層配線パターン41dとの交点Pに複数のビアを配置するための迂回パターンを作成する。例えば、図4に示すように、交点抽出部13bが抽出した交点Pが、下層配線パターン31b及び上層配線パターン41dそれぞれの終端部にある場合は、迂回配線設定部13cは、図5に示すように、交点Pから下層配線パターン31bを長手方向に延長させた下層延長パターン51aと交点Pから上層配線パターン41bを長手方向に延長させた上層延長パターン61aとをそれぞれ配置する。なお、下層配線パターン31b及び上層配線パターン41dの交点Pがそれぞれの終端部でない場合は、下層延長パターン51a及び上層延長パターン61aの配置は不要である。

#### 【0018】

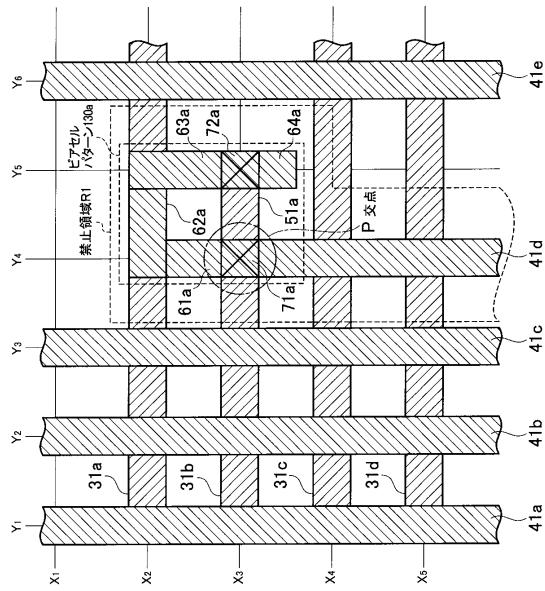

迂回配線設定部13cは、図6に示すように、上層延長パターン61aの端部に、上層延長パターン61aの長手方向に対して垂直な方向に第1迂回パターン62aを配置する。第1迂回パターン62aの端部には、第1迂回パターン62aの長手方向に対して垂直な方向に第2迂回パターン63aを配置する。この時、迂回配線設定部13cは、第2迂回パターン63aの終端部が下層延長パターン51aの終端部に重なるように第2迂回パターン63aを配置する。上層延長パターン61a、第1迂回パターン62a、及び第2迂回パターン63aにより、平面パターン上、「コの字型」を形成する上層迂回パターン160aが配置される。

#### 【0019】

終端補正部13dは、配線の終端部が設定値より短く形成されるのを防止するために、迂回配線設定部13cが設定した上層迂回パターン160aの終端部、即ち図6では第2迂回パターン63aと下層延長パターン51aとが交わる領域に終端補正パターン64aを配置する。

#### 【0020】

マルチカットビア設定部13eは、図7に示すように、交点P及び第2迂回パターン63aと下層延長パターン51aとの交点にそれぞれ第1ビアパターン71a及び第2ビアパターン72aを設定する。ビアセル抽出部13fは、第1ビアパターン71a及び第2ビアパターン72aとその周囲に存在する上層迂回パターン160a及び下層延長パターン51aの形状情報をビアセルパターン130aの情報として抽出する。ビアセル記憶装置23は、ビアセル作成部13が作成するビアセルパターン130aの情報を記憶する。

#### 【0021】

レイアウト設計部15は、フロアプラン記憶装置21に記憶されたフロアプランの情報を読み込んで、チップ領域上にセル、配線及びビアを自動設計する。レイアウト設計部15は、図1に示すように、セル配置部151、配線配置部152、及びビアセル配置部153を有する。

#### 【0022】

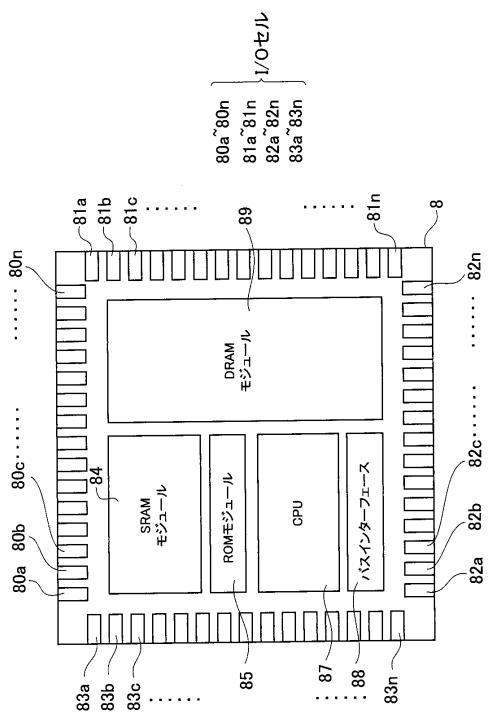

セル配置部151は、例えば図8に示すように、チップ領域の周辺領域にI/Oセル80a～80n, 81a～81n, 82a～82n, 83a～83nをそれぞれ配置し、I/Oセル80a～80n, 81a～81n, 82a～82n, 83a～83nで囲まれた領域にSRAMモジュール84, ROMモジュール85, CPU87, バスインターフェース88及びDRAMモジュール89等のマクロセル又は論理セル等を配置する。

#### 【0023】

配線配置部152は、図9に示すように、グリッドX<sub>1</sub>, X<sub>2</sub>, …, X<sub>5</sub>に沿ってそれ

10

20

30

40

50

それ平行に延伸する下層配線パターン31a～31dを、図8に示すチップ領域上の所望の位置に配置する。配線配置部152は、グリッドY<sub>1</sub>, Y<sub>2</sub>, …, Y<sub>6</sub>に沿ってそれぞれ平行に延伸する上層配線パターン41a～41eを下層配線パターン31a～31dの上層に配置する。

#### 【0024】

ビアセル配置部153は、配線配置部152が配置した下層配線パターン31a～31d及び上層配線パターン41a～41eの交点Pを抽出し、交点Pの周囲の図形環境に適合するビアセルパターン130aの情報を、ビアセル記憶装置23から抽出し、図10に示すように、交点Pに配置する。図1のレイアウト記憶装置25は、セル配置部151、配線配置部152及びビアセル配置部153が配置したレイアウト情報を記憶する。

10

#### 【0025】

入力装置4は、キーボード、マウス、ライトペン又はフレキシブルディスク装置等を含む。レイアウト実行者は、入力装置4より入出力データを指定したり自動設計に必要な数値等の設定が可能である。また、入力装置4より、出力データの形態等のレイアウトパラメータの設定、或いは演算の実行及び中止等の指示の入力も可能である。出力装置5は、ディスプレイ及びプリンタ装置等を含み、入出力データやレイアウト結果等を表示する。プログラム記憶装置6は、入出力データやレイアウトパラメータ及びその履歴や、演算途中のデータ等を記憶する。

#### 【0026】

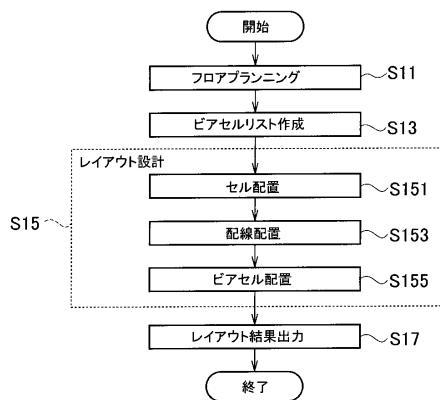

次に、実施の形態に係る半導体集積回路の設計方法の一例を、図11及び図12に示すフローチャートを用いて説明する。

20

#### 【0027】

(イ)ステップS11において、図1のフロアプラン作成部11は、設計データ記憶装置20に記憶された半導体集積回路の設計情報を読み出して、チップ領域上に論理セルや配線等を配置するためのフロアプランを作成する。そして、作成したフロアプランをフロアプラン記憶装置21に記憶させる。

#### 【0028】

(ロ)ステップS13において、ビアセル作成部13は、設計データ記憶装置20に記憶された半導体集積回路の設計情報を読み込む。ビアセル作成部13は、読み込んだ設計情報に基づいて、上下の配線層間を複数のビアで接続するための、図3(a)～図3(d)に例示するようなビアセルパターン130a～130dのリストを作成し、ビアセル記憶装置23に記憶させておく。ビアセルパターン130a～130dのリストの作成方法の詳細は後述する。

30

#### 【0029】

(ハ)ステップS15において、レイアウト設計部15は、設計データ記憶装置20に記憶された設計情報及びフロアプラン記憶装置21に記憶されたフロアプランの情報を読み込み、チップ領域上にレイアウト設計を行う。ステップS151において、セル配置部151は、設計データ記憶装置20に記憶された設計情報及びフロアプラン記憶装置21に記憶されたフロアプランの情報を読み込み、図8に示すように、チップ領域上に、I/Oセル80a～80n, 81a～81n, 82a～82n, 83a～83n、SRAMモジュール84, ROMモジュール85, CPU87, バスインターフェース88, DRAMモジュール89等のマクロセル又は論理セル等を配置する。得られたレイアウト情報は、レイアウト記憶装置25に記憶させる。

40

#### 【0030】

(ニ)ステップS153において、配線配置部152は、設計データ記憶装置20に記憶された設計情報及びフロアプラン記憶装置21に記憶されたフロアプランの情報を読み込む。配線配置部152は、図9に示すように、チップ領域上にグリッドX<sub>1</sub>, X<sub>2</sub>, …, X<sub>5</sub>及びグリッドX<sub>1</sub>, X<sub>2</sub>, …, X<sub>5</sub>に直交するグリッドY<sub>1</sub>, Y<sub>2</sub>, …, Y<sub>6</sub>を設定する。配線配置部152は、グリッドX<sub>1</sub>, X<sub>2</sub>, …, X<sub>5</sub>にそれぞれ平行に延伸する下層配線パターン31a～31dを配置し、下層配線パターン31a～31dの上層に、グ

50

リッド $Y_1, Y_2, \dots, Y_6$ にそれぞれ平行に延伸する上層配線パターン $41a \sim 41e$ を配置する。得られた配線のレイアウト情報は、レイアウト記憶装置25に記憶させる。

#### 【0031】

(ホ)ステップS155において、ピアセル配置部153は、設計情報、フロアプラン情報及びレイアウト記憶装置25に記憶された配線の配置情報を読み込んで、図9に示すように、下層配線パターン $31a \sim 31d$ 及び上層配線パターン $41a \sim 41e$ の交点Pを抽出する。ピアセル配置部153は、交点Pの周囲の図形環境に最適となるピアセルパターン $130a$ を、ピアセル記憶装置23から抽出し、図10に示すように、交点Pに配置する。得られたピアセルのレイアウト情報は、レイアウト記憶装置25に記憶させる。ステップS17において、出力装置5は、レイアウト記憶装置25に記憶されたセル、配線、ピアセルのレイアウト情報を出力し、作業を終了する。

10

#### 【0032】

ステップS15に示すピアセルパターン $130a$ の作成方法の詳細を、図12に示すフローチャートを用いて説明する。

#### 【0033】

(イ)ステップS111において、自動配線部13aは、設計データ記憶装置20に記憶された設計情報を読み込んで、図4に示すように、チップ領域上に、グリッド $X_1, X_2, \dots, X_5$ 、及びグリッド $X_1, X_2, \dots, X_5$ に直交するグリッド $Y_1, Y_2, \dots, Y_6$ を設定する。自動配線部13aは、グリッド $X_1, X_2, \dots, X_5$ に平行な方向を優先方向とする下層配線パターン $31b$ を、グリッド $X_3$ 上に配置する。自動配線部13aは、下層配線パターン $31a$ の上層に、グリッド $Y_1, Y_2, \dots, Y_6$ に平行な方向を優先方向とする上層配線パターン $41d$ を、グリッド $Y_4$ 上に配置する。自動配線部13aは、下層配線パターン $31b$ と上層配線パターン $41d$ の配置情報を、設計データ記憶装置20に記憶させる。

20

#### 【0034】

(ロ)ステップS112において、交点抽出部132は、設計データ記憶装置20に記憶された下層配線パターン $31b$ 及び上層配線パターン $41d$ の配置情報を読み込んで、図5に示すように、下層配線パターン $31b$ と上層配線パターン $41d$ との交点Pを抽出する。交点Pの情報は、設計データ記憶装置20に記憶させる。

#### 【0035】

(ハ)ステップS113において、迂回配線設定部13cは、設計データ記憶装置20に記憶された設計情報、下層配線パターン $31b$ 、上層配線パターン $41d$ 及び交点Pの配置情報を読み込んで、下層配線パターン $31b$ と上層配線パターン $41d$ とを複数のピアで接続するための上層迂回パターン $160a$ を作成する。例えば図5に示すように、交点抽出部13bが抽出した交点Pが、下層配線パターン $31b$ 及び上層配線パターン $41d$ それぞれの終端部である場合は、迂回配線設定部13cは、交点Pから下層配線パターン $31b$ の長手方向に延長させた下層延長パターン $51a$ と、交点Pから上層配線パターン $41b$ の長手方向に延長させた上層延長パターン $61a$ とをそれぞれ配置する。下層延長パターン $51a$ 及び上層延長パターン $61a$ の情報は、設計データ記憶装置20に記憶させる。

40

#### 【0036】

(ニ)さらに、迂回配線設定部13cは、図6に示すように、上層延長パターン $61a$ の端部に、上層延長パターン $61a$ に対して垂直な方向に第1迂回パターン $62a$ を配置する。第1迂回パターン $62a$ の端部には、第1迂回パターン $62a$ に対して垂直な方向に第2迂回パターン $63a$ を配置する。この時、迂回配線設定部13cは、第2迂回パターン $63a$ の終端部が、平面パターン上で下層延長パターン $51a$ に接続されるように、第2迂回パターン $63a$ を配置する。この結果、上層延長パターン $61a$ 、第1迂回パターン $62a$ 、及び第2迂回パターン $63a$ により、平面パターン上「コ」の字型をなす上層迂回パターン $160a$ が形成される。上層迂回パターン $160a$ 及び下層延長パターン $51a$ の情報は、設計データ記憶装置20に記憶させる。

50

## 【0037】

(ホ)ステップS114において、終端補正部13dは、設計データ記憶装置20に記憶された設計情報、下層延長パターン51a及び上層迂回パターン160a等の配置情報を読み込んで、上層迂回パターン160aの終端、即ち第2迂回パターン63aの終端部を抽出し、終端部の長手方向に終端補正パターン64aを配置する。終端補正パターン64aの配置情報は、設計データ記憶装置20に記憶させる。

## 【0038】

(ヘ)ステップS115において、マルチカットビア設定部13eは、図7に示すように、設計データ記憶装置20に記憶された設計情報及びレイアウト情報等を読み込んで、下層配線パターン31bと上層配線パターン41dとの交点Pと第2迂回パターン63aの終端部に、それぞれ第1ビアパターン71a及び第2ビアパターン72aを設定する。マルチカットビア設定部13eが設定したレイアウト情報は、設計データ記憶装置20に格納させる。

## 【0039】

(ト)ステップS116において、ビアセル抽出部13fは、設計データ記憶装置20に格納された設計情報及びレイアウト情報を読み込んで、第1ビアパターン71a及び第2ビアパターン72aとその周囲に存在する上層迂回パターン160a及び下層延長パターン51aの情報を抽出する。ビアセル抽出部13fは、抽出した情報をビアセルパターン130aの形状情報として抽出し、ビアセル記憶装置23に記憶させる。

## 【0040】

(チ)ステップS117において、ビアセル配置部153は、設計データ記憶装置20に記憶された設計情報に基づいて、チップ領域上に形成され得る全ての配線構造に対し、ビアセルの形状情報のリストを抽出したか否かを判定する。ビアセルの形状情報のリストを全て抽出した場合は、ビアセルパターン130a～130dの抽出を終了する。抽出しない場合は、ステップS112に進み、未抽出の設計情報及びフロアプラン情報を読み込んで、交点Pを抽出する。

## 【0041】

実施の形態に係る設計方法によれば、ビアセル作成部13が、予めチップ領域上に複数のビアを配置するためのビアセルの形状データのリストを作成し、ビアセル記憶装置23に記憶させておく。このため、上下の配線層を複数のビアで接続する場合は、対象となる部分の周囲の図形環境に基づいてビアセルの情報を抽出し、配置するだけでよいので、設計工程の高速化が図れる。

## 【0042】

また、下層配線パターン31bと上層配線パターン41dとを接続するために、複数のビア(第1及び第2ビアパターン71a, 71b)を用いるため、半導体集積回路の製造においてビアの一方に欠損等が生じた場合においても、他方のビアにより電気的接続が維持できる。この結果、信頼度及び歩留まりを向上させた半導体集積回路の設計が行える。なお、上下の配線層を1つのビアで接続したい場合は、1つのビアを配置するための情報を予めビアセル記憶装置23に記憶させておけばよい。このため、複数のビアで接続する必要のない箇所には1つのビアを配置することも可能である。

## 【0043】

図10に示すように、ショートニングの発生を防止するための終端補正パターン64aは、優先方向と異なる向きには延伸せず、上層配線パターン41dの優先方向に平行なグリッドY<sub>3</sub>上に沿って配置される。上層配線パターン41dを配置した場合に発生する配線の敷設禁止領域R1は、グリッドY<sub>3</sub>、グリッドY<sub>6</sub>には達しないため、グリッドY<sub>3</sub>、グリッドY<sub>6</sub>上に上層配線パターン41c及び上層配線パターン41eを配置できる。このため、実施の形態に係る設計方法によれば、終端補正パターン64aの配置による敷設制約を受けることなく、上層配線パターン41c及び上層配線パターン41eを上層配線パターン41dに隣接させたレイアウトを形成できる。この結果、上層迂回パターン160aを用いないレイアウトに比べて、配線可能性を30～40%程度向上でき、より高密

10

20

30

40

50

度化させた半導体集積回路の設計が可能となる。

#### 【0044】

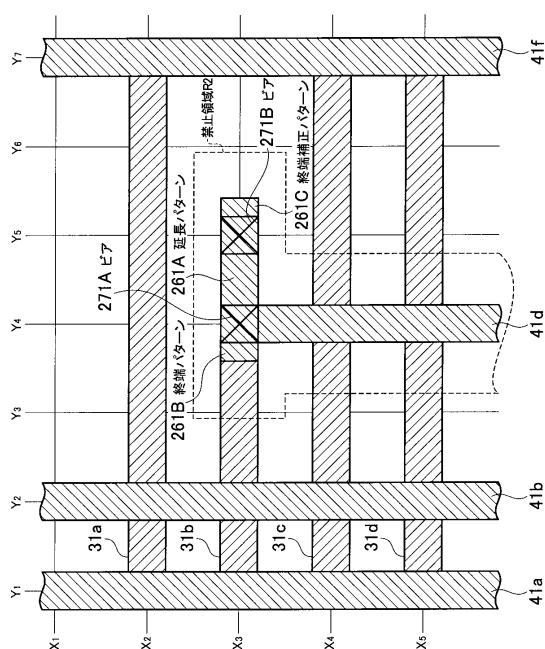

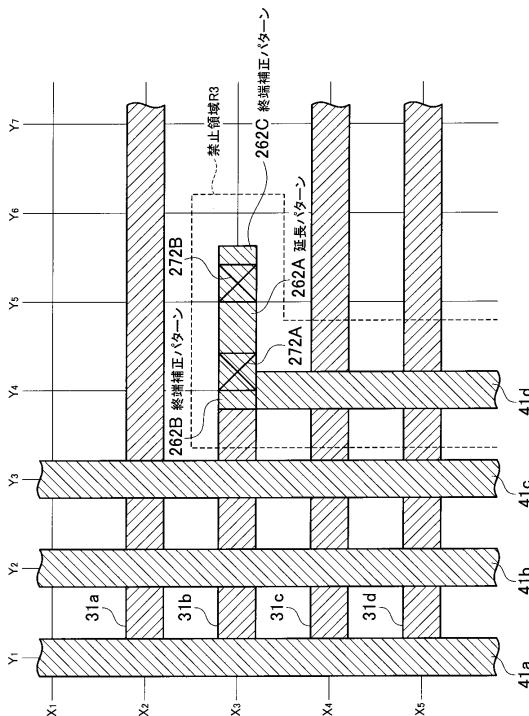

比較例として、現在一般的に設計されているレイアウトの一例を図13に示す。上層配線パターン41dの長手方向に対して直交する向きに延長パターン261Aを接続した場合は、延長パターン261Aの両端にある終端補正パターン261B, 261Cがいずれも優先方向とは異なる向きに設定される。この結果、終端補正パターン261Bの終端部がグリッドY<sub>3</sub>に近づき、終端補正パターン261Cの終端部がグリッドY<sub>6</sub>に近づくため、敷設禁止領域R2はグリッドY<sub>3</sub>, Y<sub>6</sub>にまで及ぶ。グリッドY<sub>3</sub>, Y<sub>6</sub>には新たな配線を敷設することができないため、図10に示すレイアウトに比べて配線効率が低下する。

#### 【0045】

図14に示すように、延長パターン262Aの終端部にある終端補正パターン262Bの端部を、平面パターン上、上層配線パターン41dの端部と重ね合わせるように配置すれば、敷設禁止領域R3は、グリッドY<sub>3</sub>にまでは達しない。このため、上層配線パターン41cを上層配線パターン41dに隣接させて配置することはできる。しかし、敷設禁止領域R3はグリッドY<sub>6</sub>にまで及ぶため、グリッドY<sub>6</sub>上には新たな配線を敷設できず、図10に比べれば配線効率は悪くなる。また、図14に示すレイアウトの場合は、ビアパターン272A, 272BがグリッドX<sub>1</sub>, X<sub>2</sub>, …, X<sub>5</sub>及びグリッドY<sub>1</sub>, Y<sub>2</sub>, …, Y<sub>5</sub>上には設定されないため、設計工程も複雑化する。このように、実施の形態に係る半導体集積回路の設計方法によれば、図13及び図14に示す比較例に比べてより高密度化させた半導体集積回路の設計が可能となる。

10

#### 【0046】

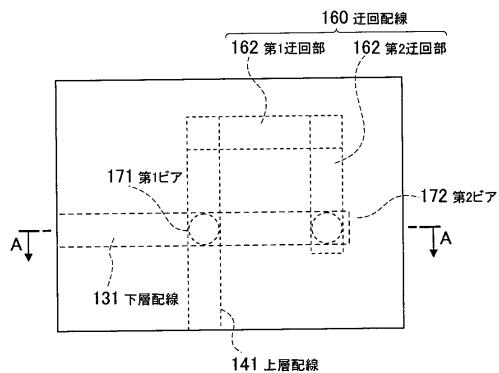

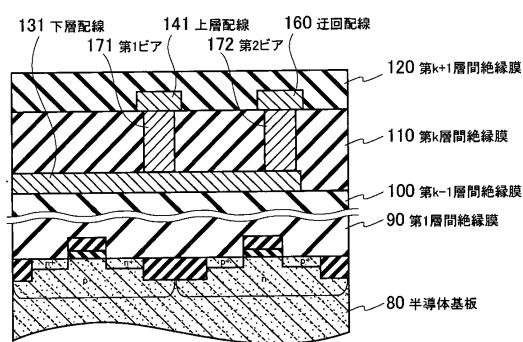

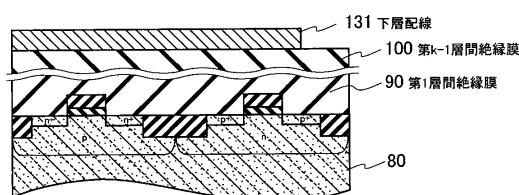

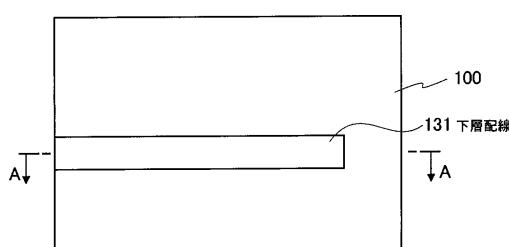

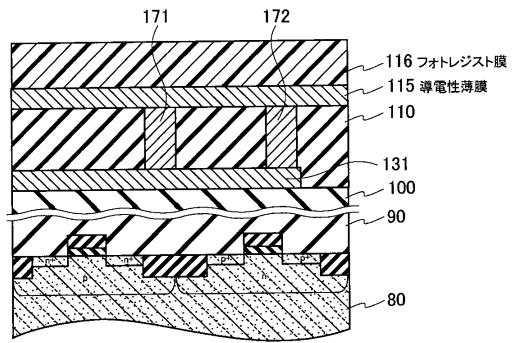

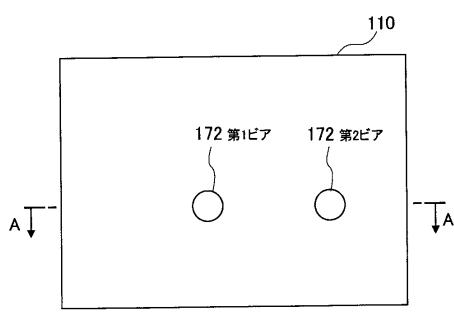

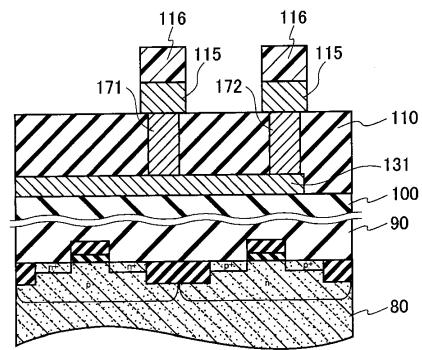

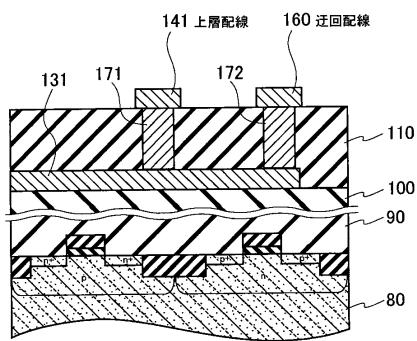

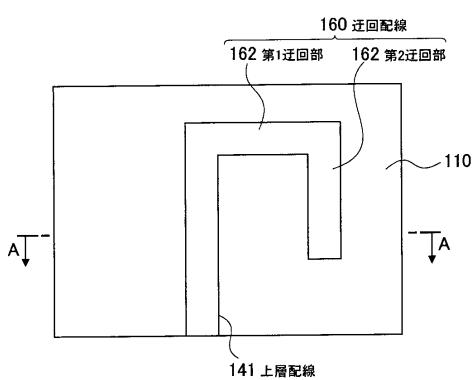

次に、実施の形態に係る半導体集積回路の多層配線構造の一例を図15及び図16に示す。図15及び図16は、図5に示すレイアウトに基づいて、パターンジェネレータ等により製造された複数枚のレチクルセットを用いて製造された半導体集積回路の一例を示している。図15のA-A方向に沿った断面からみた断面図の一例が図16である。半導体集積回路は、図16に示すように、半導体基板80と、半導体基板80の上に配置された第1層間絶縁膜90とを有する。なお、第1層間絶縁膜90は、より一般的には(k-2)層の層間絶縁膜である(k-3)。第1層間絶縁膜90の上層には、第k-1層間絶縁膜100が配置されている。

20

#### 【0047】

第k-1層間絶縁膜100の上には、下(k-1)層配線131が配置されている。第k-1層間絶縁膜100及び下層配線131の上には、第k層間絶縁膜110が配置されている。第k層間絶縁膜110の中には、下層配線131に接続された第1ビア171及び第2ビア172が埋め込まれている。第k層間絶縁膜110の上には、第1ビア171に接続された上(k)層配線141及び第2ビア172に接続された上層迂回配線160が配置されている。

30

#### 【0048】

図15に示すように、上層配線141は、下層配線131の長手方向と直交する方向に延伸し、平面パターン上、第1ビア171の位置で下層配線131と交差している。上層迂回配線160は、第1迂回部(第1迂回配線)162及び第2迂回部(第2迂回配線)163を有する。第1迂回部162は、上層配線141の端部から上層配線141の長手方向に垂直方向に配置されている。第2迂回部163は、第1迂回部162に接続され、第1迂回部162の長手方向に垂直方向に延伸し、平面パターン上、第2ビア172の位置で下層配線131と交差している。

40

#### 【0049】

実施の形態に係る半導体集積回路によれば、下層配線131と上層配線141とを接続するために、複数のビア(第1及び第2ビア171, 172)が配置されるため、半導体集積回路の製造においてビアの一方に欠損等が生じた場合においても、他方のビアにより電気的接続を維持できる。この結果、信頼度及び歩留まりを向上させた半導体集積回路が提供できる。また、迂回配線160の終端部となる第2迂回部163が、上層配線141

50

の長手方向と平行に延伸するため、上層配線 141 及び迂回配線 160 に隣接させて新たな配線を敷設することができる。この結果、半導体集積回路の高密度化・微細化が実現できる。

#### 【0050】

次に、実施の形態に係る半導体集積回路の製造方法を説明する。以下に示す半導体集積回路の製造方法は一例であり、この変形例を含めて、これ以外の種々の製造方法により実現可能であることは勿論である。

#### 【0051】

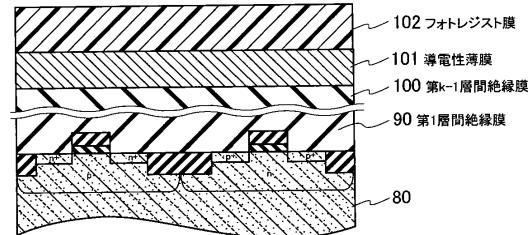

(イ) 図 17 に示すように、複数の素子が形成された半導体基板 80 の上にシリコン酸化膜 (SiO<sub>2</sub>膜) 等の第 1 層間絶縁膜 90 を、化学気相成長 (CVD) 法、物理気相成長 (PVD) 法等により堆積し、化学的機械研磨 (CMP) 法により表面を平坦化する。

10 第 1 層間絶縁膜 90 の上層に、CVD、PVD 等により第 k - 1 層間絶縁膜 100 を堆積し、表面を平坦化する。第 k - 1 層間絶縁膜 100 の上に導電性薄膜 101 を堆積し、導電性薄膜 101 を平坦化する。導電性薄膜 101 の上には、フォトレジスト膜 102 を塗布する。

#### 【0052】

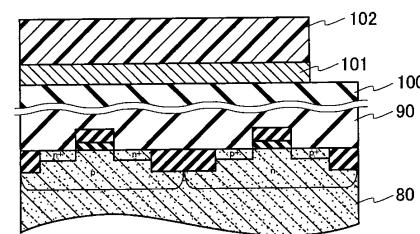

(ロ) 図 17 に示す半導体基板 80 をステッパ等の露光ステージに配置し、図 6 に示すレイアウトから製造されたレチクルを用いてフォトレジスト膜 102 を露光、現像し、導電性薄膜 101 の上にフォトレジスト膜 102 をパターニングする。パターニングされたフォトレジスト膜 102 をマスクとして、図 18 に示すように、導電性薄膜 101 の一部を RIE 等により選択的に除去する。フォトレジスト膜 102 を除去することにより、図 19 の断面図及び図 20 の平面図に示すように、第 k - 1 層間絶縁膜 100 の上に下 (k - 1) 層配線 131 が形成される。

20

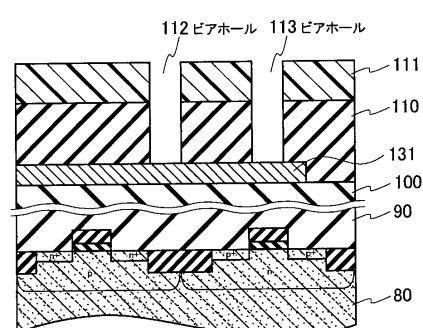

#### 【0053】

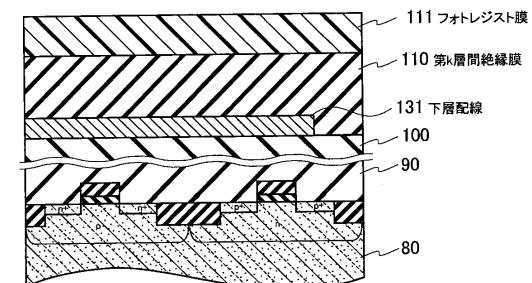

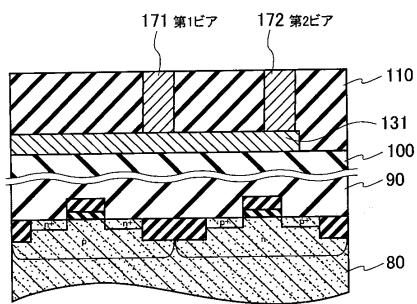

(ハ) 図 21 に示すように、CVD 法等により下層配線 131 及び第 k - 1 層間絶縁膜 100 の上に第 k 層間絶縁膜 110 を堆積し、平坦化した後、フォトレジスト膜 111 を堆積する。図 5 に示すレイアウトから製造されたレチクルを用いてフォトレジスト膜 111 をパターニングし、第 k 層間絶縁膜 110 の一部を選択的に除去し、図 22 に示すように、開口部 (ピアホール) 112、113 を形成する。フォトレジスト膜 111 を除去した後、スパッタリング法、蒸着法等によりタングステン (W)、モリブデン (Mo) 等の高融点金属をピアホール 112、113 に埋め込んだ後、表面を平坦化し、図 23 の断面図及び図 24 の平面図に示すように、第 1 ピア 171 及び第 2 ピア 172 をそれぞれ形成する。

30

#### 【0054】

(ニ) 図 25 に示すように、第 k 層間絶縁膜 110 の上に、Al, Cu 等からなる導電性薄膜 115 をスパッタリング法、蒸着法等により堆積する。導電性薄膜 115 の上には、フォトレジスト膜 116 を塗布する。続いて、図 5 に示すレイアウトから製造されたレチクルを用いてフォトレジスト膜 116 をパターニングし、図 26 に示すように、パターニングされたフォトレジスト膜 116 をマスクに導電性薄膜 115 の一部を選択的に除去する。残ったフォトレジスト膜 116 を除去することにより、図 27 及び図 28 に示すように、第 k 層間絶縁膜 110 の上に、上層配線 141 及び迂回配線 160 が形成される。

40

#### 【0055】

実施の形態に係る半導体集積回路の製造方法によれば、複数層の配線層を複数のピアで接続することにより、ピアの欠損等による高抵抗化や配線の断線を防ぐことができるので、歩留まり及び信頼性の高い半導体集積回路が提供できる。

#### 【0056】

##### (実施の形態の変形例)

図 1 に示すピアセル作成部 13 が作成可能な他のピアセルパターン 130b ~ 130g の例について、図 3 (b) ~ 図 3 (d) 及び図 29 ~ 図 33 を用いて説明する。なお、以下に示すピアセルパターン 130b ~ 130g の形状は例示であり、これ以外にも様々な

10

20

30

40

50

形状が作成可能である。

**【0057】**

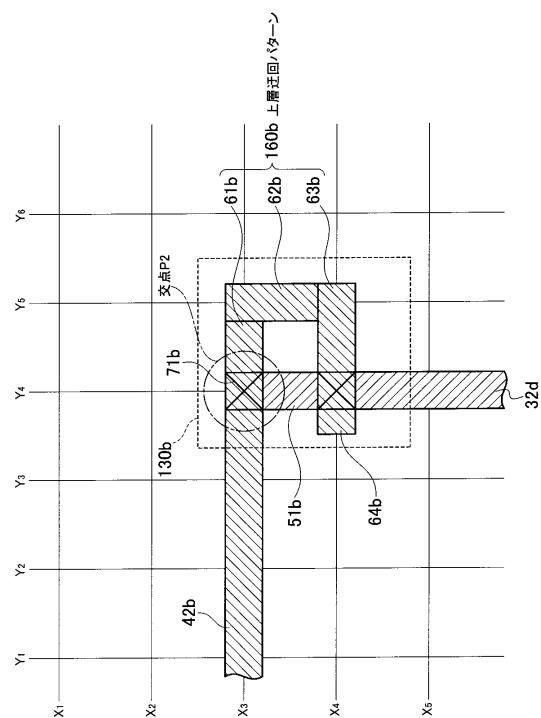

図3(b)は、図3(a)に示すビアセルパターン130aを時計回り方向に90°回転させた場合のビアセルパターン130bの一例を示している。ビアセルパターン130bは、上層延長パターン61b、上層延長パターン61bの長手方向に垂直方向に接続された第1迂回パターン62b、第1迂回パターン62cの長手方向に垂直方向に接続された第2迂回パターン63b、第2迂回パターン63bの端部に接続された終端補正パターン64b、上層延長パターン61b及び第2迂回パターン63bの端部にそれぞれ配置された第1及び第2ビアパターン71b、72b及び第1及び第2ビアパターン71b、72bを介して第1迂回パターン62b及び第2迂回パターン63bの下に配置された下層延長パターン51bを有する。

10

**【0058】**

図3(b)に示すビアセルパターン130bは、例えば図29に示すようなレイアウトパターンに好適である。チップ領域上に設定されたグリッド $X_1, X_2, \dots, X_5$ 及びグリッド $Y_1, Y_2, \dots, Y_6$ 上には、グリッド $Y_1, Y_2, \dots, Y_6$ と平行な方向を優先方向とする下層配線パターン32dが配置されている。下層配線パターン32dの上層には、グリッド $X_1, X_2, \dots, X_5$ に平行な方向を優先方向とする上層配線パターン42bが配置されている。ビアセルパターン130bの第1ビアパターン71bは、上層配線パターン42bと下層配線パターン32dとの交点P2上に配置され、上層延長パターン61bは、交点P2から上層配線パターン42bの長手方向に接続される。

20

**【0059】**

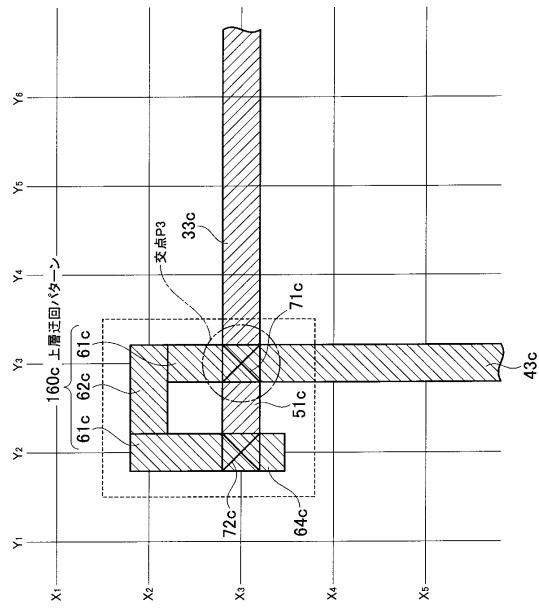

図3(c)は、図3(a)に示すビアセルパターン130aを上層延長パターン61cを軸として反転させた場合のビアセルパターン130cの一例を示している。ビアセルパターン130cは、上層延長パターン61c、上層延長パターン61cの長手方向に垂直方向に接続された第1迂回パターン62c、第1迂回パターン62cの長手方向に垂直方向に接続された第2迂回パターン63c、第2迂回パターン63cの端部に接続された終端補正パターン64c、上層延長パターン61c及び第2迂回パターン63cの端部にそれぞれ配置された第1及び第2ビアパターン71c、72c及び第1及び第2ビアパターン71c、72cを介して第1迂回パターン62c及び第2迂回パターン63cの下に配置された下層延長パターン51cを有する。

30

**【0060】**

図3(c)に示すビアセルパターン130cは、例えば図30に示すようなレイアウトパターンに好適である。チップ領域上に設定されたグリッド $X_1, X_2, \dots, X_5$ 及びグリッド $Y_1, Y_2, \dots, Y_6$ 上には、グリッド $X_1, X_2, \dots, X_5$ と平行な方向を優先方向とする下層配線パターン33cが配置されている。下層配線パターン33cの上層には、グリッド $Y_1, Y_2, \dots, Y_6$ に平行な方向を優先方向とする上層配線パターン43cが配置されている。ビアセルパターン130cの第1ビアパターン71cは、下層配線パターン33cと上層配線パターン43cとの交点P3上に配置され、上層延長パターン61cは、交点P3から上層配線パターン43cの長手方向に接続される。

40

**【0061】**

図3(d)は、図3(c)に示すビアセルパターン130cを時計回り方向に90°回転させた場合のビアセルパターン130dを示している。ビアセルパターン130dは、上層延長パターン61d、上層延長パターン61dの長手方向に垂直方向に接続された第1迂回パターン62d、第1迂回パターン62dの長手方向に垂直方向に接続された第2迂回パターン63d、第2迂回パターン63dの端部に接続された終端補正パターン64d、上層延長パターン61d及び第2迂回パターン63dの端部にそれぞれ配置された第1及び第2ビアパターン71d、72d及び第1及び第2ビアパターン71d、72dを介して第1迂回パターン62d及び第2迂回パターン63dの下に配置された下層延長パターン51dを有する。

50

**【0062】**

図3(b)～図3(d)に示すビアセルパターン130b～130dの形状情報は、図3(a)に示すビアセルパターン130aの形状に基づくライブラリ交換フォーマット(LEF)を、所望の形状・大きさとなるように変形させれば容易に作成可能である。ビアセル作成部13が、図12に示すステップS111～S117に示す方法に従って作成してもよい。

#### 【0063】

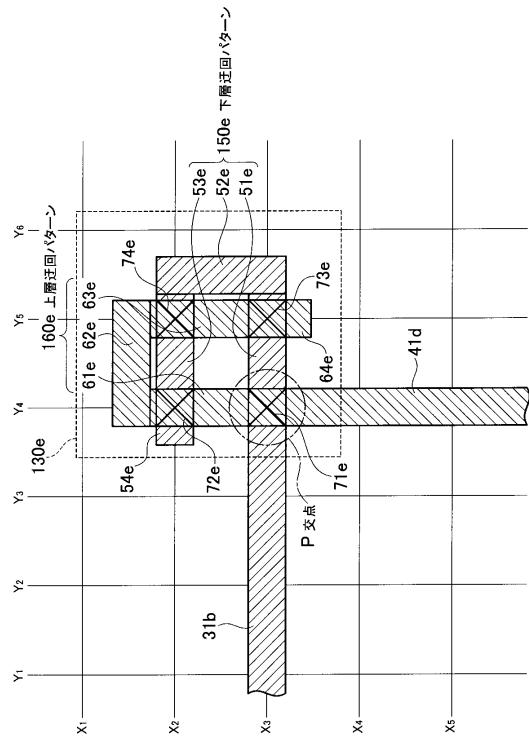

また、ビアセルパターン130a～130dの形状としては、図31に示すように、上下の配線層を接続するビアとして4つのビアを採用することで、ビアの欠損による歩留まりの低下を更に抑制できる。例えば、図31に示すレイアウト例では、グリッド $X_1, X_2, \dots, X_5$ に平行に延伸する下層配線パターン31bに下層迂回パターン150eが接続されている。下層配線パターン31bの上層に配置され、グリッド $Y_1, Y_2, \dots, Y_6$ に平行に延伸する上層配線パターン41dには、上層迂回パターン160eが接続されている。10

#### 【0064】

下層迂回パターン150eは、下層配線パターン31bに接続された下層延長パターン51e、下層延長パターン51eに接続された下層第1迂回パターン52e及び下層第1迂回パターン52eに接続された下層第2迂回パターン53eを有する。下層迂回パターン150eは、下層延長パターン51e、下層第1迂回パターン52e及び下層迂回第2パターン53eによりコの字型を形成している。上層迂回パターン160eは、上層配線パターン41dに接続された上層延長パターン61e、上層延長パターン61eに接続された上層第1迂回パターン62e及び上層第1迂回パターン62eに接続された上層第2迂回パターン63eを有する。上層迂回パターン160eは、上層延長パターン61e、上層第1迂回パターン62e及び上層第2迂回パターン64eによりコの字型を形成している。20

#### 【0065】

下層迂回パターン150e及び上層迂回パターン160eは、下層迂回パターン150e及び上層迂回パターン160eの交点にそれぞれ配置された第1ビアパターン71e、第2ビアパターン72e、第3ビアパターン73e及び第4ビアパターン74eにより電気的に接続されている。ビアセルパターン130eは、第1～第4ビアパターン71e～74e、下層迂回パターン150e及び上層迂回パターン160eからなる。30

#### 【0066】

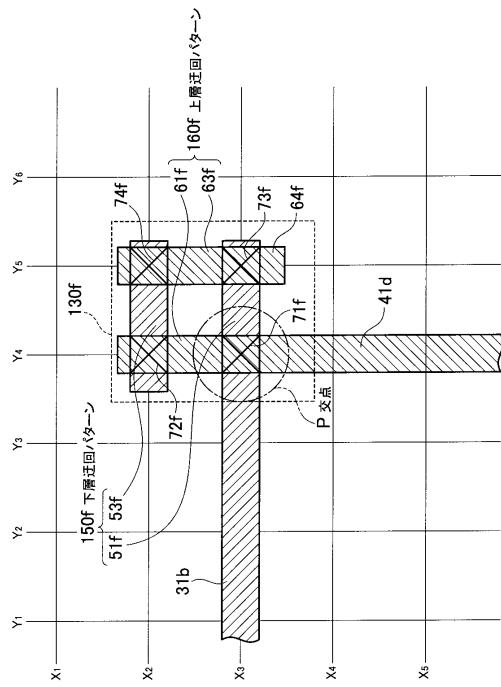

4つのビアを持つビアセルパターン130fとしては、図32に示すような「井の字型」の形状も採用可能である。図32に示すビアセルパターン130fは、下層迂回パターン150f、上層迂回パターン160f及び下層迂回パターン150fと上層迂回パターン160fとを電気的に接続する第1～第4ビアパターン71f～74fとからなる。下層迂回パターン150fは、下層配線パターン31bに接続された下層延長パターン51f及び下層延長パターン51fの長手方向に平行に配置された下層第2迂回パターン53fを有している。上層迂回パターン160fは、上層配線パターン41dに接続された上層延長パターン61f及び上層延長パターン61fの長手方向に平行に配置された上層第2迂回パターン63fを有している。なお、図32に示すビアセルパターン130fは、製造プロセス上、図31に示すような「コの字型」の形状が禁止されているような箇所への配置に好適である。40

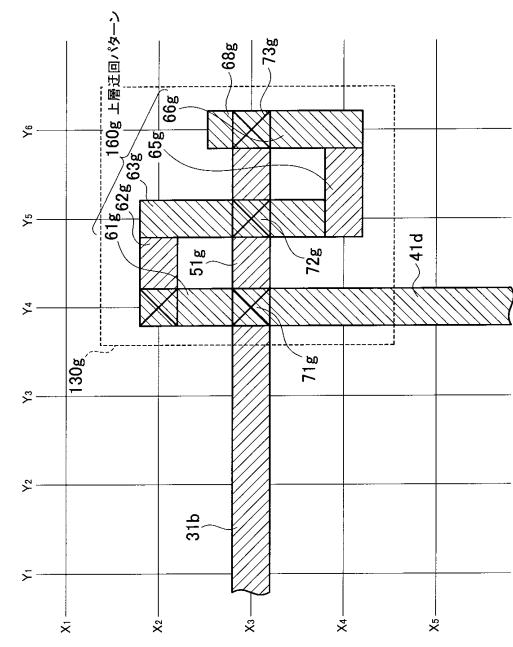

#### 【0067】

図33に示すビアセルパターン130gは、上層配線パターン41dにメアンダ(蛇行)形状の上層迂回パターン160gを配置した例を示す。上層迂回パターン160gは、上層配線パターン41dに接続された上層延長パターン61g、上層延長パターン61gに接続された第1迂回パターン62g、第1迂回パターン62gに接続された第2迂回パターン63g、第2迂回パターン63gに接続された第3迂回パターン65g、第3迂回パターン65gに接続された第4迂回パターン66gを含む。第4迂回パターン66gには、終端補正パターン67gが接続されている。下層配線パターン31bの端部には、上50

層迂回パターン 160 g と接続するための下層延長パターン 51 g が接続されている。上層迂回パターン 160 g と下層延長パターン 51 g の交点には、第 1 ビアパターン 71 g、第 2 ビアパターン 72 g 及び第 3 ビアパターン 73 g が配置されている。図 3 2 に示すビアセルパターン 130 g を用いる場合であっても上下の配線層を複数のビアで接続できるので、半導体集積回路の歩留まりの向上が図れる。

#### 【0068】

##### (その他の実施の形態)

上記のように、本発明は実施の形態によって記載したが、この開示の一部をなす論述及び図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例及び運用技術が明らかとなろう。

10

#### 【0069】

実施の形態に係る半導体集積回路としては、図 3 (a) に示すビアセルパターン 130 a のレイアウトに基づいて製造された半導体集積回路を説明した。しかし、図 3 (a) に示すレイアウトの他にも、図 3 (b) ~ 図 3 (d)、図 2 9 ~ 図 3 2 に示すレイアウトに基づいた場合も半導体集積回路を製造可能であることは勿論である。例えば、図 2 9 に示すレイアウトを用いることにより、上下の配線層にそれぞれコの字型の迂回配線を有する半導体集積回路が製造可能である。また、図 3 3 に示すレイアウトを用いることにより、平面パターン上、井の字型の迂回配線を有する半導体集積回路が製造可能である。迂回配線の配置される位置は、上下 2 層の配線層に限定されず、必要に応じて他の配線層に配置することもできる。

20

#### 【0070】

上述した実施の形態においては、上下 2 つの配線層を用いた設計方法について説明したが、2 層以上の配線層を持つ多層配線構造の半導体集積回路の設計工程においても採用可能である。この場合、上述したビアセルパターン 130 a ~ 130 g のパターン形状の他にも、現在一般的に用いられるシングルカットビアを用いたパターン形状と併用することもできる。

#### 【0071】

上述した実施の形態に係る設計方法は、配線の微細化が進んだ大規模集積回路の設計に好適である。例えば、図 8 に示すように、チップ領域上に S R A M モジュール 8 4 , R O M モジュール 8 5 , D R A M モジュール , C P U 8 7 等の複数のマクロセル、論理セル上の配線層に部分的に適用することにより、より高い歩留まりで高集積化した半導体集積回路が提供できる。また、近年の微細化要求により、配線の最小間隔が 100 nm 以下になると、ビアの欠損による歩留まりの低下が顕著になるが、実施の形態に係る設計方法を、配線間隔が 100 nm 以下の半導体集積回路に利用することにより、ビアの欠損による導通不良の問題が大幅に低減できる。このため、歩留まりの高い半導体集積回路が提供できる。

30

#### 【0072】

このように、本発明はここでは記載していない様々な実施の形態等を含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

40

#### 【図面の簡単な説明】

#### 【0073】

【図 1】本発明の実施の形態に係る設計装置を示すブロック図である。

【図 2】実施の形態に係るビアセル作成部の詳細を示すブロック図である。

【図 3】図 3 (a) ~ 図 3 (d) は、実施の形態に係るビアセルパターンの形状例を示す概念図である。

【図 4】図 3 (a) に示すビアセルパターンの作成方法を示す C A D データの一例（その 1）である。

【図 5】図 3 (a) に示すビアセルパターンの作成方法を示す C A D データの一例（その 2）である。

50

【図6】図3(a)に示すピアセルパターンの作成方法を示すCADデータの一例(その3)である。

【図7】図3(a)に示すピアセルパターンの作成方法を示すCADデータの一例(その4)である。

【図8】実施の形態に係る設計装置が設計するチップ領域の平面図の一例である。

【図9】実施の形態に係る設計方法を示すCADデータの一例(その1)である。

【図10】実施の形態に係る設計方法を示すCADデータの一例(その2)である。

【図11】実施の形態に係る設計方法の一例を示すフローチャートである。

【図12】図11のステップS15に示すレイアウト設計工程の詳細を示すフローチャートである。 10

【図13】実施の形態の比較例に係るCADデータの一例(その1)である。

【図14】実施の形態の比較例に係るCADデータの一例(その2)である。

【図15】実施の形態に係る半導体集積回路を示す平面図である。

【図16】実施の形態に係る半導体集積回路を示す断面図であり、図15のA-A断面からみた場合を示す。

【図17】実施の形態に係る半導体集積回路の製造方法を示す工程断面図である。

【図18】実施の形態に係る半導体集積回路の製造方法を示す工程断面図である。

【図19】実施の形態に係る半導体集積回路の製造方法を示す工程断面図であり、図20のA-A方向からみた場合を示す。 20

【図20】実施の形態に係る半導体集積回路の製造方法を示す平面図である。

【図21】実施の形態に係る半導体集積回路の製造方法を示す工程断面図である。

【図22】実施の形態に係る半導体集積回路の製造方法を示す工程断面図である。

【図23】実施の形態に係る半導体集積回路の製造方法を示す工程断面図であり、図24のA-A方向からみた場合を示す。

【図24】実施の形態に係る半導体集積回路の製造方法を示す平面図である。

【図25】実施の形態に係る半導体集積回路の製造方法を示す工程断面図である。

【図26】実施の形態に係る半導体集積回路の製造方法を示す工程断面図である。

【図27】実施の形態に係る半導体集積回路の製造方法を示す工程断面図であり、図28のA-A方向からみた場合を示す。 30

【図28】実施の形態に係る半導体集積回路の製造方法を示す平面図である。

【図29】実施の形態に係る設計装置により設計可能なピアセルパターンの他の一例(その1)を示す平面図である。

【図30】実施の形態に係る設計装置により設計可能なピアセルパターンの他の一例(その2)を示す平面図である。

【図31】実施の形態に係る設計装置により設計可能なピアセルパターンの他の一例(その3)を示す平面図である。

【図32】実施の形態に係る設計装置により設計可能なピアセルパターンの他の一例(その4)を示す平面図である。

【図33】実施の形態に係る設計装置により設計可能なピアセルパターンの他の一例(その5)を示す平面図である。 40

#### 【符号の説明】

【0074】

1 ... C P U

3 ... 入出力制御装置

4 ... 入力装置

5 ... 出力装置

6 ... プログラム記憶装置

11 ... フロアプラン作成部

13 ... ピアセル作成部

13 a ... 自動配線部

|                                                   |    |

|---------------------------------------------------|----|

| 1 3 b ... 交点抽出部                                   |    |

| 1 3 c ...迂回配線設定部                                  |    |

| 1 3 d ...終端補正部                                    |    |

| 1 3 e ...マルチカットビア設定部                              |    |

| 1 3 f ...ビアセル抽出部                                  |    |

| 1 5 ...レイアウト設計部                                   |    |

| 2 0 ...設計データ記憶装置                                  |    |

| 2 1 ...フロアプラン記憶装置                                 |    |

| 2 3 ...ビアセル記憶装置                                   |    |

| 2 5 ...レイアウト記憶装置                                  | 10 |

| 3 1 a ~ 3 1 d ...下層配線パターン                         |    |

| 4 1 a ~ 4 1 e ...上層配線パターン                         |    |

| 5 1 a ~ 5 1 g ...下層延長パターン                         |    |

| 5 2 e , 6 2 a ~ 6 2 g ...第1迂回パターン                 |    |

| 5 3 f , 6 3 a ~ 6 3 g ...第2迂回パターン                 |    |

| 6 1 a ~ 6 1 g , 6 7 g ...上層延長パターン                 |    |

| 6 4 a ~ 6 4 d ...終端補正パターン                         |    |

| 6 5 g ...第3迂回パターン                                 |    |

| 6 6 g ...第4迂回パターン                                 |    |

| 7 1 a ~ 7 1 g ...第1ビアパターン                         | 20 |

| 7 2 a ~ 7 2 g ...第2ビアパターン                         |    |

| 7 3 e , 7 3 g ...第3ビアパターン                         |    |

| 7 4 e ...第4ビアパターン                                 |    |

| 8 0 ...半導体基板                                      |    |

| 9 0 ...第1層間絶縁膜                                    |    |

| 1 0 0 , 1 1 0 ...層間絶縁膜                            |    |

| 1 3 0 a ~ 1 3 0 g ...ビアセルパターン                     |    |

| 1 3 1 ...下層配線                                     |    |

| 1 3 2 ...交点抽出部                                    |    |

| 1 4 1 ...上層配線                                     | 30 |

| 1 5 0 e , 1 5 0 f ...下層迂回パターン                     |    |

| 1 5 1 ...セル配置部                                    |    |

| 1 5 2 ...配線配置部                                    |    |

| 1 5 3 ...ビアセル配置部                                  |    |

| 1 6 0 ...上層迂回配線                                   |    |

| 1 6 0 a , 1 6 0 e , 1 6 0 f , 1 6 0 g ...上層迂回パターン |    |

| 1 6 2 ...第1迂回部                                    |    |

| 1 6 3 ...第2迂回部                                    |    |

| 1 7 1 ...第1ビア                                     |    |

| 1 7 2 ...第2ビア                                     | 40 |

【図1】

【図3】

【図2】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図13】

【図11】

【図12】

【図14】

【図15】

【図17】

【図16】

【図19】

【図20】

【図22】

【図23】

【図25】

【図24】

【図26】

【図27】

【図29】

【図28】

【図30】

【図31】

【図32】

【図33】

---

フロントページの続き

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 田村 尚之

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 浦川 幸広

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

審査官 池渕 立

(56)参考文献 特開昭63-029550(JP,A)

特開昭57-211249(JP,A)

特開2000-148821(JP,A)

特開2001-085614(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/82

H01L 21/3205

H01L 23/52