등록특허 10-2722138

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년10월24일

(11) 등록번호 10-2722138

(24) 등록일자 2024년10월22일

- (51) 국제특허분류(Int. Cl.)

*H01L 21/768* (2006.01) *H01L 21/02* (2006.01)

*H01L 21/027* (2006.01) *H01L 21/3065* (2006.01)

*H01L 21/324* (2017.01) *H01L 21/764* (2006.01)

- (52) CPC특허분류

*H01L 21/7682* (2013.01)

*H01L 21/02274* (2013.01)

- (21) 출원번호 10-2018-0014921

- (22) 출원일자 2018년02월07일

심사청구일자 2021년02월03일

- (65) 공개번호 10-2018-0093798

- (43) 공개일자 2018년08월22일

- (30) 우선권주장

62/458,464 2017년02월13일 미국(US)

- (56) 선행기술조사문현

JP2013179127 A\*

JP62136579 A\*

US05032221 A\*

US20070040999 A1\*

- \*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

램 리씨치 코포레이션

미국 94538 캘리포니아주 프레몬트 쿠싱 파크웨이

4650

- (72) 발명자

반 클림풋 패트릭 에이.

미국, 캘리포니아 95127, 산 호세, 스토리 코트

1387

바라다라간 세샤세이

미국, 오리건 97035, 레이크 오스위고, 헌터 코트

17372

반 슈라벤디즈크 바트 제이.

미국, 캘리포니아 94303, 팔로 알토, 코리나 웨이

3750

- (74) 대리인

특허법인인벤팅크

전체 청구항 수 : 총 17 항

심사관 : 최상원

## (54) 발명의 명칭 에어 캡들을 생성하는 방법

**(57) 요 약**

반도체 기판 프로세싱 동안 에어 캡들을 생성하도록 주석 옥사이드 막들이 사용된다.  $\text{SiO}_2$  및  $\text{SiN}$ 과 같이 다른 재료들의 노출된 층들 사이에 배치된 주석 옥사이드 막들은  $\text{H}_2$ -함유 프로세스 가스에서 형성된 플라즈마를 사용하여 선택적으로 에칭될 수 있다. 에칭은 주변 재료들 사이에 주석 옥사이드 대신 리세스된 피쳐를 생성한다. 제 3의 재료, 예컨대  $\text{SiO}_2$ 가, 발생되는 리세스된 피처를 완전히 충진하지 않고 리세스된 피처 위에 증착되어, 에어 캡을 형성한다.  $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 또는  $\text{SiCN}$ 의 존재시 주석 옥사이드를 선택적으로 에칭하는 방법은, 일부 실시예들에서, 적어도 약 50 %의  $\text{H}_2$ 를 포함하는 프로세스 가스에서 형성된 플라즈마와 기판을 콘택트하는 것을 포함한다. 주석 옥사이드의 에칭은 기판에서 외부 바이어스를 사용하지 않고 수행될 수 있고 약 100 °C 미만의 온도로 수행되는 것이 바람직하다.

**대 표 도 - 도2**

(52) CPC특허분류

*H01L 21/0274* (2013.01)

*H01L 21/3065* (2013.01)

*H01L 21/324* (2013.01)

*H01L 21/764* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

반도체 기판을 프로세싱하는 방법에 있어서,

(a) 노출된 SnO<sub>2</sub> 층을 갖는 반도체 기판을 프로세스 챔버에 제공하는 단계;

(b) 100 °C 미만의 온도에서 SnO<sub>2</sub> 층을 에칭하는 단계로서, 상기 에칭하는 단계는 상기 에칭이 휘발성 주석 수소화물의 형성을 발생시키도록 적어도 50 체적%의 H<sub>2</sub>를 포함하는 프로세스 가스로 형성된 플라즈마에 상기 반도체 기판을 노출하는 단계, 상기 형성된 휘발성 주석 수소화물이 분해되어 상기 반도체 기판 상에 입자들을 증착하지 않도록 상기 반도체 기판 상의 상기 SnO<sub>2</sub> 층의 상기 에칭 동안 에칭 프로세스 조건을 유지하는 단계, 및 상기 프로세스 챔버의 퍼지 및 배기 중 적어도 하나에 의해 상기 프로세스 챔버로부터의 상기 형성된 휘발성 주석 수소화물을 제거하는 단계를 포함하는, 상기 에칭하는 단계를 포함하는, 반도체 기판을 프로세싱하는 방법.

#### 청구항 2

제 1 항에 있어서,

상기 단계 (a)에서 제공된 상기 기판은 SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN으로 구성된 그룹으로부터 선택된 노출된 제 2 재료를 더 포함하고, 그리고 상기 단계 (b)는 상기 제 2 재료에 대해 적어도 10의 에칭 선택도로 SnO<sub>2</sub>을 에칭하는 단계를 포함하는, 반도체 기판을 프로세싱하는 방법.

#### 청구항 3

제 1 항에 있어서,

상기 단계 (a)에서 제공된 상기 기판은 SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN으로 구성된 그룹으로부터 선택된 노출된 제 2 재료를 더 포함하고, 그리고 상기 단계 (b)는 상기 제 2 재료에 대해 적어도 80의 에칭 선택도로 SnO<sub>2</sub>을 에칭하는 단계를 포함하는, 반도체 기판을 프로세싱하는 방법.

#### 청구항 4

제 1 항에 있어서,

상기 단계 (b)의 상기 SnO<sub>2</sub> 층을 에칭하는 단계는 SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN으로 구성된 그룹으로부터 선택된 제 2 재료에 노출하는 단계를 포함하고, 그리고 상기 단계 (b)는 상기 제 2 재료가 노출된 후, 상기 제 2 재료에 대해 적어도 10의 에칭 선택도로 SnO<sub>2</sub>을 계속 에칭하는 단계를 포함하는, 반도체 기판을 프로세싱하는 방법.

#### 청구항 5

제 1 항에 있어서,

상기 프로세스 가스는 적어도 80 체적%의 H<sub>2</sub>인, 반도체 기판을 프로세싱하는 방법.

#### 청구항 6

제 1 항에 있어서,

상기 프로세스 가스는 본질적으로 H<sub>2</sub>로 구성되는, 반도체 기판을 프로세싱하는 방법.

#### 청구항 7

제 1 항에 있어서,

상기 프로세스 가스는 본질적으로 H<sub>2</sub> 및 불활성 가스로 구성되는, 반도체 기판을 프로세싱하는 방법.

### 청구항 8

제 1 항에 있어서,

상기 프로세스 가스는 하이드로카본을 더 포함하는, 반도체 기판을 프로세싱하는 방법.

### 청구항 9

제 1 항에 있어서,

상기 프로세스 가스는 Cl<sub>2</sub>를 더 포함하는, 반도체 기판을 프로세싱하는 방법.

### 청구항 10

제 1 항에 있어서,

상기 단계 (b) 는 상기 기판에 대한 외부 바이어스를 사용하지 않고 플라즈마를 형성하는 것을 포함하는, 반도체 기판을 프로세싱하는 방법.

### 청구항 11

제 1 항에 있어서,

상기 단계 (b) 는 0.0018 내지 0.36 W/cm<sup>2</sup>의 전력 밀도를 사용하여 플라즈마를 생성하는 것을 포함하는, 반도체 기판을 프로세싱하는 방법.

### 청구항 12

제 1 항에 있어서,

상기 SnO<sub>2</sub>의 에칭은 1 내지 175 mTorr의 압력에서 수행되는, 반도체 기판을 프로세싱하는 방법.

### 청구항 13

제 1 항에 있어서,

상기 프로세스 가스는 H<sub>2</sub> 및 He를 포함하는, 반도체 기판을 프로세싱하는 방법.

### 청구항 14

제 1 항에 있어서,

상기 프로세스 가스는 H<sub>2</sub>, He 및 하이드로카본을 포함하는, 반도체 기판을 프로세싱하는 방법.

### 청구항 15

제 1 항에 있어서,

상기 단계 (a) 전에, ALD에 의해 상기 반도체 기판 상에 상기 SnO<sub>2</sub> 층을 증착하는 단계를 더 포함하는, 반도체 기판을 프로세싱하는 방법.

### 청구항 16

제 1 항에 있어서,

상기 단계 (b) 는 SiO<sub>2</sub>의 존재시 SnO<sub>2</sub>를 선택적으로 에칭하는 것을 포함하고, 에칭 선택도는 적어도 10인, 반도체 기판을 프로세싱하는 방법.

**청구항 17**

삭제

**청구항 18**

$\text{SnO}_2$  층을 예칭하는 장치에 있어서,

- (a) 예칭 동안 반도체 기판을 홀딩하기 위해 구성된 기판 홀더를 갖는 프로세스 챔버;

- (b) 프로세스 가스에 플라즈마를 생성하기 위해 구성된 플라즈마 생성기; 및

- (c) 제어기로서,

(i) 100 °C 미만의 온도에서 상기 반도체 기판 상의 상기  $\text{SnO}_2$  층의 예칭을 유발하기 위한 프로그램 인스트럭션으로서, 상기 예칭을 유발하는 것은 상기 예칭이 휘발성 주석 수소화물의 형성을 발생시키도록 프로세스 가스로 형성된 플라즈마에 상기 반도체 기판 상의 상기  $\text{SnO}_2$  층의 노출을 유발하는 것을 포함하고, 상기 프로세스 가스는 적어도 50 체적%의  $\text{H}_2$ 를 포함하는, 상기  $\text{SnO}_2$  층의 예칭을 유발하기 위한 프로그램 인스트럭션;

(ii) 상기 형성된 휘발성 주석 수소화물이 분해되어 상기 반도체 기판 상에 입자들을 증착하지 않도록 상기 반도체 기판 상의 상기  $\text{SnO}_2$  층의 상기 예칭 동안 예칭 프로세스 조건의 유지를 유발하기 위한 프로그램 인스트럭션; 및

(iii) 상기 프로세스 챔버의 폐지 및 배기 중 적어도 하나에 의해 상기 프로세스 챔버로부터의 상기 형성된 휘발성 주석 수소화물의 제거를 유발하기 위한 프로그램 인스트럭션을 포함하는, 상기 제어기를 포함하는, 예칭 장치.

**청구항 19**

삭제

**청구항 20**

삭제

**청구항 21**

삭제

**청구항 22**

삭제

**청구항 23**

삭제

**청구항 24**

삭제

**청구항 25**

삭제

**청구항 26**

삭제

**청구항 27**

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

청구항 33

삭제

청구항 34

삭제

## 발명의 설명

### 기술 분야

[0001] 본 발명은 반도체 디바이스 제작 방법들에 관한 것이다. 구체적으로, 본 발명의 실시예들은 반도체 기판 프로세싱 동안 에어 캡들을 생성하는 방법들에 관한 것이다.

### 배경 기술

[0002] 반도체 디바이스 제조시, 증착 및 에칭 기법들이 기판 상에 재료들의 패턴들을 형성하도록 사용된다. 패터닝은 종종 고 에칭 선택도를 갖는 또 다른 재료의 존재시 일 재료의 에칭을 필요로 한다. 에칭 선택도 요건들은 기판 상의 패터닝된 피쳐들의 사이즈들이 점점 작아짐에 따라 보다 엄격해진다. 더욱이, 습식 에칭 방법들, 예컨대 HF를 사용한 SiO<sub>2</sub>의 에칭은 리세스된 피쳐들 내로 에천트의 침투 문제들로 인해, 고 종횡비 리세스된 피쳐들을 갖는 기판들 상에서 보다 덜 바람직해진다.

[0003] 매우 선택적인 에칭 방법들이 DRAM (dynamic random-access memory) 의 형성, FinFET들 (fin field effect transistors) 의 제조, 및 BEOL (back end of line) 프로세싱시 패터닝을 포함하는 다양한 애플리케이션들에서의 패터닝에 필요하다.

### 발명의 내용

[0004] SiO<sub>2</sub> 및 SiN과 같은 일반적으로 사용된 유전체들의 존재시 고 에칭 선택도로 에칭될수 있는 재료들 및 연관된 에칭 방법들이 특히 목표된다. SnO<sub>2</sub>는 매우 선택적인 건식 에칭 화학물질을 사용하여 SiO<sub>2</sub>, SiN, 및 다양한 다른 재료들에 대해 선택적으로 에칭될 수 있는 재료로서 제공된다. 회생적 스페이서 재료로서 SnO<sub>2</sub>를 채용하는 반도체 디바이스 제조 (예를 들어, FinFET 제조 동안) 시 에어 캡들을 형성하는 방법들이 또한 제공된다.

[0005] 일 양태에 따라, 반도체 기판을 프로세싱하는 방법이 제공된다. 방법은 노출된 SnO<sub>2</sub> 층 (예를 들어, ALD에 의해 증착된 SnO<sub>2</sub> 층) 을 갖는 반도체 기판을 제공하는 단계; 약 100 °C 미만의 온도로 SnO<sub>2</sub> 층을 에칭하는 단계로서, 에칭은 적어도 약 50 %의 H<sub>2</sub>를 포함하는 프로세스 가스로 형성된 플라즈마에 반도체 기판을 노출하는 것을 포함하는, 에칭하는 단계를 포함한다. 일부 실시예들에서, 제공된 반도체 기판은 SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO,

SiCNO, 및 SiCN으로 구성된 그룹으로부터 선택된 제 2 재료를 더 포함하고, SnO2의 수소 플라즈마 에칭은 제 2 재료에 대해 적어도 약 10, 예컨대 적어도 약 80의 에칭 선택도로 수행된다. 제 2 재료는 SnO2 에칭의 시작 전에 기판 상에서 노출될 수도 있고, 또는, 일부 실시예들에서, 제 2 재료는 SnO2 에칭 동안 노출될 수도 있다. 일부 실시예들에서, 제 2 재료는 SiO2이고, 에칭은 SiO2에 대해 적어도 약 10의 에칭 선택도로 SnO2를 제거한다.

[0006] SnO2 에칭시 프로세스 가스의 조성은 가변할 수 있고, H2에 더하여 다른 가스들을 포함할 수도 있다. 그러나, 일부 실시예들에서, 프로세스 가스는 본질적으로 H2 (예를 들어, 100 %의 H2)로 구성된다. 일부 실시예들에서, 프로세스 가스는 적어도 약 50 %의 H2를 포함하고, 불활성 가스, 예컨대 헬륨을 더 포함한다. 일부 실시예들에서 프로세스 가스는 본질적으로 H2 및 불활성 가스로 구성될 수도 있다. 일부 구현예들에서, 프로세스 가스 내 H2의 농도는 적어도 약 80 %이다. 선택가능하게, 프로세스 가스는 하이드로카본 및/또는 Cl2를 더 포함할 수도 있다. 일 예에서, 프로세스 가스는 H2 (50 % 이상), 헬륨, 및 하이드로카본을 포함한다. 프로세스 가스의 플라즈마는 고 주파수 및/또는 저 주파수 플라즈마 생성을 사용하여 형성될 수 있다. 특히, 기판에서 외부 바이어스의 사용이 선택가능하다. 일부 실시예들에서, 에칭은 기판에 대한 외부 바이어스를 제공하지 않고 수행된다. 일부 실시예들에서 플라즈마는 약 0.0018 내지 0.36 W/cm<sup>2</sup>의 전력 밀도를 사용하여 생성된다. 에칭 동안 프로세스 챔버의 압력은, 일부 실시예들에서, 약 1 내지 175 mTorr이다.

[0007] 또 다른 양태에서, SnO2 층을 에칭하기 위한 장치가 제공된다. 장치는 에칭 동안 반도체 기판을 홀딩하기 위해 구성된 기판 홀더를 갖는 프로세스 챔버; 프로세스 가스에 플라즈마를 생성하기 위해 구성된 플라즈마 생성기; 및 제어기를 포함한다. 제어기는 본 명세서에 기술하는 임의의 방법들을 구현하기 위한 프로그램 인스트럭션들을 포함한다. 일 실시예에서, 제어기는 약 100 °C 미만의 온도에서 반도체 기판 상의 SnO2 층의 에칭을 유발하기 위한 프로그램 인스트럭션들을 포함하고, 에칭을 유발하는 것은 적어도 약 50 %의 H2를 포함하는 프로세스 가스로 형성된 플라즈마에 반도체 기판의 노출을 유발하는 것을 포함한다.

[0008] 또 다른 양태에서, 에칭 장치를 제어하기 위한 프로그램 인스트럭션들을 포함하는, 비일시적인 컴퓨터 머신 판독가능 매체가 제공된다. 프로그램 인스트럭션들은 약 100 °C 미만의 온도에서 반도체 기판 상에 SnO2 층의 에칭을 유발하기 위한 코드를 포함하고, 에칭은 적어도 약 50 % H2를 포함하는 프로세스 가스로 형성된 플라즈마에 반도체 기판의 노출을 유발하는 것을 포함한다.

[0009] 또 다른 양태에서, 반도체 기판 상에 에어 캡을 생성하는 방법이 제공된다. 방법은: (a) 제 1 재료의 노출된 층, 제 2 재료의 노출된 층, 및 제 1 재료의 층과 제 2 재료의 층 사이에 위치된 SnO2의 노출된 층을 갖는 반도체 기판을 제공하는 단계; (b) 수소 플라즈마 에칭 화학물질을 사용하여 제 1 재료 및 제 2 재료 모두에 대하여 노출된 SnO2를 선택적으로 에칭하여, 제 1 재료와 제 2 재료 사이에 리세스된 피처를 형성하는 단계; 및 (c) 리세스된 피처를 완전히 충진하지 않고 리세스된 피처 위에 제 3 재료를 증착하여, 제 1 재료의 층과 제 2 재료의 층 사이에 에어 캡을 형성하는 단계를 포함한다. 일부 구현예들에서, 제 1 재료는 SiO2, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN으로 구성된 그룹으로부터 선택되고, 그리고 제 2 재료는 SiO2, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN으로 구성된 그룹으로부터 선택된다. 일부 실시예들에서, 제 1 재료와 제 2 재료는 동일한 재료이다. 다른 실시예들에서, 제 1 재료 및 제 2 재료는 상이한 재료들이다. 일부 실시예들에서, 제 3 재료는 SiO2이다.

[0010] 일부 구현예들에서, SnO2 층의 수소 플라즈마 에칭은 적어도 약 50 %의 H2를 포함하는 프로세스 가스로 형성된 플라즈마에 반도체 기판을 노출하는 것을 포함한다. 일부 실시예들에서, 에칭은 약 100 °C 미만의 온도에서 수행된다. 기술된 방법들은 좁은 리세스된 피처들에 에어 캡들을 형성하는데 특히 유용하다. 일 구현예에서, SnO2 층의 폭은 약 20 내지 100 Å이다.

[0011] 일 실시예에서, 제 1 재료 층과 제 2 재료 층 사이에 놓이는 SnO2 층을 갖는 기판이 다음의 단계들의 시퀀스를 사용하여 형성된다. 프로세스는 반도체 기판 상에 게이트 (예를 들어, 하이-k 옥사이드, 예컨대 하프늄 옥사이드로부터 이루어진 돌출하는 피처)를 형성하는 단계; 제 1 재료가 게이트의 측벽들 및 상단 표면 모두를 커버하도록 반도체 기판 위에 제 1 재료 (예를 들어, SiN)의 층을 컨포멀하게 형성하는 단계; SnO2가 게이트의 측

벽들 상 및 상단 표면 상 모두의 제 1 재료를 커버하도록 제 1 재료의 층 위에  $\text{SnO}_2$  층을 (예를 들어, 약 20 내지 100 Å의 두께로) 컨포멀하게 형성하는 단계; 및 제 2 재료가 게이트의 측벽들 상 및 상단 표면 상 모두의  $\text{SnO}_2$ 를 커버하도록  $\text{SnO}_2$  층 위에 제 2 재료 (예를 들어,  $\text{SiO}_2$ ) 의 층을 컨포멀하게 형성하는 단계에 의해 시작된다. 이어서 프로세스는 기판의 수평 표면들로부터 제 2 재료를 제거하여 노출된 제 1 재료의 층과 노출된 제 2 재료의 층 사이에 노출된  $\text{SnO}_2$  층을 갖는 구조체를 형성하는 단계가 이어진다.

[0012] 또 다른 양태에서, 반도체 기판 상에 에어 캡을 형성하기 위한 시스템이 제공된다. 시스템은 하나 이상의 증착 프로세스 챔버들; 하나 이상의 애칭 프로세스 챔버들; 및 제어기를 포함한다. 제어기는 본 명세서에 기술된 임의의 에어 캡 형성 방법들을 구현하기 위한 프로그램 인스트럭션들을 포함한다. 예를 들어, 제어기는 (i) 제 1 재료의 노출된 층, 제 2 재료의 노출된 층, 및 제 1 재료의 층과 제 2 재료의 층 사이에 위치된  $\text{SnO}_2$ 의 노출된 층을 갖는 반도체 기판 상에서, 수소 플라즈마 애칭 화학물질을 사용하여 제 1 재료 및 제 2 재료 모두에 대하여 노출된  $\text{SnO}_2$ 를 선택적으로 애칭하여, 제 1 재료와 제 2 재료 사이에 리세스된 피처를 형성하는 단계; 및 (ii) 리세스된 피처를 완전히 충진하지 않고 리세스된 피처 위에 제 3 재료를 증착하여, 제 1 재료의 층과 제 2 재료의 층 사이에 에어 캡을 형성하는 단계를 유발하는 프로그램 인스트럭션들을 포함할 수도 있다.

[0013] 또 다른 양태에서, 시스템은 본 명세서에 기술된 임의의 장치들 및 시스템들 및 스텝퍼를 포함한다.

[0014] 또 다른 양태에서, 시스템을 제어하기 위한 프로그램 인스트럭션들을 포함하는 비일시적인 컴퓨터 머신 판독 가능 매체가 제공되고, 프로그램 인스트럭션들은 (i) 제 1 재료의 노출된 층, 제 2 재료의 노출된 층, 및 제 1 재료의 층과 제 2 재료의 층 사이에 위치된  $\text{SnO}_2$ 의 노출된 층을 갖는 반도체 기판 상에서, 수소 플라즈마 애칭 화학물질을 사용하여 제 1 재료 및 제 2 재료 모두에 대하여 노출된  $\text{SnO}_2$ 를 선택적으로 애칭하여, 제 1 재료와 제 2 재료 사이에 리세스된 피처를 형성하기 위한 코드; 및 (ii) 리세스된 피처를 완전히 충진하지 않고 리세스된 피처 위에 제 3 재료를 증착하여, 제 1 재료의 층과 제 2 재료의 층 사이에 에어 캡을 형성하기 위한 코드를 포함한다.

[0015] 또 다른 양태에서, 반도체 기판을 프로세싱하는 방법에 있어서,  $\text{SnO}_2$  더미 게이트의 증착을 수반하는 방법이 제공된다. 방법은: (a) 반도체 기판 상에  $\text{SnO}_2$  더미 게이트를 형성하는 단계; (b)  $\text{SnO}_2$  더미 게이트의 존재시 반도체 기판을 프로세싱하는 단계; (c) 더미 게이트 대신 리세스된 피처를 형성하도록  $\text{H}_2$ 를 포함하는 프로세스 가스로 형성된 플라즈마로  $\text{SnO}_2$  더미 게이트를 애칭하는 단계; 및 (d) 더미 게이트 대신 게이트를 형성하도록 형성된 리세스된 피처 내로 하이-k 유전체 재료를 증착하는 단계를 포함한다. 또 다른 양태에서, 반도체 기판을 프로세싱하는 시스템에 있어서, 시스템은, 하나 이상의 증착 프로세스 챔버들; 하나 이상의 애칭 프로세스 챔버들; 및 제어기로서: (i) 반도체 기판 상에  $\text{SnO}_2$  더미 게이트를 형성하는 단계; (ii)  $\text{SnO}_2$  더미 게이트의 존재시 반도체 기판을 프로세싱하는 단계; (iii) 더미 게이트 대신 리세스된 피처를 형성하도록  $\text{H}_2$ 를 포함하는 프로세스 가스로 형성된 플라즈마로  $\text{SnO}_2$  더미 게이트를 애칭하는 단계; 및 (iv) 더미 게이트 대신 게이트를 형성하도록 형성된 리세스된 피처 내로 하이-k 유전체 재료를 증착하는 단계를 유발하는 코드를 포함한다.

[0016] 일부 실시예들에서, 제공된 방법들은 포토리소그래피 패터닝 시퀀스들과 통합되고, 포토레지스트를 반도체 기판에 도포하는 단계; 포토레지스트를 광에 노출하는 단계; 포토레지스트를 패터닝하고 패턴을 기판에 전사하는 단계; 및 기판으로부터 포토레지스트를 선택적으로 제거하는 단계를 더 포함한다.

[0017] 본 명세서에 기술된 주제의 구현예들의 이들 및 다른 양태들은 첨부된 도면들 및 이하의 기술에 언급된다.

## 도면의 간단한 설명

[0018]

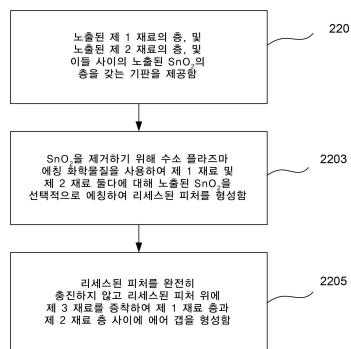

도 1은 본 명세서에 제공된 실시예에 따른 프로세싱 방법의 프로세스 흐름도이다.

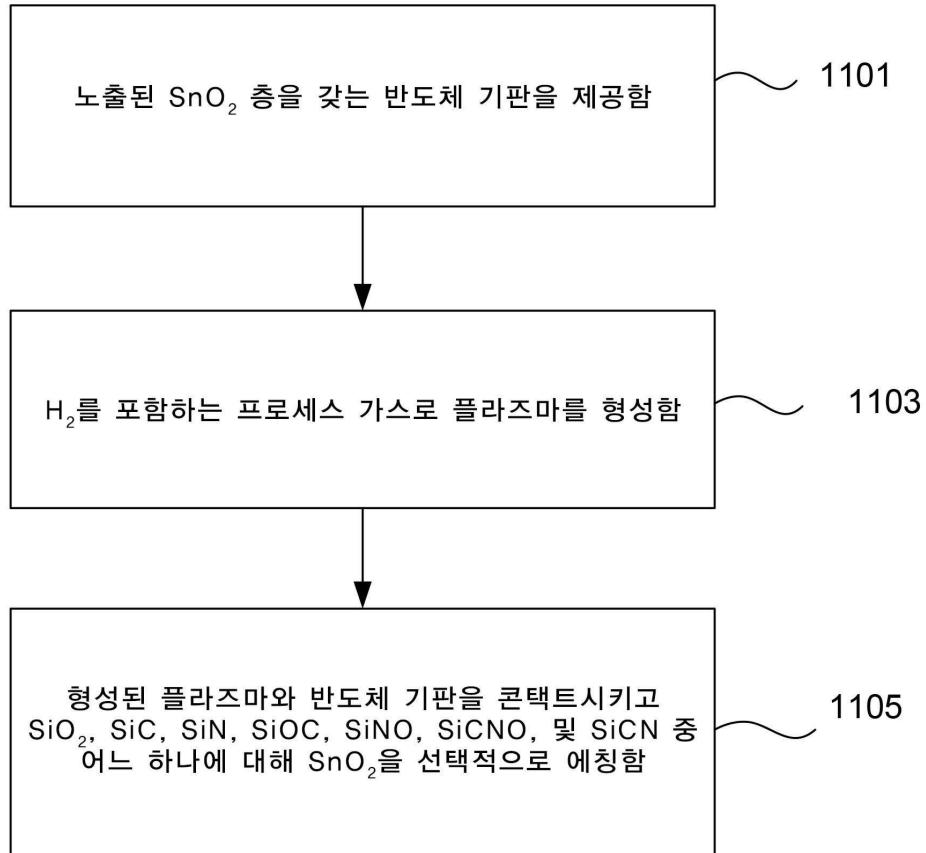

도 2는 본 명세서에 제공된 실시예에 따른 프로세싱 방법의 프로세스 흐름도이다.

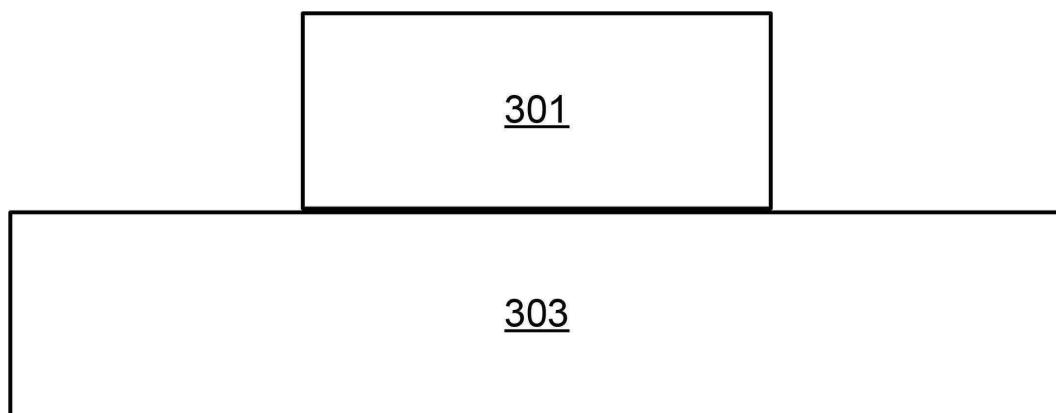

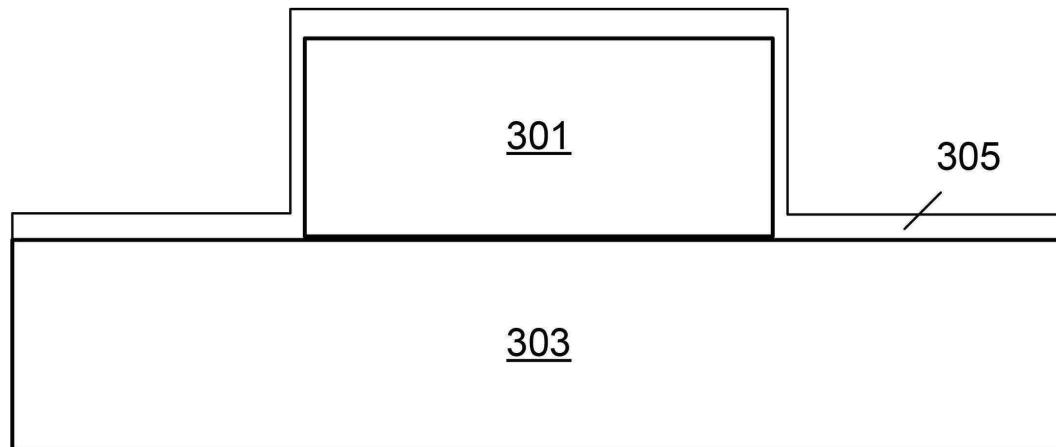

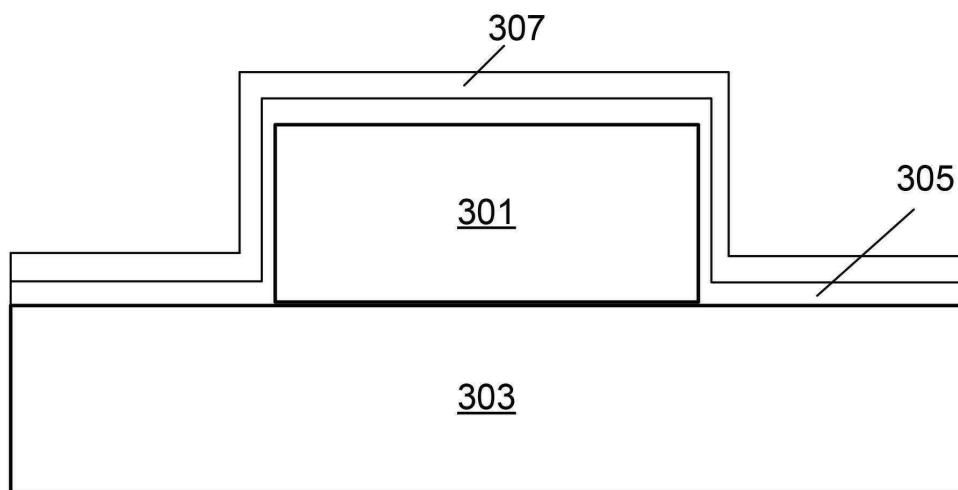

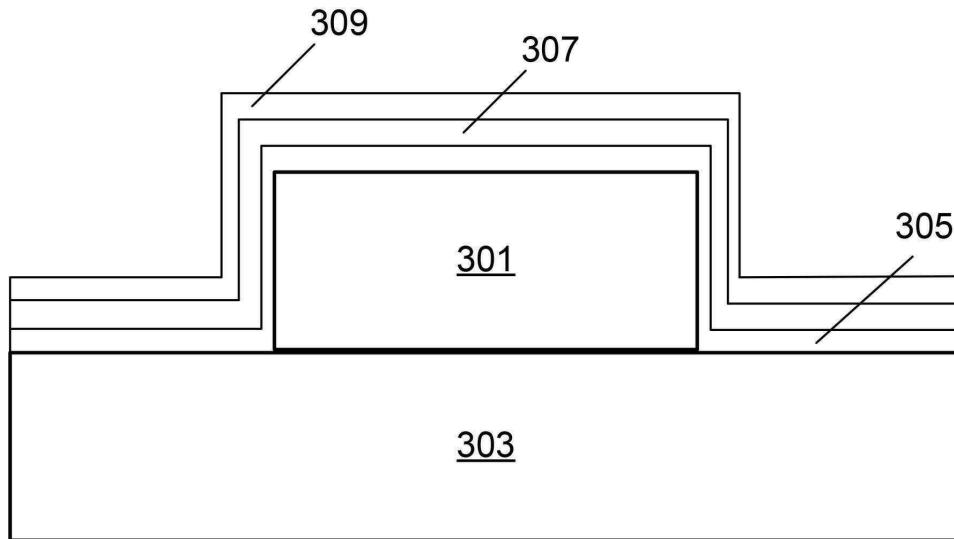

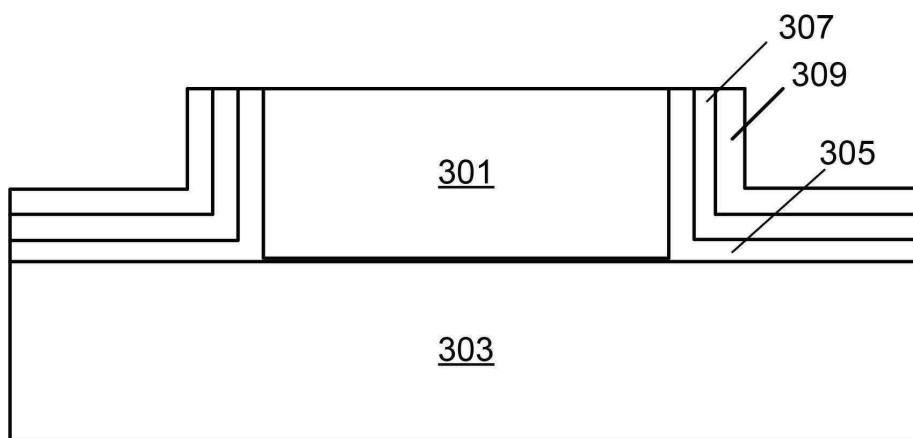

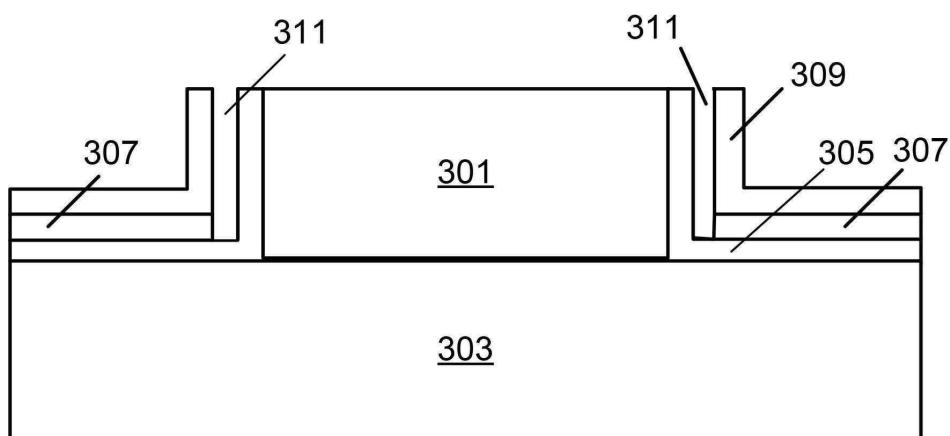

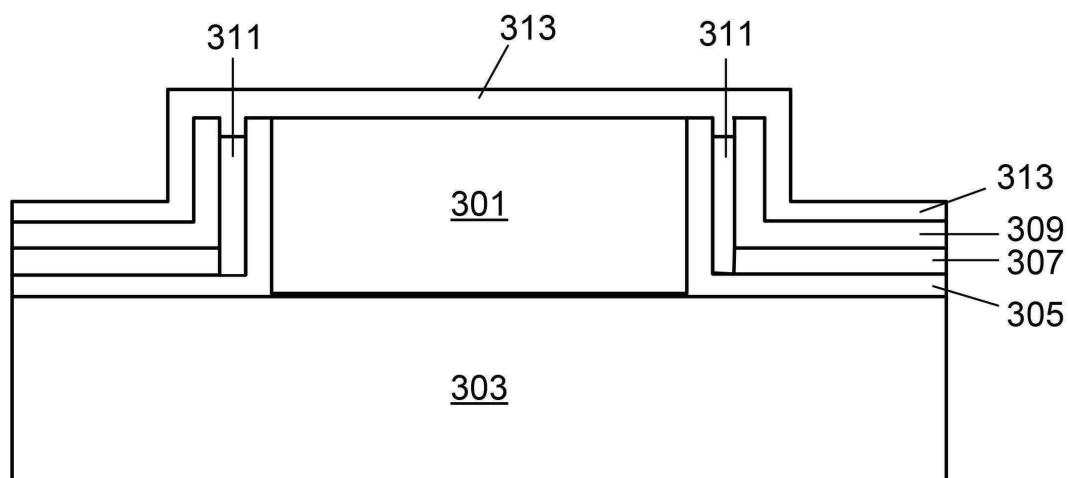

도 3a 내지 도 3g는 본 명세서에 기술된 실시예에 따른 에어 캡 형성과 함께 프로세싱을 겪는 반도체 기판의 개략적인 단면도들이다.

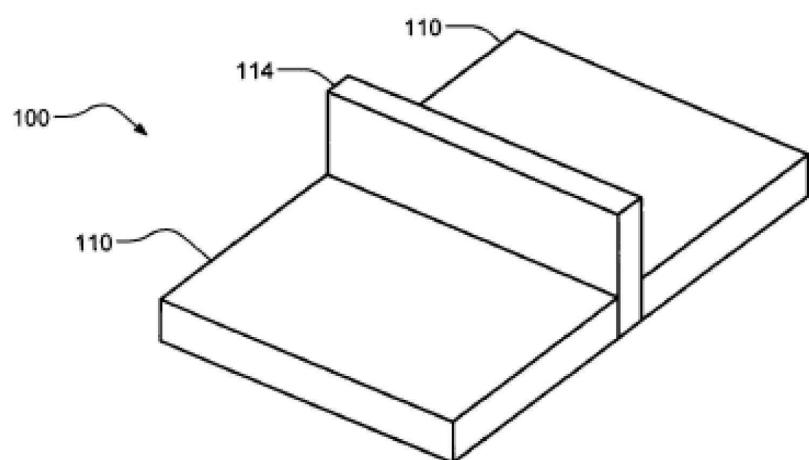

도 4a 내지 도 4t는 본 명세서에 기술된 실시예들에 따른 FinFET 디바이스 제조 동안 프로세싱을 겪는 반도체 기판의 개략적인 단면도들이다.

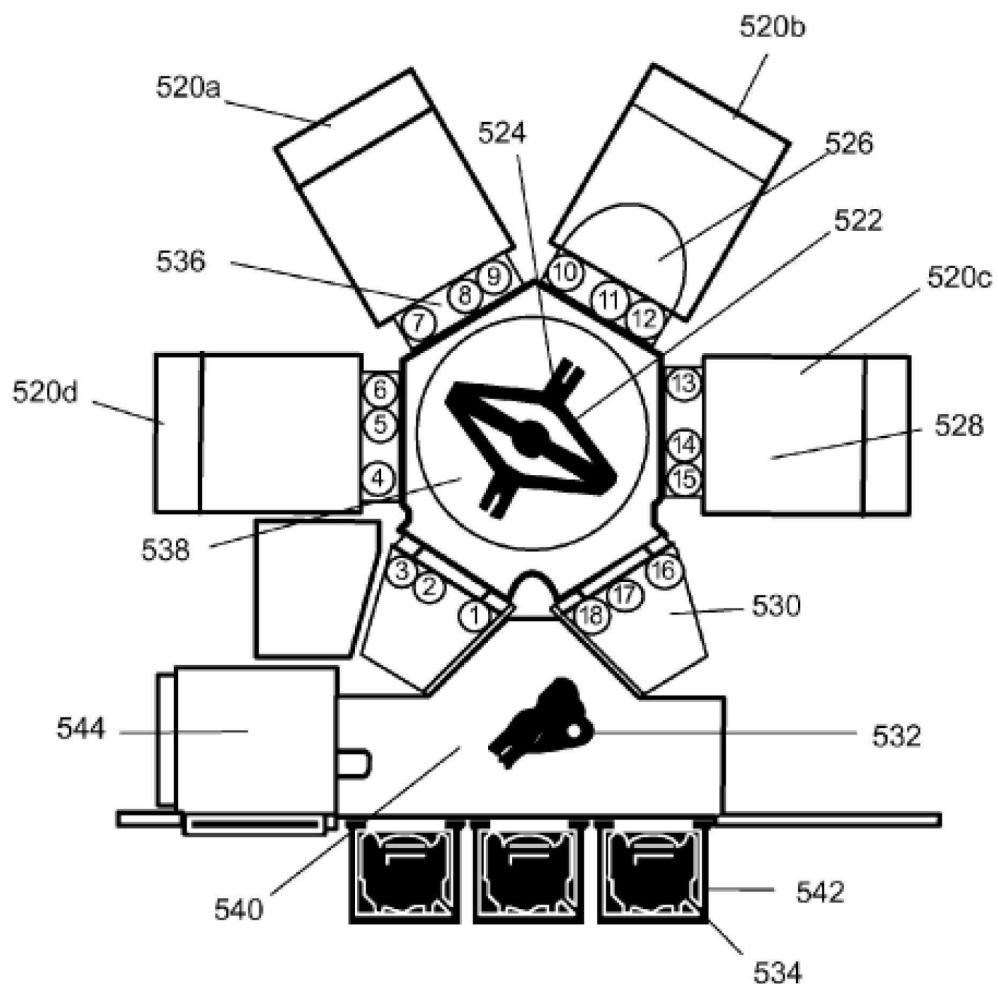

도 5는 본 명세서에 제공된 실시예에 따른 수소 플라즈마 에칭 화학물질을 사용하여 SnO<sub>2</sub>를 에칭하기 적합한 장치의 개략도이다.

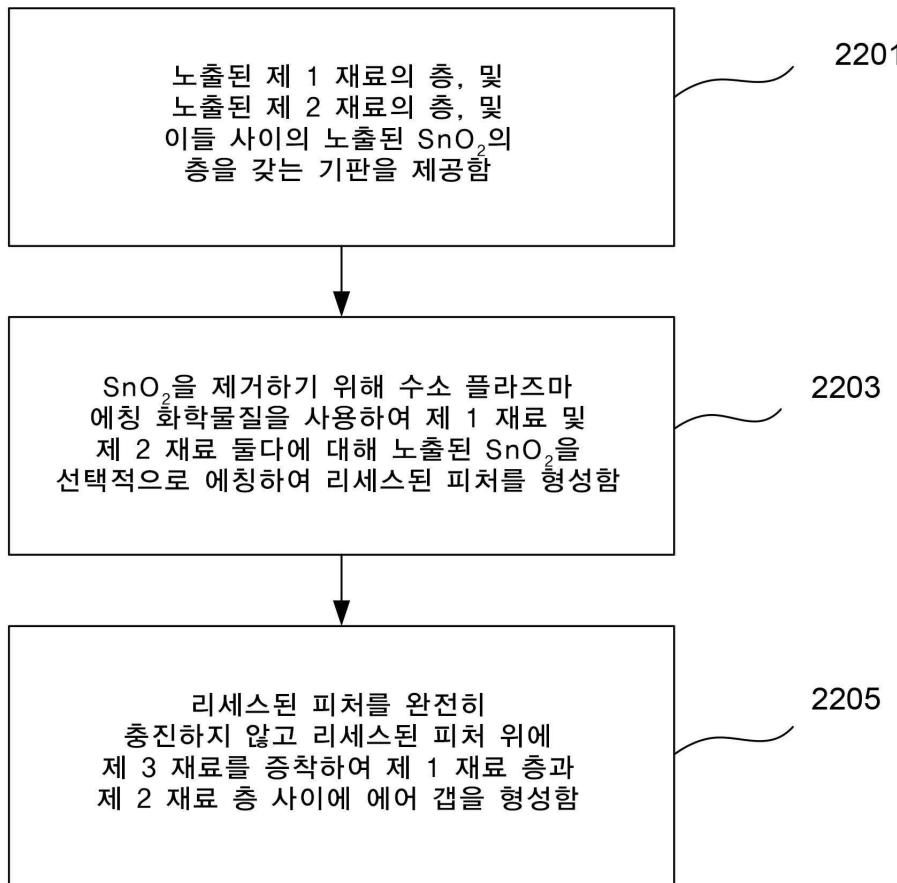

도 6은 본 명세서에 제공된 실시예에 따른 멀티-스테이션 프로세싱 시스템의 개략도를 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0019]

반도체 디바이스의 주석 (IV) 옥사이드 (SnO<sub>2</sub>) 를 에칭하기 위한 방법들이 제공된다. 일부 실시예들에서, 제공된 방법들은 SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN 중 하나 이상에 대해 고 선택도를 갖는 주석 옥사이드를 에칭하도록 사용된다. 일부 실시예들에서 에칭 선택도는 10 초파, 예컨대 30 초파, 예를 들어, 50 초파, 또는 80 초파이다. 에칭 선택도는 선택된 프로세스 조건들에 대한 SnO<sub>2</sub>의 에칭 레이트 대 다른 재료들의 에칭 레이트의 비를 지칭한다. 일부 예들에서, 100의 에칭 선택도는 SiO<sub>2</sub>에 대한 SnO<sub>2</sub>의 에칭에 대해 달성된다. 이들 에칭 선택도들은 H<sub>2</sub>를 포함하는 프로세스 가스로 형성된 플라즈마와 반도체 기판을 콘택트하는 것을 수반하는 에칭 방법에 대해 달성된다. 제공된 방법들은 SnO<sub>2</sub>의 수소 플라즈마에 대한 노출을 통해 가스성 SnH<sub>4</sub>로 고체 SnO<sub>2</sub>를 변환하는 것을 수반한다. 이어서 가스성 SnH<sub>4</sub> 생산물은 퍼지 및/또는 배기기에 의해 프로세스 챔버로부터 용이하게 제거될 수 있다. 일부 실시예들에서 다른 재료 (예를 들어, SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO, SiCNO, 또는 SiCN) 가 SnO<sub>2</sub> 에칭의 시작시 반도체 기판 상에서 노출된다. 다른 실시예들에서 다른 재료는 SnO<sub>2</sub> 에칭의 시작시 노출되지 않고 에칭 고스 동안 노출되게 된다.

[0020]

예를 들어, ALD 또는 PECVD에 의해 SnO<sub>2</sub>가 증착될 수 있고 소량의 다른 재료들, 예컨대 탄소 및 수소 (통상적으로 10 원자% 미만) 를 포함할 수도 있다. 주석 옥사이드에서 1:2의 주석:산소 화학량론으로부터 작은 편차가 가능하고 SnO<sub>2</sub> 구조의 범위 내라는 것이 또한 이해된다. 예를 들어, SnO<sub>2</sub>의 일부 예들에서 O:Sn 원자비는 약 2.0 내지 2.3이다. 약 1.5 내지 2.5의 O:Sn 비를 갖는 주석 옥사이드들은 본 명세서에 사용된 바와 같이 SnO<sub>2</sub> 재료의 범위 내이다.

[0021]

SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN 재료들은 도핑되거나 도핑되지 않을 수도 있고, 선택가능하게 수소를 포함할 수도 있다. 도편트는, 존재한다면, 통상적으로 10 원자% (수소를 제외하고) 의 농도를 초과하지 않는다. 이들 재료들은 다양한 방법들, 예컨대 CVD, PECVD 및 ALD를 사용하여 증착될 수 있다. 다양한 실리콘 함유 전구체들이 실란, 테트라알킬실란들, 트리알킬실란들, TEOS, 등을 포함하는 이들 재료들의 증착에 사용될 수 있다. 예를 들어, SiO<sub>2</sub>는 실리콘 함유 전구체로서 TEOS 또는 실란을 사용하여 증착될 수도 있다.

[0022]

본 명세서에 사용된 바와 같은 용어 "반도체 기판"은 구조 내 어딘가에 반도체 재료를 함유하는 반도체 디바이스의 임의의 제조 단계에서 기판을 지칭한다. 반도체 기판 내 반도체 재료가 노출될 필요가 없다는 것이 이해된다. 반도체 재료를 커버하는 다른 재료들 (예를 들어, 유전체들) 을 갖는 복수의 반도체 웨이퍼들이 반도체 기판들의 예이다.

[0023]

제공된 방법들은 다양한 폭들 및 종횡비들의 SnO<sub>2</sub> 층들을 에칭하기 위해 사용될 수 있다. 이들 방법들은 좁은 층들 (예를 들어, 20 내지 100 Å, 예를 들어, 25 내지 75 Å의 폭들을 갖는 SnO<sub>2</sub> 층들) 을 에칭하기 위해, 그리고 상대적으로 높은 종횡비의 리세스된 피처들을 생성하기 위해, 예컨대 적어도 약 5:1의 종횡비들을 갖는 (예를 들어 약 10:1 내지 100:1의 종횡비들을 갖는) 리세스된 피처들을 생성하기 위해 SnO<sub>2</sub>를 에칭하기 위해 특히 유리하다. 제공된 방법들은 이들 애플리케이션들로 제한되지 않고, 종래의 방법들 및 재료들 (예를 들어, SiN 스페이서들의 습식 HF 에칭) 이 이들 애플리케이션들을 위해 잘 응용되지 않기 때문에, 본 명세서에 제공된

수소 플라즈마 에칭 방법들을 사용한 좁은 층들의 에칭 및/또는 고 종횡비 리세스된 피쳐들의 형성에 특히 유용하다.

[0024] 본 명세서에 제공된 실시예에 따른 에칭 방법은 도 1에 도시된 프로세스 흐름도에 예시된다. 동작 1101에서, 노출된  $\text{SnO}_2$  층을 갖는 반도체 기판이 제공된다. 기판은 에칭 장치의 프로세스 챔버 내로 배치되고, 에칭 장치는 프로세스 가스로 플라즈마를 생성하도록 구성된다. 다음에, 동작 1103에서, 플라즈마는  $\text{H}_2$ 를 포함하는 프로세스 가스로 생성된다. 동작 1105에서, 기판은 형성된 수소 플라즈마와 콘택트하고  $\text{SnO}_2$  층은 기판 상의 임의의  $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 및  $\text{SiCN}$  재료들에 대해 선택적으로 에칭된다. 선택적인 에칭은 에칭 임의의 열거된 재료들에 상대적으로, 1 초과, 보다 바람직하게 10 초과, 예컨대 50 초과의 에칭 선택도로  $\text{SnO}_2$ 를 에칭하는 것을 수반한다.

[0025] 일부 실시예들에서, 노출된  $\text{SnO}_2$  층에 더하여, 동작 1101에서 제공된 반도체 기판, 노출된 제 2 재료의 층을 더 포함하고, 제 2 재료는  $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 및  $\text{SiCN}$  중 하나 이상을 포함한다. 다른 실시예들에서 제 2 재료는  $\text{SnO}_2$  에칭의 시작시 노출되는 것이 아니라,  $\text{SnO}_2$ 가 일정 시간 에칭된 후 노출되게 된다.

[0026] 1101에 제공된 기판은  $\text{SnO}_2$  층 및 제 2 재료 (예를 들어,  $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 및  $\text{SiCN}$ 의 임의의 조합)의 층의 중착, 그리고 선택가능하게 패터닝 후에 획득된다.  $\text{SnO}_2$  층은 임의의 적합한 방법, 예컨대 CVD (PECVD를 포함), ALD (PEALD를 포함), 스퍼터링, 등에 의해 중착된다. 일부 실시예들에서, 기판 상의 임의의 돌출부들 및 리세스된 피쳐들의 표면들을 포함하여, 기판의 표면들을 따르도록,  $\text{SnO}_2$  막을 컨포멀하게 중착하는 것이 바람직하다. 일부 실시예들에서  $\text{SnO}_2$  층은 약 20 내지 100 Å의 두께로 컨포멀하게 중착된다. 컨포멀한  $\text{SnO}_2$  막의 적합한 중착 방법들 중 하나는 ALD이다. 열적으로 또는 플라즈마 강화된 ALD가 사용될 수 있다. 통상적인 열적 ALD 방법에서, 기판이 ALD 프로세스 챔버로 제공되고 후속하여 주석 함유 전구체, 그리고 산소 함유 반응물질에 노출되어,  $\text{SnO}_2$ 를 형성하도록 주석 함유 전구체 및 산소 함유 반응물질로 하여금 기판의 표면상에서 반응하게 한다. ALD 프로세스 챔버는 통상적으로, 프로세스 챔버의 별크 내 반응을 방지하기 위해 기판이 주석 함유 전구체에 노출된 후, 그리고 산소 함유 반응물질이 프로세스 챔버로 들어가기 전에 불활성 가스를 사용하여 펴지된다. 더욱이, ALD 프로세스 챔버는 통상적으로, 기판이 산소 함유 반응물질을 사용하여 처리된 후 불활성 가스를 사용하여 펴지된다. 순차적인 노출이 몇몇 사이클들에 대해 반복되고, 예를 들어, 약 10 내지 100 사이클들은 목표된 두께를 갖는  $\text{SnO}$  층이 중착될 때까지 수행될 수 있다. 적합한 주석 함유 전구체들의 예들은 할로겐화된 주석 함유 전구체들 (예컨대  $\text{SnCl}_4$ , 및  $\text{SnBr}_4$ ), 및 할로겐화되지 않은 주석 함유 전구체들, 예컨대 알킬 치환된 주석 아미드들 등을 포함하는, 유기주석 화합물들을 포함한다. ALD에 적합한 알킬 치환된 주석 아미드들의 구체적인 예들은 테트라키스(디메틸아미노) 주석, 테트라키스(에틸메틸아미노) 주석,  $\text{N}^2,\text{N}^3\text{-di-tert-부틸-부테인-2,3-디아미노-주석(II)}$  및  $(1,3\text{-bis}(1,1\text{-디메틸에틸})-4,5\text{-디메틸-(4R, 5R)-1,3,2-디아자스타노리딘-2-일리덴이다}$ . 산소 함유 반응물질들은 제한 없이 산소, 오존, 물, 과산화수소, 및  $\text{NO}_2$ 를 포함한다. 산소 함유 반응물질들의 혼합물들이 또한 사용될 수 있다. 중착 조건들은 ALD 반응물질들의 선택에 따라 가변할 것이고, 보다 반응성 전구체들은 일반적으로 보다 덜 반응성인 전구체들보다 낮은 온도들에서 반응할 것이다. 프로세스들은 통상적으로 약 20 내지 500 °C의 온도, 및 부압 (sub-atmospheric pressure)에서 수행될 것이다. 온도 및 압력은 응결을 방지하기 위해 반응물질들이 프로세스 챔버 내에서 가스 형태로 남아 있도록 선택된다. 반응물질 각각은 단독으로 또는 캐리어 가스, 예컨대 아르곤, 헬륨, 또는 질소와 혼합된 가스 형태로 프로세스 챔버로 제공된다. 이를 혼합물들의 플로우 레이트들은 프로세스 챔버의 사이즈에 따를 것이고, 일부 실시예들에서 약 10 내지 10,000 sccm이다.

[0027] 본 명세서에 제공된  $\text{SnO}_2$  층을 중착하기 적합한 열적 ALD 프로세스 조건들의 구체적인 예는 본 명세서에 참조로서 인용된, 제목이 "Tin Oxide with Controlled Morphology and Crystallinity by ALD onto Graphene Nanosheets for Enhanced Lithium Storage"인 Li 등의 논문 (*Advanced Functional Materials*, 2012, 22, 8, 1647-1654)에 기술된다. 프로세스는 ALD 진공 챔버 내에서 200 내지 400 °C의 온도에서 기판을  $\text{SnCl}_4$  (주석 함유 전구체) 및 탈 이온수 (산소 함유 반응물질)에 순차적으로 그리고 교번적으로 노출하는 것을 포함한다. ALD 사이클의 구체적인 예에서,  $\text{SnCl}_4$  증기와  $\text{N}_2$  캐리어 가스의 혼합물이 0.5 초 동안 ALD 프로세스 챔버 내로 도입되고, 이어서 3 초 동안 기판에 노출된다. 다음에, ALD 프로세스 챔버는 프로세스 챔버의 별크로부터

$\text{SnCl}_4$ 를 제거하기 위해 10 초 동안  $\text{N}_2$ 를 사용하여 퍼지되고,  $\text{H}_2\text{O}$  증기와  $\text{N}_2$  캐리어 가스의 혼합물이 1 초 동안 프로세스 챔버 내로 흐르고 3 초 동안 기판에 노출된다. 다음에, ALD 프로세스 챔버가  $\text{N}_2$ 를 사용하여 퍼지되고 사이클이 반복된다. ALD 프로세스는 부압 (예를 들어, 0.4 Torr) 및 200 내지 400 °C의 온도에서 수행된다.

[0028] 본 명세서에 제공된 방법들에서  $\text{SnO}$  막들을 증착하기 적합한 열적 ALD 프로세스 조건들의 또 다른 예는 전체가 본 명세서에 참조로서 인용된, 제목이 "In situ Examination of Tin Oxide ALD using Quartz Crystal Microbalance and Fourier Transform Infrared Techniques"인 Du 등의 논문 (*J. Vac. Sci. Technol. A* **23**, 581 (2005))에 제공된다. 이 프로세스에서 기판은 후속하여 약 150 내지 430 °C의 온도에서 ALD 프로세스 챔버에서  $\text{SnCl}_4$  및  $\text{H}_2\text{O}_2$ 에 노출된다.

[0029] ALD에서 할로겐화된 주석 전구체들의 사용이 많은 실시예들에서 적합하지만, 일부 실시예들에서  $\text{SnCl}_4$ 와 같은 할로겐화된 전구체들의 사용으로 발생할 수도 있는 부식 문제들을 방지하기 위해 할로겐화되지 않은 유기주석 전구체들을 사용하는 것이 보다 바람직하다. 적합한 할로겐화되지 않은 유기주석 전구체들의 예들은 알킬아미노 주석 (알킬화된 주석 아미드) 전구체들, 예컨대 테트라키스(디메틸아미노) 주석을 포함한다. 이 전구체를 사용하는 적합한 열적 ALD 증착 방법의 예는 전체가 본 명세서에 참조로서 인용된, 제목이 "Atomic Layer Deposition of Tin Oxide films using Tetrakis(dimethylamino) tin"인, Elam 등의 논문 (*J. Vac. Sci. Technol. A* **26**, 244 (2008))에 제공된다. 이 방법에서 기판이 ALD 챔버 내에서 약 50 내지 300 °C의 온도에서 테트라키스(디메틸아미노) 주석 및  $\text{H}_2\text{O}_2$ 에 순차적으로 노출된다. 유리하게, 이 전구체의 사용은 100 °C 이하의 저온들에서  $\text{SnO}_2$  막들의 증착을 허용한다. 예를 들어,  $\text{SnO}_2$  막들은 반응 레이트를 향상시키기 위해 플라즈마를 사용하지 않고 50 °C에서 증착될 수 있다. 테트라키스(디메틸아미노) 주석 및  $\text{H}_2\text{O}_2$ 를 사용한  $\text{SnO}$ 의 열적 ALD의 또 다른 예는 본 명세서에 참조로서 인용된, 제목이 "Atomic Layer Deposition of Indium Tin Oxide Thin films Using Nonhalogenated Precursors"인, Elam 등의 논문 (*J. Phys. Chem. C* **2008**, 112, 1938–1945)에 제공된다.

[0030] 반응성 유기주석 전구체의 사용한 저온 열적 ALD 프로세스의 또 다른 예는 전체가 본 명세서에 참조로서 인용된, 제목이 "Low temperature Atomic Layer Deposition of Tin Oxide"인 Heo 등의 논문 (*Chem. Mater.*, **2010**, 22(7) 4964–4973)에 제공된다. (본 명세서에 제공된  $\text{SnO}_2$  막들을 증착하는데 적합한) 이 증착 프로세스에서, 기판은 ALD 진공 프로세스 챔버에서  $\text{N}^2, \text{N}^3\text{-}tert\text{-부틸-부테인-2,3-디아미노-주석(II)}$  및 50 %  $\text{H}_2\text{O}_2$ 에 순차적으로 노출된다. 이들 반응물질들이 기화되고 각각은  $\text{N}_2$  캐리어 가스와 혼합되어 프로세스 챔버에 제공된다. 챔버는 기판의 반응물질에 대한 각각의 노출 후에  $\text{N}_2$ 를 사용하여 퍼지된다. 증착은 약 50 내지 150 °C의 온도에서 수행될 수 있다.

[0031] 과산화수소가 ALD 프로세스들에서  $\text{SnO}_2$ 의 형성을 위한 산소 함유 반응물질로서 일반적으로 잘 작용하지만, 때때로  $\text{H}_2\text{O}_2$  분해로 인해  $\text{SnO}_2$  막 성장에 대한 불충분한 제어를 제공할 수도 있다. 일부 실시예들에서, 보다 안정한 산소 함유 전구체, 예컨대 NO가 사용된다. 산소 함유 반응물질로서 NO를 사용한 적합한 프로세스의 예는 참조로서 본 명세서에 인용된, 제목이 "Atomic Layer Deposition of Tin Oxide with Nitric Oxide as an Oxidant Gas"인 Heo 등의 논문 (*J. Mater. Chem.*, **2012**, 22, 4599)에 제공된다. 증착은 약 130 내지 250 °C의 온도에서 기판을 고리형  $\text{Sn(II)}$  아미드 (1,3-bis(1,1-디메틸에틸)-4,5-디메틸-(4R, 5R)-1,3,2-디아자스타놀리딘-2-일리덴 및 NO에 순차적으로 노출하는 것을 수반한다.

[0032] 일부 실시예들에서,  $\text{SnO}_2$  막들은 PEALD에 의해 증착된다. 열적 ALD에 대해 기술된 바와 같은 동일한 타입들의 주석 함유 전구체들 및 산소 함유 반응물질들이 사용될 수 있다. PEALD에서 ALD 장치는 프로세스 챔버 내에서 플라즈마를 생성하기 위한, 그리고 플라즈마를 사용하여 기판을 처리하기 위한 시스템을 구비한다. 통상적인 PEALD 프로세스 시퀀스에서, 기판이 PEALD 프로세스 챔버에 제공되고 기판의 표면에 흡착하는 주석 함유 전구체에 노출된다. 프로세스 챔버는 프로세스 챔버로부터 전구체를 제거하기 위해 불활성 가스 (예를 들어, 아르곤 또는 헬륨)를 사용하여 퍼지되고, 기판은 프로세스 챔버 내로 도입되는 산소 함유 반응물질에 노출된다. 산소 함유 반응물질의 도입과 동시에 또는 지연 후에, 플라즈마가 프로세스 챔버 내에서 형성된다. 플라즈마는  $\text{SnO}_2$ 의 형성을 발생시키는 기판의 표면 상에서 주석 함유 전구체와 산소 함유 반응물질 간의 반응을 용이하게 한다. 다음에, 프로세스 챔버는 불활성 가스를 사용하여 퍼지되고, 주석 전구체 도장, 퍼지, 산소 함유 반응물질

도정, 플라즈마 처리, 및 제 2 퍼지를 포함하는 사이클이 목표된 두께의 막을 형성하기 위해 필요한 만큼 여러 번 반복된다.

[0033]  $\text{SnO}_2$  막의 PEALD 형성에 적합한 프로세스 조건들의 예는 본 명세서에 참조로서 인용된, 제목이 "The Fabrication of Tin Oxide Films by Atomic Layer Deposition using Tetrakis(ethylmethyldiamino) tin Precursor"인 Seop 등의 논문 (*Transactions on Electrical and Electronic Materials*, 2009, 10, 5, 173-176)에 제공된다. 기판이 PEALD 프로세스 챔버 내로 제공되고 플라즈마 부재시 4 초의 노출과 함께 테트라키스(에틸메틸아미노) 주석에 노출된다. 다음에, 주석 함유 전구체는 20 초 동안 프로세스 챔버를 통해 아르곤을 흘림으로써 프로세스 챔버로부터 퍼지된다. 이어서,  $\text{O}_2$ 가 2 초와 100 W의 RF 전력을 사용한 부가적인 2 초 동안 주입된다. 아르곤 퍼지가 이어지고, 일 PEALD 사이클이 종료된다. 이 예에서, 프로세스는 50 내지 200 °C의 온도 범위 및 0.8 Torr의 압력에서 수행된다.

[0034] ALD (열적 및 플라즈마 강화 모두) 는  $\text{SnO}_2$  막들을 증착하는데 바람직한 방법들 중 하나이고, 다른  $\text{SnO}_2$  증착 방법들, 예컨대 CVD, PECVD, 및 스퍼터링이 또한 사용될 수 있다는 것이 이해된다.

[0035] 제 2 재료 ( $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 및  $\text{SiCN}$  중 어느 하나) 가 PECVD, CVD, ALD, 및 PEALD를 포함하는 다양한 방법들에 의해 증착될 수 있다. 일부 실시예들에서 제 2 재료는 PECVD에 의해 증착된다. 이 방법에서, 플라즈마는 실리콘 함유 전구체 및 기판 상의 제 2 재료의 증착을 위해 제어된 조건들 하에서 제 2 재료의 하나 이상의 엘리먼트들을 함유하는 반응물질을 포함하는 프로세스 가스로 형성된다. 예를 들어,  $\text{SiO}_2$ 는 실리콘 함유 전구체 및 산소 함유 반응물질을 포함하는 프로세스 가스로 플라즈마를 형성함으로써 증착될 수도 있고;  $\text{SiC}$ 는 실리콘 함유 전구체 및 탄소 함유 반응물질을 포함하는 프로세스 가스로 플라즈마를 형성함으로써 증착될 수도 있고;  $\text{SiN}$ 은 실리콘 함유 전구체 및 질소 함유 반응물질을 포함하는 프로세스 가스로 플라즈마를 형성함으로써 증착될 수도 있고;  $\text{SiOC}$ 는 실리콘 함유 전구체, 산소 함유 반응물질 및 탄소 함유 반응물질을 포함하는 프로세스 가스로 플라즈마를 형성함으로써 증착될 수도 있고;  $\text{SiNO}$ 는 실리콘 함유 전구체, 산소 함유 반응물질, 및 질소 함유 반응물질을 포함하는 프로세스 가스로 플라즈마를 형성함으로써 증착될 수도 있고;  $\text{SiCNO}$ 는 실리콘 함유 전구체, 산소 함유 반응물질, 탄소 함유 반응물질, 및 질소 함유 반응물질을 포함하는 프로세스 가스로 플라즈마를 형성함으로써 증착될 수도 있고; 및  $\text{SiCN}$ 은 실리콘 함유 전구체, 탄소 함유 반응물질, 및 질소 함유 반응물질을 포함하는 프로세스 가스로 플라즈마를 형성함으로써 증착될 수도 있다. 실리콘 함유 전구체가 제 2 재료의 임의의 필수 엘리먼트들을 더 포함하는, 이들 경우들에서, 실리콘 함유 전구체 및 반응물질이 동일 할 수도 있다. 예를 들어, TEOS는  $\text{SiO}_2$ 의 증착 동안 실리콘 함유 전구체 및 산소 함유 반응물질 모두로서 역할을 할 수 있다. 실리콘 함유 전구체들의 예들은 실란, 디실란, 테트라알킬실란들, 트리알킬실란들, 실록산들, TEOS, 등을 포함한다. 산소 함유 반응물질들의 예들은  $\text{CO}_2$ ,  $\text{N}_2\text{O}$ ,  $\text{O}_2$ ,  $\text{O}_3$ ,  $\text{H}_2\text{O}$ 를 포함한다. 질소 함유 반응물질들의 예들은  $\text{N}_2$ , 및  $\text{NH}_3$ 을 포함한다. 탄소 함유 반응물질들의 예들은 하이드로카본들, 예컨대 메탄, 에탄, 프로판, 등을 포함한다. 이들 재료들의 증착에 사용된 프로세스 가스들은 또한 캐리어 가스, 예컨대 He, Ar, Ne, 등을 포함할 수도 있다.

[0036] 수소 플라즈마를 활용하는  $\text{SnO}_2$  에칭 방법들은 광범위한 프로세스 조건들 하에서 다양한 장치들에서 구현될 수 있다. 이 방법들은, 일부 실시예들에서, 노출된 주석 옥사이드 층을 갖는 반도체 기판을 에칭 챔버에 제공하는 단계, 및  $\text{H}_2$ , 및 선택 가능하게 캐리어 가스, 예컨대 헬륨 또는 또 다른 불활성 가스를 포함하는 프로세스 가스로 형성된 플라즈마와 기판을 콘택트하는 단계를 수반한다. 용어 "에칭 챔버" 또는 "에칭 장치"는 에칭을 위해 구성된 챔버 및 장치를 지칭한다. 일부 실시예들에서 "에칭 챔버" 또는 "에칭 장치"는 에칭 동작들을 위해 배타적으로 구성된다. 다른 실시예들에서 "에칭 챔버" 또는 "에칭 장치"는 에칭에 부가하여, 다른 동작들 예컨대 예를 들어, 증착을 수행하도록 구성될 수도 있다. 예를 들어, 일부 실시예들에서 에칭 챔버는 또한 ALD 증착을 위해 사용될 수도 있다.

[0037] 일부 실시예들에서 수소 플라즈마 에칭에 사용된 플라즈마는 반도체 기판을 하우징하는 동일한 프로세스 챔버 내에서 생성된다. 다른 실시예들에서 플라즈마는 리모트로 생성되고, 프로세스 챔버 내 하나 이상의 유입부들을 통해 기판을 하우징하는 프로세스 챔버 내로 도입된다.

[0038] 에칭은 예컨대  $\text{SnO}_2$ 를 휘발성  $\text{SnH}_4$ 로 변환하도록 제어된다. 바람직하게, 프로세스 가스 내  $\text{H}_2$  함량은 적어도 약 50 체적% (% by volume), 예컨대 적어도 약 80 체적% (최대 100 %를 포함할 수 있다) 이다. 일부 실시예들

에서, 프로세스 가스는 하이드로카본, 예컨대  $\text{CH}_4$ 를 더 포함할 수도 있다. 일부 실시예들에서, 프로세스 가스는  $\text{Cl}_2$ 를 더 포함한다. 예를 들어, 프로세스 가스는 본질적으로  $\text{H}_2$  및 불활성 가스 (예를 들어,  $\text{He}$ )로 구성될 수도 있고, 또는 프로세스 가스는 본질적으로  $\text{H}_2$ , 불활성 가스 및 하이드로카본 (예를 들어,  $\text{CH}_4$ )으로 구성될 수도 있다. 에칭은 기판 근방에서 측정된, 약 100 °C 미만의 온도에서 수행된다. 에칭 반응은 유리하게 휘발성 재료들만, 예컨대  $\text{SnH}_4$ 를 생성하고, 휘발성 재료들은 배기 및/또는 퍼지에 의해 에칭 프로세스 챔버로부터 용이하게 제거될 수 있다. 고온이 형성된  $\text{SnH}_4$ 의 분해 및 프로세스 챔버 및 기판을 오염시킬 수 있는, 입자들의 형성을 야기할 수 있기 때문에 에칭 프로세스 온도는 바람직하게 약 100 °C 미만으로 선택된다. 프로세스 가스의 조성 및 프로세스 조건들은 예컨대 에칭 동안 입자들의 형성을 감소시키거나 제거하도록 선택된다. 중요하게, 에칭 반응은 임의의 상당한 스퍼터링 컴포넌트를 필요로 하지 않고, 기판에서 외부 바이어스의 부재시, 그리고 중이온들 (예를 들어, 아르곤 이온들)의 부재시 수행될 수 있다. 스퍼터링 컴포넌트를 감소시키는 것은 기판상의 제 2 재료에 대한 에칭 선택도를 상승시키기에 유리할 수 있다. 따라서, 일부 실시예들에서 에칭은 기판에 외부 바이어스를 제공하지 않고 수행되고 그리고/또는 스퍼터링을 감소시키도록, 캐리어 가스로서 헬륨 (가벼운 가스)을 사용하는 것을 수반한다.

[0039] 수소 플라즈마 에칭을 위한 플라즈마는 다양한 (낮고 높은) 주파수들을 사용하여 생성될 수 있다. 적합한 주파수들의 예들은 400 kHz, 2 MHz, 13.56 MHz, 27 MHz 또는 2.45 GHz를 포함한다. 플라즈마 생성에 사용된 전력은 일부 실시예들에서, 약 0.0018 내지 0.36 W/cm<sup>2</sup>의 전력 밀도에 대응하는 약 50 W 내지 1,000 W의 범위일 수 있다. 기판에서 바이어스는 선택가능하고, 바이어스 전력은 약 0 내지 500 W의 범위일 수 있다. (일 300 mW 웨이퍼를 프로세싱하기 위해) 적합한 샤크헤드 당 가스 플로우 레이트들은:

[0041] i.  $\text{H}_2$ : 25 내지 750 sccm;

[0042] ii.  $\text{Cl}_2$ : 0 내지 500 sccm (예를 들어, 5 내지 200 sccm);

[0043] iii.  $\text{He}$ : 0 내지 500 sccm (예를 들어, 5 내지 100 sccm); 그리고

[0044] iv.  $\text{CH}_4$ : 0 내지 500 sccm (예를 들어, 5 내지 100 sccm) 이다.

[0045] 에칭 프로세스는 일부 실시예들에서, 약 1 내지 175 mTorr의 압력에서 수행될 수 있다.

[0046] 일부 특정한 실시예들에서, 플라즈마는 고 주파수 생성 (예를 들어, 13.56 MHz 또는 27 MHz)을 사용하여 생성되고, 0.07 내지 0.18 W/cm<sup>2</sup>의 전력 밀도에 대응하는 약 200 내지 500 W의 플라즈마 전력을 사용하여 제공된다. 기판에서 바이어스에 대한 전력은 약 0 내지 200 W이다. (일 300 mW 웨이퍼를 프로세싱하기 위해) 적합한 샤크헤드 당 가스 플로우 레이트들은:

[0048] i.  $\text{H}_2$ : 100 내지 300 sccm;

[0049] ii.  $\text{Cl}_2$ : 0 내지 200 sccm (예를 들어, 5 내지 100 sccm);

[0050] iii.  $\text{He}$ : 0 내지 100 sccm (예를 들어, 5 내지 50 sccm);

[0051] iv.  $\text{CH}_4$ : 0 내지 100 sccm (예를 들어, 5 내지 50 sccm) 이다.

[0053] 이를 실시예들에서 에칭 프로세스는 약 1 내지 30 mTorr의 압력에서 수행된다.

[0054] 일부 실시예들에서, 에칭 전에, 노출된  $\text{SnO}_2$  층을 포함하는 기판은 또한  $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 및  $\text{SiCN}$ 으로 구성된 그룹으로부터 선택된 재료의 노출된 층을 포함하고, 제공된 에칭 방법은 이를 재료들에 대해 고 선택도로  $\text{SnO}_2$ 를 에칭한다. 일부 실시예들에서 에칭은  $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 및  $\text{SiCN}$ 으로 구성된 그룹으로부터 선택된 재료를 완전히 제거하지 않고, 기판의 표면으로부터 노출된  $\text{SnO}_2$ 를 완전히 제거한다.

[0055] 또 다른 양태에서, 기판 상에 에어 캡들을 형성하기 위한 방법이 제공되고,  $\text{SnO}_2$ 가 에어 캡들의 형성시 제거가능한 스페이서 재료로서 사용된다. 예를 들어  $\text{SnO}_2$ 로 이루어진 에어 캡 스페이서들이 FinFET 디바이스들에 사용될 수 있다.

[0056]

종래 기술들은 다음 중 하나 이상을 사용한다. DRAM 제조시,  $\text{SiO}_2$ 이 사용되고 HF를 사용하여 제거된다. 이 화학물질은 HF에 의한 다른 막들의 화학적 공격 및 매우 고 종횡비 구조들 (>15:1)에 침투하는 문제들로 인해 제한된 용법을 갖는다. 로직 제조시 종래의 FinFET 에어 캡 스페이서들의 사용은 매우 많은 단계들로 인해 매우 복잡할 수 있다. 더욱이, 재료 조합들의 완벽한 선택은 가용하지 않다. 습식 에칭 프로세스들의 사용은 소형 피처 및/또는 고 종횡비 피처 프로세싱 문제를 만든다. 이를 단점들은 본 명세서에서  $\text{SnO}_2$  에어 캡 스페이서들을 도입하고 프로세싱 방법들에 의해 처리된다.

[0057]

도 2는 제거가능한  $\text{SnO}_2$  스페이서들을 사용하여 반도체 기판 상에 에어 캡들을 생성하는 방법의 실시예들을 예시하는 프로세스 흐름도이다. 방법은 동작 2201에서 노출된 제 1 재료의 층, 및 노출된 제 2 재료의 층, 및 제 1 재료의 층과 제 2 재료의 층 사이에 위치된 노출된  $\text{SnO}_2$ 의 층을 갖는 반도체 기판을 제공함으로써 시작된다. 제 1 재료와 제 2 재료는 동일한 재료일 수도 있고, 또는 상이한 재료들일 수도 있다. 예를 들어 제 1 재료, 및 제 2 재료는  $\text{SiO}_2$ ,  $\text{SiC}$ ,  $\text{SiN}$ ,  $\text{SiOC}$ ,  $\text{SiNO}$ ,  $\text{SiCNO}$ , 및  $\text{SiCN}$ 으로부터 독립적으로 선택될 수도 있다. 일부 실시예들에서, 제 1 재료 및 제 2 재료는 모두  $\text{SiO}_2$ 이다. 다른 실시예들에서 제 1 재료는  $\text{SiO}_2$ 이고 제 2 재료는  $\text{SiN}$ 이다. 일반적으로, 임의의 조합의 재료들이 선택될 수 있다. 다음에, 동작 2203에서, 노출된  $\text{SnO}_2$ 은 본 명세서에 기술된 수소 플라즈마 에칭 화학물질을 사용하여 제 1 재료 및 제 2 재료 모두에 대해 선택적으로 에칭된다. 에칭은 노출된 제 1 재료 및 제 2 재료의 존재시  $\text{SnO}_2$ 를 제거하고 제거된  $\text{SnO}_2$  대신 리세스된 피쳐를 형성한다. 제 1 재료와 제 2 재료 모두에 대한  $\text{SnO}_2$  제거의 에칭 선택도는 바람직하게 적어도 약 5, 예컨대 적어도 약 10, 또는 적어도 약 50이다. 80 초과, 예컨대 100의 에칭 선택도들이 또한 기술된 방법들을 사용하여 달성될 수 있다. 다음에, 동작 2205에서, 제 3 재료가 리세스된 피쳐를 완전히 충진하지 않고 리세스된 피쳐 위에 증착되어, 제 1 재료의 층과 제 2 재료의 층 사이에 에어 캡을 형성한다. 제 3 재료는 임의의 적합한 재료이고, 제 1 재료와 제 2 재료 각각과 동일하거나 상이할 수도 있다. 일부 실시예들에서 제 3 재료는 유전체이다. 일부 실시예들에서, 제 3 재료는, 예를 들어, PECVD 또는 HDP (high density plasma) CVD에 의해 증착된  $\text{SiO}_2$ 이다.

[0058]

유리하게, 본 명세서에 제공된  $\text{SnO}_2$ 에 대한 에칭 프로세스들은 습식 에칭을 필요로 하지 않고, 그리고 불소 함유 화학물질에 대한 노출을 필요로 하지 않는다. 유리하게,  $\text{SnO}_2$ 에 대한 수소 플라즈마 에칭은 디바이스의 구조적 붕괴를 유발하지 않고 (예를 들어, 20 내지 100 Å) 매우 좁은 폭들을 갖는  $\text{SnO}_2$  층들 상에서 수행될 수 있다. 구조적 붕괴는 매우 작은 사이즈들을 갖는 스페이서들의 습식 에칭 동안 직면하는 문제이다. 일반적으로, 에어 캡 형성 시퀀스들에서  $\text{SnO}_2$  층의 폭들은 넓은 범위 (예를 들어, 10 내지 5,000 Å)에 걸쳐 가변할 수 있지만, 제공된 방법은 20 내지 100 Å의 폭들을 갖는 좁은  $\text{SnO}_2$  스페이서들을 갖는 기판들을 프로세싱하는데 특히 유리하다.

[0059]

에어 캡들을 형성하기 위한 프로세싱 시퀀스의 일 예는 실시예들 중 하나에 따른, 에어 캡 형성 동안 반도체 기판의 단면 개략도들을 도시하는, 도 3a 내지 도 3g에 제공된다. 도 3a 내지 도 3e는 노출된 제 1 재료의 층과 노출된 제 2 재료의 층 사이에 노출된  $\text{SnO}_2$  층을 포함하는 기판을 획득하도록 사용될 수 있는 프로세싱 단계들을 예시한다. 다양한 다른 방법들이 이러한 기판을 획득하도록 사용될 수 있다는 것이 이해된다. 예시된 방법은 기판 (303) 상에 게이트 (301)를 형성하는 것을 수반하고, 도 3a에 도시된 구조체를 발생시킨다. 게이트는 기판 상에 돌출하는 피쳐이다. 일부 실시예들에서 게이트 (301)는 하이-k 옥사이드, 예컨대, 예를 들어, 하프늄 옥사이드이다. 다음에, 도 3b에 예시된 바와 같이, 제 1 재료의 층 (305)이 기판 (303) 및 게이트 (301)를 커버하도록 기판 위에 컨포밀하게 형성된다. 중요하게, 층 (305)은 게이트 (301)의 게이트 측벽들 및 상단 표면 모두 위에서 게이트를 커버한다. 일 예시적인 예에서, 층 (305)은  $\text{SiN}$  층이다. 컨포밀한 증착은 예를 들어, ALD에 의해 달성될 수 있다. 다음에,  $\text{SnO}_2$  층 (307)이 도 3c에 도시된 바와 같이, 층 (305) 위에 컨포밀하게 형성된다.  $\text{SnO}_2$  층 (307)은 아래에 놓인 층 (305)과 콘택트하여 놓이고 기판 (303) 위 그리고 게이트 (301) 위에 놓인다.  $\text{SnO}_2$  층은 게이트의 게이트 측벽들 및 상단 표면 모두에서 게이트를 커버한다.  $\text{SnO}_2$  층은 ALD 또는 PECVD에 의해 증착될 수 있다. 다음에, 제 2 재료의 층 (309)이  $\text{SnO}_2$  층 (307) 상으로 기판 위에 컨포밀하게 증착되어 도 3d에 도시된 구조체를 발생시킨다. 일부 실시예들에서 제 2 재료는  $\text{SiO}_2$ 이다. 제 2 재

료는  $\text{SnO}_2$  층과 콘택트하고 기판 (303) 및 게이트 (301) 위에 놓이고, 게이트의 측벽들 및 상단 표면 모두에서 게이트를 커버한다. 다음 단계에서, 구조체가 (예를 들어, CMP를 사용하여) 평탄화된다. 이 단계는 게이트의 상단 표면으로부터 제 2 재료 (예를 들어,  $\text{SiO}_2$ )의 층을 제거하고, 그리고 게이트의 측벽들에서  $\text{SnO}_2$  층을 노출한다. 도 3e에 노출된 구조체는 평탄화 후 기판을 예시한다. 이는 게이트의 측벽들에서  $\text{SnO}_2$  층 (307) 이 노출된 제 1 재료의 층 (305) 과 노출된 제 2 재료의 층 (309) 사이에 놓이는 것을 도시한다. 이 구조체는 도 2의 프로세스 흐름도의 동작 2201에서 사용될 수 있는 일 가능한 구조체이다.  $\text{SnO}_2$  층이 실질적으로 컨포멀하게 증착된다면, 수평 표면들 상에 증착된  $\text{SnO}_2$  층의 두께는 게이트의 측벽들에서 노출된  $\text{SnO}_2$  층의 폭과 유사할 것이다. 예를 들어,  $\text{SnO}_2$ 가 약 20 내지 100 Å의 두께로 증착되면, 게이트의 측벽에서 노출된  $\text{SnO}_2$  층은 약 20 내지 100 Å의 폭을 가질 것이다.

[0060] 다음에, 본 명세서에 기술된 바와 같이, 수소 플라즈마 에칭이 수행된다. 도 3e에 도시된 기판은 에칭 프로세스 캠버 내에  $\text{H}_2$ 를 포함하는 프로세스 가스로 형성된 플라즈마와 콘택트하고, 노출된  $\text{SnO}_2$  층 (307) 은 제 2 재료의 층 (309) 과 제 1 재료의 층 (305) 사이에 리세스된 피처를 형성하도록 (다른 노출된 재료들에 대해) 선택적으로 에칭된다. 발생되는 구조체는, 층 (309) 과 층 (305) 사이에 리세스된 피처 (311) 를 예시하는 도 3f에 도시된다. 마지막으로, 후속하는 단계에서, 리세스된 피처 (311) 를 완전히 충진하지 않고 리세스된 피처 (311) 를 커버하도록 제 3 재료 (예를 들어,  $\text{SiO}_2$ ) 의 층 (313) 이 예를 들어, HDP CVD에 의해 증착되어, 에어 캡이 형성된다.

[0061] 에어 캡을 형성하기 위한 방법의 보다 구체적인 예는: (a) 기판 상에 게이트를 형성하는 단계, 여기서 게이트는 하이-k 옥사이드를 포함함; (b) 게이트와 콘택트하여 (게이트의 측벽들 상 및 게이트의 상단 표면 상 모두에) ALD에 의해  $\text{SiN}$  층을 컨포멀하게 증착하는 단계; (c) 예를 들어, ALD 또는 PECVD에 의해  $\text{SiN}$  층의 층 위에  $\text{SnO}_2$  층을 컨포멀하게 형성하는 단계; (d)  $\text{SiO}_2$  층 위에  $\text{SiO}_2$  층을 컨포멀하게 형성하는 단계; (e) 구조체를 (예를 들어, CMP에 의해) 평탄화하는 단계, 여기서 평탄화는 수평 표면으로부터  $\text{SiO}_2$ 를 제거하고 게이트의 측벽들에서  $\text{SnO}_2$  및 제 1 재료를 노출하여, 노출된  $\text{SiN}$  층, 노출된  $\text{SiO}_2$  층, 및 이들 층들 사이에 위치된 노출된  $\text{SnO}_2$  층을 갖는 기판을 제공함; (f)  $\text{SiN}$  및  $\text{SiO}_2$ 에 대하여 고 에칭 선택도로 본 명세서에 기술된 바와 같이 수소 플라즈마를 사용하여 노출된  $\text{SnO}_2$ 을 에칭하고  $\text{SiN}$ 과  $\text{SiO}_2$  층들 사이에 리세스된 피처를 형성하는 단계; 및 (g) 리세스된 피처를 완전히 충진하지 않고 리세스된 피처 위에  $\text{SiO}_2$ 를 증착하여 제 1 재료 층과 제 2 재료 층 사이에 에어 캡을 형성하는 단계를 포함한다. 일부 실시예들에서, 증착되고 수소 플라즈마 에칭에 의해 제거되는  $\text{SnO}_2$  층의 폭은 약 20 내지 100 Å이다.

[0062] FinFET 디바이스 제조시 에어 캡들을 형성하기 위한 상세한 프로세싱 스킴은 본 명세서에 제공된  $\text{SnO}_2$  스페이서들과 함께 사용될 수 있는 에어 캡 형성 방법을 제공할 목적을 위해, 전체가 본 명세서에 참조로서 인용된, 2016년 12월 6일 허여된, 명칭이 "Air Gap Spacer Integration For Improved Fin Device Performance"인 Besser 등의 공동으로 소유된 미국 특허 제 9,515,156 호에 기술된다. 일부 실시예들에 따른 FinFET 디바이스 제조의 맥락에서 에어 캡들을 형성하기 위한 방법들은, FinFET 디바이스 제조의 다양한 스테이지들 동안 반도체 기판의 사시도들을 도시하는, 도 4a 내지 도 4t를 참조하여 기술된다.

[0063] 일부 실시예들에서 에어 캡 스페이서들을 갖는 FinFET 디바이스들 및 희생적  $\text{SnO}_2$  스페이서들을 사용하여 FinFET 디바이스들 내로 에어 캡들을 집적하기 위한 방법들이 제공된다. 에어 캡 스페이서들은 집적 동안 희생적  $\text{SnO}_2$  스페이서를 사용하여 형성된다. 희생적 스페이서는 셀프-정렬된 소스/드레인 콘택트 형성 후 후속하여 제거된다. 에어 캡 스페이서는 FinFET 기생 커패시턴스를 감소시킨다. 저 기생 커패시턴스는 프로세스 원도우의 손실 또는 리소그래피 오버레이 요건들의 완화 없이 달성될 수 있다.

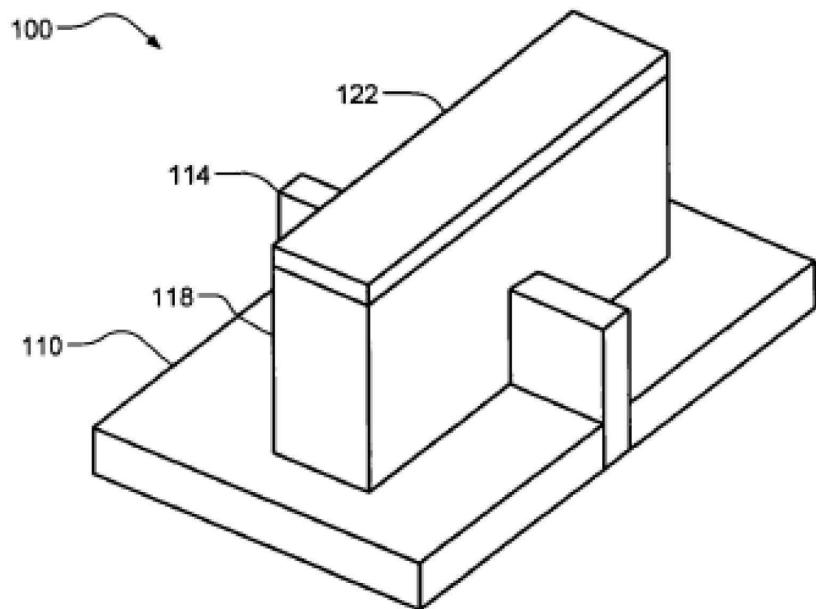

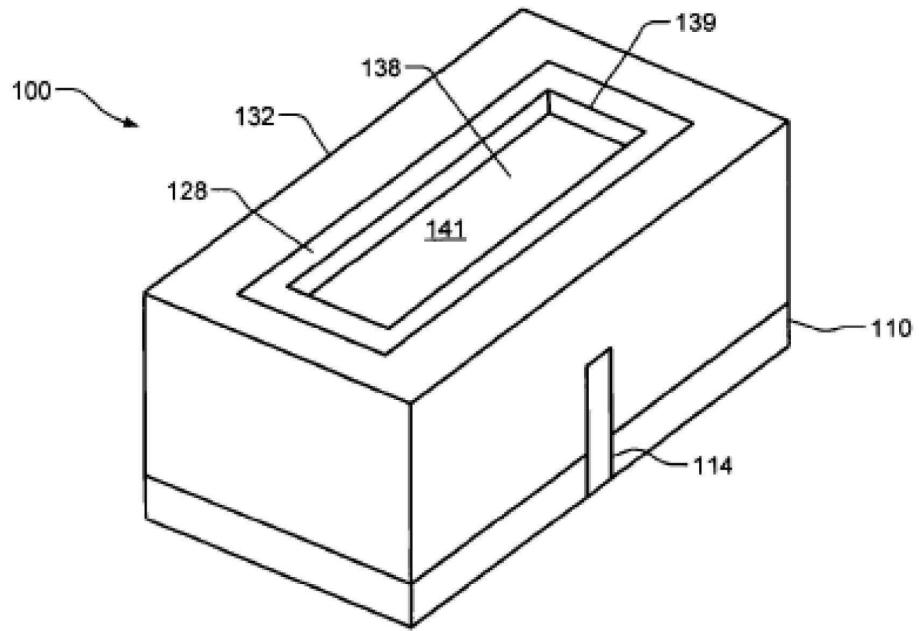

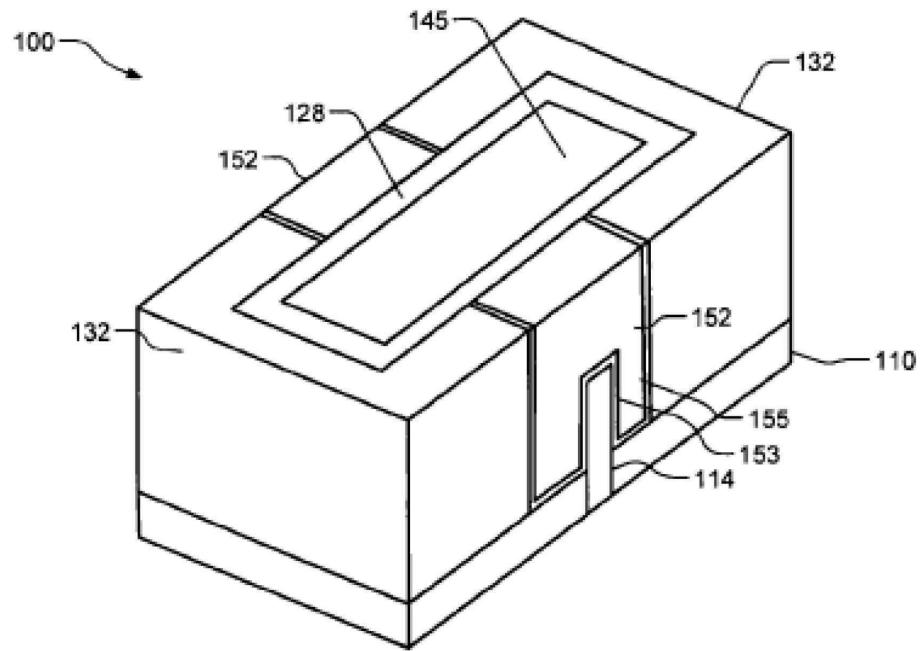

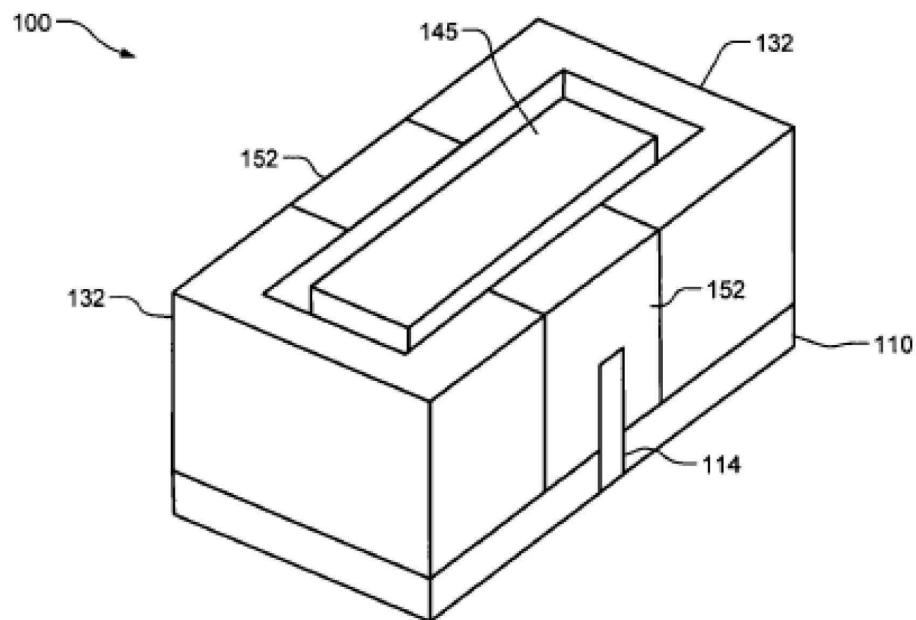

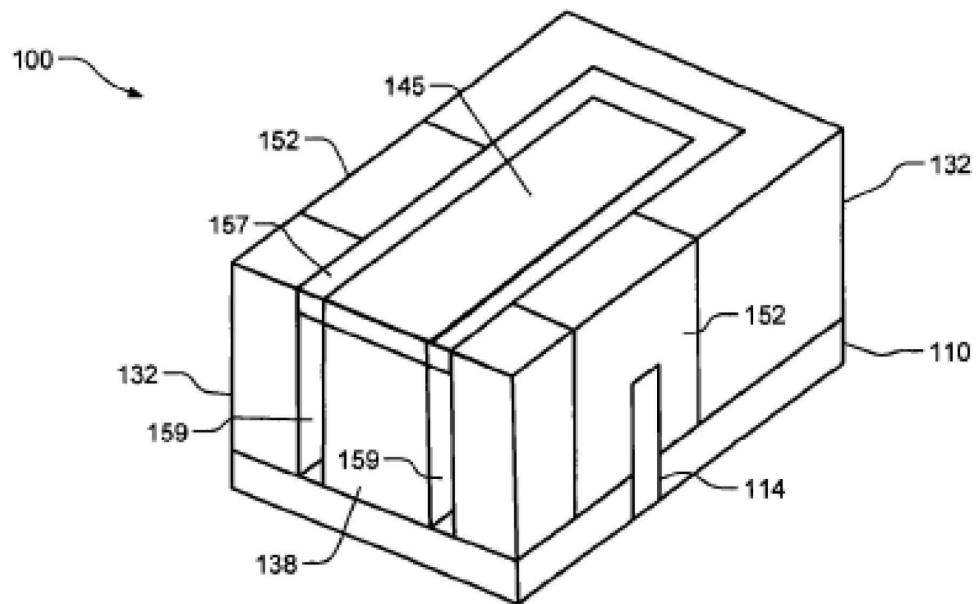

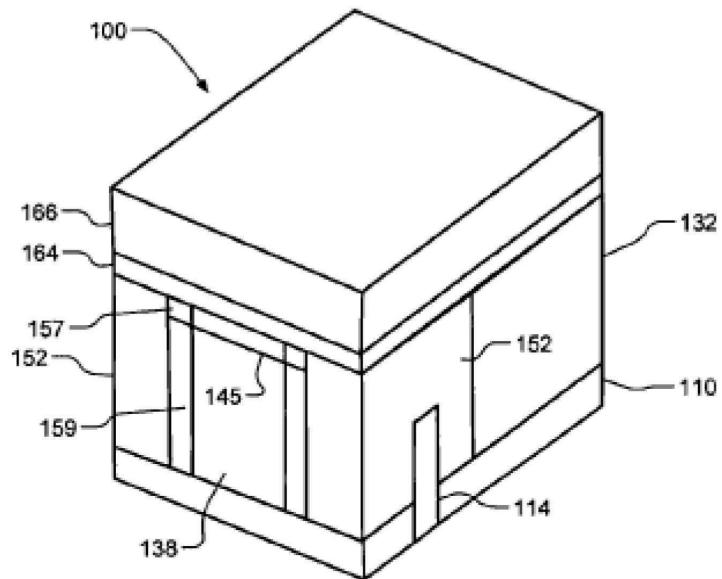

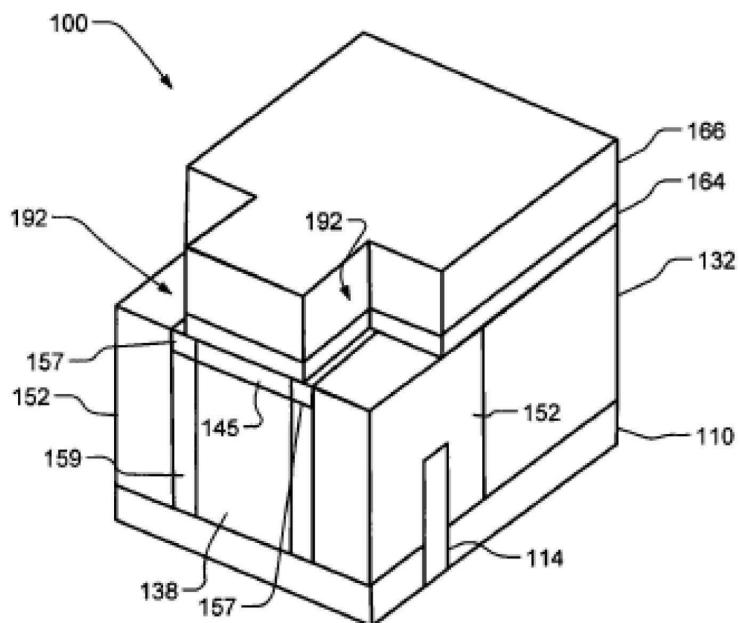

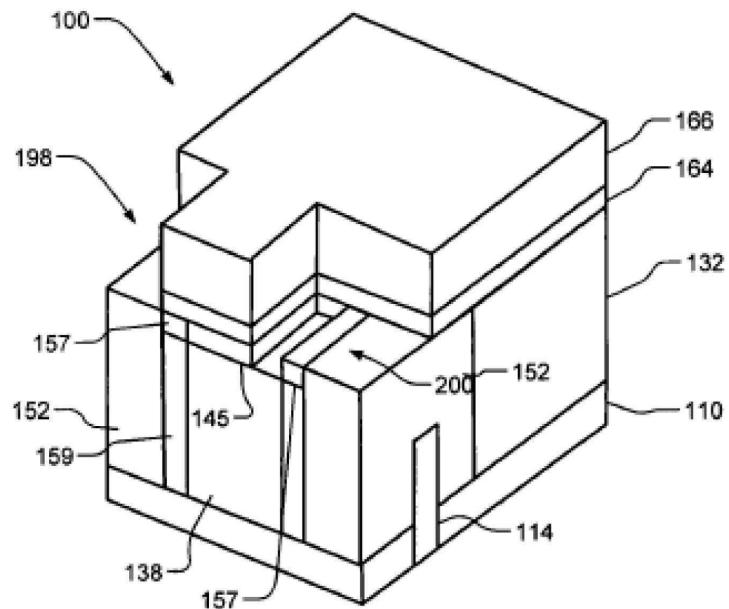

[0064] 이제 도 4a 및 도 4b를 참조하면, 각각 STI (shallow trench isolation) 리세스 에칭 및 더미 게이트 형성 후의 기판이 도시된다. 도 4a에서, 기판 (100) 은 ILD (inter-layer dielectric) 층 (110) 및 복수의 핀들 (fins) (114) 을 포함한다. ILD 층 (110) 은 로우 k 유전체들, 도핑된 옥사이드들, 유동성 옥사이드들, 실리콘 다이옥사이드 ( $\text{SiO}_2$ ) 또는 다른 적합한 재료로 이루어질 수도 있다. 일부 예들에서, 복수의 핀들 (114) 은 STI 옥사이드를 개재하여 실리콘 (Si) 으로 이루어질 수도 있다. STI 옥사이드는 또한 복수의 핀들 (114) 의 상단

표면 상에 위치될 수도 있다.

[0065] 도 4b에서, 더미 게이트 (118) 가 복수의 핀들 (114) 위에 증착되고 에칭된다. 일부 예들에서, 더미 게이트 (118) 는 ILD 층 (110) 상에 배치되고 복수의 핀들 (114) 로 가로질러 연장한다. 일부 예들에서, 더미 게이트 (118) 는 폴리실리콘으로 이루어진다. 하드마스크 층 (122) 은 에칭 동안 더미 게이트 (118) 를 마스킹하도록 사용될 수도 있다.

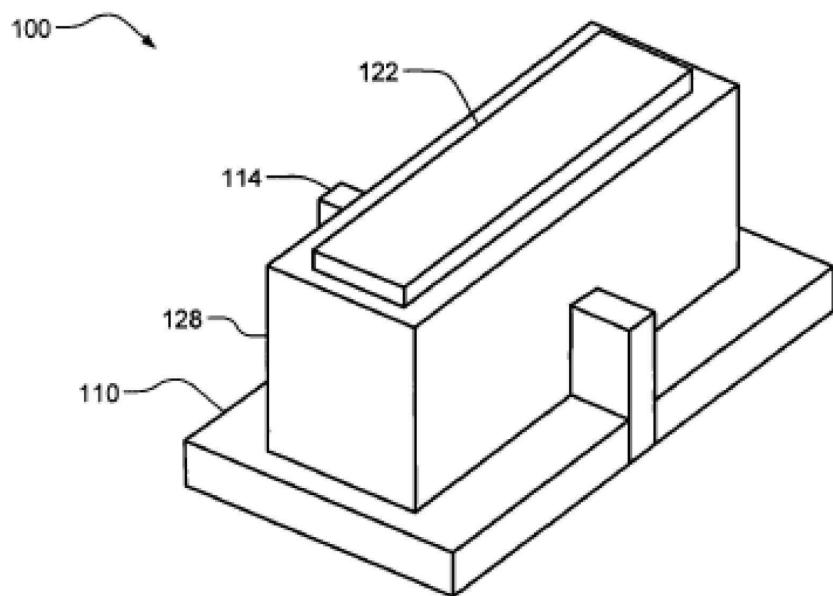

[0066] 이제 도 4c 및 도 4d를 참조하면, 각각 희생적 SnO<sub>2</sub> 스페이서가 증착되고 에칭되고 더미 게이트가 제거된다. 도 4c에서, 희생적 SnO<sub>2</sub> 스페이서 (128) 는 더미 게이트 (118) 의 외측 표면 둘레에 증착되고, 예를 들어, 본 명세서에 기술된 수소 플라즈마 에칭을 사용하여 에칭된다. 도 4d에서, ILD 층 (132) 이 희생적 SnO<sub>2</sub> 스페이서 (128) 둘레에 증착된다. 이에 더하여, 더미 게이트 (118) 및 하드마스크 층 (122) 이 에칭 또는 애싱에 의해 제거된다. 일부 예들에서, 더미 게이트 (118) 를 형성하는 실리콘인 기판 (100) 의 SnO<sub>2</sub> 및 실리콘 다이옥사이드 (SiO<sub>2</sub>) 재료에 대해 선택적으로 에칭된다.

[0067] 도 4e에서, RMG (replacement metal gate) 형성이 도시된다. RMG (138) 는 더미 게이트 (118) 의 이전 위치에 증착된다. 일부 예들에서, RMG (138) 는 1 내지 10 nm의 미리 결정된 두께의 HK (high dielectric) 상수를 갖는다. 일부 예들에서, RMG (138) 는 하프늄 옥사이드 (HfO<sub>2</sub>), HfSiO<sub>2</sub>, 알루미늄 옥사이드 (Al<sub>2</sub>O<sub>3</sub>), 지르코늄 옥사이드 (ZrO<sub>2</sub>) 또는 티타늄 옥사이드 (TiO<sub>2</sub>) 와 같은 HK 상수 재료들; 티타늄 나이트라이드 (TiN), 티타늄 알루미늄 나이트라이드 (TiAlN), 텉스텐 나이트라이드 (W<sub>N</sub><sub>x</sub>) (여기서 x는 정수), 텉스텐 탄소 나이트라이드 (WCN<sub>x</sub>), 코발트 (Co), 또는 다른 금속들과 같은 금속 일함수 설정 재료; 및 텉스텐 (W), 코발트 (Co) 또는 알루미늄 (Al) 및 이들의 합금들과 같은 벌크 도전성 금속으로 이루어진다. 일부 예들에서, CMP는 RMG (138) 의 증착 후 수행될 수도 있다. 일부 예들에서, RMG (138) 의 상단 표면은 CMP 후에, 희생적 SnO<sub>2</sub> 스페이서 (128) 및 ILD 층 (132) 의 상단 표면과 동일 평면이다.

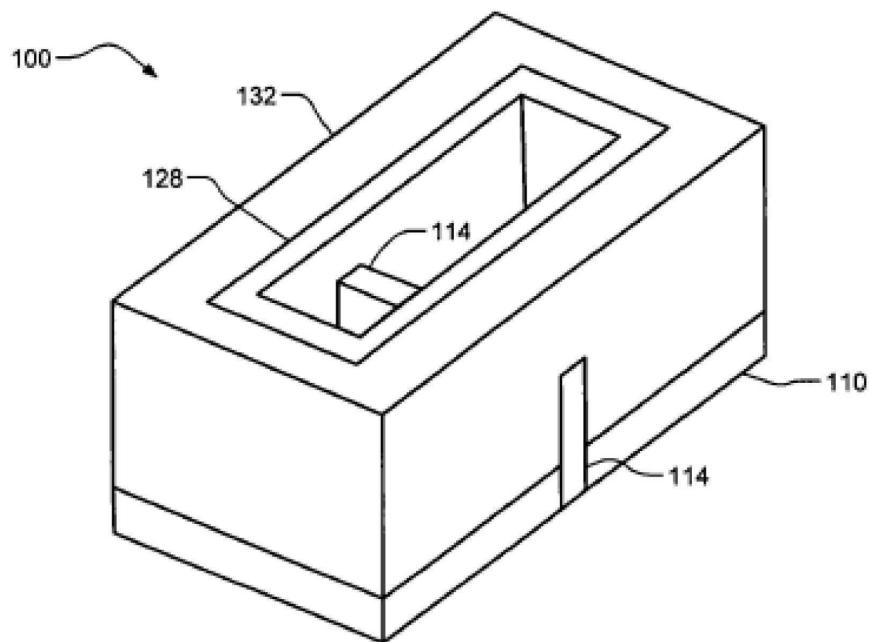

[0068] 도 4f를 이제 참조하면, RMG (138) 는 SnO<sub>2</sub> 및 실리콘 다이옥사이드 (SiO<sub>2</sub>) 에 대해 선택적으로 그리고 부분적으로 에칭된다. 보다 구체적으로, RMG (138) 는 RMG (138) 내에 리세스 (139) 를 생성하도록 희생적 SnO<sub>2</sub> 스페이서 (128) 및 ILD 층 (132) 의 상단 표면에 대해 하향 방향으로 부분적으로 그리고 선택적으로 에칭된다. RMG (138) 의 상단 표면 (141) 은 희생적 SnO<sub>2</sub> 스페이서 (128) 및 ILD 층 (132) 의 상단 표면들을 포함하는 평면 아래에 위치된다.

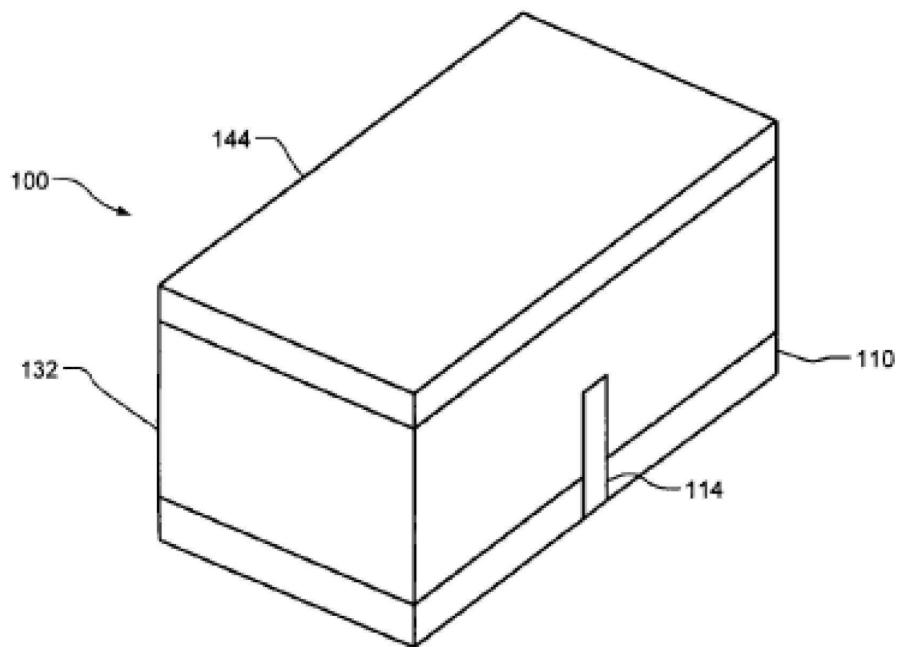

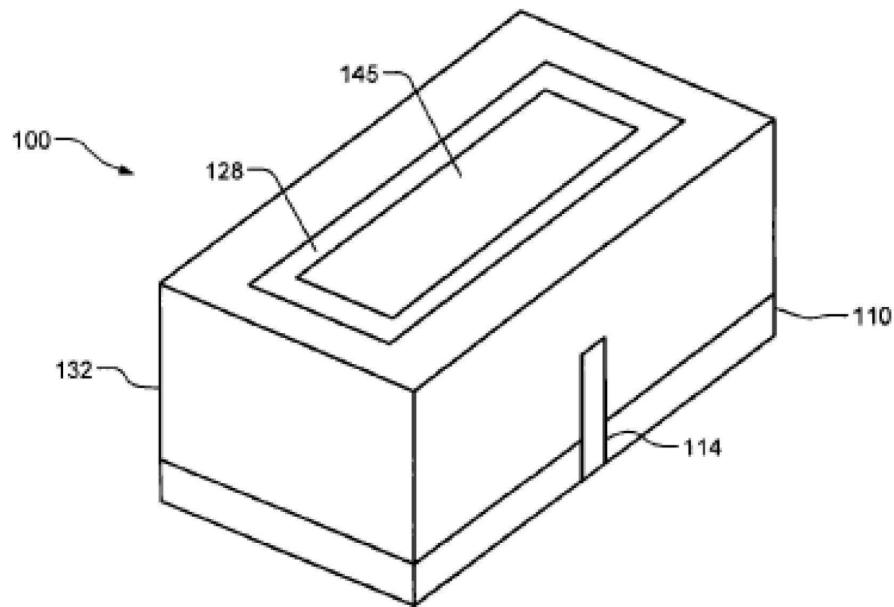

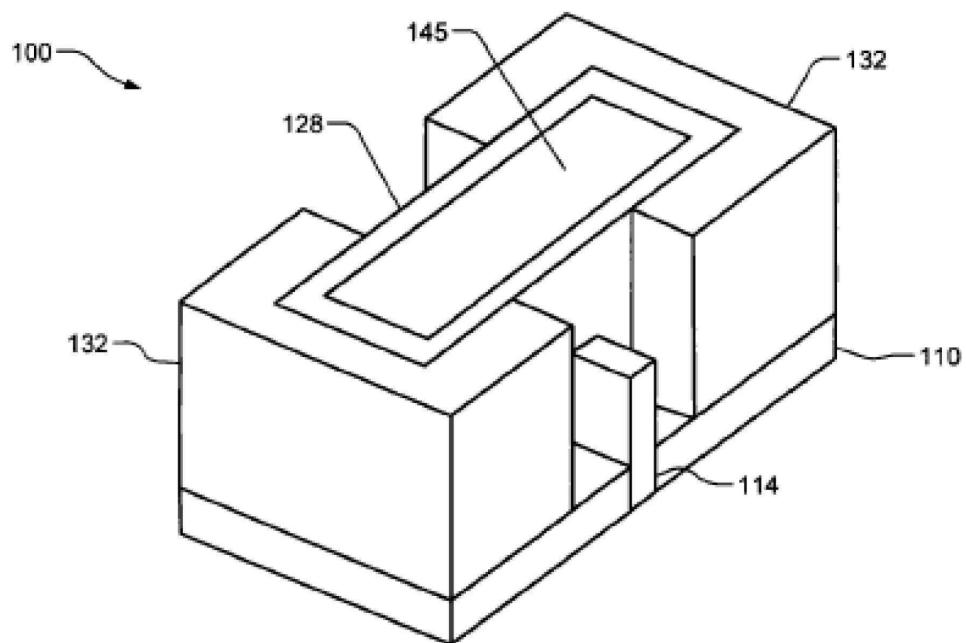

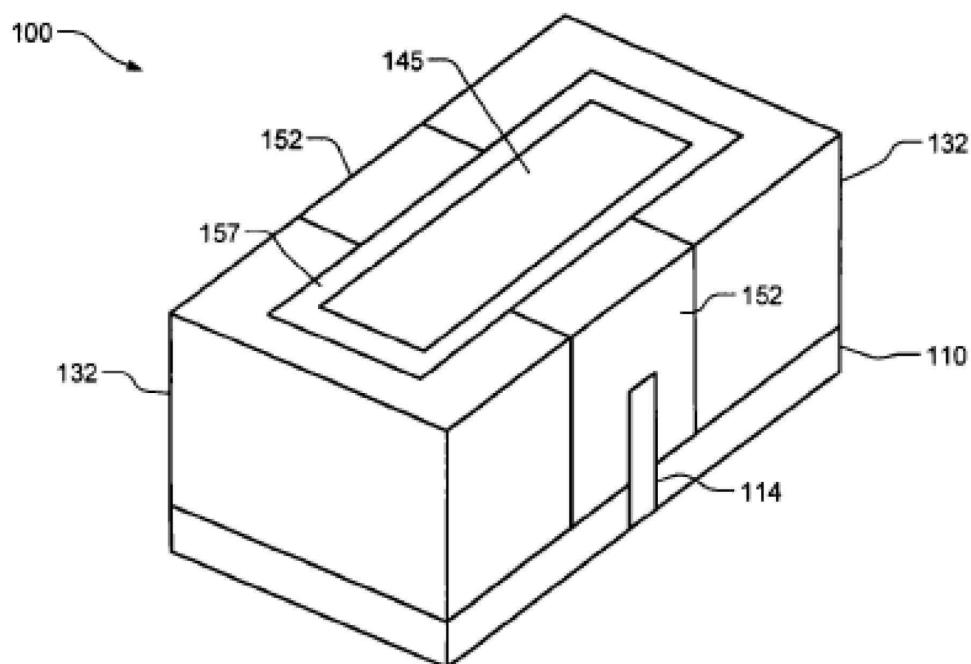

[0069] 이제 도 4g 및 도 4h를 참조하면, 게이트 캡핑 층 증착 및 게이트 캡핑 층 CMP이 각각 도시된다. 도 4g에서 게이트 캡핑 층 (144) 이 RMG (138) 내 리세스 내 그리고 기판 (100) 의 상단 표면 상에 증착된다. 일부 예들에서, 게이트 캡핑 층 (144) 은 실리콘 옥시카바이드 (SiOC) 또는 또 다른 적합한 재료로 이루어질 수도 있다. 일부 예들에서, 게이트 캡핑 층 (144) 은 2013년 12월 12일 공개되고, 전체가 참조로서 본 명세서에 인용된, 명칭이 "Remote Plasma Based Deposition of SiOC Class Films"인 공동으로 양도된 등의 미국 특허 공개번호 제 2013/0330935 호에 기술된 바와 같은 프로세스를 사용하여 증착된다. 일부 예들에서, 게이트 캡핑 층 (144) 은 상기 출원에 기술된 리모트 플라즈마 프로세스를 사용하여 증착된다. 도 4h에서, RMG (138) 에 대한 게이트 캡핑 층 (145) 을 생성하도록 게이트 캡핑 층 (144) 의 CMP가 수행된다. 일부 예들에서, 게이트 캡핑 층 (145) 의 상단 표면은 CMP 후에 희생적 SnO<sub>2</sub> 스페이서 (128) 및 ILD 층 (132) 의 상단 표면과 동일 평면 상이다.

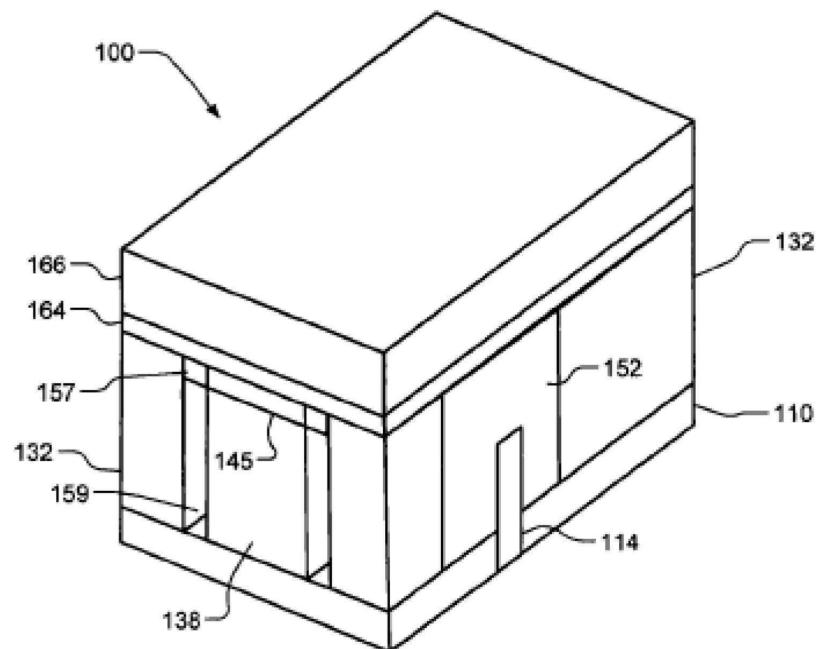

[0070] 이제 도 4i 및 도 4j를 참조하면, SAC (self-aligned contact) 영역 에칭, SAC 충진 및 희생적 스페이서 제거가 각각 도시된다. 도 4i에서, 복수의 핀들 (114) 을 노출하고 SAC 영역을 생성하기 위해, 복수의 핀들 (114) 의 마주보는 측면들을 둘러싸는 ILD 층 (132) 의 영역들이 마스킹되고 게이트 캡핑 층 및 희생적 SnO<sub>2</sub> 스페이서에 대해 선택적으로 ILD를 에칭하는 에칭을 사용하여 에칭된다.

[0071] 도 4j에서, SAC 영역은 SAC 재료 (152) 로 충진된다. 일부 예들에서, SAC 재료 (152) 는 금속 충들 (155) 또는 배리어 충들 (153) 및 배리어 충들 (153) 상에 증착된 금속 충들 (155) 을 포함한다. 일부 예들에서, 배리어 충들 (153) 은 티타늄 (Ti) 및 티타늄 나이트라이드 (TiN) 2층을 포함하고, 금속 충들 (155) 은 텉스텐 (W) 을 포함하지만, 다른 재료들, 예컨대 배리어에 대해 WCN<sub>x</sub> 및 금속 충에 대해 Co가 사용될 수 있다. 도 4k에서, 희생적 SnO<sub>2</sub> 스페이서 (128) 는 제거된다. 예를 들어, 희생적 SnO<sub>2</sub> 스페이서 (128) 의 에칭은 본 명세서에 기술된 수소 플라즈마 에칭 방법들을 사용하여 노출된 재료들에 대해 선택적으로, 수행될 수 있다. 예를 들어,

$\text{SnO}_2$  재료는  $\text{SiOC}$  층 (145) 과 ILD 층 (예를 들어, 도핑되거나 도핑되지 않은  $\text{SiO}_2$ ) (132) 사이에 놓일 수도 있고, 수소 플라즈마를 사용하여 이를 재료들에 대해 선택적으로 예칭될 수도 있다.

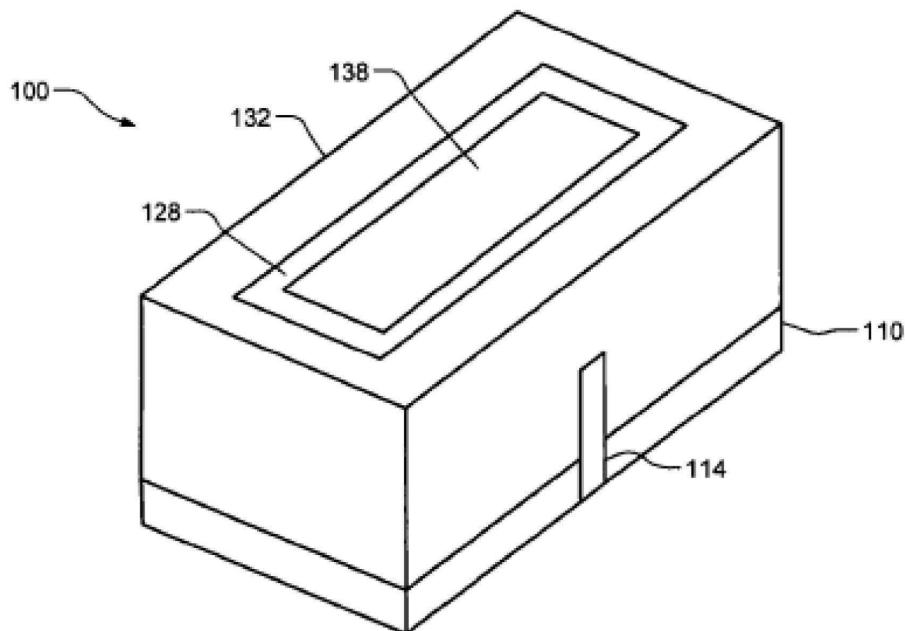

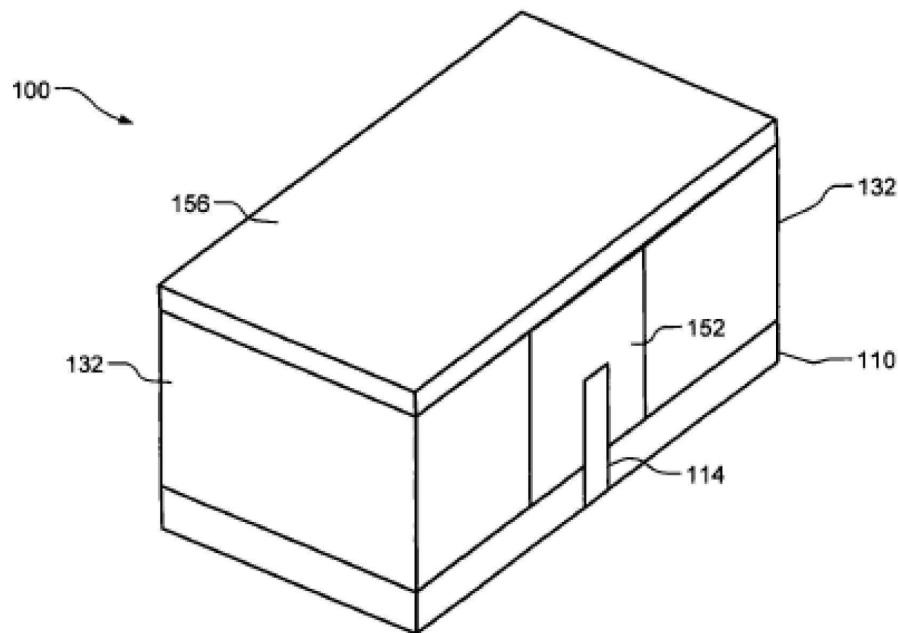

[0072] 이제 도 4I 내지 도 4n을 참조하면, 시일링 층이 기판 상에 증착되고, CMP가 에어 캡 스페이서를 생성하도록 수행된다. 도 4I에서, 시일링 층 (156) 이 기판 (100) 의 상단 표면 상에 증착된다. 증착 동안, 희생적  $\text{SnO}_2$  스페이서 (128) 이 제거된 후에 생성된 에어 캡 (159) 의 상부 부분이 시일링 층 (156) 에 의해 부분적으로 충진된다. 일부 예들에서, 시일링 층 (156) 은 ILD, 실리콘 다이옥사이드 ( $\text{SiO}_2$ ), 탄소 도핑된  $\text{SiO}_2$ , 또는 실리콘 옥시카바이드 ( $\text{SiOC}$ ) 로 이루어진다. 일부 예들에서, 시일링 층 (156) 이 PECVD (plasma enhanced chemical vapor deposition) 를 사용하여 증착되지만, 다른 증착 프로세스들이 사용될 수도 있다.

[0073] 일부 예들에서, 시일링 층 (156) 은, 참조로서 이전에 인용된 명칭이 "Remote Plasma Based Deposition of  $\text{SiOC}$  Class Films"인 공동으로 양도된 미국 특허 공개번호 제 2013/0330935 호에 기술된 바와 같이, PECVD를 사용하여 증착된  $\text{SiOC}$ 를 포함한다.

[0074] 도 4m에서, CMP는 에어 캡 시일링 (157) 을 생성하도록 기판 (100) 의 상단 표면 상에 위치된 시일링 층 (156) 의 일부를 제거하도록 사용된다. 일부 예들에서, 에어 캡 시일링 (157) 의 상단 표면은 CMP 후에 게이트 캡핑 층 (145) 및 ILD 층 (132) 의 상단 표면과 동일 평면 상이다. 도 4n에서, 복수의 펀들 (114) 로부터 이격되고 평행한 평면을 따라 취해진 기판의 단면이 도시된다. 에어 캡 (159) 이 에어 캡 시일링 (157) 아래에 위치된다.

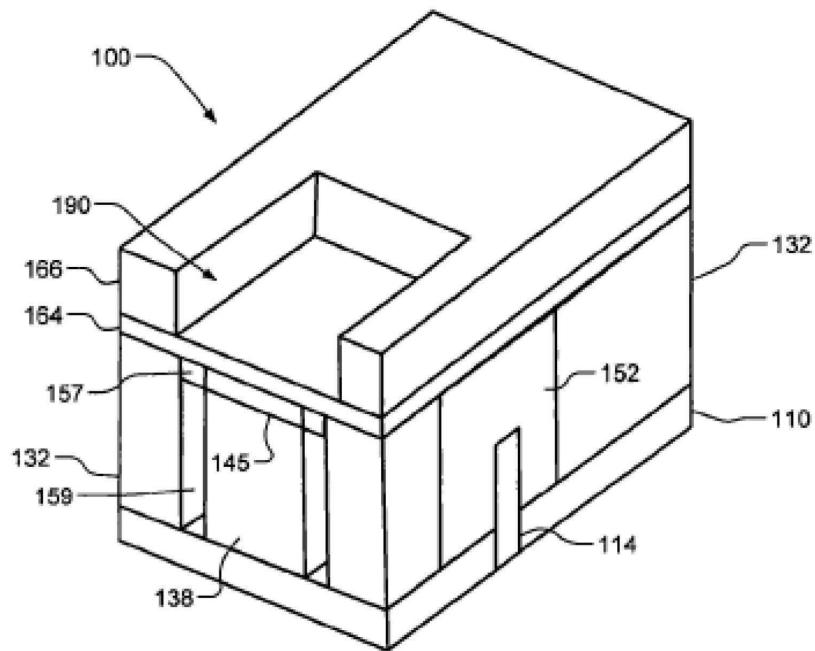

[0075] 이제 도 4o를 참조하면, 예칭 정지 층 (164) 이 기판 (100) 의 상단 표면 상에 증착된다. 일부 예들에서, 예칭 정지 층 (164) 은  $\text{SiOC}$ 를 포함하지만, 다른 재료들이 사용될 수도 있다. 일부 예들에서,  $\text{SiOC}$ 는 참조로서 이전에 인용된, 명칭이 "Remote Plasma Based Deposition of  $\text{SiOC}$  Class Films"인 공동으로 양도된 미국 특허 공개 번호 제 2013/0330935 호에 기술된 바와 같이, 증착된다. ILD 층 (166) 이 예칭 정지 층 (164) 상에 증착된다.

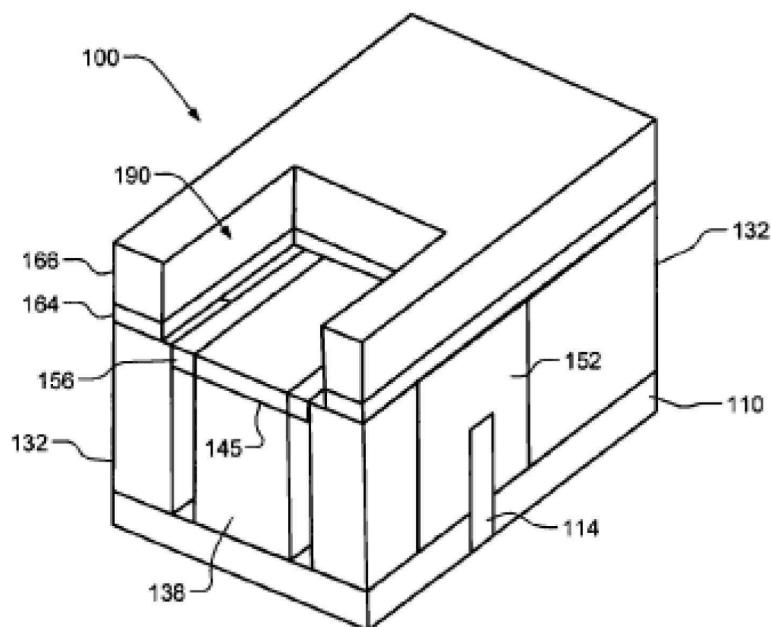

[0076] 이제 도 4p 내지 도 4t를 참조하면, 기판의 상이한 부분들을 개방하도록 다양한 상이한 예칭 단계들이 수행된다. 도 4p 및 도 4q에서, 다양한 예칭 단계들의 예가 도시된다. 도 4p에서, ILD 층 (166) 이 예칭 정지 층 (164) 의 부분 (190) 내에서 아래에 놓인 층들을 선택적으로 노출하도록 예칭된다. 도 4q에서, 예칭 정지 층 (164) 은 추가 프로세싱을 위해, 게이트 캡핑 층 (145), 에어 캡 시일링 (157), 금속 층들 (155) 및 ILD 층 (132) 의 부분들을 개방하도록 예칭된다.

[0077] 도 4r 및 도 4s에서, ILD 층 (166) 및 예칭 정지 층 (164) 이 기판 (100) 의 부분들 (192) 의 아래에 놓인 층들을 선택적으로 노출하도록 예칭된다. 도 4s에서, 추가 프로세싱을 위해 에어 캡 시일링 (157), 금속 층들 (155) 및 ILD 층 (132) 의 상이한 부분들이 개방된다.

[0078] 도 4t에서, ILD 층 (166) 이 기판 (100) 의 부분들 (198 및 200) 의 아래에 놓인 층들을 노출하도록 패터닝되고 예칭된다. 추가 프로세싱을 위해 에어 캡 시일링 (157), 금속 층들 (155), RMG (138) 및 ILD 층 (132) 의 부분들이 개방된다. 이해될 수 있는 바와 같이, 다양한 다른 하부층들이 추가 프로세싱을 위해 개방될 수도 있다.

#### [0080] 다른 실시예들

[0081] 다양한 다른 실시예들에서,  $\text{SnO}_2$  층들 및 수소 플라즈마 예칭이 다음의 애플리케이션들에서 사용될 수 있다.

[0082] 일부 실시예들에서,  $\text{SnO}_2$  층들은 일반적으로 사용된 폴리실리콘 더미 게이트들 대신 더미 게이트들로서 사용된다. 예를 들어, 도 4a 내지 도 4t를 참조하여 이전에 기술된, 프로세스 흐름은, 스페이서 (128) 가  $\text{SnO}_2$  를 포함하지 않는 재료로부터 이루어지는 동안 더미 게이트 (118) 가  $\text{SnO}_2$ 로 이루어지도록 이 실시예에서 수정된다. 예를 들어, 이 실시예에서 스페이서 (128) 는  $\text{SiN}$  스페이서일 수도 있다. 수정된 방법은 더미 게이트 제거를 위해  $\text{H}_2$  플라즈마 화학물질을 사용하여 더미 게이트 (118) 를 예칭하는 것을 수반한다. 일 구현예에서, 방법은 반도체 기판 상에  $\text{SnO}_2$  더미 게이트를 형성하는 단계;  $\text{SnO}_2$  더미 게이트의 존재시 반도체 기판을 프로세싱하는 단계, 프로세싱은 반도체 기판 상의 재료들의 증착 및/또는 예칭을 수반할 수도 있음; 더미 게이트 대신 리세스된 피쳐를 형성하기 위해  $\text{H}_2$ 를 포함하는 프로세스 가스로 형성된 플라즈마로  $\text{SnO}_2$  더미 게이트를 예칭하고 더미 게이트 대신 게이트를 형성하도록 형성된 리세스된 피쳐 내로 하이-k 유전체 재료를 증착하는 단계를 수반

한다. 일부 실시예들에서, 더미 게이트 제거 동안 수소 플라즈마 에칭은 적어도 약 50 %의 H<sub>2</sub>를 포함하는 프로세스 가스로 형성된 플라즈마를 사용하여 그리고 약 100 °C 미만의 온도에서의 에칭을 수행한다. 일부 실시예들에서, 에칭은 SiO<sub>2</sub>, SiC, SiN, SiOC, SiNO, SiCNO, 및 SiCN으로 구성된 그룹으로부터 선택된 하나 이상의 재료들에 대해 선택적으로 수행되고, 이들 재료들은 에칭 전에 기판 상에서 노출될 수도 있고 또는 에칭 동안 노출될 수도 있다. 더미 게이트에 대해 SnO<sub>2</sub> 그리고 더미 게이트 에칭을 위해 H<sub>2</sub> 플라즈마를 사용하는 것의 이점들은 SiO<sub>2</sub> 및 로우-k 스페이서에 대해 선택적인 SnO<sub>2</sub>의 용이한 제거, 및 고 내열성을 포함한다.

[0083] 다른 실시예들에서, SnO<sub>2</sub> 층들은 BEOL 애플리케이션들에서 고-레지스턴스 레지스터들로서 사용된다. 이는 폴리실리콘 BEOL에서 사용하지 않기 때문에 유용한 애플리케이션이다.

[0084] 다른 실시예들에서 SnO<sub>2</sub> 층들은 임플란트 스크린으로서 사용된다. 이 애플리케이션은 SnO<sub>2</sub> 증착에 사용한 저 증착 온도 및 수소 플라즈마 에칭에 의해 달성될 수 있는 매우 선택적인 제거를 필요로 한다. 유리하게, 수소 플라즈마 제거가 사용될 때 HF 딥핑 (dipping) 이 요구되지 않는다.

#### [0086] 장치

[0087] 본 명세서에 기술된 수소 플라즈마 에칭 방법들은 다양한 장치들에서 수행될 수 있다. 적합한 장치는 에칭 프로세스 챔버, 에칭 동안 기판을 제자리에 홀딩하도록 구성된 에칭 프로세스 챔버 내의 기판 홀더, 및 프로세스 가스로 플라즈마를 생성하기 위해 구성된 플라즈마 생성 메커니즘을 포함한다.

[0088] 적합한 장치들의 예들은, 특정한 실시예들에서, ALE (atomic layer etching) 동작들 및 ALD (atomic layer deposition) 동작들을 포함하여, 순환적 증착 및 활성화 프로세스들에 또한 적합할 수도 있는 ICP (inductively coupled plasma) 반응기들을 포함한다. 이러한 ICP 반응기들은 모든 목적들을 위해 그리고 전체가 본 명세서에 참조로서 인용된, 2016년 6월 7일 허여되고 명칭이 "Method for Forming a Mask by Etching Conformal Film on Patterned Ashable Hardmask"인 미국 특허 제 9,362,133 호에 또한 기술된다. ICP 반응기들이 또한 본 명세서에 상세히 기술되었지만, CCP (capacitively coupled plasma) 반응기들이 또한 사용될 수도 있다는 것이 이해되어야 한다.

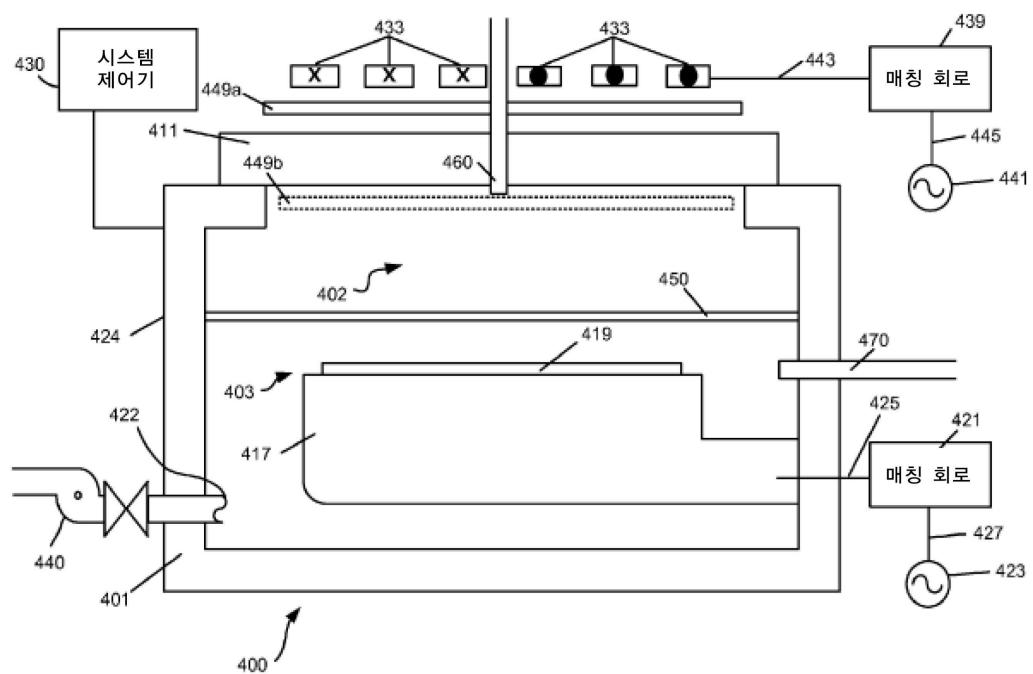

[0089] 도 5는 본 명세서에 기술된 수소 플라즈마 에칭을 구현하기에 적절한 유도 결합 통합된 플라즈마 에칭 및 증착 장치 (400)의 단면도를 개략적으로 도시하고, 이의 예는 CA, Fremont 소재의 Lam Research Corp.에 의해 생산된 Kiyo® 반응기이다. 유도 결합 플라즈마장치 (400)는 챔버 벽들 (401) 및 윈도우 (411)에 의해서 구조적으로 구획된 전체 프로세스 챔버 (424)를 포함한다. 챔버 벽들 (401)은 스테인레스 스틸 또는 알루미늄으로 제조될 수도 있다. 윈도우 (411)는 석영 또는 다른 유전체 재료로 제조될 수도 있다. 선택 가능한 내부 플라즈마 그리드 (450)는 상부 서브-챔버 (402) 및 하부 서브-챔버 (403)로 전체 프로세싱 챔버를 분할한다. 대부분의 실시예들에서, 플라즈마 그리드 (450)는 제거될 수도 있고, 따라서, 서브-챔버들 (402 및 703)로 이루어진 챔버 공간을 활용한다. 척 (417)은 하단 내측 표면 근방에서 하부 프로세싱 챔버 (403) 내에 위치된다. 척 (417)은 에칭 및 증착 프로세스들이 수행되는 반도체 웨이퍼 (419)를 수용 및 홀딩하도록 구성된다. 척 (417)은 웨이퍼 (419)가 존재하는 경우에 웨이퍼 (419)를 지지하는 정전 척일 수 있다. 일부 실시예들에서, 에지 링 (미도시)이 척 (417)을 둘러싸며 척 (417) 위에 존재할 경우에 웨이퍼 (419)의 상단 표면과 대략 동일 평면에 있는 상부 표면을 갖는다. 척 (417)은 또한 웨이퍼 (419)를 척킹 및 디척킹하기 위한 정전 전극들을 포함한다. 필터 및 DC 클램프 전력 공급부가 이 목적을 위해서 제공될 수도 있다. 척 (417)으로부터 웨이퍼 (419)를 리프팅 (lifting) 하기 위한 다른 제어 시스템들이 또한 제공될 수 있다. 척 (417)은 RF 전력 공급부 (423)를 사용하여 전기적으로 대전될 수 있다. RF 전력 공급부 (423)는 연결부 (427)를 통해 매칭 회로 (421)에 연결된다. 매칭 회로 (421)는 연결부 (425)를 통해 척 (417)에 연결된다. 이러한 방식으로, RF 전력 공급부 (423)는 척 (417)에 연결된다. 다양한 실시예들에서, 정전 척의 바이어스 전력은 약 50 Vb로 설정될 수도 있고 또는 개시된 실시예들에 따라 수행된 프로세스에 따라 상이한 바이어스 전력으로 설정될 수도 있다. 예를 들어, 바이어스 전력은 약 20 Vb 내지 약 100 Vb, 또는 약 30 Vb 내지 약 150 Vb일 수도 있다.

[0090] 플라즈마 생성을 위한 엘리먼트들은 윈도우 (411) 위에 위치된 코일 (433)을 포함한다. 일부 실시예들에서, 코일은 개시된 실시예들에 사용되지 않는다. 코일 (433)은 전기적으로 도전성 재료로 제조되고, 적어도 1 회의 완전한 턴 (turn)을 포함한다. 도 5에 도시된 코일 (433)의 예는 3 회의 턴들을 포함한다. 코일 (433)의 단면도들은 심볼들로 도시되고, "X"를 갖는 코일들은 페이지 내로 회전하여 연장하는 한편, "●"을 갖는 코일들은 페이지로부터 회전하여 연장한다. 플라즈마 생성을 위한 엘리먼트들은 또한 코일 (433)에 RF 전력을

공급하도록 구성된 RF 전력 공급부 (441)를 포함한다. 일반적으로, RF 전력 공급부 (441)는 연결부 (445)를 통해 매칭 회로 (439)에 연결된다. 매칭 회로 (439)는 연결부 (443)를 통해 코일 (433)에 연결된다. 이러한 방식으로, RF 전력 공급부 (441)는 코일 (433)에 연결된다. 선택가능한 Faraday 차폐부 (449a)는 코일 (433)과 윈도우 (411) 사이에 위치된다. Faraday 차폐부 (449a)는 코일 (433)에 대해 이격된 관계로 유지될 수도 있다. 일부 실시예들에서, Faraday 차폐부 (449a)는 윈도우 (411) 바로 위에 배치된다. 일부 실시예들에서, Faraday 차폐부 (449b)와 윈도우 (411) 사이에 있다. 일부 실시예들에서, Faraday 차폐부 (449b)는 코일 (433)에 대해 이격된 관계로 유지되지 않는다. 예를 들어, Faraday 차폐부 (449b)는 캡 없이 윈도우 (411) 바로 아래에 있을 수도 있다. 코일 (433), Faraday 차폐부 (449a), 및 윈도우 (411)는 각각 서로 실질적으로 평행하도록 구성된다. Faraday 차폐부 (449a)는 금속 또는 다른 종이 프로세스 챔버 (424)의 윈도우 (411) 상에 증착되는 것을 방지할 수도 있다.

[0091] 프로세스 가스 (예를 들어, H<sub>2</sub> 및 He, 등)는 상부 서브-챔버 (402) 내에 위치된 하나 이상의 주 가스 플로우 유입부들 (460)을 통해 그리고/또는 하나 이상의 측면 가스 플로우 유입부들 (470)을 통해 프로세스 챔버 내로 흐를 수도 있다. 유사하게, 명시적으로 도시되지 않지만, 프로세스 가스들을 용량 결합 플라즈마 프로세싱 챔버로 공급하도록 유사한 가스 플로우 유입부들이 사용될 수도 있다. 진공 펌프, 예를 들어, 1 또는 2 단계 기계적 드라이 펌프 및/또는 터보분자 펌프 (440)가 프로세스 챔버 (424)로부터 프로세스 가스들을 유출하도록 그리고 프로세스 챔버 (424) 내에서 압력을 유지하도록 사용될 수도 있다. 예를 들어, 진공 펌프가 퍼지 동작 동안 하부 서브-챔버 (403)를 배기하도록 사용될 수도 있다. 진공 펌프에 의해 제공된 진공 환경의 적용을 선택적으로 제어하도록 프로세스 챔버 (424)로 진공 펌프를 유체적으로 연결하도록 밸브-제어된 도관이 사용될 수도 있다. 이는 동작 중인 플라즈마 프로세싱 동안, 쓰로틀 밸브 (미도시) 또는 펜들럼 밸브 (미도시)와 같은 페루프 제어된 플로우 제한 디바이스를 채용함으로써 이루어질 수도 있다. 유사하게, 용량 결합 플라즈마 챔버로의 진공 펌프 및 밸브 제어된 유체 연결이 채용될 수도 있다.

[0092] 장치 (400)의 동작 동안, H<sub>2</sub>-함유 가스와 같은, 하나 이상의 프로세스 가스들이 가스 플로우 유입부들 (460 및/또는 470)을 통해 공급될 수도 있다. 특정한 실시예들에서, 프로세스 가스들은 주 가스 플로우 유입부 (460)를 통해서만, 또는 측면 가스 플로우 유입부 (470)를 통해서만 공급될 수도 있다. 일부 경우들에서, 도면에 도시된 가스 플로우 유입부들은 보다 복잡한 가스 플로우 유입부들, 예를 들어 하나 이상의 샤크헤드들로 대체될 수도 있다. Faraday 차폐부 (449a) 및/또는 선택가능한 그리드 (450)는 프로세스 챔버 (424)로의 프로세스 가스들의 전달을 허용하는 내부 채널들 및 홀들을 포함할 수도 있다. Faraday 차폐부 (449a) 및 선택가능한 그리드 (450) 중 하나 또는 양자는 프로세스 가스들의 전달을 위한 샤크헤드로서 역할을 할 수도 있다. 일부 실시예들에서, 액체 기화 및 전달 시스템은, 일단 액체 반응물질 또는 전구체가 기화되면, 기화된 반응물질 또는 전구체가 가스 플로우 유입부들 (460 및/또는 470)을 통해 프로세스 챔버 (424) 내로 도입되도록, 프로세스 챔버 (424)의 업스트림에 놓일 수도 있다.

[0093] RF 전류로 하여금 코일 (433)을 통해 흐르게 하도록 RF 전력 공급부 (441)로부터 코일 (433)로 RF 전력이 공급된다. 코일 (433)을 통한 RF 전류는 코일 (433)을 중심으로 전자기장을 생성한다. 전자기장은 상부 서브-챔버 (402) 내에 유도 전류를 생성한다. 웨이퍼 (419)와 다양한 생성된 이온들 및 라디칼들의 물리적 및 화학적 상호작용들은 웨이퍼 (419)의 피처들을 에칭하고 웨이퍼 (419) 상에 층들을 선택적으로 증착한다.

[0094] 상부 서브-챔버 (402) 및 하부 서브-챔버 (403)가 모두 있도록 플라즈마 그리드 (450)가 사용되면, 상부 서브-챔버 (402) 내에서 전자-이온 플라즈마를 생성하도록 유도 전류는 상부 서브-챔버 (402) 내에 존재하는 가스에 작용한다. 선택가능한 내부 플라즈마 그리드 (450)는 하부 서브-챔버 (403) 내 핫 (hot) 전자들의 양을 제한한다. 일부 실시예들에서, 장치 (400)는 하부 서브-챔버 (403) 내에 존재하는 플라즈마가 이온-이온 플라즈마 이도록 설계되고 동작된다.

[0095] 상부 전자-이온 플라즈마 및 하부 이온-이온 플라즈마 모두가 양이온 및 음이온을 함유할 수도 있지만, 이온-이온 플라즈마는 보다 큰 음이온 대 양이온 비를 가질 것이다. 휘발성 에칭 및/또는 증착 부산물들이 하부 서브-챔버 (403)으로부터 포트 (422)를 통해 제거될 수도 있다. 예를 들어, H<sub>2</sub> 플라즈마를 사용한 SnO<sub>2</sub>의 에칭 동안 생성된 SnH<sub>4</sub>는 퍼지 및/또는 배기 동안 포트 (422)를 통해 제거될 수 있다. 본 명세서에 개시된 척 (417)은 약 10 °C 내지 약 250 °C의 범위의 상승된 온도들에서 동작될 수도 있다. 온도는 프로세스 동작 및 특정한 레시피에 따를 것이다. 일부 실시예들에서 장치는 약 100 °C 미만의 온도에서 에칭을 수행하도록 제어된다.

[0096] 장치 (400)는 클린 품 또는 제조 설비 내에 설치될 때 설비들 (미도시)에 커플링될 수도 있다. 설비들은 프

로세싱 가스들, 진공, 온도 제어, 및 환경 입자 제어를 제공하는 플럼빙을 포함한다. 이들 설비들은 타깃 제조 설비 내에 설치될 때 장치 (400)에 커플링된다. 부가적으로, 장치 (400)는 로보틱스들로 하여금 통상적인 자동화를 사용하여 반도체 웨이퍼들을 장치 (400) 내외로 이송하게 하는 이송 챔버에 커플링될 수도 있다.

[0097] 일부 실시예들에서, (하나 이상의 물리적 또는 논리적 제어기들을 포함할 수도 있는) 시스템 제어기 (430)는 프로세스 챔버 (424)의 동작들 중 일부 또는 전부를 제어한다. 시스템 제어기 (430)는 하나 이상의 메모리 디바이스들 및 하나 이상의 프로세서들을 포함할 수도 있다. 일부 실시예들에서, 장치 (400)는 프로세스 가스들의 플로우 레이트들을 제어하기 위한 스위칭 시스템을 포함한다. 일부 실시예들에서, 제어기는 본 명세서에 제공된 임의의 방법들의 단계들을 유발하는 프로그램 인스트럭션들을 포함한다.

[0098] 일부 구현예들에서, 시스템 제어기 (430)는 상술한 예들의 일부일 수도 있는 시스템의 일부일 수 있다. 이러한 시스템들은, 프로세싱 툴 또는 툴들, 챔버 또는 챔버들, 프로세싱용 플랫폼 또는 플랫폼들, 및/또는 특정 프로세싱 컴포넌트들 (웨이퍼 페데스탈, 가스 플로우 시스템, 등)을 포함하는, 반도체 프로세싱 장비를 포함할 수 있다. 이들 시스템들은 반도체 웨이퍼 또는 기판의 프로세싱 이전에, 프로세싱 동안에 그리고 프로세싱 이후에 그들의 동작을 제어하기 위한 전자장치에 통합될 수도 있다. 전자장치들은 시스템 또는 시스템들의 다양한 컴포넌트들 또는 하위부품들을 제어할 수도 있는 "시스템 제어기 (430)"에 통합될 수도 있다. 시스템 제어기는, 시스템의 프로세싱 파라미터들 및/또는 타입에 따라서, 프로세싱 가스들의 전달, 온도 설정사항들 (예를 들어, 가열 및/또는 냉각), 압력 설정사항들, 진공 설정사항들, 전력 설정사항들, 무선 주파수 (RF) 생성기 설정사항들, RF 매칭 회로 설정사항들, 주파수 설정사항들, 플로우 레이트 설정사항들, 유체 전달 설정사항들, 위치 및 동작 설정사항들, 툴들 및 다른 이송 툴들 및/또는 특정 시스템과 연결되거나 인터페이싱된 로드록들 내외로의 웨이퍼 이송들을 포함하는, 본 명세서에 개시된 프로세스들 중 임의의 프로세스들을 제어하도록 프로그램될 수도 있다.

[0099] 일반적으로 말하면, 시스템 제어기 (430)는 인스트럭션들을 수신하고, 인스트럭션들을 발행하고, 동작을 제어하고, 세정 동작들을 인에이블하고, 엔드포인트 측정들을 인에이블하는 등을 하는 다양한 집적 회로들, 로직, 메모리, 및/또는 소프트웨어를 갖는 전자장치로서 규정될 수도 있다. 집적 회로들은 프로그램 인스트럭션들을 저장하는 펌웨어의 형태의 칩들, 디지털 신호 프로세서들 (DSP), ASIC (application specific integrated circuit)으로서 규정되는 칩들 및/또는 프로그램 인스트럭션들 (예를 들어, 소프트웨어)을 실행하는 하나 이상의 마이크로프로세서들, 또는 마이크로제어기들을 포함할 수도 있다. 프로그램 인스트럭션들은 반도체 웨이퍼 상에서 또는 반도체 웨이퍼에 대한 특정 프로세스를 실행하기 위한 동작 파라미터들을 규정하는, 다양한 개별 설정사항들 (또는 프로그램 파일들)의 형태로 제어기로 또는 시스템으로 전달되는 인스트럭션들일 수도 있다. 일부 실시예들에서, 동작 파라미터들은 하나 이상의 층들, 재료들, 금속들, 산화물들, 실리콘, 이산화 실리콘, 표면들, 회로들, 및/또는 웨이퍼의 다이들의 제조 또는 제거 동안에 하나 이상의 프로세싱 단계들을 달성하도록 프로세스 엔지니어에 의해서 규정된 레시피의 일부일 수도 있다.

[0100] 시스템 제어기 (430)는, 일부 구현예들에서, 시스템에 통합되거나, 시스템에 커플링되거나, 이와 달리 시스템에 네트워킹되거나, 또는 이들의 조합으로 될 수 있는 컴퓨터에 커플링되거나 이의 일부일 수도 있다. 예를 들어, 제어기는 웨이퍼 프로세싱의 원격 액세스를 가능하게 할 수 있는 공장 (fab) 호스트 컴퓨터 시스템의 전부 또는 일부이거나 "클라우드" 내에 있을 수도 있다. 컴퓨터는 제조 동작들의 현 진행을 모니터링하고, 과거 제조 동작들의 이력을 조사하고, 복수의 제조 동작들로부터 경향들 또는 성능 계측치들을 조사하고, 현 프로세싱의 파라미터들을 변경하고, 현 프로세싱을 따르는 프로세싱 단계들을 설정하고, 또는 새로운 프로세스를 시작하기 위해서 시스템으로의 원격 액세스를 인에이블할 수도 있다. 일부 예들에서, 원격 컴퓨터 (예를 들어, 서버)는 로컬 네트워크 또는 인터넷을 포함할 수도 있는 네트워크를 통해서 프로세스 레시피들을 시스템에 제공할 수 있다. 원격 컴퓨터는 차후에 원격 컴퓨터로부터 시스템으로 전달될 파라미터들 및/또는 설정사항들의 입력 또는 프로그래밍을 인에이블하는 사용자 인터페이스를 포함할 수도 있다. 일부 예들에서, 시스템 제어기 (430)는 하나 이상의 동작들 동안에 수행될 프로세스 단계들 각각에 대한 파라미터들을 특정한, 데이터의 형태의 인스트럭션들을 수신한다. 이 파라미터들은 제어기가 제어하거나 인터페이싱하도록 구성된 툴의 타입 및 수행될 프로세스의 타입에 특정적일 수도 있다는 것이 이해되어야 한다. 따라서, 상술한 바와 같이, 시스템 제어기 (430)는 예를 들어 서로 네트워킹되어서 함께 공통 목적을 위해서, 예를 들어 본 명세서에 기술된 프로세스들 및 제어들을 위해서 협력하는 하나 이상의 개별 제어기들을 포함함으로써 분산될 수도 있다. 이러한 목적을 위한 분산형 제어기의 예는 챔버 상의 프로세스를 제어하도록 조합되는, (예를 들어, 플랫폼 레벨에서 또는 원격 컴퓨터의 일부로서) 원격으로 위치한 하나 이상의 집적 회로들과 통신하는 챔버 상의 하나 이상의 집적 회로들일 수 있다.

- [0101] 비한정적으로, 예시적인 시스템들은 플라즈마 에칭 챔버 또는 모듈, 증착 챔버 또는 모듈, 스피-린스 챔버 또는 모듈, 금속 도금 챔버 또는 모듈, 세정 챔버 또는 모듈, 베벨 에지 에칭 챔버 또는 모듈, PVD (physical vapor deposition) 챔버 또는 모듈, CVD (chemical vapor deposition) 챔버 또는 모듈, ALD (atomic layer deposition) 챔버 또는 모듈, ALE (atomic layer etching) 챔버 또는 모듈, 이온 주입 챔버 또는 모듈, 트랙 (track) 챔버 또는 모듈, 및 반도체 웨이퍼들의 제조 및/또는 제작 시에 사용되거나 연관될 수도 있는 임의의 다른 반도체 프로세싱 시스템들을 포함할 수도 있다.

- [0102] 상술한 바와 같이, 툴에 의해서 수행될 프로세스 단계 또는 단계들에 따라서, 제어기는, 반도체 제작 공장 내의 툴 위치들 및/또는 로드 포트들로부터/로 웨이퍼들의 컨테이너들을 이동시키는 재료 이송 시에 사용되는, 다른 툴 회로들 또는 모듈들, 다른 툴 컴포넌트들, 클러스터 툴들, 다른 툴 인터페이스들, 인접 툴들, 이웃하는 툴들, 공장 도처에 위치한 툴들, 메인 컴퓨터, 또 다른 제어기 또는 툴들 중 하나 이상과 통신할 수도 있다.

- [0103] 도 6은 VTM (vacuum transfer module) (538) 과 인터페이싱하는 다양한 모듈들을 갖는 반도체 프로세스 클러스터 아키텍처를 도시한다. 복수의 저장 설비들 사이에서 웨이퍼들을 "이송"하기 위한 이송 모듈들 및 프로세스 모듈들의 장치는 "클러스터 툴 아키텍처" 시스템으로 지칭될 수도 있다. 또한 로드록 또는 이송 모듈로 공지된 에어록 (530) 은, VTM (538) 과 인터페이싱하고, 결과적으로, 다양한 제조 프로세스들을 수행하도록 개별적으로 최적화될 수도 있는 4 개의 프로세싱 모듈들 (520a 내지 520d) 과 인터페이싱한다. 예로서, 프로세싱 모듈들 (520a 내지 520d) 은 기판 에칭, 증착, 이온 주입, 웨이퍼 세정, 스퍼터링, 및/또는 다른 반도체 프로세스들을 수행하도록 구현될 수도 있다. 일부 실시예들에서, SnO<sub>2</sub> 증착 및 SnO<sub>2</sub> 에칭이 동일한 모듈에서 수행된다. 일부 실시예들에서, SnO<sub>2</sub> 증착 및 SnO<sub>2</sub> 에칭은 동일한 툴의 상이한 모듈들에서 수행된다. 하나 이상의 기판 에칭 프로세싱 모듈들 (520a 내지 520d 중 어느 하나) 이 본 명세서에 개시된 바와 같이, 예를 들어, 컨포멀한 막들을 증착하기 위해, SnO<sub>2</sub>를 선택적으로 에칭하기 위해, 에어 캡들을 형성하기 위해, 그리고 개시된 실시예들에 따른 다른 적합한 기능들을 위해 구현될 수도 있다. 에어록 (530) 및 프로세싱 모듈들 (520a 내지 520d) 은 "스테이션들"로 지칭될 수도 있다. 스테이션 각각은 스테이션을 VTM (538) 에 인터페이싱하는 패싯 (536) 을 갖는다. 패싯 각각 내부에서, 센서들 (1 내지 18) 은 웨이퍼가 각각의 스테이션들 사이에서 이동할 때 웨이퍼 (526) 의 통과를 검출하도록 사용된다.

- [0104] 로봇 (522) 이 스테이션들 사이에서 웨이퍼 (526) 를 이송한다. 일 실시예에서, 로봇 (522) 은 하나의 암을 갖고, 또 다른 실시예에서, 로봇 (522) 은 2 개의 암들을 갖고, 암 각각은 이송을 위해 웨이퍼 (526) 와 같은 웨이퍼들을 피킹하기 위해 엔드 이펙터 (524) 를 갖는다. ATM (atmospheric transfer module) (540) 의 프론트 엔드 로봇 (532) 이 LPM (Load Port Module) (542) 의 FOUP (Front Opening Unified Pod) (534) 또는 카세트로부터 에어록 (530) 으로 웨이퍼들 (526) 을 이송하도록 사용된다. 프로세스 모듈들 (520a 내지 520d) 내부의 모듈 중심 (528) 은 웨이퍼 (526) 를 배치하기 위한 일 위치이다. ATM (540) 내 열라이너 (544) 가 웨이퍼들을 정렬하기 위해 사용된다.

- [0105] 예시적인 프로세싱 방법에서, 웨이퍼는 LPM (542) 내 FOUP들 (534) 중 하나에 배치된다. 프론트엔드 로봇 (532) 은 FOUP (534) 로부터 웨이퍼 (526) 로 하여금 에칭되거나 프로세싱되기 전에 적절히 중심에 위치되게 하는, 열라이너 (544) 로 웨이퍼를 이송한다. 정렬된 후, 웨이퍼 (526) 는 프론트엔드 로봇 (532) 에 의해 에어록 (530) 내로 이동된다. 에어록 (530) 이 ATM (540) 와 VTM (538) 사이의 분위기를 매칭하는 능력을 갖기 때문에, 웨이퍼 (526) 는 손상되지 않고 두 압력 분위기들 사이에서 이동할 수 있다. 에어록 (530) 으로부터, 웨이퍼 (526) 는 로봇 (522) 에 의해 VTM (538) 을 통해 프로세싱 모듈들 (520a 내지 520d) 중 하나 내로 이동된다. 이 웨이퍼 이동을 달성하기 위해, 로봇 (522) 은 암들 각각의 엔드 이펙터들 (524) 을 사용한다. 일단 웨이퍼 (526) 가 프로세싱되면, 웨이퍼는 로봇 (522) 에 의해 프로세싱 모듈들 (520a 내지 520d) 로부터 에어록 (530) 으로 이동된다. 여기서부터, 웨이퍼 (526) 는 프론트엔드 로봇 (532) 에 의해 FOUP들 (534) 중 하나 또는 열라이너 (544) 로 이동될 수도 있다.

- [0106] 웨이퍼 이동을 제어하는 컴퓨터는 클러스터 아키텍처에 국부적일 수 있고 또는 제작 현장의 클러스터 아키텍처 외부에 위치될 수 있고, 또는 리모트 위치에 있고 네트워크를 통해 클러스터 아키텍처에 연결될 수 있다는 것을 주의해야 한다. 도 5를 참조하여 기술된 바와 같은 제어기는 도 6의 툴을 사용하여 구현될 수도 있다. 본 발명에 따른 프로세스 동작들을 제어하기 위한 인스트럭션들을 포함하는 머신 판독가능한 매체는 시스템 제어기에 커플링될 수도 있다.

- [0107] 일부 실시예들에서, 에칭 동안 반도체 기판을 홀딩하기 위해 구성된 기판 홀더를 갖는 프로세스 챔버; 프로세스

가스에 플라즈마를 생성하기 위해 구성된 플라즈마 생성기; 및 제어기를 포함하는 장치가 제공된다. 제어기는 임의의 본 명세서에 기술된 방법들을 구현하기 위한 프로그램 인스트럭션들을 포함한다. 일 실시예에서, 제어기는 약 100 °C 미만의 온도에서 반도체 기판 상의 SnO<sub>2</sub> 층의 에칭을 유발하기 위한 프로그램 인스트럭션들을 포함하고, 에칭을 유발하는 것은 적어도 약 50 %의 H<sub>2</sub>를 포함하는 프로세스 가스로 형성된 플라즈마에 반도체 기판의 노출을 유발하는 것을 포함한다.

[0108] 또 다른 양태에서, 약 100 °C 미만의 온도에서 반도체 기판 상의 SnO<sub>2</sub> 층의 에칭을 유발하기 위한 코드를 포함하는 비일시적인 컴퓨터 머신 판독가능 매체가 제공되고, 에칭을 유발하는 것은 적어도 약 50 %의 H<sub>2</sub>를 포함하는 프로세스 가스로 형성된 플라즈마에 반도체 기판의 노출을 유발하는 것을 포함한다.

[0109] 또 다른 양태에서, 반도체 기판 상에 에어 갭을 형성하기 위한 시스템이 제공된다. 시스템은 하나 이상의 증착 프로세스 챔버들; 하나 이상의 에칭 프로세스 챔버들; 및 제어기를 포함한다. 제어기는 본 명세서에 기술된 임의의 에어 갭 형성 방법들을 구현하기 위한 프로그램 인스트럭션들을 포함한다. 예를 들어, 제어기는 (i) 제 1 재료의 노출된 층, 제 2 재료의 노출된 층, 및 제 1 재료의 층과 제 2 재료의 층 사이에 위치된 SnO<sub>2</sub>의 노출된 층을 갖는 반도체 기판 상에서, 수소 플라즈마 에칭 화학물질을 사용하여 제 1 재료 및 제 2 재료 모두에 대하여 노출된 SnO<sub>2</sub>를 선택적으로 에칭하여, 제 1 재료와 제 2 재료 사이에 리세스된 피처를 형성하는 단계; 및 (ii) 리세스된 피처를 완전히 충진하지 않고 리세스된 피처 위에 제 3 재료를 증착하여, 제 1 재료의 층과 제 2 재료의 층 사이에 에어 갭을 형성하는 단계를 유발하는 프로그램 인스트럭션들을 포함할 수도 있다.

[0110] 또 다른 양태에서, 시스템은 본 명세서에 기술된 임의의 장치들 및 시스템들 및 스텝퍼를 포함한다.

[0111] 또 다른 양태에서, (i) 제 1 재료의 노출된 층, 제 2 재료의 노출된 층, 및 제 1 재료의 층과 제 2 재료의 층 사이에 위치된 SnO<sub>2</sub>의 노출된 층을 갖는 반도체 기판 상에서, 수소 플라즈마 에칭 화학물질을 사용하여 제 1 재료 및 제 2 재료 모두에 대하여 노출된 SnO<sub>2</sub>를 선택적으로 에칭하여, 제 1 재료와 제 2 재료 사이에 리세스된 피처를 형성하기 위한 코드; 및 (ii) 리세스된 피처를 완전히 충진하지 않고 리세스된 피처 위에 제 3 재료를 증착하여, 제 1 재료의 층과 제 2 재료의 층 사이에 에어 갭을 형성하기 위한 코드를 포함하는 비일시적인 컴퓨터 머신 판독가능 매체가 제공된다.

### [0113] 다른 구현예들

[0114] 본 명세서에 기술된 장치 및 프로세스들은, 예를 들어, 반도체 디바이스들, 디스플레이들, LEDs, 광전 패널들 등의 제조 또는 제작을 위해, 리소그래피 패터닝 툴들 또는 프로세스들과 함께 사용될 수도 있다. 통상적으로, 반드시 그런 것은 아니지만, 이러한 장치 및 프로세스들은 공통 제조 설비 내에서 함께 이용되거나 수행될 것이다. 막의 리소그래픽 패터닝은 통상적으로 단계들 각각이 다수의 가능한 툴들을 사용하여 인레이블되는, 이하의 단계들: (1) 스핀-온 (spin-on) 툴 또는 스프레이-온 (spray-on) 툴을 사용하여 워크피스, 즉, 기판 상에 포토레지스트를 도포하는 단계; (2) 핫 플레이트 또는 노 또는 UV 경화 툴을 사용하여 포토레지스트를 경화하는 단계; (3) 웨이퍼 스텝퍼와 같은 툴을 사용하여 가시광선 또는 UV 또는 x-선 광에 포토레지스트를 노출시키는 단계; (4) 습식 벤치와 같은 툴을 사용하여 레지스트를 선택적으로 제거하여 레지스트를 패터닝하도록 레지스트를 현상하는 단계; (5) 건식 또는 플라즈마 보조 에칭 툴을 사용함으로써 그 아래에 놓인 막 또는 워크피스 내로 레지스트 패턴을 전사하는 단계; 및 (6) RF 또는 마이크로파 플라즈마 레지스트 스트립퍼와 같은 툴을 사용하여 레지스트를 제거하는 단계의 일부 또는 전부를 포함한다.

## 도면

### 도면1

## 도면2

## 도면3a

도면3b

도면3c

도면3d

도면3e

도면3f

도면3g

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f

도면4g

도면4h

도면4i

도면4j

도면4k

도면4*l*

도면4*m*

도면4n

도면4o

도면4p

도면4q

도면4r

도면4s

도면4t

도면5

## 도면6