(19) Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 10 2004 055 452 B4 2008.05.29

(12)

## Patentschrift

(21) Aktenzeichen: **10 2004 055 452.8**

(22) Anmeldetag: 17.11.2004

(43) Offenlegungstag: **18.08.2005**

(45) Veröffentlichungstag

der Patenterteilung: **29.05.2008**

(51) Int Cl.<sup>8</sup>: **G05F 3/24** (2006.01)

**H03K 19/0185** (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

---

(30) Unionspriorität:

(73) Patentinhaber:

(74) Vertreter:

**PRÜFER & PARTNER GbR. 81479 München**

(72) Erfinder:

**Makishima, Hitoshi, Tokio/Tokyo, JP**

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

gezogene Brücke

EP 05 61 469 A2

EP 02 94 882 A2

JP 2003-0 32 102 AA

JP 2002-0 26 714 AA

JP 2001-1 47 243 AA

JP 2001-1 47 243 A

JP 05-3 16 755 AA

JP 03-1 06 115 AA

(54) Bezeichnung: **Ausgangsschaltung**

(57) Hauptanspruch: Ausgangsschaltung mit einer ersten Stromspiegelschaltung (M1) mit einem ersten und einem zweiten Strompfad (Q13, Q14), die beide mit einem Potentialpunkt auf der Seite eines hohen Potentials (VB) verbunden sind, einem ersten PMOS-Transistor (Q15) mit einem Drain, einem Gate, einer Source und einem Backgate, wobei die Source über den zweiten Strompfad der ersten Stromspiegelschaltung mit dem Potentialpunkt auf der Seite des hohen Potentials verbunden ist und das Backgate mit dem Potentialpunkt auf der Seite des hohen Potentials verbunden ist, einem ersten Gatewiderstand (R4; R41), der mit dem Gate des ersten PMOS-Transistors verbunden ist, einem ersten NMOS-Transistor (Q12; Q121; Q6) mit einer Source, einem Drain und einem Gate, wobei die Source verbunden ist mit einem mittleren Potentialpunkt (VS) zum Zuführen eines Potentials zwischen dem Potentialpunkt auf der Seite des hohen Potentials (VB) und dem Potentialpunkt auf der Seite des niedrigen Potentials (GND), der Drain über den ersten Gatewiderstand...

**Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Ausgangsschaltung, die z.B. für eine Technik zum Verschieben von Signalpegeln verwendet werden kann.

**[0002]** Eine Schaltung zum Verschieben von Signalpegeln, im allgemeinen als Pegelschiebeschaltung oder inverse Pegelschiebeschaltung bezeichnet, wird in den JP 05316755 AA, JP 2003032102 AA, JP 2002026714 AA und JP 2001147243 AA beschrieben. Insbesondere führen die JP 05316755 AA und JP 2003032102 AA eine Technik ein, die eine Spiegelschaltung verwendet.

**[0003]** JP 03106115 AA offenbart eine Treiberschaltung, bei der ein erster n-Kanal-MOSFET zwischen einen mit einer Spannungsversorgung verbundenen Widerstand und einen Drain eines zweiten n-Kanal-MOSFET geschaltet ist, der mit einer Referenzstromquelle, die einen dritten n-Kanal-MOSFET enthält, einen Stromspiegel bildet. Die durch den zweiten und dritten n-Kanal-MOSFET fließenden Ströme verhalten sich zueinander wie die Flächen der entsprechenden Transistoren. Durch den zweiten n-Kanal-MOSFET fließt jedoch nur dann ein Strom, wenn der erste n-Kanal-MOSFET eingeschaltet ist, und dieser Strom bewirkt einen Spannungsabfall an dem Widerstand. Dadurch wird eine Pegelschiebeschaltung hoher Geschwindigkeit verwirklicht.

**[0004]** EP 0 294 882 A2 offenbart eine Hochspannungshalbleitervorrichtung, die gemeinsam mit Niedrigspannungshalbleitervorrichtungen auf einem leitenden Substrat integriert ist. Das Substrat bildet eine Elektrode der Hochspannungshalbleitervorrichtung und ist im Betrieb mit einem Hochspannungsanschluss einer Leistungsversorgung verbunden. Die Niedrigspannungshalbleitervorrichtungen empfangen eine geregelte Versorgungsspannung, die mit Bezug auf die Hochspannungsversorgungsspannung geregelt ist und nicht mit Bezug auf Erde. Das verringert die Notwendigkeit, die Niedrigspannungshalbleitervorrichtungen gegenüber dem Substrat zu isolieren.

**[0005]** Die Aufgabe der vorliegenden Erfindung besteht darin, eine Technik zum Weglassen oder Verrinern der Anzahl von Schaltelementen hoher Durchbruchsspannung bereitzustellen, die in einem Teil einer Spiegelschaltung verwendet werden, um dadurch den Schaltungsaufbau zu vereinfachen.

**[0006]** Die Aufgabe wird gelöst durch eine Ausgangsschaltung gemäß Anspruch 1. Weiterbildungen der Erfindung sind jeweils in den Unteransprüchen gekennzeichnet.

**[0007]** Durch Zuführen von Strom zu dem ersten

Gatewiderstand wird an das Gate des ersten PMOS-Transistors eine Vorspannung angelegt. Weiterhin arbeitet die erste Stromspiegelschaltung so, dass sie der Source des ersten PMOS-Transistors einen Strom zuführt, der dem durch den ersten Gatewiderstand fließenden Strom entspricht.

**[0008]** Daher wird ein Strom, der dem durch den ersten Gatewiderstand fließenden Strom entspricht, dem Ausgangswiderstand zugeführt, der als Reaktion auf einem mit dem zugeführten Strom zusammenhängenden Spannungsabfall eine Spannung ausgibt.

**[0009]** Weiterhin kann die beschriebene Funktion auch unter Verwendungsbedingungen erzielt werden, bei denen die jeweiligen Spannungen an dem ersten Gatewiderstand beträchtlich höher sind als das Potential auf der Seite des niedrigen Potentials, solange nur der erste PMOS-Transistor eine hohe Durchbruchsspannung hat, ohne die Spannungsfestigkeit der ersten Stromspiegelschaltung zu erhöhen.

**[0010]** Weitere Merkmale und Zweckmäßigkeiten der Erfindung ergeben sich aus der Beschreibung von Ausführungsbeispielen anhand der beigefügten Zeichnungen.

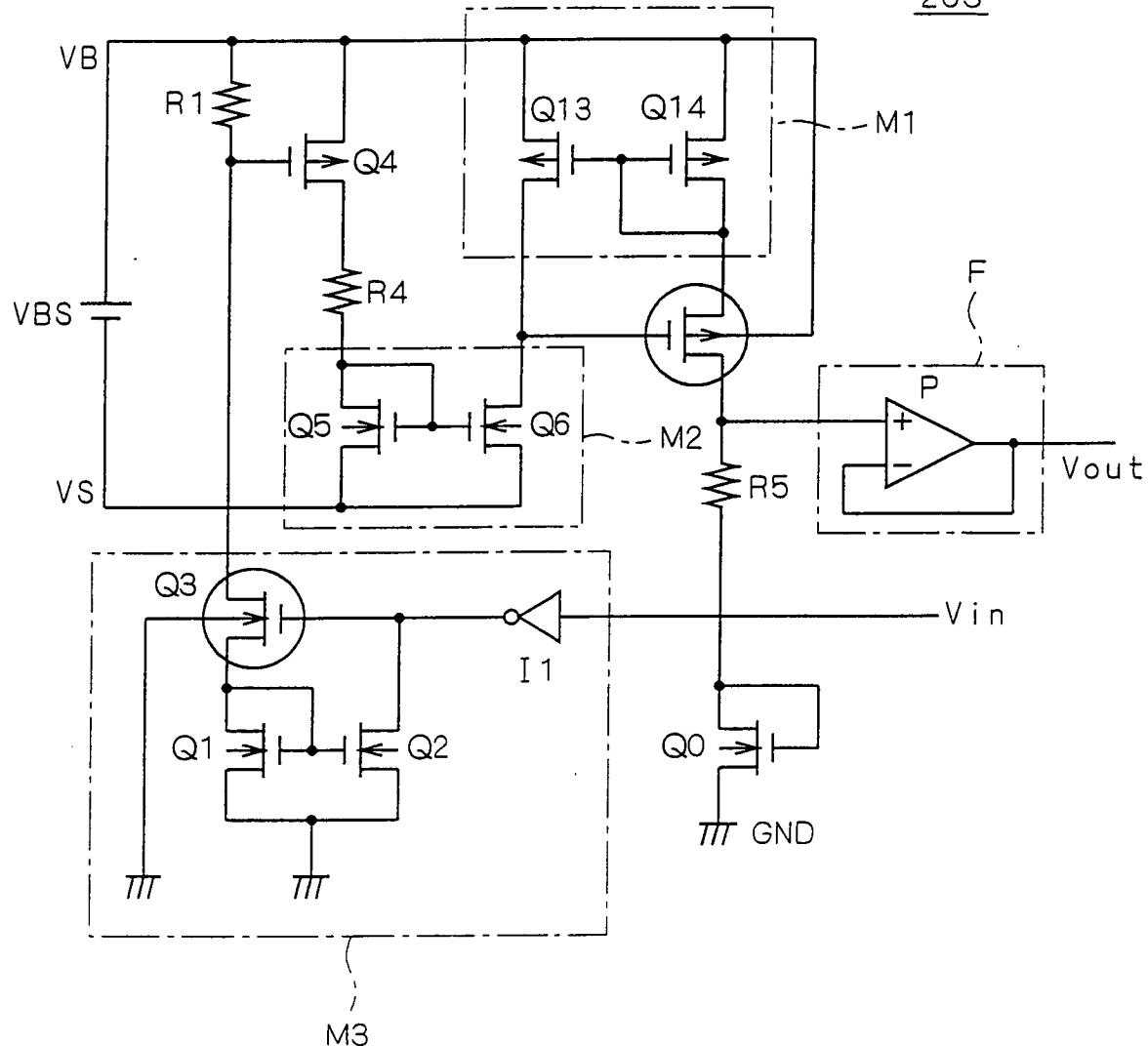

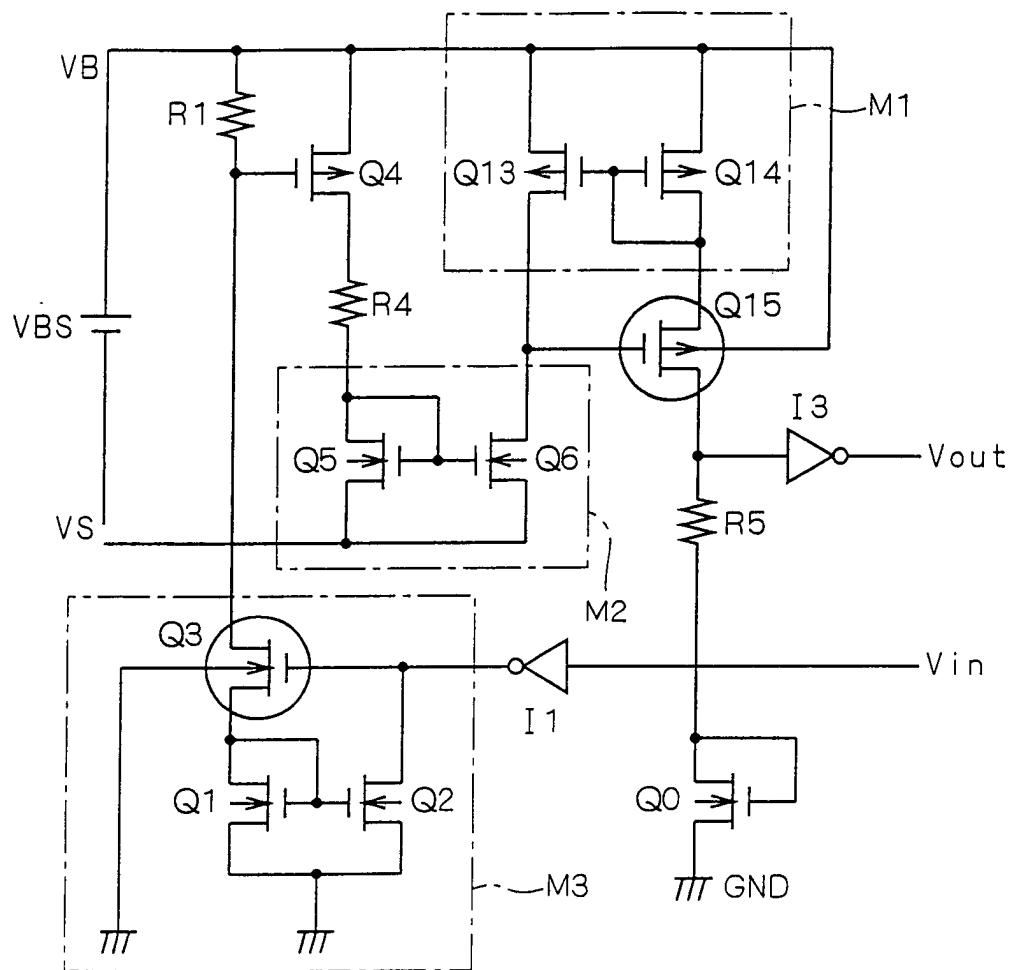

**[0011]** [Fig. 1](#) ist ein Schaltbild, das ein Beispiel für eine Pegelschiebeschaltung nach einer ersten Ausführungsform der vorliegenden Erfindung zeigt.

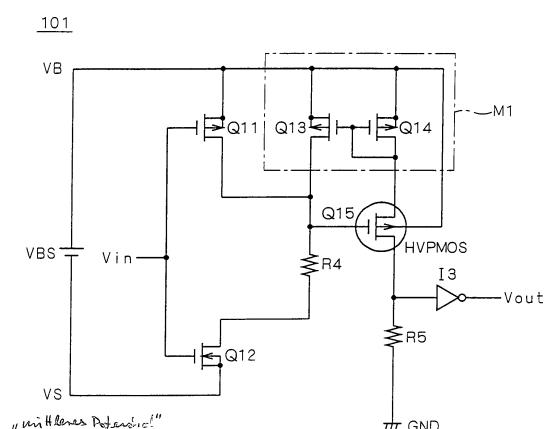

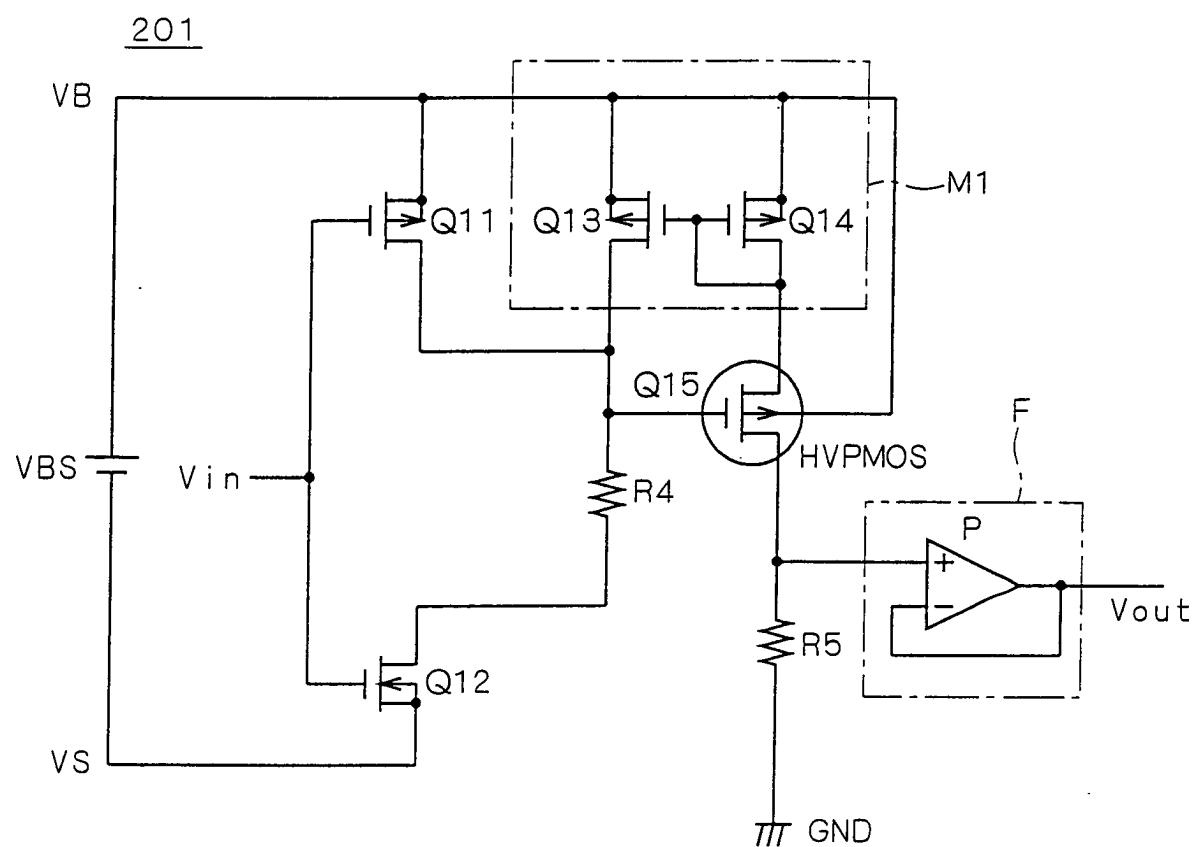

**[0012]** [Fig. 2](#) ist ein Schaltbild, das ein Beispiel für eine Pegelschiebeschaltung nach einer zweiten Ausführungsform der vorliegenden Erfindung zeigt.

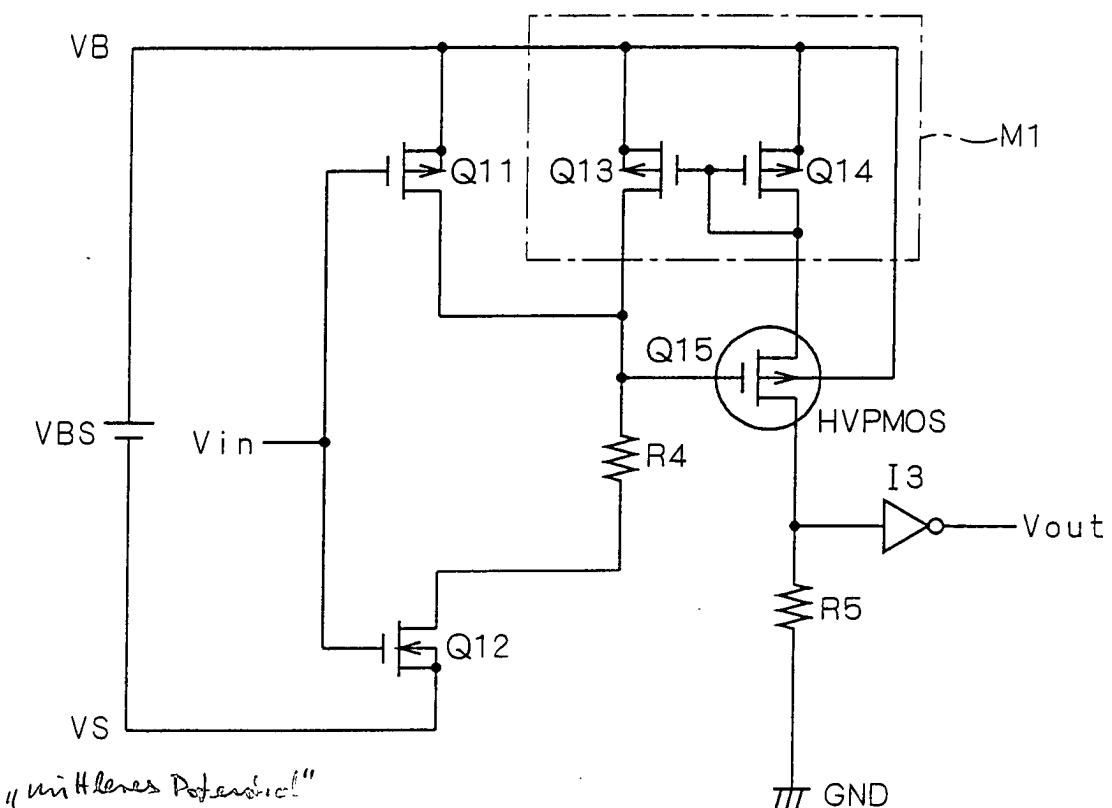

**[0013]** [Fig. 3](#) ist ein Schaltbild, das ein Beispiel für eine Ausgangsschaltung nach einer dritten Ausführungsform der vorliegenden Erfindung zeigt.

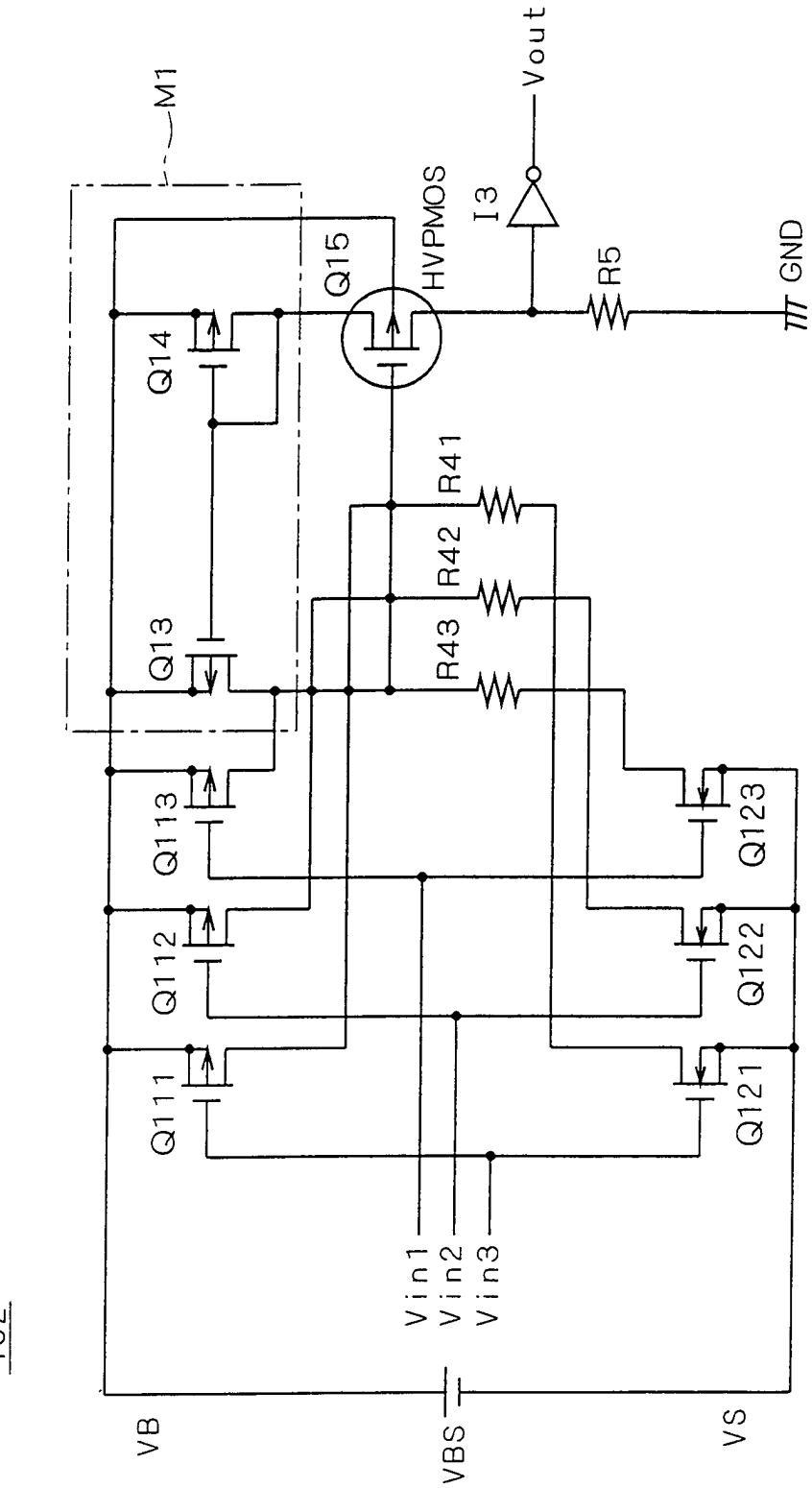

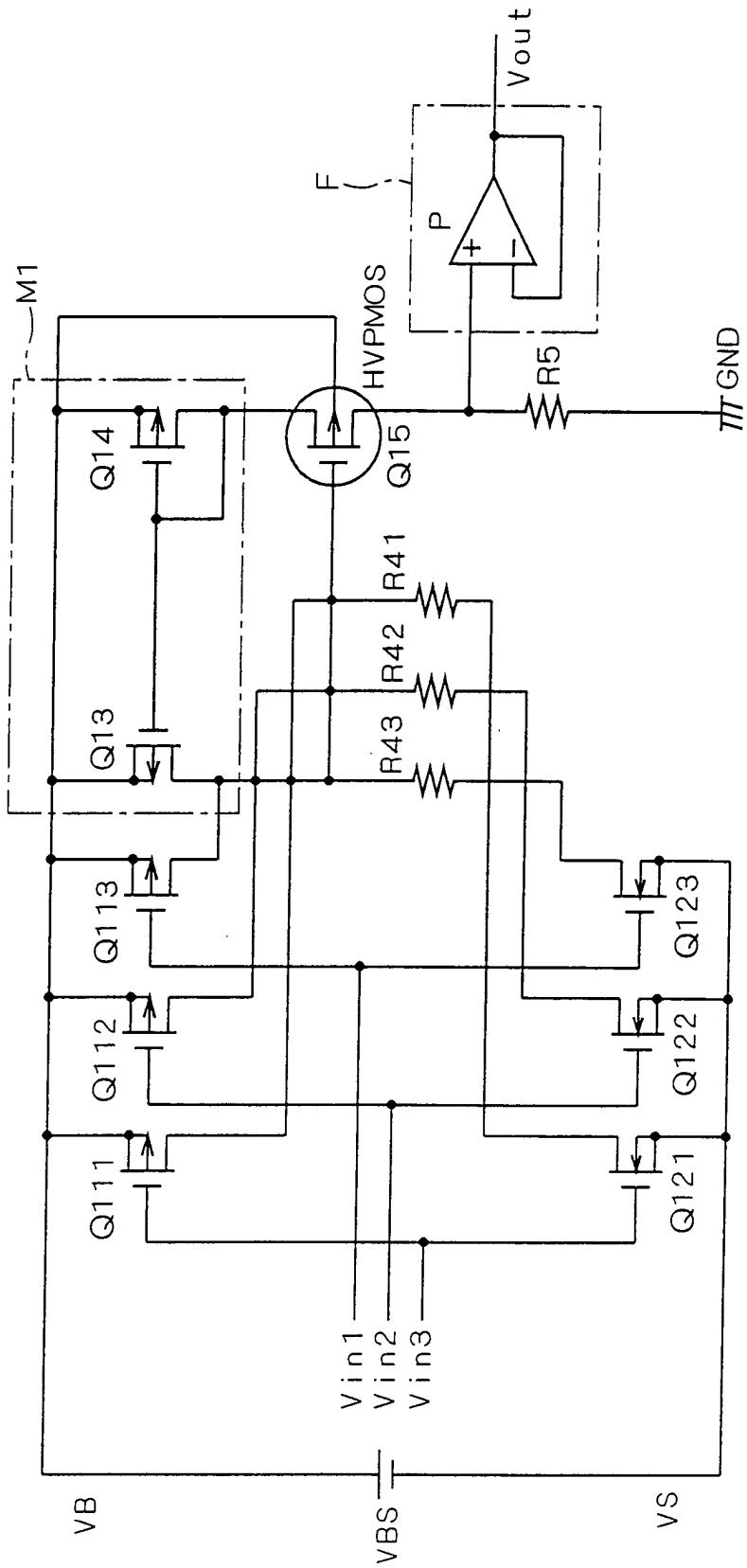

**[0014]** [Fig. 4](#) ist ein Schaltbild, das ein Beispiel für einen Aufbau einer Ausgangsschaltung nach einer vierten Ausführungsform der vorliegenden Erfindung zeigt.

**[0015]** [Fig. 5](#) ist ein Schaltbild, das ein weiteres Beispiel für einen Aufbau einer Ausgangsschaltung nach der vierten Ausführungsform der vorliegenden Erfindung zeigt.

**[0016]** [Fig. 6](#) ist ein Schaltbild, das ein weiteres Beispiel für einen Aufbau einer Ausgangsschaltung nach der vierten Ausführungsform der vorliegenden Erfindung zeigt.

**[0017]** [Fig. 1](#) ist ein Schaltbild, das eine Pegelschiebeschaltung **101** nach einer ersten Ausführungsform der vorliegenden Erfindung zeigt. Diese Schaltung kann z.B. verwendet werden, um einen Ausfall auf einer Hocharmseite einer Wechselrichterschaltung an eine Logikschaltung zu übertragen, die mit einem

niedrigen Pegel arbeitet.

**[0018]** Die Pegelschiebeschaltung **101** ist mit einer ersten Stromspiegelschaltung M1 versehen, bei der ein erster und ein zweiter Strompfad jeweils mit einem Potentialpunkt auf der Seite eines hohen Potentials VB verbunden sind. Der erste und der zweite Strompfad weisen z.B. jeweils Transistoren Q13 bzw. Q14 auf, wobei der Transistor Q14 einen Strom empfängt, der dem durch den Transistor Q13 fließenden Strom entspricht. Der Potentialpunkt VB ist z.B. mit einem positiven Pol einer Leistungsquelle VBS verbunden.

**[0019]** Die Pegelschiebeschaltung **101** ist weiter mit einem PMOS-Transistor Q15 mit einer hohen Durchbruchspannung versehen (in den Zeichnungen als HVMOS dargestellt). Eine Source des Transistors Q15 ist über den zweiten Strompfad (d.h. den Transistor Q14) der Stromspiegelschaltung M1 mit dem Potentialpunkt VB verbunden. Ein Backgate des Transistor Q15 ist mit dem Potentialpunkt VB verbunden. Der Transistor Q15 enthält weiter ein Drain und ein Gate.

**[0020]** Die Pegelschiebeschaltung **101** enthält einen Gatewiderstand R4, dessen eines Ende mit dem Gate des Transistors Q15 verbunden ist.

**[0021]** Die Pegelschiebeschaltung **101** enthält weiter einen Transistor Q12, der ein NMOS-Transistor ist. Eine Source des Transistors Q12 ist mit einem mittleren Potentialpunkt VS verbunden. Der mittlere Potentialpunkt VS ist z.B. mit einem negativen Pol der Leistungsquelle VBS verbunden.

**[0022]** Der mittlere Potentialpunkt VS liefert ein Potential mit einer Größe zwischen dem Potentialpunkt auf der Seite des hohen Potentials VB und einem Potentialpunkt auf einer Seite eines niedrigen Potentials GND. Der Potentialpunkt VB liefert z.B. einige zehn V, und der Potentialpunkt GND liefert 0V.

**[0023]** Ein Drain des Transistors Q12 ist über den Gatewiderstand R4 mit einem Gate des PMOS-Transistors Q15 verbunden. Einem Gate des Transistors Q12 wird ein Eingangssignal Vin zugeführt.

**[0024]** Das Eingangssignal Vin kann ein Signal zum Erfassen eines Kurzschlusses auf einer Hocharmseite eines Wechselrichters, ein Signal zum Erfassen einer Spannungsverringerung bei einer Steuerleistungsquelle oder ein Signal zum Erfassen eines Überstroms sein.

**[0025]** Die Pegelschiebeschaltung **101** enthält weiter einen Transistor Q11, der ein PMOS-Transistor ist. Eine Source des Transistors Q11 ist mit dem Potentialpunkt VB verbunden, ein Drain des Transistors Q11 ist mit dem Gatewiderstand R4 und dem Gate

des Transistors Q15 verbunden, und ein Gate des Transistors Q11 ist mit dem Gate des Transistors Q12 verbunden.

**[0026]** Die Pegelschiebeschaltung **101** enthält weiter einen Ausgangswiderstand R5, der zwischen dem Drain des Transistors Q15 und dem Potentialpunkt auf der Seite des niedrigen Potentials GND bereitgestellt ist.

**[0027]** Die Pegelschiebeschaltung **101** enthält weiter einen Puffer, dem ein Spannungsabfall an dem Ausgangswiderstand R5 eingegeben wird, um eine zweiwertige Logik auszugeben (in den folgenden Anwendungen als "Logikpuffer" bezeichnet), z.B. einen Inverter I3.

**[0028]** Bei dem Aufbau der Pegelschiebeschaltung **101** wird, wenn Strom durch den Gatewiderstand R4 fließt, eine Vorspannung an das Gate des Transistors Q15 angelegt. Weiterhin fließt ein Strom, der dem durch den Gatewiderstand R4 fließenden entspricht, durch den ersten Strompfad der Stromspiegelschaltung M1 (d.h. durch den Transistor Q13). Dann arbeitet die Stromspiegelschaltung M1 so, dass dem zweiten Strompfad (d.h. dem Transistor Q14) und der Source des Transistors Q15 ein Strom zugeführt wird, der dem durch den Gatewiderstand R4 fließenden entspricht.

**[0029]** Da das Gate des Transistors Q15 über den ersten Strompfad (Transistor Q13) der Stromspiegelschaltung M1 mit dem Potentialpunkt VB verbunden ist, wird beispielsweise ein Strom, der dem durch den Gatewiderstand R4 fließenden entspricht, dem ersten Strompfad (Transistor Q13) der Stromspiegelschaltung M1 zugeführt.

**[0030]** Somit wird ein Strom, der dem durch den Gatewiderstand R4 fließenden entspricht, dem Ausgangswiderstand R5 zugeführt, und eine einem mit dem gelieferten Strom zusammenhängenden Spannungsabfall entsprechende Spannung kann ausgegeben werden. Demzufolge kann auf das Eingangssignal Vin für die Ausgabe eine Pegelverschiebung angewendet werden. Der Inverter I3 liefert eine Funktion zum Schärfen (und in dieser Ausführungsform weiter zum Invertieren) der Spannung.

**[0031]** Auch unter Verwendungsbedingungen, bei denen die Spannungen an beiden Enden des Gatewiderstands R4 beträchtlich höher sind als das Potential auf der Seite des niedrigen Potentials GND, kann die genannte Funktion erzielt werden, solange der Transistor Q15 nur eine hohe Durchbruchspannung aufweist, ohne die Spannungsfestigkeit der Stromspiegelschaltung M1 zu erhöhen.

**[0032]** Insbesondere fließt bei dem Aufbau der Pegelschiebeschaltung **101**, wenn das Eingangssignal

Vin den Transistor Q12 einschaltet (und den Transistor Q11 ausschaltet), ein Strom jeweils durch den Gatewiderstand R4, den ersten und den zweiten Strompfad der Stromspiegelschaltung M1 (d.h. die Transistoren Q13 und Q14) und den Ausgangswiderstand R5. Wenn dagegen das Eingangssignal Vin den Transistor Q12 ausschaltet (und den Transistor Q11 einschaltet), fließt kein Strom durch den Gatewiderstand R4. Demzufolge fließt durch den ersten und den zweiten Strompfad der Stromspiegelschaltung M1 (die Transistoren Q13 und Q14) und den Ausgangswiderstand R5 auch kein Strom, der dem durch den Gatewiderstand R4 fließenden entspricht. Somit kann an dem Ausgangswiderstand R5 ein Spannungsabfall entsprechend dem Wert des Eingangssignals Vin erzielt werden. Das ermöglicht es, auf das Eingangssignal Vin für die Ausgabe eine Pegelverschiebung anzuwenden.

**[0033]** [Fig. 2](#) ist ein Schaltbild, das eine Pegelschiebeschaltung **102** nach einer zweiten Ausführungsform der vorliegenden Erfindung zeigt. Ähnlich wie die Pegelschiebeschaltung **101** kann diese Schaltung z.B. ebenfalls verwendet werden, um einen Ausfall auf einer Hocharmseite einer Wechselrichterschaltung zu einer mit einer niedrigen Spannung arbeitenden Logikschaltung zu übertragen.

**[0034]** Die Pegelschiebeschaltung **102** hat einen Aufbau, bei dem der Eingangsabschnitt der in der ersten Ausführungsform beschriebenen Pegelschiebeschaltung **101** mehrmals parallel angeordnet ist.

**[0035]** Genauer gesagt sind anstelle des in der Pegelschiebeschaltung **101** verwendeten Gatewiderstands R4 Gatewiderstände R41, R42 und R43 mit dem Gate des Transistors Q15 verbunden. Weiterhin ist die Pegelschiebeschaltung **102** anstelle des in der Pegelschiebeschaltung **101** verwendeten Transistors Q12 mit Transistoren Q121, Q122 und Q123 versehen, die alle NMOS-Transistoren sind. Weiterhin ist die Pegelschiebeschaltung **102** anstelle des in der Pegelschiebeschaltung **101** verwendeten Transistors Q11 mit Transistoren Q111, Q112, Q113 versehen, die alle PMOS-Transistoren sind.

**[0036]** Eine Source des Transistors Q121 ist mit dem mittleren Potentialpunkt VS verbunden, ein Drain ist über den Gatewiderstand R41 mit dem Gate des Transistors Q15 verbunden, und ein Gate empfängt eine erstes Eingangssignal Vin1.

**[0037]** Eine Source des Transistors Q122 ist mit dem mittleren Potentialpunkt VS verbunden, ein Drain ist über den Gatewiderstand R42 mit dem Gate des Transistors Q15 verbunden, und ein Gate empfängt eine erstes Eingangssignal Vin2.

**[0038]** Eine Source des Transistors Q123 ist mit dem mittleren Potentialpunkt VS verbunden, ein

Drain ist über den Gatewiderstand R43 mit dem Gate des Transistors Q15 verbunden, und ein Gate empfängt eine erstes Eingangssignal Vin3.

**[0039]** Die Eingangssignale Vin1, Vin2 und Vin3 können jeweils ein Signal zum Erfassen eines Kurzschlusses auf einer Hocharmseite eines Wechselrichters, ein Signal zum Erfassen einer Spannungsverringerung bei einer Steuerleistungsquelle und ein Signal zum Erfassen eines Überstroms sein.

**[0040]** Die Source des Transistors Q111 ist mit dem Potentialpunkt auf der Seite des hohen Potentials VB verbunden, sein Drain ist mit dem Gatewiderstand R41 und dem Gate des Transistors Q15 verbunden, und sein Gate ist mit dem Gate des Transistors Q121 verbunden.

**[0041]** Die Source des Transistors Q112 ist mit dem Potentialpunkt auf der Seite des hohen Potentials VB verbunden, sein Drain ist mit dem Gatewiderstand R42 und dem Gate des Transistors Q15 verbunden, und sein Gate ist mit dem Gate des Transistors Q122 verbunden.

**[0042]** Die Source des Transistors Q113 ist mit dem Potentialpunkt auf der Seite des hohen Potentials VB verbunden, sein Drain ist mit dem Gatewiderstand R43 und dem Gate des Transistors Q15 verbunden, und sein Gate ist mit dem Gate des Transistors Q123 verbunden.

**[0043]** Bei dem Aufbau der Pegelschiebeschaltung **102** wird, wenn ein Strom durch die Gatewiderstände R41, R42 und R43 fließt, eine Vorspannung an das Gate des Transistors Q15 angelegt. Weiterhin fließt der durch die Gatewiderstände R41, R42, R43 fließende Strom durch den ersten Strompfad der Stromspiegelschaltung M1 (Transistor Q13). Dann arbeitet die Stromspiegelschaltung M1 so, dass der Source des Transistors Q14 des zweiten Strompfades einen Strom zugeführt wird, der dem durch die Gatewiderstände R41, R42, R43 fließenden entspricht.

**[0044]** Somit wird ein Strom, der dem durch die Gatewiderstände R41, R42 und R43 entspricht, dem Ausgangswiderstand R5 zugeführt, und eine dem mit dem gelieferten Strom zusammenhängenden Spannungsabfall entsprechende Spannung kann ausgegeben werden. Demzufolge kann auf die Eingangssignale Vin1, Vin2, Vin3 für die Ausgabe eine Pegelverschiebung angewendet werden. Der Inverter I3 liefert eine Funktion zum Schärfen (und in dieser Ausführungsform weiter zum Invertieren) der Spannung.

**[0045]** Auch unter Verwendungsbedingungen, bei denen die Spannungen an beiden Enden der jeweiligen Gatewiderstände R41, R42, R43 beträchtlich höher sind als das Potential auf der Seite des niedrigen Potentials GND, kann die genannte Funktion erzielt

werden, solange der Transistor Q15 nur eine hohe Durchbruchsspannung aufweist, ohne die Spannungsfestigkeit der Stromspiegelschaltung M1 zu erhöhen.

**[0046]** Bei dem Aufbau der Pegelschiebeschaltung 102 können an dem Ausgangswiderstand R5 Spannungsabfälle entsprechend den jeweiligen mehreren Eingangssignalen gewonnen werden. Das ermöglicht es, auf eine Mehrzahl von Eingangssignalen für die Ausgabe eine Pegelverschiebung anzuwenden.

**[0047]** [Fig. 3](#) ist ein Schaltbild, das eine Ausgangsschaltung 103 nach einer dritten Ausführungsform der vorliegenden Erfindung zeigt. Diese Schaltung kann beispielsweise zum Überwachen einer Zellenspannung einer Autobatterie verwendet werden.

**[0048]** Verglichen mit der Pegelschiebeschaltung 101 sind bei dem Aufbau der Ausgangsschaltung 103 die Transistoren Q11 und Q12 weggelassen, und die Verbindungen des Gatewiderstands R4 sind geändert. Insbesondere ist sowohl in der Pegelschiebeschaltung 101 als auch in der Ausgangsschaltung 103 der Gatewiderstand R4 mit dem Gate des Transistors Q15 und dem ersten Strompfad der Stromspiegelschaltung M1 verbunden. Die Ausgangsschaltung 103 hat jedoch einen Aufbau, bei dem der Gatewiderstand R4 über eine Stromspiegelschaltung M2 mit dem Gate des Transistors Q15 und dem ersten Strompfad der Stromspiegelschaltung M1 verbunden ist.

**[0049]** Die Stromspiegelschaltung M2 hat einen ersten und einen zweiten Strompfad, die beide mit dem mittleren Potentialpunkt VS verbunden sind. Der erste und der zweite Strompfad weisen in dieser Ausführungsform beispielsweise jeweils einen Transistor Q5 bzw. Q6 auf, wobei der Transistor Q6 mit einem Strom versorgt wird, der dem durch den Transistor Q5 fließenden Strom entspricht. Als Reaktion auf den durch den Gatewiderstand R4 fließenden Strom fließt Strom durch den ersten Strompfad (d.h. den Transistor Q5) und den zweiten Strompfad (d.h. den Transistor Q6) der Spiegelschaltung M2. Dann fließt Strom durch den ersten Strompfad (d.h. den Transistor Q13) und den zweiten Strompfad (d.h. den Transistor Q14) der Stromspiegelschaltung M1. Der Strom gelangt durch den Transistor Q15 und fließt weiter durch den Ausgangswiderstand R5.

**[0050]** Daher ist es auch bei dem Aufbau der Ausgangsschaltung 103 auch unter einer Verwendungsbedingung, bei der die Spannungen an beiden Enden des Gatewiderstands R4 beträchtlich größer sind als das Potential auf der Seite des niedrigen Potentials GND, nicht erforderlich, die Spannungsfestigkeit der Stromspiegelschaltungen M1 und M2 zu erhöhen, solange nur der Transistor Q15 eine hohe Durchbruchsspannung aufweist.

**[0051]** Anstelle der Transistoren Q11 und Q12 in der Pegelschiebeschaltung 101 enthält die Ausgangsschaltung 103 einen Transistor Q4, der ein PMOS-Transistor ist, einen Gatewiderstand R1 für den Transistor Q4 und eine Stromspiegelschaltung M3.

**[0052]** Das Gate des Transistors Q4 ist über den Gatewiderstand R1 mit dem Potentialpunkt auf der Seite des hohen Potentials VB verbunden. Ein Drain des Transistors Q4 ist über den Gatewiderstand R4 mit der Stromspiegelschaltung M2 verbunden. Eine Source des Transistors Q4 ist mit dem Potentialpunkt VB verbunden.

**[0053]** Die Stromspiegelschaltung M3 hat den Aufbau eines sogenannten Wilson-Stromspiegels und enthält einen ersten Strompfad mit einem Transistor Q2, der ein NMOS-Transistor ist, und einen zweiten Strompfad, der mit dem Gate des Transistors Q4 verbunden ist. Der zweite Strompfad enthält Transistoren Q1 und Q3, die beide NMOS-Transistoren sind. Der erste und der zweite Strompfad der Stromspiegelschaltung M3 sind beide mit dem Potentialpunkt auf der Seite des niedrigen Potentials GND verbunden.

**[0054]** Weitere Einzelheiten des dargestellten Aufbaus der Stromspiegelschaltung M3 sind wie folgt: Eine Source des Transistors Q1 und eine Source des Transistors Q2 sind beide mit dem Potentialpunkt auf der Seite des niedrigen Potentials GND verbunden. Ein Drain und ein Gate des Transistors Q1, ein Gate des Transistors Q2 und eine Source des Transistors Q3 sind miteinander verbunden. Ein Drain des Transistors Q2 und ein Gate des Transistors Q3 sind miteinander verbunden. Ein Drain des Transistors Q3 ist mit dem Gatewiderstand R1 und einem Gate des Transistors Q4 verbunden. Ein Backgate des Transistors Q3 ist mit dem Potentialpunkt auf der Seite des niedrigen Potentials GND verbunden.

**[0055]** Sowohl dem Drain des Transistors Q2 als auch dem Gate des Transistors Q3 wird ein Eingangssignal zugeführt. Vorliegend ist beispielsweise der Fall dargestellt, bei dem das Eingangssignal Vin über einen Inverter I1 (d.h. durch Invertieren des Signals) eingegeben wird.

**[0056]** Wenn das Eingangssignal Vin ein Potential mit H-Pegel an das Gate des Transistors Q3 und den Drain des Transistors Q2 liefert, schalten die Transistoren Q1, Q2 und Q3 ein. Das bewirkt, dass durch den Gatewiderstand R1 (im Hinblick auf den Transistor Q4) ein Strom fließt, und ein daraus folgender Spannungsabfall bewirkt, dass dem Transistor Q4 eine Gatevorspannung zugeführt wird. Dann fließt ein der Gatevorspannung entsprechender Strom durch den Transistor Q4.

**[0057]** Der durch den Transistor Q4 fließende Strom fließt durch den Gatewiderstand R4 (im Hinblick auf den Transistor Q15), und demzufolge kann an dem Ausgangswiderstand R5 wie oben beschrieben ein Spannungsabfall erzielt werden.

**[0058]** Da die Ausgangsschaltung **103** in der beschriebenen Weise arbeitet, ändert sich die Menge des durch den Gatewiderstand R4 fließenden Stroms abhängig von einem von der Leistungsquelle VBS zugeführten Potential. Durch Einstellen der Werte des Gatewiderstands R4 und des Ausgangswiderstands R5 im Voraus kann der Spannungsabfall an dem Ausgangswiderstand R5 auf eine Spannung eingestellt werden, die bezogen auf das von der Leistungsquelle VBS gelieferte Potential relativ klein ist. Wenn daher eine akzeptierbare untere Grenze des von der Leistungsquelle VBS zuzuführenden Potentials auf einen Schwellenwert des Inverters I3 eingestellt wird, liegt ein Ausgang des Inverters I3 auf H-Pegel, wenn ein zugeführtes Potential unter der akzeptierbaren unteren Grenze liegt, und der Ausgang des Inverters I3 liegt auf L-Pegel, wenn ein zugeführtes Potential über der akzeptablen unteren Grenze liegt. Als Eingangssignal Vin kann beispielsweise eine Anweisung zum Überwachen der Leistungsquelle VBS verwendet werden.

**[0059]** Wenn das Eingangssignal Vin den L-Pegel erreicht, wird auf diese Weise ein Potentialunterschied zwischen dem Potentialpunkt auf der Seite des hohen Potentials VB und dem mittleren Potentialpunkt VS, während dessen Pegel verschoben wird, durch einen Spannungsabfall an dem Ausgangswiderstand R5 wiedergegeben, und das Ergebnis kann zu einer Logikschaltung übertragen werden, die bei einer niedrigen Spannung arbeitet. Weiterhin braucht die Spannungsfestigkeit nur an dem Transistor Q3 erhöht zu werden, der am nächsten zu dem Gatewiderstand R1 angeordnet ist, und es ist nicht erforderlich, die Spannungsfestigkeit der Transistoren Q1 und Q2 zu erhöhen.

**[0060]** Außerdem ist es unter dem Gesichtspunkt der Verhinderung eines Rückwärtsstroms vorzuziehen, eine Diode bereitzustellen, die zwischen den Ausgangswiderstand R5 und den Potentialpunkt auf der Seite des niedrigen Potentials angeordnet ist. Es können z.B. sowohl ein Gate als auch ein Drain eines Transistors Q0, der ein NMOS-Transistor ist, mit dem Ausgangswiderstand R5 verbunden werden, und eine Source des Transistors Q0 kann mit einem Potentialpunkt auf der Seite des niedrigen Potentials GND verbunden sein.

**[0061]** Die erste bis vierte Ausführungsform haben einen Fall beschrieben, bei dem ein Spannungsabfall an dem Ausgangswiderstand R5 als Eingangssignal für einen Logikpuffer angesehen wurde, z.B. für den Inverter I3. In diesem Fall wird bei der ersten und

zweiten Ausführungsform eine Pegelverschiebung für die Eingangssignale Vin bzw. Vin1, Vin2 und Vin3 durchgeführt. In der dritten Ausführungsform wird ein Potentialunterschied zwischen dem Potentialpunkt auf der Seite des hohen Potentials VB und dem mittleren Potentialpunkt VS, während sein Pegel verschoben wird, als Logiksignal ausgegeben.

**[0062]** Es ist jedoch nicht notwendig, anzunehmen, dass die Schaltung der vorliegenden Erfindung ein Logiksignal ausgibt, und die Schaltung kann eine Analogspannung ausgeben. [Fig. 4](#) bis [Fig. 6](#) sind Schaltbilder, die Beispiele für einen Aufbau einer Ausgangsschaltung nach einer vierten Ausführungsform zeigen, und sie entsprechen jeweils [Fig. 1](#) bis [Fig. 3](#).

**[0063]** [Fig. 4](#) zeigt einen Aufbau einer Ausgangsschaltung **201**, bei der der Inverter I3 der in [Fig. 1](#) gezeigten Pegelschiebeschaltung **101** durch einen Spannungsfolger F ersetzt ist. Dieser Aufbau macht es leicht, ein gewünschtes Potential als Ausgabe der Ausgangsschaltung **201** zu erzielen.

**[0064]** [Fig. 5](#) zeigt einen Aufbau einer Ausgangsschaltung **202**, bei der der Inverter I3 der in [Fig. 2](#) gezeigten Pegelschiebeschaltung **102** durch einen Spannungsfolger F ersetzt ist. Dieser Aufbau macht es leicht, ein gewünschtes Potential als Ausgabe der Ausgangsschaltung **202** zu erzielen. Durch Verändern der Werte der Widerstände R41, R42 und R43 gegeneinander kann eine Ausgangsspannung als Reaktion auf die Werte der Eingangssignale Vin1, Vin2 und Vin3 verändert werden. Daher ist es möglich, einzeln zu erfassen, ob die Eingangssignale Vin1, Vin2 und Vin3 aktiv oder inaktiv sind.

**[0065]** Wenn z.B. die Ausgangsspannungen entsprechend der Aktivität der Eingangssignale Vin1, Vin2 und Vin3 jeweils auf 1V, 2V bzw. 4V eingestellt werden, ist es natürlich möglich, die Eingangssignale voneinander zu unterscheiden. Wenn weiterhin die Eingangssignale Vin1, Vin2 und Vin3 beispielsweise jeweils aktiv, aktiv bzw. inaktiv sind, ist die Ausgangsspannung 3V, wodurch es möglich ist, zu erfassen, ob diese Signale aktiv oder inaktiv sind.

**[0066]** [Fig. 6](#) zeigt einen Aufbau einer Ausgangsschaltung **203**, bei der der Inverter I3 der in [Fig. 3](#) gezeigten Ausgangsschaltung **103** durch einen Spannungsfolger F ersetzt ist. Dieser Aufbau macht es möglich, einen Potentialunterschied zwischen dem Potentialpunkt auf der Seite des hohen Potentials VB und dem mittleren Potentialpunkt VS in einem relativ kleinen Spannungsbereich zu beobachten.

**[0067]** In jedem der genannten Spannungsfolger F kann eine Schaltung verwendet werden, die einen Operationsverstärker P verwendet. Insbesondere kann ein Spannungsfolger F so aufgebaut sein, dass

ein Spannungsabfall an dem Ausgangswiderstand R5 einem nichtinvertierenden Eingangsanschluss des Operationsverstärkers P eingegeben wird und ein invertierender Eingangsanschluss und ein Ausgangsanschluss miteinander verbunden sind.

### Patentansprüche

1. Ausgangsschaltung mit einer ersten Stromspiegelschaltung (M1) mit einem ersten und einem zweiten Strompfad (Q13, Q14), die beide mit einem Potentialpunkt auf der Seite eines hohen Potentials (VB) verbunden sind, einem ersten PMOS-Transistor (Q15) mit einem Drain, einem Gate, einer Source und einem Backgate, wobei die Source über den zweiten Strompfad der ersten Stromspiegelschaltung mit dem Potentialpunkt auf der Seite des hohen Potentials verbunden ist und das Backgate mit dem Potentialpunkt auf der Seite des hohen Potentials verbunden ist, einem ersten Gatewiderstand (R4; R41), der mit dem Gate des ersten PMOS-Transistors verbunden ist, einem ersten NMOS-Transistor (Q12; Q121; Q6) mit einer Source, einem Drain und einem Gate, wobei die Source verbunden ist mit einem mittleren Potentialpunkt (VS) zum Zuführen eines Potentials zwischen dem Potentialpunkt auf der Seite des hohen Potentials (VB) und dem Potentialpunkt auf der Seite des niedrigen Potentials (GND), der Drain über den ersten Gatewiderstand (R4; R41) mit dem Gate des ersten PMOS-Transistors (Q15) verbunden ist und ein Eingangssignal (Vin; Vin1) dem Gate zugeführt wird, und einem Ausgangswiderstand (R5), der zwischen den Drain des ersten PMOS-Transistors und einen Potentialpunkt auf der Seite eines niedrigen Potentials (GND) geschaltet ist; wobei als Reaktion auf einen durch den ersten Gatewiderstand fließenden Strom ein Strom durch den ersten Strompfad der ersten Stromspiegelschaltung fließt und eine Ausgangsspannung (Vout) auf der Grundlage eines Spannungsabfalls an dem Ausgangswiderstand bestimmt wird.

2. Ausgangsschaltung nach Anspruch 1 mit einem zweiten Gatewiderstand (R42) und einem zweiten NMOS-Transistor (Q122) mit einer Source, einem Drain und einem Gate, wobei die Source mit dem mittleren Potentialpunkt (VS) verbunden ist, der Drain über den zweiten Gatewiderstand (R42) mit dem Gate des ersten PMOS-Transistors (Q15) verbunden ist und ein weiteres Eingangssignal (Vin2) dem Gate zugeführt wird.

3. Ausgangsschaltung nach Anspruch 1 mit einer zweiten Stromspiegelschaltung (M2) mit einem ersten und einem zweiten Strompfad (Q5, Q6), die beide verbunden sind mit einem mittleren Potentialpunkt (VS) zum Zuführen eines Potentials zwischen

dem Potentialpunkt auf der Seite des hohen Potentials (VB) und dem Potentialpunkt auf der Seite des niedrigen Potentials (GND), wobei die zweite Stromspiegelschaltung so angeordnet ist, dass der erste Gatewiderstand (R4) über die zweite Stromspiegelschaltung mit dem Gate des ersten PMOS-Transistors (Q15) und dem ersten Strompfad (Q13) der ersten Stromspiegelschaltung (M1) verbunden ist, einem zweiten Gatewiderstand (R1), der mit dem Potentialpunkt auf der Seite des hohen Potentials verbunden ist, einem zweiten PMOS-Transistor (Q4) mit einem Gate, einem Drain und einer Source, wobei das Gate über den zweiten Gatewiderstand mit dem Potentialpunkt auf der Seite des hohen Potentials verbunden ist, der Drain über den ersten Gatewiderstand mit der zweiten Stromspiegelschaltung verbunden ist und die Source mit dem Potentialpunkt auf der Seite des hohen Potentials verbunden ist, und einer dritten Stromspiegelschaltung (M3) mit einem ersten Pfad (Q2) und einem zweiten Pfad (Q1, Q3), wobei der zweite Pfad mit dem Gate des zweiten PMOS-Transistors verbunden ist, die dritte Stromspiegelschaltung ein Wilson-Stromspiegel ist und sowohl der erste als auch der zweite Strompfad der dritten Stromspiegelschaltung mit dem Potentialpunkt auf der Seite des niedrigen Potentials verbunden ist.

4. Ausgangsschaltung nach einem der Ansprüche 1 bis 3 mit einem Logikpuffer (I3) zum Eingeben eines Spannungsabfalls an dem Ausgangswiderstand (R5).

5. Ausgangsschaltung nach einem der Ansprüche 1 bis 3 mit einem Spannungsfolger (F) zum Eingeben eines Spannungsabfalls an dem Ausgangswiderstand (R5).

Es folgen 6 Blatt Zeichnungen

## Anhängende Zeichnungen

F I G . 1

101

F | G . 2

102

FIG. 3

103

F I G . 4

56

2002

F | G . 6

203