MINISTERO DELLO SVILUPPO ECONOMICO

DIREZIONE GENERALE PER LA TUTELA DELLA PROPRIETÀ INDUSTRIALE

UFFICIO ITALIANO BREVETTI E MARCHI

UIBM

|                           |                        |

|---------------------------|------------------------|

| <b>DOMANDA NUMERO</b>     | <b>101997900601734</b> |

| <b>Data Deposito</b>      | <b>05/06/1997</b>      |

| <b>Data Pubblicazione</b> | <b>05/12/1998</b>      |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| H       | 03     | K           |        |             |

Titolo

CIRCUITO CONVERTITORE DA LOGICA BIPOLARE A LOGICA CMOS A ELEVATA VELOCITA'

SGS-THOMSON MICROELECTRONICS S.r.l.,

con sede a Agrate Brianza (Milano), e

MI 97 A 1333

CONSORZIO PER LA RICERCA SULLA MICROELETTRONICA NEL MEZZOGIORNO,

con sede a Catania.

\* \* \* \* \*

- 5610.1997

#### DESCRIZIONE

Il presente trovato riguarda un circuito convertitore da logica bipolare a logica CMOS ad elevata velocità. Più in particolare, il trovato riguarda un circuito convertitore che permette la connessione tra una porzione di circuito realizzata in logica bipolare ed un'altra porzione del circuito realizzata in logica CMOS.

Come è noto, molti circuiti integrati impiegati ad esempio nel campo delle comunicazioni digitali utilizzano elaborazione di segnali digitali ad una elevata frequenza di clock.

Solitamente, un approccio tipico per la realizzazione di tali circuiti è quello di suddividere la sezione digitale del circuito in due parti di cui una è realizzata in tecnologia bipolare (ECL) e l'altra in tecnologia CMOS. In molti sistemi di elaborazione digitale di segnali, anche quelli che funzionano ad una frequenza di clock molto elevata, vi è una parte importante del sistema che lavora con segnali di clock moderati e quindi può essere implementata utilizzando tecniche CMOS con risultati adeguati alle esigenze.

La possibilità di implementare il circuito di elaborazione mediante le due tecnologie sopra descritte permette di soddisfare la necessità di avere livelli di integrazione e frequenze di bit sempre più elevati, re-

quisito altrimenti limitato dal consumo di potenza dei circuiti bipolari.

In seguito alla connessione di circuiti digitali bipolari a circuiti digitali realizzati in tecnologia CMOS, ossia circuiti logici ECL con circuiti logici CMOS, sorgono due principali inconvenienti.

In primo luogo gli stati logici ECL non sono compatibili con gli stati logici CMOS e in secondo luogo, a causa della necessità di stabilità in temperatura, la massa di riferimento di un circuito bipolare è solitamente differente da quella di un circuito CMOS come è illustrato nella Fig. 1 che illustra una tipica architettura di un sistema digitale bipolare e CMOS.

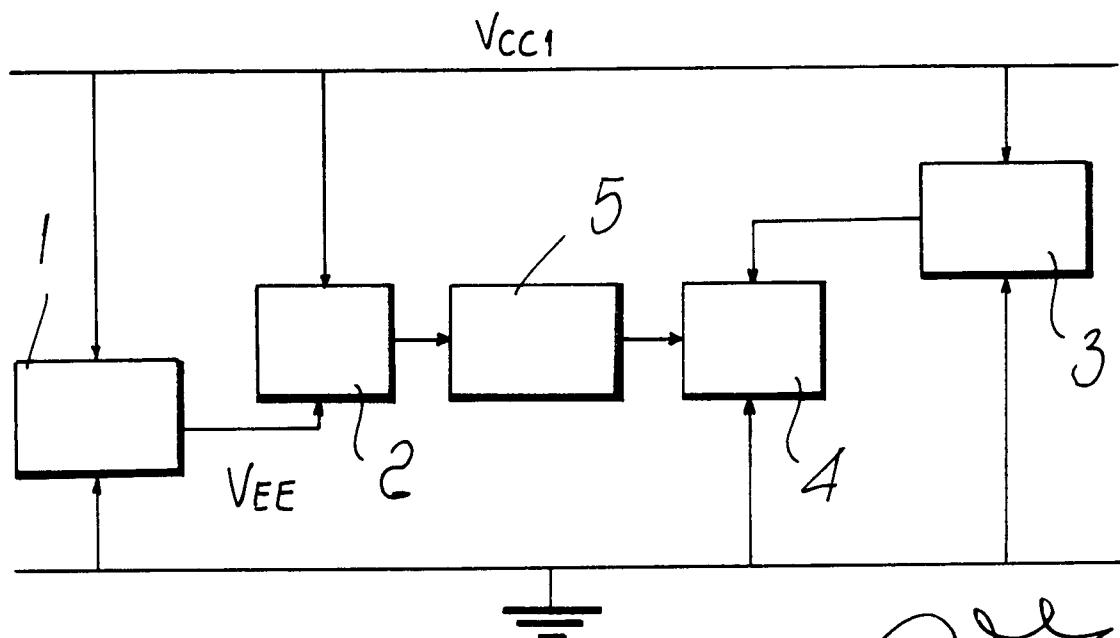

In tale figura una linea di alimentazione principale  $V_{cc1}$  alimenta un regolatore di tensione che fornisce una tensione (ossia  $V_{cc1}-V_{EE}$ ) stabile con la temperatura per il circuito bipolare 2. In modo similare, un regolatore di tensione 3 fornisce una tensione stabile  $V_{cc2}$  al circuito CMOS 4. Al fine di collegare correttamente fra loro il circuito bipolare 2 e il circuito CMOS 4 è necessaria la presenza di un circuito convertitore da logica bipolare a logica CMOS, indicato dal numero di riferimento 5.

In molti casi accade che la tensione  $V_{cc1}$  sia non regolata e varia di diverse centinaia di millivolt o persino più di 1 volt. In questo caso occorre fornire un circuito traslatore di livello dinamico al fine di compensare questa variazione, con l'effetto di rendere più critico e complicato il progetto del circuito convertitore 5 impiegato come interfaccia tra la porzione digitale bipolare e la porzione digitale CMOS del sistema.

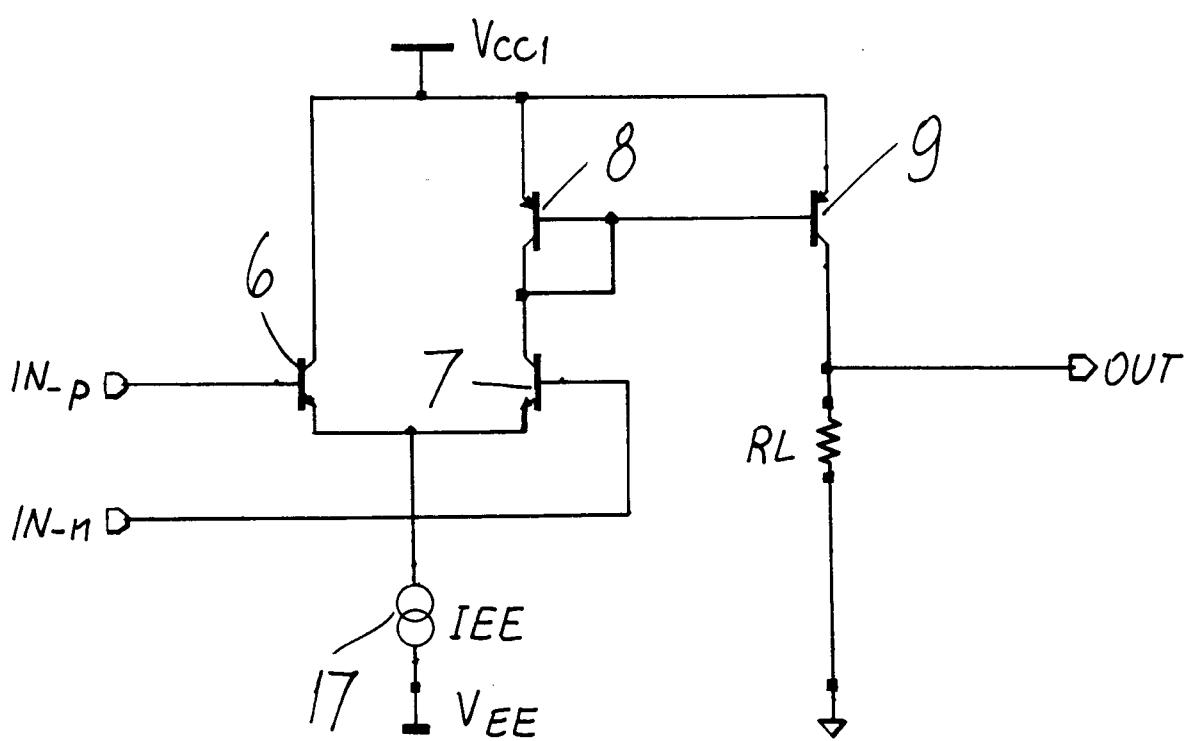

La Fig. 2 illustra una soluzione circuitale comunemente adottata per un circuito convertitore da logica bipolare a logica CMOS.

In tale figura è evidenziato un generatore di corrente commutato il

quale è implementato da una coppia di transistori bipolari di tipo NPN, indicati dai numeri di riferimento 6 e 7 e collegati ad emettitore accoppiato, e da una coppia di transistori bipolari di tipo PNP collegati a specchio di corrente. Questo circuito fornisce intrinsecamente il traslatore di livello richiesto. Tuttavia, la soluzione circuitale sopra proposta risente del fatto che i transistori di tipo PNP hanno prestazioni scadenti e, in particolare, i transistori PNP impiegati in circuiti per applicazioni in radiofrequenza sono transistori di tipo laterale con una frequenza di taglio molto bassa ( $f_t < 100$  MHz).

Dato che la corrente di uscita nel circuito della Fig. 2 è commutata dai transistori PNP 8 e 9, la velocità massima del circuito non può superare alcuni megahertz.

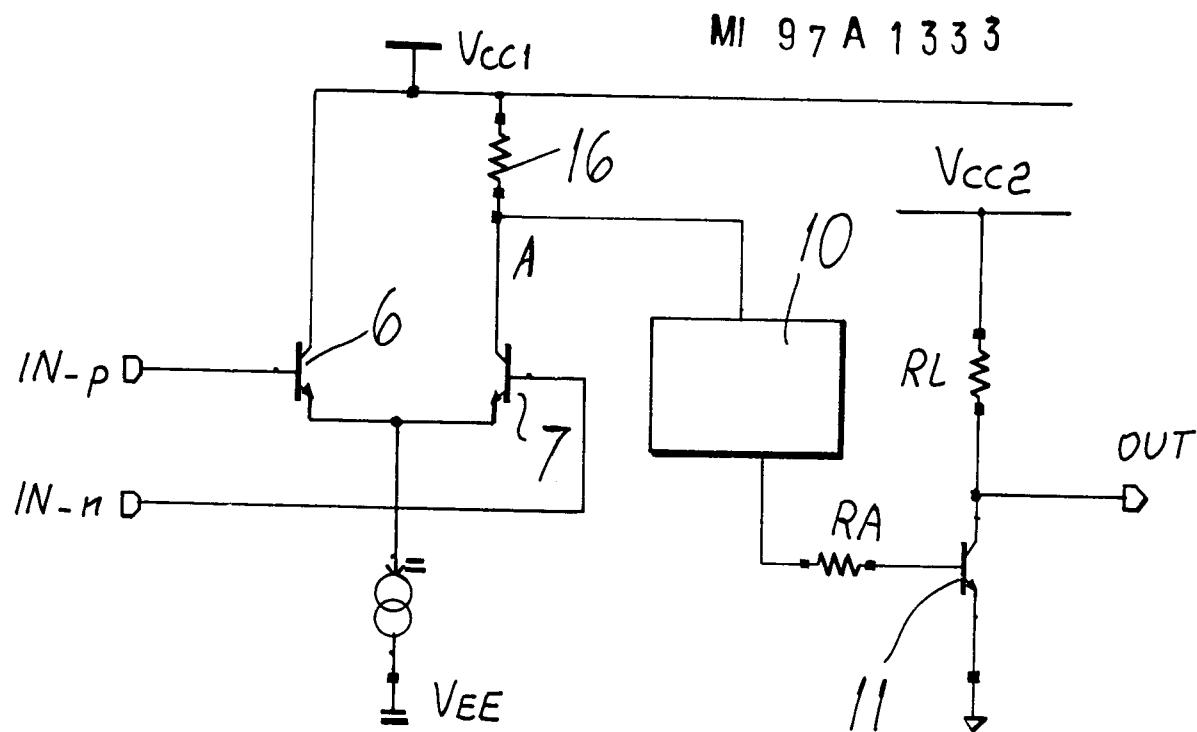

Una seconda soluzione circuitale di tipo noto è illustrata nella Fig. 3 in cui viene sempre impiegato uno stadio ad emettitore accoppiato (con i transistori 6 e 7 di tipo NPN, analoghi a quelli della Fig. 1), ma viene invece usato un traslatore di livello 10 di tipo fisso. In questo caso gli inconvenienti sono dovuti al fatto che vi è uno scarso controllo della corrente di pilotaggio della base del transistore di uscita 11 dovuta alla variazione della tensione  $V_{cc1}$  e alla saturazione del transistore 11 quando l'uscita OUT è nello stato basso. Questi inconvenienti portano ad un consumo di potenza elevato e ad una bassa frequenza di lavoro.

Compito precipuo del presente trovato è quindi quello di realizzare un circuito di conversione da logica bipolare a logica CMOS che abbia una velocità di conversione elevata.

Nell'ambito di questo compito, uno scopo del presente trovato è quel-

lo di realizzare un circuito di conversione da logica bipolare a logica CMOS che consenta di ottenere un frequenza operativa elevata.

Un altro scopo del presente trovato è quello di realizzare un circuito di conversione da logica bipolare a logica CMOS che abbia un consumo di potenza inferiore a quello di soluzioni circuitali di tipo noto.

Un ulteriore scopo del presente trovato è quello di realizzare un circuito di conversione da logica bipolare a logica CMOS che sia stabile.

Non ultimo scopo del presente trovato è quello di realizzare un circuito di conversione da logica bipolare a logica CMOS che sia di elevata affidabilità, di relativamente facile realizzazione a costi competitivi.

Questo compito, nonchè questi e altri scopi che meglio appariranno in seguito sono raggiunti da un circuito convertitore da logica bipolare a logica CMOS ad elevata velocità, comprendente uno stadio di ingresso costituito da un amplificatore differenziale destinato ad essere collegato ad una porzione circuitale di logica bipolare e alimentato dalla tensione di alimentazione della porzione di logica bipolare, e uno stadio di uscita alimentato dalla tensione di una porzione circuitale di logica CMOS, caratterizzato dal fatto che tra detto stadio di ingresso e detto stadio di uscita è interposto un circuito traslatore di livello dinamico, detto stadio di uscita essendo collegato alla porzione circuitale di logica CMOS.

Ulteriori caratteristiche e vantaggi del trovato risulteranno maggiormente dalla descrizione di una forma di realizzazione preferita, ma non esclusiva, del circuito secondo il trovato, illustrata a titolo indicativo e non limitativo negli uniti disegni, in cui:

la Fig. 1 è uno schema a blocchi illustrante una tipica architettura

di un sistema digitale bipolare e CMOS;

la Fig. 2 è uno schema circuitale di un circuito convertitore da logica bipolare a logica CMOS impiegante transistori di tipo PNP, secondo una prima forma di realizzazione di tipo noto;

la Fig. 3 è uno schema circuitale di un circuito convertitore da logica bipolare a logica CMOS impiegante un traslatore di livello di tipo fisso, in conformità con una seconda forma di realizzazione di tipo noto;

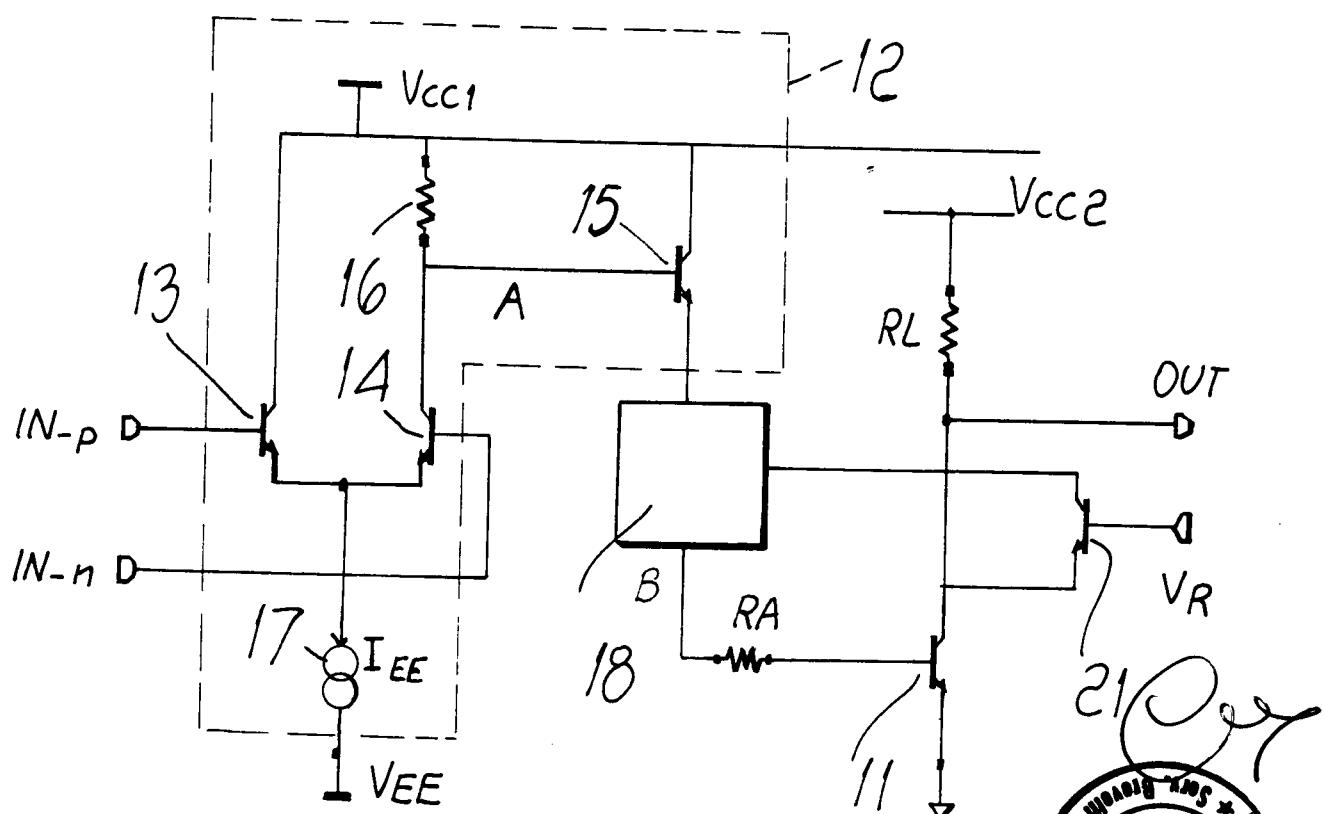

la Fig. 4 è uno schema circuitale semplificato del circuito convertitore da logica bipolare a logica CMOS secondo il presente trovato;

la Fig. 5 è uno schema circuitale dettagliato del circuito convertitore da logica bipolare a logica CMOS, secondo il presente trovato; e

la Fig. 6 è un grafico dei segnali di ingresso e uscita del circuito convertitore da logica bipolare a logica CMOS secondo il presente trovato.

Si noti che in tutte le figure a numeri di riferimento uguali corrispondono elementi uguali.

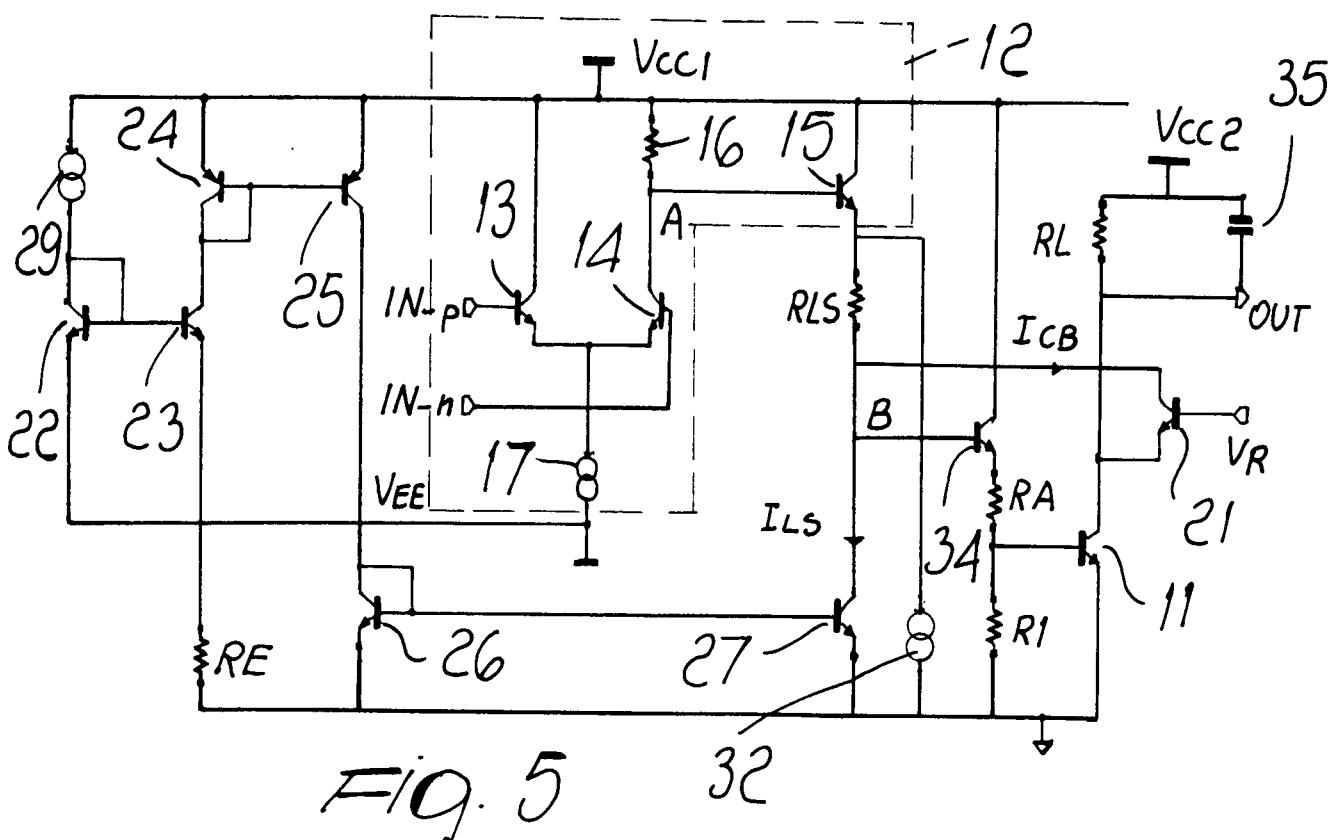

Con riferimento alle figure citate, il circuito convertitore secondo il presente trovato, illustrato nelle figure 4 e 5 comprende un primo stadio 12 costituito da transistori 13, 14, 15 (primo, secondo e terzo transistor), di tipo NPN, da un primo resistore 16 e da un primo generatore di corrente 17, ed è similare ad una porta ECL tranne per il fatto che l'uscita non è qui differenziale.

I transistori 13 e 14 sono collegati a emettitore accoppiato e il transistore 13 ha il suo collettore collegato alla tensione di alimentazione  $V_{CC1}$  così come il transistore 14 il quale però ha interposto il resistore 16.

Il terminale di base del transistore 15 è collegato al terminale di collettore del transistore 14, in corrispondenza del punto A illustrato nelle Figg. 4 e 5.

Un circuito traslatore di livello di tipo dinamico, 18, è collegato all'emettitore del transistore 15.

Collegato in serie al traslatore di livello 18 vi è un secondo resistore  $R_A$  il quale è collegato alla base di un quarto transistore 11 il cui emettitore è collegato a massa.

Il resistore  $R_A$  imposta la corrente di base del transistore 11 nello stato basso.

Il quarto transistore 11 e un terzo resistore,  $R_L$ , costituiscono il ramo di uscita che è alimentato alla tensione di alimentazione  $V_{cc2}$ .

Un quinto transistore 21, di retroazione, di tipo NPN ha il collettore collegato al traslatore di livello 18, l'emettitore collegato al collettore del transistore 11 e la base collegata alla tensione di riferimento  $V_R$ .

Il transistore 21 chiude l'anello di retroazione che include il traslatore di livello 18, il resistore  $R_L$  e il transistore 11.

Nella Fig. 5 è illustrato in dettaglio il circuito secondo il trovato con il traslatore dinamico di livello 18 esplicitato.

Il circuito traslatore di livello 18 comprende tre rami circuitali collegati ciascuno tra la linea di alimentazione  $V_{cc1}$  e la linea di massa: il primo ramo comprende un sesto transistore 22 ed un generatore di corrente 29, il secondo ramo comprende settimo ed ottavo transistore 23 e 24 ed un quarto resistore  $R_E$  mentre il terzo ramo comprende nono e decimo

transistore 25 e 26 ed un undicesimo transistore 27 ad esso collegato. I transistori 22, 23, 26 e 27 sono di tipo NPN.

In dettaglio, il transistore 22 e il transistore 23 hanno il terminale di base in comune e il transistore 22 ha il collettore collegato alla base e alla linea di alimentazione  $V_{cc1}$  con un generatore di corrente 29; il suo emettitore è invece collegato alla tensione  $V_{EE}$ .

Il transistore 23 ha invece l'emettitore collegato alla linea di massa tramite un quinto resistore  $R_E$ , e il suo collettore collegato al collettore del transistore 24 il quale ha base e collettore collegati in comune; l'emettitore del transistore 24 è invece collegato alla linea di alimentazione  $V_{cc1}$ .

La base del transistore 24 è anche collegata alla base del transistore 25 il cui emettitore è collegato alla linea di alimentazione  $V_{cc1}$  ed il cui collettore è collegato al collettore del transistore 26; il collettore del transistore 26 è collegato alla base del medesimo transistore e il suo emettitore è invece collegato alla linea di massa.

La base del transistore 26 è collegata alla base del transistore 27 il cui emettitore è collegato a massa; il collettore del transistore 27 è invece collegato all'emettitore del transistore 15 con l'interposizione di un quinto resistore  $R_{LS}$ .

Un ulteriore resistore  $R_1$  è collegato tra la base del transistore 11 e la linea di massa e un secondo generatore di corrente 32 è collegato tra la linea di massa e l'emettitore del transistore 15.

Il resistore  $R_1$  ha la funzione di permettere una scarica veloce della base del transistore 11 nella transizione da stato basso ad alto.

Il generatore di corrente 32 garantisce invece una corrente di polarizzazione minima al transistore 15.

Un ulteriore transistore 34 è collegato con il collettore alla linea di alimentazione  $V_{cc1}$ , con l'emettitore ad un capo del resistore  $R_A$  e con la base al collettore del transistore 27.

Un condensatore di carico 35 è infine collegato in parallelo al resistore  $R_L$ .

Il terminale di uscita OUT costituisce il terminale di gate di una porta CMOS mentre i terminali IN-n e IN-p sono i terminali di uscita di un circuito bipolare.

Con riferimento alle sopra citate figure, il funzionamento del circuito secondo il trovato è come segue.

Quando l'ingresso (terminali IN-p e IN-n) è basso, la tensione in corrispondenza del nodo A diventa bassa e la sua variazione attraverso il resistore 15 e il circuito traslatore di livello è replicata in corrispondenza del nodo B. Se la tensione del nodo B diventa quindi bassa seguendo la tensione del nodo A e raggiunge un valore sufficientemente basso, il transistore 11 si spegne e la tensione di uscita sul ramo di uscita OUT del circuito assume lo stato alto che è uguale a  $V_{cc2}$  (tensione di alimentazione della porzione a logica C-MOS).

Nello stato alto il transistore 21 che chiude l'anello di retroazione sul circuito traslatore di livello è spento.

Quando invece l'ingresso è alto, le tensioni in corrispondenza dei nodi A e B sono pure alte e l'uscita OUT del circuito, contrariamente al caso precedente, diventa bassa.

Il valore minimo che l'uscita OUT può assumere,  $V_{OMIN}$  è impostato dalla tensione di riferimento  $V_R$  immessa alla base del transistore 21, in base alla seguente equazione

$$V_{OMIN} = V_R - V_{BE2I} \quad (1)$$

dove  $V_{BE21}$  è la tensione tra base ed emettitore del transistore 21.

Quando la tensione di uscita raggiunge il valore  $V_{OMIN}$ , il transistore 21 si accende (entra in conduzione) e la corrente sul resistore  $R_L$  raggiunge il valore massimo,  $I_{OMAX}$ , che è dato dalla seguente relazione

$$I_{OMAX} = \frac{V_{CC2} - V_{OMIN}}{R_I} \quad (2)$$

La tensione  $V_{OMIN}$  è impostata al valore massimo ammissibile per lo stato basso di una porta CMOS.

La corrente di collettore  $I_{C11}$  del transistore 11 è data da

$$I_{C11} = \beta_{FII} \left[ \frac{V_B - V_{BE34} - V_{BE11}}{R_A} - \frac{V_{BE11}}{R_I} \right] \quad (3)$$

dove  $V_B$  è la tensione in corrispondenza del nodo B e  $V_{BE11}$  è la tensione tra base ed emettitore del transistore 11.

Il valore della corrente  $I_{C11}$  è impostato dall'anello di retroazione che agendo sul circuito traslatore di livello 18 riduce la tensione  $V_B$  e porta il transistore 11 nella regione attiva.

In questo modo è pure ridotta la quantità di carica nella regione di

base del transistore 11 consentendo di ottenere una prestazione ad alta velocità del transistore stesso.

Inoltre, il controllo della corrente nel transistore 11 consente di ridurre il consumo di potenza evitando che questo raggiunga un valore eccessivo.

Considerando ora la Fig. 5 in cui è illustrato in dettaglio il circuito traslatore di livello 18, la corrente,  $I_{LS}$ , che passa nel resistore  $R_{LS}$  e la tensione  $V_{LS}$  ai suoi capi sono rispettivamente date, nello stato alto (con  $I_{C21}=0$ ) da

$$I_{LS} = \frac{V_{EE}}{R_E} \quad (4a)$$

$$V_{LS} = V_{EE} \frac{R_{LS}}{R_E} \quad (4b)$$

Dato che la tensione  $V_{CC1}-V_{EE}$  è fissata da un regolatore di tensione, la variazione di  $V_{CC1}$  influenza  $V_{EE}$  e quindi  $V_{LS}$ , mantenendo in questo modo costante la tensione di base del transistore 34.

La corrente di pilotaggio del transistore 11 e la prestazione dell'intero circuito non dipendono quindi dalla variazione della tensione  $V_{CC1}$ .

In particolare, una caratteristica peculiare del trovato è quella del controllo di corrente realizzabile con il circuito sopra menzionato.

Infatti, velocità, stabilità e consumo di potenza dipendono fortemente dalla corrente di collettore  $I_{C11}$  del transistore 11 e dalla corrente di collettore  $I_{C21}$  del transistore 21 nello stato basso.

La corrente  $I_{C11}$  e la corrente  $I_{C21}$  sono definite dall'azione combi-

nata dell'anello di retroazione e del circuito traslatore di livello 18.

Nello stato alto la corrente  $I_{C21}$  è uguale a zero e la tensione  $V_{LS}$  è determinata solamente dalla corrente  $I_{LS}$ . Nello stato basso invece la tensione  $V_{LS}$  e quindi la tensione di base del transistore 34 sono determinate da entrambe le correnti  $I_{LS}$  e  $I_{C21}$  ( $I_{C21}$  produce una caduta di tensione addizionale sul resistore  $R_{LS}$ ). Dato che la corrente in  $R_L$  è impostata dall'equazione (2) ( $I_{OMAX} = I_{RL}$ ) secondo i requisiti del circuito, la corrente  $I_{C21}$  può essere facilmente calcolata come:

$$I_{C21} \approx \frac{R_A}{\beta_{FII} R_{LS}} \left[ \beta_{FII} \left( \frac{V_B - V_{BE34} - V_{BE11}}{R_A} - \frac{V_{BE11}}{R_I} \right) - I_{RL} \right] \quad (5)$$

dove la tensione  $V_B$  è:

$$V_B = V_{CCI} - V_{BE15} - I_{LS} R_{LS} \quad (6)$$

con  $V_{BE15}$  rappresentante la tensione tra base ed emettitore del transistore 15.

Nello stato basso l'anello di retroazione è attivo e deve essere garantito un comportamento stabile del circuito. Inoltre, si deve impostare una frequenza di guadagno unitario opportuna per il guadagno di anello. La stabilità e la velocità possono essere definite utilizzando la funzione di trasferimento  $T(S)$  del guadagno di anello e quindi si ha che

$$T(S) = g_{m11} R_{LS} \frac{r_{\pi11}}{R_{11}} \frac{1}{1 + S r_{\pi11} C_{\pi11}} \frac{1}{1 + S \frac{g_{m21}}{C_L}} \quad (7)$$

dove si è assunto che

$$R_L \gg \frac{I}{g_{m21}} \quad R_I, R_A \gg r_{\pi II}$$

Il polo dominante è dovuto alla resistenza di ingresso e dalla capacità del transistore 11 mentre il secondo polo è determinato dalla transconduttanza  $g_{m21}$  del transistore 21 e dalla condensatore di carico  $C_{\pi II}$ . Allo scopo di garantire il margine di fase richiesto, si devono impostare correttamente la transconduttanza  $g_{m21}$  e la corrente  $I_{C21}$ .

La frequenza di guadagno unitario del guadagno di anello è data da

$$f_T = \frac{I}{2\pi} \frac{g_{m11} R_{LS}}{R_A C_{\pi II}} \quad (8)$$

A causa della corrente elevata che scorre nel transistore 11 nello stato basso, si può assumere  $C_{\pi 11}$  uguale al condensatore di diffusione e la frequenza di guadagno unitaria è data da

$$f_T \approx \frac{1}{2\pi} \frac{R_{LS}}{R_A} \frac{1}{\tau_F} \quad (9)$$

dove  $\tau_F$  è il tempo di transizione del transistore 11.

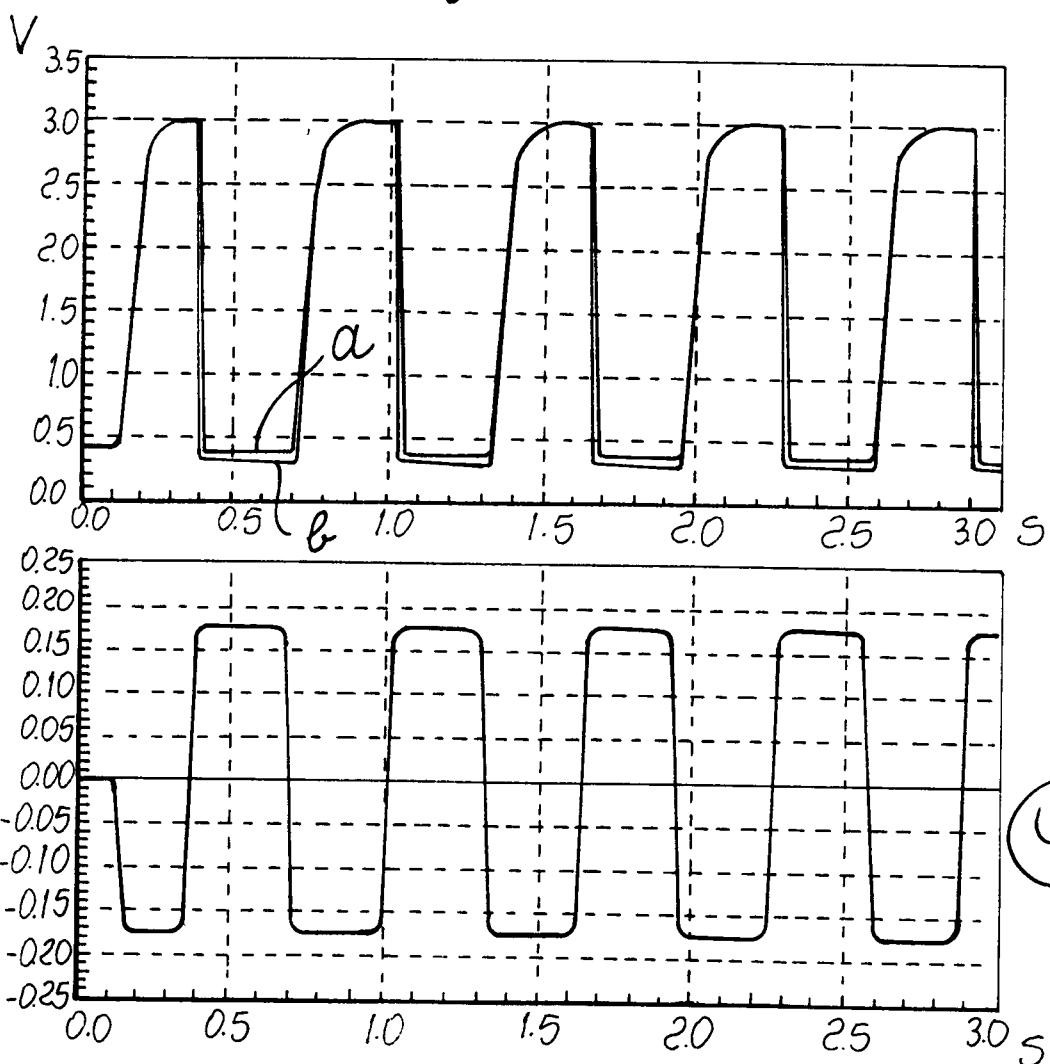

La figura 6 è un grafico che illustra il comportamento del circuito secondo il trovato e in particolare la porzione inferiore della figura illustra un segnale di ingresso proveniente da una porzione di circuito in logica bipolare con un'alimentazione  $V_{CC1}$ , mentre la porzione superiore della medesima figura mostra la tensione di uscita in corrispondenza del

nodo OUT del circuito secondo il trovato, per due valori differenti della tensione di alimentazione  $V_{CC1}$  (le curve a e b del grafico superiore sono ottenute rispettivamente con due differenti valori della tensione di alimentazione  $V_{CC1}$ ).

Come si può notare dal grafico, le curve a e b sono praticamente sovrapposte ad indicare che il valore della tensione di uscita del circuito è sostanzialmente invariante con il variare della tensione di alimentazione della porzione di logica bipolare a monte del circuito secondo il trovato.

Si è in pratica constatato come il circuito convertitore da logica bipolare a logica CMOS secondo il trovato assolva pienamente il compito prefissato in quanto consente di realizzare un convertitore la cui uscita sia indipendente dalla variazione della tensione di alimentazione  $V_{CC1}$  della porzione di logica bipolare a cui è interfacciato a monte il circuito.

Inoltre, la frequenza operativa e il consumo di potenza del circuito secondo il trovato, rispetto a soluzioni note, sono migliorati.

Il circuito convertitore così concepito è suscettibile di numerose modifiche e varianti, tutte rientranti nell'ambito del concetto inventivo; inoltre tutti i dettagli potranno essere sostituiti da altri elementi tecnicamente equivalenti.

In pratica, i materiali impiegati, purchè compatibili con l'uso specifico, nonchè le dimensioni, potranno essere qualsiasi secondo le esigenze e lo stato della tecnica.

Laddove le caratteristiche tecniche nelle rivendicazioni sono seguite da riferimenti numerici e/o sigle, detti riferimenti numerici e/o sigle

sono stati aggiunti all'unico scopo di aumentare l'intelligibilità delle rivendicazioni e pertanto detti riferimenti numerici e/o sigle non producono alcun effetto sull'ambito di ciascun elemento identificato solo a titolo indicativo da detti riferimenti numerici e/o sigle.

\* \* \* \* \*

## RIVENDICAZIONI

1. Circuito convertitore da logica bipolare a logica CMOS ad elevata velocità, comprendente uno stadio di ingresso costituito da un amplificatore differenziale destinato ad essere collegato ad una porzione circuitale di logica bipolare e alimentato dalla tensione di alimentazione della porzione di logica bipolare, e uno stadio di uscita alimentato dalla tensione di una porzione circuitale di logica CMOS, caratterizzato dal fatto che tra detto stadio di ingresso e detto stadio di uscita è interposto un circuito traslatore di livello dinamico, detto stadio di uscita essendo collegato alla porzione circuitale di logica CMOS.

2. Circuito secondo la rivendicazione 1, caratterizzato dal fatto che detto stadio di ingresso è costituito da un primo ed un secondo transistore collegati ad emettitore accoppiato, ed un terzo transistore collegato con la sua base al collettore di detto primo transistore, detto terzo transistore essendo collegato con il suo emettitore a detto circuito traslatore di livello dinamico, detto primo, secondo e terzo transistore essendo collegati con i loro collettori a detta prima tensione di alimentazione.

3. Circuito secondo la rivendicazione 2, caratterizzato dal fatto che alle basi di detto primo e secondo transistore è applicato un segnale di ingresso proveniente da detta porzione circuitale di logica bipolare, agli emettitori di detto primo e secondo transistore essendo collegato un primo generatore di corrente.

4. Circuito secondo la rivendicazione 2, caratterizzato dal fatto che un primo resistore è interposto tra il collettore di detto secondo transi-

store e detta prima tensione di alimentazione.

5. Circuito secondo la rivendicazione 2, caratterizzato dal fatto di comprendere un secondo resistore interposto tra detto circuito traslatore di livello dinamico e detto stadio di uscita.

6. Circuito secondo la rivendicazione 5, caratterizzato dal fatto che detto stadio di uscita comprende un quarto transistore e un terzo resistore collegati in serie.

7. Circuito secondo la rivendicazione 6, caratterizzato dal fatto di comprendere un quinto transistore collegato ad un regolatore di tensione e costituente, con detto quarto transistore, detto secondo resistore e detto circuito traslatore di livello dinamico, un anello di retroazione della tensione di uscita di detto circuito convertitore.

8. Circuito secondo la rivendicazione 7, caratterizzato dal fatto che detto quinto transistore ha l'emettitore collegato al collettore di detto quarto transistore e il collettore collegato a detto circuito traslatore di livello dinamico.

9. Circuito secondo la rivendicazione 8, caratterizzato dal fatto che detto circuito traslatore di livello dinamico comprende un sesto transistore interposto tra detta prima tensione di alimentazione e detto primo generatore di corrente, un settimo ed un ottavo transistore collegati a collettore accoppiato e interposti tra detta prima linea di alimentazione e un quarto resistore collegato a massa, un nono ed un decimo transistore collegati a collettore comune ed interposti tra detta prima tensione di alimentazione e massa, e un undicesimo transistore collegato in serie ad un quinto resistore il quale è a sua volta collegato all'emettitore di

detto terzo transistore.

10. Circuito secondo la rivendicazione 9, caratterizzato dal fatto che la base di detto ottavo transistore è collegata al collettore del medesimo transistore e alla base di detto nono transistore.

11. Circuito secondo la rivendicazione 9, caratterizzato dal fatto che la base di detto decimo transistore è collegata alla base di detto undicesimo transistore il cui emettitore è collegato a massa tramite un resistore.

12. Circuito secondo la rivendicazione 9, caratterizzato dal fatto che un ulteriore transistore è collegato con il collettore a detta prima tensione di alimentazione, con l'emettitore a detto secondo resistore e con la base al collettore di detto undicesimo transistore.

13. Circuito secondo la rivendicazione 9, caratterizzato dal fatto che un secondo generatore di corrente è collegato tra massa e l'emettitore di detto terzo transistore.

14. Circuito secondo la rivendicazione 6, caratterizzato dal fatto di comprendere inoltre un ulteriore resistore collegato tra la base di detto quarto transistore e massa.

15. Circuito secondo la rivendicazione 9, caratterizzato dal fatto che il collettore di detto quinto transistore è collegato al collettore di detto undicesimo transistore.

16. Circuito secondo la rivendicazione 9, caratterizzato dal fatto che la base e il collettore di detto sesto transistore sono collegati in comune.

17. Circuito secondo la rivendicazione 9, caratterizzato dal fatto

che la base ed il collettore di detto decimo transistore sono collegati in comune.

18. Circuito secondo una o più delle rivendicazioni precedenti, caratterizzato dal fatto di comprendere una o più delle caratteristiche descritte e/o illustrate.

Il Mandatario:

- Dr. Ing. Guido MODIANO -

MI 97 A 1333

Fig. 1

Fig. 2

FIG. 3

FIG. 4

MI 97 A 1333

TAV. III