(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6054070号

(P6054070)

(45) 発行日 平成28年12月27日(2016.12.27)

(24) 登録日 平成28年12月9日(2016.12.9)

(51) Int.Cl.

F 1

|             |           |      |        |      |

|-------------|-----------|------|--------|------|

| H01L 21/338 | (2006.01) | H01L | 29/80  | H    |

| H01L 29/778 | (2006.01) | H01L | 21/28  | 301B |

| H01L 29/812 | (2006.01) | H01L | 21/283 | C    |

| H01L 21/28  | (2006.01) | H01L | 21/283 | B    |

| H01L 21/283 | (2006.01) | H01L | 21/90  | M    |

請求項の数 10 外国語出願 (全 22 頁) 最終頁に続く

(21) 出願番号

特願2012-138007 (P2012-138007)

(22) 出願日

平成24年6月19日 (2012.6.19)

(65) 公開番号

特開2013-12735 (P2013-12735A)

(43) 公開日

平成25年1月17日 (2013.1.17)

審査請求日

平成27年4月10日 (2015.4.10)

(31) 優先権主張番号

61/498, 951

(32) 優先日

平成23年6月20日 (2011.6.20)

(33) 優先権主張国

米国 (US)

(31) 優先権主張番号

61/526, 107

(32) 優先日

平成23年8月22日 (2011.8.22)

(33) 優先権主張国

米国 (US)

(73) 特許権者 591060898

アイメック

1 M E C

ペルギー、ペーー・3001ルーヴアン、カ

ペルドリーフ75番

(74) 代理人 100101454

弁理士 山田 阜二

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100100479

弁理士 竹内 三喜夫

(74) 代理人 100112911

弁理士 中野 晴夫

最終頁に続く

(54) 【発明の名称】 HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極とソースドレイン・オーミック接触を有するIII族窒化物HEMTを製造する方法において、

- a ) 基板(101)を提供するステップと、

- b ) III族窒化物層のスタック(I)を基板(101)上に形成するステップと、

- c ) 窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>を含み、スタック(I)の上方層(203、204)に対して上に位置すると共に当接する第1パッシベーション層(301)を形成するステップと、

- d ) 第1パッシベーション層(301)に対して上に位置すると共に当接する誘電体層(302)を形成するステップと、

- e ) 窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>を含み、誘電体層(302)に対して上に位置すると共に当接する第2パッシベーション層(303)を形成し、第2パッシベーション層(303)が、低圧化学気相成長法及び/又は有機金属化学気相成長法等の化学気相成長法によって450より高い温度で堆積されるステップと、

- f ) 第1パッシベーション層(301)と誘電体層(302)の少なくとも一部を含むゲート誘電体が形成されるように、ソースドレイン・オーミック接触とゲート電極(601)を形成するステップと、

を含み、

ゲート電極を形成するステップが、

10

20

第 2 パッシベーション層（303）を誘電体層に向けて選択的にエッチングすることによって、ゲートトレーニングをパターニングするステップと、メタルゲート層を堆積及びパターニングすることによって、少なくともゲートトレーニングにおいてゲート電極（601）を形成するステップと、を更に含み、

ゲートトレーニングを形成するステップが、誘電体層を少なくとも部分的にエッチングするステップと、ゲート電極を形成する前に第 2 誘電体層を再堆積するステップと、を更に含む方法。

【請求項 2】

第 1 パッシベーション層（301）が、その場でスタック（I）に堆積される請求項 1 に記載の方法。 10

【請求項 3】

ステップ c )、d ) と e ) が、その場で有機金属化学気相成長法によって行われる請求項 1 又は 2 に記載の方法。

【請求項 4】

ソースドレイン・オーミック接触を形成するステップが、

第 2 パッシベーション層（303）、誘電体層（302）及び第 1 パッシベーション層（301）を選択的にエッチングすることによって、ソースドレイン・オーミック接触領域をパターニングするステップと、

メタル層（401）を堆積及びパターニングすると共に、オーミック合金を形成することによって、オーミック接触を形成するステップと、 20

を更に備える請求項 1 乃至 3 のいずれかに記載の方法。

【請求項 5】

メタル層をパターニングするステップが、メタル層の乾式エッチングプロセスを含み、メタル層の乾式エッチングプロセスが、第 2 パッシベーション層を部分的に消費する請求項 4 に記載の方法。

【請求項 6】

メタルゲート層をパターニングするステップが、メタルゲート層の乾式エッチングプロセスを含み、メタルゲート層の乾式エッチングプロセスが、第 2 パッシベーション層（303）を部分的に消費する請求項 1 に記載の方法。 30

【請求項 7】

ソースドレイン・オーミック接触とゲート電極のどちらが最初に形成されるかに応じて、誘電体キャップ層（501）をソースドレイン・オーミック接触又はゲート電極に形成して、後のメタル層の堆積又はメタルゲート層の堆積中の、夫々の、ソースドレイン・オーミック接触又はゲート電極を保護するステップを更に含む請求項 1 乃至 6 のいずれかに記載の方法。

【請求項 8】

誘電体層（302）が、Al、好ましくは、Al<sub>2</sub>O<sub>3</sub> 及び / 又は AlN を含む請求項 1 乃至 7 のいずれかに記載の方法。

【請求項 9】

第 1 パッシベーション層（301）が、少なくとも 0.5 nm の厚さを有する請求項 1 乃至 8 のいずれかに記載の方法。 40

【請求項 10】

第 2 パッシベーション層（303）が、少なくとも 50 nm の厚さを有する請求項 1 乃至 9 のいずれかに記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。より詳しくは、本発明は、HEMT 装置を製造する方法とその HEMT 装置に関する。

【背景技術】 50

## 【0002】

ガリウム窒化物をベースにした高電子移動度トランジスタ（HEMT）は、その高速で低ロスのスイッチング、高い降伏電圧と高い動作電圧により、高周波用途に、最近は高パワー用途に対して関心を集めている。

## 【0003】

しかしながら、ショットキゲートを有するがパッシベーションを有しないAlGaN/GaN・HEMTは、高いゲートリーク及び電流分散と各種の信頼性の問題を抱える。

## 【0004】

EP1612866は、特に、現場で、有機金属化学気相成長（MOCVD）リアクタ内で高温でIII族窒化物層に堆積される時の窒化シリコンが、AlGaNのリラクゼーション、クラッキングと表面粗さを低減する高品質パッシベーション層を開示する。それは、又、頂部AlGaN界面における電荷を中和すると共に、低界面準位密度を有する高品質界面を形成する。10

## 【0005】

パワー用途では、オフ状態での電力消費を最小化するために、ゲートリーク電流を減少させることが重要である。高速のオンオフスイッチングを得るために、大きなゲートバイアススイングが必要である。この理由により、後方及び前方のゲートバイアシングの両方において低ゲートリークが必須であり、後者は、特に、エンハンスマントモード（eモード）に対して重要である。ゲートリーク電流を抑制するために、ゲート誘電体が、しばしば、ショットキゲートとAlGaNバリアの間に挿入され、金属・絶縁体・半導体（MIS）トランジスタが製作される。20

## 【0006】

しかしながら、より高いトランスコンダクタンスを得ることができるので、理想的なゲート誘電体は、高誘電率を有する。更に、リークを抑制するために、大きなバンドオフセットエネルギーが、絶縁体/AlGaN界面において必要である。この観点から、Si<sub>3</sub>N<sub>4</sub>の誘電率（~7）は、AlGaN化合物のそれ（~9）と比較して十分に高くない。又、Si<sub>3</sub>N<sub>4</sub>のバンドギャップ（~5eV）は、AlGaNのそれ（~4eV）よりもはるかに高いことはない。

## 【0007】

Al<sub>2</sub>O<sub>3</sub>は、その大きなバンドギャップ（~7eV）、相対的に高い誘電率（~9）と高い降伏電界（~10MV/cm）により、パワーMIS装置に適用し得る最も魅力的な誘電体である。最高品質のAl<sub>2</sub>O<sub>3</sub>膜は、原子層堆積（ALD）によって堆積されるが、AlGaN界面における界面準位密度（DIT）は、典型的に、1×10<sup>-2</sup>cm<sup>-2</sup>eV<sup>-1</sup>以上と非常に高い。30

## 【0008】

前田等（Appl Phys Lett 87, 073504 (2005)）は、Si<sub>3</sub>N<sub>4</sub>が、AlGaNと接触すると共に、ゲート領域上だけに、即ち、ゲートメタルの下に堆積されたAl<sub>2</sub>O<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>ゲート絶縁体を有するMIS-HFETを開示する。ソース（ドレイン）領域とゲート領域の間に、Si<sub>3</sub>N<sub>4</sub>層とSiO<sub>2</sub>層が、連続的に表面パッシベーションとして堆積された。全ての絶縁体が、電子サイクロトロン共鳴（ECR）スパッタリングによって堆積された。40

## 【0009】

今日、GaNトランジスタは、典型的に、2インチ又は3インチの直径のSiC又はサファイア基板という小領域上に製作される。オーミックソース-ドレインとショットキゲート電極は、通常、コンタクトリソグラフィとそれに続くメタルリフトオフによってパターニングされる金含有メタライゼーションスタックによって形成される。

## 【0010】

しかしながら、シリコン技術と競争するために、コストの削減が基本要因である。この理由により、150mm、200mm、又は300mmの大径のシリコン基板上のGaNエピタキシャル成長材料が開発されている。新しいトランジスタ製作技術は、ステップ50

ーリソグラフィ、金不使用メタライゼーションと乾式エッチングによるメタルパターニングを使用して Si - CMOS コンパチブルでなければならない。

#### 【0011】

上記の方法のいずれも、Si - CMOS コンパチブルなやり方に使用するのに適しない。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0012】

従って、例えば、ステッパー・リソグラフィ、金不使用メタライゼーション及び／又は乾式エッチングによるメタルパターニングの使用を可能にするように、Si - CMOS プロセス技術とコンパチブルな HEMT 装置製造方法を得ることが望ましい。10

#### 【課題を解決するための手段】

#### 【0013】

ゲート電極とソースドレイン・オーミック接触を有するIII族窒化物HEMTを製造する方法であって、a) 基板を提供するステップと、b) III族窒化物層のスタックを基板上に形成するステップと、c) 窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>からなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層を形成し、第1パッシベーション層が、好ましくは、現場でスタッ�に堆積されるステップと、d) 第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、e) 窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>からなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450より高い温度で堆積されるステップと、f) 第1パッシベーション層と誘電体層の少なくとも一部を含むゲート誘電体が形成されるように、ソースドレイン・オーミック接触とゲート電極を形成するステップとを備える方法が提供される。第2パッシベーション層は、化学気相成長法等の堆積手法、例えば、低圧化学気相成長法(LPCVD)及び／又は有機金属化学気相成長法(MOCVD)によって450より高い温度で堆積される。20

#### 【0014】

一実施形態で、ステップc)、d)とe)が、現場でMOCVDによって行われる。

#### 【0015】

一実施形態で、ソースドレイン・オーミック接触を形成することが、第2パッシベーション層、誘電体層と第1パッシベーション層を選択的にエッチングすることによって、ソースドレイン・オーミック接触領域をパターニングするステップと、メタル層を堆積及びパターニングすると共に、オーミック合金を形成することによって、オーミック接触を形成するステップとを更に備える。好ましくは、メタル層をパターニングすることが、メタル層の乾式エッチングプロセスを備え、メタル層の乾式エッチングプロセスが、第2パッシベーション層を部分的に消費する。

#### 【0016】

一実施形態で、ゲート電極を形成することが、第2パッシベーション層を誘電体層に向けて選択的にエッチングすることによって、ゲートトレンチをパターニングするステップと、メタルゲート層を堆積及びパターニングすることによって、ゲートトレンチにおいてゲート電極を形成するステップとを更に備える。好ましくは、メタルゲート層のパターニングは、メタルゲート層の乾式エッチングプロセスを備え、メタルゲート層の乾式エッチングプロセスは、第2パッシベーション層を部分的に消費する。40

#### 【0017】

一実施形態で、方法は、ソースドレイン・オーミック接触とゲート電極のどちらが最初に形成されるかに応じて、誘電体キャップ層をソースドレイン・オーミック接触又はゲート電極に形成して、後のメタル層の堆積又はメタルゲート層の堆積中の、夫々の、ソースドレイン・オーミック接触又はゲート電極を保護するステップを更に備える。

#### 【0018】

10

20

30

40

50

一実施形態で、ゲートトレンチを形成することが、誘電体層を少なくとも部分的にエッチングするステップと、ゲート電極を形成する前に第2誘電体層を堆積するステップとを更に備える。

【0019】

一実施形態で、誘電体層がA1からなる。

【0020】

一実施形態で、誘電体層は、Al<sub>2</sub>O<sub>3</sub>、AlN、AlSiN及びその混合物又は組合せからなる群から選択される。

【0021】

一実施形態で、誘電体層は、Al<sub>2</sub>O<sub>3</sub>からなる。 10

【0022】

一実施形態で、誘電体層は、AlNからなる。

【0023】

一実施形態で、第1パッシベーション層が、少なくとも0.5nmの厚さを有する。

【0024】

一実施形態で、第2パッシベーション層が、少なくとも50nmの厚さを有する。

【0025】

又、III族窒化物HEMT装置を製作用の工学基板であって、a)基板と、b)基板上のIII族窒化物層のスタックと、c)窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>からなり、II族窒化物層のスタック(I)の上方層に対して上に位置すると共に当接する第1パッシベーション層と、d)高k誘電体材料からなり、第1パッシベーション層に対して上に位置すると共に当接する誘電体層と、e)窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>、好ましくは、LPCVD窒化シリコン、より好ましくはLPCVD・Si<sub>3</sub>N<sub>4</sub>からなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層とを備える工学基板が提供される。よって、好ましくは、窒化シリコンは、化学気相成長法等の堆積手法、例えば、低圧化学気相成長法(LPCVD)及び/又は有機金属化学気相成長法(MOCVD)によって450より高い温度で堆積される。 20

【0026】

又、本発明の方法で得られて、基板の活性領域上に形成されると共に、ゲート電極とソースドレイン接点を備えるIII族窒化物HEMT装置であって、a)基板と、b)基板上のIII族窒化物層のスタックと、c)ソースドレイン接点の下を除く活性領域の全てにおいて、スタックの上方層に対して上に位置すると共に当接し、更に、窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>からなる第1パッシベーション層と、d)ソースドレイン接点の下を除く活性領域の全てにおいて、第1パッシベーション層に対して上に位置すると共に当接し、更に、高k誘電体材料からなる誘電体層と、e)ゲート電極の下とソースドレイン接点の下を除く活性領域の全てにおいて、誘電体層に対して上に位置すると共に当接し、更に、窒化シリコン、好ましくは、Si<sub>3</sub>N<sub>4</sub>、好ましくは、LPCVD窒化シリコン、より好ましくはLPCVD・Si<sub>3</sub>N<sub>4</sub>からなる第2パッシベーション層とを更に備えるIII族窒化物HEMT装置が提供される。よって、好ましくは、窒化シリコンは、化学気相成長法等の堆積手法、例えば、低圧化学気相成長法(LPCVD)及び/又は有機金属化学気相成長法(MOCVD)によって450より高い温度で堆積される。 30

【0027】

一実施形態で、第2パッシベーション層の窒化シリコン、好ましくは、LPCVD窒化シリコンは、3-8%の水素を含有すると共に、約2.9-3.1g/cm<sup>3</sup>の密度を有する。

【0028】

一実施形態で、誘電体層が、複数の層を備える。

【0029】

一実施形態で、誘電体層が、A1からなる。

【0030】

50

一実施形態で、誘電体層は、 $\text{Al}_2\text{O}_3$ 、 $\text{AlN}$ 、 $\text{AlSiN}$ 及びその混合物又は組合せからなる群から選択される。

【0031】

一実施形態で、誘電体層は、 $\text{Al}_2\text{O}_3$ からなる。

【0032】

一実施形態で、誘電体層は、 $\text{AlN}$ からなる。

【0033】

一実施形態で、第1パッシベーション層が、少なくとも $0.5\text{ nm}$ の厚さを有する。

【0034】

一実施形態で、第2パッシベーション層が、少なくとも $50\text{ nm}$ の厚さを有する。 10

【図面の簡単な説明】

【0035】

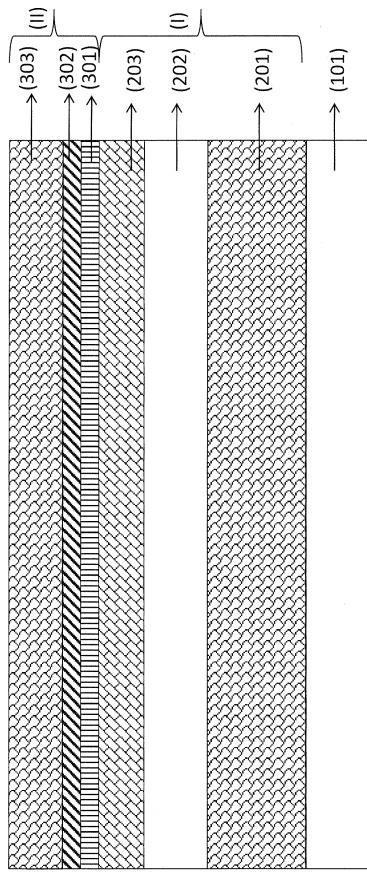

【図1】基板101と、III族窒化物層であるバッファ層201、チャネル層202とバリア層203を有するスタックIと、第1パッシベーション層301、誘電体層302と第2パッシベーション層303を有するパッシベーションスタックIIとを含む本発明の工学基板を概略的に示す。

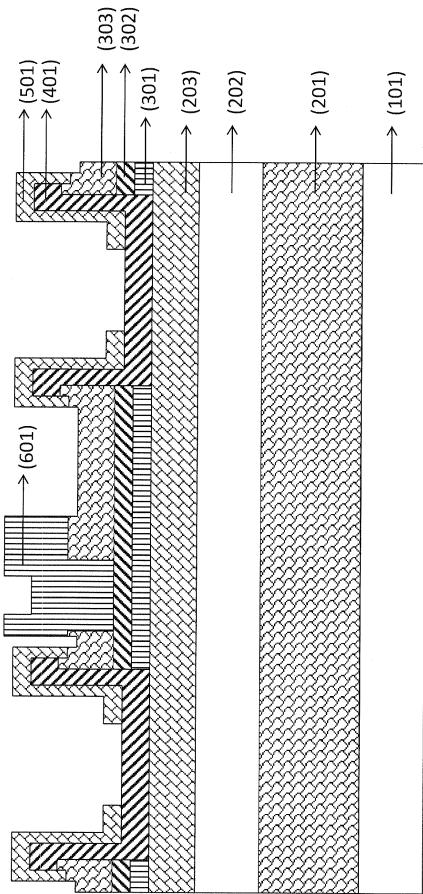

【図2】基板101、バッファ層201、チャネル層202、バリア層203、第1パッシベーション層301、誘電体層302、第2パッシベーション層303、オーミック接触用のメタル層401、誘電体キャップ層501とメタルゲート層/層のスタック601を含む本発明のIII族窒化物装置を概略的に示す。 20

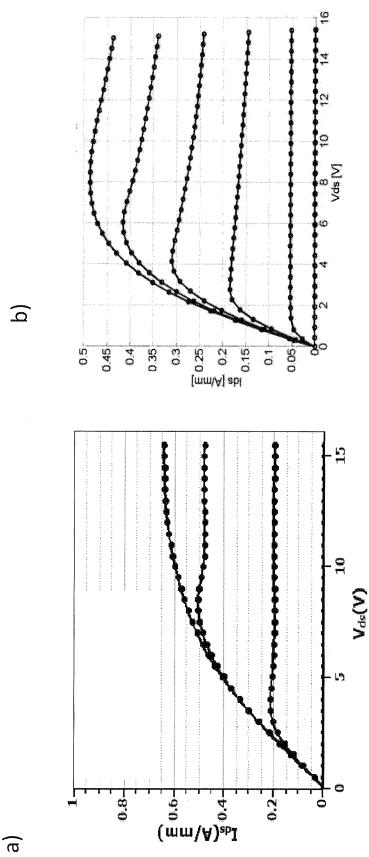

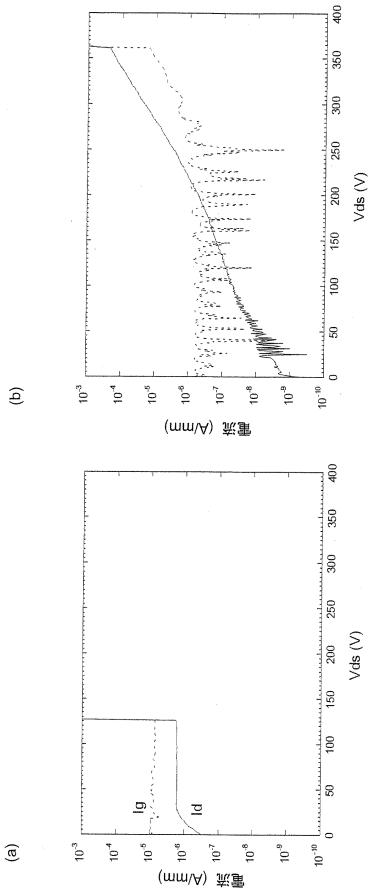

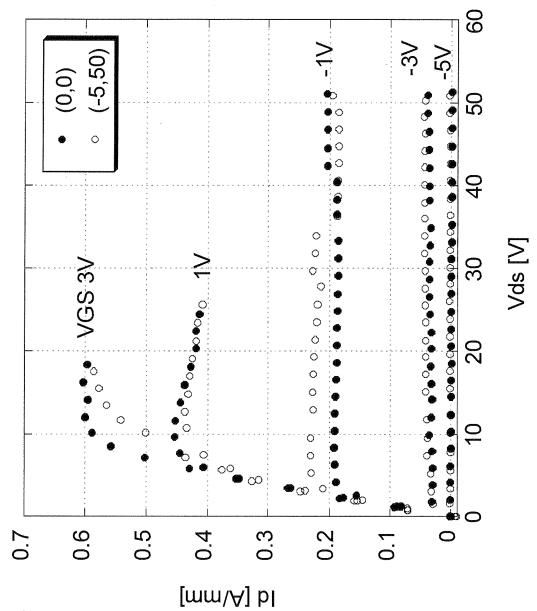

【図3】(a)は、HEMT "A" の $I_d - V_{ds}$ トランジスタ特性を示し、(b)は、HEMT "B" の $I_d - V_{ds}$ トランジスタ特性を示す。

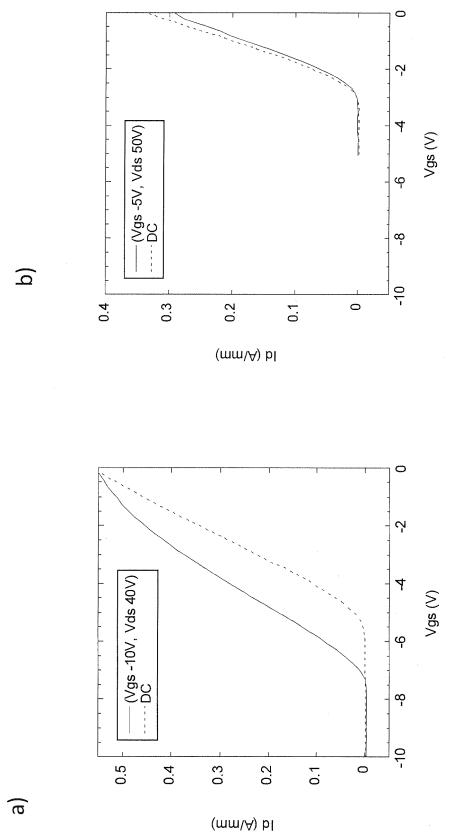

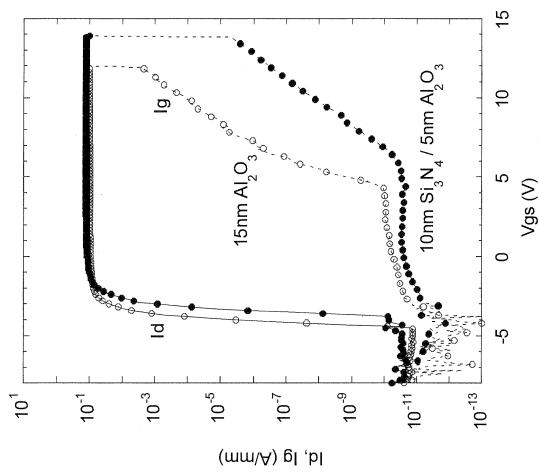

【図4】(a)は、HEMT "A" の $I_d - V_{gs}$ パルス特性を示し、(b)は、HEMT "B" の $I_d - V_{gs}$ パルス特性を示す。

【図5】(a)は、HEMT "A" のピンチオフにおける降伏を示し、(b)は、HEMT "B" のピンチオフにおける降伏を示す。

【図6】HEMT "C" (白抜き円)とHEMT "D" (黒べた円)の $I_d - V_{gs}$ 特性と $I_g - V_{gs}$ 特性を示す。

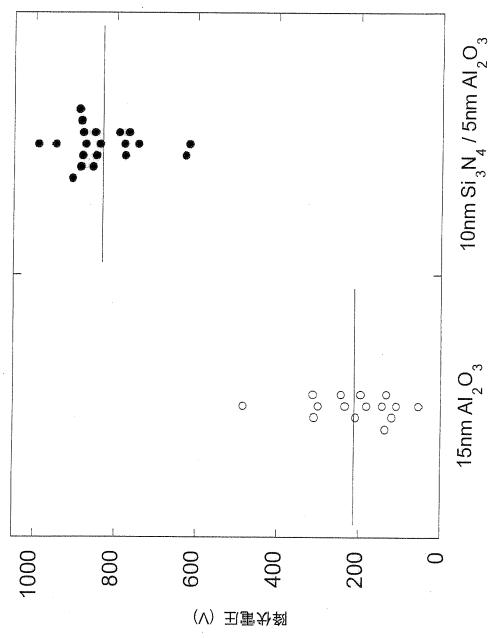

【図7】HEMT "C" (白抜き円)とHEMT "D" (黒べた円)の降伏電圧分布を示す。 30

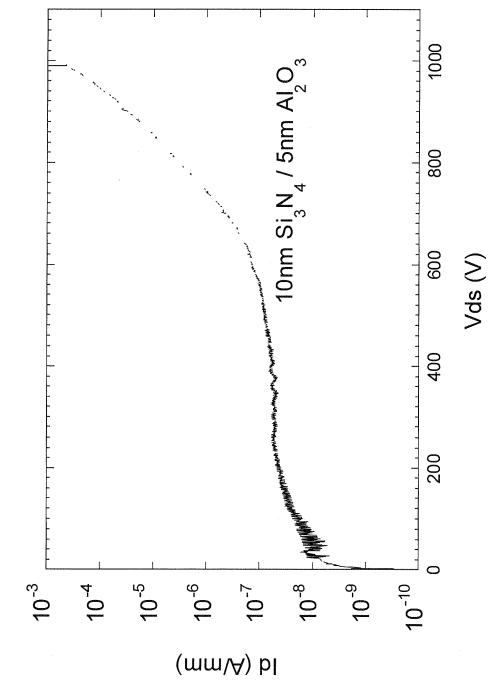

【図8】HEMT "D" のピンチオフにおける降伏を示す。

【図9】HEMT "D" の $I_d - V_{ds}$ パルス特性を示す。

【発明を実施するための形態】

【0036】

以下に、本発明を特定の実施の形態について図面を参照して説明するが、本発明は、それらに限定されず、請求項によってのみ限定される。図面は、概略的であって、限定的ではない。図面において、いくつかの要素の大きさが、誇張されて、図解目的のために尺度通りに描かれていない。寸法及び相対寸法は、本発明の実際の実施物に必ずしも対応しない。

【0037】

更に、明細書と請求項内の「第1」、「第2」、「第3」等の用語は、類似の要素を区別するために使用されていて、必ずしも、逐次的又は時間的な順序を記載するものではない。その用語は、適当な状況下で交換可能であり、本発明の実施の形態は、記載され又は図示されたものと異なる順で動作し得る。 40

【0038】

更に、明細書と請求項中の「頂部」、「底部」、「上に」、「下に」等の用語は、描写目的で使用されていて、必ずしも、相対位置を示すために使用されていない。そのように使用された用語は、適当な状況下で交換可能であり、本発明の実施の形態は、記載され又は図示されたとは異なる方位で動作し得る。

【0039】

更に、「好ましい」と呼ばれても、各種の実施の形態は、開示の範囲を限定するよりもむしろ本発明を実施するための例示として解釈すべきである。

#### 【0040】

請求項内で使用される用語「備える」(comprising)は、その後に列記された要素又はステップに限定されると解釈すべきでなく、他の要素又はステップを除外しない。それは、言及して挙げられた特徴、整数、ステップ又は部品の存在を指定するものと解釈する必要があるが、1個以上の他の特徴、整数、ステップ又は部品又はその群の存在又は追加を排除しない。よって、「AとBを備える装置」という表現の範囲は、部品AとBのみから成る装置に限定されるべきでなく、装置の列挙された部品がAとBだけであって、請求項は、更に、それらの部品の同等物を含むと解釈すべきである。

10

#### 【0041】

本発明の目的は、Si-CMOS製造フローとコンパチブルなIII族窒化物HEMTを製造する方法を提供することである。他の目的は、メタルパターニングのための乾式エッチング法を使用する金不使用プロセスフローとコンパチブルなIII族窒化物HEMTを製造する方法を提供することである。

#### 【0042】

別の目的は、Si-CMOSコンパチブルな製造フローに使用されるのに適したIII族窒化物HEMT製作用の工学基板を提供することである。更に別の目的は、改善された性能を有するIII族窒化物HEMT装置を提供することである。

#### 【0043】

例えば、高電子移動度トランジスタ(HEMT)等のIII族窒化物装置は、2個の活性層の間、例えば、GaN層とAlGaN層の間に2次元電子ガス(2-DEG)層を備える。この2-DEG層は、材料内の電荷分離につながる圧電分極と自発分極の違いの結果である。この型式の公知の装置では、2-DEGは、材料の特性によりゼロゲートバイアスにおいて存在する。AlGaN層の頂部に形成された接点を有するGaN電界効果トランジスタ(FET)は、ノーマリオン装置である。もし2-DEGが処理前に存在すれば、2-DEGが、AlGaN層の頂部への接点の形成の後にそこに残存するように、AlGaN層上の接点の形成は、ヘテロ構造の電荷分極を変化させない。ゲート上のしきい値電圧と呼ばれる負電圧が、静電結合により2-DEGを空乏化するために必要である。負電圧をゲートに印加することにより、電子チャネルをピンチオフすることができる。この負電圧は、典型的に-1Vと-8Vの間の負しきい値電圧(Vth)よりも典型的に下である。これらのトランジスタは、トランジスタをオフするためにチャネルを空乏化しなければならないことを意味するデプレーションモード(Dモード)で動作する。

20

#### 【0044】

例えば、パワースイッチング又は集積ロジック等のある用途では、陰極ゲート電圧供給を必要とせず、例えば、電源におけるパワー装置のゲート制御が、シリコン装置に使用されるのと同様にしなければならない。しきい値電圧Vth(>0V)を有する電界効果トランジスタ(FET)は、ノーマリオフ装置である。ゼロゲート電圧では、電流を通すチャネルは存在しない。これらのトランジスタは、エンハンスマントモード(Eモード)で動作する。Eモードトランジスタは、ノーマリオフ・パワースイッチ用、デジタル電子機器用途と高能率RF用途に魅力的である。

30

#### 【0045】

Dモード構成とEモード構成の両方において、金属-絶縁体-半導体・高電子移動度トランジスタ(MISHEMT)が、全シートキャリア密度からの利点を得られる前方方向でゲートをオーバードライブする可能性の点で好ましい。MISHEMTの別の利点は、例えば、オフ状態のパワースイッチの低消費電力につながるゲートリーク電流とドレインリーカ電流の抑制である。MISHEMTの場合、 $\text{SiO}_2$ 、 $\text{Si}_3\text{N}_4$ と、 $\text{Al}_2\text{O}_3$ 、 $\text{HfO}_2$ 又は $\text{Sc}_2\text{O}_3$ 等の高誘電率を有する他の酸化物(高k誘電体)とを備えるゲート誘電体が使用してきた。しかしながら、全ての場合において、半導体と堆積酸化物の間の界面は、制御が困難で、これは、MISHEMT構成の全可能性からの利点を得るこ

40

50

とを防止すると共に装置の低信頼性につながる。

**【0046】**

本発明において、用語「III族窒化物」は、元素周期表のIII族の少なくとも1個の元素と窒素を備える半導体材料を意味する。本発明において使用することができるIII族窒化物化合物半導体の例は、GaN、AlN、InGaN、InAlN、AlGaNとその混合物及び組合せを含むが、それらに限定されない。

**【0047】**

全開示を通じて、用語「バンドギャップ」は、価電子帯の頂部と伝導帯の底部の間のエネルギー差を指す。一般に、広バンドギャップ(WBG)半導体は、1eVより大きい、好ましくは、2eVより大きい電子バンドギャップを有する半導体材料である。一般に、狭バンドギャップ(NBG)半導体は、1eVより小さい、好ましくは、0.6eVより小さい電子バンドギャップを有する半導体材料である。しかしながら、全開示を通じて、装置の良好な動作を決定するのは、バンドギャップの実際の絶対値よりも、むしろWBGとNGBの間の相対差であるので、上記の絶対的な範囲は情報を与えるだけである。

**【0048】**

3.9(SiO<sub>2</sub>のk値)より大きい誘電率を有する誘電体材料は、ここで、「高k誘電体」と呼ぶ。典型的に、高k誘電体は、約7.0以上の誘電率を有し、約10.0以上の誘電率は、更に典型的である。

**【0049】**

第1の態様において、本発明は、ゲート電極とソースドレイン・オーミック接触を有するIII族窒化物HEMTを製造する方法において、

- a) 基板101を提供するステップと、

- b) 各層がIII族窒化物材料を備える層のスタック(1)を、エピタキシャル成長によって基板上に形成するステップと、

- c) スタック(1)の上方層203、204に対して上に位置すると共に当接する窒化シリコンからなる第1パッシベーション層301を形成するステップであって、第1パッシベーション層301が、現場でスタック(1)に堆積されるステップと、

- d) 第1パッシベーション層301に対して上に位置すると共に当接する誘電体層302を形成するステップと、

- e) 誘電体層302に対して上に位置すると共に当接する窒化シリコンからなる第2パッシベーション層303を形成し、第2パッシベーション層303が、低圧化学気相成長(LPCVD)又は有機金属化学気相成長(MOCVD)又は同等の手法によって450より高い温度で堆積されるステップと、

- f) ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える方法を開示する。

**【0050】**

括弧の間の数字は、本発明の工学基板とIII族窒化物装置を、夫々、概略的に図示する図1と図2を参照している。

**【0051】**

本発明の異なる態様の実施形態において、用語「基板」は、装置、回路又はエピタキシャル層が上に形成されて使用されるように下方に位置するなんらかの材料を含む。他の代りの実施形態において、この「基板」は、例えば、ドープトシリコン、ひ化ガリウム(GaAs)、ひ化りん化ガリウム(GaAsP)、りん化インジウム(InP)、ゲルマニウム(Ge)、シリコンゲルマニウム(SiGe)の基板等の半導体基板を含む。「基板」は、例えば、半導体基板部分の他に、SiO<sub>2</sub>層又はSi<sub>3</sub>N<sub>4</sub>層等の誘電体層を含む。よって、用語「基板」は、例えば、ガラス層、メタル層等の層が上に形成されるなんらかの他の基部であり得る。

**【0052】**

好ましくは、基板は、シリコン、炭化シリコン、サファイア又はGaN等のIII族窒化物材料からなる。より好ましくは、基板はシリコンからなる。より好ましくは、基板は、

10

20

30

40

50

(111) 又は同等の結晶配列を有する単結晶シリコンからなる。本発明の特定の実施形態において、基板は、(111)結晶配列と150mm、200mm又は300mmの直径を有するシリコンウエハである。好都合に、シリコンウエハを使用することは、シリコンをベースとするCMOSとの共同集積化(co-integration)を可能にする。

#### 【0053】

以下に「III族窒化物層のスタック」と呼ぶ各層がIII族窒化物材料からなる層のスタックは、好ましくは、基板上のエピタキシャル法によって形成される。III族窒化物層のスタックは、一般に、HEMT装置の活性層とも呼ばれるバッファ層201、チャネル層202とバリア層203を備える。別のやり方として、チャネル層は、厚いバッファ層201の上部(頂部)であり得る。活性層の各々は、多層又は傾斜組成を有する層であり得る。

10

#### 【0054】

HEMTの活性層は、有機金属化学気相成長(MOCVD)又は装置層が真空中の分子堆積によって作り上げられる分子線エピタキシー(MBE)によって製作され得る。

#### 【0055】

例えば、AlGaAs/GaAs・HEMTである従来のHEMTは、チャネル層(例えば、GaAs)に非ドープトで相対的に低いバンドギャップ材料を使用し、チャネル層は、チャネルと、相対的に高いバンドギャップ材料(例えば、AlGaAs)からなるバリア層内のゲート接点との間に位置するドーピング層によって電子を供給される。異なるバンドギャップを有する材料、即ち、より高いバンドギャップを有する材料とより低いバンドギャップを有する材料を組合せることによって、量子井戸が、組合された材料の間の界面に形成される。電子散乱が高いチャネルドーパント層をチャネル自身と分離することは、チャネル内の電子の移動度を大幅に増大させる。高周波操作における従来のMESFETに対するHEMT技術の基本的な利点を与えるのは、キャリアの高移動度である。AlGaN/GaN・HEMTのより特別な場合、その例ではAlGaNであるより高いバンドギャップ材料は、ドーピングされず、量子井戸中の高いシートキャリア濃度が、圧電分極と自発分極の効果によって得られる。

20

#### 【0056】

HEMTの成長は、典型的に、高品質装置を達成するために、バッファ層201で始まる。基板材料が活性材料と異なる場合、このバッファ層は、又、格子定数の相違に適合する。

30

#### 【0057】

本開示において、バッファ層201の厚さは、例えば、200nmと10μmの間、好ましくは、1μmと3μmの間である。選択肢として、例えば、核形成層である追加バッファ層201'及び/又は例えば、AlGaN、AlN又はGaN中間層等の中間層を、熱膨張と基板と活性層の間の格子ミスマッチを解消するために設けてもよい。

#### 【0058】

次に、チャネル層202は、GaN、GaAs又はInGaAsからなる。チャネル層の厚さは、例えば、5nmと200nmの間、好ましくは、50nmと200nmの間である。次に、バリア層203は、例えば、AlGaN、AlGaAs又はInAlAsからなる。バリア層の厚さは、例えば、1nmと50nmの間、好ましくは、5nmと30nmの間である。別のやり方として、AlGaAs/GaAsトランジスタを、明示のチャネル層無しに製作することができる。その上、III族窒化物材料からなるキャップ層204(不図示)を、エピタキシャル成長によってバリア層203の上に形成することができる。このような追加キャップ層は、GaNからなると共に、1nmと10nmの間の厚さを有する。

40

#### 【0059】

次のステップで、窒化シリコンからなる第1パッシベーション層301が、層のスタックの上方層に対して上に位置するとともに当接するように、好ましくは、現場で成長させられる。上方層は、バリア層203、又は追加キャップ層204、又はHEMTを形成す

50

るよう<sup>10</sup>に使用されるIII族窒化物層のスタック(1)のなんらかの他のIII族窒化物層部分であり得る。第1パッシベーション層301は、好ましくは、現場で、即ち、同じプロセスチャンバー内で、MOCVD又はMBE又は同等の手法によって層のスタックに堆積される。特定の実施形態において、第1パッシベーション層301は、現場で900と1250の間の温度で、より好ましくは、1100でMOCVDによって層のスタックに堆積される。

#### 【0060】

本発明の異なる態様の実施形態において、第1パッシベーション層は、窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)からなる。いくつかの実施形態では、第1パッシベーション層は、更に、Alを含んでもよい。選択肢として、第1パッシベーション層は、均質組成の単一層、又は傾斜組成を有する単一層からなり、又は、それは、複数の層からなる。より好ましくは、第1パッシベーション層は、窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)からなる。好ましくは、第1パッシベーション層(現場窒化シリコン)の厚さは、0.5nmと20nmの間、より好ましくは、0.5nmと10nmの間である。

#### 【0061】

次に、第1パッシベーション層に対して上に位置すると共に当接する誘電体層302は、原子層堆積(ALD)又はMOCVDによって堆積される。別のやり方として、メタライゼーション(例えば、Alメタライゼーション)を最初に行い、次に、高温酸化を行って、誘電体層を形成する。好ましくは、誘電体層は、ALDによって堆積される。

#### 【0062】

選択肢として、本発明の異なる態様の実施形態において、第1パッシベーション層301、誘電体層302と第2パッシベーション層303は、全て、(真空破壊無しに)現場でMOCVDによって、順にIII族窒化物層の頂部上に成長させられる。

#### 【0063】

選択肢として、第1パッシベーション層301と第2パッシベーション層303の各々は、Si<sub>3</sub>N<sub>4</sub>からなり、好ましくは、両パッシベーション層は、Si<sub>3</sub>N<sub>4</sub>からなる。誘電体層302は、好ましくは、Alからなる。好ましくは、誘電体層302は、AlN、Al<sub>2</sub>SiN、Al<sub>2</sub>O<sub>3</sub>及びその組合せ又は混合物からなる群から選択される。より好ましくは、誘電体層302は、AlNからなり、これは、上記方法のステップc)、d)とe)を現場でMOCVDによって行う時に特に好都合である。別のやり方として又は好ましくは、誘電体層302はAl<sub>2</sub>O<sub>3</sub>からなる。

#### 【0064】

別のやり方として、誘電体層302は、Al<sub>2</sub>O<sub>3</sub>、HfO<sub>2</sub>、ZrO<sub>2</sub>又はその組合せ及び/又は混合物等の高k誘電体材料からなる。

#### 【0065】

本発明の異なる態様の実施形態において、誘電体層302は、均質組成を有する単一層であり得る。別のやり方として、絶縁層は、傾斜組成を有する単一層であり得るし、又は、それは複数の層からなる。

#### 【0066】

誘電体層302と第1パッシベーション層301は、共に、ゲート誘電体として機能する。従って、現開示の文脈において、ゲート誘電体は、2層ゲート誘電体とも呼ばれる。その上、本発明の方法では、誘電体層302は、LPCVD(又は同等の)窒化シリコンからなる第2パッシベーション層303を選択的にエッティングするためのエッチストップ層として機能する。更に、誘電体層302がAl<sub>2</sub>O<sub>3</sub>からなる特定の実施形態においては、それが、第1パッシベーション層301(現場窒化シリコン)に対して湿式エッティングにより選択的に除去される。

#### 【0067】

好ましくは、誘電体層は、1nmと30nmの間の、より好ましくは、1nmと20nmの間の厚さを有する。1nmは、エッチストップ層として機能するのに原則的に十分であるので、誘電体層の厚さは、HEMT装置のゲート誘電体仕様によって決定される。

10

20

30

40

50

**【0068】**

特定の実施形態において、誘電体層は、ALDによって約400 の温度で堆積された Al<sub>2</sub>O<sub>3</sub>からなる。選択肢として、高k材料の結晶化温度より低い温度のポスト堆積アニールが適用される。

**【0069】**

一般に、界面準位密度(DIT)は、高温(600 - 800 )でポスト堆積アニール(PDA)又はポストメタル堆積アニール(PMA)を適用することによって下げることができる。

**【0070】**

Al<sub>2</sub>O<sub>3</sub>からなる誘電体層の特定の場合、600 と1000 の間の温度のポスト堆積アニールが適用される。ALD・Al<sub>2</sub>O<sub>3</sub>の結晶化温度は、800 と850 の間である。PDA又はPMAアニール温度は、多結晶フィルムが好ましい時にこの温度よりも高い。

10

**【0071】**

次に、誘電体層302に対して上に位置すると共に当接する窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)からなる第2パッシベーション層303が、形成される。第2パッシベーション層303が、LPCVD(バッチ又は單一ウエハプロセス)又はMOCVD又は同等の手法によって450 より高い温度、より好ましくは550 より高い温度、更に好ましくは700 より高い温度で堆積される。

**【0072】**

20

本発明の実施形態において、第2パッシベーション層は、オーミック接触合金温度より高い温度で堆積される。オーミック接触合金温度は、金不使用オーミック接触には500 と700 の間で、金含有メタライゼーション法では700 と900 の間である。

**【0073】**

好ましくは、第2パッシベーション層は、窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)からなる。本開示を通して、LPCVD(バッチ又は單一ウエハプロセス、即ち、SINGEN(商標))又はMOCVD又はなんらかの同等の手法によって450 より高い温度で堆積される窒化シリコンは、「LPCVD窒化シリコン」と呼ばれる。好ましくは、LPCVD窒化シリコンは、550 と800 の間、より好ましくは600 と800 の間の温度で堆積される。

30

**【0074】**

メタルゲート601材料が、第2パッシベーション層303でストップするように乾式エッティングされる集積法を取扱う実施形態では、第2パッシベーション層303は、メタルゲート・オーバエッチに耐えるのに十分に厚くなければならない。好ましくは、第2パッシベーション層(LPCVD窒化シリコン)は、少なくとも50nm、より好ましくは、約120nmの厚さを有する。

**【0075】**

好都合に、高温で堆積されるLPCVD窒化シリコン層は、プラズマ増強化学気相成長(PECVD)窒化シリコンより優れたパッシベーション層である。LPCVD窒化物は、PECVD窒化物の10 - 40 %よりも低い約3 - 8 %の水素含量を有する。又、LPCVD窒化物は、PECVD窒化物の2.3 - 3.1 g / cm<sup>3</sup>よりも高い約2.9 - 3.1 g / cm<sup>3</sup>の密度と、より低いピンホール密度を有する。LPCVD窒化シリコンの同様の値は、MOCVD窒化シリコンの水素含量と密度の値に当てはまる。

40

**【0076】**

PECVD窒化シリコン層は、約300 - 400 の温度で堆積されることが知られている。後のステップでより高い温度、例えば、オーミック合金形成の温度を受ける時、このような装置は、ブリスターとクラック又は装置収量を落とす離層を示す。LPCVD窒化シリコンは、このような欠点を有しない。

**【0077】**

本発明の方法では、LPCVD窒化シリコンからなる第2パッシベーション層は、下に

50

位置する層を保護して、乾式エッチングプロセス、例えば、オーミック接触形成のためのメタルエッチ及び／又はゲート電極形成のためのメタルゲートエッチ中の2DEG損傷を防止する。LPCVD窒化シリコンのかなり厚い層が、コスト効率のよい、Si-CMO<sub>S</sub>コンパチブルなプロセスで堆積される。

#### 【0078】

次のステップで、ソースドレイン・オーミック接触が、HEMT構造上に以下の順、

a) 第2パッシベーション層303、誘電体層302と第1パッシベーション層301を選択的にエッチングすることによって、ソースドレイン・オーミック接触領域をパターニングするステップと、

b) メタル層401を堆積及びパターニングすると共に、オーミック合金形成のために熱処理することによって、オーミック接触を形成するステップと

で形成される。

#### 【0079】

特定の実施形態において、第2パッシベーション層303(LPCVD窒化シリコン)を、Al<sub>2</sub>O<sub>3</sub>からなる誘電体層302に向けて選択的にエッチングすることは、SF<sub>6</sub>からなるプラズマで乾式エッチングによって行われる。次に、Al<sub>2</sub>O<sub>3</sub>膜が、稀薄HF溶液の湿式エッチングによって、第1パッシベーション層301(現場Si<sub>3</sub>N<sub>4</sub>)に向けて高選択性で除去される。次に、現場窒化シリコン301が、SF<sub>6</sub>からなるプラズマの乾式エッチングによって、AlGaNバリア層203に向けて高選択性で除去される。

#### 【0080】

メタル層401は、複数のメタル層を備えるメタルスタック、好ましくは、シリコン処理とコンパチブルな金不使用メタルスタックであり得る。ソースドレイン接触を形成するのに使用できる適当なメタル層スタックの例は、Ti/Al、Ti/Ta/Al、Ti/Al/TiW、Ti/Al/TiN、Ti/Al/WとTi/Al/WSiである。他の例は、Ta/Al/M、TaN/Al/M、Ta/Si/M、TaN/Si/Mであり、ここで、Mは、別のメタルスタックであり得る。メタルスタックMの機能は、下に位置する材料の酸化を防止し、及び／又は、ソースドレイン接触の接触抵抗を下げることである。Mは、例えば、TaN/Cuであり得る。

#### 【0081】

オーミック接触を形成するためのメタル層401のパターニングは、リフトオフ技術又は直接エッチング(例えば、乾式エッチング)によって行うことができる。

#### 【0082】

好ましくは、オーミック合金形成のための熱処理は、500と900の間の温度で行われる。より好ましくは、オーミック合金形成は、600と800の間のLPCVD窒化物堆積温度より低い温度で行われる。AlGaN/GaNに対する金不使用オーミック接触は、600付近の典型的なオーミック合金温度を有するが、金含有オーミック接触の場合、これは800付近である。より好ましくは、オーミック合金形成は、Al<sub>2</sub>O<sub>3</sub>が誘電体層として使用される特定の実施形態において500と850の間にあり、ゲート誘電体として使用される高k材料の結晶化温度より低い温度で行われる。

#### 【0083】

本発明の方法の利点は、オーミック合金形成の後、製造プロセスが、低い熱経費を有する、即ち、オーミック合金形成の温度より高い温度のプロセスステップを含まないことがある。

#### 【0084】

次に、ゲート電極601を形成することが、

a) 第2パッシベーション層303を誘電体層302に向けて選択的にエッチングすることによって、ゲートトレンチをパターニングするステップと、

b) メタルゲート層を堆積及びパターニングすることによって、少なくともゲートトレンチにおいてゲート電極601を形成するステップと

を更に備える。

10

20

30

40

50

**【 0 0 8 5 】**

別のやり方として、ゲート電極の形成を第1に行い、次に、オーミック接触を形成することができる。

**【 0 0 8 6 】**

メタルゲート層は、均質組成の層又は傾斜組成の層であり得る。別のやり方として、メタルゲート層は、ゲート電極を形成するのに適した仕事機能を有する多層（又はメタル層のスタック）であり得る。

**【 0 0 8 7 】**

ゲート電極を形成するのに使用できる適當なメタルゲートスタックの例は、ゲートメタル抵抗を下げるために、最終的に Al、Ti / Al、TiN / Al 又は Ti / TiN / Al の上層と組合される Ni、Mo、TiN、TaN、W、WSiN 又は WN である。

10

**【 0 0 8 8 】**

メタルゲート層のパターニングは、リフトオフ技術又は第2パッシベーション層上でストップするメタルゲート層の直接エッチング（例えば、乾式エッチング）によって行うことができる。乾式エッチングを用いる実施形態において、第2パッシベーション層 303 は、図2に示すように乾式エッチングプロセスのオーバエッチ・ステップ中に、部分的に消費（除去）される。その結果、第2パッシベーション層は、例えば、メタルゲート電極 601 によって覆われた領域内の元の（アズデポ（堆積時状態）の）厚さと比較すると、露出領域（ゲート縁部とソース／ドレイン接点の間）においてより薄くなっている。

**【 0 0 8 9 】**

本発明の方法は、ソースドレイン・オーミック接触とゲート電極のどちらが最初に形成されるかに応じて、誘電体キャップ層 501 をソースドレイン・オーミック接触又はゲート電極に形成して、後のメタル層 401 の堆積又はメタルゲート層 601 の堆積中の、夫々の、ソースドレイン・オーミック接触又はゲート電極を保護するステップを更に備える。

20

**【 0 0 9 0 】**

本発明の別の実施形態では、ゲートトレンチを形成することが、誘電体層 302 を少なくとも部分的にエッチングするステップと、ゲート電極を形成する前に第2誘電体層 302'（不図示）を再堆積するステップとを更に備える。

**【 0 0 9 1 】**

本発明の実施形態において、誘電体層 302 は、下に位置する第1パッシベーション層 301 上でストップして、部分的に又は全般的にエッチングされ得る。その後、第2誘電体層 302' を、部分的エッチングにより残った誘電体層の上に、又は、誘電体層 302 が完全に除去された時は第1パッシベーション層 301 の上に堆積することができる。第2誘電体層 302' は、均質組成の層、又は傾斜組成の層又は複数層（多層）のスタックであり得る。第2絶縁層は、ALD、MBE 又はスパッタリングによって堆積し、更に、選択肢として、スパッタリングの後にポスト堆積アニールを行うことができる。オーミック接触が第1に形成される実施形態では、第2誘電体層のポスト堆積アニールの温度を、オーミック合金形成温度より低く保つべきである。又、第2誘電体層のポスト堆積アニールの温度は、オーミック接触合金温度以下である。

40

**【 0 0 9 2 】**

第2の態様において、本発明は、III族窒化物HEMT製作用の工学基板であって、

a) 基板 101 と、

b) 基板上で各層がIII族窒化物材料からなる層のスタック（「III族窒化物層のスタック」とも呼ぶ）と、

c) 窒化シリコンからなり、III族窒化物層のスタックの上方層に対して上に位置すると共に当接する第1パッシベーション層 301 と、

d) 高k誘電体材料からなり、第1パッシベーション層 301 に対して上に位置すると共に当接する誘電体層 302 と、

e) 窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシ

50

ベースン層 303 と

を備える工学基板を開示する。

【0093】

本発明の特定の実施形態において、基板は、(111)配列又は同等の配列を有する単結晶シリコンからなるシリコンウエハである。

【0094】

本発明のHEMT装置の工学基板の第1パッシベーション層301と第2パッシベーション層303は、共に、本発明の方法で堆積された窒化シリコン(「LPCVD窒化シリコン」と呼ぶ)、即ち、約3-8%の低水素含量と約2.9-3.1g/cm<sup>3</sup>の高密度を有する窒化シリコンからなる。

10

【0095】

本発明の工学基板は、本発明の方法で得られると共に、ゲート誘電体を備えて、Si-CMOSコンパチブルな製造プロセスにHEMT装置を形成するのに使用するのに適したパッシベーションされた基板を提供する利点を有する。

【0096】

III族窒化物HEMTを製造するための出発基板としての工学基板の別の利点は、ゲート誘電体のポスト堆積アニールやパッシベーション層の高温堆積等の高温経費プロセスが、オーミック接触形成の前に行われる所以、従来の集積法の全ての後続プロセスに対して課せられるオーミック合金形成の拘束が解消される結果、HEMT装置の総合性能が改善される。

20

【0097】

III族窒化物HEMTを製造するための出発基板としての工学基板の更に別の利点は、現場窒化シリコン301、誘電体層302とLPCVD窒化シリコン303によって形成される3層スタック(II)が、III族窒化物スタック(I)をパッシベーションすると共に、III族窒化物HEMT装置を製造ために金不使用メタライゼーションステップとメタル(又はメタルゲート)層の乾式エッチングを使用する時のオーミック接触形成とゲート電極形成中にIII族窒化物スタック(I)をパッシベーションすると共に保護するのに適していることである。

【0098】

III族窒化物HEMTを製造するための出発基板としての工学基板の更に別の利点は、LPCVD窒化物が、オーミック接触形成の温度経費に耐えられることであり、これは、前述したようにPECVD窒化物では得られない。

30

【0099】

第3の態様で、本発明は、本発明の方法で得られて、基板の活性領域上に形成されると共に、ゲート電極とソースドレイン接点を備えるIII族窒化物HEMTであって、

a) 基板101と、

b) 基板上で各層がIII族窒化物材料からなる層のスタック(I)(「III族窒化物層のスタック」とも呼ぶ)と、

c) ソースドレイン接点の下を除く活性領域の全てにおいて、スタックの上方層203、204に対して上に位置すると共に当接し、更に、窒化シリコンからなる第1パッシベーション層301と、

40

d) ソースドレイン接点の下を除く活性領域の全てにおいて、第1パッシベーション層301に対して上に位置すると共に当接し、更に、高k誘電体材料からなる誘電体層302、302' と、

e) ゲート電極の下とソースドレイン接点の下を除く活性領域の全てにおいて、誘電体層に対して上に位置すると共に当接し、更に、LPCVD窒化シリコンからなる第2パッシベーション層303と

を更に備えるIII族窒化物HEMTを開示する。

【0100】

本発明の一般に適用される態様によれば、本発明の方法の実行の結果として、窒化シリ

50

コン、好ましくは、 $\text{Si}_3\text{N}_4$  からなり、III族窒化物層のスタックの上方層に対して上に位置すると共に当接する第1パッシベーション層と、第1パッシベーション層に対して上に位置すると共に当接する誘電体層とが提供されるか得られる。よって、本発明の方法の実行の結果として、第1パッシベーション層と誘電体層を備える又はからなる2層ゲート誘電体が提供されるか得られる。好ましくは、2層ゲート誘電体を得るために、誘電体層は、第1パッシベーション層の頂部に堆積される。特に、有機金属化学気相成長（MO CVD）リアクタ内で高温で現場でIII族窒化物層に堆積される時の窒化シリコンからなる第1パッシベーション層によって、 $\text{AlGaN}$ のリラクゼーション、クラッキングと表面粗さを減少する高品質パッシベーション層が得られる。それは、又、頂部 $\text{AlGaN}$ 界面における電荷を中和し及び／又は低界面準位密度を有する高品質界面を形成する。堆積後、第1パッシベーション層の厚さは、選択肢として低減される。このような低減のために、当業者には公知の手法を使用してもよい。堆積後、第1パッシベーション層の厚さは、例えば、約100ナノメートルである。厚さの低減後、第1パッシベーション層の厚さは、例えば、せいぜい20ナノメートル、せいぜい10ナノメートル、又はせいぜい5ナノメートル、例えば、約3ナノメートルである。誘電体層は、 $\text{Si}_3\text{N}_4$ と異なるもの、又は窒化シリコン不使用のものから選択されてもよい。誘電体層は、例えば、 $\text{Si}_3\text{N}_4$ と比較して、相対的に高い、例えば、約9より高い誘電率及び／又は相対的に高い、例えば、10MV/cmより高い降伏電界を有する。誘電体層は、例えば、原子層堆積（ALD）によって堆積される。

## 【0101】

10

本発明の方法と装置のいくつかの利点を説明するために、我々は、 $\text{Al}_2\text{O}_3$ ゲート誘電体を使用して、2個の型式の $\text{AlGaN}/\text{GaN}\cdot\text{HEMT}$ を製作及び評価した。好ましくは、両HEMTは、金含有プロセスとリフトオフを使用して処理された。HEMT“A”は、厚い現場窒化物のゲートリセスの後で単一ALD・ $\text{Al}_2\text{O}_3$ ゲート誘電体を堆積する従来の方法を使用する。HEMT“B”は、薄い現場窒化物の後にALD・ $\text{Al}_2\text{O}_3$ とLPCVD窒化物堆積を第1ステップとして続ける本発明の方法を使用して処理される。

## 【0102】

20

HEMT“A”的製作は、順に、

a)  $\text{AlN}$ 核形成層と、それに後続する $2.5\ \mu\text{m}$ 厚さの $\text{AlGaN}$ バッファ層、 $150\text{nm}$ 厚さの $\text{GaN}$ チャネル層と $10\text{nm}$ 厚さの $35\%\text{AlGaN}$ バリア層からなるシリコン(111)基板の頂部に成長するように、 $\text{AlGaN}/\text{GaN}$ エピ層スタックを形成するステップと、

b)  $120\text{nm}$ の現場窒化シリコンパッシベーションを形成するステップと、

c) コンタクトリソグラフィ、 $\text{SF}_6$ プラズマを用いた $120\text{nm}$ 現場窒化物の乾式エッチング、 $\text{Ti}/\text{Al}/\text{Mo}/\text{Au}$ メタルスタックの堆積、リフトオフと合金、好ましくは、合金形成でオーミック領域を画定することによって、オーミック接触を形成するステップと、

d) 素子分離のステップと、

e) コンタクトリソグラフィを用いたゲートトレントレンチエッチングと、後続の $\text{SF}_6$ プラズマを用いた $120\text{nm}$ 現場窒化物の乾式エッチングのステップと、

f)  $\text{HCl}/\text{TMAH}$ 溶液内のウエハクリーニングと、その直後の $10\text{nm}$ の $\text{Al}_2\text{O}_3$ 膜の堆積及び $700\text{ }^{\circ}\text{C}$ ポスト堆積アニールのステップと、

g) コンタクトリソグラフィを用いたゲートメタル堆積と、 $\text{Mo}/\text{Au}$ メタルスタックの堆積及びリフトオフのステップと

を備える。

## 【0103】

30

HEMT“B”的製作は、順に、

a)  $\text{AlN}$ 核形成層と、それに後続する $2.5\ \mu\text{m}$ 厚さの $\text{AlGaN}$ バッファ層、 $150\text{nm}$ 厚さの $\text{GaN}$ チャネル層と $10\text{nm}$ 厚さの $25\%\text{AlGaN}$ バリア層からなるシリ

40

50

コン(111)基板の頂部に成長するように、AlGaN/GaNエピ層を形成するステップと、

- b) 5 nmの現場窒化シリコンパッシベーションを形成するステップと、

- c) HCl/TMAH溶液内のウエハクリーニングと、その直後の10 nmのAl<sub>2</sub>O<sub>3</sub>膜の堆積及び700℃ポスト堆積アニールのステップと、

- d) 120 nmのLPCVD窒化物の800℃における堆積のステップと、

- e) コンタクトリソグラフィ、SF<sub>6</sub>プラズマを用いた120 nm LPCVD窒化物の乾式エッチング、稀釈BF<sub>3</sub>(緩衝HF)内のAl<sub>2</sub>O<sub>3</sub>・ALD膜の湿式エッチングと、SF<sub>6</sub>プラズマを用いた5 nm現場窒化物の乾式エッチング及び後続のTi/Al/Mo/Auメタルスタックの堆積、リフトオフと合金でオーミック領域を画定することによって、オーミック接触を形成するステップと、

- f) 素子分離のステップと、

- g) コンタクトリソグラフィを用いたゲートトレンチエッチングと、後続のSF<sub>6</sub>プラズマを用いた120 nm LPCVD窒化物の乾式エッチングのステップと、

- h) コンタクトリソグラフィを用いたゲートメタル堆積と、Mo/Auメタルスタックの堆積及びリフトオフのステップと

- を備える。

#### 【0104】

ステップg)で、10 nmのALD・Al<sub>2</sub>O<sub>3</sub>膜と5 nm現場窒化物層は除去されなかったので、底部の5 nm現場窒化物と頂部の10 nm Al<sub>2</sub>O<sub>3</sub>からなる2層ゲート誘電体が得られた。

#### 【0105】

本発明における概念の実行可能性と装置の改善された性能を証明するために、試験が、金含有メタライゼーションとリフトオフで行われた。しかしながら、Si-CMOSコンパチビリティに対しては、金不使用メタライゼーションが望ましい。

#### 【0106】

HEMT"A"のId-Vdsトランジスタ特性が、HEMT"B"の特性を示す図3(b)と比較して、図3(a)に示されている。Vgsバイアスは、HEMT"A"に対しては10 Vから5 V(ステップ5 V)であり、HEMT"B"に対しては-6 Vから2 V(ステップ1 V)である。HEMT"A"では、AlGaNバリアのAl濃度が高くなるにつれて、Vthがより負になると説明される。HEMT"A"とHEMT"B"の両装置は、良好なピンチオフと低リーケの良好なDCトランジスタ挙動を示している。

#### 【0107】

HEMT"A"とHEMT"B"のId-Vgsパルス特性を、夫々、図4(a)と図4(b)に示して、5 nm現場窒化物と10 nm ALD・Al<sub>2</sub>O<sub>3</sub>をゲート誘電体として有するHEMT"B"は、10 nm ALD・Al<sub>2</sub>O<sub>3</sub>だけをゲート誘電体として有するHEMT"A"と比較してより高い品質を有する。グラフは、DC挙動(点線)を、休止バイアス点、例えば、HEMT"A"に対するVgs=-10 V、Vds=40 V休止バイアス点、又、バイアス点、例えば、HEMT"B"に対するVgs=-5 V、Vds=50 Vバイアス点からのパルス特性(実線)と比較する。従来の方法で処理されたHEMT"A"は、パルス操作下でVthシフトと電流減少を示すが、これは、本発明の方法で処理されたHEMT"B"に当てはならない。これは、HEMT"A"の低品質なAlGaN/Al<sub>2</sub>O<sub>3</sub>界面及び/又はゲート誘電体により、ゲート下のトラッピングが生じていることと関連すると考えられる。

#### 【0108】

装置HEMT"A"とHEMT"B"のピンチオフにおける降伏が、夫々、図5(a)と図5(b)で比較される。HEMT"A"では、ゲートトラッピングが、ゲート酸化物降伏により、125 Vドレイン電圧で初期の降伏において発生する。HEMT"B"の降伏は400 Vに改善される。これは、現場窒化物とALD・Al<sub>2</sub>O<sub>3</sub>の組合せを使用する時のゲート誘電体のより優れた品質と関連すると考えられる。

10

20

30

40

50

## 【0109】

本発明の方法と装置の利点と好ましい利点を更に説明するために、我々は、Al<sub>2</sub>O<sub>3</sub>ゲート誘電体を使用して、別の2個の型式のAlGaN/GaN・HEMTを製作及び評価した。両HEMTが、金不使用メタル法、ステッパー・リソグラフィと乾式エッチングによるメタルパターニングを用いてCMOSコンパチブルなプロセスによって処理された。HEMT "C" は、厚い現場窒化物のゲートリセスの後に堆積された単一のALD・Al<sub>2</sub>O<sub>3</sub>ゲート誘電体で従来の方法を使用する。HEMT "D" は、薄い現場窒化物の堆積と後続のALD・Al<sub>2</sub>O<sub>3</sub>及びLPCVD窒化物堆積で本発明の方法を使用して処理される。

## 【0110】

HEMT "C" の製作は、順に、

a) AlN核形成層と、それに後続する2.5 μm厚さのAlGaNバッファ層、150 nm厚さのGaNチャネル層と10 nm厚さの25%AlGaNバリア層からなるシリコン(111)基板の頂部に成長するように、AlGaN/GaNエビ層スタックを形成するステップと、

b) 120 nmの現場窒化シリコンパッセーションを形成するステップと、

c) ステッパー・リソグラフィ及びSF<sub>6</sub>プラズマを用いた120 nm現場窒化物の乾式エッチング、Ti/Al/Wメタルスタックの堆積、ステッパー・リソグラフィ、乾式メタルエッチングと600 における合金でオーミック領域を画定することによって、オーミック接触を形成するステップと、

d) PECVD窒化物堆積、ステッパー・リソグラフィと現場窒化物に向けたPECVD窒化物の選択的エッチングで、オーミック領域の頂部に誘電体キャップを形成するステップと、

e) 素子分離のステップと、

f) ステッパー・リソグラフィを用いたゲートトレンチエッチングと、後続のSF<sub>6</sub>プラズマを用いた120 nm現場窒化物の乾式エッチングのステップと、

g) HCl/TMAH溶液内のウエハクリーニングと、その直後の15 nmのAl<sub>2</sub>O<sub>3</sub>膜の堆積及び600 ポスト堆積アニールのステップと、

h) W/Ti/Al堆積によるゲートメタル形成、後続のステッパー・リソグラフィと乾式メタルエッチングのステップと

を備える。

## 【0111】

HEMT "D" の製作は、順に、

a) AlN核形成層と、それに後続する2.5 μm厚さのAlGaNバッファ層、150 nm厚さのGaNチャネル層と10 nm厚さの25%AlGaNバリア層からなるシリコン(111)基板の頂部に成長するように、AlGaN/GaNエビ層を形成するステップと、

b) 10 nmの現場窒化シリコンパッセーションを形成するステップと、

c) HCl/TMAH溶液内のウエハクリーニングと、その直後の5 nmのAl<sub>2</sub>O<sub>3</sub>膜の堆積及び700 ポスト堆積アニールのステップと、

d) 120 nmのLPCVD窒化物の800 における堆積のステップと、

e) ステッパー・リソグラフィ、SF<sub>6</sub>プラズマを用いた120 nm LPCVD窒化物の乾式エッチング、1%HF内のAl<sub>2</sub>O<sub>3</sub>・ALD膜の湿式エッチングとSF<sub>6</sub>プラズマを用いた5 nm現場窒化物の乾式エッチングでオーミック領域を画定することによって、オーミック接触を形成するステップと、

f) PECVD窒化物堆積、ステッパー・リソグラフィとLPCVD窒化物に向けたPECVD窒化物の選択的エッチングで、オーミック領域の頂部に誘電体キャップを形成するステップと、

g) 素子分離のステップと、

h) コンタクトリソグラフィを用いたゲートトレンチエッチングと、後続のSF<sub>6</sub>プラ

10

20

30

40

50

ズマを用いた 120 nm L P C V D 窒化物の乾式エッチングのステップと

を備える。

#### 【0112】

Ti / Al / W メタルスタックの堆積、ステップパリソグラフィ、乾式メタルエッチングと 600 nm の合金が、ステップ e ) に続く。又、5 nm Al<sub>2</sub>O<sub>3</sub> と 10 nm 現場窒化物層は除去されなかったので、底部の 10 nm 現場窒化物と頂部の 5 nm Al<sub>2</sub>O<sub>3</sub> からなる 2 層ゲート誘電体が形成される。

#### 【0113】

HEMT "D" と HEMT "C" の Id - Vgs 特性 Ig - Vgs 特性を図 6 に示して

、10 nm 現場窒化物と 5 nm Al<sub>2</sub>O<sub>3</sub> をゲート誘電体として有する HEMT 10

"D" は、15 nm Al<sub>2</sub>O<sub>3</sub> だけをゲート誘電体として有する HEMT "C" と比較してより高い品質を有する。HEMT "D" では、前方ゲートバイアスゲートリーク電流 Ig は、約 2 衍低い。

#### 【0114】

HEMT "C" と HEMT "D" の全 150 mm ウエハに対するピンチオフにおける降伏の分布が、図 7 に示されている。HEMT "D" のゲート誘電体のより優れた品質が、一様な高降伏電圧を生じる。HEMT "D" の平均降伏電圧は 800 V であるのに対し、HEMT "C" のそれは 200 V である。HEMT "D" の典型的な Id - Vds (Vgs = -8 V) 降伏曲線が、図 8 に示される。ドレインリークは、Vds が約 700 V まで 20

1 μA / mm より低い。

#### 【0115】

図 9 は、HEMT "D" の分散挙動を示す。そのグラフは、(Vds = 0 V, Vgs = 0 V) と (Vds = 50 V, Vgs = -5 V) の休止バイアス点からパルシングする時の Id - Vds 曲線を比較する。観察された電流コラプスは、非常に限定的である。

#### 【符号の説明】

#### 【0116】

- 101 基板

- 201 バッファ層

- 202 チャネル層

- 203 バリア層

- 301 第 1 パッシベーション層

- 302 誘電体層

- 303 第 2 パッシベーション層

- 401 メタル層

- 501 誘電体キャップ層

- 601 ゲート電極

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

| (51)Int.Cl.             | F I                  |

|-------------------------|----------------------|

| H 01 L 21/768 (2006.01) | H 01 L 29/80 Q       |

| H 01 L 23/532 (2006.01) | H 01 L 29/78 3 0 1 B |

| H 01 L 21/336 (2006.01) | H 01 L 29/78 6 1 6 K |

| H 01 L 29/78 (2006.01)  | H 01 L 29/78 6 1 7 T |

| H 01 L 29/786 (2006.01) | H 01 L 29/78 6 1 7 U |

|                         | H 01 L 29/78 6 1 7 V |

|                         | H 01 L 29/78 6 1 9 A |

(72)発明者 マルレーン・ファン・ホーフェ

ベルギー 3 0 0 1 ルーヴァン、カペルドリーフ 7 5 番 アイメック内

審査官 恩田 和彦

(56)参考文献 特開2009-224760(JP,A)

特表2009-524242(JP,A)

特開2002-009253(JP,A)

国際公開第2011/039800(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 338

H 01 L 21 / 28

H 01 L 21 / 283

H 01 L 21 / 336

H 01 L 21 / 768

H 01 L 23 / 532

H 01 L 29 / 778

H 01 L 29 / 78

H 01 L 29 / 786

H 01 L 29 / 812