(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-267734

(P2005-267734A)

(43) 公開日 平成17年9月29日(2005.9.29)

(51) Int.Cl.<sup>7</sup>**G 11 C 16/06****G 11 C 16/04****H 02 M 3/07**

F 1

|        |       |         |

|--------|-------|---------|

| G 11 C | 17/00 | 6 3 2 A |

| H 02 M | 3/07  |         |

| G 11 C | 17/00 | 6 3 2 B |

| G 11 C | 17/00 | 6 2 1 Z |

| G 11 C | 17/00 | 6 2 3 A |

テーマコード(参考)

5 B 1 2 5

5 H 7 3 0

審査請求 未請求 請求項の数 11 O L (全 11 頁)

(21) 出願番号

特願2004-77757 (P2004-77757)

(22) 出願日

平成16年3月18日 (2004.3.18)

(71) 出願人

503121103 株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人

100068504

弁理士 小川 勝男

(74) 代理人

100086656

弁理士 田中 恭助

(72) 発明者

山添 孝徳

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者

秋元 雄一郎

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】昇圧回路及びそれを用いた不揮発性メモリ

## (57) 【要約】

## 【課題】

不揮発性メモリ等で、消去、Write、Read、スタンバイ等のモードに応じて、異なる昇圧電圧及び出力電流が必要となる半導体集積回路装置において、昇圧回路のチップ面積を増大させることなく、1つの昇圧回路で異なる昇圧電圧及び出力電流を発生することができる技術を提供し、スタンバイ等の低消費電力モードでは、昇圧回路の消費電力を超低消費電力にすることができる技術を提供する。

## 【解決手段】

不揮発性メモリ等の消去、Writeを行なう為に、基本ポンプセルをN段接続し昇圧する1つの昇圧回路で、N段以下のポンプセルを直列または並列に使用することで、出力電流供給能力が異なる消去、Write時以下の昇圧電圧を発生し、また昇圧用クロックを昇圧電圧検出信号に切替えることを特徴とする半導体集積回路装置である。

【選択図】 図10

**【特許請求の範囲】****【請求項 1】**

不揮発性メモリのデータの読み出し、書き込み、消去を制御する電圧を供給する基本ポンプセルをN段接続した昇圧回路であって、

前記昇圧回路は、前記不揮発性メモリのデータの読み出し時に、

N段の前記基本ポンプセルの中から選定されたN/2段以下の段数からなる一対の基本ポンプセルを並列動作させることを特徴とする昇圧回路。

**【請求項 2】**

請求項1記載の昇圧回路であって、

前記昇圧回路は、前記不揮発性メモリのデータの消去、書き込み時に、前記基本ポンプセルのN段を直列に動作させることを特徴とする昇圧回路。 10

**【請求項 3】**

請求項1記載の昇圧回路であって、

前記基本ポンプセルの中から、前記不揮発性メモリの待機時に、N段以下の前記基本ポンプセルを動作させることを特徴とする昇圧回路

**【請求項 4】**

2種の異なる電圧で制御され、基本ポンプセルがN段接続された昇圧回路と、

前記昇圧回路の出力電圧が所定の閾値を超えているか否かを判定し、該判定に応じて2種の異なる電圧を発生させる検出回路とを有し、

前記昇圧回路は、前記検出回路の発生する2種の異なる電圧にて制御されることを特徴とする昇圧回路。 20

**【請求項 5】**

前記昇圧回路は、不揮発性メモリのデータの読み出し、書き込み、消去を制御する電圧を供給するものであって、

前記昇圧回路は、前記不揮発性メモリの待機時に、前記検出回路の発生する2種の異なる電圧にて制御されることを特徴とする請求項4に記載の昇圧回路。

**【請求項 6】**

請求項1から4に記載の昇圧回路であって、

2種の異なる電圧を周期的に発生させ、前記昇圧回路を制御するクロック発生回路とを有し、 30

前記クロック発生回路は、

前記昇圧回路が前記不揮発性メモリの消去、書き込み、読み出しを制御する電圧を発生させる場合には、前記周期を変更し、

前記昇圧回路が前記不揮発性メモリの待機を制御する電圧を発生させる場合には、前記ドライブ能力を変更することを特徴とする昇圧回路。

**【請求項 7】**

請求項1に記載の昇圧回路であって、

並列動作させるN/2段以下の前記基本ポンプセルは、それぞれ前記昇圧回路の初段を含む前半部の基本ポンプセルと、前記昇圧回路の最終段を含む後半部の基本ポンプセルとあって、この2つの出力を合成することを特徴とする昇圧回路。 40

**【請求項 8】**

請求項3記載の昇圧回路であって、

前記N段以下の前記基本ポンプセルは、前記昇圧回路の後半部の基本ポンプセルであることを特徴とする昇圧回路。

**【請求項 9】**

請求項7または8に記載の昇圧回路であって、

2種の異なる電圧を周期的に発生させ、前記昇圧回路を制御するクロック発生回路を有し、

前記クロック発生回路は、動作させない基本ポンプセルへ前記電圧を供給しないことを特徴とする昇圧回路。 50

**【請求項 10】**

半導体記憶素子がマトリックス状に配列されてなる不揮発性メモリであつて、請求項1から9の昇圧回路を有することを特徴とする不揮発性メモリ。

**【請求項 11】**

前記半導体記憶素子に、MONOS構造を有するメモリセルを用いることを特徴とする請求項10記載の不揮発性メモリ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、フラッシュメモリ等の不揮発性メモリの消去、書き込み、および読み出し時に要する高電圧を発生させる昇圧回路並びにそれを用いた半導体集積回路に関する。 10

**【背景技術】****【0002】**

フラッシュ、EEPROM(Electrically Erasable Programmable Read Only Memory)等の不揮発性メモリは、消去時及びWrite時にトンネル効果又はホットエレクトロン、ホットホールを使用する為、高電圧を発生させる必要がある。

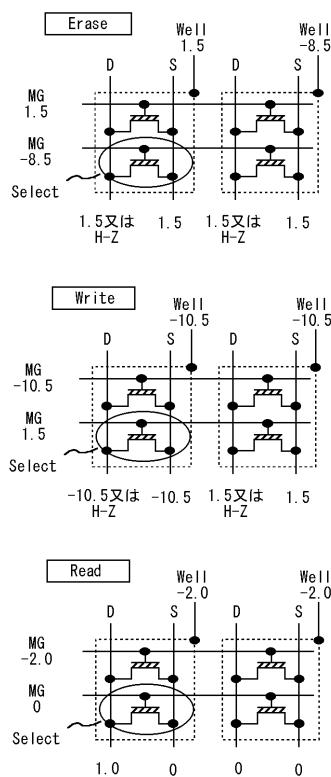

例えは、電気的書き換え可能なEEPROMの中で、MONOS(Metal Oxide Nitride Oxide Semiconductor)構造を持ったメモリセルと、エンハンスメント型のN型スイッチMOS(Metal Oxide Semiconductor)とで1ビットを構成したMONOS型EEPROMの消去、Write及びReadの各モードにおける動作バイアスを図1に示した。 20

**【0003】**

図1の動作バイアスは、電源電圧Vdd=1.5Vとした時の動作バイアスであり、消去時のメモリセルは0V未満のスレッシュホールド電圧値(Vt)となり、Write時のメモリセルは0V以上のVtとなる。

よって、Read時はメモリゲート(Mg)に0Vを印加し、選択されたスイッチMOSのゲート(Cg)に1.5Vを印加すればスイッチMOSがONとなり、メモリセルが消去状態の時には、約1V程度にプリチャージされたビット線からメモリセルを通じてソース線に電流が流れ、ビット線の電位が下がるのを検出し、メモリセルがWrite状態の時には、約1V程度にプリチャージされたビット線の電位が保持されているのを検出することで、データ"1" "0"を判断していた。ここで、図1中に示すH-Zはハイ・インピーダンスであること示す。 30

また、消去、Write時に必要な高電圧を発生する昇圧回路としては、非特許文献1で紹介、解析されているようなDickson型チャージポンプが一般的に知られており、回路構成も簡単な為、よく使用されている。

**【0004】**

従来からEEPROMは、頻繁にデータを書き換える用途として用いられてきているが、近年アプリケーションソフトの多様性及び複数のアプリケーションが1つのLSI又は1つのシステムで動作することにより、EEPROMの大容量化が望まれている。

その大容量化を阻害する原因として1ビット当たりのメモリサイズが大きいということもあり、エンハンスメント型のN型スイッチMOSを削除したMONOSメモリ(Single MONOS)が特許文献1及び2で提案されている。 40

**【0005】**

図2にこのSingle MONOSの各モードにおける動作バイアスを示した。図2からわかるように消去、Write時の動作バイアスは、図1で示した従来MONOS型メモリと同等であるが、Read時にはメモリWell及び非選択Mgに消去Vt以下のマイナス電圧を印加する必要がある。

また、スタンバイ時にはメモリに印加する電圧を全て0Vにしても良いが、スタンバイから立上がる場合、Read動作可能な昇圧マイナス電圧を得るために数μ秒から数十μ秒の時間がかかるので、立ち上がりスピードを上げるために、スタンバイ時にも予めマイナス電圧を印加することとしている。ここで、図2中に示すH-Zはハイ・インピーダンスであること示す。

**【0006】**

10

20

30

40

50

【特許文献1】特許第1876108号公報

【0007】

【特許文献2】特許第1950956号公報

【特許文献3】特願2002-333033号

【非特許文献1】T.Tanzawa and T.Tanaka, "A dynamic analysis of the Dickson charge pump circuit," IEEE J.Solid-State Circuits, vol.32, no8, pp.1231-1240, Aug. 1997.

【発明の開示】

【発明が解決しようとする課題】

【0008】

このようなSingle MONOSをモジュールとして周辺回路も含めたサイズを考えた場合、メモリ自体はスイッチMOSを削除することで小さくなるが、Read時にも昇圧したマイナス電圧を印加しないといけない為、Read用の昇圧回路が必要となり、さらにこのRead用の昇圧回路は数十MHz程度の高速Read動作に耐えうるように電流供給能力を大きくする必要がある。

【0009】

そうなると昇圧回路として消去、Writeの他に、出力電流供給能力が高いRead用の昇圧回路が必要となり昇圧回路のサイズ増大が考えられる。

また、スタンバイ時にもReadと同じく昇圧マイナス電圧を印加する必要があるのでスタンバイ時においても昇圧回路を動作させておく必要がある為、スタンバイ時の消費電流増大が懸念される。

【0010】

そこで、本発明の目的は、昇圧回路において、電流供給能力が異なる複数の昇圧電圧を発生する昇圧回路の面積削減及び消費電流の削減することができる技術を提供するものである。

【0011】

本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0013】

不揮発性メモリの消去、Writeを行なう為に、基本ポンプセルをN段接続し昇圧する1つの昇圧回路で、N段以下のポンプセルを直列または並列に使用することで、消去、Write時以下の出力電流供給能力が異なる昇圧電圧を発生し、また昇圧用クロックを昇圧電圧検出信号に切替えることを特徴とする半導体集積回路装置である。

【0014】

よって、昇圧回路の面積の増大なく1つの昇圧回路で消去、Write時以下の出力電流供給能力が異なる昇圧電圧を発生でき、昇圧用クロック回路を止めることができるので低消費電流の昇圧回路ができる。

【発明の効果】

【0015】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0016】

(1) 1つの昇圧回路で、昇圧電圧と出力電流が異なる電源を作ることができ、チップ面積の削減ができる。

【0017】

(2) 昇圧検出信号をチャージポンプのクロックとすることで、超低消費電力の昇圧回路

10

20

30

40

50

路が可能となる。

**【発明を実施するための最良の形態】**

**【0018】**

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一部材には同一の符号を付し、その繰り返しの説明は省略する。

**【0019】**

(実施の形態1)

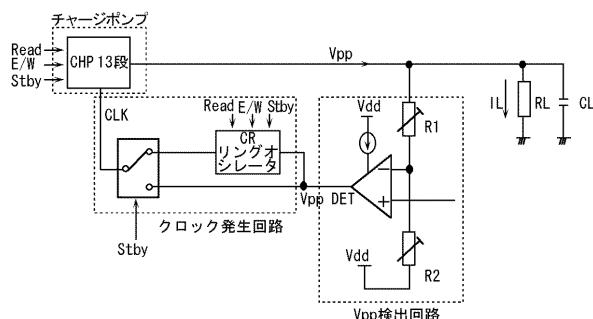

図3はメモリセルに昇圧バイアスを印加する昇圧回路の構成の一例を示したものである。

10

この本発明の昇圧回路は、チャージポンプ、クロック発生回路及び昇圧電圧( $V_{pp}$ )を検出する $V_{pp}$ 検出回路から構成されている。

クロック発生回路は、一般的なリングオシレータで構成したが、これに限るものではなく、機能的にチャージポンプにクロックを供給することができれば良い。チャージポンプはこのクロックに同期して昇圧電圧を発生させることとなる。

チャージポンプがクロックを受けて、動作すると昇圧電圧が発生し、ある規定電圧に到達すると $V_{pp}$ 検出回路が判定して $V_{pp}$ 検出信号( $V_{pp}$  DET)を発生する。

**【0020】**

$V_{pp}$ 検出回路は、コンパレータと基準電圧及び抵抗から構成されており、抵抗分圧された $V_{pp}$ と基準電圧とを比較することで、 $V_{pp}$  DETを発生する。ここで、 $V_{pp}$  DETを発生するとは、例えばコンパレータ出力が0VからVddになることである。

20

この $V_{pp}$  DETをうけてクロック発生回路はクロックを止める。クロックが止まることにより、チャージポンプは昇圧動作が止まることになる。

**【0021】**

昇圧動作が止まると、昇圧電圧は規定電圧未満となり、 $V_{pp}$  DETの発生が止まる。

$V_{pp}$  DETが止まると、ふたたびクロック発生回路が動作して、チャージポンプへクロックが供給されてチャージポンプが動作し、昇圧動作が行われる。

この動作を繰り返して、規定の昇圧電圧をキープすることとなる。

**【0022】**

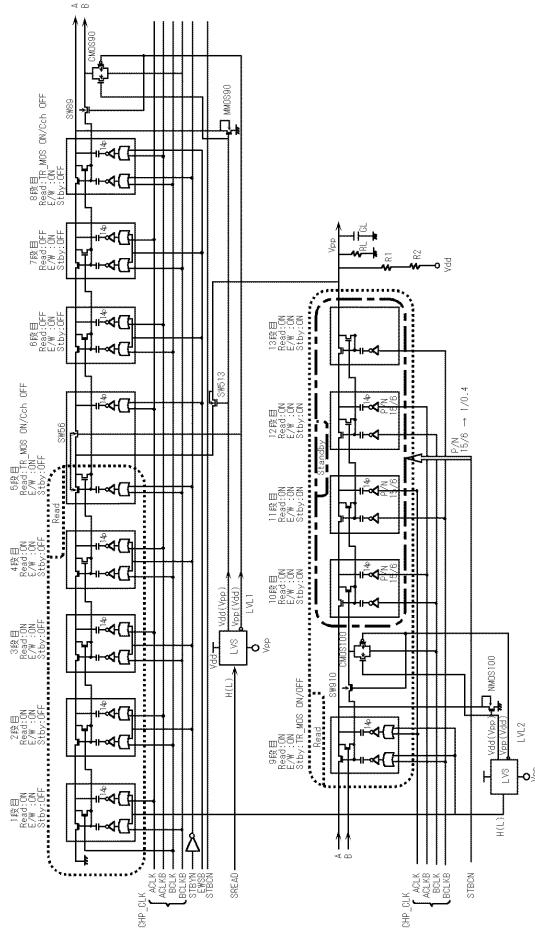

図4は、チャージポンプの構成を示した図であり、チャージ容量14pFで13段のポンプセルを直列接続し、基板効果をなくしたDickson型チャージポンプ回路である。

30

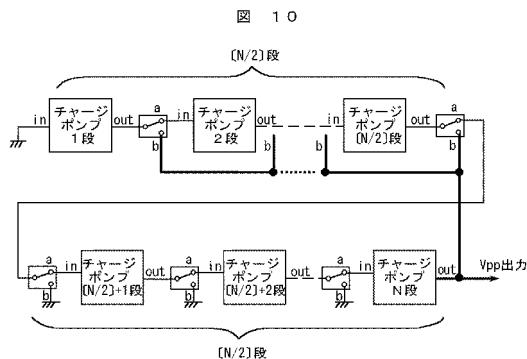

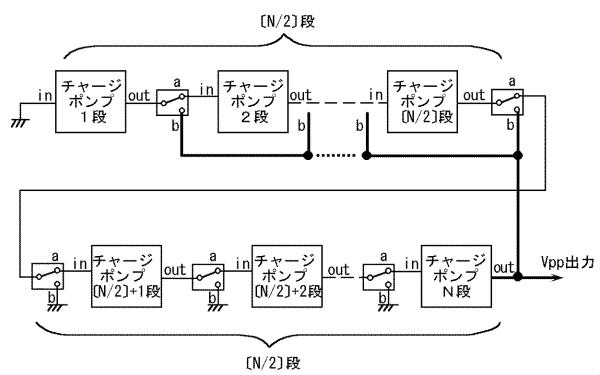

また、図10を用いて、図4に示す回路の動作を少し説明すると、Erase、Write時は、全てのスイッチが上記a側に接続されN段が直列に接続される。

ここで、図中に示す[N/2]等の[ ]は、ガウス記号を意味し、Nが奇数の時は、(N-1)/2を、Nが偶数の時は、N/2を示すものとする。

Read時は、例えば5段が並列に動作するとなると、チャージポンプ5段の出力スイッチがb側に接続され、(N-4)段の入力スイッチがb側に接続される。その他のスイッチは、a側に接続される。スタンバイ時は、例えば3段のみが動作することになり、(N-2)段の入力スイッチがb側に接続され、その他のスイッチはa側に接続される。

**【0023】**

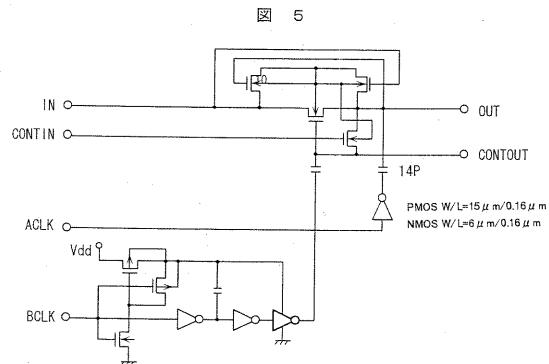

また、図5には1段あたりのチャージポンプ回路を示した。

この基板効果をなくしたDickson型チャージポンプ回路は、特許文献3で示されている回路である。

**【0024】**

図6は、64kB Single MONOS型EEPROMを動作させる時に必要な昇圧回路の仕様を示した図である。

消去、Write時には、それぞれマイナス高電圧の-8.5V、-10.7Vが必要である。消去、Writeは、トンネル効果を利用する為、消去、Write電流としては、数pA/bitである。よって、64kBのEEPROM容量とした場合、最大でも10μA以下の電流供給能力があればよい。

この場合、13段のポンプセルを全て直列動作させてマイナス高電圧の-8.5V、-10.7V

40

50

を発生させることとした。

【0025】

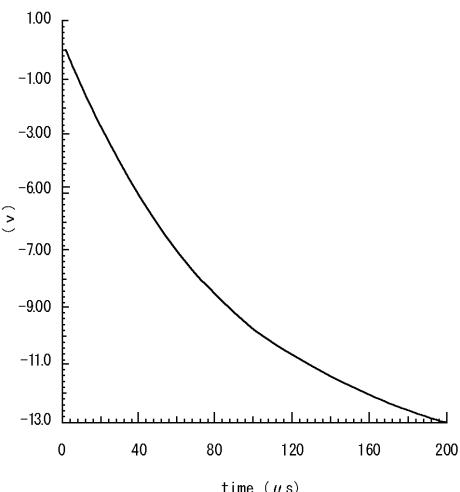

図7には、最悪条件( $V_{dd}=1.375V$ ,  $T_a=95^{\circ}C$ )における $V_{pp}$ シミュレーション波形を示した。

クロックは、10.8MHzとし、出力供給電流 $10\mu A$ 以上となる1M (0V- $V_{pp}$ 間)と、メモリ64kBに相当する1000pFの容量を $V_{pp}$ 出力における負荷とした。また、チャージポンプの実力を見るために、 $V_{pp}$ 検出回路をオフさせた。

図7からわかるように、 $V_{pp}$ 出力は-10.7V以下の昇圧電圧を発生していることが確認できた。

【0026】

次に、Read時は、メモリ消去 $V_t$ 以下の-2Vが必要である。Read動作速度30MHz、選択されたメモリゲート(Mg)容量を2pF(128Byte相当)とすると(1)式より、

$$2 \times 2 \times 10^{-12} \times 30 \times 10^6 = 120 \times 10^{-6} \dots \dots \dots (1)$$

出力供給電流は $120\mu A$ 必要となる。

【0027】

このRead時の昇圧回路として、チャージポンプ前後5段(1段から5段、9段から13段)のポンプセルを並列動作させて供給電流能力が高い-2V電圧を発生させることとした。

クロックは、10.8MHzとし、使用しない3段(6段から8段)のポンプセルは、論理回路によりクロックが供給されないようにした。

【0028】

また、5段目のポンプセルと6段目を切り離すスイッチNMOS(SW56)と5段目ポンプセル出力と、最終段13段目の出力を接続するスイッチNMOS(SW513)を設け、 $V_{dd}-V_{pp}$ を出力するレベルシフタLVL1でSW56をオフ、SW513をオンさせて5段目ポンプセルと13段目ポンプセルの出力を接続した。

【0029】

また、9段目ポンプセルの入力を0VにするためのNMOS90及び8段目ポンプセルから9段目ポンプセルへ入力される制御信号をオフさせるスイッチNMOS(SW89)とその制御信号をクロックへ接続するスイッチCMOS90を、LVL1で制御して最終段13段目からも-2Vが出力するようにした。

【0030】

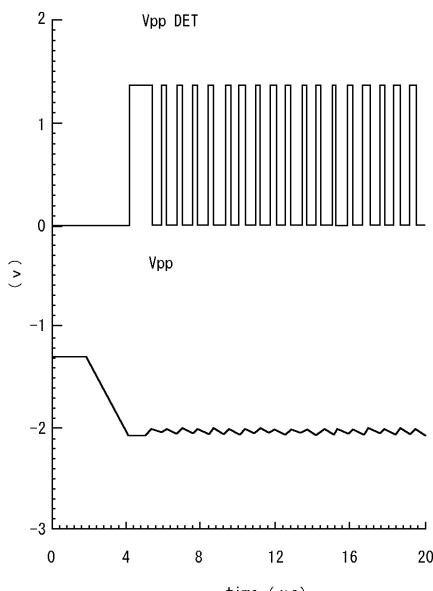

図8に最悪条件( $V_{dd}=1.375V$ ,  $T_a=95^{\circ}C$ )における $V_{pp}$ シミュレーション波形を示した。 $V_{pp}$ の負荷には、35MHzで2pFを0V- $V_{pp}$ 間でオン、オフするMgドライバを動作させた。また、 $V_{pp}$ 検出回路を動作させて、-2V typ.検出とした。

図8からわかるように、35MHz Read動作(出力供給電流 $I_{out}=163.6\mu A$  avg.シミュレーション実測値)において、-2V±0.15Vを出力し続けることができていることがわかった。

【0031】

次にスタンバイ時だが、前述したようにスタンバイにおいても $V_{pp}=-1.5V$  typ.が必要であり、リーク電流を考慮して $V_{pp}$ 供給電流としては最大 $1\mu A$ とした。

また、スタンバイでは、昇圧回路全体の消費電流を削減する必要があることから、昇圧回路消費電流として $10\mu A$ 以下にする必要がある。

このスタンバイ時の昇圧回路として、後ろ10段から13段のポンプセル4段を動作させることとし、使用しない9段(1段から9段)のポンプセルは、論理回路によりクロックが供給されないようにした。

【0032】

また、10段目ポンプセルの入力を0VにするためのNMOS100及び9段目ポンプセルから10段目ポンプセルへ入力される制御信号をオフさせるスイッチNMOS(SW910)とその制御信号をクロックへ接続するスイッチCMOS100を、LVL2で制御した。

【0033】

さらに動作する4段のポンプセルのクロックドライバ能力を切替えてチャージ容量をド

10

20

30

40

50

ライブする時に発生する貫通電流を抑えて、回路消費電流を抑えることとした。

また、クロック発生回路を止めて、チャージポンプへ供給するクロックとしては、Vpp検出信号を入力した。Vpp検出信号は、前述したように、規定電圧以下の時には、0VからVddとなり、規定電圧以上の時には、Vddから0Vになるので、クロックとして使用することが可能である。

これにより、クロック発生回路で消費する電流を、ほぼ0にすることができ、昇圧回路として全体の消費電流を削減することが可能となった。

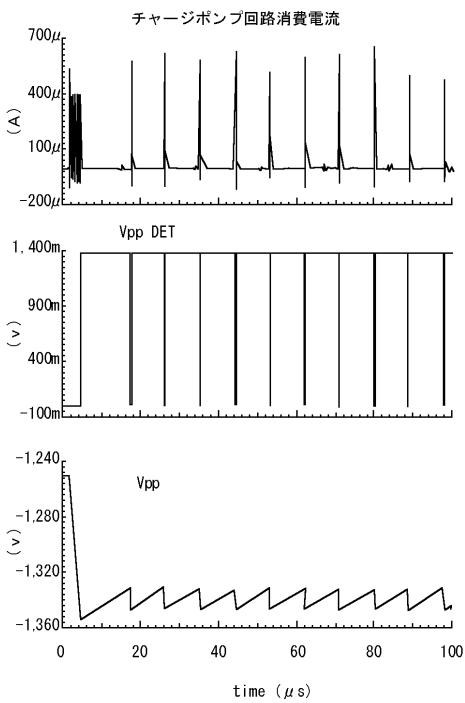

#### 【0034】

図9にVpp出力能力最悪となる条件(Vdd=1.375V, Ta=95 )におけるVppシミュレーション波形を示した。

Vpp DETにより、Vppが-1.33Vから-1.346Vの間で変動しており、Vpp DETがチャージポンプのクロックとして動作していることがわかる。

昇圧回路全体の消費電流は、チャージポンプは4μA、Vpp検出回路は3μAとなり合計7μAで低消費電流が達成できていることが確認できた。

#### 【図面の簡単な説明】

#### 【0035】

【図1】MONOS型EEPROMの各モードにおける動作バイアスを示す図である。

【図2】Single MONOS型EEPROMの各モードにおける動作バイアスを示す図である。

【図3】本発明の昇圧回路の構成を示す図である。

【図4】本発明の昇圧回路の内、チャージポンプ構成図である。

【図5】本発明の1段あたりのチャージポンプ回路を示す図である。

【図6】64KB Single MONOS型EEPROMの昇圧回路に対する仕様を示す図である。

【図7】本発明の昇圧回路で、Erase・Write時に発生するVppシミュレーション波形を示す図である。

【図8】本発明の昇圧回路で、Read時のシミュレーション波形を示す図である。

【図9】本発明の昇圧回路で、Stby(待機)時のシミュレーション波形を示す図である。

【図10】本発明の昇圧回路の内におけるチャージポンプ構成図である。

#### 【符号の説明】

#### 【0036】

CG...制御ゲート、MG...メモリ・ゲート、Select...選択領域、H-Z...ハイ・インピーダンス、E/W...Erase / Read、Read...読み出し、Write...書き込み、Stby...待機、IL...リーク電流。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

【図5】

【図6】

図6

@Vdd=1.375~1.625V, Ta=-40~95°C

|             | Vpp                                               | 電流能力IL      | 消費電流         | 備考                                                            |

|-------------|---------------------------------------------------|-------------|--------------|---------------------------------------------------------------|

| Erase/Write | Erase:-8.5V±0.2 <sup>*1</sup><br>Write:-10.7V±0.2 | 10 μA       | TBD          | <sup>*1</sup><br>Erase電圧=Vdd-Vpp=10V<br>Write電圧=Vdd-Vpp=12.2V |

| Read        | -2.0V±0.15                                        | 120 μA typ. | TBD          | <sup>*2</sup><br>MG合計容量2pF<br>Read動作 30MHz<br>IL=2p*2.0*30M   |

| Stand by    | -1.5V typ.                                        | 1 μA max.   | ≤ 10 μA avg. |                                                               |

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図 10

---

フロントページの続き

(72)発明者 石田 尚信

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 山崎 英治

東京都小平市上水本町五丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 大平 信裕

東京都小平市上水本町五丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

F ターム(参考) 5B125 BA08 CA04 CA06 EG03 EG06 EG08 FA02 FA05

5H730 AA14 AA15 AS04 BB02 DD04 FD03 FG08

【要約の続き】