(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6577450号

(P6577450)

(45) 発行日 令和1年9月18日(2019.9.18)

(24) 登録日 令和1年8月30日(2019.8.30)

(51) Int.Cl.

F 1

G06F 17/16 (2006.01)

G06F 17/16

G06F 9/315 (2006.01)

G06F 9/315

G06F 9/38 (2006.01)

G06F 9/38

Q

M

310G

請求項の数 21 (全 22 頁)

(21) 出願番号 特願2016-501361 (P2016-501361)

(86) (22) 出願日 平成26年3月12日 (2014.3.12)

(65) 公表番号 特表2016-511491 (P2016-511491A)

(43) 公表日 平成28年4月14日 (2016.4.14)

(86) 國際出願番号 PCT/US2014/023849

(87) 國際公開番号 WO2014/150636

(87) 國際公開日 平成26年9月25日 (2014.9.25)

審査請求日 平成29年2月22日 (2017.2.22)

審判番号 不服2018-8586 (P2018-8586/J1)

審判請求日 平成30年6月22日 (2018.6.22)

(31) 優先権主張番号 13/834,785

(32) 優先日 平成25年3月15日 (2013.3.15)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 アジャイ・アナント・イングル

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

早期審査対象出願

最終頁に続く

(54) 【発明の名称】水平置換を用いるベクトル間接要素垂直アドレッシングモード

## (57) 【特許請求の範囲】

## 【請求項 1】

1つまたは複数の要素データ値を出力ベクトル内に配置するための方法であって、複数の要素を含む垂直置換制御ベクトルを識別するステップであって、前記複数の要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタをそれぞれ示す、対応する複数のレジスタアドレスを含む、ステップと、

前記垂直置換制御ベクトルの前記複数の要素から前記複数のレジスタアドレスを読み取るステップと、

前記対応する複数のレジスタアドレスに基づく前記複数の要素について、前記複数のベクトルレジスタから複数の要素データ値を取り出すステップであって、前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタから取り出される、ステップと、

出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別するステップと、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記複数の要素データ値の少なくとも一部を前記出力ベクトル内に配置するステップとを含む、方法。

## 【請求項 2】

10

20

命令に関連するデータを受け取るステップと、

前記受け取ったデータを複数の要素に分割するステップと、

前記複数の要素を前記垂直置換制御ベクトル内に配置するステップと

をさらに含む、請求項1に記載の方法。

【請求項3】

前記複数の要素データ値を取り出すステップが、前記垂直置換制御ベクトル内の読み取ったメモリアドレスを間接的アドレスとして使用して、それぞれの要素データ値を取り出すステップを含む、請求項1に記載の方法。

【請求項4】

前記複数の要素データ値の前記少なくとも一部を前記出力ベクトル内に配置するステップが、クロスバーを使用して、前記複数の要素データ値の前記少なくとも一部を前記出力ベクトル内に配置するステップを含む、請求項1に記載の方法。

10

【請求項5】

前記水平置換制御ベクトルを識別するステップが、前記ベクトルレジスタファイル内のベクトルレジスタを識別するステップを含む、請求項1に記載の方法。

【請求項6】

読み取り専用メモリ(ROM)内に格納されたデータ構造を参照するスカラ値を受け取るステップをさらに含み、前記垂直置換制御ベクトルを識別するステップが、前記スカラ値を使用して、前記データ構造内の前記垂直置換制御ベクトルを識別するステップを含む、請求項1に記載の方法。

20

【請求項7】

読み取り専用メモリ(ROM)内に格納されたデータ構造を参照するスカラ値を受け取るステップをさらに含み、前記水平置換制御ベクトルを識別するステップが、前記スカラ値を使用して、前記データ構造内の前記水平置換制御ベクトルを識別するステップを含む、請求項1に記載の方法。

【請求項8】

前記複数の要素データ値を一時ベクトル内に配置するステップをさらに含み、前記複数の要素データ値の少なくとも一部を前記出力ベクトル内に配置するステップが、前記水平置換制御ベクトルを使用して前記一時ベクトルを置換するステップを含む、請求項1に記載の方法。

30

【請求項9】

プロセッサであって、

複数の要素を含む垂直置換制御ベクトルを識別することであって、前記複数の要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタをそれぞれ示す、対応する複数のレジスタアドレスを含む、識別することと、

前記垂直置換制御ベクトルの前記複数の要素から前記複数のレジスタアドレスを読み取ることと、

前記対応する複数のレジスタアドレスに基づく前記複数の要素について、前記複数のベクトルレジスタから複数の要素データ値を取り出すことであって、前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタから取り出される、取り出すことと、

40

出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別することと、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記複数の要素データ値の少なくとも一部を前記出力ベクトル内に配置することと

を行うように構成されるプロセッサ

を備える、装置。

【請求項10】

50

前記プロセッサが、前記ベクトルレジスタファイル内のベクトルレジスタを識別するよう<sup>10</sup>にさらに構成され、前記識別されたベクトルレジスタが前記水平置換制御ベクトルである、請求項9に記載の装置。

【請求項11】

前記プロセッサが、読み取り専用メモリ(ROM)内に格納されたデータ構造を参照するスカラ値を受け取るようにさらに構成され、前記垂直置換制御ベクトルが、前記データ構造内に格納される、請求項9に記載の装置。

【請求項12】

前記プロセッサが、読み取り専用メモリ(ROM)内に格納されたデータ構造を参照するスカラ値を受け取るようにさらに構成され、前記水平置換制御ベクトルが、前記データ構造内に格納される、請求項9に記載の装置。

10

【請求項13】

複数の要素を含む垂直置換制御ベクトルを識別することであって、前記複数の要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタをそれぞれ示す、対応する複数のレジスタアドレスを含む、識別することと、

前記垂直置換制御ベクトルの前記複数の要素から前記複数のレジスタアドレスを読み取ることと、

前記対応する複数のレジスタアドレスに基づく前記複数の要素について、前記複数のベクトルレジスタから複数の要素データ値を取り出すことであって、前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタから取り出される、取り出すことと、

20

出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別することと、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記複数の要素データ値の少なくとも一部を前記出力ベクトル内に配置することと

を含む動作を実施するためのコンピュータ実行可能命令を格納する、コンピュータ可読記録媒体。

【請求項14】

30

1つまたは複数の要素データ値を出力ベクトル内に配置するための装置であって、

複数の要素を含む垂直置換制御ベクトルを識別するための手段であって、前記複数の要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタをそれぞれ示す、対応する複数のレジスタアドレスを含む、手段と、

前記垂直置換制御ベクトルの前記複数の要素から前記複数のレジスタアドレスを読み取るための手段と、

前記対応する複数のレジスタアドレスに基づく前記複数の要素について、前記複数のベクトルレジスタから複数の要素データ値を取り出すための手段であって、前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタから取り出される、手段と、

40

出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別するための手段と、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記複数の要素データ値の少なくとも一部を前記出力ベクトル内に配置するための手段とを備える、装置。

【請求項15】

要素データ値を出力ベクトル内に書き込むための方法であって、

複数の要素データ値を含む入力ベクトルを読み取るステップと、

50

アドレスのセットを含む水平置換制御ベクトルを識別するステップと、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記入力ベクトル内の前記複数の要素データ値のうちの少なくとも一部を再構成するステップと、

前記複数の要素データ値のうちの前記再構成された少なくとも一部を一時ベクトル内に配置するステップと、

複数の要素を含む垂直置換制御ベクトルを識別するステップであって、前記複数の要素のうちの各要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタを示すレジスタアドレスを含む、ステップと、

前記垂直置換制御ベクトル内の前記レジスタアドレスに基づいて、前記一時ベクトル内の前記複数の要素データ値を前記複数のベクトルレジスタのうちの複数内に配置するステップと

を含み、

前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタに配置される、方法。

【請求項 16】

前記水平置換制御ベクトルを識別するステップが、前記ベクトルレジスタファイル内のベクトルレジスタを識別するステップを含む、請求項15に記載の方法。

【請求項 17】

読み取り専用メモリ(ROM)内に格納されたデータ構造を参照するスカラ値を受け取るステップをさらに含み、前記水平置換制御ベクトルを識別するステップが、前記スカラ値を使用して、前記データ構造内の前記水平置換制御ベクトルを識別するステップを含む、請求項15に記載の方法。

【請求項 18】

読み取り専用メモリ(ROM)内に格納されたデータ構造を参照するスカラ値を受け取るステップをさらに含み、前記垂直置換制御ベクトルを識別するステップが、前記スカラ値を使用して、前記データ構造内の前記垂直置換制御ベクトルを識別するステップを含む、請求項15に記載の方法。

【請求項 19】

プロセッサであって、

複数の要素データ値を含む入力ベクトルを読み取ることと、

アドレスのセットを含む水平置換制御ベクトルを識別することと、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記入力ベクトル内の前記複数の要素データ値のうちの少なくとも一部を再構成することと、

前記複数の要素データ値のうちの前記再構成された少なくとも一部を一時ベクトル内に配置することと、

複数の要素を含む垂直置換制御ベクトルを識別することであって、前記複数の要素のうちの各要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタを示すレジスタアドレスを含む、識別することと、

前記垂直置換制御ベクトル内の前記レジスタアドレスに基づいて、前記一時ベクトル内の前記複数の要素データ値を前記複数のベクトルレジスタのうちの複数内に配置することと

を行うように構成されるプロセッサ

を備え、

前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタに配置される、装置。

【請求項 20】

10

20

30

40

50

複数の要素データ値を含む入力ベクトルを読み取ることと、

アドレスのセットを含む水平置換制御ベクトルを識別することと、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記入力ベクトル内の前記複数の要素データ値のうちの少なくとも一部を再構成することと、

前記複数の要素データ値のうちの前記再構成された少なくとも一部を一時ベクトル内に配置することと、

複数の要素を含む垂直置換制御ベクトルを識別することであって、前記複数の要素のうちの各要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタを示すレジスタアドレスを含む、識別することと、

前記垂直置換制御ベクトル内の前記レジスタアドレスに基づいて、前記一時ベクトル内の前記複数の要素データ値を前記複数のベクトルレジスタのうちの複数内に配置することと

を含み、

前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタに配置される、

動作を実施するためのコンピュータ実行可能命令を格納する、コンピュータ可読記録媒体。

#### 【請求項 21】

要素データ値を出力ベクトル内に書き込むための装置であって、

複数の要素データ値を含む入力ベクトルを読み取るための手段と、

アドレスのセットを含む水平置換制御ベクトルを識別するための手段と、

前記水平置換制御ベクトル内の前記アドレスのセットに基づいて、前記入力ベクトル内の前記複数の要素データ値のうちの少なくとも一部を再構成するための手段と、

前記複数の要素データ値のうちの前記再構成された少なくとも一部を一時ベクトル内に配置するための手段と、

複数の要素を含む垂直置換制御ベクトルを識別するための手段であって、前記複数の要素のうちの各要素が、ベクトルレジスタファイル内の複数のベクトルレジスタのうちのベクトルレジスタを示すレジスタアドレスを含む、手段と、

前記垂直置換制御ベクトル内の前記レジスタアドレスに基づいて、前記一時ベクトル内の前記複数の要素データ値を前記複数のベクトルレジスタのうちの複数内に配置するための手段と

を備え、

前記複数の要素データ値の各要素データ値は、前記垂直置換制御ベクトル内の対応するレジスタアドレスの位置と一対一対応を有する前記ベクトルレジスタ内の位置において、前記対応するレジスタアドレスによって示される前記複数のベクトルレジスタのうちのベクトルレジスタに配置される、装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

優先権出願

本願は、参照によりその全体が本明細書に組み込まれる「VECTOR INDIRECT ELEMENT VERTICAL ADDRESSING MODE WITH HORIZONTAL PERMUTE」という名称の2013年3月15日出願の米国特許出願第13/834,785号の優先権を主張する。

##### 【0002】

本開示は、一般にはプロセッサに関し、より詳細には、プロセッサで要素を処理することに関する。

##### 【背景技術】

##### 【0003】

10

20

30

40

50

プロセッサは、データストリームを受け取り、レジスタ内にデータを格納することができる。データストリームは、複数のレジスタに及び、プロセッサにとっての関心の対象のデータのサブセットを含み得る。一例では、ユーザは、プロセッサを含むハンドセットを使用することができる。信号は、ユーザに関連するデータを含むことがあり、基準信号がタワーからハンドセットに送られ得る。基準信号は、ユーザのデータおよび他のデータと共にインターレースされ得る。たとえば、信号は、基準信号および他のユーザに関連するデータを含み得る。パケットが失われた場合、ユーザのデータを含むパケット全体と比較して、より少量のユーザのデータが失われる所以、信号は、ユーザのデータおよび他のユーザのデータを含み得る。このことは、ユーザごとにパケットを失う影響を緩和し得る。

【発明の概要】

10

【発明が解決しようとする課題】

【0004】

プロセッサが、たとえば関心の対象のデータ(たとえば、基準信号)を効率的に取り出し、データストリーム内にインターリープされる関心の対象のデータを編成することは望ましいものとなり得る。

【課題を解決するための手段】

【0005】

本開示はプロセッサに関する。プロセッサで要素を処理するための方法、システム、および技法が提供される。

【0006】

20

一実施形態によれば、1つまたは複数の要素データ値を出力ベクトル内に配置するための方法が、複数の要素を含む垂直置換制御ベクトルを識別することを含む。複数の要素のうちの各要素はレジスタアドレスを含む。本方法はまた、複数の要素のうちの各要素について、垂直置換制御ベクトルからレジスタアドレスを読み取ることをも含む。本方法は、レジスタアドレスに基づいて複数の要素データ値を取り出すことをさらに含む。本方法はまた、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別することをも含む。本方法は、水平置換制御ベクトル内のアドレスのセットに基づいて、複数の要素データ値のうちの取り出した要素データ値の少なくとも一部を出力ベクトル内に配置することをさらに含む。

【0007】

30

別の実施形態によれば、装置は、複数の要素を含む垂直置換制御ベクトルを識別するように動作可能なプロセッサを含み、複数の要素のうちの各要素がレジスタアドレスを含む。プロセッサはまた、複数の要素のうちの各要素について、垂直置換制御ベクトルからレジスタアドレスを読み取るように動作可能である。プロセッサまた、レジスタアドレスに基づいて複数の要素データ値を取り出すように動作可能である。プロセッサはまた、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別するように動作可能である。プロセッサはまた、水平置換制御ベクトル内のアドレスのセットに基づいて、取り出した要素データ値の少なくとも一部を出力ベクトル内に配置するように動作可能である。

【0008】

40

別の実施形態によれば、コンピュータ可読記録媒体が、複数の要素を含む垂直置換制御ベクトルを識別することであって、複数の要素のうちの各要素がレジスタアドレスを含むこと、複数の要素のうちの各要素について、垂直置換制御ベクトルからレジスタアドレスを読み取ること、1つまたは複数のレジスタアドレスを読み取ることに基づいて、複数の要素データ値を取り出すこと、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別すること、および水平置換制御ベクトル内のアドレスのセットに基づいて、複数の要素データ値のうちの取り出した要素データ値の少なくとも一部を出力ベクトル内に配置することを含む動作を実施するためのコンピュータ実行可能命令をその上に格納している。

【0009】

50

別の実施形態によれば、1つまたは複数の要素データ値を出力ベクトル内に配置するための装置が、複数の要素を含む垂直置換制御ベクトルを識別するための手段であって、複数の要素のうちの各要素がレジスタアドレスを含む手段と、複数の要素のうちの各要素について、垂直置換制御ベクトルからレジスタアドレスを読み取るための手段と、1つまたは複数のレジスタアドレスを読み取ることに基づいて、複数の要素データ値を取り出すための手段と、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別するための手段と、水平置換制御ベクトル内のアドレスのセットに基づいて、複数の要素データ値のうちの取り出した要素データ値の少なくとも一部を出力ベクトル内に配置するための手段とを含む。

【0010】

10

別の実施形態によれば、要素データ値を出力ベクトルに書き込むための方法が、複数の要素データ値を含む入力ベクトルを読み取ることを含む。本方法はまた、アドレスのセットを含む水平置換制御ベクトルを識別することをも含む。本方法は、水平置換制御ベクトル内のアドレスのセットに基づいて、入力ベクトル内の複数の要素データ値のうちの要素データ値の少なくとも一部を再構成することをさらに含む。本方法はまた、再構成した複数の要素データ値を一時ベクトル内に配置することをも含む。本方法は、複数の要素を含む垂直置換制御ベクトルを識別することをさらに含む。複数の要素のうちの各要素はレジスタアドレスを含む。本方法はまた、垂直置換制御ベクトル内のレジスタアドレスに基づいて、一時ベクトル内の要素データ値を少なくとも1つのベクトルレジスタ内に配置することをも含む。

【0011】

20

別の実施形態によれば、装置は、複数の要素データ値を含む入力ベクトルを読み取るように動作可能であるあるプロセッサを含む。プロセッサはまた、アドレスのセットを含む水平置換制御ベクトルを識別するように動作可能である。プロセッサはまた、水平置換制御ベクトル内のアドレスのセットに基づいて、入力ベクトル内の要素データ値の少なくとも一部を再構成するように動作可能である。プロセッサはまた、再構成した複数の要素データ値を一時ベクトル内に配置するように動作可能である。プロセッサはまた、複数の要素を含む垂直置換制御ベクトルを識別するように動作可能であり、複数の要素のうちの各要素がレジスタアドレスを含む。プロセッサはまた、垂直置換制御ベクトル内のレジスタアドレスに基づいて、一時ベクトル内の要素データ値を少なくとも1つのベクトルレジスタ内に配置するように動作可能である。

【0012】

30

別の実施形態によれば、コンピュータ可読媒体が、複数の要素データ値を含む入力ベクトルを読み取ること、アドレスのセットを含む水平置換制御ベクトルを識別すること、水平置換制御ベクトル内のアドレスのセットに基づいて、入力ベクトル内の複数の要素データ値のうちの要素データ値の少なくとも一部を再構成すること、再構成した複数の要素データ値を一時ベクトル内に配置すること、複数の要素を含む垂直置換制御ベクトルを識別することであって、複数の要素のうちの各要素がレジスタアドレスを含むこと、および垂直置換制御ベクトル内のレジスタアドレスに基づいて、一時ベクトル内の要素データ値を少なくとも1つのベクトルレジスタ内に配置することを含む動作を実施するためのコンピュータ実行可能命令をその上に格納している。

【0013】

40

別の実施形態によれば、要素データ値を出力ベクトルに書き込むための装置が、複数の要素データ値を含む入力ベクトルを読み取るための手段と、アドレスのセットを含む水平置換制御ベクトルを識別するための手段と、水平置換制御ベクトル内のアドレスのセットに基づいて、入力ベクトル内の複数の要素データ値のうちの要素データ値の少なくとも一部を再構成するための手段と、再構成した複数の要素データ値を一時ベクトル内に配置するための手段と、複数の要素を含む垂直置換制御ベクトルを識別するための手段であって、複数の要素のうちの各要素がレジスタアドレスを含む手段と、垂直置換制御ベクトル内のレジスタアドレスに基づいて、一時ベクトル内の要素データ値を少なくとも1つのベク

50

トルレジスタ内に配置するための手段とを含む。

【0014】

本明細書の一部を形成する添付の図面は、本発明の実施形態を示し、説明と共に、実施形態の原理について説明する役割をさらに果たす。図面では、同様の参照番号は、同一の要素または機能的に類似の要素を示し得る。要素が最初に現れる図面が、一般には、対応する参照番号の左端の桁によって示される。

【図面の簡単な説明】

【0015】

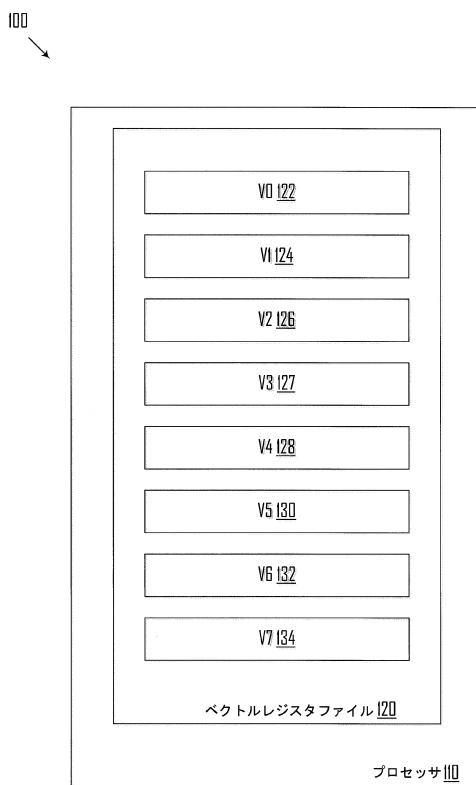

【図1】一実施形態による、ベクトルレジスタファイルを含むプロセッサを示すブロックダイアグラムである。

10

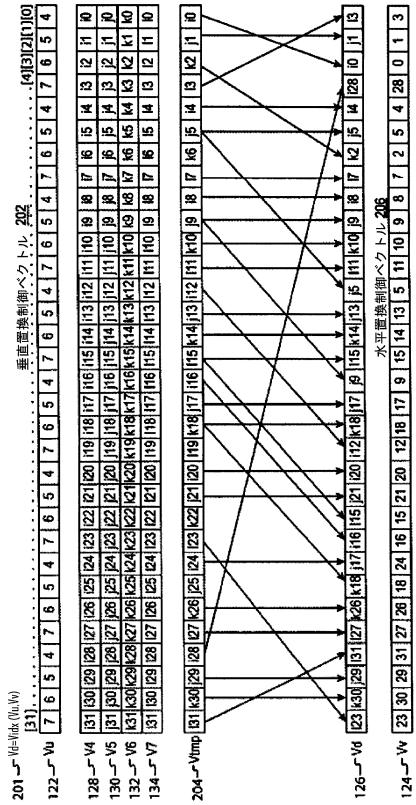

【図2】一実施形態による、1つまたは複数の要素データ値が出力ベクトル内に配置されることを示すブロックダイアグラムである。

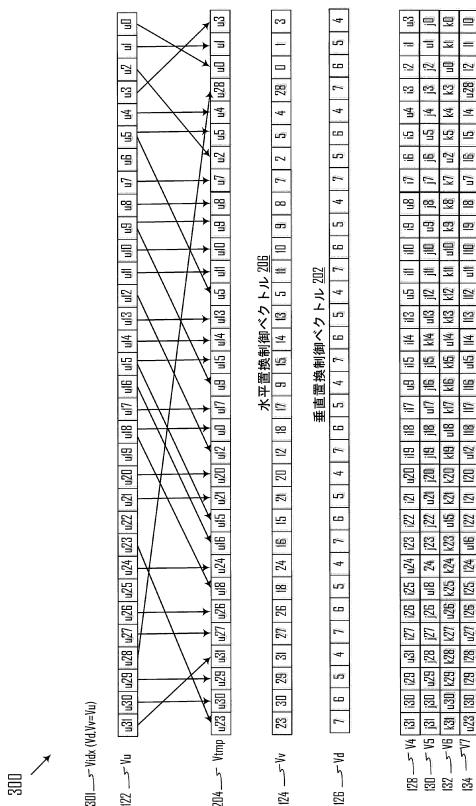

【図3】一実施形態による、要素データ値が少なくとも1つの出力ベクトル内に書き込まれることを示すブロックダイアグラムである。

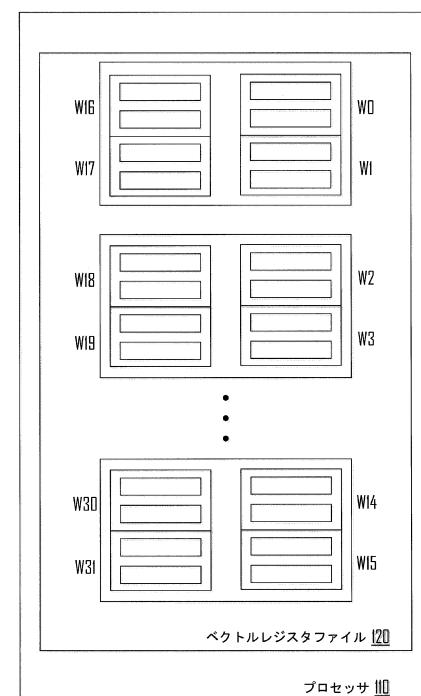

【図4】一実施形態による、ベクトルレジスタファイルを示すブロックダイアグラムである。

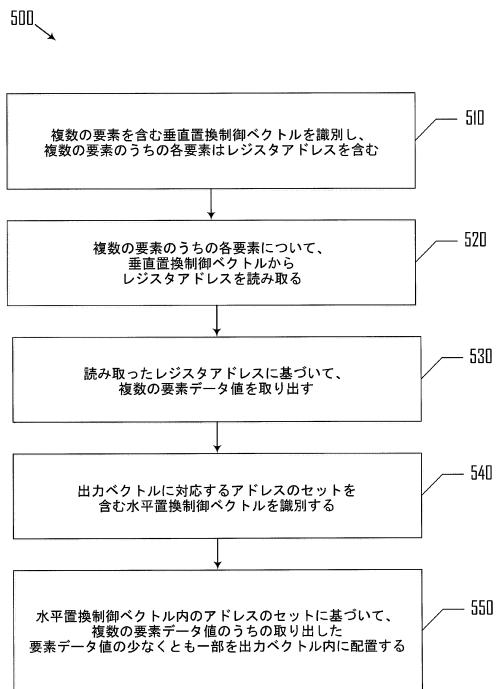

【図5】一実施形態による、1つまたは複数の要素データ値を出力ベクトル内に配置するための方法を示す流れ図である。

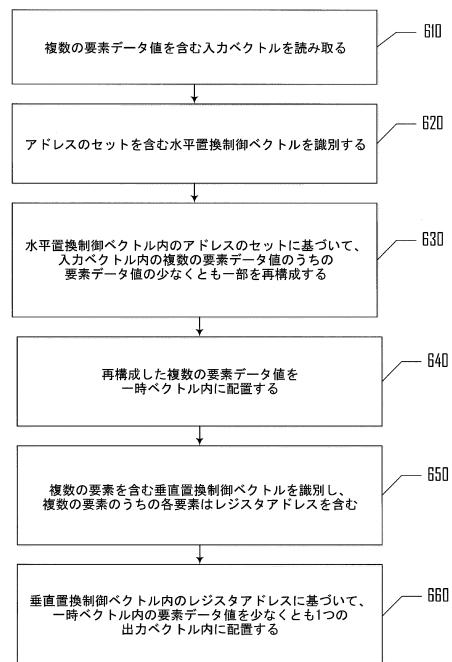

【図6】一実施形態による、要素データ値を少なくとも1つの出力ベクトル内に書き込むための方法を示す流れ図である。

20

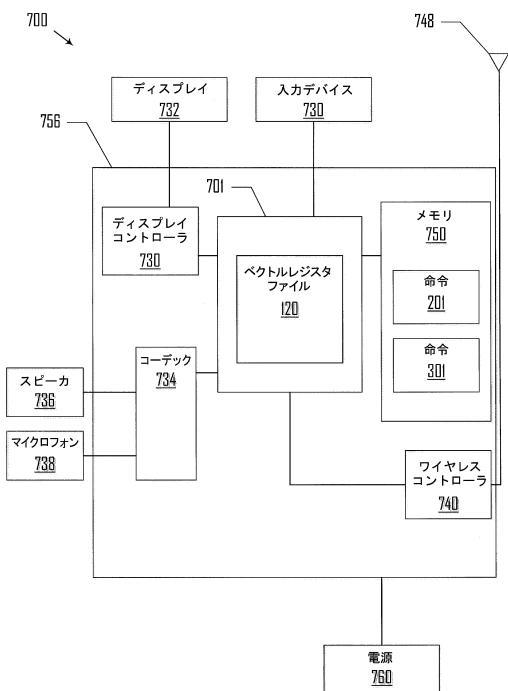

【図7】一実施形態による、デジタル信号プロセッサを含むワイヤレスデバイスを示すブロックダイアグラムである。

【発明を実施するための形態】

【0016】

I. 概要

II. 例示的命令

- A. 例示的読み取り命令

- B. 例示的書き込み命令

- C. スカラ値

III. 例示的レジスタファイル

30

IV. 例示的方法

V. 例示的ワイヤレスデバイス

【0017】

I. 概要

本開示の様々な特徴を実装する、多くの異なる実施形態、または実施例を以下で開示されることを理解されたい。いくつかの実施形態は、これらの特定の詳細の一部またはすべてを用いずに実施され得る。本開示を単純化するために、構成要素、モジュール、および構成の特定の実施例が以下で説明される。これらはもちろん例にすぎず、限定ではないものとする。

【0018】

40

プロセッサは、複数のベクトルレジスタを含むベクトルレジスタファイルを含み得る。ベクトルレジスタは要素データ値を格納することがあり、要素データ値に関連するデータのサブセットが関心の対象であり得る。複数のベクトルレジスタ(たとえば、ユーザデータとインターレースされた基準信号)から要素データ値のサブセットを読み取り、要素データ値のサブセットを出力ベクトル内に配布することは望ましいものとなり得る。

【0019】

一実施例では、要素データ値のサブセットを取り出し、要素データ値のサブセットの1つまたは複数を出力ベクトル内に配置するために、制御の2つのセットが使用され得る。制御の第1のセットは、複数のベクトルレジスタのうちのベクトルレジスタ内のどの列要素を読み出すかを決定するためのレジスタアドレスを含む垂直置換制御ベクトルであり得

50

る。たとえば、垂直置換制御ベクトルは、要素データ値がそれから読み取られる垂直アドレスを含み得る。制御の第2のセットは、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルであり得る。水平置換制御ベクトルは、出力ベクトル内の取り出した要素データ値のサブセットの水平分布を決定し得る。取り出した要素データ値のサブセットの少なくとも一部は、水平置換制御ベクトル内のアドレスのセットに基づいて、出力ベクトル内に配置され得る。

#### 【0020】

別の実施例では、要素データ値を少なくとも1つの出力ベクトル内に書き込むために、制御の2つのセットが使用され得る。一実施例では、複数の要素データ値を含む入力ベクトルが読み取られ得る。入力ベクトル内の複数の要素データ値のうちの要素データ値の少なくとも一部が、水平置換制御ベクトル内のアドレスのセットに基づいて再構成されることがあり、再構成された要素データ値が、一時ベクトル内に配置され得る。一時ベクトル内の要素データ値が、垂直置換制御ベクトルに基づいて、少なくとも1つの出力ベクトルに配置され得る。垂直置換制御ベクトルは、複数の要素を含むことがあり、複数の要素のうちの各要素は、ベクトルレジスタファイル内のベクトルレジスタのレジスタアドレスを含む。

#### 【0021】

図1は、一実施形態による、ベクトルレジスタファイル120を含むプロセッサ110を示すブロックダイアグラムである。

#### 【0022】

ベクトルレジスタファイル120は、N個の汎用ベクトルレジスタを含むことがあり、Nは0より大きい整数である。各ベクトルレジスタには、M個の要素のベクトルが充填されることがあり、Mは0より大きい整数である。要素は、ベクトルレジスタから読み取られ得るデータの最小の細分性を指すことがある。各ベクトルレジスタ内で、データは、たとえば、バイト(8ビット)、ショートワード(16ビット)、ワード(32ビット)、またはダブルワード(64ビット)として書き込まれ、または読み取られ得る。一実施例では、ベクトルレジスタファイル120は、32個のベクトルレジスタ(N=32)および32個の32ビット要素(M=32)を含み、各ベクトルレジスタは1024ビット幅(32要素×32ビット)である。

#### 【0023】

図1では、ベクトルレジスタファイル120が、ベクトルレジスタV0(122)、V1(124)、V2(126)、V3(127)、V4(128)、V5(130)、V6(132)、およびV7(134)を含む。図1ではベクトルレジスタファイル120が8つのベクトルレジスタを含むものとして示されているが、ベクトルレジスタファイル120内に8つより少ない、または多いベクトルレジスタを有する他の実施形態は、本開示の範囲内にある。一実施例では、ベクトルレジスタファイル120は、32個のベクトルレジスタV0～V31を含む。

#### 【0024】

プロセッサ110は、要素をベクトルレジスタにロードし、ベクトルレジスタから値を読み込み得る。一実施例では、ベクトルレジスタV4、V5、V6、およびV7に関連する要素のサブセットが、垂直および水平置換制御ベクトルに基づいて処理され得る。

#### 【0025】

##### 11. 例示的命令

###### A. 例示的読み取り命令

プロセッサ110は、1つまたは複数の要素データ値を出力ベクトル内に配置する読み取り命令を受け取り得る。

#### 【0026】

図2は、一実施形態による、1つまたは複数の要素データ値が出力ベクトル内に配置されることを示すブロックダイアグラム200である。

#### 【0027】

ダイアグラム200は、 $Vd=vidx(Vu, Vv)$ を含む例示的読み取り命令201を含む。命令201は、2つの入力ベクトルレジスタ(たとえば、VuおよびVv)を読み取ること、および出力を出力ベ

10

20

30

40

50

クトルレジスタ(たとえば、 $Vd$ )に書き込むことを含む。ベクトルレジスタ $Vu$ 、 $Vv$ 、および $Vd$ は、ベクトルレジスタファイル120からのベクトルレジスタ $V0$ ～ $V7$ のいずれかでよく、 $u$ 、 $V$ 、および $d$ は、0から7までの任意の値でよい。命令は、 $Vu$ 、 $Vv$ 、および $Vd$ についての特定の値を指定するオペコードに変換し得る。一実施例では、 $Vu=V0$ 、 $Vv=V1$ 、および $Vv=V3$ である。 $Vu$ は、垂直置換制御ベクトルを含むことがあり、 $Vv$ は、水平置換制御ベクトルを含むことがある、 $Vd$ は、出力ベクトルおよび各ベクトルレジスタを含むことがある。 $Vu$ 、 $Vx$ 、および $Vv$ のそれぞれは、ベクトルレジスタファイル120内のベクトルレジスタのいずれかであり得る。

#### 【0028】

プロセッサ110は、命令201を受け取り、実行し得る。命令201を実行することは、垂直置換制御ベクトルを識別すること、垂直置換制御ベクトルから1つまたは複数のメモリアドレスを読み取ること、および読み取ったメモリアドレスに基づいて複数の要素データ値を取り出すことを含み得る。命令201を実行することはまた、水平置換制御ベクトルを識別すること、および水平置換制御ベクトルに基づいて、取り出した要素データ値の少なくとも一部を出力ベクトル内に配置することをも含み得る。

10

#### 【0029】

ダイアグラム200は、ベクトルレジスタファイル120内に含まれる得る複数のベクトルレジスタを含む。複数のベクトルレジスタはベクトルレジスタ $V4$ 、 $V5$ 、 $V6$ 、および $V7$ を含み、各ベクトルレジスタは要素データ値を含み得る。複数のベクトルレジスタ内に格納された要素データ値のサブセットを取り出すことは望ましいものとなり得る。

20

#### 【0030】

プロセッサ110は、複数の要素を含む垂直置換制御ベクトル202を識別し得る。一実施形態では、プロセッサ110は、命令に関連するデータを受け取り、受け取ったデータを複数の要素に分割する。複数の要素は、垂直置換制御ベクトル内に配置されてよく、複数の要素のうちの各要素はレジスタアドレスを含む。

#### 【0031】

図2では、垂直置換制御ベクトル202は、ベクトルレジスタファイル120からベクトルレジスタ $Vu122$ 内に格納され得る。したがって、プロセッサ110が垂直置換制御ベクトルを識別したとき、プロセッサ110は、ベクトルレジスタファイル120内のベクトルレジスタ $Vu$ を識別し得る。ベクトルレジスタファイル120内のベクトルレジスタは、プログラマにとって可視であることがあり、ベクトルレジスタファイル120内のベクトルレジスタから間接的に読み取るために使用され得る。上記の実施例を参照すると、ベクトルレジスタ $V4$ 、 $V5$ 、 $V6$ 、および $V7$ 内の要素データ値のサブセットのみが、基準信号を格納することがあり、要素データ値の残りは、関心の対象ではない他のデータを含み得る。関心の対象の要素データ値のサブセットは複数のベクトルレジスタに及び得る。これらの特定の要素データ値を取り出すために、プログラマは、このパターンを $Vu$ 内にプログラムして、適切なレジスタアドレスに格納された関心の対象の要素データ値を抽出し得る。

30

#### 【0032】

ベクトルレジスタ $Vu$ は、32個の要素を含むことがあり、各要素は、32ビットレジスタアドレスを含み得る。たとえば、 $Vu[0]=4$ かつベクトルレジスタ $V4[0]$ についてのレジスタアドレスを含み、 $Vu[1]=5$ かつベクトルレジスタ $V5[1]$ についてのレジスタアドレスを含み、 $Vu[2]=6$ かつベクトルレジスタ $V6[2]$ についてのレジスタアドレスを含み、 $Vu[3]=7$ かつベクトルレジスタ $V7[3]$ についてのレジスタアドレスを含む。

40

#### 【0033】

複数の要素データ値が、レジスタアドレスを読み取ることに基づいて取り出され得る。具体的には、垂直置換制御ベクトル内のレジスタアドレスが、ベクトルレジスタファイルから適切な要素データ値を取り出すための間接アドレスとして使用され得る。このようにして、垂直置換制御ベクトル202内に格納された1つまたは複数のレジスタアドレスが、対応するレジスタアドレスに格納された要素データ値への間接アクセスとして使用され得る。間接読み取りは、レジスタアドレスではなく要素データ値を指定する直接読み取りと対照的

50

なものであり得る。間接読み取りでは、レジスタアドレスが読み取られ、関心の対象の要素データ値を取り出すために使用され得る。

#### 【 0 0 3 4 】

一実施例では、Vu[0]からベクトルレジスタV4についてのレジスタアドレスを読み取った後、プロセッサ110は、ベクトルレジスタV4[0]に格納された要素データ値である要素データ値「i0」を取り出し得る。同様に、Vu[1]からベクトルレジスタV5についてのレジスタアドレスを読み取った後、プロセッサ110は、ベクトルレジスタV5[1]に格納された要素データ値である要素データ値「j1」を取り出し得る。同様に、Vu[2]からベクトルレジスタV6についてのレジスタアドレスを読み取った後、プロセッサ110は、ベクトルレジスタV6[2]に格納された要素データ値である要素データ値「k2」を取り出し得る。同様に、Vu[3]からベクトルレジスタV7についてのレジスタアドレスを読み取った後、プロセッサ110は、ベクトルレジスタV7[3]に格納された要素データ値である要素データ値「l3」を取り出し得る。プロセッサ110は、Vu内に格納された他のレジスタアドレスについて同様の動作を実施し得る。一実施形態では、プロセッサ110は単一命令多重データ(SIMD)プロセッサであり、本開示で説明される命令を並列に実施する。たとえば、プロセッサ110は、Vv内のレジスタアドレスを並列に読み取り、読み取ったレジスタアドレスに基づいて要素データ値を並列に取り出し得る。10

#### 【 0 0 3 5 】

プロセッサ110は、取り出した複数の要素データ値を一時ベクトルレジスタ内に配置し得る。ダイアグラム200はベクトルレジスタVtmp204を含む。プロセッサ110はパイプライン式プロセッサであることがあり、Vtmp204は、中間結果を格納するために使用される一時パイプラインベクトルレジスタであり得る。別の実施例では、Vtmp204は、ベクトルレジスタファイル120内のベクトルレジスタであり得る。Vu内のレジスタアドレスに基づいて取り出された要素データ値は、Vtmp204内に配置され得る。20

#### 【 0 0 3 6 】

たとえば、図2では、ベクトルレジスタV4[0]から読み取られた「i0」がVtmp[0]内に配置され、ベクトルレジスタV5[1]から読み取られた「j1」がVtmp[1]内に配置され、ベクトルレジスタV6[2]から読み取られた「k2」がVtmp[2]内に配置され、ベクトルレジスタV7[3]から読み取られた「l3」がVtmp[3]内に配置される。プロセッサ110は、垂直置換制御ベクトル内のレジスタアドレスに基づいて、他の取り出した要素データ値のすべてについて同様の動作を実施し得る。30

#### 【 0 0 3 7 】

一実施形態では、プロセッサ110は、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトル206を識別する。水平置換制御ベクトル206は、出力ベクトル内の取り出したデータ値要素の配置を決定する制御のセットを有する。プロセッサ110は、水平置換制御ベクトル内のアドレスのセットに基づいて、複数の要素データ値のうちの取り出した要素データ値の少なくとも一部を出力ベクトル内に配置し得る。たとえば、Vtmp204内の要素データ値が置換され、出力ベクトル内に配置され得る。一実施例では、クロスバーを使用して水平置換が実装される。この実施例では、取り出した要素データ値の少なくとも一部が、クロスバーを使用して出力ベクトル内に配置され得る。40

#### 【 0 0 3 8 】

図2では、水平置換制御ベクトルがベクトルレジスタVv(124)内に格納されることがあり、出力ベクトルは、ベクトルレジスタファイル120からのVd(126)であり得る。

#### 【 0 0 3 9 】

一実施例では、Vv[0]=3であり、Vtmp[3]に対応する要素データ値がVd[0]に属することを示す。したがって、Vtmp[3]に対応する要素データ値である「l3」が、出力ベクトルVd[0]内に配置される。同様に、Vv[1]=1であり、Vtmp[1]に対応する要素データ値がVd[1]に属することを示す。したがって、Vtmp[1]に対応する要素データ値である「j1」が、出力ベクトルVd[1]内に配置される。同様に、Vv[2]=0であり、Vtmp[0]に対応する要素データ値がVd[2]に属することを示す。したがって、Vtmp[0]に対応する要素データ値である「i050

」が、出力ベクトルVd[2]内に配置される。同様に、Vv[3]=28であり、Vtmp[28]に対応する要素データ値がVd[3]に属することを示す。したがって、Vtmp[28]に対応する要素データ値である「i28」が、出力ベクトルVd[3]内に配置される。プロセッサ110は、同様の動作を実施して、Vtmp204内の他の要素データ値を出力ベクトルVd126内に配置し得る。

#### 【0040】

ベクトルレジスタ120は、アドレスが与えられる読み取りポートを有し得る。一実施例では、第1のサイクルでは、プロセッサ110が、垂直置換制御ベクトル(たとえば、図1のベクトルレジスタファイル120内のベクトルレジスタVu)からレジスタアドレスを読み取る。プロセッサ110は、同じタイプの1つの命令で32個の異なる動作を実施し得る。たとえば、ベクトルレジスタVuが垂直置換制御ベクトルを含む場合、プロセッサ110がベクトルレジスタVuから32個のレジスタアドレスを同時に読み取るように、プロセッサ110は、Vu[0] ~ Vu[31]に対して読み取り動作を実施し得る。次のサイクルで内部的に、プロセッサ110は、読み取ったレジスタアドレスに基づいて再びベクトルレジスタファイル120から読み取り、適切な要素データ値を取り出し得る。プロセッサ110がベクトルレジスタVuから読み取ったレジスタアドレスに基づいて32個の要素データ値を同時に取り出すように、プロセッサ110は取り出し動作を実施し得る。プロセッサ110は、32個の取り出した要素データ値をVtmp内に同時に配置し得る。

#### 【0041】

Vtmp内に格納された32個の取り出した要素データ値は、水平置換制御ベクトルを使用して、出力ベクトル内で水平に分布し得る。水平置換制御ベクトルは、出力ベクトルに対応するアドレスのセットを含み得る。プロセッサ110は、水平置換制御ベクトルを識別し、水平置換制御ベクトル内のアドレスのセットに基づいて、複数の要素データ値のうちの取り出した要素データ値の少なくとも一部を出力ベクトル内に配置し得る。プロセッサ110は、水平置換制御ベクトル内のアドレスのセットに基づいて、32個の取り出した要素データ値を出力ベクトル内に同時に配置し得る。その場合、出力ベクトルは、関心の対象の要素データ値を含み得る。

#### 【0042】

##### B. 例示的書込み命令

プロセッサ110はまた、要素データ値を少なくとも1つのベクトルレジスタ内に書き込む書込み命令を受け取り得る。プロセッサ110は、垂直置換制御ベクトルおよび水平置換制御ベクトルを使用して、要素データ値を少なくとも1つのベクトルレジスタ内に書き込み得る。書込み命令は、上記で論じた読み取り命令と類似の書き込みバージョンであり得る。

#### 【0043】

図3は、一実施形態による、要素データ値が少なくとも1つの出力ベクトル内に書き込まれることを示すブロックダイアグラム300である。

#### 【0044】

ダイアグラム300は、Vidx(Vd, Vv)=Vuを含む例示的書込み命令301を含む。命令301は、入力ベクトルレジスタ(たとえば、ベクトルレジスタVu)を読み取ること、ならびに垂直置換制御ベクトル(たとえば、ベクトルレジスタVd)および水平置換制御ベクトル(たとえば、ベクトルレジスタVv)に基づいて、入力ベクトルレジスタからの要素データ値を少なくとも1つのベクトルレジスタ(たとえば、ベクトルレジスタV4、V5、V6、およびV7)に書き込むことを含む。

#### 【0045】

ベクトルレジスタVu、Vv、およびVdは、ベクトルレジスタファイル120からのベクトルレジスタV0 ~ V7のいずれかでよく、ここで、u、v、およびdは、0から7までの任意の値でよい。命令は、Vu、Vv、およびVdについての特定の値を指定するオペコードに変換し得る。一実施例では、Vu=V0、Vv=V1、およびVv=V3である。Vuは、入力ベクトルレジスタを含むことがあり、Vvは、水平置換制御ベクトルを含むことがあり、Vdは、垂直置換制御ベクトルを含むことがある。

#### 【0046】

10

20

30

40

50

プロセッサ110は命令301を受け取り、実行し得る。命令301を実行することは、複数の要素データ値を含む入力ベクトルVu(122)を読み取ることを含み得る。たとえば、Vu[0]=u0、Vu[1]=u1、Vu[2]=u2、およびVu[3]=u3である。一実施例では、入力ベクトルは、少なくとも1つの出力ベクトルに書き込む実際の要素データ値を含む。

#### 【0047】

Vu内の要素データ値は、水平置換制御ベクトルに基づいて読み取られ、置換され得る。プロセッサ110は、アドレスのセットを含む水平置換制御ベクトル206を識別し得る。水平置換制御ベクトル206は、ベクトルレジスタファイル120からベクトルレジスタVv(124)内に格納され得る。したがって、プロセッサ110が水平置換制御ベクトルを識別したとき、プロセッサ110は、ベクトルレジスタファイル120内のベクトルレジスタVvを識別し得る。10

入力ベクトルVu内の複数の要素データ値のうちの要素データ値の少なくとも一部が、水平置換制御ベクトル206内のアドレスのセットに基づいて再構成され得る。複数の再構成された要素データ値が、一時ベクトルVtmp204内に配置され得る。

#### 【0048】

一実施例では、Vv[0]からのレジスタアドレス=3であり、プロセッサ110は、Vu[3]に格納された要素データ値「u3」を取り出し、取り出した要素データ値をVtmp[0]内に配置し得る。同様に、Vv[1]からのレジスタアドレス=1であり、プロセッサ110は、Vu[1]に格納された要素データ値「u1」を取り出し、取り出した要素データ値をVtmp[1]内に配置し得る。同様に、Vv[2]からのレジスタアドレス=0であり、プロセッサ110は、Vu[0]に格納された要素データ値「u0」を取り出し、取り出した要素データ値をVtmp[2]内に配置し得る。20

。プロセッサ110は、Vu内に格納された他の要素データ値を一時ベクトルVtmp内に配置するための同様の動作を実施し得る。

#### 【0049】

命令301を実行することはまた、複数の要素を含む垂直置換制御ベクトル202を識別することをも含むことがあり、複数の要素のうちの各要素はレジスタアドレスを含む。垂直置換制御ベクトル202は、ベクトルレジスタファイル120からベクトルレジスタVd(126)内に格納され得る。Vtmp内の要素データ値は、垂直置換制御ベクトル内のレジスタアドレスに基づいて、少なくとも1つのベクトルレジスタ内に配置され得る。具体的には、Vd内のレジスタアドレスが、Vtmp内の要素データ値を少なくとも1つのベクトルレジスタに垂直に書き込むために使用され得る。30

#### 【0050】

たとえば、図3では、Vd[0]=4であり、Vtmp[0]に対応する要素データ値がV4[0]に属することを示す。したがって、Vtmp[0]に対応する要素データ値である「i0」が、ベクトルレジスタV4[0]内に配置される。同様に、Vd[1]=5であり、Vtmp[1]に対応する要素データ値がV5[1]に属することを示す。したがって、Vtmp[1]に対応する要素データ値である「j1」が、ベクトルレジスタV5[1]内に配置される。同様に、Vd[2]=6であり、Vtmp[2]に対応する要素データ値がV6[2]に属することを示す。したがって、Vtmp[2]に対応する要素データ値である「k2」が、ベクトルレジスタV6[2]内に配置される。同様に、Vd[3]=7であり、Vtmp[3]に対応する要素データ値がV7[3]に属することを示す。したがって、Vtmp[3]に対応する要素データ値である「l3」が、ベクトルレジスタV7[3]内に配置される。プロセッサ110は、同様の動作を実施して、Vtmp204内の他の要素データ値を1つまたは複数のベクトルレジスタ(たとえば、ベクトルレジスタV4、V5、V6、およびV7)内に配置し得る。次いで、ベクトルレジスタは、入力ベクトルからの要素データ値を適切な場所に格納し得る。40

#### 【0051】

上記で論じ、ここでさらに強調するように、図1～図3は例にすぎず、例は特許請求の範囲を過度に限定すべきではない。

#### 【0052】

上記で示したように、置換制御ベクトル(たとえば、垂直置換制御ベクトルおよび/または水平置換制御ベクトル)は、データがプロセッサ110によって受け取られるときに更新される動的レジスタ内に格納され得る。たとえば、図1では、垂直置換制御ベクトルがベク50

トルレジスタ(たとえば、Vu)内に含まれ、水平置換制御ベクトルも、ベクトルレジスタファイルからのベクトルレジスタ(たとえば、Vv)内に含まれる。これは限定ではないものとし、置換制御ベクトルは、いくつかの方式で取り出され得る。

#### 【0053】

たとえば、置換制御ベクトル内に示されるパターンは、図2および図3に示されるものとは異なり得る。たとえば、図2の垂直置換制御ベクトルは、ベクトルレジスタV4、V5、V6、V7、V4、V5、V6、V7などから要素データ値を読み取ることを指定するパターンを有する。これは限定ではないものとし、任意のパターンが使用され得る。たとえば、プログラマは、任意のパターンを置換制御ベクトル内にプログラムし得る。

#### 【0054】

さらに、図3では、入力ベクトルVu内の値のすべてが、少なくとも1つの出力ベクトル内に書き込まれる。これは限定ではないものとする。たとえば、別の実施形態では、入力ベクトルVu内の1つまたは複数の要素データ値が、出力ベクトル内に書き込まれない。さらに、入力ベクトルVu内の要素データ値が、単一のベクトルレジスタまたは複数のベクトルレジスタに書き込まれ得る。一実施例では、垂直置換制御が同一のレジスタアドレスを含む場合、Vtmp内の要素データ値のすべてが、同一のベクトルレジスタ(たとえば、ベクトルレジスタV4)に書き込まれ得る。

#### 【0055】

##### C.スカラ値

さらに、置換制御ベクトル(たとえば、垂直置換制御ベクトルまたは水平置換制御ベクトル)が、ベクトルレジスタ以外のメモリ位置に格納され得る。一実施例では、置換制御ベクトルが、読み取り専用メモリ(ROM)内に格納され、ROMから読み取られ得る。例示的読み取り命令では、プロセッサ110は、Vd=Vidx(R,Vv)などの命令を受け取ることがあり、ここで、Rは、ROM内のデータ構造を参照するスカラ値である。垂直置換制御ベクトルは、ROM内のデータ構造(たとえば、テーブル)内に格納され得る。したがって、垂直置換制御ベクトルを識別するために、プロセッサ110は、スカラ値を使用してROM内のデータ構造内の垂直置換制御ベクトルを識別し得る。

#### 【0056】

別の例示的読み取り命令では、プロセッサ110は、Vd=Vidx(Vu,R)などの命令を受け取ることがあり、ここで、Rは、ROM内のデータ構造を参照するスカラ値である。水平置換制御ベクトルは、ROM内のデータ構造(たとえば、テーブル)内に格納され得る。したがって、水平置換制御ベクトルを識別するために、プロセッサ110は、スカラ値を使用してROM内のデータ構造内の水平置換制御ベクトルを識別し得る。

#### 【0057】

別の読み取り実施例では、プロセッサ110は、Vd=Vidx(R1,R2)などの命令を受け取ることがあり、ここで、R1は、ROM内の第1のデータ構造を参照する第1のスカラ値であり、R2は、ROM内の第2のデータ構造を参照する第2のスカラ値である。垂直置換制御ベクトルは、ROM内の第1のデータ構造(たとえば、テーブル)内に格納されることがあり、水平置換制御ベクトルは、ROM内の第2のデータ構造(たとえば、テーブル)内に格納され得る。したがって、垂直置換制御ベクトルを識別するために、プロセッサ110は、第1のスカラ値を使用してROM内の第1のデータ構造内の垂直置換制御ベクトルを識別することができ、水平置換制御ベクトルを識別するために、プロセッサ110は、第2のスカラ値を使用してROM内の第2のデータ構造内の水平置換制御ベクトルを識別し得る。

#### 【0058】

同様に、書き込み命令もスカラ値を含み得る。たとえば、プロセッサ110は、Vidx(R,Vv)=Vuなどの命令を受け取ることがあり、ここで、Rは、ROM内のデータ構造を参照するスカラ値である。垂直置換制御ベクトルは、ROM内のデータ構造(たとえば、テーブル)内に格納され得る。したがって、垂直置換制御ベクトルを識別するために、プロセッサ110は、スカラ値を使用してROM内のデータ構造内の垂直置換制御ベクトルを識別し得る。

#### 【0059】

10

20

30

40

50

別の例示的書込み命令では、プロセッサ110は、 $Vidx(Vd, R)=Vu$ などの命令を受け取ることがあり、ここで、Rは、ROM内のデータ構造を参照するスカラ値である。水平置換制御ベクトルは、ROM内のデータ構造(たとえば、テーブル)内に格納され得る。したがって、水平置換制御ベクトルを識別するために、プロセッサ110は、スカラ値を使用してROM内のデータ構造内の水平置換制御ベクトルを識別し得る。

#### 【0060】

別の書込み実施例では、プロセッサ110は、 $Vidx(R1, R2)=Vu$ などの命令を受け取ることがあり、ここで、R1は、ROM内の第1のデータ構造を参照する第1のスカラ値であり、R2は、ROM内の第2のデータ構造を参照する第2のスカラ値である。垂直置換制御ベクトルは、ROM内の第1のデータ構造(たとえば、テーブル)内に格納されることがあり、水平置換制御ベクトルは、ROM内の第2のデータ構造(たとえば、テーブル)内に格納され得る。したがって、垂直置換制御ベクトルを識別するために、プロセッサ110は、第1のスカラ値を使用してROM内の第1のデータ構造内の垂直置換制御ベクトルを識別することがあり、水平置換制御ベクトルを識別するために、プロセッサ110は、第2のスカラ値を使用してROM内の第2のデータ構造内の水平置換制御ベクトルを識別し得る。

10

#### 【0061】

これは、置換制御ベクトルを格納するためにベクトルレジスタを使用することが不要であり得るので、いくつかの実施形態では有利であり得る。したがって、ベクトルレジスタは、他のデータを格納するために解放され得る。さらに、置換制御ベクトル内にパターンをプログラムするためにコンピューティングサイクルを消費することが不要となり得るよう、置換制御ベクトルの値が事前格納された値であり得る。

20

#### 【0062】

スカラ値は、命令で指定され得る。一実施形態では、プロセッサ110はコプロセッサであり、別のプロセッサからスカラ値を受け取る。一実施形態では、プロセッサ110は、メインメモリまたはROMからスカラ値を受け取り得る。さらに、プロセッサ110は、他のプロセッサから垂直置換制御ベクトルおよび/または水平置換制御ベクトルを受け取り得る。

#### 【0063】

### III. 例示的レジスタファイル

図4は、一実施形態による、ベクトルレジスタファイルを示すブロックダイアグラムである。

30

#### 【0064】

一実施形態では、プロセッサ110は、ベクトルレジスタファイル120内のベクトルレジスタから読み取り、それに書き込むSIMDプロセッサである。一実施例では、ベクトルレジスタファイル120内の各ベクトルレジスタは、Pビット幅であるWord 0(W0)122、Pビット幅であるWord 1(W1)124、...、Pビット幅であるWord 31(W31)までを含み得る。Pは0よりも大きい整数であり得る。ベクトルレジスタは、バイトの最小の細分性から構築され得る。一実施例では、ベクトルレジスタファイル120は32個のベクトルレジスタを含み、各ベクトルレジスタは1024ビット幅である。各ベクトルレジスタは、32ビットをそれぞれ含む32ワードを含み得る。

40

#### 【0065】

一実施例では、Pは8の任意の倍数(たとえば、8、16、32、64など)であり得る。P=32である場合であっても、32ビットのデータよりも大きい構成が使用され得るように、置換制御は互いに隣接し得る。たとえば、ワードが32ビット幅であり、64ビット幅であるデータを扱うことが望ましい場合、システムが64ビットのデータを扱い、置換し得るように、32ビットチャンクでの同一の制御が隣接して配置され得る。

#### 【0066】

### IV. 例示的方法

図5は、一実施形態による、1つまたは複数の要素データ値を出力ベクトル内に配置するための方法500を示す流れ図である。方法500は限定を意味するものではなく、他の応用例で使用され得る。

50

## 【0067】

方法500はステップ510～550を含む。ステップ510では、複数の要素を含む垂直置換制御ベクトルを識別し、複数の要素のうちの各要素はレジスタアドレスを含む。一実施例では、プロセッサ110が、複数の要素を含む垂直置換制御ベクトルを識別し、複数の要素のうちの各要素はレジスタアドレスを含む。垂直置換制御ベクトル内に格納されたレジスタアドレスが、ベクトルレジスタファイル内の1つまたは複数のベクトルレジスタから要素データ値を読み取るために使用され得る。垂直置換制御ベクトルは、動的レジスタまたはスタティックメモリ内に格納され得る。たとえば、図2の読み取り命令では、プロセッサ110は、ベクトルレジスタファイルからのVuを垂直置換制御ベクトルと識別し得る。別の実施例では、プロセッサは、ROMから垂直置換制御ベクトルを取り出す。

10

## 【0068】

ステップ520では、複数の要素のうちの各要素について、垂直置換制御ベクトルからレジスタアドレスを読み取る。一実施例では、複数の要素のうちの各要素について、プロセッサ110が垂直置換制御ベクトルからレジスタアドレスを読み取る。垂直置換制御ベクトル内のレジスタアドレスは、1つまたは複数のベクトルレジスタから垂直に読み取るために使用され得る。プロセッサにとっての関心の対象の要素データ値が、レジスタアドレスに配置され得る。

## 【0069】

ステップ530では、読み取ったレジスタアドレスに基づいて、複数の要素データ値を取り出す。一実施例では、プロセッサ110が、読み取ったレジスタアドレスに基づいて複数の要素データ値を取り出す。取り出した複数の要素データ値は、一時ベクトル内に配置され得る。たとえば、図2では、ベクトルレジスタV4[0]のアドレスが、Vu[0]の垂直置換制御ベクトル内に格納される。次いで、ベクトルレジスタV4[0]の要素データ値が、一時ベクトル内に配置され得る。取り出した要素データ値は、プロセッサにとって関心の対象であり得る。

20

## 【0070】

ステップ540では、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別する。一実施例では、プロセッサ110が、出力ベクトルに対応するアドレスのセットを含む水平置換制御ベクトルを識別する。水平置換制御ベクトル内のアドレスのセットは、出力ベクトル内の(たとえば、一時ベクトルレジスタ内に格納された)取り出した複数の要素データ値を水平に構成するために使用され得る。水平置換制御ベクトルは、動的レジスタまたはスタティックメモリ内に格納され得る。たとえば、図2の読み取り命令では、プロセッサ110は、ベクトルレジスタファイルからのVvを水平置換制御ベクトルと識別し得る。別の実施例では、プロセッサは、ROMから水平置換制御ベクトルを取り出す。

30

## 【0071】

ステップ550では、水平置換制御ベクトル内のアドレスのセットに基づいて、複数の要素データ値のうちの取り出した要素データ値の少なくとも一部を出力ベクトル内に配置する。一実施例では、プロセッサ110が、水平置換制御ベクトル内のアドレスのセットに基づいて、複数の要素データ値のうちの取り出した要素データ値の少なくとも一部を出力ベクトル内に配置する。関心の対象の要素データ値は、本来は、その間に分散する他のデータと共に複数のレジスタに及んでいた可能性がある。次いで、出力ベクトルは、関心の対象の要素データ値のみを格納し得る。

40

## 【0072】

上記で論じたステップ510～550の前、間、または後に、追加の方法ステップが実施され得ることも理解されたい。たとえば、方法500は、要素データ値を少なくとも1つの出力ベクトル内に書き込むステップを含み得る。本明細書で説明される方法500のステップのうちの1つまたは複数が、必要に応じて省略され、組み合わされ、または異なるシーケンスで実施され得ることも理解されたい。

## 【0073】

図6は、一実施形態による、要素データ値をベクトルレジスタ内に書き込むための方法6

50

00を示す流れ図である。方法600は限定を意味するものではなく、他の応用例で使用され得る。

#### 【 0 0 7 4 】

方法600はステップ610～660を含む。ステップ610では、複数の要素データ値を含む入力ベクトルを読み取る。一実施例では、プロセッサ110が、複数の要素データ値を含む入力ベクトルを読み取る。たとえば、図3では、プロセッサ110は、ベクトルレジスタファイルからのVuを入力ベクトルと識別し得る。別の実施例では、プロセッサはROMから入力ベクトルを取り出す。入力ベクトル内に格納された要素データ値のうちの1つまたは複数が、水平置換制御ベクトルおよび垂直置換制御ベクトルに基づいて少なくとも1つのベクトルレジスタに書き込まれ得る。

10

#### 【 0 0 7 5 】

ステップ620では、アドレスのセットを含む水平置換制御ベクトルを識別する。一実施例では、プロセッサ110が、アドレスのセットを含む水平置換制御ベクトルを識別する。水平置換制御ベクトルは、動的レジスタまたはスタティックメモリ内に格納され得る。たとえば、図3の書き込み命令では、プロセッサ110は、ベクトルレジスタファイルからのベクトルレジスタVvを水平置換制御ベクトルと識別し得る。別の実施例では、プロセッサは、ROMから水平置換制御ベクトルを取り出す。

#### 【 0 0 7 6 】

ステップ630では、水平置換制御ベクトル内のアドレスのセットに基づいて、入力ベクトル内の複数の要素データ値のうちの要素データ値の少なくとも一部を再構成する。一実施例では、プロセッサ110が、水平置換制御ベクトル内のアドレスのセットに基づいて、入力ベクトル内の複数の要素データ値のうちの要素データ値の少なくとも一部を再構成する。具体的には、水平置換制御ベクトル内に格納されたアドレスのセットは、入力ベクトル内の複数の要素データ値を水平に再構成するために使用され得る。

20

#### 【 0 0 7 7 】

ステップ640では、再構成した複数の要素データ値を一時ベクトル内に配置する。一実施例では、プロセッサ110が、再構成した複数の要素データ値を一時ベクトル内に配置する。たとえば、図3では、Vtmp204が、再構成した複数の要素データ値を格納する一時ベクトルであり得る。

#### 【 0 0 7 8 】

30

ステップ650では、複数の要素を含む垂直置換制御ベクトルを識別し、複数の要素のうちの各要素はレジスタアドレスを含む。一実施例では、プロセッサ110が、複数の要素を含む垂直置換制御ベクトルを識別し、複数の要素のうちの各要素はレジスタアドレスを含む。垂直置換制御ベクトル内に格納されたレジスタアドレスは、一時ベクトルからの要素データ値を少なくとも1つのベクトルレジスタに垂直に書き込むために使用され得る。垂直置換制御ベクトルは、動的レジスタまたはスタティックメモリ内に格納され得る。たとえば、図3の書き込み命令では、プロセッサ110は、ベクトルレジスタファイルからのベクトルレジスタVdを垂直置換制御ベクトルと識別し得る。別の実施例では、プロセッサは、ROMから垂直置換制御ベクトルを取り出す。

#### 【 0 0 7 9 】

40

ステップ660では、垂直置換制御ベクトル内のレジスタアドレスに基づいて、一時ベクトル内の要素データ値を少なくとも1つのベクトルレジスタ内に配置する。一実施例では、プロセッサ110が、垂直置換制御ベクトル内のレジスタアドレスに基づいて、一時ベクトル内の要素データ値を少なくとも1つのベクトルレジスタ内に配置する。たとえば、図3では、一時ベクトル内の要素データ値が、ベクトルレジスタVd内のレジスタアドレスに基づいて、ベクトルレジスタV4、V5、V6、および/またはV7内に配置される。次いで、入力ベクトルVu内に格納されたデータ要素値は、1つまたは複数のベクトルレジスタに適切に書き込まれ得る。

#### 【 0 0 8 0 】

上記で論じたステップ610～660の前、間、または後に、追加の方法ステップが実施され

50

得ることも理解されたい。たとえば、方法600は、1つまたは複数の要素データ値をベクトルレジスタ内に配置するステップを含み得る。本明細書で説明される方法600のステップのうちの1つまたは複数が、必要に応じて省略され、組み合わされ、または異なるシーケンスで実施され得ることも理解されたい。

【 0 0 8 1 】

V. 例示的ワイヤレスデバイス

図7は、一実施形態による、デジタル信号プロセッサを含むワイヤレスデバイス700を示すブロックダイアグラムである。デバイス700は、デジタル信号プロセッサ(DSP)701などのプロセッサを含む。命令201および/または命令301がメモリ750内に格納され得ることがあり、VRF120がDSP701内に含まれ得る。一実施例では、DSP701およびVRF129が、図1～図4のうちの1つまたは複数に従って、かつ/または図5および図6の方法のうちの1つまたは複数に従って、またはそれらの任意の組合せに従って、命令201および/または命令301を処理し得る。

10

【 0 0 8 2 】

図7はまた、DSP701およびディスプレイ732に結合されるディスプレイコントローラ730をも示す。コーダ/デコーダ(コーデック)734もDSP701に結合され得る。スピーカ736およびマイクロフォン738がコーデック734に結合され得る。さらに、ワイヤレスコントローラ740が、DSP701およびワイヤレスアンテナ748に結合され得る。一実施形態では、DSP701、ディスプレイコントローラ730、メモリ750、コーデック734、およびワイヤレスコントローラ740が、システムインパッケージまたはシステムオンチップデバイス756内に含まれる。

20

【 0 0 8 3 】

一実施形態では、入力デバイス730および電源760が、システムオンチップデバイス756に結合される。さらに、一実施形態では、図7に示されるように、ディスプレイ732、入力デバイス730、スピーカ736、マイクロフォン738、ワイヤレスアンテナ748、および電源760は、システムオンチップデバイス756の外部にある。ディスプレイ732、入力デバイス730、スピーカ736、マイクロフォン738、ワイヤレスアンテナ748、および電源760の各々が、インターフェースやコントローラなどのシステムオンチップデバイス756の構成要素に結合され得る。

【 0 0 8 4 】

30

本明細書で開示される実施形態に関して説明した様々な例示的論理ブロック、構成、モジュール、回路、およびステップが、電子的ハードウェア、コンピュータソフトウェア、または両者の組合せとして実装され得ることを当業者ならさらに理解されよう。ハードウェアおよびソフトウェアのこの互換性を明確に示すために、様々な例示的構成要素、ブロック、構成、モジュール、回路、およびステップについて、その機能の点で一般的に上記で説明した。そのような機能がハードウェアとして実装されるか、それともソフトウェアとして実装されるかは、特定の応用例、およびシステム全体に対して課される設計制約に依存する。当業者は、説明した機能をそれぞれの特定の応用例について様々な方式で実装することができるが、そのような実装判断が、本開示の範囲からの逸脱を引き起こすと解釈すべきではない。

40

【 0 0 8 5 】

本明細書で開示される実施形態に関して説明した方法のステップは、直接的にハードウェアで、プロセッサによって実行されるソフトウェアモジュールで、またはその2つの組合せで実施され得る。ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、プログラマブル読み取り専用メモリ(PROM)、消去可能プログラマブル読み取り専用メモリ(EPROM)、電気消去可能プログラマブル読み取り専用メモリ(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、コンパクトディスク読み取り専用メモリ(CD-ROM)、または当技術分野で周知の任意の他の形態の記憶媒体内に常駐し得る。プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるよう、例示的記憶媒体がプロセッサに結合される。代替実施形態では、記憶媒

50

体はプロセッサと一体であり得る。プロセッサおよび記憶媒体は、特定用途向け集積回路(ASIC)内に常駐し得る。ASICは、コンピューティングデバイスまたはユーザ端末内に常駐し得る。代替実施形態では、プロセッサおよび記憶媒体は、別個の構成要素としてコンピューティングデバイスまたはユーザ端末内に常駐し得る。

【0086】

開示される実施形態の先の説明は、開示される実施形態を当業者が作成または使用することを可能にするために与えられる。これらの実施形態に対する様々な修正が当業者には容易に理解されることになり、本明細書で定義される原理は、本開示の範囲から逸脱することなく他の実施形態に適用され得る。したがって、本開示は、本明細書に示される実施形態に限定されないものとし、以下の特許請求の範囲で定義される原理および新規な特徴に一致する、可能な最も広い範囲が与えられるべきである。したがって、本開示は特許請求の範囲のみによって限定される。

10

【符号の説明】

【0087】

|     |                  |    |

|-----|------------------|----|

| 110 | プロセッサ            |    |

| 120 | ベクトルレジスタファイル     |    |

| 122 | ベクトルレジスタV0       |    |

| 122 | Word 0(W0)       |    |

| 124 | ベクトルレジスタV1       |    |

| 124 | Word 1(W1)       | 20 |

| 126 | ベクトルレジスタV2       |    |

| 127 | ベクトルレジスタV3       |    |

| 128 | ベクトルレジスタV4       |    |

| 129 | VFR              |    |

| 130 | ベクトルレジスタV5       |    |

| 132 | ベクトルレジスタV6       |    |

| 134 | ベクトルレジスタV7       |    |

| 201 | 命令               |    |

| 202 | 垂直置換制御ベクトル       |    |

| 204 | ベクトルレジスタVtmp     | 30 |

| 206 | 水平置換制御ベクトル       |    |

| 301 | 命令               |    |

| 700 | ワイヤレスデバイス        |    |

| 701 | デジタル信号プロセッサ(DSP) |    |

| 730 | ディスプレイコントローラ     |    |

| 730 | 入力デバイス           |    |

| 732 | ディスプレイ           |    |

| 734 | コーダ/デコーダ(コーデック)  |    |

| 736 | スピーカ             |    |

| 738 | マイクロフォン          | 40 |

| 740 | ワイヤレスコントローラ      |    |

| 748 | ワイヤレスアンテナ        |    |

| 750 | メモリ              |    |

| 756 | システムオンチップデバイス    |    |

| 760 | 電源               |    |

【図1】

【図2】

【 図 3 】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 デヴィッド・ジェイ・ホイル

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 マーク・エム・ホフマン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

合議体

審判長 辻本 泰隆

審判官 須田 勝巳

審判官 山崎 慎一

(56)参考文献 米国特許第5996057(US, A)

特開2001-273277(JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 17/16