(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-508573

(P2005-508573A)

(43) 公表日 平成17年3月31日(2005.3.31)

(51) Int.Cl.<sup>7</sup>

H01L 21/768

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792

F 1

H01L 21/90

C

テーマコード(参考)

5FO33

H01L 27/10

434

5FO83

H01L 29/78

371

5F101

審査請求 未請求 予備審査請求 有 (全 29 頁)

(21) 出願番号 特願2003-542676 (P2003-542676)

(86) (22) 出願日 平成14年11月8日 (2002.11.8)

(85) 翻訳文提出日 平成16年5月7日 (2004.5.7)

(86) 国際出願番号 PCT/US2002/035910

(87) 国際公開番号 WO2003/040436

(87) 国際公開日 平成15年5月15日 (2003.5.15)

(31) 優先権主張番号 09/986,263

(32) 優先日 平成13年11月8日 (2001.11.8)

(33) 優先権主張国 米国(US)

(71) 出願人 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ピイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68(番地なし)

(74) 代理人 100099324

弁理士 鈴木 正剛

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】 タングステンプラグ中のボイドを除去する方法

## (57) 【要約】

絶縁体層(200)内の開口部をW(202)で充填して、レーザー・サーマル・アニールを行って、ボイド(203)を除去または相当量減少させることで、信頼性のあるコンタクト/ピアを形成する。実施形態は、層間絶縁膜(200)内のコンタクト/ピア用開口部を充填するためにW(202)をデポジションする処理と、N<sub>2</sub>中でレーザー・サーマル・アニール(30)を行って前記コンタクト/ピア用開口部を充填するWの温度を上昇させて前記Wをリフローさせ、それによってボイド(203)を除去する処理とを含む。実施形態は、レーザー・サーマル・アニールの前またはその後で、CMPを実行する処理を含む。

**【特許請求の範囲】****【請求項 1】**

半導体装置の製造方法であって、

絶縁体層(200)に開口部を形成する処理と、

前記開口部にタンゲステン(W)(202)をデポジションする処理と、

前記デポジションされたWをレーザー・サーマル・アニール(30)する処理とを含む製造方法。

**【請求項 2】**

前記開口部を充填するデポジションされたW(202)に、約0.78から約1.10ジユール/平方センチメーターの放射フルエンスで、パルスレーザー光ビーム(30)を照射することにより、レーザー・サーマル・アニールする処理を含む、請求項1記載の製造方法。 10

**【請求項 3】**

前記開口部を充填するデポジションされたWを摂氏約3000度から約3600度の温度まで加熱して、それによって前記開口部内のWをリフローさせる、レーザー・サーマル・アニール処理(30)を含む、請求項2記載の製造方法。

**【請求項 4】**

窒素(N<sub>2</sub>)中でレーザー・サーマル・アニールする処理(30)を含む、請求項1記載の製造方法。

**【請求項 5】**

約200から約2000sccmの流量のN<sub>2</sub>を用いるレーザー・サーマル・アニール処理(30)を含む、請求項4記載の製造方法。 20

**【請求項 6】**

前記Wのデポジションの前に、前記開口部をライニングするバリア層(201)をデポジションする処理を含む、請求項1記載の製造方法。

**【請求項 7】**

レーザー・サーマル・アニールの後で、化学機械研磨(CMP)を実行して、前記開口部内の前記W(50)の上面と前記絶縁体層(200)の上面とが実質的にともに平坦になるようにする処理を含む、請求項1記載の製造方法。

**【請求項 8】**

レーザー・サーマル・アニールの前に、化学機械研磨(CMP)を実行して、前記W(80)の上面と前記絶縁体層(200)の上面とが実質的にともに平坦になるようにする処理を含む、請求項1記載の製造方法。 30

**【請求項 9】**

前記開口部を充填するデポジションされたW(202)に、約0.78から約1.10ジユール/平方センチメーターの放射フルエンスで、パルスレーザー光ビーム(30)を照射することにより、レーザー・サーマル・アニールする処理を含む、請求項4記載の製造方法。

**【請求項 10】**

前記開口部を充填するデポジションされたW(202)を摂氏約3000度から約3600度の温度まで加熱して、それによって前記開口部内のWをリフローさせる、レーザー・サーマル・アニール処理(30)を含む、請求項9記載の製造方法。 40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、正確にサブミクロン構造が形成された半導体装置を製造するための方法に関する。本発明は、信頼性の高い低抵抗のコンタクト/ビアを持つ、高密度な多層構造のフラッシュメモリ半導体装置の製造に特に適用可能である。

**【背景技術】****【0002】**

半導体回路のジオメトリ(形状)がサブミクロン体制(regime)に深く突入し続けるにつれ、必要とされる信頼性および回路速度を持つ個々の半導体装置を正確に形成することが 50

段々と難しくなってきている。設計ルールが約0.15ミクロン以下、例えば約0.12ミクロン以下のフラッシュメモリ装置の製造における実装が特に問題となっている。

#### 【0003】

従来の半導体装置は、様々な要素、例えばトランジスタが形成される半導体基板、および続いて形成される複数の上部の層間絶縁膜および導電パターンを含み、これらの中で導電ラインを有する相互接続システムが形成される。一般に、異なったレベル（つまり、上のレベルと下のレベル）にある導電パターンは、ビア（via）ホールを充填する導電プラグによって電気的に接続され、コンタクトホールを充填する導電プラグは、半導体基板上の能動領域、例えばソース／ドレイン領域との間で電気的接点を形成する。ビアホールを埋める導電プラグは、一般的に、少なくとも一つの導電構造を含む導電レベル上に層間絶縁膜（ILD）をデポジションし、従来のフォトリソグラフィックおよびエッチング技術によってILDを貫通する開口部を形成し、その開口部を導電材料で充填することによって形成される。ILDの表面上の余分な導電材料または表面部分は、通常化学機械研磨（CMP）によって除去される。そのための方法の一つとして知られるダマシン技術は、基本的に、ILD内に開口部を形成し、その開口部を金属で充填する。デュアルダマシン技術は、上部のトレンチ部と繋がる下部のコンタクトホールまたはビアホール部を有する開口部を形成し、その開口部を導電材料、通常は金属で充填して、上部の導電ラインと電気的に接触する導電プラグを同時に形成する。

#### 【0004】

ジオメトリがサブミクロン体制に深く進むにつれて、信頼性の高い、低抵抗の接点および相互接続を形成するのが特に問題になってきている。例えば、コンタクト／ビア開口部の直径が小さくなり、アスペクト比（深さ／直径）が大きくなる（約4：1以上）につれて、開口部は、継ぎ目やコンタクトまたはビアの中央部分を通る孔（porosity）またはボイド（void）の形態を取る芯抜き（coring）などの欠陥に対してより脆弱になってきている。そのようなボイドによって、高い、不安定な接触抵抗が分布することになり、フラッシュメモリ装置およびマイクロプロセッサに欠陥および低いエレクトロマイグレーション耐性をもたらすことになる。

#### 【0005】

従って、改善された信頼性を持つ半導体装置の製造を可能にする方法が求められている。そのような半導体装置にはMOSトランジスタを有する半導体装置が含まれ、電気的消去可能なプログラマブル・リード・オンリー・メモリ（EEPROM）装置などのフラッシュメモリ装置も含まれる。また、深いサブミクロンレンジの構造を持ち、改善されたエレクトロマイグレーション耐性を持つ信頼性の高い、低抵抗のコンタクトおよびビアを含む、半導体装置の製造を可能にする方法に対する特別なニーズがある。

#### 【発明の開示】

#### 【発明の概要】

#### 【0006】

本発明の特長は、深いサブミクロン体制の構造を持ち、低く、安定した接触抵抗分布および改善されたエレクトロマイグレーション耐性を示す高い信頼性のビアおよびコンタクトを持つ、半導体装置の製造方法である。

本発明のさらなる特長およびその他の特徴は、この後の発明の詳細な説明で説明される。その一部は以下の説明を理解した当業者には明白なものであり、または本発明を実行することによって学ぶことができる。本発明の特徴は、添付の特許請求の範囲に特に記載されているように、実現し、得ることができる。

本発明に従って、上述の、およびその他の特長の一部は半導体装置を製造する方法によって達成される。当該方法は、絶縁体層に開口部を形成する処理と、その開口部を充填するためにタンゲステン（W）をデポジション（deposition）する処理と、開口部内のタンゲステンをレーザー・サーマル（熱）・アニールする（laser thermal annealing）処理とを含む。

#### 【0007】

10

20

30

40

50

本発明の実施形態は、ホウ素リンドープされたケイ酸塩ガラス (BPSG, boron-phosphorus-doped silicated glass) またはBPSG層の上にテトラエトキシシラン (TEOS, tetraethyl orthosilicate) から得られたシリコン酸化物層を載せた合成酸化物層などの酸化物絶縁体層に開口部を形成する処理と、チタン (Ti) の第1バリア層をデポジションし、次に、チタン層上に窒化チタンの層を、少なくとも一層、例えば三層デポジションする。次に、開口部をタングステン (W) で充填する。本発明の一実施形態においては、充填された開口部に向けたレーザー光ビームをデポジションされたタングステンに当てるにより、レーザー・サーマル・アニールが実行される。このレーザー・サーマル・アニールは、通常、放射フルエンス約0.78から約1.10ジュール/平方センチメートルで、短時間、例えば約10から約100ナノ秒の間、窒素 ( $N_2$ ) 中で行われ、開口部内のタングステンの温度を上昇させて、充填された開口部内のタングステンを溶融させリフローさせる (例えば、摂氏約3000度から約3600度の温度)。次に、化学機械研磨 (CMP) を実行する。本発明の他の実施形態では、CMPはレーザー・サーマル・アニールの前に実行される。

#### 【0008】

本発明のさらなる特長は、この後の詳細な説明から当業者に容易に明白になるであろう。詳細な説明中の本発明の実施形態は、本発明を実施するために最良の形態であると考えられるものを単に例示して説明したにすぎない。本発明はその他の、異なった実施形態において実施することができ、そしてそのいくつかの細かい部分は様々な明白な観点から変更することが可能であるが、それらはすべて本発明から乖離するものではない、ことを理解していただきたい。従って、添付の図面および説明は本質的に例示のためのものとして取り扱われるべきであって、制限目的のものとして取り扱われるべきではない。

#### 【発明を実施するための最良の形態】

#### 【0009】

図2から図8において、類似の要素または構造は、類似の参照符号で記載される。本発明は、不所望なホール (孔) の形成から生じるタングステンコンタクト / ビアの信頼性の問題と、それに伴う高く、不安定な接触抵抗の分布および低いエレクトロマイグレーション耐性の問題を取り扱い、解決する。これらの問題は、デバイスのジオメトリがサブミクロン体制に深く縮小されたときに顕著となる。例えば、コンタクト / ビア開口部の幅が約0.225から約0.257ミクロンまで、例えば約0.25ミクロンにまで減少し、コンタクト / ビア開口部の深さが約0.81から約0.99ミクロンまで、例えば約0.90ミクロン以上にまで延びて、アスペクト比が4:1またはそれ以上に近づくと、ボイドの形成なしにコンタクト / ビア開口部を埋めるのは非常に困難になる。本発明はこの問題を取り扱い、解決するのに、高いアスペクト比を持つコンタクト / ビア開口部を従来の方法で充填して、ボイドを持つタングステンプラグを形成する従来の方法から始める。本発明は、高いアスペクト比を持つコンタクト / ビア開口部の充填の際に形成されたボイドの除去を可能にする効率的な方法を提供し、それによって接触抵抗を減少させ、抵抗値の分布をより狭くし、エレクトロマイグレーション耐性 (特性) を改善する点において、従来のやり方とは異なる。

#### 【0010】

本発明の実施形態に従って、コンタクト / ビア開口部を、酸化物層などの絶縁体層、例えばBPSGまたはTEOSから得られたシリコン酸化物の層に形成する。次に、バリア層の合成物が開口部のライニング (内張り、内層) を形成する。本発明の実施形態に従って、第1の (最初の) 薄いチタン (Ti) 層をデポジションして開口部をライニングし、第1のチタン層の上にチタン窒化物層をデポジションする。次に、タングステンを従来の方法でデポジションし、表土 (overburden; オーバーバーデン) を形成する。この時点で、コンタクト / ビア開口部を充填しているタングステンは、エレクトロマイグレーション耐性を含むデバイスの性能に悪影響を与える不所望なボイドまたは孔 (pore) を含んでいる。

#### 【0011】

本発明の実施形態に従って、開口部を充填するタングステンは、開口部内のタングステンに向けられたパルスレーザー光ビームの照射により、レーザー・サーマル・アニールされる。このレーザー・サーマル・アニールは、放射フルエンス約0.78から約1.10ジュール /

10

20

30

40

50

平方センチメートルで、約200から約2000sccmの流量でN<sub>2</sub>を流しながら行われる。レーザー・サーマル・アニールの間、開口部内のタングステンの温度は摂氏約3000度から約3600度まで上昇し、タングステンを溶融させリフローさせる。これによって、ボイドが除去される。次に、従来の方法で化学機械研磨(CMP)を実行して、開口部を充填しているタングステンの上面と絶縁体層の上面とが実質的にともに平坦に(co-planar)なるようにする。本発明の他の実施形態では、CMPはレーザー・サーマル・アニールの前に実行される。

#### 【0012】

本発明の実施形態に従ったレーザー・サーマル・アニールの使用による相互接続中のボイドの減少および接触抵抗の低減はいくつかの有利性をもたらす。例えば、レーザー・サーマル・アニールは、開口部を充填しているタングステンを目標とする際にピンポイントで正確に狙うことができ、それによってウェハの他の部分の温度を必要に上昇させて、不適切な不純物拡散などの様々な問題を引き起こすことを防止することができる。

#### 【0013】

本発明の実施形態を実現する際には、約10から約2000mJ/cm<sup>2</sup>/パルスの間のエネルギー、例えば約100から約400mJ/cm<sup>2</sup>/パルスで動作可能なレーザー光源を使用した、商業的に提供されている様々なレーザー装置の任意のものを採用することができる。そのようなレーザーアニールを、マスクを用いて、またはマスクなしに実行できる装置が、商業的に提供されている。Verdant Technologies社のレーザーアニール装置は一例であって、照射波長308nmで動作する。

#### 【0014】

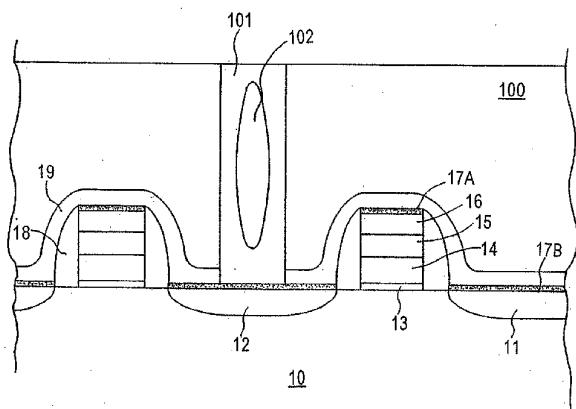

図1は、本発明が取り扱うタングステンプラグのボイド形成の問題を示す図であって、基板10にトランジスタが形成されている。トランジスタは、MOSトランジスタおよび/またはデュアルゲートメモリセルトランジスタを含みうる。デュアルゲートメモリセルトランジスタは、フローティングゲートおよびコントロールゲートを有し、それらの間にポリ層間(interpoly)絶縁膜(ONO)が配置されている。

#### 【0015】

例えば、トランジスタは、トンネル酸化物13、フローティングゲート電極14、ONOスタッカポリ層間絶縁膜15およびコントロールゲート16を含みうる。金属シリサイドの層17Aがゲート電極スタッカの上面に形成されている。金属シリサイドの層17Bがソース/ドレイン領域11, 12の上に形成される。シリコン酸化物、シリコン酸化窒化物またはシリコン窒化物などの絶縁物サイドウォールスペーサ18がゲート電極の側面に形成され、一般的にその上にシリコン窒化物のエッチングトップ層19がデポジションされる。BPSGまたはBPSGとその上に形成されるTEOSから得られたシリコン酸化物からなる合成物などの絶縁体層100が、約7500オングストロームから約8500オングストロームの間、例えば約8000オングストロームの厚さにデポジションされる。

#### 【0016】

次に、従来のフォトリソグラフィー技術およびエッチング技術を用いて、絶縁体層100にコンタクト用開口部を形成し、ソース/ドレイン領域12を露出させる。次に、タングステンをデポジションして、コンタクト用開口部を充填し、表土(オーバーバーデン)を形成する。続いて、CMPを行い、不所望な程度の多孔度102を有するタングステンプラグ101を残す。本発明はこの特定の問題を効率的な方法で効率的に解決し、それによってそのようなボイドを相当程度減少させ、または除去する。それによって、同時にエレクトロマイグレーション耐性およびデバイスの信頼性が改善される。

#### 【0017】

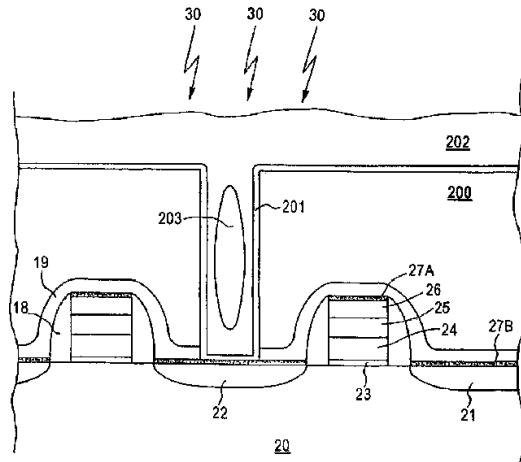

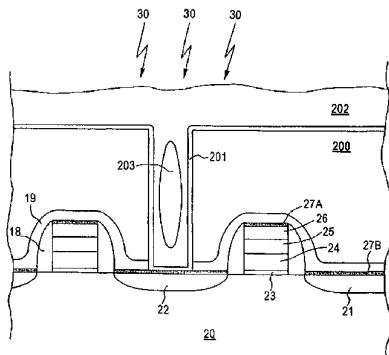

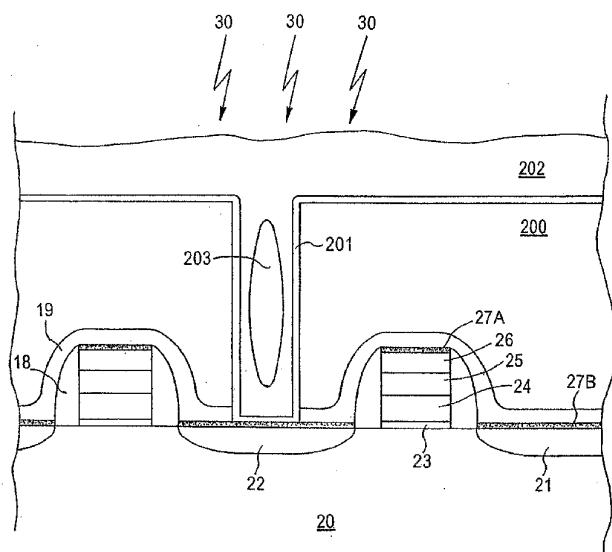

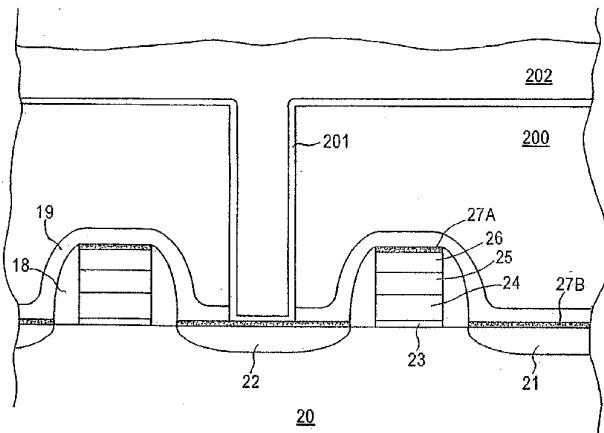

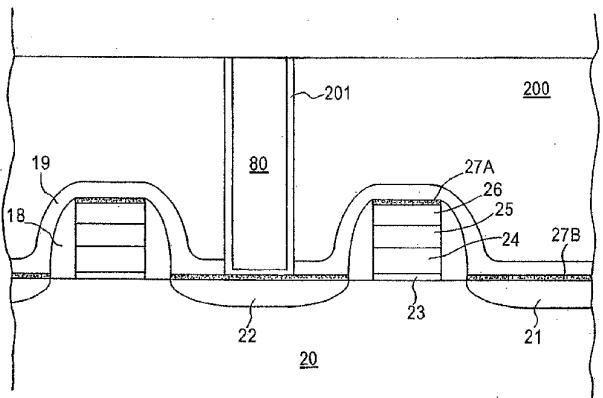

本発明の実施形態を図2から図5に示す。図2において、トランジスタが基板20に形成されている。トランジスタは、MOSトランジスタおよび/またはデュアルゲートメモリセルトランジスタを含みうる。デュアルゲートメモリセルトランジスタは、フローティングゲートおよびコントロールゲートを有し、それらの間にポリ層間(interpoly)絶縁膜(ONO)が配置されている。例えば、トランジスタは、トンネル酸化物23、フローティング

10

20

30

40

50

ゲート電極 24、ONO スタックポリ間絶縁膜 25 およびコントロールゲート 26 を含みうる。金属シリサイドの層 27A、例えばニッケルシリサイドがゲート電極スタックの上面に形成される。金属シリサイドの層 27B、例えばニッケルシリサイドがソース／ドレイン領域 21, 22 の上に形成される。シリコン酸化物、シリコン酸化窒化物またはシリコン窒化物などの絶縁物サイドウォールスペーサ 28 がゲート電極の側面に形成され、一般的にその上にシリコン窒化物のエッチング層 29 がデポジションされる。BPSG または BPSG とその上に形成される TEOS から得られたシリコン酸化物からなる合成物などの絶縁体層 200 が、約 7500 オングストロームから約 8500 オングストロームの間、例えば約 8000 オングストロームの厚さにデポジションされる。

## 【0018】

10

次に、従来のフォトリソグラフィー技術およびエッチング技術を用いて、絶縁体層 200 にコンタクト用開口部を形成し、ソース／ドレイン領域 22 を露出させる。コンタクト用開口部は、一般的に、約 4 : 1 以上のアスペクト比（深さ／直径）を持つ。

## 【0019】

次に、チタンの第 1 層およびその上の窒化チタン層などの合成物バリア層 201 をデポジションして、開口部をライニングする。次に、タングステンをデポジションして開口部を充填し、表土（オーバーバーデン）202 を形成する。コンタクト用開口部の高アスペクト比に起因して、タングステンプラグに相当量のボイド 203 が発生する。

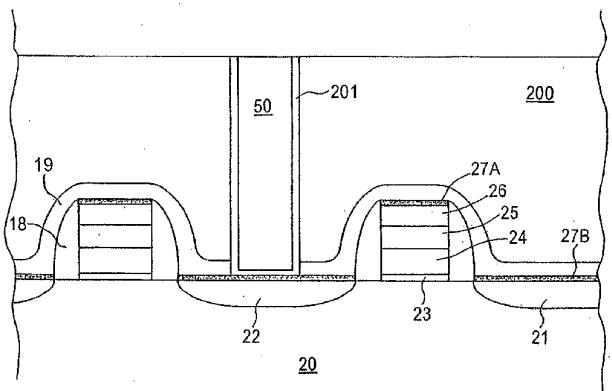

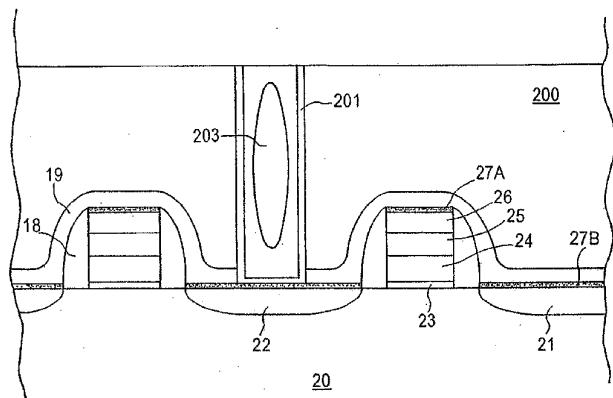

## 【0020】

20

本発明の実施形態に従って、図 3 に矢印 30 で示すように、充填された開口部に向けたパルスレーザー光ビームをデポジションされたタングステンに当てるにより、レーザー・サーマル・アニールを実行する。このレーザー・サーマル・アニールは、通常、放射フルエンス約 0.78 から約 1.10 ジュール／平方センチメートルの間で、約 10 から約 100 ナノ秒間行われ、プラグ内のタングステンの温度を摂氏約 3000 度から約 3600 度まで上昇させて、タングステンを溶融させリフローさせてボイドを除去する（図 4 参照）。次に CMP を行い、図 5 に示すような構造を得る。当該構造では、タングステンプラグ 50 にボイドはない。

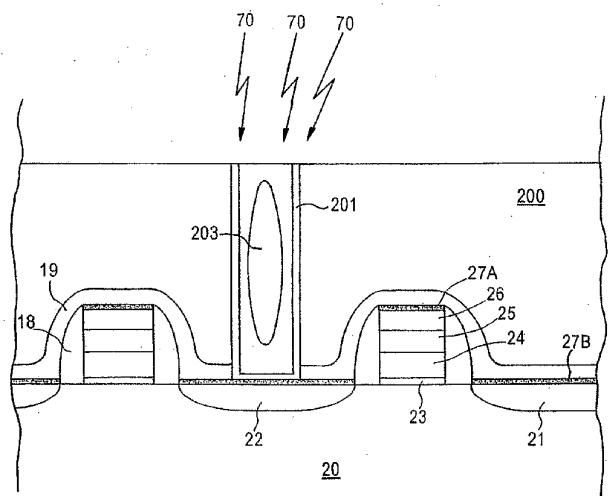

## 【0021】

30

本発明の他の実施形態においては、図 6 から図 8 に示すように、レーザー・サーマル・アニールの前に CMP を行う。図 6 に示された構造は、図 2 に示された構造に CMP を施した後のものである。次に、図 7 に示すように、タングステンプラグに向けられたパルスレーザー光ビーム 70 の照射により、レーザー・サーマル・アニールを行い、リフローを生じさせてボイドを除去する。図 8 はその結果としての構造を示し、この構造におけるタングステンプラグ 80 にはボイドがない。

## 【0022】

40

本発明は、例えば 4 以上の高アスペクト比を持ち、ボイドがない、または相当程度ボイドを減少させたタングステンコンタクトおよび／またはビアを有する相互接続の形成を可能にする方法を提供する。それにより、接触抵抗を減らし、接触抵抗値の分布を安定させて、より幅の狭い抵抗値分布をもたらし、デバイスの信頼性を改善し、エレクトロマイグレーション耐性を改善する。本発明は、改善された信頼性を持ち、回路速度を高速化した様々な種類の半導体装置のうち任意のものの製造において、産業上の利用可能性を持つ。本発明は、深いサブミクロン体制の設計構造を持つ半導体装置、例えば、相当程度信頼性が改善され、回路速度が向上し、エレクトロマイグレーション耐性が向上し、製造効率の改善が実現された、約 0.12 ミクロン以下の設計ルールを持つフラッシュメモリデバイス（例えば EEPROM）の製造において特に利用可能性を持つ。

## 【0023】

上述の詳細な説明においては、その特有の例示的な実施形態を参照して本発明を説明した。しかしながら、添付の特許請求の範囲に記載されているように、本発明のより広い範囲から離れることなしに、様々な変形および変更を加えることができるることは明らかである。従って、詳細な説明および図面は例示のためのものと取り扱われるべきであって、限定

50

的なものとして取り扱われるべきではない。本発明は他の様々な組み合わせおよび環境において使用可能であり、ここに明示した発明概念の範囲内で変更または変形が可能であることは理解できるであろう。

【図面の簡単な説明】

【0024】

【図1】本発明によって取り扱われ、解決されるタングステンプラグのボイドの問題を示す図。

【図2】本発明の一実施形態である方法の連続する段階のうちの一つを示す図。

【図3】本発明の一実施形態である方法の連続する段階のうちの一つを示す図。

10

【図4】本発明の一実施形態である方法の連続する段階のうちの一つを示す図。

【図5】本発明の一実施形態である方法の連続する段階のうちの一つを示す図。

【図6】本発明の他の実施形態である方法の連続する段階のうちの一つを示す図。

【図7】本発明の他の実施形態である方法の連続する段階のうちの一つを示す図。

【図8】本発明の他の実施形態である方法の連続する段階のうちの一つを示す図。

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

15 May 2003 (15.05.2003)

PCT

(10) International Publication Number

WO 03/040436 A1(51) International Patent Classification<sup>5</sup>: C25D 5/50, I1011, 21/20, 23/522

(21) International Application Number: PCT/US02/35910

(22) International Filing Date: 8 November 2002 (08.11.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 09/986,263 8 November 2001 (08.11.2001) US

(71) Applicant: ADVANCED MICRO DEVICES, INC. [US/US]; One AMD Place, Mail Stop 68, P.O. Box 3453, Sunnyvale, CA 94088-3453 (US).

(72) Inventors: NGO, Minh, Van; 40986 Canyon Heights Drive, Fremont, CA 94539 (US); PATON, Eric; 498 Rio Grande Court, Morgan Hill, CA 95037 (US).

(74) Agent: RODDY, Richard, J.; Advanced Micro Devices, Inc., One AMD Place, Mail Stop 68, Sunnyvale, CA 94088-3453 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DK, DM, DZ, EC, FI, HS, HU, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, ME, MN, MW, MX, MZ, NO, NZ, OM, PL, PI, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SI, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report

[Continued on next page]

(54) Title: METHOD OF ELIMINATING VOIDS IN W PLUGS

WO 03/040436 A1

(57) Abstract: Reliable contacts/vias are formed by filling an opening in a dielectric layer (200) with W (202) and laser thermal annealing (30) to eliminate or significantly reduce voids (203). Embodiments include depositing W (202) to fill a contact/via opening in an interlayer dielectric (200), laser thermal annealing (30) in N<sub>2</sub> to elevate the temperature of the W filling the contact/via opening and reflow the W thereby eliminating voids (203). Embodiments include conducting CMP either before or subsequent to laser thermal annealing.

---

**WO 03/040436 A1**

*before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments*

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WO 03/040436

PCT/US02/35910

## METHOD OF ELIMINATING VOIDS IN W PLUGS

## FIELD OF THE INVENTION

The present invention relates to a method of manufacturing semiconductor devices with accurately formed sub-micron features. The present invention has particular applicability in manufacturing high density, multi-level flash-memory semiconductor devices with reliable, low resistance contacts/vias.

## BACKGROUND ART

As integrated circuit geometries continue to plunge into the deep sub-micron regime, it becomes increasingly more difficult to accurately form discrete semiconductor devices exhibiting the requisite reliability and circuit speed. Implementation becomes particularly problematic in manufacturing flash memory devices having a design rule less than about 0.15 micron and under, e.g., less than about 0.12 micron and under.

Conventional semiconductor devices comprise a semiconductor substrate in which various elements are formed, such as transistors, and a plurality of overlying sequentially formed interlayer dielectrics and conductive patterns in which an interconnect system is formed comprising conductive lines. Typically, conductive patterns on different levels, i.e., upper and lower levels, are electrically connected by a conductive plug filling a via hole, while a conductive plug filling a contact hole establishes electrical contact with an active region on a semiconductor substrate, such as a source/drain region. A conductive plug filling a via hole is typically formed by depositing an interlayer dielectric (ILD) on a conductive level comprising at least one conductive feature, forming an opening through the ILD by conventional photolithographic and etching techniques and filling the opening with a conductive material. Excess conductive material or the overburden on the surface of the ILD is typically removed by chemical-mechanical polishing (CMP). One such method is known damascene and basically involves forming an opening in the ILD and filling the opening with a metal. Dual damascene techniques involve forming an opening comprising a lower contact hole or via hole section in communication with an upper trench section, which opening is filled with a conductive material, typically a metal, to simultaneously form a conductive plug in electrical contact with an upper conductive line.

As geometries proceed into the deep sub-micron regime, the formation of reliable, low resistance contacts and interconnects becomes particularly problematic. For example, as contact/via openings are reduced in diameter and the aspect ratio (depth/diameter) increased, as to about 4:1 and higher, the openings become more vulnerable to defects, such as seams and coring in the form of porosity or voids running through the central portion of the contact or via. Such voids result in high and unstable contact resistance distribution, generate defects and decrease electromigration resistance in both flash memory devices and microprocessors.

Accordingly, there exists a need for methodology enabling the manufacture of semiconductor devices with improved reliability, including semiconductor devices containing MOS transistors as well as flash memory devices, such as electrically erasable programmable read only memory (EEPROM) devices. There exists a particular need for methodology enabling the manufacture of semiconductor devices

WO 03/040436

PCT/US02/35910

having features in the deep sub-micron range and containing reliable and low resistance contacts and vias with improved electromigration performance.

**DISCLOSURE OF THE INVENTION**

5 An advantage of the present invention is a method of manufacturing a semiconductor device having features in the deep sub-micron regime with highly reliability vias and contacts exhibiting low and stable contact resistance distribution and improved electromigration performance.

10 Additional advantages and other features of the present invention will be set forth in the description which follows and in part will be apparent to those having ordinary skill in the art upon examination of the following or may be learned from the practice of the present invention. The advantages of the present invention may be realized and obtained as particularly pointed out in the appended claims.

15 According to the present invention, the foregoing and other advantages are achieved in part by a method of manufacturing a semiconductor device, the method comprising: forming an opening in a dielectric layer; depositing tungsten (W) to fill the opening; and laser thermal annealing the W in the opening.

20 Embodiments of the present invention comprise forming an opening in an oxide dielectric layer, such as a boron-phosphorus-doped silicated glass (BPSG) or a composite oxide layer comprising a BPSG layer with a silicon oxide layer derived from tetraethyl orthosilicate (TEOS) thereon, depositing an initial barrier layer of titanium (Ti) and then depositing at least one layer, e.g., three layers, of titanium nitride on the titanium layer. The opening is then filled with W. In an embodiment of the present invention, laser thermal annealing is conducted by impinging a laser light beam on the deposited W directed at the filled opening, typically at a radian fluence of about 0.78 to about 1.10 joules/cm<sup>2</sup>, for a brief period of time, e.g., about 10 to about 100 nanoseconds, in nitrogen (N<sub>2</sub>), to elevate the temperature of the W in the opening thereby melting and reflowing the W in the filled opening, e.g., at a temperature of about 3,000°C to about 3,600°C. Chemical mechanical polishing (CMP) is then conducted. In another embodiment of the present invention, CMP is conducted prior to laser thermal annealing.

25 Additional advantages of the present invention will become readily apparent to those skilled in the art from the following detailed description wherein embodiments of the present invention are described simply by way of illustration of the best mode contemplated for carrying out the present invention. As will be realized, the present invention is capable of other and different embodiments, and its several details are capable of modifications in various obvious respects, all without departing from the present invention. Accordingly, the drawings and description are to be regarded as illustrative in nature, and not as restrictive.

30 **BRIEF DESCRIPTION OF THE DRAWINGS**

35 Fig. 1 schematically illustrates a W plug void problem addressed and solved by the present invention.

Figs. 2 through 5 schematically illustrate sequential phases of a method in accordance with an embodiment of the present invention.

WO 03/040436

PCT/US02/35910

Figs. 6 through 8 schematically illustrate sequential phases of a method in accordance with another embodiment of the present invention.

In Figs. 2 through 8, similar elements or features are denoted by like reference characters.

#### DESCRIPTION OF THE INVENTION

5 The present invention addresses and solves W contact/via reliability problems stemming from the undesirable formation of holes, with attendant high and unstable contact resistance distribution and poor electromigration performance, particularly as device geometries are reduced into the deep sub-micron regime. For example, as the width of a contact/via opening is reduced to about 0.225 to about 0.257 microns, e.g., about 0.25 microns, and the depth of the contact/via opening is extended to about 0.81 to about 0.99 micron, e.g., about 0.90 micron, or greater, and aspect ratios approach 4:1 and greater, it becomes extremely difficult to fill the contact/via openings without generating voids. The present invention addresses and solves that problem by proceeding in a conventional manner to fill the contact/via openings having high aspect ratios in a conventional manner to form a W plug having voids. The present invention departs from conventional practices by providing efficient methodology enabling the removal of the voids formed upon filling a contact/via opening having a high aspect ratio, thereby reducing contact resistance, providing a tighter resistance distribution and improving electromigration performance.

10 In accordance with embodiments of the present invention, a contact/via opening is formed in a dielectric layer, such as an oxide layer, e.g., BPSG or silicon oxide derived from TEOS. A barrier layer composite is then formed lining the opening. In accordance with embodiments of the invention, an initial thin Ti layer is deposited to line the opening and a titanium nitride layer is deposited on the initial Ti layer. W is then deposited in a conventional manner forming an overburden. At this point the W filling the contact/via opening contains undesirable voids or pores adversely impacting device performance, including electromigration performance.

15 20 25 In accordance with embodiments of the present invention, the W filling the opening is subjected to laser thermal annealing by impinging a pulsed laser light beam directed toward the W in the opening, as at a radiant fluence of about 0.78 to about 1.10 joules/cm<sup>2</sup>, while flowing N<sub>2</sub> as at a flow rate of about 200 to about 2,000 sccm. During laser thermal annealing, W in the opening is elevated to a temperature of about 3,000°C to about 3,600°C causing melting and reflowing, thereby eliminating the voids. Subsequently, CMP can be induced in a conventional manner such that the upper surface of the W filling the opening is substantially co-planar with the upper surface of the dielectric layer. In another embodiment, CMP is conducted prior to laser thermal annealing.

30 35 The use of laser thermal annealing in accordance with embodiments of the present invention to reduce interconnect voiding and to decrease contact resistance offers several advantages. For example, laser thermal annealing enables pinpoint accuracy in targeting the W filling the opening, thereby avoiding unnecessarily elevating the temperature of other portions of the wafer causing various problems, such as undue impurity diffusion.

In implementing embodiments of the present invention, any of various commercially available laser tools may be employed, such as those utilizing a laser source capable of operating at energies of

WO 03/040436

PCT/US02/35910

about 10 to about 2,000 mJ/cm<sup>2</sup>/pulse, e.g., about 100 to about 400 mJ/cm<sup>2</sup>/pulse. Commercially available tools exist which can perform such laser annealing, either with or without mask. The Verdant Technologies laser anneal tool is but an example and operates at an exposure wavelength of 308 nm.

5 A W plug voiding problem addressed by the present invention is illustrated in Fig. 1 wherein transistors are formed on substrate 10. The transistors can comprise MOS transistors and/or dual gate memory cell transistors comprising floating and control gates with an interpoly (ONO) dielectric layer therebetween. For example, the transistors can comprise a tunnel oxide 13, a floating gate electrode 14, an ONO stack interpoly dielectric 15, and a control gate 16. A layer of metal silicide 17A, is formed on the upper surface of the gate electrode stack, while a layer of metal silicide 17B is formed on the source/drain regions 11, 12. A dielectric sidewall spacer 18, such as silicon oxide, silicon oxynitride or silicon nitride, is formed on the side surfaces of the gate electrode, and a silicon nitride etch stop layer 19 is typically deposited thereon. A dielectric layer 100, such as BPSG, or a composite of BPSG and silicon oxide derived from TEOS thereon, is deposited, as at a thickness of about 7,500 Å to about 8,500 Å, e.g., about 8,000 Å.

10 15 Conventional photolithographic and etching techniques are then implemented to form a contact opening in dielectric layer 100 exposing source/drain region 12. W is then deposited to fill the contact opening forming an overburden and CMP is then conducted leaving W plug 101 having an undesirable degree of porosity 102. The present invention effectively solves this particular problem in an efficient manner, thereby significantly reducing or eliminating such voids with an attendant improvement in electromigration performance and device reliability.

20 25 An embodiment of the present invention is schematically illustrated in Figs. 2 through 5. Referring to Fig. 2, transistors are formed on substrate 20. The transistor can comprise MOS transistors and/or dual gate memory cell transistors comprising floating and control gates with an interpoly (ONO) dielectric layer therebetween. For example, the transistor can comprise a tunnel oxide 23, a floating gate electrode 24, and ONO stack interpoly dielectric 25 and a control gate 26. A layer of metal silicide 27A, e.g., nickel silicide, is formed on the upper surface of the gate electrode stack, while a layer metal silicide 27B, e.g., nickel silicide, is formed on the source/drain regions 21, 22. A dielectric sidewall spacer 28, such as a silicon oxide, silicon oxynitride or silicon nitride, is formed on the side surfaces of the gate electrode, and a silicon nitride etch stop layer 29 is typically deposited thereon. A dielectric layer 200, such as BPSG, or a composite of BPSG and silicon oxide derived from TEOS thereon, is deposited, as at a thickness of about 7,500 Å to about 8,500 Å, e.g., about 8,000 Å.

30 35 Conventional photolithographic and etching techniques are then implemented to form a contact opening in dielectric layer 200 exposing source/drain region 22. The contact opening typically has an aspect ratio (depth/diameter) of about 4:1 or greater.

A composite barrier layer 201 is then deposited to line the opening, such as an initial layer of Ti and a layer of titanium nitride thereon. W is then deposited to fill the opening and form an overburden 202. Due to the high aspect ratio of the contact opening, significant voiding 203 is generated in the W plug.

WO 03/040436

PCT/US02/35910

In accordance with an embodiment of the present invention, as illustrated in Fig. 3, laser thermal annealing is conducted by impinging a pulsed laser light beam on the deposited W directed toward the filled contact, as schematically illustrated by arrows 30, typically at a radiant fluence of about 0.78 to about 1.10 joules/cm<sup>2</sup>, for a period of time of about 10 to about 100 nanoseconds, thereby elevating at a temperature of W in the plug to about 3,000°C to about 3,600°C, causing melting and reflowing to eliminate the voids, as schematically illustrated in Fig. 4. CMP is then conducted resulting in the structure illustrated in Fig. 5 wherein tungsten plug 50 does not exhibit voids.

In accordance with another embodiment of the present invention, as schematically illustrated in Figs. 6 through 8, CMP is conducted prior to laser thermal annealing. Referring to Fig. 6, the depicted structure is that resulting from performing CMP on the structure schematically illustrated in Fig. 2. Laser thermal annealing is then conducted, as illustrated in Fig. 7, by impinging a pulsed laser light beam 70 directed at the W plug causing reflowing and void elimination. The resulting structure is schematically illustrated in Fig. 8 and comprises W plug 80 without voids.

The present invention, provides methodology enabling the formation of interconnects having W contacts and/or vias with large aspect ratios, e.g., 4 or greater, with no or significantly reduced voids, thereby reducing contact resistance and stabilizing contact resistance distribution to provide a tighter resistance distribution, improving device reliability and improving electromigration performance. The present invention enjoys industrial applicability in manufacturing any of various types of semiconductor devices with improved reliability and increased circuit speed. The present invention has particular applicability in manufacturing semiconductor devices with design features in the deep sub-micron regime, such as flash memory devices, e.g., EEPROMs, with a design rule of about 0.12 micron and under, with significantly improved reliability, increased circuit speed, improved electromigration performance and improved manufacturing throughput.

In the preceding detailed description, the present invention is described with reference to specific exemplary embodiments thereof. It will, however, be evident that various modifications and changes may be made thereto without departing from the broader scope of the present invention, as set forth in the claims. The specification and drawings are, accordingly, to be regarded as illustrative and not as restrictive. It is understood that the present invention is capable of use in various other combinations and environments and is capable of changes or modifications within the scope of the inventive concept as expressed herein.

WO 03/040436

PCT/US02/35910

## WHAT IS CLAIMED IS:

1. A method of manufacturing a semiconductor device, the method comprising:

forming an opening in a dielectric layer (200);

depositing tungsten (W) (202) to the opening; and

5 laser thermal annealing (30) the deposited W.

2. The method according to claim 1, comprising laser thermal annealing by impinging a pulsed laser light beam (30) on the deposited W (202) filling the opening at a radiant fluence of about 0.78 to about 1.10 joules/cm<sup>2</sup>.

3. The method according to claim 2, comprising laser thermal annealing (30) to heat the 10 deposited W filling the opening to a temperature of about 3,000°C to about 3,600°C, thereby reflowing the W in the opening.

4. The method according to claim 1, comprising laser thermal annealing (30) in nitrogen (N<sub>2</sub>).

5. The method according to claim 4, comprising laser thermal annealing (30) employing an 15 N<sub>2</sub> flow rate of about 200 to about 2,000 sccm.

6. The method according to claim 1, comprising depositing a barrier layer (201) lining the opening before depositing the W.

7. The method according to claim 1, comprising conducting chemical mechanical polishing (CMP) after laser thermal annealing such that an upper surface of the W (50) in the opening is 20 substantially co-planar with an upper surface of the dielectric layer (200).

8. The method according to claim 1, comprising conducting chemical mechanical polishing (CMP) before laser thermal annealing such that an upper surface of the W (80) is substantially co-planar with an upper surface of the dielectric layer (200).

9. The method according to claim 4, comprising laser thermal annealing by impinging a 25 pulsed laser light beam (30) on the deposited W (202) filling the opening at a radiant fluence of about 0.78 to about 1.10 joules/cm<sup>2</sup>.

10. The method according to claim 9, comprising laser thermal annealing (30) to heat the deposited W (202) filling the opening to a temperature of about 3,000°C to about 3,600°C, thereby reflowing the W in the opening.

WO 03/040436

PCT/US02/35910

FIG. 1

WO 03/040436

PCT/US02/35910

FIG. 2

WO 03/040436

PCT/US02/35910

FIG. 3

WO 03/040436

PCT/US02/35910

FIG. 4

WO 03/040436

PCT/US02/35910

FIG. 5

WO 03/040436

PCT/US02/35910

FIG. 6

WO 03/040436

PCT/US02/35910

FIG. 7

WO 03/040436

PCT/US02/35910

FIG. 8

**【手続補正書】**

【提出日】平成15年10月28日(2003.10.28)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

半導体装置の製造方法であって、

絶縁体層(200)に開口部を形成する処理と、

前記開口部を充填するためにタンゲステン(W)(202)をデポジションする処理と、前記デポジションされたWをレーザー・サーマル・アニール(30)して、前記開口部内の前記Wを溶解し、リフローさせる処理とを含む製造方法。

**【請求項2】**

前記開口部を充填するデポジションされたW(202)に、約0.78から約1.10ジユール/平方センチメーターの放射フルエンスで、パルスレーザー光ビーム(30)を照射することにより、レーザー・サーマル・アニールする処理を含む、請求項1記載の製造方法。

**【請求項3】**

前記開口部を充填するデポジションされたWを摂氏約3000度から約3600度の温度まで加熱して、それによって前記開口部内のWをリフローさせる、レーザー・サーマル・アニール処理(30)を含む、請求項2記載の製造方法。

**【請求項4】**

窒素(N<sub>2</sub>)中でレーザー・サーマル・アニールする処理(30)を含む、請求項1記載の製造方法。

**【請求項5】**

約200から約2000sccmの流量のN<sub>2</sub>を用いるレーザー・サーマル・アニール処理(30)を含む、請求項4記載の製造方法。

**【請求項6】**

前記Wのデポジションの前に、前記開口部をライニングするバリア層(201)をデポジションする処理を含む、請求項1記載の製造方法。

**【請求項7】**

レーザー・サーマル・アニールの後で、化学機械研磨(CMP)を実行して、前記開口部内の前記W(50)の上面と前記絶縁体層(200)の上面とが実質的にともに平坦になるようにする処理を含む、請求項1記載の製造方法。

**【請求項8】**

レーザー・サーマル・アニールの前に、化学機械研磨(CMP)を実行して、前記W(80)の上面と前記絶縁体層(200)の上面とが実質的にともに平坦になるようにする処理を含む、請求項1記載の製造方法。

**【請求項9】**

前記開口部を充填するデポジションされたW(202)に、約0.78から約1.10ジユール/平方センチメーターの放射フルエンスで、パルスレーザー光ビーム(30)を照射することにより、レーザー・サーマル・アニールする処理を含む、請求項4記載の製造方法。

**【請求項10】**

前記開口部を充填するデポジションされたW(202)を摂氏約3000度から約3600度の温度まで加熱して、それによって前記開口部内のWをリフローさせる、レーザー・サーマル・アニール処理(30)を含む、請求項9記載の製造方法。

**【手続補正2】**

【補正対象書類名】明細書

【補正対象項目名】0006

【補正方法】変更

【補正の内容】

【0006】

本発明の特長は、深いサブミクロン体制の構造を持ち、低く、安定した接触抵抗分布および改善されたエレクトロマイグレーション耐性を示す高い信頼性のピアおよびコンタクトを持つ、半導体装置の製造方法である。

本発明のさらなる特長およびその他の特徴は、この後の発明の詳細な説明で説明される。その一部は以下の説明を理解した当業者には明白なものであり、または本発明を実行することによって学ぶことができる。本発明の特徴は、添付の特許請求の範囲に特に記載されているように、実現し、得ることができる。

本発明に従った方法は、絶縁体層に開口部を形成する処理と、その開口部を充填するためにタングステン(W)をデポジション(deposition)する処理と、開口部内のタングステンをレーザー・サーマル(熱)・アニール(laser thermal annealing)して、前記開口部内の前記タングステンを溶解し、リフローさせる処理とを含む。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                         |                                                                                                                                                                                                                                                      | International Application No<br>PCT/US 02/35910                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 C25D5/50 H01L21/20 H01L23/522                                                                                                          |                                                                                                                                                                                                                                                      |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                   |                                                                                                                                                                                                                                                      |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                       |                                                                                                                                                                                                                                                      |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                       |                                                                                                                                                                                                                                                      |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, WPI Data, PAJ                           |                                                                                                                                                                                                                                                      |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                              |                                                                                                                                                                                                                                                      |                                                                                |

| Category *                                                                                                                                                                          | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                   | Relevant to claim No.                                                          |

| Y                                                                                                                                                                                   | EP 1 069 213 A (APPLIED MATERIALS INC)<br>17 January 2001 (2001-01-17)<br>column 1, line 39-50<br>column 3, line 34-42<br>column 5, line 2-7<br>column 7, line 20-26<br>column 8, line 15-22<br>column 8, line 32-40<br>abstract; figures 1,2<br>--- | 1-10                                                                           |

| Y                                                                                                                                                                                   | US 6 143 650 A (PRAMANICK SHEKHAR ET AL)<br>7 November 2000 (2000-11-07)<br>column 2, line 51-57<br>column 4, line 48-52<br>abstract<br>---                                                                                                          | 1-10<br>-/-                                                                    |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                      |                                                                                                                                                                                                                                                      | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents :                                                                                                                                           |                                                                                                                                                                                                                                                      |                                                                                |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                                            |                                                                                                                                                                                                                                                      |                                                                                |

| "B" document published on or after the International filing date                                                                                                                    |                                                                                                                                                                                                                                                      |                                                                                |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another document under special reason (as specified)                |                                                                                                                                                                                                                                                      |                                                                                |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                                                        |                                                                                                                                                                                                                                                      |                                                                                |

| "P" document published prior to the International filing date but later than the priority date claimed                                                                              |                                                                                                                                                                                                                                                      |                                                                                |

| -- document member of the same patent family                                                                                                                                        |                                                                                                                                                                                                                                                      |                                                                                |

| Date of the actual completion of the International search                                                                                                                           | Date of mailing of the International search report                                                                                                                                                                                                   |                                                                                |

| 18 March 2003                                                                                                                                                                       | 03.04.2003                                                                                                                                                                                                                                           |                                                                                |

| Name and mailing address of the ISA<br>EPO - Patent Office, P.B. 5918 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016 | Authorized officer<br>ERIK MILIANDER/JA A                                                                                                                                                                                                            |                                                                                |

Form PCT/ISA/210 (Second sheet) (July 1992)

| INTERNATIONAL SEARCH REPORT                          |                                                                                            | International Application No.<br>PCT/US 02/35910 |

|------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------|

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                            |                                                  |

| Category *                                           | Citation of document, with indication, where appropriate, of the relevant passages         | Relevant to claim No.                            |

| A                                                    | US 6 261 963 B1 (ZISTL CHRISTIAN ET AL)<br>17 July 2001 (2001-07-17)<br>abstract<br>-----  | 1-10                                             |

| P, A                                                 | US 6 399 486 B1 (CHEN SHENG-HSIUNG ET AL)<br>4 June 2002 (2002-06-04)<br>abstract<br>----- | 1-10                                             |

Form PCT/ISA/210 (continuation of second sheet) (July 1992)

| INTERNATIONAL SEARCH REPORT            |                  |                         |                 | International Application No |  |

|----------------------------------------|------------------|-------------------------|-----------------|------------------------------|--|

| Information on patent family members   |                  |                         |                 | PCT/US 02/35910              |  |

| Patent document cited in search report | Publication date | Patent family member(s) |                 | Publication date             |  |

| EP 1069213                             | A                | 17-01-2001              | EP 1069213 A2   | 17-01-2001                   |  |

|                                        |                  |                         | JP 2001085437 A | 30-03-2001                   |  |

|                                        |                  |                         | TW 478072 B     | 01-03-2002                   |  |

| US 6143650                             | A                | 07-11-2000              | NONE            |                              |  |

| US 6261963                             | B1               | 17-07-2001              | NONE            |                              |  |

| US 6399486                             | B1               | 04-06-2002              | NONE            |                              |  |

Form PCT/ISA210 (patent family annex) (July 1992)

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,N0,NZ,OM,PH,PL,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VN,YU,ZA,ZM,ZW

(74)代理人 100108604

弁理士 村松 義人

(72)発明者 ミン バン エヌジーオー

アメリカ合衆国、カリフォルニア州 94539、フリーモント、キャニオン ハイツ ドライブ

40986

(72)発明者 エリック ペイトン

アメリカ合衆国、カリフォルニア州 95037、モーガン ヒル、リオ グランデ コート 498

F ターム(参考) 5F033 KK01 KK18 KK19 KK25 KK33 NN06 NN07 QQ09 QQ10 QQ37

QQ48 QQ53 QQ75 QQ83 RR04 RR15 SS04 VV16 WW03 WW06

WW07 XX04 XX05 XX09 XX34

5F083 EP23 EP55 ER22 GA27 JA04 JA35 JA39 JA40 JA56 MA05

MA06 MA19 PR33 PR40

5F101 BA29 BB05 BC01 BD33 BE07 BH16