(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2015/161157 A1

(43) International Publication Date

22 October 2015 (22.10.2015)

WIPO | PCT

(51) International Patent Classification:

G10K 11/34 (2006.01) G01S 7/524 (2006.01)

B06B 1/02 (2006.01)

(21) International Application Number:

PCT/US2015/026304

(22) International Filing Date:

17 April 2015 (17.04.2015)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/981,469 18 April 2014 (18.04.2014) US

(71) Applicant: BUTTERFLY NETWORK, INC. [US/US];

530 Old Whitfield Street, Guilford, CT 06437 (US).

(72) Inventors: ROTHBERG, Jonathan, M.; 215 Uncas Point Road, Guilford, CT 06437 (US). RALSTON, Tyler, S.; 56 Beach Park Road, Clinton, CT 06413 (US). SANCHEZ, Nevada, J.; 1280 Little Meadow Road, Guilford, CT 06437 (US). CASPER, Andrew, J.; 161 East Main Street, Unit 205, Clinton, CT 06413 (US).

(74) Agent: FRANKLIN, Thomas, A.; Wolf, Greenfield & Sacks, P.C., 600 Atlantic Avenue, Boston, MA 02210-2206 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: ARCHITECTURE OF SINGLE SUBSTRATE ULTRASONIC IMAGING DEVICES, RELATED APPARATUSES, AND METHODS

FIG. 1

(57) Abstract: Aspects of the technology described herein relate to ultrasound device circuitry as may form part of a single substrate ultrasound device having integrated ultrasonic transmission units, a delay mesh circuitry integrated with the substrate, coupled to inputs of the plurality of ultrasound transmission units and configured to output to the plurality of ultrasound transmission units a plurality of time-delayed versions of a delay mesh circuitry input signal corresponding to a waveform generated by a waveform generator.

- 1 -

## ARCHITECTURE OF SINGLE SUBSTRATE ULTRASONIC IMAGING DEVICES, RELATED APPARATUSES, AND METHODS

### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** The present application claims the benefit under 35 U.S.C. §119(e) of U.S. Provisional Patent Application Serial No. 61/981,469 entitled “ARCHITECTURE OF SINGLE SUBSTRATE ULTRASONIC IMAGING DEVICES, RELATED APPARATUSES, AND METHODS,” filed April 18, 2014 under Attorney Docket No. B1348.70011US00, which is incorporated herein by reference in its entirety.

### FIELD

**[0002]** Aspects of the technology described herein relate to the architecture of single substrate ultrasonic imaging devices, related apparatuses, and methods.

### BACKGROUND

**[0003]** Conventional ultrasonic scanners dominating the ultrasound imaging industry have discrete transducers and control electronics. The transducers are often piezoelectric. As a result, the scanners are made using “dice and fill” manufacturing processes in which individual piezoelectric elements are cut and then positioned individually on a substrate to form a transducer probe. Such processes are prone to the cost, non-uniformity, and non-scalability of machining and wiring. Control electronics are typically not integrated with the transducers, but rather formed and housed separately.

**[0004]** Ultrasound transducer probes used for medical applications typically comprise many ultrasound elements each configured to emit ultrasound signals that collectively produce a medically relevant ultrasound field used to produce ultrasound images for medical applications. Typically, each ultrasound transducer is configured to emit an ultrasound waveform generated by a corresponding waveform generator. Thus, many waveform generators are needed to produce an ultrasound field with a conventional ultrasound transducer probe having many ultrasound elements.

### BRIEF SUMMARY

**[0005]** Aspects of the technology described herein include an architecture and techniques which

may facilitate integration of a substantial portion of, or even an entire, ultrasonic imaging system on a single semiconductor substrate. Accordingly, many of the features and methodologies described herein relate to a single-chip ultrasonic imaging solution, or to devices and systems wherein at least a substantial portion of the ultrasonic imaging system is provided on a single chip.

**[0006]** According to an aspect of the technology, the single substrate ultrasound imaging system comprises waveform generators, delay mesh circuitry, and ultrasound transducers all integrated with the substrate. The delay mesh circuitry may be configured to provide waveforms generated by the waveform generators to the ultrasound transducers and may allow for the system to have fewer waveform generators than ultrasound transducers, which may facilitate the provision of the imaging system on a single chip. To this end, the delay mesh circuitry may receive an input signal corresponding to a waveform generated by a waveform generator, produce a plurality of time-delayed versions of the input signal, and provide the resulting signals to multiple ultrasonic transducers.

**[0007]** Some embodiments are directed to an apparatus, comprising: a substrate; a first ultrasound transmission unit integrated with the substrate; and delay mesh circuitry integrated with the substrate, coupled to an input of the first ultrasound transmission unit and configured to output to the first ultrasound transmission unit a time-delayed version of a delay mesh circuitry input signal corresponding to a waveform generated by a waveform generator.

**[0008]** Some embodiments are directed to an apparatus, comprising: a substrate; a plurality of ultrasound transmission units integrated with the substrate; and delay mesh circuitry integrated with the substrate, coupled to inputs of the plurality of ultrasound transmission units and configured to output to the plurality of ultrasound transmission units a plurality of time-delayed versions of a delay mesh circuitry input signal corresponding to a waveform generated by a waveform generator.

**[0009]** Some embodiments are directed to an apparatus, comprising: a substrate; a plurality of ultrasound transmission units integrated with the substrate; and delay mesh circuitry integrated with the substrate, coupled to inputs of the plurality of ultrasound transmission units, and configured to: in response to input of a first delay mesh control signal, output to the plurality of ultrasound transmission units a first plurality of time-delayed versions of a delay mesh circuitry input signal corresponding to a waveform generated by a waveform generator; and in response

to input of a second delay mesh control signal different from the first delay mesh control signal, output to the plurality of ultrasound transmission units a second plurality of time-delayed versions of the delay mesh circuitry input signal corresponding to the waveform generated by the waveform generator, wherein the first plurality of time-delayed version of the delay mesh circuitry input signal is different from the second plurality of time delayed versions of the delay mesh circuitry input signal.

**[0010]** Some embodiments are directed to an apparatus, comprising: a substrate; a plurality of waveform generators integrated with the substrate; a plurality of ultrasound transmission units integrated with the substrate; and delay mesh circuitry integrated with the substrate, coupled to inputs of the plurality of ultrasound transmission units and configured to output to the plurality of ultrasound transmission units a plurality of time-delayed versions of delay mesh circuitry input signals corresponding to a plurality of waveforms generated by the plurality of waveform generators.

**[0011]** Some embodiments are directed to an apparatus, comprising: a complementary metal oxide semiconductor (CMOS) substrate; at least one waveform generator integrated with the CMOS substrate and configured to generate at least one initial waveform; encoding circuitry integrated with the CMOS substrate, coupled to at least one output of the at least one waveform generator, and configured to encode the at least one initial waveform to produce at least one encoded waveform; delay mesh circuitry integrated with the CMOS substrate, coupled to at least one output of the encoding circuitry, and configured to generate a plurality of time-delayed versions of the at least one encoded waveform; and a plurality of ultrasound transmission units integrated with the CMOS substrate, coupled to a plurality of outputs of the delay mesh circuitry, the plurality of ultrasound transmission units comprising: decoding circuitry configured to decode the plurality of time-delayed versions of the at least one encoded waveform to produce a plurality of decoded waveforms; and a plurality of ultrasonic transducers configured to generate an ultrasound field at least in part by concurrently transmitting ultrasound signals corresponding to the plurality of decoded waveforms.

**[0012]** Some embodiments are directed to a method comprising using a single substrate ultrasound device to perform: encoding a waveform generated by a waveform generator to obtain an encoded waveform; producing a plurality of time-delayed versions of the encoded waveform; decoding the plurality of time-delayed versions of the encoded waveform to obtain a

- 4 -

plurality of decoded waveforms; and generating an ultrasound field at least in part by transmitting in parallel, using a plurality of ultrasound elements, ultrasound signals corresponding to the plurality of decoded waveforms.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0013]** Various aspects and embodiments of the technology will be described with reference to the following figures. It should be appreciated that the figures are not necessarily drawn to scale. Items appearing in multiple figures are indicated by the same reference number in all the figures in which they appear.

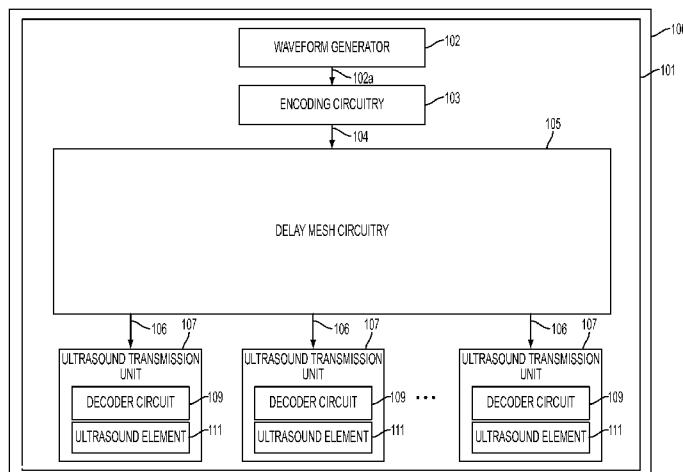

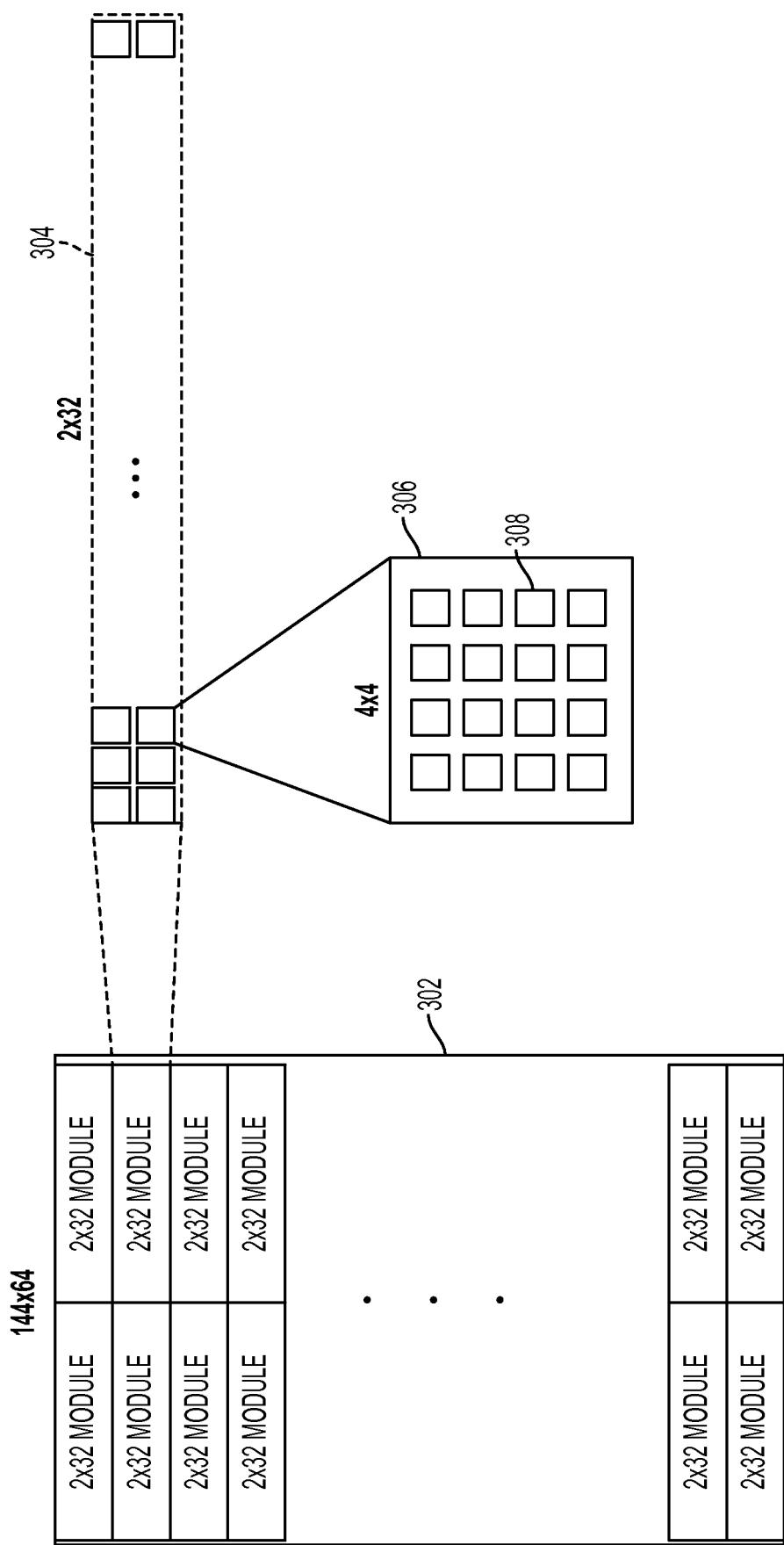

**[0014]** FIG. 1 shows an illustrative single substrate ultrasound device embodying various aspects of the technology described herein.

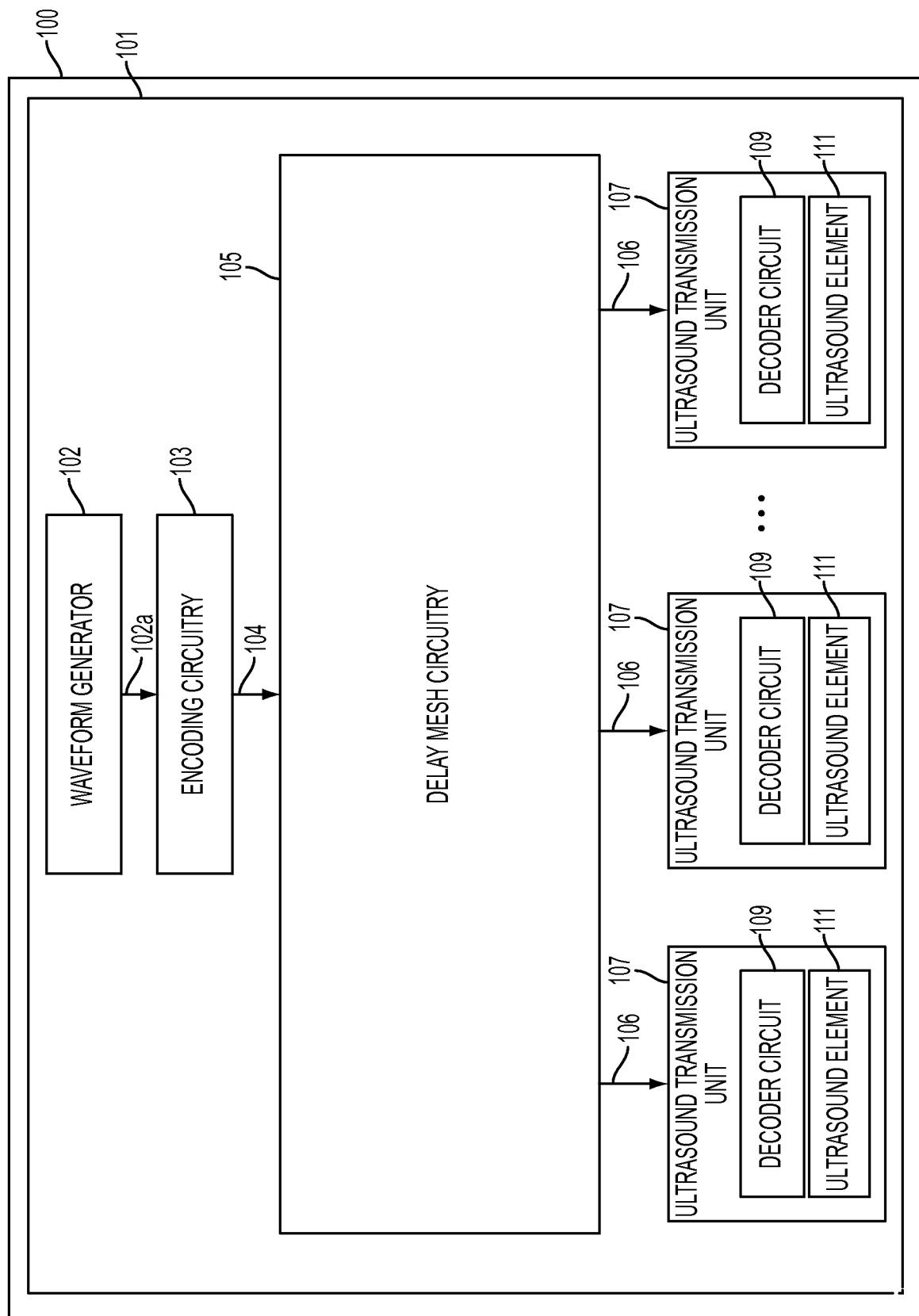

**[0015]** FIG. 2 is a flowchart of an illustrative process for generating and transmitting an ultrasound field using a single substrate ultrasound device, in accordance with some embodiments described herein.

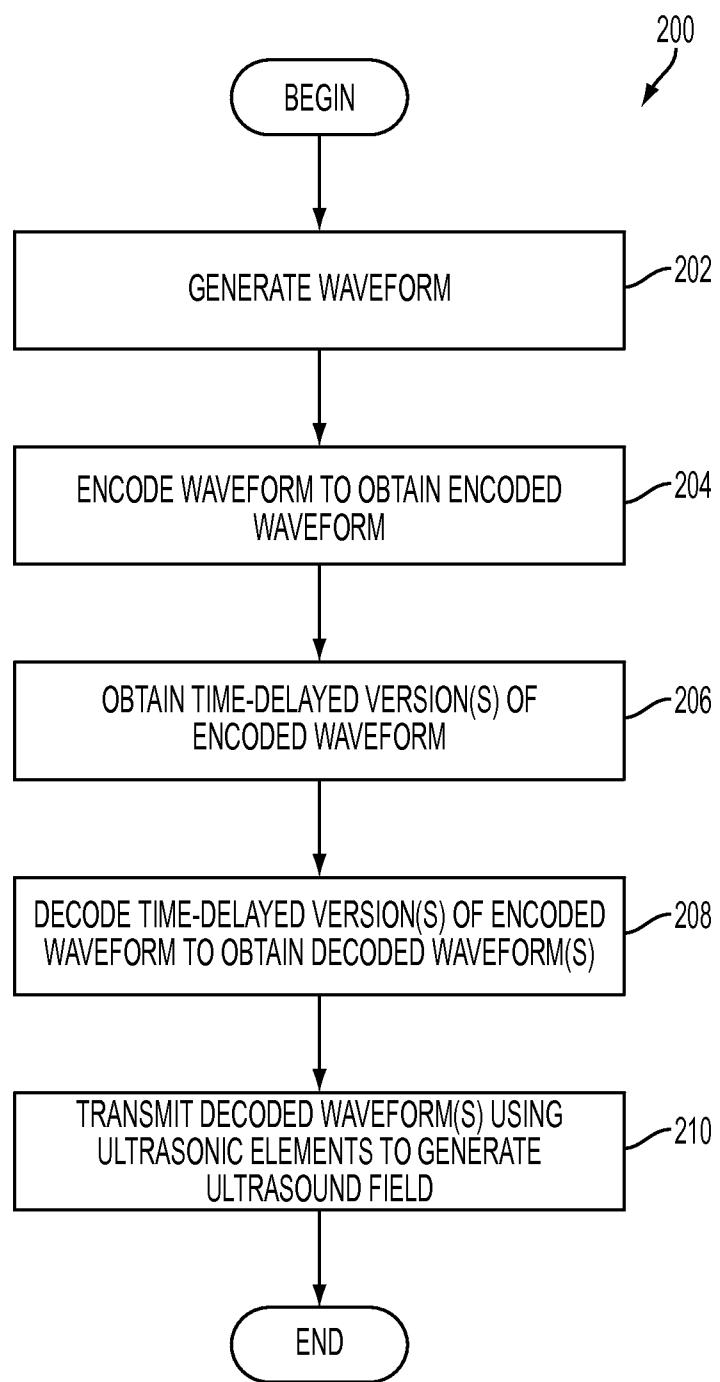

**[0016]** FIG. 3 shows an illustrative arrangement of ultrasonic transducers integrated with the substrate of a single substrate ultrasound device, in accordance with some embodiments described herein.

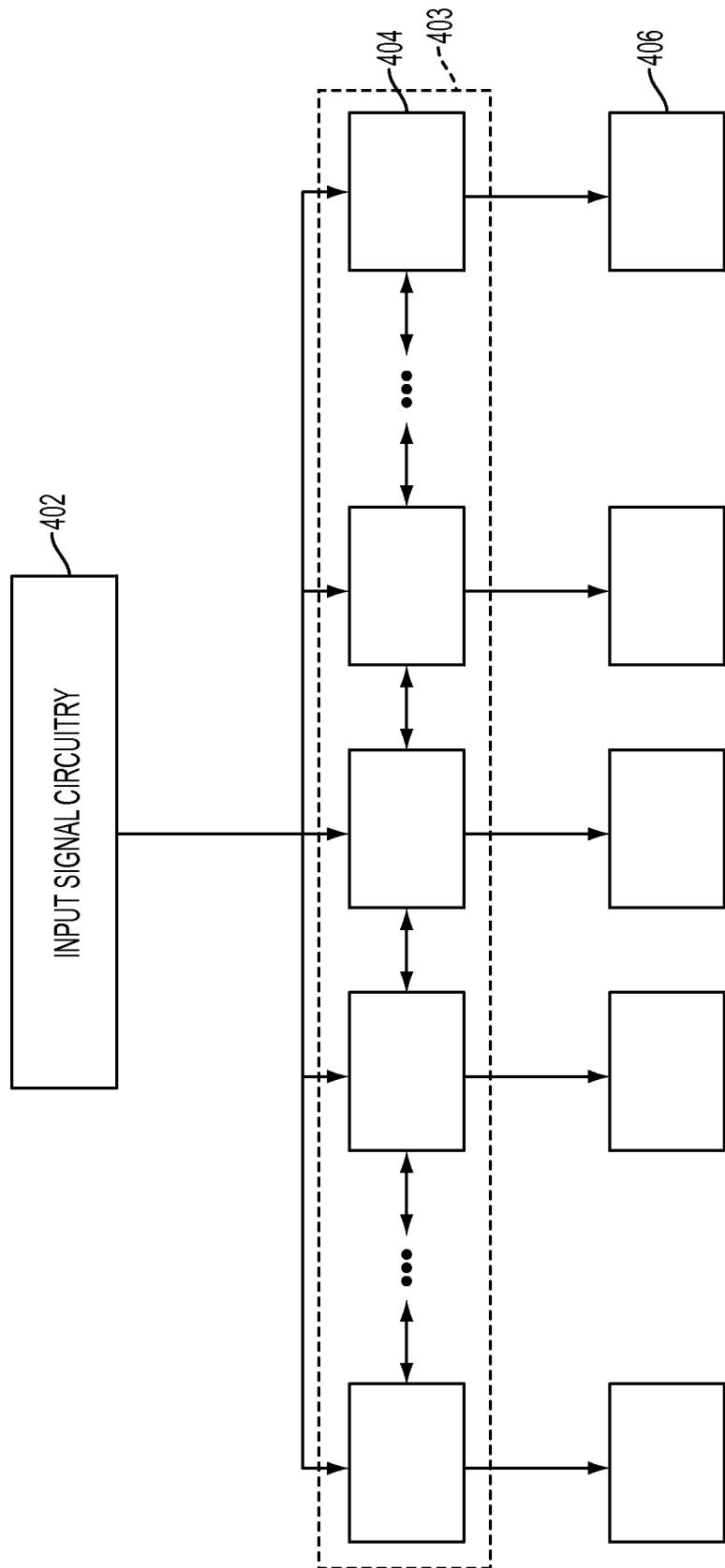

**[0017]** FIG. 4 illustrates delay mesh circuitry comprising multiple delay mesh units, in accordance with some embodiments described herein.

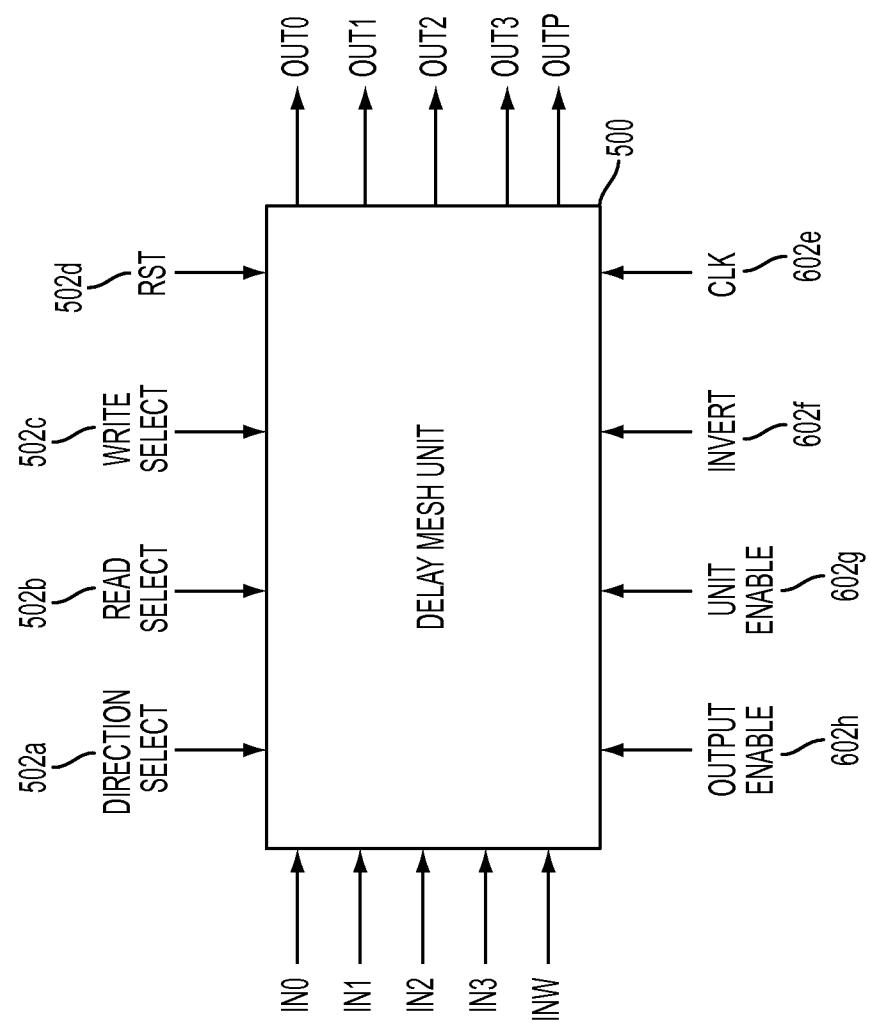

**[0018]** FIG. 5A illustrates the inputs and outputs of an illustrative delay mesh unit of a delay mesh, in accordance with some embodiments described herein.

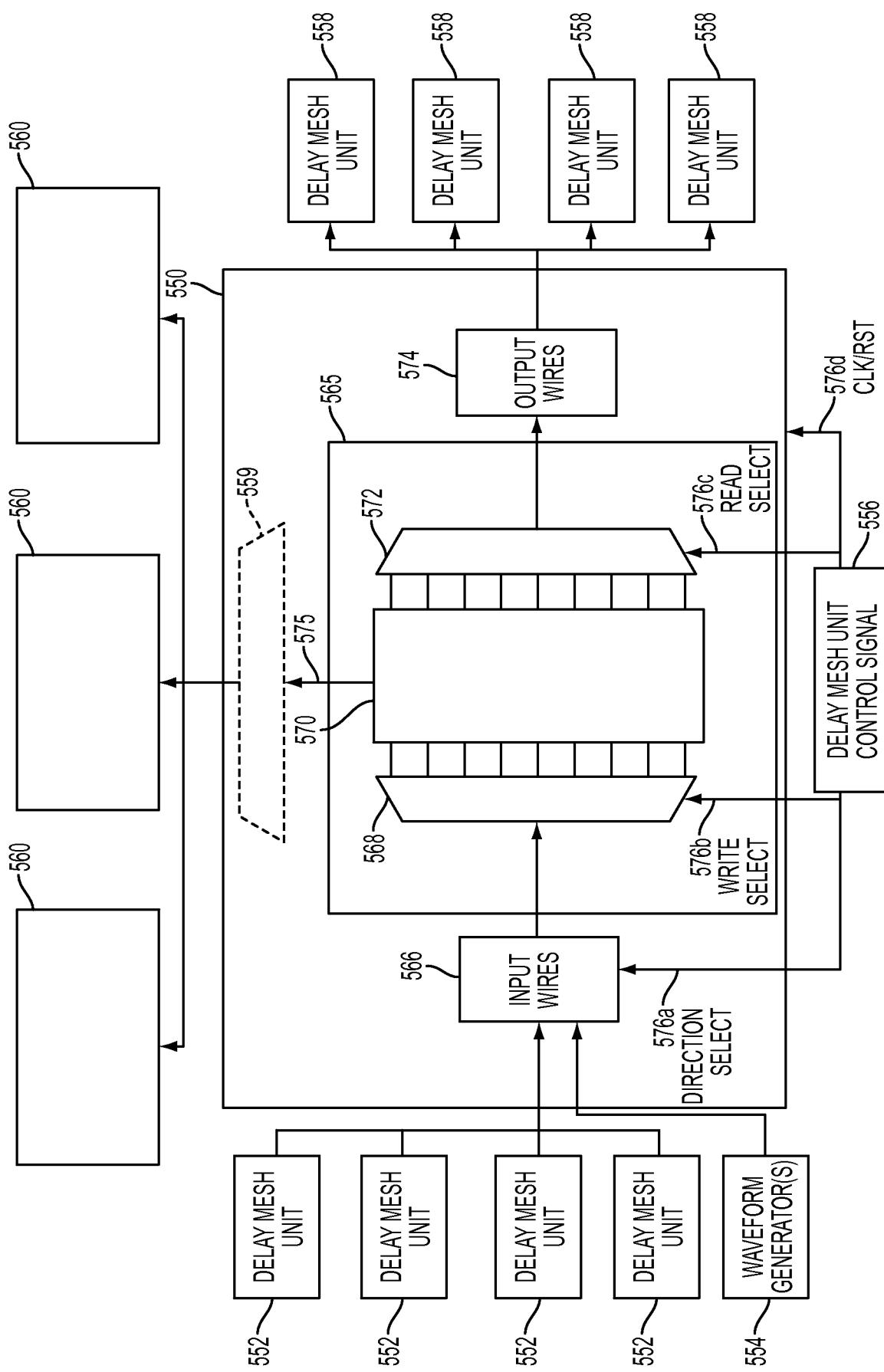

**[0019]** FIG. 5B illustrates the architecture of an illustrative delay mesh unit, in accordance with some embodiments described herein.

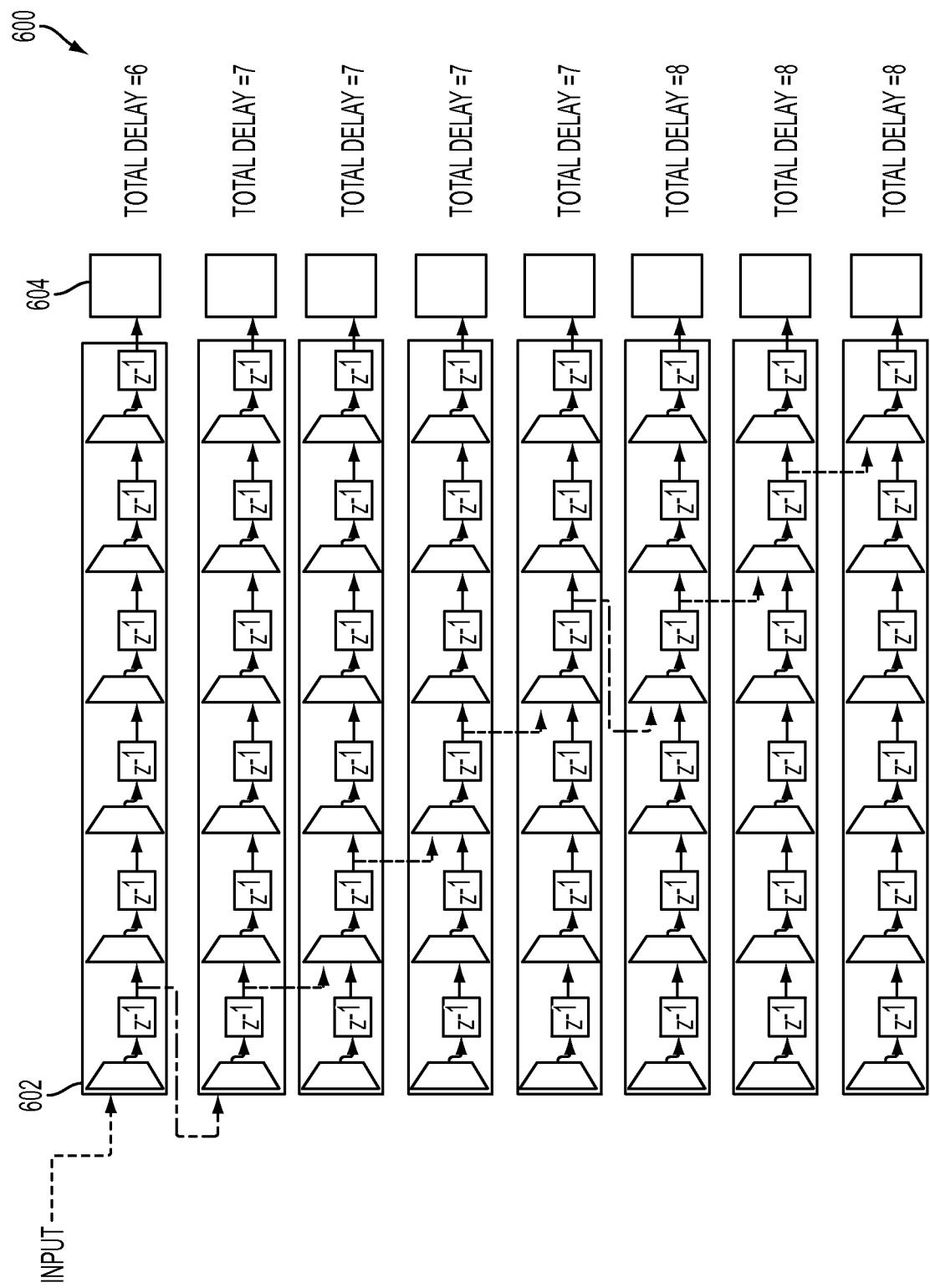

**[0020]** FIG. 6 shows an illustrative configuration of delay mesh circuitry comprising delay mesh units, in accordance with some embodiments described herein.

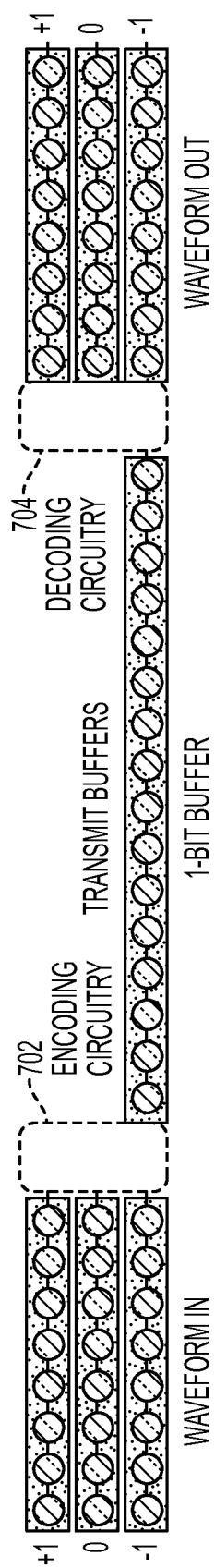

**[0021]** FIG. 7 illustrates operation of encoding and decoding circuitry that may be part of the circuitry of a single substrate ultrasound device, in accordance with some embodiments described herein.

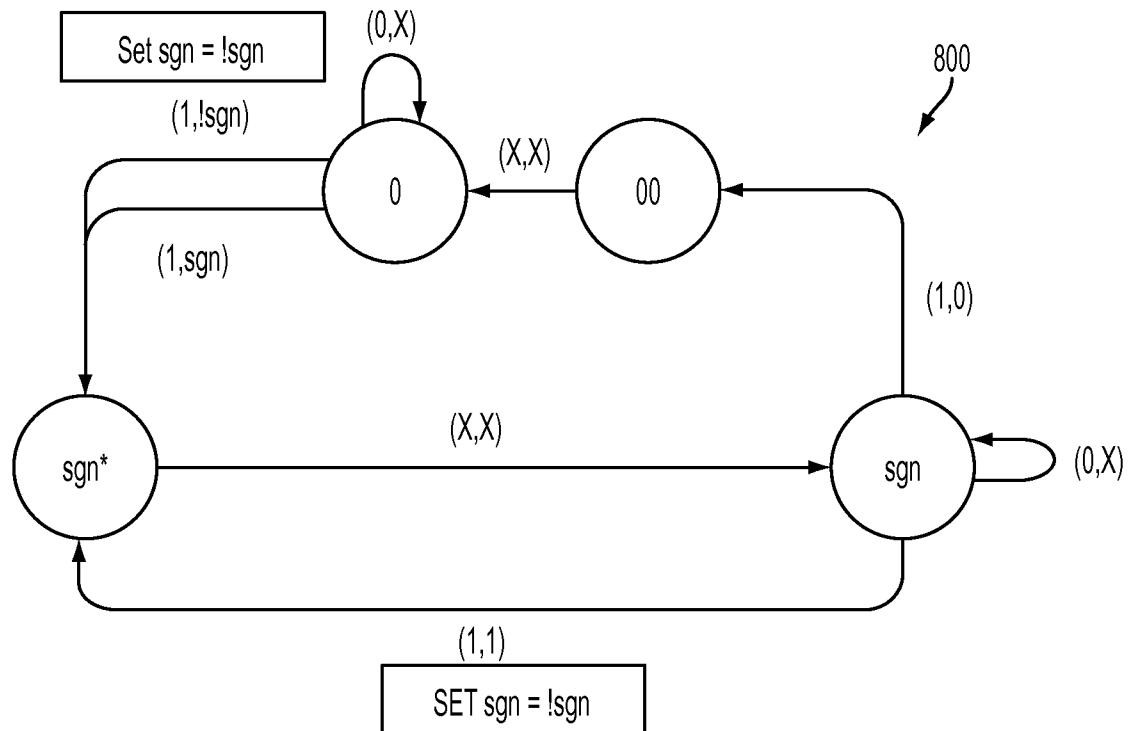

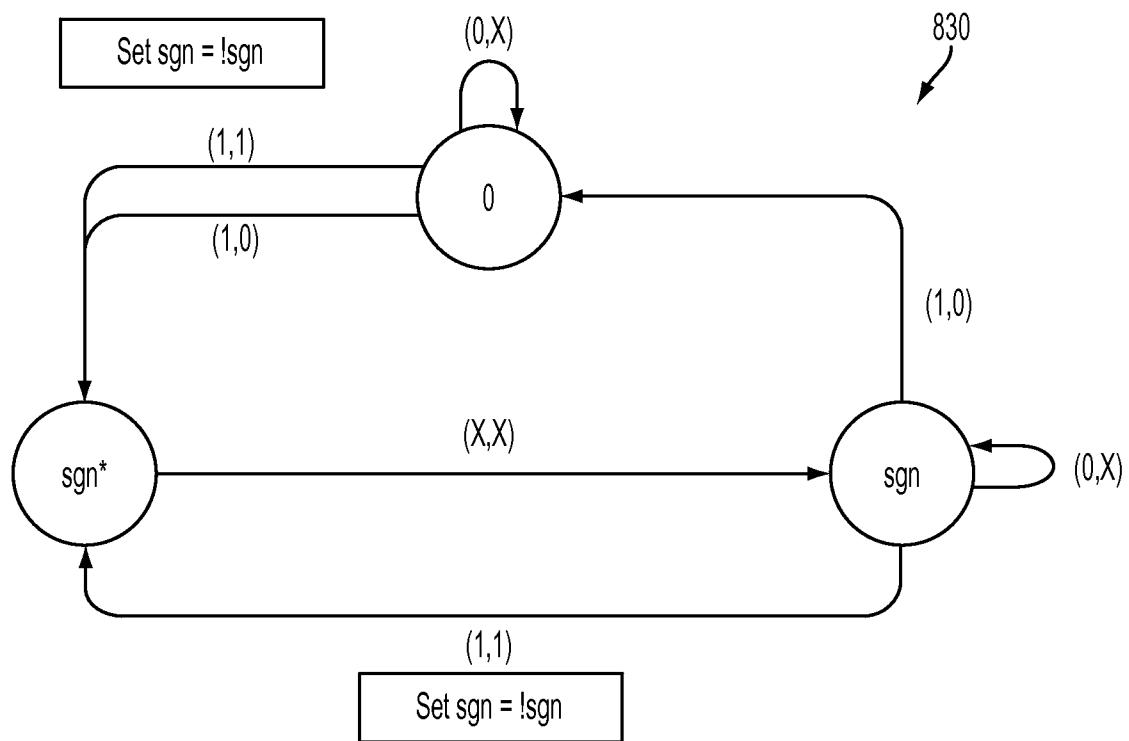

**[0022]** FIG. 8A is a finite state machine diagram illustrating the operation of one embodiment of encoding circuitry.

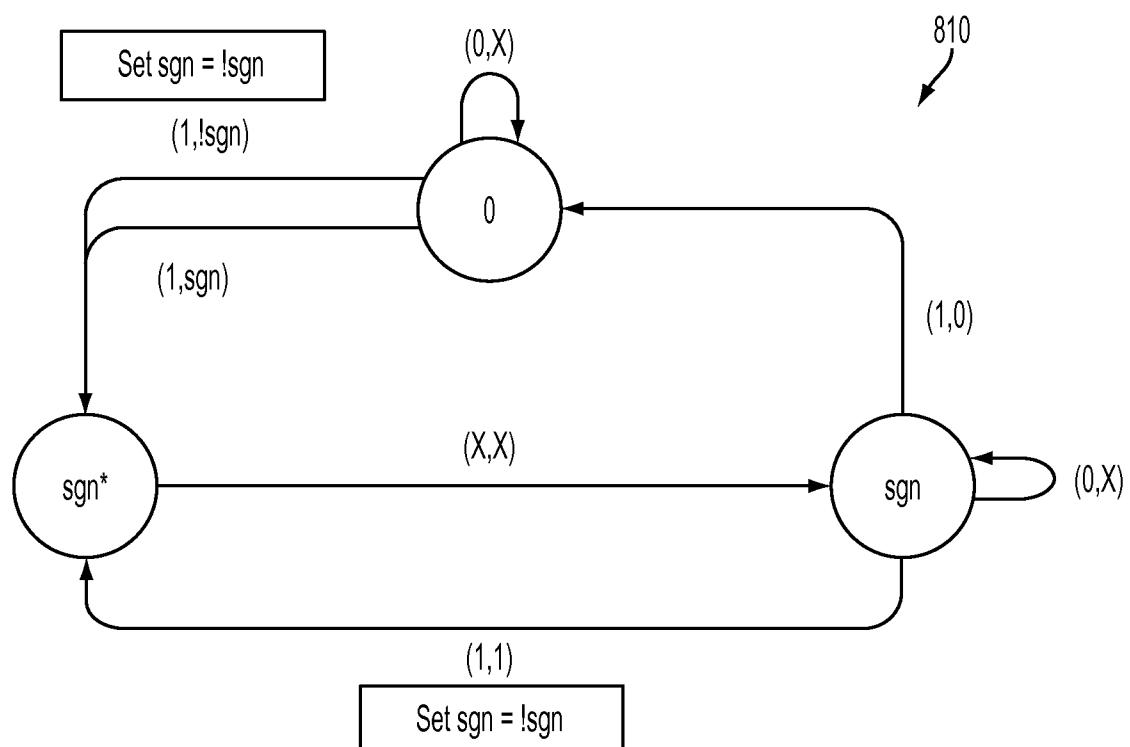

**[0023]** FIG. 8B is a finite state machine diagram illustrating the operation of one embodiment of

- 5 -

decoding circuitry configured to decode signals encoded by the encoding circuitry whose operation is illustrated in FIG. 8A.

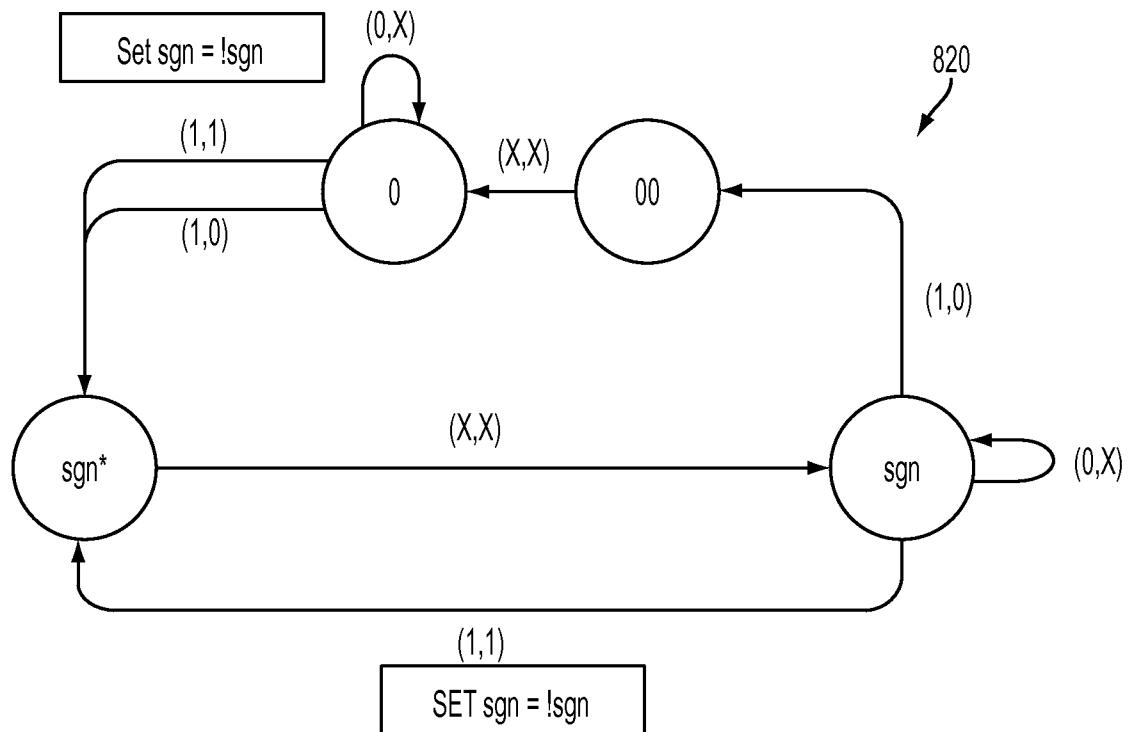

**[0024]** FIG. 8C is a finite state machine diagram illustrating the operation of another embodiment of encoding circuitry.

**[0025]** FIG. 8D is a finite state machine diagram illustrating the operation of another embodiment of decoding circuitry configured to decode signals encoded by the encoding circuitry whose operation is illustrated in FIG. 8C.

#### DETAILED DESCRIPTION

**[0026]** Aspects of the technology described herein relate to an ultrasound device circuitry architecture, as may form part of a single substrate ultrasound device having integrated ultrasonic transducers, for example complementary metal oxide semiconductor (CMOS) ultrasonic transducers. Thus, the circuitry architecture may in some embodiments form part of an ultrasound system-on-a-chip (SoC) having integrated circuitry and ultrasonic transducers integrated with (e.g., formed in, or monolithically integrated with) a substrate, such as a semiconductor substrate.

**[0027]** As described further below, aspects of the present technology provide delay and encoding/decoding circuitry configurations facilitating the generation of medically relevant ultrasound waveforms using an integrated ultrasonic transducer arrangement in a manner that is power- and data-efficient.

**[0028]** Applicants have appreciated that implementing an ultrasound device having integrated ultrasonic transducers and integrated circuitry on a single substrate, such as a CMOS substrate, remains difficult due to the complexity of such devices. Creating complex and medically relevant ultrasound waveforms for use in ultrasound imaging generally requires large amounts of data, and therefore large available memory storage for storing waveform parameters. At the same time, there are practical limits to the configuration and operation of a single substrate ultrasound device, for example in terms of the amount of memory, data, and power which can be used.

**[0029]** One such practical limitation is the number of waveform generators used to generate the waveforms to be emitted by an arrangement (e.g., an array) of ultrasonic transducers integrated with the substrate. While providing one waveform generator for each ultrasonic transducer may be beneficial in some contexts, doing so is impractical in the scenario in which the waveform

generators are to be integrated on the substrate with the ultrasonic transducers due to the space and power requirements. Thus, Applicants have appreciated that in some scenarios it is preferable to provide a single substrate ultrasound device having integrated thereon fewer waveform generators than ultrasonic transducers to which the desired waveform is to be provided.

**[0030]** According to an aspect of the technology, the circuitry architecture of an ultrasound device may include circuitry configured to produce, from a single waveform provided by a waveform generator, a plurality of versions of the waveform that can be provided to a plurality of ultrasonic transducers of an ultrasonic transducer arrangement to produce a desired ultrasound field. The plurality of versions of the waveform may include time-delayed and/or inverted versions of the waveform. The plurality of versions of the waveform may be provided in parallel in at least some embodiments so that desired (e.g., medically relevant) ultrasound fields may be emitted from the plurality of ultrasonic transducers (e.g., plane wave fields, cylindrically focused fields, focused beams, virtual source fields, etc.).

**[0031]** According to an aspect of the technology, the circuitry may include a delay mesh for accomplishing the task of producing the multiple versions of the waveform, the delay mesh having an input configured to receive the waveform generated by the waveform generator and a plurality of (parallel) outputs configured to provide the multiple versions of the waveform to the plurality of ultrasonic transducers. The delay mesh may be controlled to produce different versions of the waveform generated by the waveform generator in response to different controls applied to the delay mesh. In this way, the ultrasound device can be controlled to generate different types of ultrasound fields, examples of which are described below.

**[0032]** According to an aspect of the technology, the circuitry of the ultrasound device includes encoding and decoding circuitry configured to encode and decode waveforms to be provided to a plurality of ultrasonic transducers of an ultrasonic transducer arrangement. The encoding and decoding circuitry may reduce the amount of data required to provide waveforms generated by one or more waveform generators to the ultrasonic transducer(s) configured to transmit ultrasound signals corresponding to the waveforms, and thus may provide a valuable reduction in the amount of memory required to store and communicate the desired waveform data among components of the single substrate ultrasound device. In some embodiments, the encoding and decoding circuitry may be arranged between a waveform generator and the ultrasonic

transducer(s) to which the waveform is to be provided. In some embodiments, delay mesh circuitry may be arranged between encoding circuitry and the decoding circuitry, which may provide a valuable reduction in the amount of memory required to store and communicate the waveform data among components of the delay mesh circuitry.

**[0033]** In some embodiments, delay mesh circuitry may comprise a plurality of delay mesh units each of which may delay an input signal to obtain one or more time-delayed versions of the input signal and provide them as output signals to one or more ultrasound transmission units to be transmitted and/or to one or more other delay mesh units for further processing. Output signals provided to one or more other delay mesh units may be further time-delayed by those delay mesh units and be transmitted and/or further processed by still other delay mesh units. In this way, a signal input to the delay mesh circuitry may propagate through a plurality of delay mesh units, with one or more of the delay mesh units time-delays the signal providing the resulting time-delayed version(s) to one or more ultrasound elements for transmission. As such, delay mesh circuitry may generate multiple time-delayed versions of the input signal and provide these versions for transmission to ultrasound transducers integrated with the single substrate ultrasound device for generation of an ultrasound field.

**[0034]** A delay mesh unit may comprise a buffer for storing and/or performing operations on a signal input to the buffer. In some embodiments, delay mesh circuitry may comprise many delay mesh units and, as such, reducing the size of the buffer of each delay mesh unit may reduce both space and power requirements of implementing delay mesh circuitry on a single substrate ultrasound device.

**[0035]** As may be appreciated from the above, aspects of the present technology provide space- and power-efficient circuitry configurations for providing desired waveforms to an ultrasonic transducer arrangement to allow for production of medically relevant ultrasonic fields. The circuitry may be fully digitized in some embodiments, and may be integrated with the ultrasonic transducers on a single substrate, such as a CMOS substrate.

**[0036]** The aspects and embodiments described above, as well as additional aspects and embodiments, are described further below. These aspects and/or embodiments may be used individually, all together, or in any combination of two or more, as the technology described herein is not limited in this respect.

**[0037]** FIG. 1 shows an illustrative single substrate ultrasound device 100 embodying various

aspects of the technology described herein. Ultrasound device 100 comprises a substrate 101, such as a CMOS substrate or chip (e.g., a semiconductor substrate such as a silicon substrate), and integrated circuitry formed thereon. As shown, circuitry integrated with the substrate 101 may comprise waveform generator 102, encoding circuitry 103, delay mesh circuitry 105, and a plurality of ultrasound transmission units 107. An ultrasound transmission unit 107 may comprise a decoding circuit 109 and one or more ultrasound elements 111. As such, ultrasound device 100 may comprise a plurality of decoding circuits (herein also referred to as “decoding circuitry”) and a plurality of ultrasound elements. Ultrasound element 111 may include one or more ultrasonic transducers (also referred to herein as “transducer cells”). Stated differently, ultrasonic transducers may be grouped together to form ultrasound elements, as described in more detail below with reference to FIG. 3. It should be appreciated that although in some embodiments the above-described components may be integrated on a single substrate, aspects of the present technology are not limited in this respect and, in other embodiments, at least some of the above-described components may not be integrated on a same substrate with one another.

**[0038]** The illustrative configuration shown in FIG. 1 may facilitate formation of an ultrasound system-on-a-chip device or an ultrasound sub-system-on-a-chip device including integrated ultrasonic transducers and circuitry (e.g., analog and/or digital circuitry such as front-end and/or back-end circuitry for controlling operation of the ultrasonic transducers and/or processing signals produced by such transducers, for example to form and/or display ultrasound images). In at least some embodiments, an ultrasound system-on-a-chip device may include, on a single substrate, an arrangement of ultrasonic transducers integrated with analog and digital circuitry, and may be capable of performing ultrasound imaging functions such as emitting and receiving ultrasound waves and processing received ultrasound waves to produce ultrasound images.

**[0039]** As illustrated in FIG. 1., the circuitry arranged between waveform generator 102 and ultrasound elements 111 functions to provide waveforms generated by waveform generator 102 to ultrasound elements 111 in a space- and power-efficient manner and may be referred to as “compact-mesh architecture.” In the illustrated embodiment, the compact-mesh architecture includes encoding circuitry 103, delay mesh circuitry 105, and decoding circuitry 109. Though, in other embodiments, the compact mesh architecture may comprise delay mesh circuitry but not include encoding or decoding circuitry.

**[0040]** In some embodiments, waveform generator 102 may generate an initial waveform and

output the initial waveform to an input of encoding circuitry 103. Encoding circuitry 103 may be configured to encode the initial waveform to produce an encoded waveform and output the encoded waveform to an input of the delay mesh circuitry 105. Delay mesh circuitry 105 may be configured to generate a plurality of time-delayed versions of the encoded waveform and output, in parallel, the plurality of time-delayed versions of the encoded waveform to inputs of ultrasound transmission units 107. That is, the delay mesh circuitry may produce a greater number of output versions than it receives input versions. The ultrasound transmission units 107 may be configured to decode the respective ones of plurality of time-delayed versions of the encoded waveform using decoding circuitry 109 to produce a plurality of decoded waveforms and drive the ultrasound elements 111, based on the plurality of decoded waveforms, such that the ultrasound elements 111 transmit ultrasound signals corresponding to (e.g., based on) the decoded waveforms. In this way, ultrasound elements 111 may operate in parallel to emit a desired ultrasound wave, examples of which will be provided below. The above-mentioned components and corresponding functionality are described in more detail below.

**[0041]** In the embodiment shown, all of the illustrated elements are formed on a single substrate 101. It should be appreciated, however, that in alternative embodiments one or more of the illustrated elements may be coupled to substrate 101 but not be integrated with it. For example, in some embodiments waveform generator 102 may be instead located off of the substrate 101, but be coupled to the substrate 101 so that waveform generator 102 may communicate with (e.g., provide input signals to) encoding circuitry 103. As another example, the compact mesh architecture (e.g., the delay mesh circuitry 105 and, optionally, encoding circuitry 103 and decoding circuitry 109) may be integrated with the substrate 101, but the waveform generator 102 and/or ultrasound elements 111 may be coupled to but not integrated with substrate 101.

**[0042]** As described, in some embodiments ultrasound device 100 may comprise a single substrate, ultrasonic transducers integrated with that substrate, and circuitry (e.g., controlling circuitry) integrated with that substrate. It should be appreciated that the ultrasonic transducers may be positioned in any suitable way with respect to any other circuitry integrated with the substrate (e.g., waveform generator 102, encoding circuitry 103, delay mesh 105, decoding circuitry 109, etc.). In some embodiments, at least some circuitry integrated with the substrate of the ultrasound device may be positioned beneath the ultrasonic transducers of the device. In some embodiments, some of the integrated circuitry may be positioned on a peripheral region

- 10 -

(or “tab”) of the ultrasound device. For example, circuitry which is shared among two or more of the ultrasonic transducers or ultrasound elements may be positioned on the peripheral region. Circuitry specific to an ultrasound element or to a particular ultrasonic transducer may be positioned beneath that ultrasound element or ultrasonic transducer in some embodiments.

**[0043]** Waveform generator 102 may be configured to generate (or produce) any suitable excitation waveform(s) to excite the ultrasonic transducers. The waveform generator may be configured to (e.g., programmable to) generate a desired kind of waveform from among multiple possible kinds, including impulses, continuous waves, chirp waveforms (e.g., linear frequency modulation (LFM) chirps), and coded excitations (e.g., binary coded excitations). Such flexibility in the waveform generated may also facilitate the use of highly advanced ultrasound imaging techniques. In some embodiments, the waveform generator may generate a waveform as a sequence of values each of which is selected from a set of possible values. The set of possible values may consist of two values, three values, five values, at least five values, thirteen values or any other suitable number of values. For example, the set of possible values may consist of any values that may be generated by a n-bit digital to analog converter (i.e.,  $2^n$  bits), where n is any positive integer (e.g., 2, 4, 8, 16, 32, 64, etc.). In some embodiments, the waveform generator may be configured to generate outputs for a bipolar pulser.

**[0044]** As shown, waveform generator 102 is coupled to an input of encoding circuitry 103. In this way, waveform generator may provide any signal or signals 102a it generates to encoding circuitry 103. The waveform generator 102 may be coupled to an input of encoding circuitry 103 in any suitable way, as aspects of the technology described herein are not limited in this respect.

**[0045]** Encoding circuitry 103 may be configured to encode an initial waveform generated by the waveform generator 102 to produce an encoded waveform 104 and to provide the encoded waveform as an input signal to the delay mesh circuitry 105. To this end, an input of encoding circuitry 103 may be coupled to an output of waveform generator 102 and an output of encoding circuitry 103 may be coupled to an input of delay mesh circuitry 105. The coupling of the encoding circuitry 103 to waveform generator 102 and to delay mesh circuitry 105 may be implemented in any suitable way, as aspects of the technology described are not limited in this respect.

**[0046]** Encoding circuitry 103 may be configured to implement a compressive encoding so that

when the encoding circuitry 103 encodes an input signal, the resultant encoded signal consists of fewer bits than the input signal that was encoded. This reduction of data makes integration of the system described herein on a single substrate more feasible. For example, as described in more detail below, compressive encoding of the input signal allows for the delay mesh units in the delay mesh circuitry to be implemented using a smaller amount of memory, which results in space and power savings. In some embodiments, encoding circuitry 103 may be configured to implement an N-to-M bit encoder (where each of N and M is a positive integer and where N is greater than M) so that when the encoding circuitry 103 encodes an input signal consisting of B bits the resultant encoded signal consists of approximately  $B^*M/N$  bits (where B is a positive integer). As a specific non-limiting example, encoding circuitry 103 may be configured to implement a 2-to-1 bit encoder so that when the encoding circuitry encodes an input signal consisting of B bits, the resultant encoded signal consists of approximately  $B/2$  bits. As another specific non-limiting example, encoding circuitry 103 may be configured to implement a 3-to-2 bit encoder so that when the encoding circuitry encodes an input signal consisting of B bits, the resultant encoded signal consists of approximately  $2B/3$  bits. As yet another specific non-limiting example, the encoding circuitry 103 may be configured to implement a 3-to-1 bit encoder so that when the encoding circuitry encodes an input signal consisting of B bits, the resultant signal consists of approximately  $B/3$  bits. Encoding circuitry 103 is described in more detail with reference to FIGs. 7, 8A, and 8C below.

**[0047]** Delay mesh circuitry 105 may be configured to generate a plurality of time-delayed versions of a delay mesh circuitry input signal 104 corresponding to a waveform generated by a waveform generator and provide the generated time-delayed versions of the waveform to the ultrasound transmission units 107. In the embodiment of FIG. 1, the delay mesh circuitry input signal may be an encoded waveform obtained by using encoding circuitry 103 to encode a waveform generated by waveform generator 102. In other embodiments (e.g., where the encoding circuitry 103 is either not used or is not part of ultrasound device 100), the delay mesh circuitry input signal may be a waveform 102a generated by waveform generator 102. In such embodiments, the delay mesh would be able to accommodate (e.g., with appropriately sized buffers) to accommodate the unencoded input signals.

**[0048]** As shown, an input of delay mesh circuitry 105 may be coupled to an output of encoding

- 12 -

circuitry 103 and an output of delay mesh circuitry 105 may be coupled to inputs of ultrasound transmission units 107. Alternatively, an input of delay mesh circuitry 105 may be coupled to an output of waveform generator 102. The coupling of the delay mesh circuitry 105 to encoding circuitry 103 (and/or waveform generator 102) and to ultrasound transmission units 107 may be implemented in any suitable way, as aspects of the technology described herein are not limited in this respect.

**[0049]** Delay mesh circuitry 105 may be configured to generate a plurality of time-delayed versions of a delay mesh circuitry input signal at least in part by propagating the input signal through a network of interconnected delay mesh units that are part of the delay mesh circuitry. Each delay mesh unit may be configured to receive an input signal, delay it by a specified amount, and output one or more delayed versions of the input signal to one or more other delay mesh units and/or ultrasound transmission units. In this way, the delay mesh units operate to generate a set of time-delayed versions of the delay mesh input signal and provide these signals to the plurality of ultrasound transmission units 107, which operate to transmit concurrently at least some of the time-delayed versions of the delay mesh input signal to emit a desired ultrasound field. As may be appreciated, each delay mesh unit may be configured to provide one or more time-delayed versions of the signal received by the delay mesh unit to multiple other destinations (e.g., a delay mesh unit may provide a version of the signal delayed by one amount to another delay mesh unit and a version of the signal delayed by another different amount to an ultrasound transmission unit). This flexibility allows the delay mesh to create multiple instances or versions of the delay mesh input signal.

**[0050]** In some embodiments, delay mesh circuitry 105 may be controlled to produce a desired set of time-delayed versions 106 of the delay mesh input signal. In some embodiments, delay mesh circuitry 105 may be programmable so that one or more delay mesh units in the delay mesh circuitry 105 may be programmed to delay the signal(s) input to the controllable delay mesh unit(s) by an amount (e.g., amount of time, number of bits, etc.) indicated by control signal(s) provided to the delay mesh unit(s). Additionally or alternatively, the delay mesh circuitry 105 may be reconfigurable so that one or more control signals may be used to specify which delay mesh unit(s) may communicate (e.g., receive input from and/or provide output to) with one another. For example, a delay mesh unit in the delay mesh circuitry 105 may be controlled to receive an input signal from a source (e.g., another delay mesh unit, a waveform

- 13 -

generator, etc.) indicated by control signal(s) provided to the delay mesh unit. As another example, a delay mesh unit in the delay mesh circuitry 105 may be controlled to provide a delayed version 106 of the input signal to those delay mesh units and/or ultrasound transmission units that are indicated by control signal(s) provided to the delay mesh unit. Accordingly, the manner in which the delay mesh input signal is propagated through the delay mesh circuitry 105 may be controlled by providing control signals to one more delay mesh units in the delay mesh circuitry 105 in order to obtain a desired set of time-delayed versions of the delay mesh circuitry input signal. Aspects of delay mesh circuitry 105 are further described below with reference to FIGs. 4, 5A-5B, and 6.

**[0051]** Ultrasound transmission units 107 may be configured to receive the time-delayed versions of the delay mesh circuitry signal from delay mesh circuitry 105, decode the time-delayed versions of the delay mesh circuitry signal to obtain a plurality of decoded waveforms, and transmit ultrasound signals corresponding to at least a subset of the plurality of decoded waveforms. As shown, inputs of ultrasound transmission units 107 may be coupled to outputs of delay mesh circuitry 105. The coupling between the ultrasound transmission units 107 and delay mesh circuitry 105 may be implemented in any suitable way, as aspects of the technology described herein are not limited in this respect. Ultrasound device 100 may comprise any suitable number of ultrasound transmission elements. This is described in further detail below with reference to FIG. 3.

**[0052]** As shown, an ultrasound transmission unit comprises a decoding circuit 109 and one or more ultrasound elements 111. However, in some embodiments, an ultrasound transmission unit may comprise additional circuitry including, but not limited to, one or more amplifiers (e.g., one or more transimpedance amplifiers), one or more pulsers (e.g., one or more tri-level pulsers, one or more bipolar pulsers configured to drive positive and negative voltages, one or more unipolar pulsers, etc.), and/or any other suitable circuitry, as aspects of the technology described herein are not limited by the types of circuitry which are part of ultrasound elements 111.

**[0053]** Ultrasound transmission units 107 may be configured to decode the time-delayed versions 106 of the delay mesh circuitry input signal 104 by using decoding circuitry 109. Decoding circuitry 109 may be configured to implement a decoding corresponding to the encoding implemented by encoding circuitry 103. For example, in embodiments where encoding circuitry 103 is configured to encode an initial signal so that the resultant encoded signal has

fewer bits than the initial signal, decoding circuitry 109 may be configured to decode the encoded signal so that the decoded signal has a greater number of bits than the encoded signal (e.g., the decoded signal may have the same number of bits as the initial signal encoded by the encoding circuitry).

**[0054]** In some embodiments, decoding circuitry 109 may be configured to implement an M-to-N bit decoder (where each of N and M is a positive integer and where N is greater than M) so that when the decoding circuitry 109 decodes an encoded signal consisting of B bits, the resultant decoded signal consists of approximately  $B \times N/M$  bits. As a specific non-limiting example, decoding circuitry 109 may be configured to implement a 1-to-2 bit decoder so that when the decoding circuitry decodes an encoded signal consisting of B bits, the resultant decoded signal consists of approximately 2B bits. As another specific non-limiting example, decoding circuitry 109 may be configured to implement a 2-to-3 bit decoder so that when the decoding circuitry decodes an encoded signal consisting of B bits, the resultant decoded signal consists of approximately  $3B/2$  bits. Such a decoder may be useful for a 5-8 level pulser. As yet another specific non-limiting example, decoding circuitry 109 may be configured to implement a 1-to-3 bit decoder so that when the decoding circuitry decodes an encoded signal consisting of B bits, the resultant decoded signal consists of approximately 3B bits. Decoding circuitry 109 is described in more detail with reference to FIGs. 7, 8B, and 8D below.

**[0055]** Ultrasound transmission units 107 may be configured to transmit ultrasound signals corresponding to the plurality of decoded waveforms by using ultrasound elements 111. This may be done in any suitable way. For example, the ultrasound elements may be driven according to the plurality of decoded waveforms to generate ultrasound signals corresponding to the plurality of decoded waveforms. As previously described, an ultrasound element 111 may comprise one or multiple ultrasonic transducers. The ultrasonic transducers may be of any suitable type, and in some embodiments the ultrasonic transducers may be compatible with a CMOS substrate, thus allowing them to be monolithically formed on a CMOS substrate with CMOS integrated circuits. In this manner, an integrated device (e.g., an ultrasound system-on-a-chip) may be formed.

**[0056]** In some embodiments, the ultrasonic transducers may be CMOS ultrasonic transducers (CUTs), which include an ultrasonic transducer formed on a CMOS wafer and monolithically integrated with CMOS integrated circuitry. A CUT may, for example, include a cavity formed

in a CMOS wafer, with a membrane (or diaphragm) overlying the cavity, and in some embodiments sealing the cavity. Electrodes may be provided to create a transducer cell from the covered cavity structure. The CMOS wafer may include integrated circuitry to which the transducer cell may be connected.

**[0057]** CUTs are not the only type of ultrasonic transducer which may allow for integration of the transducer with an IC. In some embodiments, the ultrasonic transducers may be capacitive micromachined ultrasonic transducers (CMUTs).

**[0058]** Not all embodiments are limited to employing CUTs or CMUTs in an ultrasound transducer device of the types described herein. Some aspects of the technology described herein apply to ultrasound transducer devices irrespective of the type of ultrasonic transducer implemented. For example, in some embodiments, an array of speakers, microphones, or any suitable ultrasound transducer array may be used.

**[0059]** In some embodiments, each of the plurality of time-delayed versions of the delay mesh circuitry input signal (generated by delay mesh circuitry 105) may be output to a respective ultrasound transmission unit 107 (each comprising a decoding circuit 109 and ultrasound element 111, as shown in FIG. 1). The decoding circuit 109 of a particular ultrasound transmission unit 107 may be configured to decode the time-delayed version of the delay mesh circuitry input signal provided to the particular ultrasound transmission unit. Accordingly, the decoding circuits 109 in the ultrasound transmission units 107 may be configured to produce a plurality of decoded waveforms. In turn, the ultrasound elements 111 in the ultrasound transmission units 107 are configured to transmit ultrasound signals corresponding to the plurality of decoded waveforms.

**[0060]** In some embodiments, the ultrasound elements 111 in the ultrasound transmission units 107 are configured to transmit ultrasound signals corresponding to the plurality of decoded waveforms temporally in parallel so that the parallel transmission of the decoded waveforms results in the emission, by the single substrate ultrasound device 100, of a desired ultrasound field. For example, the emitted ultrasound field may be formed as a superposition of signals (e.g., ultrasound signals corresponding to the decoded waveforms) transmitted in parallel by the ultrasound elements 111.

**[0061]** In some embodiments, parallel transmission of two signals may be concurrent,

- 16 -

substantially concurrent, or substantially simultaneous. The transmission of two signals is concurrent if the signals have any overlap in time as they are being transmitted. The transmission of signals is substantially concurrent if overlapping in time by at least 80%, by at least 90%, or more. The transmission of two signals is simultaneous if overlapping in time by approximately 95% or more.

**[0062]** As may be appreciated from the above, the type of ultrasound field produced by parallel operation of ultrasound elements 111 depends, at least in part, on the manner in which delay mesh circuitry 105 is controlled to produce a set of time-delayed versions of a waveform, after it is encoded, and generated by waveform generator 102. The delay mesh circuitry 105 may be controlled so that the parallel operation of ultrasound elements may be configured to generate any of numerous types of ultrasound fields including, but not limited to, plane wave fields, fields having azimuthal symmetry, fields having elevation symmetry, fields having both azimuthal and elevation symmetry, cylindrical fields, cylindrical fields having azimuthal symmetry, cylindrical fields having elevation symmetry, spherically or cylindrically focused beam fields, spherically or cylindrically diverging wave fields, 3D plane wave fields, any suitable medically-relevant ultrasound field, and/or any other suitable type of ultrasound field or set of fields. As one non-limiting example, applying an inversion to waveforms according to a Hadamard code may create a suitable set of fields.

**[0063]** It should also be appreciated that controlling the manner in which the delay mesh circuitry 105 generates a set of time-delayed versions of each of a sequence of fields generated by a waveform generator may be used to implement scanning of a target and/or steering of the fields emitted by the ultrasound device. Such functionality, in turn, may be used to implement 3D imaging functionality.

**[0064]** It should also be appreciated that the architecture of a single substrate ultrasound device shown in FIG. 1 is illustrative and that variations of this architecture are possible. For example, although in the embodiment of FIG. 1 a single waveform generator 102 is coupled to encoding circuitry 103, in other embodiments ultrasound device 100 may comprise multiple waveform generators coupled to encoding circuitry 103. In such embodiments, encoding circuitry 103 may comprise multiple encoding circuits each coupled to a respective waveform generator or multiple waveform generators may be coupled to a single encoding circuit. Each waveform

- 17 -

generator may be configured to generate one or more waveforms. The waveform generators may be operated one at a time or two or more waveform generators may be operated in parallel.

**[0065]** Accordingly, in some embodiments, a single substrate ultrasound device may comprise any suitable number of waveform generators. In some embodiments, the single substrate ultrasound device may consist of fewer waveform generators than ultrasound transmission units. As discussed above, having fewer waveform generators than ultrasound transmission units, each of which including one or more ultrasonic transducers, may serve to reduce space and power required for integrating the waveform generators on a single substrate with the ultrasound transmission units (in contrast with a scenario where the number of waveform generators is equal to the number of ultrasound transmission units). As one non-limiting example, a single substrate ultrasound device may include at least twice as many ultrasound transmission units as waveform generators. As another non-limiting example, a single substrate ultrasound device may include at least four times as many ultrasound transmission units as waveform generators. As yet another non-limiting example, a single substrate ultrasound device may include eight (or sixteen, or thirty-two, or sixty-four, at least 100, at least 250, at least 500, at least 1000, at least 5000, at least 10,000, between 500 and 15,000, etc.) times as many ultrasound transmission units as waveform generators.

**[0066]** As another example of a variation of the architecture shown in FIG. 1, which shows encoding and decoding circuitry, in some embodiments a single substrate ultrasound device may be implemented without encoding and decoding circuitry. In such an embodiment, the waveform generator(s) integrated with the substrate may be coupled, directly or indirectly, to an input of the delay mesh circuitry integrated with the substrate, which in turn may be coupled to inputs of ultrasound transmission units integrated with the substrate.

**[0067]** It should also be appreciated that the components shown in FIG. 1 may be only a portion of the single substrate ultrasound device 100. For example, the components shown in FIG. 1 may be a single ultrasound circuitry module of components of ultrasound device 100, whereas ultrasound device 100 may comprise multiple such modules (e.g., at least two modules, at least ten modules, at least 100 modules, at least 1000 modules, at least 5000 modules, at least 10,000 modules, at least 25,000 modules, at least 50,000 modules, at least 100,000 modules, at least 250,000 modules, at least 500,000 modules, between two and one million modules, etc.) each module comprising the components illustrated in FIG. 1. The multiple ultrasound circuitry

- 18 -

modules may be configured to operate independently of one another and/or collaboratively with one another. This is described in more detail with reference to FIG. 3 below.

**[0068]** In some embodiments, operation of components shown in FIG. 1 may be controlled by components located off single substrate ultrasound device 100. For example, in some embodiments, another computing device (e.g., an FPGA, at least one computer hardware processor programmable using instructions stored on at least one non-transitory computer readable medium, etc.) may be configured to control operation of one or more components of single substrate device 100. As one non-limiting example, a computing device may provide one or more control signals to control operation of waveform generator 102, encoding circuitry 103, delay mesh circuitry 105, and/or one or more ultrasound transmission units 107. Additionally or alternatively, single substrate ultrasound device 100 may comprise one or more control components configured to control (e.g., via one or more control signals) operation of other components of single substrate ultrasound device 100. In some embodiments, one or more components of single substrate ultrasound device may be controlled by a combination of one or more “on-chip” components in device 100 and “off-chip” components arranged off of device 100.

**[0069]** Aspects of operation of the circuitry illustrated in FIG. 1 are further explained below with reference to FIG. 2, which is a flowchart of an illustrative process 200 for generating and transmitting an ultrasound field by using a single substrate ultrasound device to generate and transmit one or more ultrasound waveforms that form the ultrasound field. Process 200 may be performed by any suitable single substrate ultrasound device (e.g., ultrasound device 100 described with reference to FIG. 1).

**[0070]** Process 200 begins at 202, where a waveform is generated by a waveform generator. The waveform generator may be any suitable type of generator and may be integrated with the substrate of the single substrate ultrasound device such as waveform generator 102 described with reference to FIG. 1. The generated waveform may be of any suitable type (e.g., a waveform comprising one or more impulses, a continuous wave, a chirp, a coded excitation, etc.). In some embodiments, the waveform may be generated as part of process 200. In other embodiments, the waveform may have been generated prior to performance of 202 of process 200 (by the waveform generator or any other suitable circuitry) and may be loaded (or otherwise accessed) as part of stage 202 of process 200.

- 19 -

**[0071]** Next, process 200 proceeds to 204, where the waveform obtained at 202 is encoded by encoding circuitry to obtain an encoded waveform. The encoding circuitry may be of any suitable type and may be integrated with the substrate of the single substrate ultrasound device such as encoding circuitry 103 described with reference to FIG. 1. The waveform may be encoded using any suitable encoding technique (e.g., a compressive technique, a lossy encoding technique, a lossless encoding technique, any of the encoding techniques described herein, etc.). In some embodiments, the encoded waveform may consist of fewer bits than the waveform obtained at 202.

**[0072]** After an encoded waveform is obtained at 204, process 200 proceeds to 206 where one or more time-delayed versions or instances of the encoded waveform may be obtained. Any suitable number of time-delayed versions of the encoded waveform may be obtained. In some embodiments, a time-delayed version of the encoded waveform may be obtained for each of multiple ultrasound transmission units integrated with the single substrate device. As one non-limiting example, a time-delayed version of the encoded waveform may be obtained for each of some or all of the ultrasound transmission units in an ultrasound circuitry module formed on the substrate of the ultrasound device. As another non-limiting example, a time-delayed version of the encoded waveform may be obtained for each of some or all of the ultrasound transmission units in multiple ultrasound circuitry modules formed on the substrate of the ultrasound device.

**[0073]** In some embodiments, the time-delayed instance(s) of the encoded waveform may be obtained by using delay mesh circuitry integrated on the substrate of the single substrate ultrasound device. For example, delay mesh circuitry 105 (described with reference to FIG. 1) may be used to perform stage 206 of process 200. The delay mesh circuitry may comprise multiple delay mesh units and may be configured to generate the time-delayed version(s) of the encoded waveform at least in part by propagating the encoded waveform among the delay mesh units. Each of the delay mesh units may be configured to delay the waveform passing through it by a configurable amount. As described in more detail below, operation of the delay mesh may be controlled by one or multiple parameters that control how the delay mesh units in the delay mesh network communicate with one another and the manner in which each delay mesh unit operates to delay the signals passing through that unit.

**[0074]** After the time-delayed version(s) of the encoded waveform are obtained at 206, process

- 20 -

200 proceeds to 208 where the time-delayed version(s) of the encoded waveform are decoded by decoding circuitry to obtain one or more decoded waveforms. The decoding circuitry may be of any suitable type and may be integrated with the substrate of the single substrate ultrasound device such as decoding circuitry 109 described with reference to FIG. 1. The decoding may be performed using any suitable decoding technique (examples of which are described herein). In some embodiments, a decoded waveform may consist of more bits than the time-delayed version of the encoded waveform used to obtain it.

**[0075]** After the decoded waveform(s) are obtained at 208, process 200 proceeds to 210 where the decoded waveforms are used to drive the one or more ultrasound elements (e.g., ultrasound elements 111 described with reference to FIG. 1) to generate an ultrasound signals. At least some (e.g., all) of the decoded waveforms may drive multiple ultrasound elements in parallel to generate a desired ultrasound wave. Examples of ultrasound waves that may be generated in this way have been described above.

**[0076]** It should be appreciated that process 200 is illustrative and that variations are possible. For example, in some embodiments, process 200 may be performed without the performing encoding and decoding at 204 and 208, respectively. In such embodiments, a waveform generated would be generated at 202 and, at 206, one or more time-delayed version(s) of the generated waveform would be obtained. In turn, the time-delayed version(s) of the generated waveform would be provided to the ultrasound transducer(s) for transmission at 210.

**[0077]** It should also be appreciated that process 200 may be performed by each of one or multiple ultrasound circuitry modules of an ultrasound device that comprises multiple such modules. One embodiment of a single substrate ultrasound device comprising multiple ultrasound circuitry modules is shown in FIG. 3.

**[0078]** FIG. 3 shows substrate 302 (e.g., a semiconductor substrate) of an ultrasound device having multiple ultrasound circuitry modules 304 formed thereon. As shown, an ultrasound circuitry module 304 may comprise multiple ultrasound elements 306. An ultrasound element 306 may comprise multiple ultrasonic transducers 308.

**[0079]** In the illustrated embodiment, substrate 302 comprises 144 modules arranged as an array having 72 rows and 2 columns. However, it should be appreciated that a substrate of a single substrate ultrasound device may comprise any suitable number of ultrasound circuitry modules (e.g., at least two modules, at least ten modules, at least 100 modules, at least 1000 modules, at

- 21 -

least 5000 modules, at least 10,000 modules, at least 25,000 modules, at least 50,000 modules, at least 100,000 modules, at least 250,000 modules, at least 500,000 modules, between two and a million modules, etc.) that may be arranged as an two-dimensional array of modules having any suitable number of rows and columns or in any other suitable way.

**[0080]** In the illustrated embodiment, each module comprises 64 ultrasound elements arranged as an array having two rows and 32 columns. However, it should be appreciated that an ultrasound circuitry module may comprise any suitable number of ultrasound elements (e.g., one ultrasound element, at least two ultrasound elements, at least four ultrasound elements, at least eight ultrasound elements, at least 16 ultrasound elements, at least 32 ultrasound elements, at least 64 ultrasound elements, at least 128 ultrasound elements, at least 256 ultrasound elements, at least 512 ultrasound elements, between two and 1024 elements, at least 2500 elements, at least 5,000 elements, at least 10,000 elements, at least 20,000 elements, between 1000 and 20,000 elements, etc.) that may be arranged as a two-dimensional array of ultrasound elements having any suitable number of rows and columns or in any other suitable way.

**[0081]** In the illustrated embodiment, each ultrasound element comprises 16 ultrasonic transducers arranged as a two-dimensional array having four rows and four columns. However, it should be appreciated that an ultrasound element may comprise any suitable number of ultrasonic transducers (e.g., one, at least two, at least four, at least 16, at least 25, at least 36, at least 49, at least 64, at least 81, at least 100, between one and 200, etc.) that may be arranged as a two dimensional array having any suitable number of rows and columns (square or rectangular) or in any other suitable way.

**[0082]** It should be appreciated that any of the components described above (e.g., ultrasound transmission units, ultrasound elements, ultrasound transducers) may be arranged as a one-dimensional array, as a two-dimensional array, or in any other suitable manner.

**[0083]** As previously described, an ultrasound circuitry module may comprise circuitry in addition to one or more ultrasound elements. In some embodiments, an ultrasound circuitry module may comprise one or more waveform generators (e.g., two waveform generators, four waveform generators, etc.), encoding circuitry (e.g., encoding circuitry 103), delay mesh circuitry (e.g., delay mesh circuitry 105), and/or decoding circuitry (e.g., decoding circuitry 109 comprising one or more decoding circuits). These examples of circuitry that may be part of an

ultrasound circuitry module are illustrative and are not limiting, as an ultrasound circuitry may additionally or alternatively comprise any other suitable circuitry.

**[0084]** In some embodiments, a single substrate ultrasound device may comprise module interconnection circuitry integrated with the substrate and configured to connect ultrasound circuitry modules to one another to allow data to flow among the ultrasound circuitry modules. For example, the device module interconnection circuitry may provide for connectivity among adjacent ultrasound circuitry modules. In this way, an ultrasound circuitry module may be configured to provide data to and/or received data from one or more other ultrasound circuitry modules on the device.

**[0085]** In embodiments where ultrasound circuitry modules are configured to communicate with one another, a time-delayed version of a waveform generated by a waveform generator (and optionally encoded) in one ultrasound circuitry module may be propagated to and (after decoding if encoding was performed) transmitted by one or more ultrasound elements in one or more other ultrasound circuitry modules. As one non-limiting example, an ultrasound field may be generated by using a single waveform generator disposed near the center of the substrate by propagating the generated waveform outward through all the ultrasound circuitry modules. The propagation of a signal originating in a first ultrasound circuitry module to a second circuitry module may be performed at least in part by propagating the signal through the delay mesh of the first ultrasound circuitry module, the delay mesh of the second circuitry module, and the delay mesh(es) of any ultrasound circuitry modules separating the first and second ultrasound circuitry modules. As such, it should be appreciated that module interconnection circuitry may comprise circuitry connecting the delay meshes of different ultrasound circuitry modules.

**[0086]** Aspects of delay mesh circuitry (e.g., delay mesh circuitry 105 of FIG. 1) may be further understood with reference to FIG. 4 that illustrates delay mesh circuitry 403 comprising a plurality of delay mesh units 404. Delay mesh circuitry 403 may be configured to receive input signals from input circuitry 402 and provide output signals to ultrasound transmission units 406. In the illustrated embodiment, an input of each delay mesh unit 404 is coupled to an output of input signal circuitry 402, which is configured to provide one or more input signals to delay mesh units 404. An output of each delay mesh unit 404 is coupled to an input of a corresponding ultrasound transmission unit 406. Accordingly, delay mesh units 404 in delay mesh circuitry 403 may be configured to receive an input signal from input signal circuitry 402, generate multiple

- 23 -

time-delayed versions of the input signal, and provide the generated time-delayed versions of the input signal to the ultrasound transmission units 406.

**[0087]** In some embodiments, input signal circuitry 402 comprises encoding circuitry (e.g., encoding circuitry 103 of FIG. 1) configured to provide encoded signals as input signals to delay mesh circuitry 403. The encoding circuitry may provide, as input signals to delay mesh units 404, one or more encoded waveforms obtained by encoding one or more waveforms generated by one or multiple waveform generators (e.g., waveform generator 102 of FIG. 1). Additionally or alternatively, input signal circuitry 402 may comprise one or multiple waveform generators (e.g., one waveform generator, two waveform generators, three waveform generators, etc.) configured to generate waveforms and provide them to the delay mesh units 404 as input signals.

**[0088]** Delay mesh circuitry 403 may be coupled to any suitable number of ultrasound transmission units 406 (e.g., at least one unit, at least two units, at least four units, at least eight units, at least sixteen units, at least 32 units, at least 64 units, at least 128 units, at least 256 units, some or all of the ultrasound transmission units in a single ultrasound circuitry module, some or all of the ultrasound transmission units in multiple ultrasound circuitry modules, etc.).

**[0089]** In the illustrated embodiment, an output of each delay mesh unit 404 is coupled to an input of a single corresponding ultrasound transmission unit 406. However, in some embodiments, one or multiple delay mesh units 404 may be configured to provide output signals to multiple ultrasound transmission units 406, as aspects of the technology described herein are not limited in this respect. This is discussed further with reference to FIG. 5B.

**[0090]** Delay mesh circuitry 403 comprises a network of interconnected delay mesh units 404. As described in more detail below, each delay mesh unit 404 may be configured to receive one or more input signals from one or more sources (e.g., one or more other delay mesh units and/or input signal circuitry 402), receive one or more control signals, perform one or more actions on the input signal(s) based, at least in part, on the control signals to produce one or more output signals, and provide the output signals to one or multiple destinations (e.g., one or more other delay mesh units 404 and/or one or more ultrasound transmission units 406).

**[0091]** Delay mesh circuitry 403 may comprise any suitable number of delay mesh units. In some embodiments, delay mesh circuitry 403 may comprise at least as many delay mesh units as the number of ultrasound transmission units to which delay mesh circuitry 403 is coupled. As

one non-limiting example, delay mesh circuitry 403 may comprise the same number of delay mesh units as the number of ultrasound transmission units to which delay mesh circuitry 403 is coupled. As another non-limiting example, delay mesh circuitry 403 may comprise at least twice (or three times, or four time, or five times, etc.) as many delay mesh units as the number of ultrasound transmission units to which delay mesh circuitry 403 is coupled.

**[0092]** A delay mesh unit may be configured to perform any of numerous types of actions on an input signal including, but not limited to, any one or more of: delaying the input signal before outputting it to one or more destinations, selecting and providing a portion of the input signal as the output signal to one or more destinations, and performing any suitable bit-level arithmetic and/or logical operation on the input signal.

**[0093]** A delay mesh unit may be configured to output different versions of the input signal to different destinations. For example, in some embodiments, a delay mesh unit may be configured to delay the input signal by a first amount and provide the resulting delayed signal to one or more delay mesh units, and delay the input signal by a second amount and provide the resulting delayed signal to one or more ultrasound transmission units.

**[0094]** Delay mesh units 404 may be configured to communicate with (e.g., receive input from and/or provide output to) one another. In some embodiments, a delay mesh unit may be configured to communicate with one or more adjacent delay mesh units in the delay mesh circuitry. For example, as shown in FIG. 4, a delay mesh unit is configured to communicate with its left and right neighbors. As another example, if the delay mesh units were arranged in a two-dimensional grid, a delay mesh unit may be configured to communicate with one or more of its left, right, top, and bottom neighbors. It should be appreciated, however, that a delay mesh unit is not limited communicating with its neighboring delay mesh units and, additionally or alternatively, may be configured to communicate with any other delay mesh unit in the delay mesh circuitry (e.g., diagonal neighbors, neighbors of neighbors, delay mesh units beyond neighbors, delay mesh units in a same row, delay mesh units in a same column, etc.).

**[0095]** Delay mesh circuitry may be controlled to produce a desired set of time-delayed versions of the delay mesh input signal in response to one or more delay mesh circuitry control signals. In some embodiments, delay mesh circuitry may be configured to produce a different set of time-delayed versions of the same delay mesh input signal in response to different delay mesh circuitry control signals. In some embodiments, delay mesh circuitry may be controlled at

- 25 -

varying degrees of precision (e.g., within a desired time period, to within a desired number of clock cycles, to within a specified phase of the input waveform, etc.) to produce delayed versions of the delay mesh input signal.

**[0096]** A delay mesh circuitry control signal may comprise one or more delay mesh unit control signals for controlling individual delay mesh units in the delay mesh. A delay mesh unit control signal may control various aspects of how a delay mesh unit operates. FIG. 5A illustrates portions of a delay mesh unit control signal applied to delay mesh unit 500 (shown outside of any delay mesh circuitry).

**[0097]** In some embodiments, a delay mesh unit control signal may specify the source from which the delay mesh unit is to receive an input signal. For example, the delay mesh unit control signal for a delay mesh unit may specify another delay mesh unit as the source from which the delay mesh unit is to receive an input signal or may select delay mesh input circuitry (e.g., a waveform generator, an encoder encoding output of a waveform generator, etc.) as the source from which the delay mesh unit is to receive an input signal. As shown in FIG. 5A, for instance, a delay mesh unit control signal comprises portion 502a for controlling selection of the source from which the delay mesh unit 500 is to receive an input signal. In the embodiment of FIG. 5A, portion 502a controls selection of the source (e.g., by controlling a multiplexer) from among four neighboring delay mesh units and a waveform generator. In other embodiments, portion 502a may control selection of the source from among any suitable number of delay mesh units (neighboring or not) and/or any suitable number of waveform generators, as aspects of the technology described herein are not limited in this respect.

**[0098]** A delay mesh unit may comprise a buffer (e.g., implemented as a shift register, addressable memory, and/or in any other suitable way) configured to store one or more input signals received by the delay mesh unit (e.g., from another delay mesh unit, from a waveform generator, etc.). Accordingly, in some embodiments, a delay mesh unit control signal may specify the location(s) in the buffer to which the input signal is to be written. As shown in FIG. 5A, for instance, a delay mesh unit control signal comprises portion 502c (termed “write select”) for specifying the location(s) in the buffer to which the input signal is to be written. As one non-limiting example, in embodiments where the buffer is implemented as a shift register, portion 502c may specify a location within the shift register to which the input signal is to be written. As another non-limiting example, in embodiments where the buffer is implemented as addressable

memory, portion 502c may specify an initial location starting from which the input signal is to be written contiguously to the buffer or portion 502c may specify a set of locations to which to write the input signal.

**[0099]** In some embodiments, a delay mesh unit control signal may specify the location(s) in the buffer from which a signal to be output is to be read. As shown in FIG. 5A, for instance, a delay mesh unit control signal comprises portion 502b (termed “read select”) for specifying the location(s) in the buffer from which the input signal is to be read. As one non-limiting example, in embodiments where the buffer is implemented as a shift register, portion 502b may specify a location within the shift register from which the output signal is to be read. As another non-limiting example, in embodiments where the buffer is implemented as addressable memory, portion 502b may specify an initial location starting from which the input signal is to be read contiguously from the buffer or portion 502b may specify a set of locations to which to read the output signal.

**[0100]** As may be appreciated from the above, controlling location(s) in a buffer of a delay mesh unit to which to write an input signal and the locations from which to read an output signal from the buffer allows for specifying an amount of time (e.g., by number of clock samples) by which to delay a signal coming into the delay mesh unit before outputting it to a destination (e.g., another delay mesh unit and/or an ultrasound transmission unit). In this way, each delay mesh unit in delay mesh circuitry may be controlled to delay respective input signals by specified amounts. It should be appreciated that different delay mesh units may be controlled to delay respective incoming input signals by different amounts, as aspects of the technology provided herein are not limited in this respect.

**[0101]** Additionally, a delay mesh unit control signal may comprise a reset signal (e.g., portion 502d in FIG. 5A termed “RST”) to reset the delay mesh unit, a clock signal (e.g., portion 502e in FIG. 5A termed “CLK”), a signal indicating whether or not to invert the waveform being output to the ultrasound transmission unit (see e.g., portion 502f in FIG. 5A termed “invert”), a signal indicating whether to enable or disable the delay mesh unit (see e.g., portion 502f in FIG. 5A termed “unit enable”), and a signal indicating whether to enable or disable output to one or more output destinations such as a pulser in a corresponding ultrasound transmission unit (see e.g., portion 502h in FIG. 5A termed “output enable”) or one or more other delay mesh units. The unit enable and output enable signals may be used to power down the delay mesh unit or to

enable its use as a buffer but suppress the output to one or more output destinations such as the corresponding ultrasound transmission unit(s).

**[0102]** FIG. 5B provides the architecture of an illustrative delay mesh unit 550, in accordance with some embodiments described herein. Delay mesh unit 550 may be any suitable delay mesh unit and, for example, may be one of delay mesh units 404 described with reference to FIG. 4. Delay mesh unit 550 may be controlled by one or more delay mesh unit control signals. As shown, delay mesh unit 550 is controlled by delay mesh control signal 556. Delay mesh control signal 556 comprises portions 576a, 576b, 576c, which are described in more detail below, and portion 576d comprising the clock and reset signals previously described. Delay mesh unit control signal 556 may be provided by one or more “on-chip” components integrated with the single substrate device on which delay mesh unit 550 is integrated on, by one or more “off-chip” components such as one or more computing device(s) coupled to the single substrate ultrasound device, but not integrated with it, or by one or more on-chip and one or more off-chip components.

**[0103]** Delay mesh unit 550 comprises input wires 566 controlled by delay mesh control signal portion 576a (termed “direction select) to select the source from which delay mesh unit 550 receives input. In some embodiments, input wires 566 may comprise at least one multiplexer controllable by portion 576a to select an input source. As shown, delay mesh unit 550 may be controlled to receive an input signal from one of neighboring delay mesh units 552 or from other input circuitry such from one or more waveform generators (shown as waveform generator(s) 554) or encoding circuitry (not shown). It should be appreciated that a delay mesh unit is not limited to receiving input only from one or more neighboring delay mesh units (e.g., units to the left, to the right, above and below the delay mesh unit) and, for example, may be configured to receive input from any other delay mesh unit part of delay mesh circuitry in the single substrate ultrasound device. For example, in an embodiment where the delay mesh units are arranged in a two-dimensional grid, a delay mesh unit may be configured to receive input from another delay mesh unit located at a diagonal to the delay mesh unit.

**[0104]** Delay mesh unit 550 further comprises delay unit 565 used, at least in part, for storing input signals received by delay mesh unit 550 via input wires 566. The circuitry in delay mesh unit 550, but not in delay unit 565 may be referred to as “mesh linkage.” As shown in FIG. 5B, mesh linkage includes input wires 566, output wires 574, and output wire 575.

**[0105]** Delay unit 565 comprises buffer 570, write select circuitry 568 configured to control (in response to “write select” delay mesh unit control signal portion 576b) the location(s) in buffer 570 to which an input signal received by delay mesh unit 550 is to be written, and read select circuitry 572 configured to control (in response to “read select” portion 576c) the location(s) in buffer 570 from which to read a signal to be provided as an output signal to one or more output destinations. It should be appreciated that delay unit 565 is one embodiment of a delay unit and that a delay unit may be implemented in any other suitable way, as aspects of the technology described herein are not limited in this respect.

**[0106]** In some embodiments, buffer 570 may be implemented as a shift register. In such embodiments, each of write select circuitry 568 and read select circuitry 572 may be implemented using one or more multiplexers respectively configured to select the location(s) in buffer 570 to which to write an input signal and from which to read an output signal. In other embodiments, buffer 570 may be implemented as addressable memory. In such embodiments, each of write select circuitry 568 and read select circuitry 572 may be configured to use one or more pointers to select the location(s) in buffer 570 to which to write an input signal and from which to read an output signal. The pointer may be incremented in any suitable way, as aspects of the technology provided herein are not limited in this respect. It should be appreciated that buffer 570 is not limited to being implemented as a shift register or addressable memory and may be implemented in any other suitable way.

**[0107]** Regardless of the manner in which buffer 570 is implemented, buffer 570 may be configured to store an input signal of any suitable size. As one non-limiting example, buffer 570 may be configured to store 10 values or less, 20 values or less, values bits or less, 50 values or less, 100 values or less between 10-100 values, between 50 and 500 values, between 100 and 1000 values, between 500 and 1000 values or any other suitable number of values. In turn, each value may consist of any suitable number of bits (e.g., one bit, two bits, four bits, eight bits, 16 bits, 32 bits, 64 bits, 128 bits, 256 bits, etc.).

**[0108]** An output signal from delay mesh unit 550 may be provided to one or more output destinations. As shown, delay mesh unit 550 comprises output wires 574 configured to provide an output signal from buffer 570 to one or more delay mesh units 558 (which may be the same as or different from delay mesh units 552). Output wires 574 may comprise any

suitable number of wires to enable providing the output signal to any suitable number of delay mesh units (e.g., one, two, three, four, five, etc.).