(19) 日本国特許庁(JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-145527

(P2006-145527A)

(43) 公開日 平成18年6月8日(2006.6.8)

(51) Int.C1.

GO 1 R 31/28

(2006, 01)

F 1

GO 1 R 31/28

GO 1 R 31/28

V

G

### テーマコード（参考）

2 G 1 3 2

(21) 出願番号 特願2005-326186 (P2005-326186)

(22) 出願日 平成17年11月10日 (2005.11.10)

(31) 優先権主張番号 10/996113

(32) 優先日 平成16年11月23日 (2004.11.23)

(33) 優先権主張国 米国 (US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

A G I L E N T   T E C H N O L O G I E

S,   I N C.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100087642

弁理士 古谷 脩

(74) 代理人 100076680

弁理士 溝部 孝彦

(74) 代理人 100121061

弁理士 西山 清春

最終頁に続く

(54) 【発明の名称】埋め込み型時間領域反射率試験の方法及び装置

(57) 【要約】 (修正有)

**【課題】**プリント回路基板の配線の故障を最小限のコストと時間で特定する埋め込み型時間領域反射率試験の方法及び装置を提供する。

【解決手段】集積回路を搭載した回路基盤の配線を試験する方法及び装置であって、搭載された集積回路より発生される試験遷移信号を配線 102 に送出し、その試験遷移信号の反射 502 をキャプチャすることにより、時間領域反射率試験を実施する機能を有する回路が組み込まれた I C を含む方法及び装置。

【選択図】図 2

**【特許請求の範囲】****【請求項 1】**

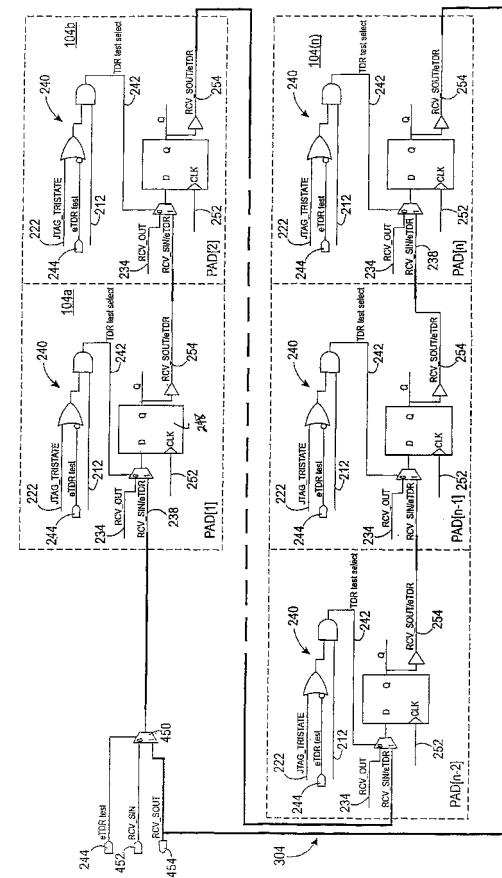

クロック(210)によって制御される1以上の入出力(「I/O」)パッド(104)を有する集積回路(「IC」)(100)を含む装置であって、該I/Oパッド(104)のそれぞれが、出力インピーダンス(202)を有するデータ出力ドライバ回路(200)と、データ出力レジスタ(206)と、プログラマブル基準電圧発生器(232)を有するレシーバ回路(226)と、前記クロック(210)とデータキャプチャレジスタ(248)との間に配置されたプログラマブル遅延素子(250)と、前記データキャプチャレジスタ(248)に対する入力(238)を選択するためのデータキャプチャ選択論理回路(450)とを含み、前記データキャプチャレジスタ(248)が前記プログラマブル遅延素子(250)の出力(252)によってクロック供給を受ける、装置。

10

**【請求項 2】**

前記I/Oパッド(104)を少なくとも2つ有し、該少なくとも2つのI/Oパッド(104)のデータキャプチャレジスタ(248)が相互接続され、シフトレジスタとして機能する、請求項1に記載の装置。

**【請求項 3】**

前記シフトレジスタの開始点は、前記データキャプチャ選択論理回路(450)によって決定される、請求項1又は請求項2に記載の装置。

**【請求項 4】**

前記データキャプチャレジスタ(248)は、マルチビットローカル記憶素子に対する入力を生成する、請求項1又は請求項2に記載の装置。

20

**【請求項 5】**

前記I/Oパッド(104)を少なくとも2つ有し、該少なくとも2つのI/Oパッド(104)のデータ出力レジスタ(206)が相互接続され、シフトレジスタとして機能する、請求項1又は請求項2に記載の装置。

**【請求項 6】**

前記データ出力レジスタ(206)は読み出し可能であり、且つ、前記I/Oパッドに少なくとも1つの試験遷移信号を供給するためのデータを格納する、請求項1又は請求項2に記載の装置。

**【請求項 7】**

前記ICは伝送要素(106)に接続され、前記データ出力ドライバ回路(200)は試験遷移信号を前記伝送要素(106)に送出し、前記データキャプチャレジスタ(248)は前記試験遷移信号の反射から得られるデータを格納する、請求項1又は請求項2に記載の装置。

30

**【請求項 8】**

前記I/Oパッド(104)をN個有し、該I/Oパッドのそれぞれがスキャンイン信号(238)を受け取ってスキャンアウト信号(254)を生成し、前記I/Oパッドがレシーバスキャンチェーン(304)として連続的に接続され、前記I/Oパッドのうちの1つから出力された前記スキャンアウト信号(254)を前記I/Oパッドのうちの別の1つに前記スキャンイン信号(238)として渡し、N番目のI/Oパッドの前記スキャンアウト信号(254)を最初のI/Oパッド(104)に前記スキャンイン信号(238)として渡し、循環レシーバスキャンチェーン構成を実現している、請求項1に記載の装置。

40

**【請求項 9】**

TDR試験信号(244)がアサートされたときにのみ、前記N番目のI/Oパッドの前記スキャンアウト信号(254)が、前記最初のI/Oパッドに前記スキャンイン信号(238)として渡される、請求項8に記載の装置。

**【請求項 10】**

前記TDR試験信号(244)がアサートされたときに、前記N番目のI/Oパッドの前記スキャンアウト信号(254)は、循環MUX(450)を通じて前記最初のI/O

50

パッド(104)に前記スキャンイン信号(238)として渡される、請求項8又は請求項9に記載の装置。

#### 【請求項11】

集積回路(IC)に接続された伝送要素を試験する方法であって、

クロック(210)によって制御される少なくとも1つの入出力(I/O)パッド(104)を有するIC(100)を設けるステップと、

前記I/Oパッド(104)から前記伝送要素(106)に試験遷移信号を送出するステップ(416)と、

前記クロック(210)に遅延(250)を加えたものが変化したときに、前記I/Oパッド(104)において、電圧基準(232)に対する前記試験遷移信号の反射の振幅状態を示すデータをキャプチャするステップと

10

からなる方法。

#### 【請求項12】

前記電圧基準(232)はプログラム可能である(410)、請求項11に記載の方法。

。

#### 【請求項13】

前記電圧基準(232)の複数の値について、前記送出するステップ(416)及び前記キャプチャするステップ(418)を繰り返すステップ(428)を更に含む、請求項11又は請求項12に記載の方法。

#### 【請求項14】

前記遅延(250)はプログラム可能であり(412)、

前記遅延(250)の複数の値について、前記送出するステップ(416)及び前記キャプチャするステップ(418)を繰り返すステップ(424)を更に含む、請求項11に記載の方法。

20

#### 【請求項15】

前記I/Oパッド(104)のそれぞれが、出力インピーダンス(202)を有するデータ出力ドライバ回路(200)と、読み出し可能なデータ出力ドライバ回路(206)と、プログラマブル基準電圧発生器(232)を有するレシーバ回路(226)と、前記クロック(210)とプログラマブル遅延素子(250)の出力によってクロック供給を受けるデータキャプチャレジスタ(248)との間に配置されたプログラマブル遅延素子(250)と、前記データキャプチャレジスタ(248)に対する入力を選択するためのデータキャプチャ選択論理回路(450)とを含み、前記データキャプチャレジスタ(248)が前記プログラマブル遅延素子(250)の出力によってクロック供給を受ける、請求項11、請求項12、又は請求項14に記載の方法。

30

#### 【請求項16】

前記データキャプチャレジスタレジスタ間を相互接続し、シフトレジスタとして機能させるステップを更に含む、請求項11又は請求項12に記載の方法。

#### 【請求項17】

前記設定するステップは、前記I/Oパッド(104)のうちの1つだけを試験対象の伝送線(106)に接続し、該伝送線に関連する前記データキャプチャレジスタ(248)を前記シフトレジスタの開始点として設定することを含む、請求項16に記載の方法。

40

#### 【請求項18】

前記遅延の複数の値及び前記電圧基準(232)の複数の値について前記送出するステップ(416)及び前記キャプチャするステップ(418)を繰り返し、前記反射に関する電圧と時間の関係(502)を作成することを更に含む、請求項17に記載の方法。

#### 【請求項19】

前記反射に関する電圧と時間の関係(502)から前記伝送要素の伝送特性を判定するステップを更に含む、請求項18に記載の方法。

#### 【請求項20】

前記ICはN個のI/Oパッド(104)を有し、該I/Oパッドのそれぞれがスキャ

50

ンイン信号(238)を受け取ってスキャンアウト信号(254)を生成し、前記I/Oパッド(104)がレシーバスキャンチェーン(304)として連続的に接続され、前記I/Oパッド(104)のうちの1つから出力された前記スキャンアウト信号(254)が前記I/Oパッド(104)のうちの別の1つに前記スキャンイン信号(238)として渡され、N番目の前記I/Oパッド(104)の前記スキャンアウト信号(254)が最初の前記I/Oパッド(104)に前記スキャンイン信号(238)として渡され、循環スキャンチェーン構成を実現している、請求項11、請求項12、又は請求項14に記載の方法。

#### 【請求項21】

前記TDR試験信号(244)がアサートされたときに、前記N番目のI/Oパッドの前記スキャンアウト信号(254)が、循環MUX450を通じて前記最初のI/Oパッドに前記スキャンイン信号(238)として渡される、請求項20に記載の方法。 10

#### 【発明の詳細な説明】

#### 【背景技術】

#### 【0001】

プリント回路基板(PCB)が故障するとき、その原因には様々なものがある。原因の特定は非常に困難であり、PCBのサイズや複雑さが増すにつれて、原因の特定はさらに困難になる。PCB故障の原因はICの故障である場合もあれば、IC間の1以上の配線の故障である場合もある。PCB上のICを試験する従来の方法には、様々なものがある。IC試験法には、専用装置を使用して機能試験を行うインサーキット試験法から、IEE規格1149.1仕様書に記載されているようなJTAGプロトコルを用いた試験まで、様々なものがある。また、ICによっては、特定のICが使用可能であるか否かを示す指標を出力する自己試験機能が組み込まれたものもある。しかしながら、こうした試験によって特定できるのは、PCB故障を引き起こす可能性がある全ての故障のうちの一部に過ぎない。 20

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0002】

従来は、IC間の配線の故障や配線インピーダンスの問題を特定するために、システムからPCBを取り外し、更にPCBから1以上のICを取り外した上で試験を実施している。しかしながら、こうした手順は時間やコストを要する上に、破壊の可能性も有している。従って、PCB配線の故障を最小限の費用で特定することが必要とされている。 30

#### 【課題を解決するための手段】

#### 【0003】

ICに埋め込まれた埋め込み型試験を実施することで、そのICに対する外部接続を試験する方法及び装置を開示する。「埋め込み型試験」と呼ぶ理由は、試験を実施する回路をIC自体に配置しているからである。本発明による埋め込み型試験は、時間領域反射率測定(以下、「TDR」と呼ぶ)を基礎としたものであり、IC外部の素子を試験する機能を有する。擬似TDR試験を実施するための論理回路をICの1以上のI/Oパッド、又はそれらのI/Oパッドに接続された回路に埋め込む。この論理回路は、幾つかの新規な論理回路及び配線を備えるとともに、従来のI/Oパッドの一部に形成された既存の回路を有効に利用し、試験機能の埋め込みによって生じるコストやサイズの増加を最小限に抑えることが出来る。埋め込み型試験機能の一部として追加される論理回路は、ICの実際の機能とは無関係であり、IC外部の素子を試験するという特定の目的のためにICに組み込まれる。 40

#### 【発明を実施するための最良の形態】

#### 【0004】

本発明は、添付の図面を参照し、下記の説明を読むことにより理解できるであろう。 50

## 【0005】

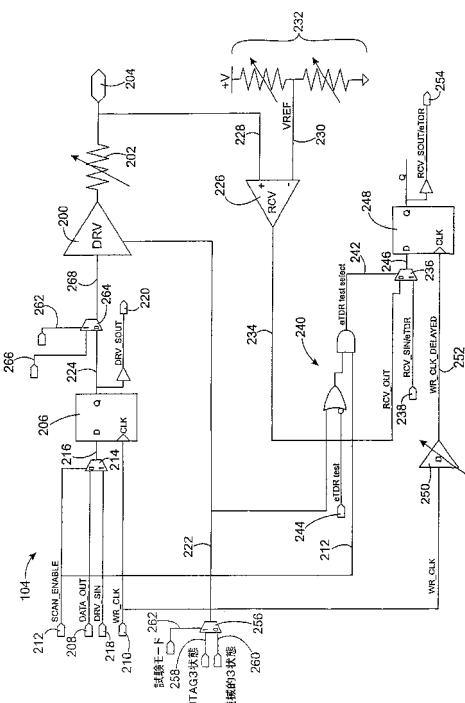

まず図1を参照する。図1はパッケージIC100の角の部分を示している。従来同様に、パッケージIC100は、ICチップ内の論理回路104とICピン106との間に、パッケージ配線102を有している。ICピン106は、ガルウィングリード、ボールグリッドアレイリード、又はフリップチップ型リード（ただし、これらに限定はしない）のような、いかなる従来タイプのものであってもよい。説明のために、IC上の論理回路104は、IC100の入出力機能を有する特定タイプの論理回路から構成されているものとする。本明細書では、この入出力機能を有するIC100内の回路をI/Oパッド104と呼ぶ。なお、この回路は、アナログ素子とデジタル素子のどちらで構成してもよく、また、それら両方から構成してもよい。この回路は物理的には、接点部の近くに配置してもよいし、ICの他の面に分散して配置してもよい。

10

## 【0006】

本発明の埋め込み型TDR試験法は、既知のインピーダンス、振幅、及び持続時間有する遷移信号すなわちパルスを伝送要素の一端に印加するステップを含む。ICに取り付けられる伝送要素には一般に、PCBトレースの形の伝送ラインがある。伝送ラインは終端を備えている場合もあれば、備えていない場合もある。既知のインピーダンス、振幅、及び持続時間を有する遷移信号すなわちパルスを伝送要素に送出し、反射された信号を測定する。そして、反射信号の特性を送信信号の既知の特性と比較し、反射信号の特性を分析することで、伝送ラインのインピーダンス、伝送ラインの電気的な長さ、伝送ラインの不具合の有無、場所、及び特性、並びに終端インピーダンスなどの情報が得られる。

20

## 【0007】

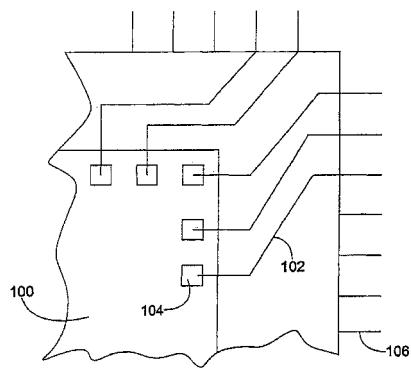

次に図2を参照する。図2は、本発明によるI/Oパッド104を示す論理図である。データ出力ドライバ回路200は、外部接続パッド204に接続されたプログラマブル出力インピーダンス202を有する。一般に、一個のIC上には複数のI/Oパッド104が存在する。図2の論理図は各I/Oパッド104上の論理回路を示している。データ出力ドライバ回路200は、既知の出力インピーダンスの変化すなわちパルスを加えることが出来る。一実施形態では、プロセス、電圧、及び温度（PVT）が補償された従来のドライバ回路を使用することが出来る。データ出力ドライバ回路200は、3状態イネーブル信号222によって制御される。データ出力ドライバ回路200を高インピーダンス状態にすると、データ出力ドライバ回路200はディセーブルされる。データ出力ドライバ回路200をイネーブルすると、その入力部における論理値が、プログラマブル出力インピーダンス202を通じて外部接続パッド204に出力される。本発明の一実施形態において、3状態イネーブル信号222は、JTAG3状態イネーブルレジスタ（図示せず）から供給される。JTAG3状態イネーブルレジスタは、TDR試験の準備の際にそこにユーザ定義データをロードしておくことが出来るという意味で、スキヤンすることが可能である。本発明の他の実施形態において、3状態イネーブル信号222は2対1の3状態MUX256の出力である。この3状態MUX256は入力として、JTAG3状態イネーブルレジスタの出力258と、機能的3状態信号260とを有する。3状態MUX256の出力の選択は、試験モード信号262によって制御される。データ出力レジスタ206は、IC論理回路（図示せず）からデータアウト信号208を受信する。このデータアウト信号208は、書き込み／読み出しクロック信号210に従ってデータ出力レジスタ206に入力される。一実施形態において、データ出力レジスタ206の出力はデータ出力ドライバ回路200に直接出力され、外部接続パッド204へと出力される場合がある。図2に記載されている他の実施形態では、データ出力レジスタの出力224が、2対1のデータアウトMUX264の一方の入力になっている。また、データアウトMUX264の他方の入力が、JTAGデータアウト信号266になっている。データアウトMUX264の出力の選択は、試験モード信号262によって制御される。この実施形態の場合、データアウトMUX264の出力はデータ出力ドライバ回路200へ出力され、外部接続パッド204へと出力される。従って、試験モード信号が論理「1」である場合、3状態MUX256はその出力222としてJTAG3状態信号を出力し、データアウトMU

30

40

50

X 2 6 4 はその出力 2 6 8 として J T A G データアウト信号を出力する。一方、試験モード信号が論理「0」である場合、3 状態 MUX 2 5 6 はその出力 2 2 2 として機能的 3 状態信号 2 6 0 を出力し、データアウト MUX 2 6 4 はその出力 2 6 8 としてデータ出力レジスタ 2 0 6 の出力を出力する。このように 3 状態 MUX 2 5 6 及びデータ出力 MUX 2 6 4 を有する実施形態では、データ出力ドライバ回路 2 0 0 は、I C 論理回路回路の一部に関する J T A G 信号又は機能的信号によって制御することができる。なお、J T A G 3 状態信号 2 5 8 、 J T A G データアウト信号 2 6 6 、及び試験モード信号 2 6 2 の供給元である図 2 には図示されていない種々のレジスタは、I E E E 1 4 4 9 . 6 規格に準拠し、書き込み / 読み出しクロック信号 2 1 0 及び遅延クロック信号 2 5 2 とは非同期の別のクロックによって動作している。スキャンイネーブル信号 2 1 2 はスキャンイネーブルマルチプレクサ 2 1 4 を制御し、スキャンイネーブルマルチプレクサ 2 1 4 にデータアウト信号 2 0 8 又はスキャンイン信号 2 1 8 を選択させ、それをスキャンイネーブルマルチプレクサ出力 2 1 6 に出力させる。また、データ出力レジスタ 2 0 6 の出力 2 2 4 は、スキャンアウト信号 2 2 0 としても出力される。

#### 【 0 0 0 8 】

I / O パッド 1 0 4 は、比較器タイプのデータ入力シーバ回路 2 2 6 を更に有する。データ入力シーバ回路 2 2 6 の正の入力 2 2 8 は外部接続パッド 2 0 4 に接続され、データ入力シーバ回路 2 2 6 の負の入力 2 3 0 は基準電圧発生器 2 3 2 に接続される。データ入力シーバ回路 2 2 6 は、外部接続パッド 2 0 4 の電圧を基準電圧と比較することによりデジタル信号を生成する。好ましい実施形態において、データ入力シーバ回路 2 2 6 は、広いコモンモードレンジにわたって動作し、コモンモードレンジにおいて最小限の伝播遅延を有し、最小限のオフセット電圧を有する。基準電圧発生器 2 3 2 をプログラムすることにより、データ入力シーバ回路 2 2 6 が外部接続パッド 2 0 4 上の信号を論理「1」又は論理「0」として登録する電圧レベルを設定することができる。好ましい実施形態において、プログラマブル基準電圧発生器 2 3 2 は、論理「0」から論理「1」までの範囲で、6 つ以上（多い方が望ましい）の異なる電圧設定を有する。データ入力シーバ回路の出力 2 3 4 は、デュアル入力試験マルチプレクサ 2 3 6（本明細書では「試験 MUX 2 3 6」と呼ぶ）に入力として供給される。試験 MUX 2 3 6 の他方の入力は、T D R / スキャンイン信号 2 3 8 である。試験 MUX 2 3 6 は、試験 MUX 制御論理回路 2 4 0 から出力される試験セレクト信号 2 4 2 によって制御される。試験 MUX 制御論理回路 2 4 0 に対する入力は、スキャンイネーブル信号 2 1 2 、 J T A G 3 状態イネーブル信号 2 2 2 、及び T D R 試験セレクト信号 2 4 4 からなる。なお、図示の論理回路は實際には代表的なものに過ぎず、本発明の一実施形態による論理回路の詳細にとって重要なのは、下記の真理値表を備えていることである。

#### 【 0 0 0 9 】

【表1】

| 論理<br>試験モード        | eTDR<br>試験<br>(244) | JTAG3<br>試験<br>(222) | スキャン<br>イネーブル<br>(212) | TDR試験<br>選択<br>(242) |

|--------------------|---------------------|----------------------|------------------------|----------------------|

| 通常試験モード            | X                   | X                    | 0                      | 0                    |

| 従来の試験モード           | 0                   | X                    | 1                      | 1                    |

| 試験対象<br>I/OパッドのTDR | 1                   | 0                    | 1                      | 0                    |

| 試験対象<br>I/OパッドのTDR | 1                   | 1                    | 1                      | 1                    |

10

20

30

## 【0010】

試験MUXの出力246は、データキャプチャレジスタ248に入力される。データキャプチャレジスタ248は、遅延クロック252に従って動作する。遅延クロック252は、書き込み／読み出しクロック信号210を遅延素子250によって時間遅延させた信号である。好ましい実施形態において、各I/Oパッド104は、書き込み／読み出しクロック210と、データキャプチャレジスタ248に対するクロック入力との間にプログラマブル遅延素子250を有する。他の実施形態では、プログラマブル遅延素子が1つしかなく、その出力を遅延クロックツリー（図示せず）に供給し、共通信号源から個々の遅延クロック信号がI/Oパッドに供給されるようにする場合がある。この共通遅延素子の実施形態では、データ出力レジスタ206とデータキャプチャレジスタ248に供給される独立したクロックツリーが必要である。遅延素子250は、書き込み／読み出しクロック210の1周期よりも小さな増分単位で遅延時間をプログラムすることが出来る。データキャプチャレジスタ248の出力は、TDRスキャンアウト信号254として出力される。

## 【0011】

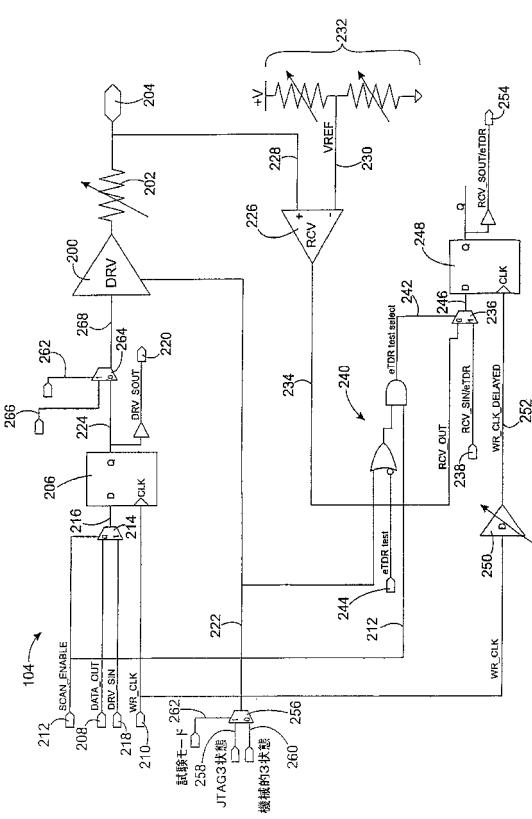

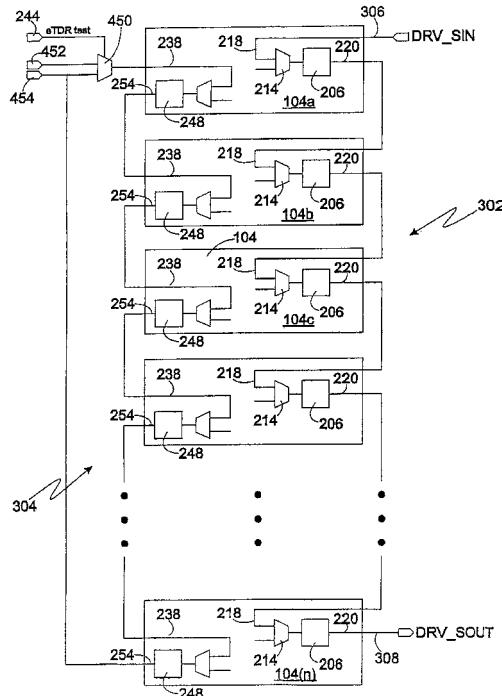

次に、図3及び図4を参照する。図3及び図4は、複数のI/Oパッド104をスキャンチェーンとして接続するための本発明の一実施形態を示す概略図である。図3は従来のドライバスキャンチェーン302を示す図である。このドライバスキャンチェーン302では、複数のI/Oパッドのうちの第1のI/Oパッド104aからのドライバスキャンアウト信号220が、複数のI/Oパッドのうちの第2のI/Oパッド104bのドライバスキャンイン信号218に接続されている。ドライバスキャンチェーン302は、開始点（ドライバスキャンイン信号306）と、終了点（ドライバスキャンアウト信号308）とを有する。図4を参照すると、独立して別個に構成されたレシーバスキャンチェーン304では、第1のI/Oパッド104aのレシーバスキャンアウト/eTDR信号254が、第2のI/Oパッド104bのレシーバスキャンイン/eTDR信号238に接続されている。レシーバスキャンチェーン304が従来のレシーバスキャンチェーンと異なるのは、全てのデータキャプチャレジスタ248をレシーバスキャンイン/eTDR23

40

50

8 ヒレシーバスキャンアウト / e T D R 2 5 4 の両方において相互接続し、レシーバスキャンチェーン 3 0 4 を循環型に構成出来る点にある。具体的には、n 番目の I / O パッド 1 0 4 のレシーバスキャンアウト / e T D R 信号 2 5 4 が、2 対 1 の T D R 循環 M U X 4 5 0 の第 1 の入力に接続され、更に、外部レシーバスキャンアウト接続パッド 4 5 4 にも接続される。T D R 循環 M U X 4 5 0 の第 2 の入力は、従来の外部レシーバスキャンイン信号 4 5 2 である。T D R 循環 M U X 4 5 0 における選択は、T D R 試験信号 2 4 4 によって制御される。T D R 試験信号 2 4 4 がアサートされている場合、T D R 循環 M U X 4 5 0 は n 番目の I / O パッド 1 0 4 ( n ) のレシーバスキャンアウト / e T D R 信号 2 5 4 を選択して出力する。T D R 循環 M U X 4 5 0 の出力は、第 1 の I / O パッド 1 0 4 a のレシーバスキャンイン / e T D R 信号 2 3 8 としてレシーバスキャンチェーン 3 0 4 に 10 入力される。その結果、レシーバスキャンチェーン 3 0 4 の循環構成が完成する。T D R 試験信号 2 4 4 がアサートされていない場合、T D R 循環 M U X 4 5 0 は外部レシーバスキャンイン信号 4 5 2 を選択して出力する。その結果、レシーバスキャンチェーン 3 0 4 は、従来同様に外部スキャンイン信号によって動作することになる。一方、T D R 試験信号 2 4 4 がアサートされている場合、T D R 循環 M U X 4 5 0 はレシーバスキャンアウト / e T D R 信号 2 5 4 を選択して出力する。その結果、レシーバスキャンチェーン 3 0 4 は、本明細書に開示するような e T D R 試験のための再循環モードで動作することになる。

#### 【 0 0 1 2 】

レシーバスキャンチェーン 3 0 4 は、試験の際にマルチビットシフトレジスタとして動作するように構成される。マルチビットシフトレジスタの開始点は、T D R 試験セレクト信号 2 4 2 の値によって決まる。表 1 を参照すると、試験対象の I / O パッドでは、試験 M U X 2 3 6 が T D R 試験セレクト信号 2 4 2 によって制御される。すなわち、試験対象の I / O パッドでは、T D R 試験セレクト信号 2 4 2 により、レシーバデータキャプチャレジスタ 2 4 8 に入力される信号としてレシーバ信号 2 3 4 が、M U X 2 3 6 において選択される。その結果、レシーバスキャンチェーン 3 0 4 が切断される。実際には、これにより、その試験対象の I / O パッドが、循環型のスキャンチェーン構成によって生成されるマルチビットシフトレジスタ中の第 1 ビットとして設定される。T D R 試験の際、試験対象でない I / O パッドでは、試験セレクト信号 2 4 2 により、試験 M U X 2 3 6 の入力として接続されている I / O パッドからのレシーバスキャンアウト信号 2 5 4 が、試験 M U X 2 3 6 において選択される。その結果、レシーバスキャンチェーン 3 0 4 内の試験対象ではない全 I / O パッドについてシフトレジスタ構成が生成される。 20

#### 【 0 0 1 3 】

ドライバスキャンチェーン 3 0 2 内で相互接続されたデータ出力レジスタ 2 0 6 は、T D R 刺激信号を生成するためのデータの記憶に使用される一方、レシーバスキャンチェーン 3 0 4 内で相互接続されたデータキャプチャレジスタ 2 4 8 は、T D R 試験の際にキャプチャされた試験応答データの格納に使用される。T D R 試験を行っていないときは、これらのスキャンチェーン 3 0 2 、 3 0 4 は、従来どおり動作し、従来の目的に使用される。なお、図 3 には図示されていないが、I / O パッド 1 0 4 はその構成の一部に J T A G スキャンチェーンを有する。この J T A G スキャンチェーンは従来どおりのものであり、J T A G 試験の際に I C の設定に使用される。ただし、J T A G スキャンチェーンは本発明の一実施形態においても使用される場合がある。 30

#### 【 0 0 1 4 】

T D R 試験は、 $1 / f_{c1\_o\_ck} = T_{c1\_o\_ck}$  の周期を持つ動作クロック周波数  $f_{c1\_o\_ck}$  で実施され、試験データはレシーバスキャンチェーン 3 0 4 に格納される。従つて、本発明の一実施形態において、レシーバスキャンチェーン 3 0 4 はクロック周波数  $f_{c1\_o\_ck}$  で動作しなければならない。従来、スキャンチェーンは動作クロック周波数未満の周波数で動作している。そのため、本発明の一実施形態によるレシーバスキャンチェーン 3 0 4 は、T D R 試験のタイミング要件を満たす I / O パッドの相互接続が得られるように配慮されている。実施形態によっては、試験刺激データをドライバスキャンチェー 40

10

20

30

40

50

ン302に格納し、そのデータをクロック周波数  $f_{clock}$  でスキャンチェーン全体に流す場合がある。ただし、ドライバスキャンチェーン302を循環構成にする必要は必ずしもなく、ドライバスキャンチェーン302を従来のスキャンチェーンとして構成し、本発明の目的に使用することも可能である。試験遷移信号を生成するドライバスキャンチェーン302の代替には、ドライバスキャンチェーン302を使用しない独立した論理回路、例えばIEEEE規格1149.6「ドライバのバウンダリスキャンレジスタ」に規定されているエッジ生成回路などがある。

#### 【0015】

次に、具体的な処理の流れを理解してもらうために、本発明によるTDR試験プロセスの一実施形態について、その概略を簡単に説明する。I/Oパッド104を1つだけ使用して、そのI/Oパッドに接続された1つの伝送要素（本明細書では「試験対象伝送要素」と呼ぶ）を試験する。1つのレシーバスキャンチェーン304の中には、一度に1つの試験対象伝送要素しか存在しない。試験遷移信号をドライバスキャンチェーン302で生成する実施形態では、試験対象伝送要素に接続されたデータ出力ドライバ回路200が、1つのTDR試験遷移信号を複数回送出するようにプログラムされる。試験対象伝送要素に接続されたデータキャプチャレジスタ248は、その試験におけるレシーバスキャンチェーン304内の第1のデータキャプチャレジスタとなる。TDR試験遷移信号を送出するたびに、試験対象のI/Oパッドのデータキャプチャレジスタ248だけが、様々なクロック遅延及び基準電圧について自身のレシーバ回路226を通じてデータを受信する。一方、レシーバスキャンチェーン304内にある試験対象ではないI/Oパッドのデータキャプチャレジスタ248は全て、レシーバスキャンチェーン304内を通るデータをレシーバスキャンイン/TDR信号238を介して受信する。試験遷移信号の一回の送出により得られる測定値の数は、レシーバスキャンチェーン304内のI/Oパッド104の数によって決まる。最大測定インターバルは、試験遷移信号の一回の送出によって得られるデータ点の数によって定義される。スキャンチェーン304内にN個のI/Oパッド104があり、従ってスキャンチェーン304内にN個のデータキャプチャレジスタ248がある場合、 $N \times T_{clock}$ に等しいインターバルで、データがレシーバスキャンチェーン304の中にキャプチャされる。このレシーバスキャンチェーン304は、オーバーフローしたビットを破棄するシフトレジスタとして動作する。ただし、このシフトレジスタは循環構成で接続されているため、TDR試験の際は、データキャプチャレジスタ248のどのビットをスキャンチェーンシフトレジスタの開始点として定義してもよい。従って、 $2NT_{clock}$ に等しいインターバルだけデータをキャプチャするためには、第1の試験遷移信号の送出に対し、第1の $NT_{clock}$ インターバルだけデータをキャプチャし、キャプチャしたデータを読み出した後、第2の試験遷移信号を送出する際に、その第1の $NT_{clock}$ インターバルに相当する記憶データをシフトアウトさせ、第2の $NT_{clock}$ インターバルだけデータをキャプチャした後、その第2の $NT_{clock}$ インターバルに相当する記憶データを読み出す。試験の実施に使用されるクロックパルスを適当に選択し、その数を調節することで、 $NT_{clock}$ の任意の整数倍の時間だけデータをキャプチャすることが出来る。このようにして試験対象伝送要素において受信された信号は、送出した試験遷移信号に対する反射信号に関する時間と振幅の関係を示すグラフを形成する。なお、本発明の教示は1つの試験遷移信号に関するものになっているが、2つの試験遷移信号を有する試験パルスを用いて伝送要素を試験することも可能である。「試験遷移信号」という用語は、1以上の試験遷移信号を指すものとして一般的意味で使用している。そのため、試験遷移信号は、1つの試験パルスに対応する場合もあれば、2以上の論理遷移を有する試験信号に相当する場合もある。

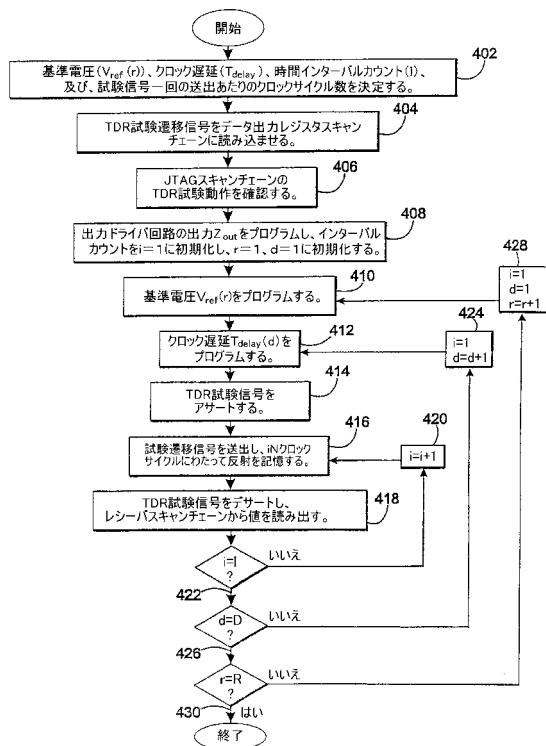

#### 【0016】

次に図5を参照する。図5は、本発明によるTDR試験プロセスの一実施形態を示すフロー図である。まず、準備段階として、試験対象の伝送要素について、基準電圧アレイ  $V_{ref}$ 、遅延時間アレイ  $T_{delay}$ 、及びインターバルカウントI、並びに、1回の試験当たりのクロックサイクル数Nを設定する(402)。次に、ドライバスキャンチェー

10

20

30

40

50

ン302を介して、論理値をデータ出力レジスタ206の中に読み込む(404)。読み込まれる論理値は、試験対象の伝送要素に接続されたI/Oパッド104の外部データ出力204にTDR試験遷移信号を出力するためのものである。実施形態によっては、1つのI/Oパッド104だけでTDR試験を実施する場合もある。好ましい実施形態において、TDR試験遷移信号は、論理「0」から「1」への1クロックサイクルの遷移である。他の試験遷移信号として、「1」から「0」への1クロックサイクルの遷移や、1クロックサイクル経過後に元の論理値に戻る低又は高を基準とするパルス(例えば論理「010」、「101」など)を使用する場合もある。低から高へのTDR試験遷移信号をプログラムする一例として、ドライバスキャンチェーン302が16個の相互接続されたI/Oパッド104を有している場合、2値論理パターン「0111 1111 1111」10をドライバスキャンチェーン302に格納する場合がある。次に、表1を参照し、TDR試験の準備として、値をJTAGスキャンチェーン(図示されてはいない)に読み込ませ(406)、全てのI/Oパッド104を設定する。値を各I/Oパッド104に読み込ませた後(410)、試験対象の伝送要素用のデータ出力ドライバ回路200を除いて、JTAGスキャンチェーン内の全てのデータ出力ドライバ回路200をJTAG高インピーダンス状態にする。単一のデータ出力ドライバ回路200のイネーブル状態にし、TDR試験信号244をアサートすることで、試験遷移信号を送出するためのドライバスキキャンチェーン302が構成される。このTDR試験信号244のアサートにより、レシーバスキキャンチェーン304はキャプチャ及びシフトモードの動作に設定され、TDR試験の際の受信データを格納することが可能になる。次に、TDR試験を実施するI/Oパッド104のデータ出力ドライバ回路200のドライバ出力インピーダンスZ<sub>out</sub>202をプログラム(408)し、内部カウンタ変数iを1に初期化する。TDR試験の間、このドライバ出力インピーダンス202は一定に維持される。次に、最初の電圧基準値V<sub>ref</sub>(1)、最後の電圧基準値V<sub>ref</sub>(R)として、複数の電圧基準値V<sub>ref</sub>(r)を定義する(410)。そして、試験対象の伝送要素に接続されたI/Oパッドのレシーバ回路226の基準電圧232を第1電圧基準値V<sub>ref</sub>(1)に初期化する。次に、最初のクロック遅延値をT<sub>delay</sub>(1)とし、最後のクロック遅延値をT<sub>clock</sub>(D)20として、複数のクロック遅延値T<sub>clock</sub>(d)を定義する。そして、試験対象のI/Oパッドのクロック遅延T<sub>delay</sub>(d)をプログラムする(412)。なお、クロック遅延値や電圧基準値をICにプログラムするためには、いかなる数の従来の方法を使用してもよく、例えば、JTAGプロトコル、従来のスキャンチェーン、又は専用IC構成入力などによってプログラムすることが出来る。ただし、それらに限定はしない。一実施形態では、ドライバスキキャンチェーン302とレシーバスキキャンチェーン304の両方を同一の書き込み/読み出しクロック信号210で制御することから、TDR試験のクロックとして、書き込み/読み出しクロック信号だけしか必要としない場合がある。

### 【0017】

TDR試験の動作を開始するために、TDR試験信号244をアサートする(414)。次に、周波数f<sub>clock</sub>の一連のクロックパルスを生成し、試験を実施する。出力ドライバ回路200から試験遷移信号を送出する(416)。この試験は、クロックが最初にアサートされた時点で開始され、そのクロック周波数で継続される。試験遷移信号は試験対象伝送要素を伝播してゆき、なんらかの終端に到達し、試験遷移信号の送出からしばらく経った後に、試験対象伝送要素の外部接続パッド204に反射が返ってくる。受信される反射は、伝送要素の特性によって決まる。遅延クロック252の各クロックサイクルごとに、外部接続パッド204上の論理値を、試験対象伝送要素に接続されたI/Oパッド104のデータキャプチャレジスタ248に格納する(416)。データキャプチャレジスタ248に以前格納されていた値は、レシーバスキキャンチェーン304を介して、次の隣りのデータキャプチャレジスタ248にシフトされる。こうして、各クロックサイクルごとに1つのデータ点がキャプチャされ、各試験遷移信号の送出ごとに合計N個のデータ点がキャプチャされる。各試験遷移信号の送出の際にキャプチャするインターバルは、4050

$N T_{clock}$  時間単位である。Nクロックサイクルの経過後、クロックを停止し、TDR試験信号244をデアサートする(418)。表1を参照すると、その結果、レシーバスキャンチェーン304は正常なスキャンモードになり、後で分析するために、データキャプチャレジスタ248内の値が読み出され、外部に格納される(418)。データは、レシーバスキャンチェーン304から外部レシーバスキャンアウト接続パッド454を通じて読み出される。このような外部レシーバスキャンアウト接続パッド454は、1個のレシーバスキャンチェーン304当たり1個しか存在しない。従って、このレシーバスキャンチェーン304内の外部レシーバスキャンアウト接続パッド454の配置は、キャプチャ対象データの論理的な開始点からずらすことも出来る。このように、レシーバスキャンチェーン304からデータを取得するシステムでは、レシーバスキャンチェーン304内における外部レシーバスキャンアウト接続パッド454と試験対象のI/Oパッドとの間の位置関係が維持される。レシーバスキャンチェーン304からデータをキャプチャして読み出した後、そのデータは、レシーバスキャンチェーン304内における試験対象I/Oパッドの外部レシーバスキャンアウト接続パッド454に対する位置に応じて再配置される。

10

20

30

40

### 【0018】

試験の際に $1 N T_{clock}$ よりも長いインターバルが必要な場合は、同じ基準電圧 $V_{ref}(r)$ 及びクロック遅延 $T_{delay}(d)$ で、このプロセスをNクロックサイクルの整数倍の回数(最大で $i * N$ 個のクロックサイクルまで)だけ繰り返す(420)。 $I$ 個のインターバルにおいてデータを全てキャプチャしたら(422)、遅延素子250を次の遅延値 $T_{delay}(d+1)$ にプログラムし(424)、インターバルカウント $i$ を1にリセットする。電圧基準 $V_{ref}(r)$ は同じ値に維持する。次に、クロック周期 $T_{clock}$ にわたって、試験遷移信号を送出するステップ416と同じステップを繰り返し、一連の遅延値について遅延値カウント $d$ が遅延値の総数Dに達するまで、 $I$ 個のインターバルのそれぞれにおいて外部接続パッド204における反射値をキャプチャする(426)。次に、一連の電圧基準値 $V_{ref}(r)$ について、それがその最大値 $V_{ref}(R)$ に達するまで、 $N T_{clock}$ の $I$ 個のインターバルにおいて、一連の電圧基準値 $V_{ref}(r)$ について、このTDR送出・キャプチャプロセス全体を繰り返す(428)。その結果、この試験送出・データ格納プロセスはM回繰り返され、P個のデータ点が収集される。ただし、M及びPは、次のとおりである。

30

### 【0019】

$$M = I \times R \times D \quad (1)$$

$$P = M \times N \quad (2)$$

### 【0020】

一実施形態において、基準電圧増分値は、利用可能な電圧基準値範囲全体にわたって均一に設定される。他の実施形態において、基準電圧増分値は、利用可能な電圧基準値範囲を有する任意の電圧値集合として設定される場合がある。同じことが、クロック遅延値についても言える。すなわち、一実施形態において、遅延増分値は均一なインターバルで設定される。他の実施形態において、クロック遅延値はクロック周期にわたって任意のインターバルで設定される。

40

### 【0021】

図5に示すスキャンデータのローディングやアンローディングの動作は、自動試験装置(A TE)によって実施することが出来る。この種の装置は、コンピュータのようなデータ処理装置と、試験対象のデバイスに接続するための適当なコンポーネントを有している。一実施形態において、A TEには、IEEE規格1149.1に規定されている試験対象I CのTAP(Test Access Port)に接続するJTAG系試験システムが使用される。他の実施形態において、A TEは、システム接続を使用してデータアクセスを提供するI Cアーキテクチャ自体の一部であってもよい。

### 【0022】

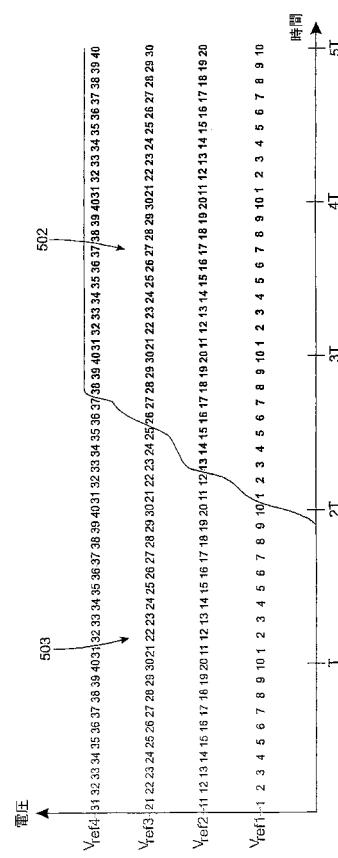

次に、図6を参照する。図6は、本発明によるプロセスによってキャプチャされたデータ

50

タ点のグラフを示している。グラフ中、 $x$  軸は時間を表し ( $t = 0$  は試験遷移信号の送出である)、 $y$  軸は電圧基準値を表している。コンピュータのような外部処理装置は、キャプチャされたデータ点を受信してグラフを形成したり、他の分析装置に渡したりする。式 (1) を参照すると、番号 1 ~ 40 は、 $M = (1)(4)(10) = 40$  であるときの、TDR 試験プロセスの一例における、試験遷移信号送出・データキャプチャの各バスにおいて取得されたデータ点を例として示している。図示の例では、 $I = 1$  であり、単一のインターバル  $T_{c10ck}$  においてのみデータをキャプチャしている。また、 $N = 5$  であり、そのインターバルは 5 つのクロックサイクルから構成されている。従って、図 6 の試験例では、200 個のデータ点をキャプチャしている。グラフ中に太字フォント 502 で示されているデータ点番号は、データキャプチャレジスタにキャプチャされた論理「1」を意味し、グラフ中に通常フォント 503 で示されているデータ点番号は、データキャプチャレジスタにキャプチャされた論理「0」を意味している。このグラフに示した試験では、クロック遅延が  $T_{c10ck} / 10$  のインターバルでプログラムされ、基準電圧が利用可能な基準電圧範囲全体にわたる 4 つの均等なインターバルでプログラムされている。また、 $N = 5$  は、レシーバスキャンチェーン 340 内に 5 つの I/O パッド 104 が存在することを意味する。なお、当業者であれば知っているとおり、レシーバスキャンチェーン 304 は通常、もっと多くの I/O パッドを有している。本明細書では、説明を分かり易くするために、レシーバスキャンチェーンに使用される I/O パッドの数を少なくしている。ただし、規模を変更しても、その動作原理は、基本的なプロセスの変更することなく適用可能である。

### 【0023】

最初の試験遷移信号を送出する前に、プログラマブル遅延を  $T_{delay}(1) = T_{c10ck} / 10$  に設定し、プログラマブル基準電圧を  $V_{ref}(1)$  に設定する。その結果、「書き込み / 読み出しクロック 210」 + 「 $T_{c10ck} / 10$  の遅延 250」の各遷移時に、プログラマブル基準電圧に対する外部接続パッドに存在する論理値が、クロックに従ってデータキャプチャレジスタ 248 に入力される。書き込み / 読み出しクロック 210 が 5 回遷移した後、レシーバスキャンチェーン 304 は満杯になり、レシーバスキャンチェーン 304 に格納された値が読み出される。この例において読み出された 5 つの値は、図 6 のグラフ上のデータ点 1 に相当する。次に、同じ基準電圧  $V_{ref}(1)$  のままで、プログラマブル遅延 250 を  $T_{delay}(2) = 2T_{c10ck} / 10$  (即ち、 $T_{c10ck} / 5$ ) に設定する。そして、第 2 の試験遷移信号を送出し、更に 5 つの値をレシーバスキャンチェーン 304 内にキャプチャした後、それらの値をレシーバスキャンチェーン 304 から読み出す。新たに読み出された 5 つの値は、図 6 のグラフ上のデータ点 2 に相当する。そして、同じプログラマブル基準電圧  $V_{ref}(1)$  を使用して更に 8 つの試験遷移信号を送出し、図 6 のデータ点 3 ~ 10 に相当するような 5 つのデータ点の 8 つの組を更にキャプチャし、それらをレシーバスキャンチェーン 304 から読み出す。なお、図示の例では、10 番目の遅延インターバルにおいて、試験遷移信号が外部接続パッド 204 に出力される遷移よりも後の書き込み / 読み出しクロック 210 の全周期である値が、データキャプチャレジスタに入力されている点に注意して欲しい。具体的には例えば、 $d = D$  のときに新たな電圧基準値  $V_{ref}(2)$  がプログラムされる。次に、プログラマブル遅延  $T_{delay}$  をその初期値である  $T_{c10ck} / 10$  にリセットし、試験遷移信号を更に 10 回送出し、送出した試験遷移信号のそれぞれについて、データキャプチャを実施し、レシーバチェーン 304 の読み出しを実行する。この新たな電圧基準値でキャプチャされたデータは、図 6 のデータ点 11 ~ 20 に相当する。電圧基準値  $V_{ref}(3)$  及び  $V_{ref}(4)$  についても同様にデータをキャプチャすることで、40 個の試験遷移信号の送出及びデータキャプチャに相当する、図 6 に示すような完全なグラフを構成する論理値が得られる。図 6 のグラフに太字フォントで書かれているデータ点は、論理値「1」を有するキャプチャデータ点を示している。一方、図 6 のグラフに通常フォントで書かれているデータ点は、論理値「0」を有するキャプチャデータ点を示している。試験遷移信号は  $t = 0$  の遷移時に出力されることが分かっていて、図 6 に示すキャプチャデ

10

20

30

40

50

ータ値の振幅と時間の関係は反射された試験遷移信号の特性を示しているので、試験対象伝送要素のインピーダンス特性、及び外部接続パッド 204 からの断絶の電気的距離に関する結論が得られる。

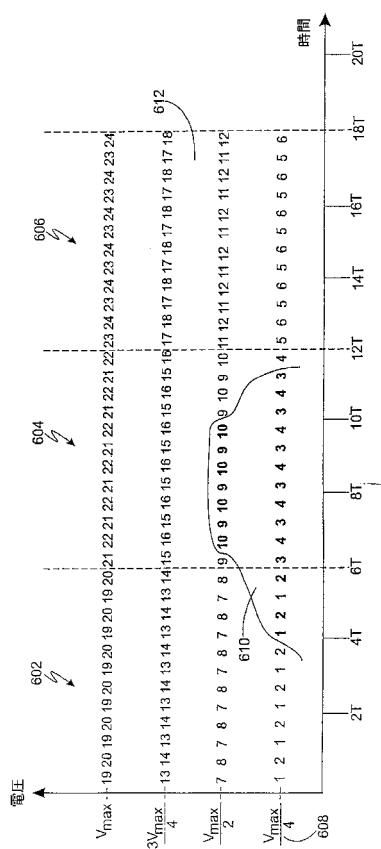

#### 【0024】

次に図 7 を参照する。図 7 は、本発明による試験プロセスの他の実施形態におけるグラフを示している。このグラフは、単一のレシーバスキャンチェーンによって実現可能なインターバルよりも長いインターバルを得るためにプロセスを示している。なお、説明を分かり易くするために、図示の例は実際的な例にはなっていないが、この例に示す特徴は、当業者であれば、本発明の利点を損なうことなくその規模を自由に変更することが可能である。図 7 のグラフは、第 1 (602) の  $NT_{c1 \circ ck}$  インターバル、第 2 の  $NT_{c1 \circ ck}$  インターバル (604)、及び第 3 の  $NT_{c1 \circ ck}$  インターバル (605) を示している。 $N = 6$  は、試験遷移信号を送出するたびに、6 個のデータ点がレシーバスキャンチェーン 304 にキャプチャされることを意味する。説明を簡単にするために、 $T_{c1 \circ ck} / 2$  のクロック遅延をプログラムするものと仮定している。4 つの異なる電圧基準値がある。このグラフは、単一の  $NT_{c1 \circ ck}$  インターバルにおいて得られる時間データよりも多くの時間データを蓄積するための方法を示しており、全部で 3 つの  $NT_{c1 \circ ck}$  インターバルにおいてデータをキャプチャしている。

#### 【0025】

第 1 の電圧基準値 608 において第 1 の試験遷移信号及び第 2 の試験遷移信号を送出することにより、図 7 のグラフに番号「1」及び「2」でそれぞれ示されているデータ点がキャプチャされる。 $N = 6$  の場合、 $6T_{c1 \circ ck}$  の長さの第 1 のキャプチャインターバルにおいて、レシーバスキャンチェーン 304 内には、6 個のデータキャプチャレジスター 248 が存在する。そのため、TDR 試験信号 244 をデアサートし、レシーバスキャンチェーン 304 内に格納されたデータを読み出すまでには、N サイクルの書き込み / 読み出しクロック 210 が発生する。第 2 のキャプチャインターバル 604 においてデータをキャプチャするためには、TDR 試験信号 244 をデアサートするまでに、2N サイクルの書き込み / 読み出しクロック 210 が発生する。第 1 のキャプチャインターバル 602 でキャプチャされたデータは第 2 のキャプチャインターバル 604 においてシフトアウトされ、第 2 のキャプチャインターバル 604 においてキャプチャされた新たなデータを格納することが出来るようになる。従って、第 3 の試験遷移信号及び第 4 の試験遷移信号の送出に対応する番号「3」及び「4」でそれぞれ示されているデータ点は、2N 個のクロックサイクル後に読み出された値である。同様に、第 3 のキャプチャインターバル 606 に示されている第 5 の試験遷移信号及び第 6 試験遷移信号の送出に対応するデータをキャプチャするためには、TDR 試験信号 244 をデアサートするまでに、3N サイクルの書き込み / 読み出しクロック 210 が発生する。図 7 のグラフにおいて、太字フォント 610 でデータ点が示されている領域は論理値「1」に相当するデータ点を示し、通常フォント 612 でデータ点を示している領域は論理値「0」に相当するデータ点を示している。

#### 【0026】

本明細書に開示又は示唆されている試験装置や試験プロセスの種々の実施形態は、説明を目的としたものであり、特許請求の範囲を制限するためのものではない。当業者であれば、本明細書の教示の利点を損なうことなく、本明細書に具体的に記載されていない多数の代替形態を考えつくことも可能であろう。当然ながら、それら多数の代替実施形態も本発明の特許請求の範囲に含まれる。具体的には、本明細書は、伝送要素を試験するための時間領域反射率測定を近似する回路を IC に埋め込み、IC 自体の一部にはしないプロセス及び装置を示している。本明細書は、本発明による IC や試験プロセスの規模を当業者が変更し、プログラマブルクロック遅延値、電圧基準値、インターバル（従って、試験の長さ）、及びスキャンチェーンの長さを有する任意数の異なる試験を実施する方法について説明している。本明細書は、試験刺激が、高又は低を基準とする論理遷移、又は、高又は低を基準とする試験パルスであってよいことも開示している。また、当業者であれば、1 以上の試験パルス及び遷移を用いた更に複雑な試験信号プロファイルによって試験を実

10

20

30

40

50

施することも考え付くであろう。また、実際には、レシーバスキャンチェーン 304 を構成する I/O パッドの数はもっと多く、分解能を高めるために、電圧基準値やクロック遅延値の数も図示の実施形態のものより多いことが多い。また、記憶素子をレシーバスキャンチェーンに更に追加することにより、単にレシーバスキャンチェーンの長さを増加させ、キャプチャ出来的サンプルの数を増やしたり、所与の周波数における試験時間を拡張したり、あるいは比較的高い周波数において所与の数のサンプル点を取得したりすることが可能である。更に、I/O パッド上のサンプルデータをレシーバスキャンチェーン 304 に格納するかわりに、1 以上のシフトレジスタやオンチップランダムアクセスメモリのような TDR スキャンアウト信号 254 を受信する代替データ記憶装置を使用して格納することも可能である。このような代替ローカル記憶装置を使用すれば、複数の伝送要素を並行して試験することが可能になる。ただし、ローカル記憶装置を使用した代替実施形態の場合、I C 上に更に回路領域が必要となる。更に、試験 MUX 236 の出力部 246 に、データキャプチャレジスタ 248 に加えてローカル記憶素子を更に配置し、そのローカル記憶素子を比較的高い別の周波数で動作する第 2 のクロックで動作させることにより、タイミング分解能を向上させることも可能である。この第 2 のクロックの比較的高い周波数は、書き込み / 読み出しクロック周波数の整数倍に設定し、書き込み / 読み出しクロック周波数に同期させることが望ましい（ただし必須ではない）。その結果生成されるデータは刻みの細かいタイミングバーニアとして使用することができ、スキャンチェーンシフト周波数 ( $f_{c10ck}$ ) によって定義される刻みの粗いタイミングインターバルと組み合わせることにより、複合タイミングダイアグラムを作成することが出来る。本明細書では、ドライバスキャンチェーン 302 で試験遷移信号を生成するものとしているが、ドライバスキャンチェーン 302 を使用せずに、代わりに IEEEEE 規格 1149.6 に規定されているドライババウンダリスキャンレジスタ内のエッジ生成回路のような独立した回路によって試験遷移信号を生成することも可能である。試験遷移信号生成用のドライババウンダリスキャンレジスタを実現する回路は図 2 に描かれている。当業者であれば、本発明の利点を損なうことなく、実施形態や変形形態を考えつくことも可能であろう。

10

20

30

40

50

#### 【図面の簡単な説明】

#### 【0027】

【図 1】本発明の一実施形態を含む集積回路を示す図である。

【図 2】本発明による I C 入出力 (I/O) パッドの一実施形態を示す概略図である。

【図 3】本発明による I/O パッド回路間の内部接続の一実施形態を示す図である。

【図 4】本発明による I/O パッド回路間の内部接続の一実施形態を示す図である。

【図 5】本発明による時間領域反射率試験を実施するプロセスを示すフロー図である。

【図 6】本発明による試験の結果得られたデータを示すグラフである。

【図 7】本発明による他の試験の結果得られたデータを示すグラフである。

#### 【符号の説明】

#### 【0028】

100 I C

104 I/O パッド

200 データ出力ドライバ回路

202 出力インピーダンス

206 データ出力レジスタ

210 書き込み / 読み出しクロック

226 データ入力レシーバ回路

232 プログラマブル基準電圧発生器

238 スキャンイン信号

244 TDR 試験信号

248 データキャプチャレジスタ

250 プログラマブル遅延素子

252 遅延クロック

2 5 4 スキャンアウト信号

3 0 4 レシーバスキャンチェーン

4 5 0 T D R 循環 M U X

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

---

フロントページの続き

(72)発明者 デイビッド・エル・リナム

アメリカ合衆国コロラド州80525, フォートコリンズ, サンリーフ・コート・2306

(72)発明者 ジェフェリー・アール・リーリック

アメリカ合衆国コロラド州80526, フォートコリンズ, ネスピット・コート・3206

(72)発明者 ガイ・ハーラン・ハンフリー

アメリカ合衆国コロラド州80525, フォートコリンズ, ロックウッド・ドライブ・キュー83

・3465

F ターム(参考) 2G132 AA20 AC07 AC15 AD15 AG01 AG09 AK07 AL04 AL09