(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4869471号

(P4869471)

(45) 発行日 平成24年2月8日(2012.2.8)

(24) 登録日 平成23年11月25日(2011.11.25)

|              |           |              |         |

|--------------|-----------|--------------|---------|

| (51) Int.Cl. | F 1       |              |         |

| HO 1 L 21/02 | (2006.01) | HO 1 L 27/12 | B       |

| HO 1 L 27/12 | (2006.01) | GO 9 F 9/30  | 3 6 5 Z |

| GO 9 F 9/30  | (2006.01) | HO 1 L 27/08 | 3 3 1 E |

| HO 1 L 27/32 | (2006.01) | HO 1 L 29/78 | 6 2 6 C |

| HO 1 L 27/08 | (2006.01) | HO 1 L 29/78 | 6 2 7 D |

請求項の数 11 (全 32 頁) 最終頁に続く

|           |                              |           |                                                |

|-----------|------------------------------|-----------|------------------------------------------------|

| (21) 出願番号 | 特願2000-216690 (P2000-216690) | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日  | 平成12年7月17日(2000.7.17)        | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号 | 特開2002-33464 (P2002-33464A)  | (72) 発明者  | 高山 徹<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (43) 公開日  | 平成14年1月31日(2002.1.31)        |           |                                                |

| 審査請求日     | 平成19年6月13日(2007.6.13)        | 審査官       | 萩原 周治                                          |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

素子形成基板の一方の面側に、接着層を用いて固定基板を貼り合わせ、

前記素子形成基板の他方の面側に、発光素子を形成し、

レーザー光の照射により前記接着層の一部又は全部を気化させて、前記固定基板を分離

することを特徴とする半導体装置の作製方法。

## 【請求項 2】

請求項1において、

前記接着層は、有色の有機物であることを特徴とする半導体装置の作製方法。

## 【請求項 3】

請求項1において、

前記接着層は、黒色の有機物であることを特徴とする半導体装置の作製方法。

## 【請求項 4】

素子形成基板の一方の面側に、水素を含有するダイヤモンド状炭素膜を形成し、

前記ダイヤモンド状炭素膜に、接着層を用いて固定基板を貼り合わせ、

前記素子形成基板の他方の面側に、発光素子を形成し、

レーザー光の照射により前記ダイヤモンド状炭素膜に含有された前記水素を気化させて

、前記固定基板を分離することを特徴とする半導体装置の作製方法。

## 【請求項 5】

請求項1乃至請求項4のいずれか一項において、

10

20

前記固定基板は、透光性の基板であり、

前記レーザー光は、前記固定基板を通過して照射されることを特徴とする半導体装置の作製方法。

【請求項 6】

素子形成基板の一方の面側に、第1接着層を用いて第1固定基板を貼り合わせ、

前記素子形成基板の他方の面側に、発光素子を形成し、

前記素子形成基板の他方の面側に、第2接着層を用いて第2固定基板を貼り合わせ、

前記第2固定基板を貼り合わせた後、前記レーザー光の照射を行うことにより前記第1接着層の一部又は全部を気化させて、前記第1固定基板を分離することを特徴とする半導体装置の作製方法。

10

【請求項 7】

請求項1乃至請求項6のいずれか一項において、

前記素子形成基板は、有機樹脂からなる基板または遮光性を有する基板であることを特徴とする半導体装置の作製方法。

【請求項 8】

請求項1乃至請求項7のいずれか一項において、

前記レーザー光は、エキシマレーザー光、YAGレーザー光、又はYVO<sub>4</sub>レーザー光であることを特徴とする半導体装置の作製方法。

【請求項 9】

請求項1乃至請求項7のいずれか一項において、

前記レーザー光は、YAGレーザー光の基本波、第2高調波、または第3高調波のいずれかを用いたレーザー光であることを特徴とする半導体装置の作製方法。

20

【請求項 10】

請求項1乃至請求項9のいずれか一項において、

前記素子形成基板の他方の面側に絶縁膜を形成した後に、前記発光素子を形成することを特徴とする半導体装置の作製方法。

【請求項 11】

請求項1乃至請求項10のいずれか一項に記載された半導体装置とは、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、カーナビゲーション、パソコンコンピュータ、又は携帯情報端末であることを特徴とする半導体装置の作製方法。

30

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本願発明は、電極間に発光性材料を挟んだ素子（以下、発光素子という）を有する装置（以下、発光装置という）の作製方法に関する。特に、EL（Electro Luminescence）が得られる発光性材料（以下、EL材料という）を用いた発光装置、即ちEL表示パネルに代表される電気光学装置およびその様な電気光学装置を部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

40

【0003】

【従来の技術】

近年、発光性材料のEL現象を利用した発光素子（以下、EL素子という）を用いた発光装置（以下、EL表示装置という）の開発が進んでいる。EL表示装置は、陽極と陰極との間にEL材料を挟んだ構造のEL素子を有した構造からなる。この陽極と陰極との間に電圧を加えてEL材料中に電流を流すことによりキャリアを再結合させて発光させる。即ち、EL表示装置は発光素子自体に発光能力があるため、液晶表示装置に用いるようなバックライトが不要である。さらに視野角が広く、軽量であり、且つ、低消費電力という利点をもつ。

50

**【0004】**

このようなEL表示装置を利用したアプリケーションは様々なものが期待されているが、特にEL表示装置の厚みが薄いこと、従って軽量化が可能であることにより携帯機器への利用が注目されている。そのため、フレキシブルなプラスチックフィルムの上に発光素子を形成することが試みられている。

**【0005】**

しかしながら、プラスチックフィルムの耐熱性が低いためプロセスの最高温度を低くせざるを得ず、結果的にガラス基板上に形成する時ほど良好な電気特性のTFTを形成できないのが現状である。そのため、プラスチックフィルムを用いた高性能な発光装置は実現されていない。

10

**【0006】**

また、特開平8-288522号公報では、ガラス基板上に薄膜トランジスタを形成し、封止層を介して樹脂基板を接着した後、ガラス基板を剥離する技術が記載されている。この技術を用いた場合、TFTの活性層が下地絶縁膜で保護されるのみとなっており、TFTが劣化しやすいという問題が生じていた。

**【0007】**

また、特開平11-243209号公報では、分離層を設け、レーザー光によって分離層において剥離を生じせしめた後、接着層を介して一次転写体に接合し、さらに接着層を介して二次転写体を接合した後、一次転写体を除去する技術が記載されている。この技術を用いた場合においても、TFTの活性層が下地絶縁膜のみで保護される状態が作製工程中に存在するため、傷つきやすくなっている、TFTが劣化しやすいという問題が生じていた。

20

**【0008】****【発明が解決しようとする課題】**

本願発明はプラスチック支持体（可撓性のプラスチックフィルムもしくはプラスチック基板を含む。）を用いて高性能な電気光学装置を作製するための技術を提供することを課題とする。

**【0009】****【課題を解決するための手段】**

本願発明は、プラスチックに比べて耐熱性のある第1固定基板の上にプラスチック支持体からなる素子形成基板を第1接着層で接着した後、該素子形成基板上に必要な素子を形成した後に第1固定基板を分離することを特徴とする。

30

**【0010】**

また、第1固定基板の上に素子形成基板を第1接着層で貼り合わせた後、該素子形成基板上に必要な素子を形成し、該素子上に第2固定基板を第2接着層で貼り合わせた後に第1固定基板を分離してもよい。第2固定基板及び第2接着層を設けることによって、必要な素子を保護するとともに外部からの水分や酸素等のEL層の酸化による劣化を促す物質が侵入することを防ぐことができる。

**【0011】**

なお、前記必要な素子とは、アクティブマトリクス型の電気光学装置ならば画素のスイッチング素子として用いる半導体素子（典型的にはTFT）もしくはMIM素子並びに発光素子を指す。また、パッシブ型の電気光学装置ならば発光素子を指す。

40

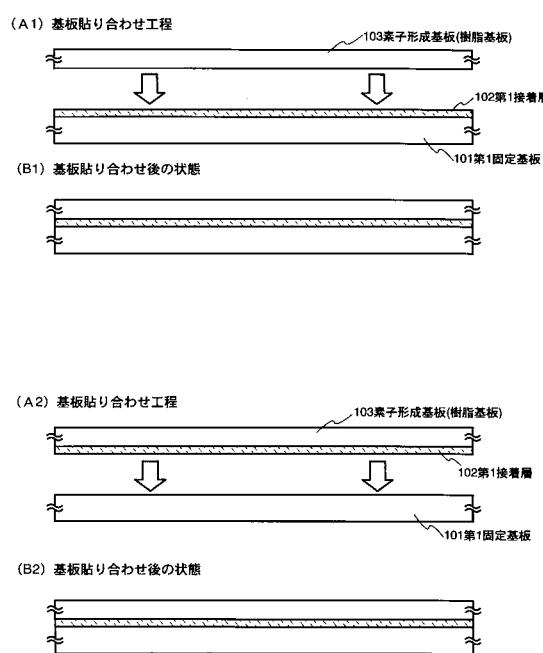

**【0012】**

また、第1固定基板と素子形成基板との貼り合わせ方法は、特に限定されないが、図1に示したように、第1固定基板に第1接着層を形成した後で素子形成基板を貼り合わせる方法、あるいは素子形成基板に第1接着層を形成した後で第1固定基板を貼り合わせる方法を用いればよい。

**【0013】**

また、プラスチック支持体からなる素子形成基板及び第2固定基板としては厚さ10μm以上の樹脂基板、例えばPES（ポリエチレンサルファイル）、PC（ポリカーボネート

50

)、P E T (ポリエチレンテレフタレート)もしくはP E N (ポリエチレンナフタレート)を用いることができる。なお、第1の固定基板上に接着層を形成した後、その上に有機樹脂層(ポリイミド層、ポリアミド層、ポリイミドアミド層B C B (ベンゾシクロブテン)層等)を成膜したものを素子形成基板と呼んでもよい。

【0014】

また、素子形成基板としては、金属基板、例えばステンレス基板を用いることもできる。その場合は金属基板上に下地絶縁膜を形成して必要な素子を形成すればよい。薄い金属基板(厚さ10~200μm)を用いることによって軽量化、薄型化が図れるとともに可撓性を有する発光装置を得ることできる。

【0015】

また、第1固定基板を分離するのは、素子形成基板上に必要な素子を形成した後に行うが、その代表的な手段としてレーザー光の照射により第1接着層の全部または一部を気化させる方法を用いる。また、レーザー光の照射に代えて、例えば、特開平8-288522号公報に記載されたエッティングで第1固定基板を分離する方法や、第1接着層に対して流体(圧力が加えられた液体もしくは気体)を噴射することにより第1固定基板を分離する方法(代表的にはウォータージェット法)を用いてもよいし、これらを組み合わせて用いてもよい。

【0016】

レーザー光としては、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いることができる。図3(D)に示すようにレーザー光を裏面側から第1固定基板を通過させて第1接着層を照射して第1接着層のみを気化させて第1固定基板を分離もしくは剥離する。従って、第1固定基板としては少なくとも照射するレーザー光が通過する基板、代表的には透光性を有する基板、例えばガラス基板、石英基板等を用い、さらに素子形成基板よりも厚さの厚いものが好ましい。

【0017】

本発明においては、レーザー光が第1固定基板を通過させるため、レーザー光の種類と第1固定基板を適宜選択する必要がある。例えば、第1固定基板として石英基板を用いるのであれば、YAGレーザー(基本波(1064nm)、第2高調波(532nm)、第3高調波(355nm)、第4高調波(266nm)あるいはエキシマレーザー(波長308nm)を用い、線状ビームを形成し、石英基板を通過させればよい。なお、エキシマレーザーはガラス基板を通過しない。従って、第1固定基板としてガラス基板を用いるのであればYAGレーザーの基本波、第2高調波、または第3高調波を用い、好ましくは第2高調波(波長532nm)を用いて線状ビームを形成し、ガラス基板を通過させればよい。

【0018】

また、第1接着層としては有機物を用い、好ましくは照射するレーザー光で全部または一部が気化するものを用いる。また、効率よく第1接着層のみにレーザー光を吸収するために、第1接着層がレーザー光を吸収する特性を有するもの、例えば、YAGレーザーの第2高調波を用いる場合、有色、あるいは黒色(例えば、黒色着色剤を含む樹脂材料)のものを用いることが望ましい。ただし、第1接着層は素子形成工程における熱処理によって気化しないものを用いる。また、第1接着層は単層であっても積層であってもよく、図2に示したように第1接着層と素子形成基板の間にアモルファスシリコン膜またはDLC膜を設ける構成としてもよい。

【0019】

このような構成とすることによって、素子形成基板の厚さが非常に薄い、具体的には50μm~300μm、好ましくは150μm~200μmの厚さの基板を用いても、信頼性の高い発光装置を得ることができる。また、従来ある公知の製造装置を用いて、このように厚さの薄い基板上に素子形成を行うことは困難であったが、本発明は第1固定基板に貼り合わせて素子形成を行うため、装置の改造を行うことなく厚さの厚い基板を用いた製造装置を使用することができる。また、素子形成工程中において、素子形成基板を素子形成

基板上に形成される絶縁膜と、第1固定基板とで挟まれた状態とすることで素子形成基板の耐熱性を向上させることができる。

【0020】

本明細書で開示する発明の構成は、

第1固定基板と素子形成基板とを該素子形成基板に設けられた第1接着層で貼り合わせ、該素子形成基板を貼り合わせた後に絶縁膜を形成し、該絶縁膜の上に発光素子を形成し、該発光素子の上に第2接着層で第2固定基板を貼り合わせた後、レーザー光の照射により前記第1接着層を除去して前記第1固定基板を分離することを特徴とする半導体装置の作製方法である。

【0021】

10

また、他の発明の構成は、

第1固定基板と素子形成基板とを前記固定基板に設けられた第1接着層で貼り合わせ、該素子形成基板を貼り合わせた後に絶縁膜を形成し、該絶縁膜の上に発光素子を形成し、該発光素子の上に第2接着層で第2固定基板を貼り合わせた後、レーザー光の照射により前記第1接着層を除去して前記第1固定基板を分離することを特徴とする半導体装置の作製方法である。

【0022】

上記各構成において、前記素子形成基板及び前記第2固定基板は有機樹脂からなる支持体（可撓性のプラスチックフィルムもしくはプラスチック基板を含む）であることを特徴としている。また、前記素子形成基板及び前記第2固定基板としては、第1固定基板と比べて厚さの薄いものを用いる。

20

【0023】

また、上記各構成において、前記素子形成基板と第1接着層の間には、非晶質シリコン薄膜を形成してもよい。また、前記素子形成基板と第1接着層の間には、ダイヤモンド状炭素薄膜を形成してもよい。

【0024】

また、上記各構成において、前記第1接着層は、顔料や染料を用いて有色または黒色としてレーザー光を吸収するようにしてもよい。

【0025】

30

また、上記各構成において、前記レーザー光の照射は、線状ビームを形成して走査させて照射することを特徴としており、前記レーザー光は、パルス発振型または連続発光型のエキシマレーザーや、YAGレーザーや、YVO<sub>4</sub>レーザーを用いることができる。

【0026】

また、上記各構成において、前記レーザー光の照射は、前記第1固定基板の裏面側から前記第1固定基板を通過させて、前記第1固定基板の表面側に設けられた前記第1接着層に前記レーザー光を照射することを特徴としている。従って、前記第1固定基板は、使用するレーザー光を透過することが好ましい。

【0027】

【発明の実施の形態】

本願発明の実施形態について、以下に説明する。

40

【0028】

まず、第1固定基板101と素子形成基板103とを貼り合わせるが、図1に示したように2通りの貼り合わせ方法がある。

【0029】

一つ目の方法は、第1固定基板101上に第1接着層102を設けた後、第1固定基板101と素子形成基板103とを貼り合わせる方法である。（図1（A1））なお、貼り合わせ後の状態を図1（B1）に示した。

【0030】

また、二つ目の方法は、素子形成基板103に第1接着層102を設けた後、第1固定基板101と素子形成基板103とを貼り合わせる方法である。（図1（A2））なお、貼

50

り合わせ後の状態を図1(B2)に示した。

【0031】

また、ここでは図示しないが、第1固定基板上に第1接着層を形成した後、その上に有機樹脂層(ポリイミド層、ポリアミド層、ポリイミドアミド層等)を成膜したものを素子形成基板と同等なものとしてもよい。

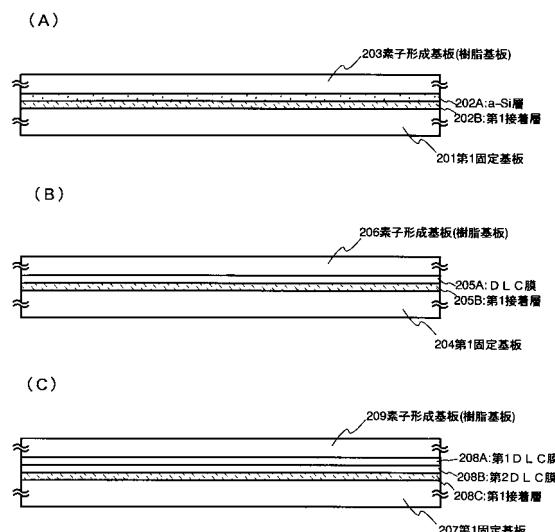

【0032】

また、図2(A)に示したように、第1接着層202Bと素子形成基板203の間にaSi(アモルファスシリコン)層202Aを設ける構成としてもよい。後の工程で、このaSi層にレーザー光を照射することにより第1固定基板201を剥離させてもよい。第1固定基板201が分離または剥離しやすいようにするため水素を多く含むaSi層を用いることが好ましい。レーザー光を照射することによりaSi層に含まれる水素を気化させて第1固定基板を分離または剥離する。

10

【0033】

また、図2(B)に示したように、第1接着層205Bと素子形成基板206の間に、素子形成基板206を保護するためのDLC膜(具体的にはダイヤモンドライカーボン膜)を設けてもよい。なお、第1固定基板204は、図1中に示した第1固定基板101と同一である。

【0034】

この場合、素子形成基板の片面もしくは両面に保護膜としてDLC膜を膜厚2~50nmでコーティングしたものを用いてもよい。なお、DLC膜の成膜はスパッタ法もしくはECRプラズマCVD法を用いればよい。DLC膜の特徴としては、1550cm<sup>-1</sup>くらいに非対称のピークを有し、1300cm<sup>-1</sup>くらいに肩をもつラマンスペクトル分布を有する。また、微小硬度計で測定した時に15~25GPaの硬度を示すという特徴をもつ。このような炭素膜は、酸素および水の侵入を防ぐとともに樹脂基板の表面を保護する役割を持つ。こうして、外部からの水分や酸素等のEL層の酸化による劣化を促す物質が侵入することを防ぐことができる。従って、信頼性の高いEL発光装置が得られる。

20

【0035】

また、図2(C)に示したように、第1接着層208Cと素子形成基板209の間に、素子形成基板を保護するための第1DLC膜208Aと、第1固定基板207が分離または剥離しやすいようにするための第2DLC膜208Bを設けてもよい。このような第1DLC膜208Aとしては水素を含まない成膜条件で成膜したものを用い、第2DLC膜208Bとしては水素を含む成膜条件で成膜したものを用いればよい。また、第2DLC膜208Bにレーザー光を照射することにより膜中に含まれる水素を気化させて第1固定基板207を分離または剥離させてもよい。

30

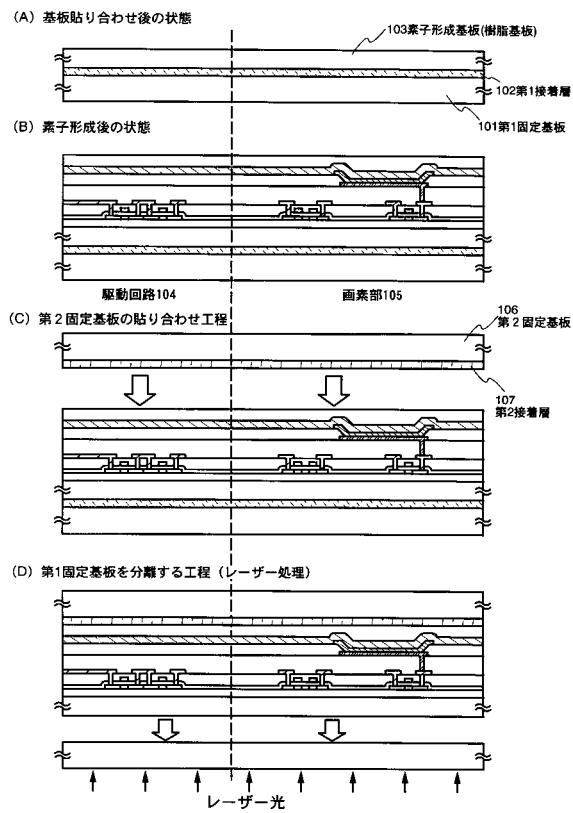

【0036】

上記各方法によって得られる貼り合わせ後の状態を図3(A)に示した。ここでは、図1(B1)及び図1(B2)と同一のものを例示する。なお、符号は図1(B1)及び図1(B2)と同じ符号を用いた。

【0037】

次いで、素子形成基板103上に下地絶縁膜を形成した後、その下地絶縁膜上に必要な素子を形成する。ここでは、駆動回路104とEL素子を有する画素部105を形成した例を示す。(図3(B))

40

【0038】

次いで、第2固定基板106を第2接着層107で貼り合わせる。(図3(C))なお、ここではEL素子を外部からの水分や酸素等の侵入から保護するために第2固定基板106を用いたが、特に必要がなければ用いなくともよい。第2固定基板106としては、樹脂基板を用いればよく、片面もしくは両面に保護膜としてDLC膜を設けたものを用いてもよい。

【0039】

次いで、裏面側からレーザー光を照射して第1接着層102の全部または一部を気化させ

50

て第1固定基板101を分離する。（図3（D））従って、第1接着層102はレーザー光によって層内または界面において剥離現象が生じる物質を用いる。また、レーザー光は第1固定基板101を通過して第1接着層で吸収するものを適宜選択する。例えば、第1固定基板として石英基板を用いるのであれば、YAGレーザー（基本波（1064nm）、第2高調波（532nm）、第3高調波（355nm）、第4高調波（266nm）あるいはエキシマレーザー（波長308nm）を用い、線状ビームを形成し、石英基板を通過させればよい。なお、エキシマレーザーはガラス基板を通過しない。従って、第1固定基板としてガラス基板を用いるのであればYAGレーザーの基本波、第2高調波、第3高調波を用いることができ、好ましくは第2高調波（波長532nm）を用いて線状ビームを形成し、ガラス基板を通過させればよい。

10

#### 【0040】

そして、最終的には、樹脂基板である素子形成基板と樹脂基板である第2固定基板とで挟まれた発光装置が完成する。

#### 【0041】

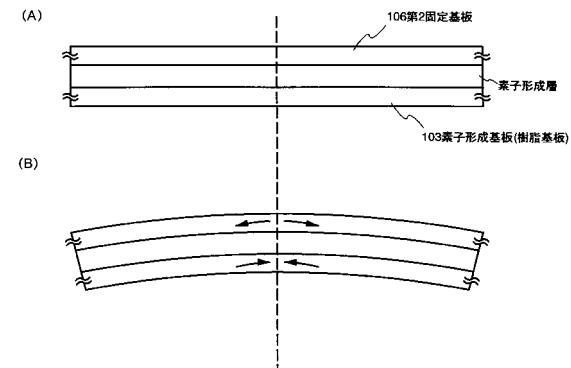

また、図23に示したように、樹脂基板である素子形成基板103と樹脂基板である第2固定基板106とで素子形成層（EL素子含む）を挟んだ発光装置は、多少の応力が発生しても破損しない柔軟性（フレキシビリティ）を有している。図23（A）は曲率を与えていないときの状態を示し、図23（B）は曲率を与えたときの状態を示す。図23（B）において、素子形成基板には圧縮応力が働き、第2固定基板には引張応力が働くが、素子形成層においては、応力がほとんど働かず、中央部における伸び縮みを±1μm以下とすることができる。なお、曲率半径が10cmまでの曲率を与えて問題ない。

20

#### 【0042】

以上の構成でなる本願発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

#### 【0043】

##### 【実施例】

###### 【実施例1】

本実施例は、樹脂基板である素子形成基板と樹脂基板である第2固定基板とで挟まれた発光装置の作製方法の一例を図3を用いて示す。なお、ここでは、全ての工程を350以下、好ましくは200以下で行うこととする。ただし、本発明が本実施例に限定されないことはいうまでもない。

30

###### 【0044】

まず、第1固定基板101としてガラス基板を用いる。そして、実施の形態に示したいずれかの方法を用いて、第1固定基板101と樹脂基板である素子形成基板103とを第1接着層102で貼り合わせた。（図3（A））

###### 【0045】

次いで、素子形成基板103上に下地絶縁膜を形成した後、その下地絶縁膜上に必要な素子を形成する。ここでは、駆動回路104とEL素子を有する画素部105を形成した例を示す。（図3（B））

###### 【0046】

下地絶縁膜としては、低温で成膜が可能なスパッタ法を用いて、膜組成において酸素元素より窒素元素を多く含む酸化窒化シリコン膜と、膜組成において窒素元素より酸素元素を多く含む酸化窒化シリコン膜を積層形成した。

40

###### 【0047】

次いで、下地絶縁膜上に半導体層を形成する。半導体層の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム（ $\text{Si}_x\text{Ge}_{1-x}$ （ $0 < x < 1$ ））合金などで形成すると良い。本実施例では、低温で成膜が可能なスパッタ法を用いて非晶質シリコン膜を形成し、レーザー結晶化法により結晶質シリコン膜を形成した。レーザー結晶化法で結晶質半導体膜を作製する場合には、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いることができる。

50

## 【0048】

次いで、半導体層を覆うゲート絶縁膜を形成する。本実施例では、低温で成膜が可能なスパッタ法を用いて酸化シリコン膜を形成した。

## 【0049】

次いで、ゲート絶縁膜上に導電層を形成する。導電層は、導電膜を公知の手段（熱CVD法、プラズマCVD法、減圧熱CVD法、蒸着法、またはスパッタ法等）により成膜した後、マスクを用いて所望の形状にパターニングして形成する。

## 【0050】

次いで、イオン注入法またはイオンドーピング法を用い、半導体層にn型を付与する不純物元素またはp型を付与する不純物元素を適宜、添加してLDD領域やソース領域やドレイン領域を形成する不純物領域を形成する。

10

## 【0051】

その後、スパッタ法により作製される窒化シリコン膜、窒化酸化シリコン膜、または酸化シリコン膜により層間絶縁膜を形成する。また、添加された不純物元素は活性化処理を行う。ここでは、レーザー光の照射を行った。レーザー光の照射に代えて、350以下での加熱処理で活性化を行ってもよい。

## 【0052】

次いで、公知の技術を用いてソース領域またはドレイン領域に達するコンタクトホールを形成した後、ソース電極またはドレイン電極を形成しTFTを得る。

20

## 【0053】

次いで、公知の技術を用いて水素化処理を行い、全体を水素化してnチャネル型TFTまたはpチャネル型TFTが完成する。本実施例では比較的低温で行うことが可能な水素プラズマを用いて水素化処理を行った。

## 【0054】

次いで、スパッタ法により作製される窒化シリコン膜、窒化酸化シリコン膜、または酸化シリコン膜により層間絶縁膜を形成する。次いで、公知の技術を用いて画素部のドレイン電極に達するコンタクトホールを形成した後、画素電極を形成する。次いで、画素電極の両端にパンクを形成し、画素電極上にEL層およびEL素子の陽極（あるいは陰極）を形成する。

## 【0055】

30

次いで、画素部及び駆動回路に含まれる素子は全て絶縁膜で覆う。

## 【0056】

次いで、素子形成基板に形成された素子を全て覆う絶縁膜と第2固定基板106とを第2接着層107で貼り合わせる。（図3（C））なお、ここではEL素子を外部からの水分や酸素等の侵入から保護するために第2固定基板106を用いたが、特に必要がなければ用いなくともよい。第2固定基板106としては、樹脂基板を用いればよく、片面もしくは両面に保護膜として DLC膜を設けたものを用いてもよい。

## 【0057】

次いで、裏面側からレーザー光を照射して第1接着層102の全部または一部を気化させて第1固定基板101を分離する。（図3（D））本実施例では、第1固定基板としてガラス基板を用いるため、YAGレーザーの基本波、第2高調波、第3高調波を用いる。ここでは第2高調波（波長532nm）を用いて線状ビームを形成し、第1固定基板101であるガラス基板を通過させて第1接着層を照射した。

40

## 【0058】

そして、最終的には、樹脂基板である素子形成基板と樹脂基板である第2固定基板とで挟まれた発光装置が完成した。スパッタ法を用いて各膜（絶縁膜、半導体膜、導電膜等）を形成し、全てのプロセスを350以下、好ましくは200以下で行うことができる。

## 【0059】

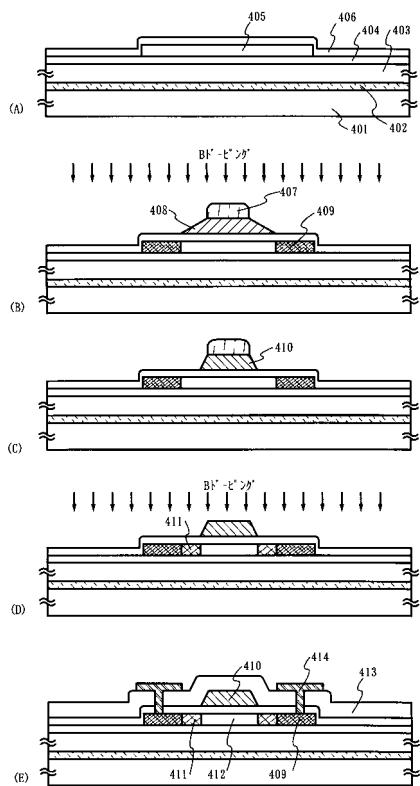

## [実施例2]

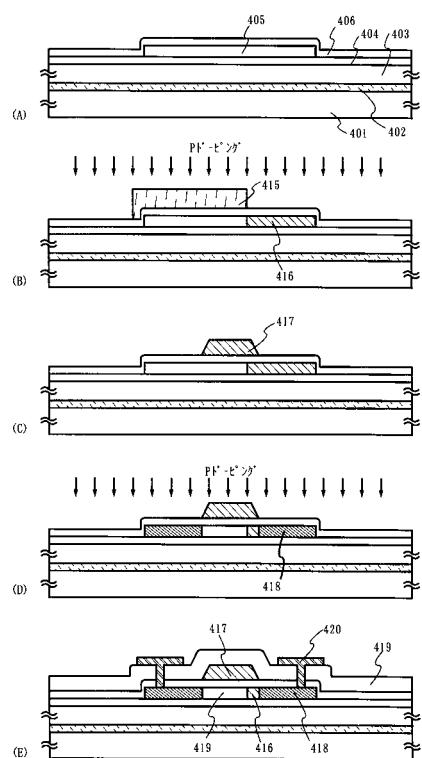

本実施例は、pチャネル型TFTを作製する例であり、図4を用いて説明する。

50

## 【0060】

まず、第1固定基板401と第1接着層402（分離層）で貼りつけた素子形成基板403上に下地絶縁膜404を形成する。下地絶縁膜404としては、酸化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜（Si<sub>OX</sub>N<sub>Y</sub>）、またはこれらの積層膜等を100～500nmの膜厚範囲で用いることができ、形成手段としては熱CVD法、プラズマCVD法、蒸着法、スパッタ法、減圧熱CVD法等の形成方法を用いることができる。

## 【0061】

本実施例では、低温で成膜が可能なスパッタ法を用いて、膜組成において酸素元素より窒素元素を多く含む酸化窒化シリコン膜と、膜組成において窒素元素より酸素元素を多く含む酸化窒化シリコン膜を積層形成した。

10

## 【0062】

なお、第1固定基板401と第1接着層402（分離層）で貼りつけた素子形成基板403は上記実施形態で示した方法により作製されるいすれのものも適用可能である。

## 【0063】

次いで、下地絶縁膜上に半導体層405を形成する。半導体層405は、非晶質構造を有する半導体膜を公知の手段（熱CVD法、プラズマCVD法、減圧熱CVD法、蒸着法、またはスパッタ法等）により成膜した後、公知の結晶化処理（レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等）を行って得られた結晶質半導体膜を所望の形状にパターニングして形成する。この半導体層405の厚さは20～100nm（好ましくは30～60nm）の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム（Si<sub>X</sub>Ge<sub>1-X</sub>（0 < X < 1））合金などで形成すると良い。本実施例では、低温で成膜が可能なスパッタ法を用いて非晶質シリコン膜を形成し、レーザー結晶化法により結晶質シリコン膜を形成した。レーザー結晶化法で結晶質半導体膜を作製する場合には、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いることができる。

20

## 【0064】

また、半導体層405を形成した後、TFTのしきい値を制御するために微量な不純物元素（ボロンまたはリン）のドーピングを行ってもよい。

## 【0065】

次いで、半導体層405を覆うゲート絶縁膜406を形成する。ゲート絶縁膜406はプラズマCVD法またはスパッタ法を用い、厚さを40～150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、低温で成膜が可能なスパッタ法を用いて酸化シリコン膜を形成した。（図4（A））

30

## 【0066】

次いで、ゲート絶縁膜406上に導電層408を形成する。導電層408は、導電膜を公知の手段（熱CVD法、プラズマCVD法、減圧熱CVD法、蒸着法、またはスパッタ法等）により成膜した後、マスク407を用いて所望の形状にパターニングして形成する。導電層408の材料としては、Ta、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いてもよい。また、AgPdCu合金を用いてもよい。本実施例では、低温で成膜が可能なスパッタ法を用いてW膜を成膜し、パターニングした。導電層408の端部はテーパー状に形成する。エッチング条件は適宜決定すれば良いが、例えば、Wの場合にはCF<sub>4</sub>とCl<sub>2</sub>の混合ガスを用い、基板を負にバイアスすることにより良好にエッチングすることができる。

40

## 【0067】

次いで、図4（B）に示すように、自己整合的にソース及びドレイン領域を形成する不純物領域（p+領域）409を形成する。この不純物領域（p+領域）409はイオンドープ法により形成し、ボロンに代表される周期律表第13族の元素をドーピングする。不純物領域（p+領域）409の不純物濃度は、1×10<sup>20</sup>～2×10<sup>21</sup>/cm<sup>3</sup>の範囲とな

50

るようとする。

【0068】

次に、図4(C)に示すように導電層408の端部が後退するようにエッチングして導電層410を形成する。本実施例の構造ではこれをゲート電極とする。ゲート電極の形成には2回のエッチング工程を用いるが、そのエッチング条件は適宜決定されるものである。例えば、Wの場合にはCF<sub>4</sub>とCl<sub>2</sub>の混合ガスを用い、基板を負にバイアスすることにより良好に端部がテーパー形状に加工することができる。また、CF<sub>4</sub>とCl<sub>2</sub>に酸素を混合させることにより、下地と選択性良く、Wの異方性エッチングエッチングをすることができます。

【0069】

その後、図4(D)に示すように、導電層410をマスクとしてp型の不純物(アクセプタ)をドーピングし、自己整合的に不純物領域(p-領域)411を形成する。不純物領域(p-領域)411の不純物濃度は、 $1 \times 10^{17} \sim 2 \times 10^{19} / \text{cm}^3$ の範囲となるようとする。

【0070】

その後、スパッタ法またはプラズマCVD法により作製される窒化シリコン膜、窒化酸化シリコン膜により層間絶縁膜413を形成する。また、添加された不純物元素は活性化のために350～500の加熱処理またはレーザー光の照射を行う。さらに、公知の技術を用いて不純物領域(p+領域)に達するコンタクトホールを形成した後、ソース電極またはドレイン電極414を形成しTFTを得る。

【0071】

最後に公知の技術を用いて水素化処理を行い、全体を水素化してpチャネル型TFTが完成する。(図4(E))

【0072】

半導体層にはチャネル形成領域412、不純物領域(p-領域)で形成されるLDD(Lightly Doped Drain)領域411、不純物領域(p+領域)で形成されるソースまたはドレイン領域409が形成されている。ここでは、pチャネル型TFTをLDD構造で示したが、勿論シングルドレインや、或いはLDDがゲート電極とオーバーラップした構造で作製することもできる。本実施例で示すpチャネル型TFTを用いて基本論理回路を構成したり、さらに複雑なロジック回路(信号分割回路、D/Aコンバータ、オペアンプ、補正回路など)をも構成することができ、さらにはメモリやマイクロプロセッサをも形成しうる。例えば、EL表示装置の駆動回路を全てpチャネル型TFTで構成することも可能である。

【0073】

また、本実施例は実施例1と組み合わせることが可能である。

【0074】

[実施例3]

本実施例は、nチャネル型TFTを作製する例であり、図5を用いて説明する。なお、図4(A)と図5(A)は同一であるため、同じ符号を用い、ここでは作製工程の説明を省略する。

【0075】

実施例2に従って図5(A)の状態を得た後、光露光プロセスによりレジストによるマスク415を形成し、半導体膜405にイオン注入またはイオンドープ法によりn型の不純物(ドナー)をドーピングする。(図5(B))作製される不純物領域(n-領域)416において、ドーピングされる濃度は $1 \times 10^{17} \sim 2 \times 10^{19} / \text{cm}^3$ の範囲となるようする。

【0076】

次いで、絶縁膜406上には、タンタル、タングステン、チタン、アルミニウム、モリブデンから選ばれた一種または複数種の元素を成分とする導電性材料でゲート電極417を形成する。(図5(C))ゲート電極417の一部は不純物領域(n-領域)416とゲ

10

20

30

40

50

ート絶縁膜を介して一部が重なるように形成する。

【0077】

その後、図5(D)に示すように、ゲート電極417をマスクとしてn型の不純物(ドナー)をドーピングし、自己整合的に不純物領域(n+領域)418を形成する。不純物領域(n+領域)418の不純物濃度は、 $1 \times 10^{17} \sim 2 \times 10^{19} / \text{cm}^3$ の範囲となるようとする。

【0078】

その後、プラズマCVD法により作製される窒化シリコン膜、窒化酸化シリコン膜により層間絶縁膜419を形成する。また、添加された不純物元素は活性化のために350~500の加熱処理またはレーザー光の照射を行う。さらに、公知の技術を用いて不純物領域(n+領域)に達するコンタクトホールを形成した後、ソース電極またはドレイン電極420を形成しTFTを得る。

10

【0079】

最後に公知の技術を用いて水素化処理を行い、全体を水素化してnチャネル型TFTが完成する。(図5(E))

【0080】

半導体層にはチャネル形成領域419、不純物領域(n-領域)で形成されるLDD(Lightly Doped Drain)領域416、不純物領域(n+領域)で形成されるソースまたはドレイン領域418が形成されている。また、LDD領域416はゲート電極417とオーバーラップして形成され、ドレイン端における電界の集中を緩和して、ホットキャリアによる劣化を防いでいる。勿論シングルドレインや、LDD構造でnチャネル型TFTを作製することもできる。本実施例で示すnチャネル型TFTを用いて基本論理回路を構成したり、さらに複雑なロジック回路(信号分割回路、D/Aコンバータ、オペアンプ、補正回路など)を構成することができ、さらにはメモリやマイクロプロセッサをも形成しうる。例えば、EL表示装置の駆動回路を全てnチャネル型TFTで構成することも可能である。

20

【0081】

また、本実施例は実施例1と組み合わせることが可能である。

【0082】

[実施例4]

30

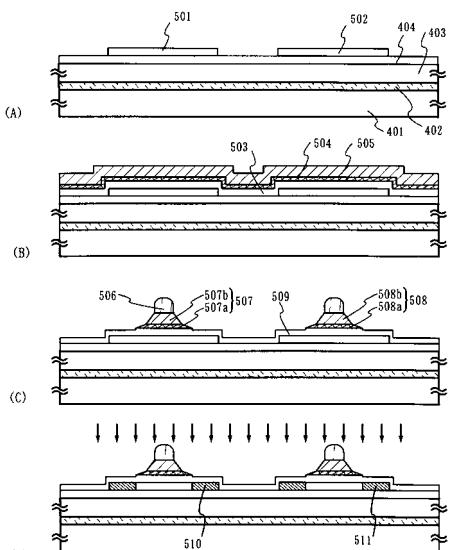

本実施例は、nチャネル型TFTとpチャネル型TFTとを相補的に組み合わせたCMOS回路を作製する例であり、図6、図7を用いて説明する。

【0083】

実施例2に従って、第1固定基板と第1接着層(分離層)で貼りつけた素子形成基板上に下地絶縁膜を形成した後、半導体層501、502を形成する。(図6(A))

【0084】

次いで、スパッタ法によりゲート絶縁膜503と第1導電膜504と第2導電膜505を形成する。(図6(B))本実施例では、第1導電膜504を窒化タンタルまたはチタンで50~100nmの厚さに形成し、第2導電膜505をタンゲステンで100~300nmの厚さに形成する。

40

【0085】

次に図6(C)に示すように、レジストによるマスク506を形成し、ゲート電極を形成するための第1のエッチング処理を行う。エッチング方法に限定はないが、好適にはICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いる。エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>を混合し、0.5~2Pa、好ましくは1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した場合にはタンゲステン膜、窒化タンタル膜及びチタン膜の場合でも、それぞれ同程度の速度でエッチングすることができる。

50

## 【0086】

上記エッティング条件では、レジストによるマスクの形状と、基板側に印加するバイアス電圧の効果により端部をテーパー形状とすることができます。テーパー部の角度は15～45°となるようにする。また、ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10～20%程度の割合でエッティング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2～4（代表的には3）であるので、オーバーエッティング処理により、酸化窒化シリコン膜が露出した面は20～50nm程度エッティングされる。こうして、第1のエッティング処理により第1導電膜と第2導電膜から成る第1形状の導電層507、508（第1の導電層507a、508aと第2導電層507b、508b）を形成する。509はゲート絶縁膜であり、第1の形状の導電層で覆われない領域は20～50nm程度エッティングされ薄くなる。10

## 【0087】

そして、第1のドーピング処理を行いn型の不純物（ドナー）をドーピングする。（図6（D））その方法はイオンドープ法若しくはイオン注入法で行う。イオンドープ法の条件はドーズ量を $1 \times 10^{13} \sim 5 \times 10^{14} / \text{cm}^2$ として行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン（P）または砒素（As）を用いる。この場合、第1形状の導電層507、508はドーピングする元素に対してマスクとなり、加速電圧を適宜調節（例えば、20～60keV）して、ゲート絶縁膜509を通過した不純物元素により不純物領域（n+領域）520、521を形成する。例えば、不純物領域（n+領域）におけるリン（P）濃度は $1 \times 10^{20} \sim 1 \times 10^{21} / \text{cm}^3$ の範囲となるよう20にする。

## 【0088】

さらに図7（A）に示すように第2のエッティング処理を行う。エッティングはICPエッティング法を用い、エッティングガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>を混合して、1Paの圧力でコイル型の電極に500WのRF電力（13.56MHz）を供給してプラズマを生成する。基板側（試料ステージ）には50WのRF（13.56MHz）電力を投入し、第1のエッティング処理に比べ低い自己バイアス電圧を印加する。このような条件によりタンゲステン膜を異方性エッティングし、第1の導電層である窒化タンタル膜またはチタン膜を残存せらるようする。こうして、第2形状の導電層512、513（第1の導電膜512a、513aと第2の導電膜512b、513b）を形成する。516はゲート絶縁膜であり、第2の形状の導電層512、513で覆われない領域はさらに20～50nm程度エッティングされて膜厚が薄くなる。30

## 【0089】

そして、図7（B）に示すように第2のドーピング処理を行う。第1のドーピング処理よりもドーズ量を下げ高加速電圧の条件でn型の不純物（ドナー）をドーピングする。例えば、加速電圧を70～120keVとし、 $1 \times 10^{13} / \text{cm}^2$ のドーズ量で行い、図6（D）で島状半導体膜に形成された第1の不純物領域の内側に不純物領域を形成する。ドーピングは、第2の導電膜512b、513bを不純物元素に対するマスクとして用い、第1の導電膜512a、512aの下側の領域に不純物元素が添加されるようにドーピングする。こうして、第1の導電膜512a、513aと重なる不純物領域（n-領域）514、515が形成される。この不純物領域は、第2の導電層512a、513aがほぼ同じ膜厚で残存していることから、第2の導電層に沿った方向における濃度差は小さく、 $1 \times 10^{17} \sim 1 \times 10^{19} / \text{cm}^3$ の濃度で形成する。40

## 【0090】

そして、図7（B）に示すように、第3のエッティング処理を行い、ゲート絶縁膜346のエッティング処理を行う。その結果、第2の導電膜もエッティングされ、端部が後退して小さくなり、第3形状の導電層517、518が形成される。図中で519は残存するゲート絶縁膜である。

## 【0091】

そして、図7（C）に示すように、レジストによるマスク520を形成し、pチャネル型50

TFTを形成する島状半導体層501にp型の不純物(アクセプタ)をドーピングする。典型的にはボロン(B)を用いる。不純物領域(p+領域)521、522の不純物濃度は $2 \times 10^{20} \sim 2 \times 10^{21} / \text{cm}^3$ となるようにし、含有するリン濃度の1.5~3倍のボロンを添加して導電型を反転させる。

## 【0092】

以上までの工程でそれぞれの島状半導体層に不純物領域が形成される。第3形状の導電層517、518はゲート電極となる。その後、図7(D)に示すように、窒化シリコン膜または酸化窒化シリコン膜から成る保護絶縁膜523をプラズマCVD法で形成する。そして導電型の制御を目的としてそれぞれの島状半導体層に添加された不純物元素を活性化する工程を行う。

10

## 【0093】

さらに、窒化シリコン膜524を形成し、水素化処理を行う。その結果、窒化シリコン膜524中の水素が島状半導体層中に拡散させることで水素化を達成することができる。

## 【0094】

層間絶縁膜525は、ポリイミド、アクリルなどの有機絶縁物材料で形成する。勿論、プラズマCVD法でTEOS(Tetraethyl Ortho silicate)を用いて形成される酸化シリコン膜を適用しても良いが、平坦性を高める観点からは前記有機物材料を用いることが望ましい。

## 【0095】

次いで、コンタクトホールを形成し、アルミニウム(A1)、チタン(Ti)、タンタル(Ta)などを用いて、ソース配線またはドレイン配線526~528を形成する。

20

## 【0096】

以上の工程で、nチャネル型TFTとpチャネル型TFTとを相補的に組み合わせたCMOS回路を得ることができる。

## 【0097】

pチャネル型TFTにはチャネル形成領域530、ソース領域またはドレイン領域として機能する不純物領域521、522を有している。

## 【0098】

nチャネル型TFTにはチャネル形成領域531、第3形状の導電層から成るゲート電極518と重なる不純物領域515a(Gate Overlapped Drain: GOLD領域)、ゲート電極の外側に形成される不純物領域515b(LDD領域)とソース領域またはドレイン領域として機能する不純物領域516を有している。

30

## 【0099】

このようなCMOS回路は、アクティブマトリクス型のEL表示装置の駆動回路を形成することを可能とする。それ以外にも、このようなnチャネル型TFTまたはpチャネル型TFTは、画素部を形成するトランジスタに応用することができる。

## 【0100】

このようなCMOS回路を組み合わせることで基本論理回路を構成したり、さらに複雑なロジック回路(信号分割回路、D/Aコンバータ、オペアンプ、補正回路など)をも構成することができ、さらにはメモリやマイクロプロセッサをも形成することができる。

40

## 【0101】

また、本実施例は実施例1と組み合わせることが可能である。

## 【0102】

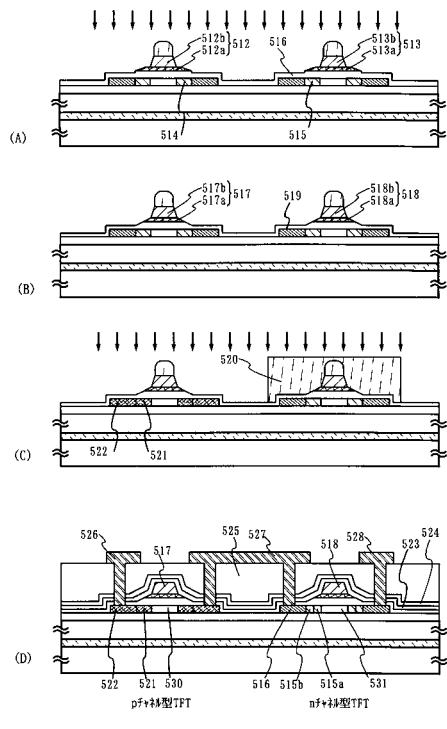

## [実施例5]

実施例3に示すnチャネル型TFTは、チャネル形成領域となる半導体に周期表の15族に属する元素(好ましくはリン)もしくは周期表の13族に属する元素(好ましくはボロン)を添加することによりエンハンスマント型とデプレッション型とを作り分けることができる。

## 【0103】

50

また、nチャネル型TFTを組み合わせてNMOS回路を形成する場合、エンハンスマント型TFT同士で形成する場合（以下、EEMOS回路という）と、エンハンスマント型とデプレッション型とを組み合わせて形成する場合（以下、EDMOS回路という）がある。

【0104】

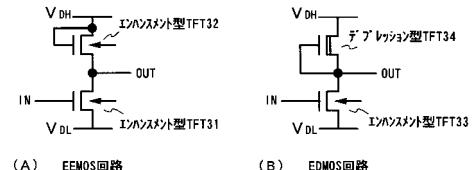

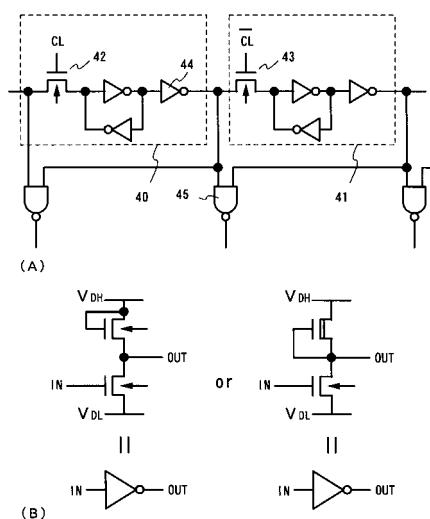

ここでEEMOS回路の例を図8(A)に、EDMOS回路の例を図8(B)に示す。図8(A)において、31、32はどちらもエンハンスマント型のnチャネル型TFT（以下、E型N TFTという）である。また、図8(B)において、33はE型N TFT、34はデプレッション型のnチャネル型TFT（以下、D型N TFTという）である。

【0105】

なお、図8(A)、(B)において、VDHは正の電圧が印加される電源線（正電源線）であり、VDLは負の電圧が印加される電源線（負電源線）である。負電源線は接地電位の電源線（接地電源線）としても良い。

【0106】

さらに、図8(A)に示したEEMOS回路もしくは図8(B)に示したEDMOS回路を用いてシフトレジスタを作製した例を図9に示す。図9において、40、41はフリップフロップ回路である。また、42、43はE型N TFTであり、E型N TFT 42のゲートにはクロック信号(CL)が入力され、E型N TFT 43のゲートには極性の反転したクロック信号(CLバー)が入力される。また、44で示される記号はインバータ回路であり、図9(B)に示すように、図8(A)に示したEEMOS回路もしくは図8(B)に示したEDMOS回路が用いられる。従って、EL表示装置の駆動回路を全てnチャネル型TFTで構成することも可能である。

【0107】

また、本実施例は実施例1または実施例3と組み合わせることが可能である。

【0108】

[実施例6]

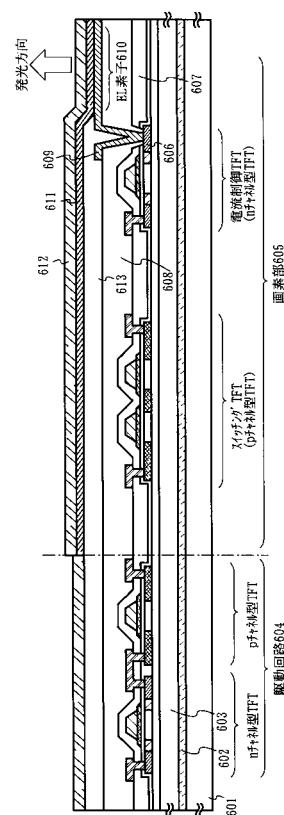

ここでは、上記実施例2～5で得られるTFTを用いてEL（エレクトロルミネンス）表示装置を作製した例について図10～図13を用い、以下に説明する。

【0109】

同一の絶縁体上に画素部とそれを駆動する駆動回路を有した発光装置の例（但し封止前の状態）を図10に示す。なお、駆動回路には基本単位となるCMOS回路を示し、画素部には一つの画素を示す。このCMOS回路は実施例4に従えば得ることができる。

【0110】

図10において、601は第1固定基板、602は第1接着層、603は素子形成基板であり、その上にはnチャネル型TFTとpチャネル型TFTからなる駆動回路604、pチャネル型TFTからなるスイッチングTFTおよびnチャネル型TFTからなる電流制御TFTとが形成されている。また、本実施例では、TFTはすべてトップゲート型TFTで形成されている。

【0111】

nチャネル型TFTおよびpチャネル型TFTの説明は実施例4を参照すれば良いので省略する。また、スイッチングTFTはソース領域およびドレイン領域の間に二つのチャネル形成領域を有した構造（ダブルゲート構造）となっているが、実施例2でのpチャネル型TFTの構造の説明を参照すれば容易に理解できるので説明は省略する。なお、本実施例はダブルゲート構造に限定されることなく、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。

【0112】

また、電流制御TFTのドレイン領域606の上には第2層間絶縁膜608が設けられる前に、第1層間絶縁膜607にコンタクトホールが設けられている。これは第2層間絶縁膜608にコンタクトホールを形成する際に、エッチング工程を簡単にするためである。第2層間絶縁膜608にはドレイン領域606に到達するようにコンタクトホールが形成

10

20

30

40

50

され、ドレイン領域 606 に接続された画素電極 609 が設けられている。画素電極 609 は E L 素子の陰極として機能する電極であり、周期表の 1 族もしくは 2 族に属する元素を含む導電膜を用いて形成されている。本実施例では、リチウムとアルミニウムとの化合物からなる導電膜を用いる。

【 0113 】

次に、613 は画素電極 609 の端部を覆うように設けられた絶縁膜であり、本明細書中ではバンクと呼ぶ。バンク 613 は珪素を含む絶縁膜もしくは樹脂膜で形成すれば良い。樹脂膜を用いる場合、樹脂膜の比抵抗が  $1 \times 10^6 \sim 1 \times 10^{12}$  m (好ましくは  $1 \times 10^8 \sim 1 \times 10^{10}$  m) となるようにカーボン粒子もしくは金属粒子を添加すると、成膜時の絶縁破壊を抑えることができる。

10

【 0114 】

また、E L 素子 610 は画素電極 (陰極) 609、E L 層 611 および陽極 612 からなる。陽極 612 は、仕事関数の大きい導電膜、代表的には酸化物導電膜が用いられる。酸化物導電膜としては、酸化インジウム、酸化スズ、酸化亜鉛もしくはそれらの化合物を用いれば良い。

【 0115 】

なお、本明細書中では発光層に対して正孔注入層、正孔輸送層、正孔阻止層、電子輸送層、電子注入層もしくは電子阻止層を組み合わせた積層体を E L 層と定義する。

【 0116 】

なお、ここでは図示しないが陽極 612 を形成した後、E L 素子 610 を完全に覆うようにしてパッシベーション膜を設けることは有効である。パッシベーション膜としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いる。

20

【 0117 】

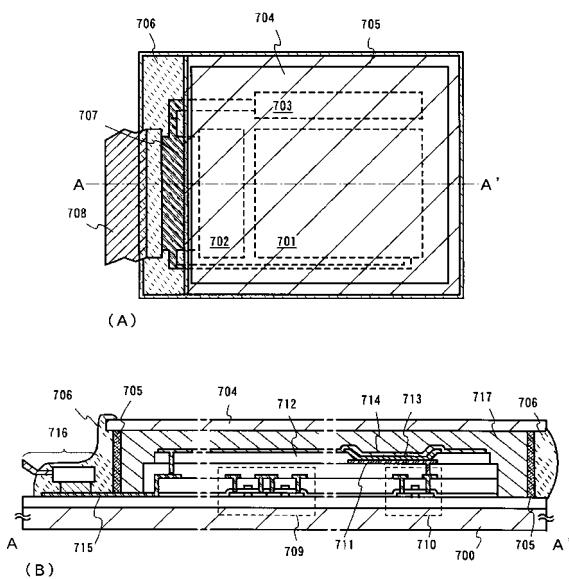

次いで、E L 素子を保護するための封止 (または封入) 工程まで行った後、実施の形態および実施例 1 に示したようにレーザー照射により第 1 固定基板 601 を分離した。その後の E L 表示装置について図 11 (A)、(B) を用いて説明する。

【 0118 】

図 11 (A) は、E L 素子の封止までを行った状態を示す上面図、図 11 (B) は図 11 (A) を A - A' で切断した断面図である。点線で示された 701 は画素部、702 はソース側駆動回路、703 はゲート側駆動回路である。また、704 はカバー材、705 は第 1 シール材、706 は第 2 シール材である。

30

【 0119 】

なお、708 はソース側駆動回路 702 及びゲート側駆動回路 703 に入力される信号を伝送するための配線であり、外部入力端子となる F P C (フレキシブルプリントサーチケット) 708 からビデオ信号やクロック信号を受け取る。なお、ここでは F P C しか図示されていないが、この F P C にはプリント配線基盤 (P W B) が取り付けられていても良い。

【 0120 】

次に、断面構造について図 11 (B) を用いて説明する。絶縁体 700 (素子形成基板 603 に相当) の上方には画素部、ソース側駆動回路 709 が形成されており、画素部は電流制御 T F T 710 とそのドレインに電気的に接続された画素電極 711 を含む複数の画素により形成される。また、ソース側駆動回路 709 は n チャネル型 T F T と p チャネル型 T F T を組み合わせた C M O S 回路を用いて形成される。なお、絶縁体 700 には偏光板 (代表的には円偏光板) を貼り付けても良い。

40

【 0121 】

また、画素電極 711 の両端にはバンク 712 が形成され、画素電極 711 上には E L 層 713 および E L 素子の陽極 714 が形成される。陽極 714 は全画素に共通の配線としても機能し、接続配線 715 を経由して F P C 716 に電気的に接続されている。さらに、画素部及びソース側駆動回路 709 に含まれる素子は全てパッシベーション膜 (図示し

50

ない)で覆われている。

【0122】

また、第1シール材705によりカバー材704が貼り合わされている。なお、カバー材704とEL素子との間隔を確保するためにスペーサを設けても良い。そして、第1シール材705の内側には空隙717が形成されている。なお、第1シール材705は水分や酸素を透過しない材料であることが望ましい。さらに、空隙717の内部に吸湿効果をもつ物質や酸化防止効果をもつ物質を設けることは有効である。

【0123】

なお、カバー材704の表面および裏面には保護膜として炭素膜(具体的にはダイヤモンドライクカーボン膜)を2~30nmの厚さに設けると良い。このような炭素膜(ここでは図示しない)は、酸素および水の侵入を防ぐとともにカバー材704の表面を機械的に保護する役割をもつ。

10

【0124】

また、カバー材704を接着した後、第1シール材705の露呈面を覆うように第2シール材706を設けている。第2シール材706は第1シール材705と同じ材料を用いることができる。

【0125】

以上のような構造でEL素子を封入することにより、EL素子を外部から完全に遮断することができ、外部から水分や酸素等のEL層の酸化による劣化を促す物質が侵入することを防ぐことができる。従って、信頼性の高いEL表示装置が得られる。

20

【0126】

また、本実施例は実施例1と組み合わせることが可能である。

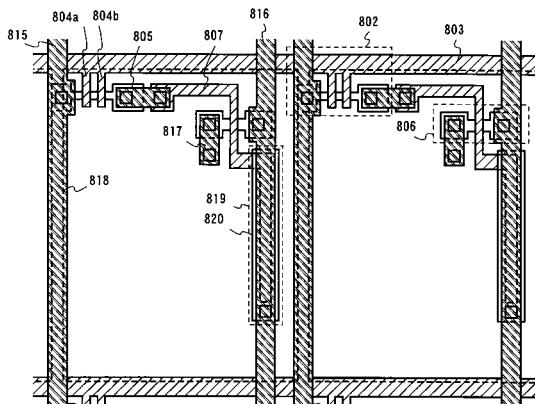

【0127】

[実施例7]

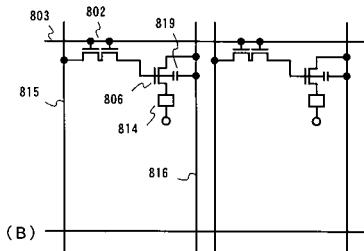

本実施例では、実施例6で得られるEL表示装置において、画素部のさらに詳細な上面構造を図12(A)に、回路図を図12(B)に示す。図12(A)及び図12(B)では共通の符号を用いるので互いに参照すれば良い。

【0128】

スイッチング用TFT802のソースはソース配線815に接続され、ドレインはドレイン配線805に接続される。また、ドレイン配線805は電流制御用TFT806のゲート電極807に電気的に接続される。また、電流制御用TFT806のソースは電流供給線816に電気的に接続され、ドレインはドレイン配線817に電気的に接続される。また、ドレイン配線817は点線で示される画素電極(陰極)818に電気的に接続される。

30

【0129】

このとき、819で示される領域には保持容量が形成される。保持容量819は、電流供給線816と電気的に接続された半導体膜820、ゲート絶縁膜と同一層の絶縁膜(図示せず)及びゲート電極807との間で形成される。また、ゲート電極807、第1層間絶縁膜と同一の層(図示せず)及び電流供給線816で形成される容量も保持容量として用いることが可能である。

40

【0130】

また、本実施例は実施例1または実施例6と組み合わせることが可能である。

【0131】

[実施例8]

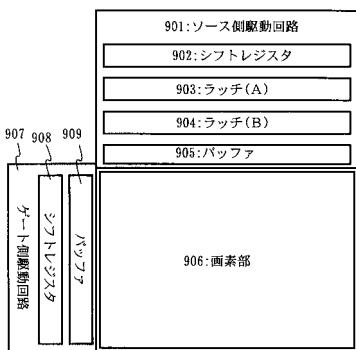

本実施例では実施例6または実施例7に示したEL表示装置の回路構成例を図13に示す。なお、本実施例ではデジタル駆動を行うための回路構成を示す。本実施例では、ソース側駆動回路901、画素部906及びゲート側駆動回路907を有している。なお、本明細書中において、駆動回路とはソース側処理回路およびゲート側駆動回路を含めた総称である。

【0132】

50

ソース側駆動回路 901 は、シフトレジスタ 902、ラッチ (A) 903、ラッチ (B) 904、バッファ 905 を設けている。なお、アナログ駆動の場合はラッチ (A)、(B) の代わりにサンプリング回路 (トランスマッピングゲート) を設ければ良い。また、ゲート側駆動回路 907 は、シフトレジスタ 908、バッファ 909 を設けている。

【0133】

また、本実施例において、画素部 906 は複数の画素を含み、その複数の画素に E-L 素子が設けられている。このとき、E-L 素子の陰極は電流制御 TFT のドレインに電気的に接続されていることが好ましい。

【0134】

これらソース側駆動回路 901 およびゲート側駆動回路 907 は実施例 2 ~ 4 で得られる n チャネル型 TFT または p チャネル型 TFT で形成されている。

10

【0135】

なお、図示していないが、画素部 906 を挟んでゲート側駆動回路 907 の反対側にさらにゲート側駆動回路を設けても良い。この場合、双方は同じ構造でゲート配線を共有しており、片方が壊れても残った方からゲート信号を送って画素部を正常に動作させるような構成とする。

【0136】

また、本実施例は実施例 1、実施例 6 または実施例 7 と組み合わせることが可能である。

【0137】

[実施例 9]

20

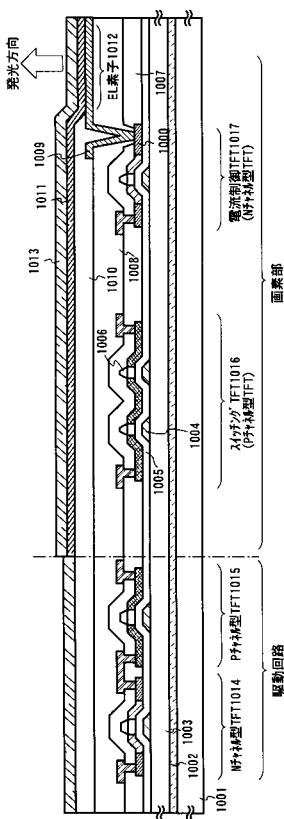

本実施例では、画素部及び駆動回路に使用する TFT を全て逆スタガ型 TFT で構成した E-L 表示装置の例を図 14 に示す。

【0138】

図 14 において、1001 は第 1 固定基板、1002 は第 1 接着層、1003 は素子形成基板であり、まず、実施の形態に従い、第 1 固定基板 1001 と第 1 接着層 1002 ( 分離層 ) で貼りつけた素子形成基板 1003 を用意する。なお、必要があれば素子形成基板上に下地絶縁膜を形成してもよい。

【0139】

次いで、素子形成基板 1003 上に単層構造または積層構造を有するゲート配線 ( ゲート電極含む ) 1004 を形成する。ゲート配線 12 の形成手段としては熱 CVD 法、プラズマ CVD 法、減圧熱 CVD 法、蒸着法、スパッタ法等を用いて 10 ~ 1000 nm、好ましくは 30 ~ 300 nm の膜厚範囲の導電膜を形成した後、公知のパターニング技術で形成する。また、ゲート配線 12 の材料としては、導電性材料または半導体材料を主成分とする材料、例えば Ta ( タンタル )、Mo ( モリブデン )、Ti ( チタン )、W ( タングステン )、クロム ( Cr ) 等の高融点金属材料、これら金属材料とシリコンとの化合物であるシリサイド、N 型又は P 型の導電性を有するポリシリコン等の材料、低抵抗金属材料 Cu ( 銅 )、Al ( アルミニウム ) 等を主成分とする材料層を少なくとも一層有する構造であれば特に限定されることなく用いることができる。

30

【0140】

次いで、ゲート絶縁膜 1005 を形成する。

40

【0141】

次いで、非晶質半導体膜を成膜する。次いで、非晶質半導体膜のレーザー結晶化処理を行い、結晶質半導体膜を形成した後、得られた結晶質半導体膜を所望の形状にパターニングして半導体層を形成する。次いで、半導体層上に絶縁層 1006 を形成する。この絶縁層 1006 は不純物元素の添加工程時にチャネル形成領域を保護する。

【0142】

次いで、イオン注入法またはイオンドーピング法を用い、半導体層に n 型を付与する不純物元素または p 型を付与する不純物元素を適宜、添加して LDD 領域やソース領域やドレイン領域を形成する不純物領域を形成する。

【0143】

50

その後、スパッタ法により作製される窒化シリコン膜、窒化酸化シリコン膜、または酸化シリコン膜により層間絶縁膜を形成する。また、添加された不純物元素は活性化処理を行う。ここでは、レーザー光の照射を行った。レーザー光の照射に代えて、350℃以下の加熱処理で活性化を行ってもよい。

【0144】

次いで、公知の技術を用いてソース領域またはドレイン領域に達するコンタクトホールを形成した後、ソース電極またはドレイン電極を形成して逆スタガ型のTFTを得る。

【0145】

次いで、公知の技術を用いて水素化処理を行い、全体を水素化してnチャネル型TFT及びpチャネル型TFTが完成する。本実施例では比較的低温で行うことが可能な水素プラズマを用いて水素化処理を行った。

10

【0146】

次いで、スパッタ法により作製される窒化シリコン膜、窒化酸化シリコン膜、または酸化シリコン膜により第1層間絶縁膜1007を形成する。次いで、公知の技術を用いて画素部のドレイン領域1000に達するコンタクトホールを形成した後、第2層間絶縁膜1008を形成する。次いで、公知の技術を用いて画素部のドレイン領域1000に達するコンタクトホールを形成した後、画素電極1009を形成する。次いで、画素電極の両端にバンク1010を形成し、画素電極上にEL層1011およびEL素子1012の陽極1013を形成する。

【0147】

20

図14において、素子形成基板上にはNチャネル型TFT1014、Pチャネル型TFT1015からなる駆動回路、Pチャネル型TFTからなるスイッチングTFT1016およびNチャネル型TFTからなる電流制御TFT1017が形成されている。また、本実施例では、TFTはすべて逆スタガ型TFTで形成されている。

【0148】

また、スイッチングTFT1016はソース領域およびドレイン領域の間に二つのチャネル形成領域を有した構造（ダブルゲート構造）となっているが、実施例2でのPチャネル型TFTの構造の説明を参照すれば容易に理解できるので説明は省略する。なお、本実施例はダブルゲート構造に限定されることなく、チャネル形成領域が一つ形成されるシングルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。

30

【0149】

さらに、画素部及び駆動回路に含まれる素子は全てパッシベーション膜（図示しない）で覆うことが好ましい。

【0150】

以降の工程は、実施例6の工程に従って、第2接着層で第2固定基板を貼り合わせた後、第1接着層1002にレーザーを照射して第1固定基板1001を分離して、発光装置が完成する。

【0151】

なお、本実施例は、実施例1、実施例7、または実施例8と自由に組み合わせることが可能である。

40

【0152】

[実施例10]

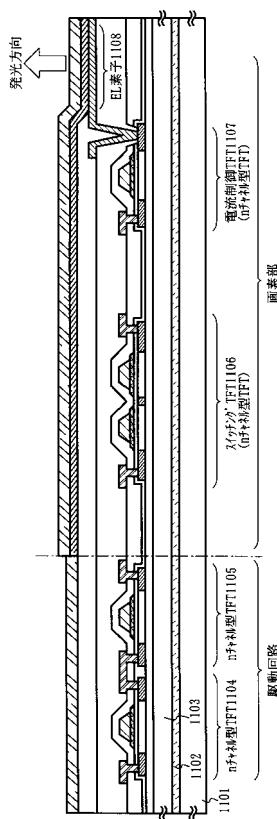

本実施例では、画素部及び駆動回路に使用するTFTを全てNチャネル型TFTで構成したEL表示装置の例を図15に示す。

【0153】

図15において、1101は第1固定基板、1102は第1接着層、1103は素子形成基板であり、まず、実施の形態に従い、第1固定基板1101と第1接着層1102（分離層）で貼りつけた素子形成基板1103上に下地絶縁膜を形成する。

【0154】

下地絶縁膜上にはNチャネル型TFT1104、Nチャネル型TFT1105からなる駆

50

動回路、Nチャネル型TFTからなるスイッチングTFT1106およびNチャネル型TFTからなる電流制御TFT1107が形成されている。なお、Nチャネル型TFTの説明は実施例3を参照すれば良いので省略する。また、EL素子1108の説明は実施例6を参照すれば良いので省略する。

【0155】

さらに、画素部及び駆動回路に含まれる素子は全てパッシベーション膜(図示しない)で覆うことが好ましい。

【0156】

また、図15の状態を得た後、実施例6の工程に従って、第2接着層で第2固定基板を貼り合わせた後、第1接着層1102にレーザーを照射して第1固定基板1101を分離して、発光装置が完成すればよい。

10

【0157】

Nチャネル型TFTのみでゲート側駆動回路およびソース側駆動回路を形成することにより画素部および駆動回路をすべてNチャネル型TFTで形成することが可能となる。従って、アクティブマトリクス型の電気光学装置を作製する上でTFT工程の歩留まりおよびスループットを大幅に向上させることができ、製造コストを低減することが可能となる。

【0158】

なお、ソース側駆動回路もしくはゲート側駆動回路のいずれか片方を外付けのICチップとする場合にも本実施例は実施できる。

20

【0159】

また、本実施例では、E型N TFTのみを用いて駆動回路を構成したがE型N TFTおよびD型N TFTを組み合わせて形成してもよい。

【0160】

なお、本実施例は、実施例1、実施例3、実施例5、実施例7、または実施例8と自由に組み合わせることが可能である。また、本実施例ではトップゲート型TFTを用いたが特に限定されず、実施例9に示したような逆スタガ型TFTを用いることもできる。

【0161】

[実施例11]

本実施例では、画素部及び駆動回路に使用するTFTを全てPチャネル型TFTで構成したEL表示装置の例を図16に示す。

30

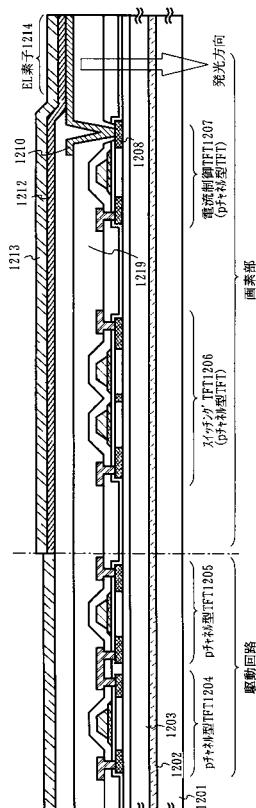

【0162】

図16において、1201は第1固定基板、1202は第1接着層、1203は素子形成基板であり、まず、実施の形態に従い、第1固定基板1201と第1接着層1202(分離層)で貼りつけた素子形成基板1203上に下地絶縁膜を形成する。

【0163】

その上にはNチャネル型TFT1204、Nチャネル型TFT1205からなる駆動回路、Nチャネル型TFTからなるスイッチングTFT1206およびNチャネル型TFTからなる電流制御TFT1207が形成されている。なお、Nチャネル型TFTの説明は実施例2を参照すれば良いので省略する。

【0164】

40

本実施例では、電流制御TFT1207の上には層間絶縁膜1208、1209が形成され、その上に電流制御TFT1207のドレインと電気的に接続する画素電極1210が形成される。本実施例では、仕事関数の大きい透明導電膜からなる画素電極1210がEL素子の陽極として機能する。

【0165】

そして、実施例6と同様に画素電極1210の上にはバンク1211が形成される。

【0166】

次ぎに、画素電極1210の上にはEL層1212が形成される。そのEL層1212の上には周期表の1族または2族に属する元素を含む導電膜からなる陰極1213が設けられる。こうして、画素電極(陽極)1210、EL層1212及び陰極1213からなる

50

E L 素子 1 2 1 4 が形成される。

【 0 1 6 7 】

さらに、画素部及び駆動回路に含まれる素子は全てパッシベーション膜（図示しない）で覆うことが好ましい。

【 0 1 6 8 】

但し、本実施例は実施例 6、実施例 9 及び実施例 10 とは E L 素子からの光の放射方向が異なり、素子形成基板は透明でなければならない。

【 0 1 6 9 】

以降の工程は、実施例 6 の工程に従って、第 2 接着層で第 2 固定基板を貼り合わせた後、第 1 接着層 1 2 0 2 にレーザーを照射して第 1 固定基板 1 2 0 1 を分離して、発光装置が完成する。

【 0 1 7 0 】

なお、本実施例は、実施例 1、実施例 2、実施例 6、実施例 7、または実施例 8 と自由に組み合わせることが可能である。また、本実施例ではトップゲート型 TFT を用いたが特に限定されず、実施例 9 に示したような逆スタガ型 TFT を用いることもできる。

【 0 1 7 1 】

【 実施例 1 2 】

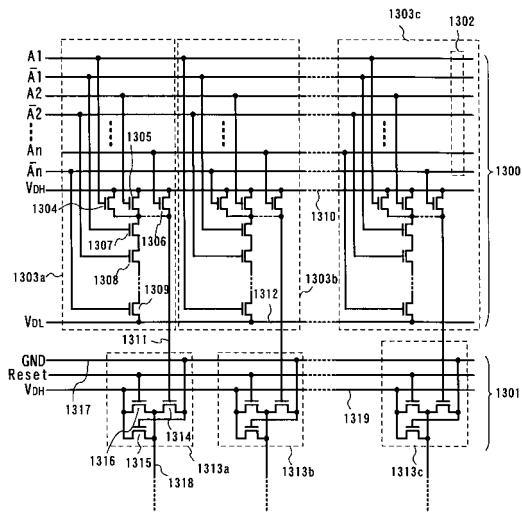

本実施例では、一般的なシフトレジスタの代わりに図 4 に示すような P チャネル型 TFT を用いたデコーダを用いて駆動回路を形成した例を示す。なお、図 17 はゲート側駆動回路の例である。

【 0 1 7 2 】

図 17において、1 3 0 0 がゲート側駆動回路のデコーダ、1 3 0 1 がゲート側駆動回路のバッファ部である。

【 0 1 7 3 】

まずゲート側デコーダ 1 3 0 0 を説明する。まず 1 3 0 2 はデコーダ 1 3 0 0 の入力信号線（以下、選択線という）であり、ここでは A 1、A 1 バー（A 1 の極性が反転した信号）、A 2、A 2 バー（A 2 の極性が反転した信号）、… A n、A n バー（A n の極性が反転した信号）を示している。

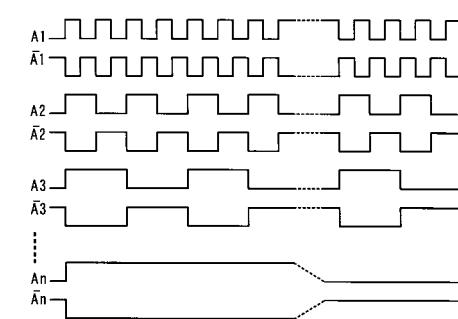

【 0 1 7 4 】

選択線 1 3 0 2 は図 18 のタイミングチャートに示す信号を伝送する。図 18 に示すように、A 1 の周波数を 1 とすると、A 2 の周波数は  $2^{-1}$  倍、A 3 の周波数は  $2^{-2}$  倍、A n の周波数は  $2^{-(n-1)}$  倍となる。

【 0 1 7 5 】

また、1 3 0 3 a は第 1 段の NAND 回路（NAND セルともいう）、1 3 0 3 b は第 2 段の NAND 回路、1 3 0 3 c は第 n 段の NAND である。

【 0 1 7 6 】

また、NAND 回路 1 3 0 3 a ~ 1 3 0 3 c は、P チャネル型 TFT 1 3 0 4 ~ 1 3 0 9 が組み合わされて NAND 回路を形成している。

【 0 1 7 7 】

また、NAND 回路 1 3 0 3 a において、A 1、A 2 … A n（これらを正の選択線と呼ぶ）のいずれかに接続されたゲートを有する P チャネル型 TFT 1 3 0 4 ~ 1 3 0 6 は、互いに並列に接続されており、共通のソースとして正電源線（V<sub>DH</sub>）1 3 1 0 に接続され、共通のドレインとして出力線 1 3 1 1 に接続されている。

【 0 1 7 8 】

次に、バッファ 1 3 0 1 は NAND 回路 1 3 0 3 a ~ 1 3 0 3 c の各々に対応して複数のバッファ 1 3 1 3 a ~ 1 3 1 3 c により形成されている。但しバッファ 1 3 1 3 a ~ 1 3 1 3 c はいずれも同一構造で良い。また、バッファ 1 3 1 3 a ~ 1 3 1 3 c は一導電型 TFT として P チャネル型 TFT 1 3 1 4 ~ 1 3 1 6 を用いて形成される。

【 0 1 7 9 】

また、P チャネル型 TFT 1 3 1 6 はリセット信号線（Reset）をゲートとし、正電源線

10

20

30

40

50

1319をソースとし、ゲート配線1318をドレインとする。なお、接地電源線1317は負電源線（但し画素のスイッチング素子として用いるPチャネル型TFTがオン状態になるような電圧を与える電源線）としても構わない。

#### 【0180】

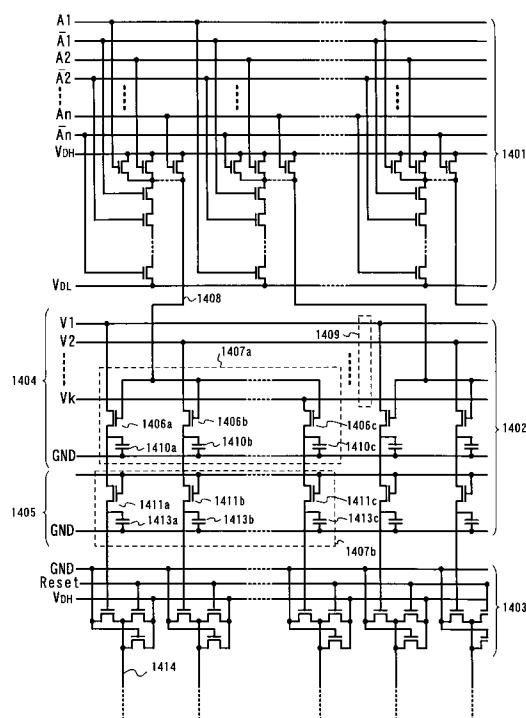

次に、ソース側駆動回路の構成を図19に示す。図19に示すソース側駆動回路はデコーダ1401、ラッチ1402およびバッファ1403を含む。なお、デコーダ1401およびバッファ1403の構成はゲート側駆動回路と同様であるので、ここでの説明は省略する。

#### 【0181】

図19に示すソース側駆動回路の場合、ラッチ1402は第1段目のラッチ1404および第2段目のラッチ1405からなる。また、第1段目のラッチ1404および第2段目のラッチ1405は、各々m個のPチャネル型TFT1406a～1406cで形成される複数の単位ユニット1407を有する。

#### 【0182】

そして、Pチャネル型TFT1406a～1406cのソースは各々ビデオ信号線（V1、V2…V<sub>k</sub>）1409に接続される。出力線1408に負電圧が加えられると一斉にPチャネル型TFT1406a～1406cがオン状態となり、各々に対応するビデオ信号が取り込まれる。また、こうして取り込まれたビデオ信号は、Pチャネル型TFT1406a～1406cの各々に接続されたコンデンサ1410a～1410cに保持される。

#### 【0183】

また、第2段目のラッチ1405も複数の単位ユニット1407bを有し、単位ユニット1407bはm個のPチャネル型TFT1411a～1411cで形成される。Pチャネル型TFT1411a～1411cのゲートはすべてラッチ信号線1412に接続され、ラッチ信号線1412に負電圧が加えられると一斉にPチャネル型TFT1411a～1411cがオン状態となる。

#### 【0184】

その結果、コンデンサ1410a～1410cに保持されていた信号が、Pチャネル型TFT1411a～1411cの各々に接続されたコンデンサ1413a～1413cに保持されると同時にバッファ303へと出力される。そして、バッファを介してソース配線1414に出力される。以上のような動作のソース側駆動回路によりソース配線が順番に選択されることになる。

#### 【0185】

以上のように、Pチャネル型TFTのみでゲート側駆動回路およびソース側駆動回路を形成することにより画素部および駆動回路をすべてPチャネル型TFTで形成することが可能となる。従って、アクティブマトリクス型の電気光学装置を作製する上でTFT工程の歩留まりおよびスループットを大幅に向上させることができ、製造コストを低減することが可能となる。

#### 【0186】

なお、本実施例は、実施例1、実施例2、実施例6、実施例7、または実施例8、実施例11と自由に組み合わせることが可能である。また、本実施例ではトップゲート型TFTを用いたが特に限定されず、実施例9に示したような逆スタガ型TFTを用いることもできる。

#### 【0187】

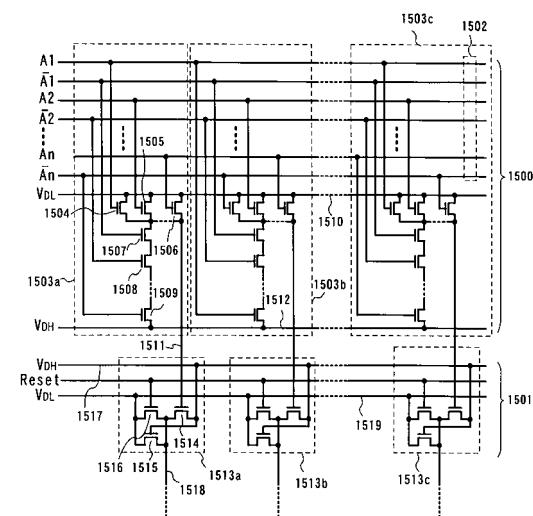

##### [実施例13]

本実施例では、一般的なシフトレジスタの代わりに図5に示すようなNチャネル型TFTを用いたデコーダを用いて駆動回路を形成した例を示す。なお、図20はゲート側駆動回路の例である。

#### 【0188】

図20において、1500がゲート側駆動回路のデコーダ、1501がゲート側駆動回路のバッファ部である。なお、バッファ部とは複数のバッファ（緩衝増幅器）が集積化され

10

20

30

40

50

た部分を指す。また、バッファとは後段の影響を前段に与えずに駆動を行う回路を指す。

【0189】

まずゲート側デコーダ1500を説明する。まず1502はデコーダ1500の入力信号線（以下、選択線という）であり、ここではA1、A1バー（A1の極性が反転した信号）、A2、A2バー（A2の極性が反転した信号）、…An、Anバー（Anの極性が反転した信号）を示している。即ち、2n本の選択線が並んでいると考えれば良い。

【0190】

選択線1502は図21のタイミングチャートに示す信号を伝送する。図21に示すように、A1の周波数を1とすると、A2の周波数は2<sup>-1</sup>倍、A3の周波数は2<sup>-2</sup>倍、Anの周波数は2<sup>-(n-1)</sup>倍となる。

10

【0191】

また、1503aは第1段のNAND回路（NANDセルともいう）、1503bは第2段のNAND回路、1503cは第n段のNANDである。NAND回路はゲート配線の本数分が必要であり、ここではn個が必要となる。即ち、本実施例ではデコーダ1500が複数のNAND回路からなる。

【0192】

また、NAND回路1503a～1503cは、Nチャネル型TFT1504～1509が組み合わされてNAND回路を形成している。また、Nチャネル型TFT1504～1509の各々のゲートは選択線1502（A1、A1バー、A2、A2バー…An、Anバー）のいずれかに接続されている。

20

【0193】

また、NAND回路1503aにおいて、A1、A2…An（これらを正の選択線と呼ぶ）のいずれかに接続されたゲートを有するNチャネル型TFT1504～1506は、互いに並列に接続されており、共通のソースとして負電源線（V<sub>DL</sub>）1510に接続され、共通のドレインとして出力線1511に接続されている。

【0194】

本実施例において、NAND回路は直列に接続されたn個のNチャネル型TFTおよび並列に接続されたn個のNチャネル型TFTを含む。

【0195】

次に、バッファ部1501はNAND回路1503a～1503cの各々に対応して複数のバッファ1513a～1513cにより形成されている。但しバッファ1513a～1513cはいずれも同一構造で良い。

30

【0196】

また、バッファ1513a～1513cはNチャネル型TFT1514～1516を用いて形成される。

【0197】

本実施例において、バッファ1513a～1513cは第1のNチャネル型TFT（Nチャネル型TFT1514）および第1のNチャネル型TFTに直列に接続され、且つ、第1のNチャネル型TFTのドレインをゲートとする第2のNチャネル型TFT（Nチャネル型TFT1515）を含む。

40

【0198】

また、Nチャネル型TFT1516（第3のNチャネル型TFT）はリセット信号線（Reset）をゲートとし、負電源線（V<sub>DL</sub>）1519をソースとし、ゲート配線1518をドレインとする。なお、負電源線（V<sub>DL</sub>）1519は接地電源線（GND）としても構わない。

【0199】

なお、Nチャネル型TFT1516は正電圧が加えられたゲート配線1518を強制的に負電圧に引き下げるリセットスイッチとして用いられる。即ち、ゲート配線1518の選択期間が終了したら。リセット信号を入力してゲート配線1518に負電圧を加える。但しNチャネル型TFT1516は省略することもできる。

50

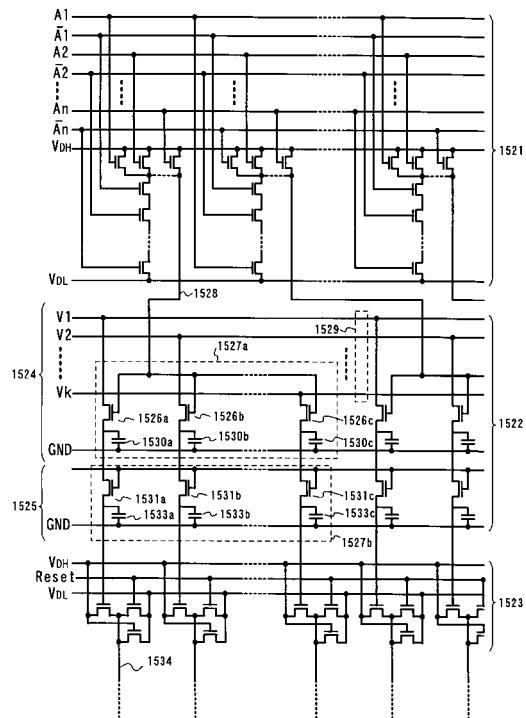

## 【0200】

次に、ソース側駆動回路の構成を図22に示す。図22に示すソース側駆動回路はデコーダ1521、ラッチ1522およびバッファ部1523を含む。

## 【0201】

図22に示すソース側駆動回路の場合、ラッチ1522は第1段目のラッチ1524および第2段目のラッチ1525からなる。また、第1段目のラッチ1524および第2段目のラッチ1525は、各々m個のNチャネル型TFT1526a～1526cで形成される複数の単位ユニット1527を有する。デコーダ1521からの出力線1528は単位ユニット1527を形成するm個のNチャネル型TFT1526a～1526cのゲートに入力される。なお、mは任意の整数である。

10

## 【0202】

そして、Nチャネル型TFT1526a～1526cのソースは各々ビデオ信号線(V1、V2…V<sub>k</sub>)1529に接続される。即ち、出力線1528に正電圧が加えられると一斉にNチャネル型TFT1526a～1526cがオン状態となり、各々に対応するビデオ信号が取り込まれる。また、こうして取り込まれたビデオ信号は、Nチャネル型TFT1526a～1526cの各々に接続されたコンデンサ1530a～1530cに保持される。

## 【0203】

また、第2段目のラッチ1525も複数の単位ユニット1527bを有し、単位ユニット1527bはm個のNチャネル型TFT1531a～1531cで形成される。Nチャネル型TFT1531a～1531cのゲートはすべてラッチ信号線1532に接続され、ラッチ信号線1532に負電圧が加えられると一斉にNチャネル型TFT1531a～1531cがオン状態となる。

20

## 【0204】

その結果、コンデンサ1530a～1530cに保持されていた信号が、Nチャネル型TFT1531a～1531cの各々に接続されたコンデンサ1533a～1533cに保持されると同時にバッファ1523へと出力される。そして、バッファを介してソース配線1534に出力される。以上のような動作のソース側駆動回路によりソース配線が順番に選択されることになる。

## 【0205】

以上のように、Nチャネル型TFTのみでゲート側駆動回路およびソース側駆動回路を形成することにより画素部および駆動回路をすべてNチャネル型TFTで形成することが可能となる。従って、アクティブマトリクス型の電気光学装置を作製する上でTFT工程の歩留まりおよびスループットを大幅に向上させることができ、製造コストを低減することが可能となる。

30

## 【0206】

なお、ソース側駆動回路もしくはゲート側駆動回路のいずれか片方を外付けのICチップとする場合にも本実施例は実施できる。

## 【0207】

また、本実施例では、E型NFTのみを用いて駆動回路を構成したがE型NFTおよびD型NFTを組み合わせて形成してもよい。

40

## 【0208】

なお、本実施例は、実施例1、実施例3、実施例5、実施例7、または実施例8と自由に組み合わせることが可能である。また、本実施例ではトップゲート型TFTを用いたが特に限定されず、実施例9に示したような逆スタガ型TFTを用いることもできる。

## 【0209】

## [実施例14]

素子形成基板としては、金属基板、例えばステンレス基板を用いることもできる。本実施例は、その場合の例を以下に示す。

## 【0210】

本実施例では、実施例1の素子形成基板として、ステンレス基板(厚さ10～200μm)

50

)を用いる。まず、実施の形態に従って第1固定基板とステンレス基板とを第1接着層で貼り合わせる。

【0211】

以降は、実施例1に従って、ステンレス基板からなる素子形成基板上に下地絶縁膜を形成して必要な素子を形成すればよい。なお、実施例1とは異なり、耐熱性が高いステンレス基板を用いているため、実施例1よりも高い温度(約500以下)でのプロセスを使用してTFTを作製することができる。

【0212】

そして、第1固定基板を分離する際、ステンレス基板を用いているため、レーザー光を照射しても素子形成基板上に形成された素子に全く影響を与えることなく第1固定基板分離することができる。

10

【0213】

また、ステンレス基板は遮光性を有しているため、本実施例の発光装置は、上方出射の発光装置となる。

【0214】

薄い金属基板(厚さ10~200μm)を用いることによって軽量化、薄型化が図れるとともに可撓性を有する発光装置を得ることができる。また、金属基板を用いているため、素子基板上に形成されたTFT素子の放熱効果が得られる。

【0215】

また、本実施例は、実施例1乃至13のいずれか一と自由に組み合わせることが可能である。

20

【0216】

[実施例15]

本願発明を実施して形成された駆動回路や画素部は様々な電気光学装置(アクティブマトリクス型液晶ディスプレイ、アクティブマトリクス型ELディスプレイ、アクティブマトリクス型ECディスプレイ)に用いることができる。即ち、それら電気光学装置を表示部に組み込んだ電子機器全てに本願発明を実施できる。

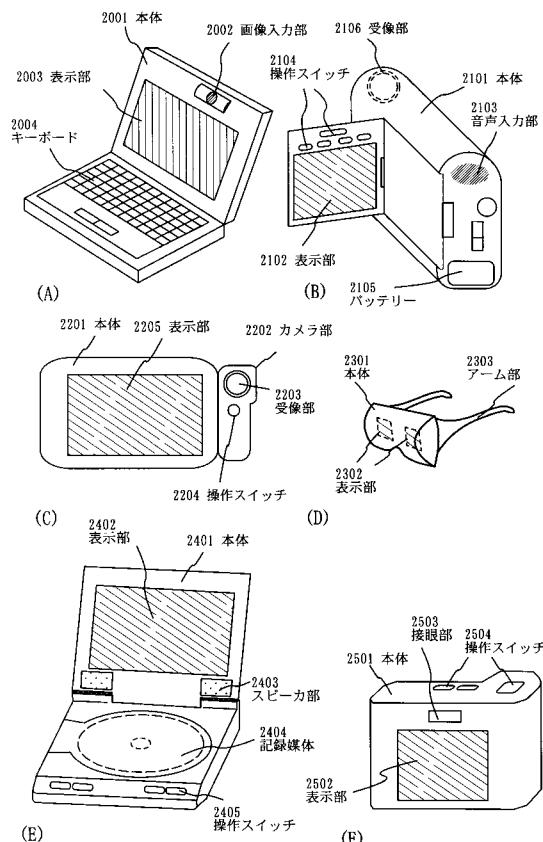

【0217】

その様な電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、カーステレオ、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図24及び図25に示す。

30

【0218】

図24(A)はパーソナルコンピュータであり、本体2001、画像入力部2002、表示部2003、キーボード2004等を含む。本発明を画像入力部2002、表示部2003やその他の駆動回路に適用することができる。

【0219】

図24(B)はビデオカメラであり、本体2101、表示部2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106等を含む。本発明を表示部2102やその他の駆動回路に適用することができる。

40

【0220】

図24(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示部2205等を含む。本発明は表示部2205やその他の駆動回路に適用できる。

【0221】

図24(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム部2303等を含む。本発明は表示部2302やその他の駆動回路に適用することができる。

【0222】

図24(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレー

50

ヤーであり、本体 2401、表示部 2402、スピーカ部 2403、記録媒体 2404、操作スイッチ 2405 等を含む。なお、このプレーヤーは記録媒体として DVD (Digital Versatile Disc)、CD 等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部 2402 やその他の駆動回路に適用することができる。

【0223】

図 24 (F) はデジタルカメラであり、本体 2501、表示部 2502、接眼部 2503、操作スイッチ 2504、受像部 (図示しない) 等を含む。本願発明を表示部 2502 やその他の駆動回路に適用することができる。

【0224】

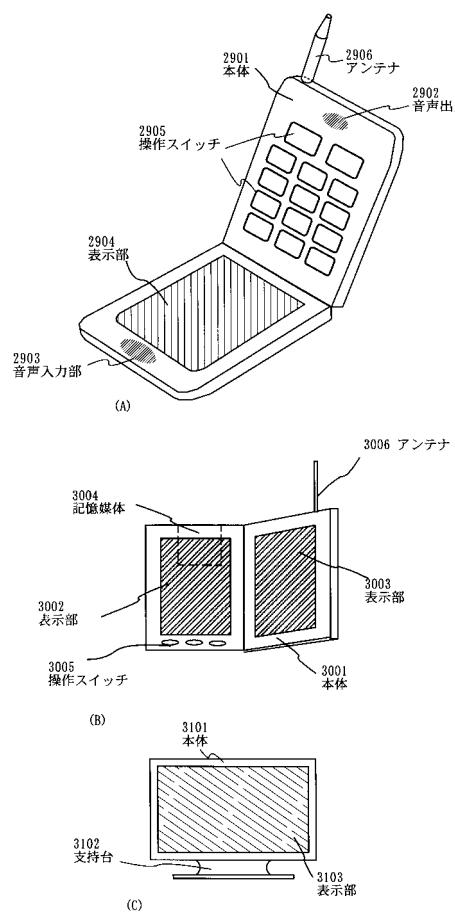

図 25 (A) は携帯電話であり、本体 2901、音声出力部 2902、音声入力部 2903、表示部 2904、操作スイッチ 2905、アンテナ 2906 等を含む。本願発明を音声出力部 2902、音声入力部 2903、表示部 2904 やその他の駆動回路に適用することができる。

【0225】

図 25 (B) は携帯書籍 (電子書籍) であり、本体 3001、表示部 3002、3003、記憶媒体 3004、操作スイッチ 3005、アンテナ 3006 等を含む。本発明は表示部 3002、3003 やその他の駆動回路に適用することができる。

【0226】

図 25 (C) はディスプレイであり、本体 3101、支持台 3102、表示部 3103 等を含む。本発明は表示部 3103 に適用することができる。本発明のディスプレイは特に大画面化した場合において有利であり、対角 10 インチ以上 (特に 30 インチ以上) のディスプレイには有利である。

【0227】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例 1 ~ 14 のどのような組み合わせからなる構成を用いても実現することができる。

【0228】

【発明の効果】

本発明により樹脂基板である素子形成基板と樹脂基板である第 2 固定基板とで素子形成層 (EL 素子含む) を挟んだ発光装置は、多少の応力が発生しても破損しない柔軟性 (フレキシビリティ) を有している。

【0229】

また、素子形成基板の厚さが非常に薄い、具体的には 50 μm ~ 300 μm、好ましくは 150 μm ~ 200 μm の厚さの基板を用いても、信頼性の高い発光装置を得ることができる。

【図面の簡単な説明】

【図 1】 基板貼り合わせ工程を示す図。

【図 2】 貼り合わせた基板の状態を示す図。

【図 3】 作製工程を示す図。

【図 4】 p チャネル型 TFT の作製工程を示す図。

【図 5】 n チャネル型 TFT の作製工程を示す図。

【図 6】 CMOS 回路を作製する工程を説明する図。

【図 7】 CMOS 回路を作製する工程を説明する図。

【図 8】 NMOS 回路の構成を示す図。

【図 9】 シフトレジスタの構成を示す図。

【図 10】 EL 表示装置の駆動回路及び画素部の断面構造図。

【図 11】 EL 表示装置の上面図及び断面図。

【図 12】 EL 表示装置の画素の上面図及び回路図。

【図 13】 デジタル駆動の EL 表示装置の回路ブロック図。

10

20

30

40

50

- 【図14】 E L表示装置の駆動回路及び画素部の断面構造図。

- 【図15】 E L表示装置の駆動回路及び画素部の断面構造図。

- 【図16】 E L表示装置の駆動回路及び画素部の断面構造図。

- 【図17】 ゲート側駆動回路の構成を示す図。

- 【図18】 デコーダ入力信号のタイミングチャートを説明する図。

- 【図19】 ソース側駆動回路の構成を示す図。

- 【図20】 ゲート側駆動回路の構成を示す図。

- 【図21】 デコーダ入力信号のタイミングチャートを説明する図。

- 【図22】 ソース側駆動回路の構成を示す図。

- 【図23】 曲率を与えた状態を示す図。

- 【図24】 電子機器の一例を示す図。

- 【図25】 電子機器の一例を示す図。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

〔 9 〕

【 図 1 0 】

【 図 1 1 】

【図12】

(A)

(B)

【図13】

【図14】

【図15】

【 図 1 6 】

【 図 1 7 】

【 図 1 9 】

【 図 20 】

〔 図 21 〕

【図22】

【図23】

【図24】

【図25】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 29/786 (2006.01)

H 01L 21/336 (2006.01)

(56)参考文献 特開2001-267578 (JP, A)

特開平11-026733 (JP, A)

特開昭63-107073 (JP, A)

特開2000-196243 (JP, A)

特開2000-243943 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/12

H01L 21/02

G09F 9/30-9/46

H01L 21/336

H01L 27/06

H01L 27/08

H01L 27/32

H01L 29/786