등록특허 10-2788661

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2025년03월28일

(11) 등록번호 10-2788661

(24) 등록일자 2025년03월26일

- (51) 국제특허분류(Int. Cl.)

*G03F 7/20* (2006.01) *G03F 7/00* (2006.01)

*H01L 21/027* (2006.01) *H01L 21/66* (2006.01)

- (52) CPC특허분류

*G03F 7/70616* (2023.05)

*G03F 7/0002* (2013.01)

- (21) 출원번호 10-2018-7031153

- (22) 출원일자(국제) 2016년11월04일

심사청구일자 2021년11월04일

- (85) 번역문제출일자 2018년10월26일

- (65) 공개번호 10-2018-0123156

- (43) 공개일자 2018년11월14일

- (86) 국제출원번호 PCT/US2016/060626

- (87) 국제공개번호 WO 2017/176314

국제공개일자 2017년10월12일

- (30) 우선권주장

62/318,086 2016년04월04일 미국(US)

- (56) 선행기술조사문현

JP2006048067 A\*

(뒷면에 계속)

전체 청구항 수 : 총 15 항

심사관 : 정성용

## (54) 발명의 명칭 필 팩터 변조에 의한 공정 호환성 개선

## (57) 요 약

계측 타겟 및 타겟 설계 방법이 제공되며, 여기서 타겟 요소는 단일 피치로서 피치 p를 유지하는 복합 주기적 구조물을 형성하기 위해, 피치 p를 갖는 주기적 패턴의 요소를, 상기 요소와는 적어도 하나의 기하학적 차이를 갖는 보조 요소로 대체함으로써 정의된다. 진보된 다중 패터닝 기술과의 호환성의 범위 내에서 타겟을 구성하는 것은 타겟의 충실도를 향상시키고, 필 팩터 변조는 타겟의 공정 호환성을 달성하면서 오버레이를 추출하기 위한 충분한 계측 감도를 생성하도록 타겟의 조정을 가능하게 한다.

대 표 도 - 도3a

(52) CPC특허분류

*G03F 7/70633* (2023.05)

*H01L 21/0274* (2013.01)

*H01L 22/12* (2013.01)

(72) 발명자

**이츠코비치 탈**

이스라엘 99735 크파 유리야 크파 유리야 #10

**아하론 샤론**

이스라엘 1796000 하나톤 유발 40

**아델 마이클 이**

이스라엘 30900 야아코브 지크론 이갈 알론 스트리트 14

**파스코버 유리**

이스라엘 38900 카에사레아 스코햄 스트리트 10

**네그리 다리아**

이스라엘 하이파 예헤츠텔 코이프만 스트리트 10/3

**루바쉐브스키 유발**

이스라엘 하이파 스몰른스킨 스트리트 22

**마나센 암논**

이스라엘 34892 하이파 골다 메이어 10

**이 명준**

미국 캘리포니아주 95134 산 호세 리버 옥스 플래

이스 55 아파트먼트 429

**스미스 마크 디**

미국 캘리포니아주 95125 산 호세 코흐 래인 1596

(56) 선행기술조사문현

JP2006293081 A\*

WO2016030255 A2\*

WO2015109036 A1

US20150268564 A1

\*는 심사관에 의하여 인용된 문현

## 명세서

### 청구범위

#### 청구항 1

타겟 설계 방법으로서,

단일 피치로서 피치 p를 유지하는 복합 주기적 구조물을 형성하기 위해, 상기 피치 p를 갖는 주기적 패턴의 요소(elements)를, 상기 요소와는 적어도 하나의 기하학적 차이(geometric difference)를 갖는 보조 요소로 대체함으로써 타겟 요소를 정의하는 단계;

복수의 상기 복합 주기적 구조물로부터 계측 오버레이 이미징 타겟을 설계하는 단계; 및

모델 디바이스에 대한 상기 타겟의 회절 패턴의 근접 매칭(close match)을 얻도록 상기 타겟 요소 간의 공간 및 상기 피치 p 중 적어도 하나를 조정하는 단계

를 포함하는 타겟 설계 방법.

#### 청구항 2

타겟 설계 방법으로서,

단일 피치로서 피치 p를 유지하는 복합 주기적 구조물을 형성하기 위해, 상기 피치 p를 갖는 주기적 패턴의 요소(elements)를, 상기 요소와는 적어도 하나의 기하학적 차이(geometric difference)를 갖는 보조 요소로 대체함으로써 타겟 요소를 정의하는 단계;

복수의 상기 복합 주기적 구조물로부터 계측 오버레이 이미징 타겟을 설계하는 단계; 및

모델 디바이스에 대한 상기 타겟의 회절 패턴의 근접 매칭을 얻도록 구성된 보조 요소를 상기 복합 주기적 구조물에 추가하는 단계

를 포함하는 타겟 설계 방법.

#### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 적어도 하나의 기하학적 차이는 임계 치수인 것인, 타겟 설계 방법.

#### 청구항 4

제 1 항 또는 제 2 항에 있어서,

금지된 리소그래피 피치를 피하기 위해 상기 타겟 요소 간의 공간 및 상기 피치 p 중 적어도 하나를 조정하는 단계를 더 포함하는, 타겟 설계 방법.

#### 청구항 5

제 1 항에 있어서,

상기 타겟 요소의 예지 배치를 설계하기 위해 리소그래피 시뮬레이션을 사용하는 단계를 더 포함하는, 타겟 설계 방법.

#### 청구항 6

제 1 항에 있어서,

적어도 하나의 컴퓨터 프로세서에 의해 수행되는 것인, 타겟 설계 방법.

#### 청구항 7

제 1 항 또는 제 2 항의 방법에 따라 복합 주기적 타겟 구조물을 제조하는 방법.

#### 청구항 8

제 7 항의 방법에 따라 복합 주기적 타겟 구조물을 복수 개 포함하는 계측 오버레이 이미징 타겟을 제조하는 방법.

#### 청구항 9

제 1 항 또는 제 2 항의 방법을 수행하도록 구성된 컴퓨터 판독 가능 프로그램이 구현되어 있는 비일시적 컴퓨터 판독 가능 저장 매체.

#### 청구항 10

복수의 복합 주기적 타겟 구조물을 포함하는 계측 타겟으로서,

상기 복수의 복합 주기적 타겟 구조물 각각은, 적어도 하나의 기하학적 피처가 상이하고 단일 피치 p로 배치되어 복합 주기적 타겟 구조물을 형성하는 타겟 요소 및 보조 요소를 포함하고,

모델 디바이스에 대한 타겟 설계의 회절 패턴의 근접 매칭(close match)을 얻도록 상기 타겟 요소 간의 공간 및 상기 피치 p 중 적어도 하나가 조정된 것인, 계측 타겟.

#### 청구항 11

복수의 복합 주기적 타겟 구조물을 포함하는 계측 타겟으로서,

상기 복수의 복합 주기적 타겟 구조물 각각은, 적어도 하나의 기하학적 피처가 상이하고 단일 피치 p로 배치되어 복합 주기적 타겟 구조물을 형성하는 타겟 요소 및 보조 요소를 포함하고,

상기 복합 주기적 타겟 구조물은 모델 디바이스에 대한 타겟 설계의 회절 패턴의 근접 매칭을 얻도록 구성된 적어도 하나의 보조 요소를 포함하는 것인, 계측 타겟.

#### 청구항 12

제 10 항 또는 제 11 항에 있어서,

상기 적어도 하나의 기하학적 피처는 임계 치수인 것인, 계측 타겟.

#### 청구항 13

제 10 항 또는 제 11 항에 있어서,

상기 타겟 요소 간의 공간 및 상기 피치 p 중 적어도 하나는 금지된 리소그래피 피치를 피하기 위해 조정되는 것인, 계측 타겟.

#### 청구항 14

제 10 항 또는 제 11 항에 따른 계측 타겟을 제조하는 방법으로서, 상기 타겟 요소의 에지 배치는 리소그래피 시뮬레이션을 사용하여 설계되는 것인, 계측 타겟 제조 방법.

#### 청구항 15

제 10 항 또는 제 11 항에 따른 계측 타겟으로부터 다중 패터닝에 의해 획득되는 타겟을 제조하는 방법.

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

## 발명의 설명

### 기술 분야

[0001]

관련 출원에 대한 상호 참조

[0002]

본 출원은 2016년 4월 4일자에 출원된 미국 가특허 출원 제62/318,086호의 우선권을 주장하며, 상기 출원의 전체 내용은 참조에 의해 본 명세서에 통합된다.

[0003]

기술분야

[0004]

본 발명은 계측 분야에 관한 것으로, 특히 오버레이 계측 타겟 설계에 관한 것이다.

### 배경 기술

[0005]

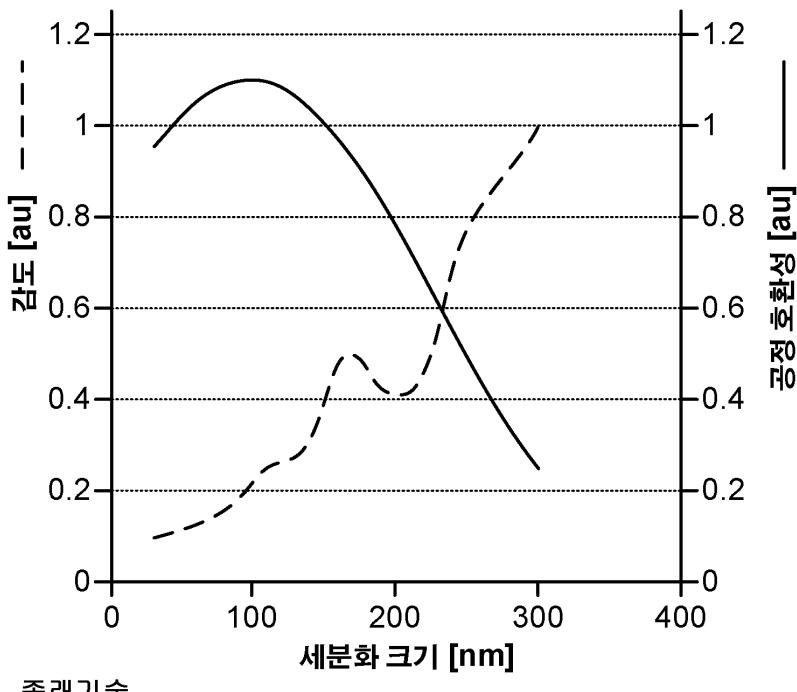

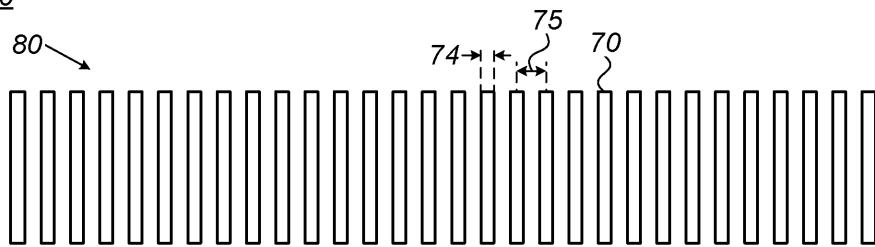

오버레이 계측 구조물은 한편으로는 상충하는 계측 감도 요구 사항을 충족시켜야 하며, 다른 한편으로는 제조 가능성 또는 공정 호환성을 충족시켜야 한다. 이에 상응하여, 예시로서, 도 1a는 종래 기술에 따라, 타겟 구조물의 세분화(segmentation) 크기와 관련하여 타겟 설계의 공정 호환성과 감도 간의 트레이드 오프를 개략적으로 나타낸다.

[0006]

일반적으로, 통합 방식의 최소 피치는 계측 센서에 대해 최적화된 계측 구조물의 소위 조대 피치(coarse pitch)보다 상당히 작다. 조대 피치의 하한은 전형적으로 주어진 조명 파장에 대해, 최소 두 개의 회절 차수가 센서 수집 광학기에 의해 수집되도록 요구되는 요구 사항에 의해 설정된다. 또한, 많은 경우에, 최소 조명 파장은 계측 타겟의 현재 총 격자와 이전 총 격자 사이의 중간 총의 짧은 파장에서의 불투명도에 의해 염매여 있다. 예를 들어, 최소 인쇄 가능 리소그래피 피치는 100nm일 수 있는 반면, 오버레이 타겟의 조대 피치는 대략 2000nm일 수 있다.

[0007]

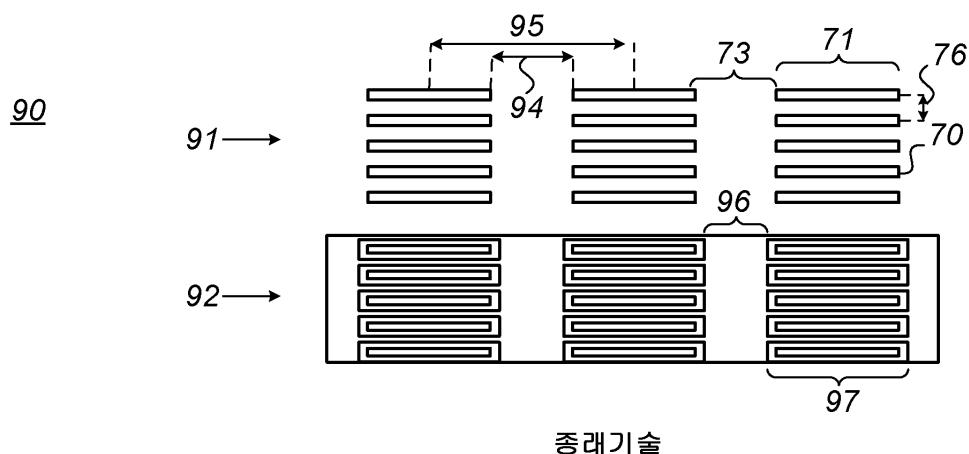

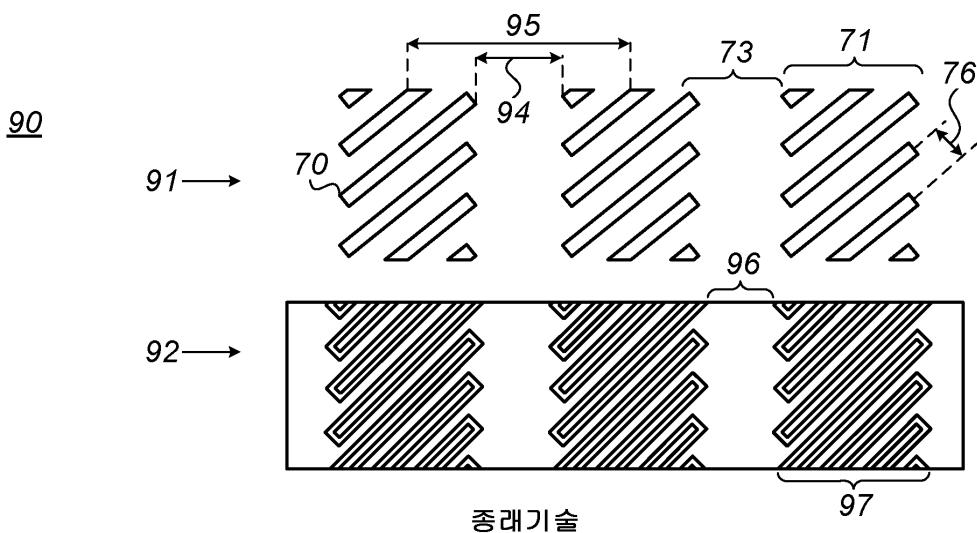

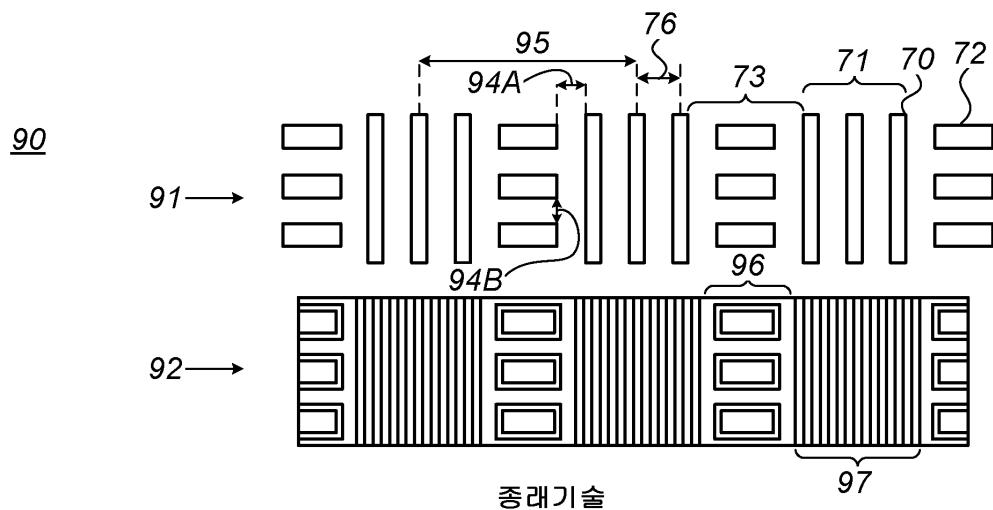

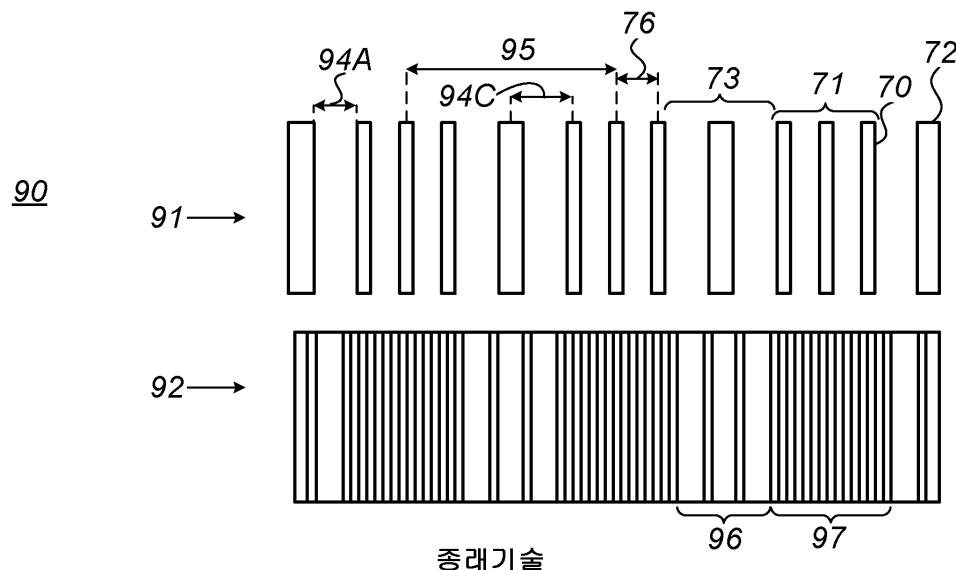

공정 호환성을 달성하기 위한 종래의 방법은 세분화 크기(계측 타겟의 미세 피치)를 특정 총의 최소 설계 규칙 피치의 도메인으로 감소시키는 것이다. 세분화 크기가 제조 공정이 최적화된 최소 설계 규칙의 크기에 접근함에 따라, 센서가 합당한 불확실성의 범위 내에서 오버레이를 추출할 수 없는 수준으로 감도가 감소하기 때문에, 이 접근법에는 고유의 트레이드 오프가 있다. 도 1b, 도 1c 및 도 1d에 각각 예시된 바와 같이, 이러한 고유의 트레이드 오프를 고려하여 타겟을 최적화하기 위해, 타겟 구조물의 평행, 직각 또는 심지어 대각선 세분화와 같은 다양한 종래 기술의 타겟 설계가 제안되었다.

[0008]

최근의 반도체 제조 노드에서, 자기 정렬 이중 및 사중 패터닝이 극자외선 또는 다른 고급 패터닝 방식에 대한 실용적이고 중요한 대안으로 떠오르고 있어 점점 더 조밀하고 작은 피치를 가능하게 하고 있다. 이 방법에서, 더욱 타이트한 피치를 인쇄할 수 있는 능력은 인쇄할 수 있는 것과 인쇄할 수 없는 것에 대한 제한이 매우 타이트한 복잡한 통합 방식에 의해 가능하게 된다.

[0009]

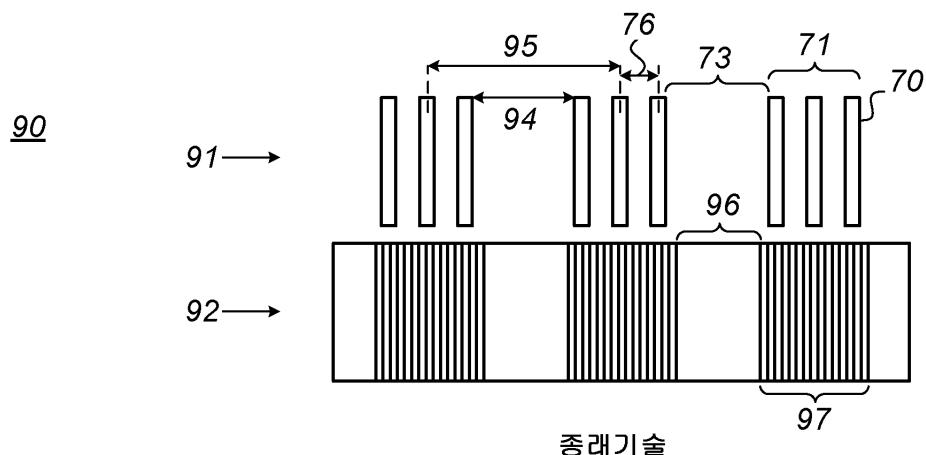

도 1b, 도 1c 및 도 1d는 종래 기술에 따라, 각각 타겟 구조물의 평행, 직각 및 대각선 세분화 방식(90)을 개략적으로 도시한다. 도 1b, 도 1c 및 도 1d는 GDS 마스크 방식(91) 및 온 웨이퍼 방식(92)으로서 세분화 방식(90)(스페이서는 사중 패터닝 병렬 세분화를 지원함)을 도시한다. 타겟 요소는 미세 세분화 피치(76) 및 조대 세분화 피치(95)를 갖는 세분화 요소(70)를 포함하고, 타겟 요소로 구성된 인접한 세분화된 구조물 사이에 공간(94)이 있다. 타겟 구조물은 세분화된 구조물(71)과 이들 사이의 캡(73)을 포함하며, 이들은 대응하는 구조물(97) 및 캡(96)으로 인쇄된다. 그러나 이러한 종래 기술 방법은 전형적으로, 예를 들어, SADP(self-aligned

double patterning; 자기 정렬 이중 패터닝) 또는 SAQP(self-aligned quadruple patterning; 자기 정렬 사중 패터닝) 통합 방식으로 인해, 다중 패터닝 방식에서 설계 규칙 위반을 초래한다.

[0010] (가시광을 사용하는) 측정 툴의 광학적 제한 때문에, 광학 해상도를 준수하고 라인과 공간 사이의 콘트라스트를 유도하기 위해, 바(97) 사이에 최소 공간(96)이 유지되어야 한다. 큰 공간(96)은 타겟의 공정 호환성에 영향을 줄 수 있으며, 따라서 타겟 성능 및 디바이스 대 타겟 유사성을 감소시킨다. 이 문제를 극복하기 위해, 공정 호환성과 콘트라스트를 트레이드 오프하는 CMP(chemical mechanical processing; 화학적 기계적 처리) 보조 피처가 도입되었다.

[0011] 도 1e 및 도 1f는 종래 기술에 따라, CMP 보조 피처(72)를 갖는 세분화 방식(90)을 개략적으로 도시한다. 도 1e 및 도 1f는 GDS 마스크 방식(91) 및 온 웨이퍼 방식(92)으로서 세분화 방식(90)(스페이서는 사중 패터닝 별별 세분화를 지원함)을 도시한다. CMP 보조 피처(72)는 공간(73) 내에 존재하는 세분화된 피처로서, 유효 공간(피처 없는 영역)을 감소시킨다. 바(71)와 공간(73) 사이의 구별을 유지하기 위해, CMP 보조 피처(72)의 세분화는 계획적으로 바(71)의 세분화와 본질적으로 상이하다. 차이점은 도 1e에 개략적으로 도시된 상이한 세분화 방향 및 도 1f에 개략적으로 도시된 설계 규칙과의 의도적 비호환성(최소 설계 규칙의 두 배 정도)(피치(94C) ≫ 피치(76))을 포함할 수 있다. 또한, 리소그래피 공정의 제한으로 인해 (인쇄 가능성을 손상시키는 근접 효과 문제를 피하기 위해), 최소 세분화 간격과는 상이한 공간(94A)뿐만 아니라 CMP 보조 피처(72) 사이의 공간(94B)이 세분화 요소(70)와 CMP 보조 요소(72) 사이에서 유지된다(보통, 공간(94A) ≫ 피치(76)).

### 발명의 내용

[0012] 다음은 본 발명의 초기 이해를 제공하는 간략한 요약이다. 상기 요약은 반드시 핵심 요소를 식별하는 것도 아니며 본 발명의 범위를 제한하는 것도 아니라, 단지 다음의 설명을 소개하기 위한 것이다.

[0013] 본 발명의 일 양태는, 단일 피처로서 피치 p를 유지하는 복합 주기적 구조물을 형성하기 위해, 피치 p를 갖는 주기적 패턴의 요소를, 상기 요소와는 적어도 하나의 기하학적 차이를 갖는 보조 요소로 대체함으로써 타겟 요소를 정의하는 단계를 포함하는 타겟 설계 방법을 제공한다.

[0014] 본 발명의 이들, 추가의, 및/또는 다른 양태 및/또는 장점을 다음의 상세한 설명에 기재되고, 상세한 설명으로부터 추론할 수 있으며 및/또는 본 발명의 실시에 의해 학습 가능하다.

### 도면의 간단한 설명

[0015] 본 발명의 실시예를 더 잘 이해하고 그 실시예가 실시될 수 있는 방법을 나타내기 위해, 이제 첨부 도면을 순전히 예로서 참조할 것이며, 첨부 도면에서 동일한 도면 부호는 전체에 걸쳐 대응하는 요소 또는 섹션을 나타낸다.

첨부 도면에서,

도 1a는 종래 기술에 따라, 타겟 구조물의 세분화 크기와 관련하여 타겟 설계의 공정 호환성과 감도 간의 트레이드 오프를 개략적으로 나타낸다.

도 1b, 도 1c 및 도 1d는 종래 기술에 따라, 각각 타겟 구조물의 평행, 직각 및 대각선 세분화 방식을 개략적으로 도시한다.

도 1e 및 도 1f는 종래 기술에 따라, CMP 보조 피처를 갖는 세분화 방식을 개략적으로 도시한다.

도 2a 및 도 2b는 본 발명의 일부 실시예에 따라, 타겟 설계 방법에 의해 유도된 복합 주기적 타겟 구조물 설계의 하이 레벨 개략도이다.

도 2c는 본 발명의 일부 실시예에 따라, 미세 피치 선택의 하이 레벨 개략도이다.

도 3a 내지 도 3d는 본 발명의 일부 실시예에 따라, 디바이스, 종래 기술의 타겟 및 개시된 타겟 설계 간의 비교의 개략도이다.

도 4는 본 발명의 일부 실시예에 따라, 방법을 도시하는 하이 레벨 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0016] 상세한 설명을 기재하기 전에, 이후에 사용될 특정 용어의 정의를 기재하는 것이 도움이 될 수 있다.

- [0017] 본 출원에서 사용된 "요소", "타겟 요소" 및 "보조 요소"라는 용어는 설계 단계, 레티클, 레지스트, 다양한 생산 단계 및 결과 타겟과 같은 임의의 생산 단계에서의 계측 타겟 부분, 특히 이미징 타겟을 나타낸다. 전형적으로, 계측 타겟은 본 발명이 나타내는 반복 요소를 갖는 주기적 구조물을 포함한다. 예를 들어, 타겟 요소는 웨이퍼로 타겟 설계를 전사하는데 사용되는 레티클 상에 있을 수 있다. 다양한 생산 단계에서의 타겟의 물리적 특성이 상이하지만, 개시된 설계 원리 및 결과적인 구조물은 임의의 특정 생산 단계에 한정되지 않으며, 사용된 리소그래피 기술에 의해 링크된 임의의 생산 단계와 관련하여 적용될 수 있음을 명시적으로 언급한다. 유사한 설계 원리 및 타겟 요소 설계가 스캐터로메트리 타겟에 사용될 수 있고, 개시된 발명은 타겟 설계의 적절한 수정과 함께 스캐터로메트리 타겟뿐만 아니라 이미징 타겟에도 적용 가능하다는 것이 강조된다.

- [0018] 이하의 설명에서, 본 발명의 다양한 양태가 설명된다. 설명을 위해, 특정 구성 및 세부 사항이 본 발명의 완전한 이해를 제공하기 위해 기재된다. 그러나 본 발명이 본 명세서에 제공된 특정 세부 사항 없이 실시될 수 있다는 것이 당업자에게 또한 명백할 것이다. 또한, 잘 공지된 피처는 본 발명을 모호하게 하지 않기 위해 생략되거나 단순화될 수 있다. 도면을 구체적으로 참조하면, 도시된 상세한 사항은 단지 예일 뿐 본 발명의 예시적인 설명을 위한 것이며, 본 발명의 원리 및 개념적 측면의 가장 유용하고 쉽게 이해되는 설명인 것으로 여겨지는 것을 제공하기 위해 제시된다는 점이 강조된다. 이와 관련하여, 본 발명의 근본적인 이해를 위해 필요한 것보다 본 발명의 구조적 세부 사항을 보다 상세하게 나타내려는 시도는 없으며, 도면과 함께 취해진 설명은 본 발명의 몇몇 형태가 실제로 구현될 수 있는 방법을 당업자에게 명백하게 한다.

- [0019] 본 발명의 적어도 하나의 실시예가 상세하게 설명되기 전에, 본 발명은 그 적용에 있어서 이하의 설명에 기재되거나 도면에 도시된 구성 요소의 구성 및 배열의 세부 사항으로 한정되지 않는다는 것을 이해해야 한다. 본 발명은 개시된 실시예들의 조합뿐만 아니라 다양한 방식으로 실시되거나 수행될 수 있는 다른 실시예들에 적용 가능하다. 또한, 본 명세서에 사용되는 표현 및 용어는 설명을 위한 것이며, 제한적인 것으로 간주되어서는 안 된다는 것을 이해해야 한다.

- [0020] 특별히 다르게 언급되지 않는 한, 다음의 설명으로부터 명백한 바와 같이, 본 명세서 전반에 걸쳐, "프로세싱", "컴퓨팅", "계산", "결정", "강화" 등과 같은 용어를 사용하는 설명은 컴퓨팅 시스템의 레지스터 및/또는 메모리 내의 전자와 같은 물리적인 양으로서 표현된 데이터를 컴퓨팅 시스템의 메모리, 레지스터 또는 다른 이러한 정보 저장, 전송 또는 디스플레이 디바이스 내의 물리적인 양으로 유사하게 표현된 다른 데이터로 조작 및/또는 변환하는 컴퓨터 또는 컴퓨팅 시스템 또는 유사한 전자 컴퓨팅 디바이스의 동작 및/또는 프로세스를 나타낸다는 것이 이해된다.

- [0021] 본 발명의 실시예는 계측 타겟 설계를 개선 및 최적화하여 계측 기술 분야에 개선을 제공하고, 특히 측정 정확도와 타겟 인쇄 가능성 사이의 트레이드 오프를 최적화하는 오버레이 이미징 및/또는 스캐터로메트리 계측 타겟을 제공하기 위한 효율적이고 경제적인 방법 및 메커니즘을 제공한다.

- [0022] 본 발명자들은 오버레이 계측 타겟의 충실도가 자기 정렬 이중 및 사중 패터닝(각각, SADP 및 SAQP)과 같은 진보된 패터닝 기술과의 호환성 범위 내에서 보다 엄격하게 타겟을 구성함으로써 개선될 수 있다는 것을 발견하였지만, 이는 본 발명을 제한하는 것으로 이해되어서는 안 된다. 공정 호환성은 이 호환성을 기반으로 필 팩터 변조로 개선될 수 있다. 종래 기술(예를 들어, 도 1b 내지 도 1f에 도시된 바와 같음)과 관련하여, 개시된 실시예는 이러한 복잡한 통합 방식의 범위 내에 있지만 합당한 불확실성의 범위 내에서 오버레이의 추출을 가능하게 하는 충분한 계측 감도를 생성하는 계측 타겟 설계를 제공한다.

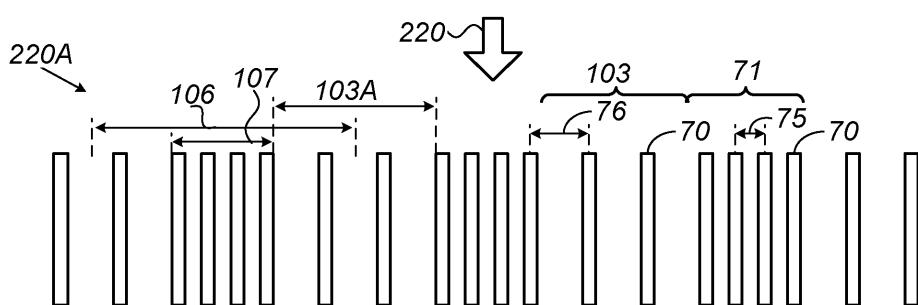

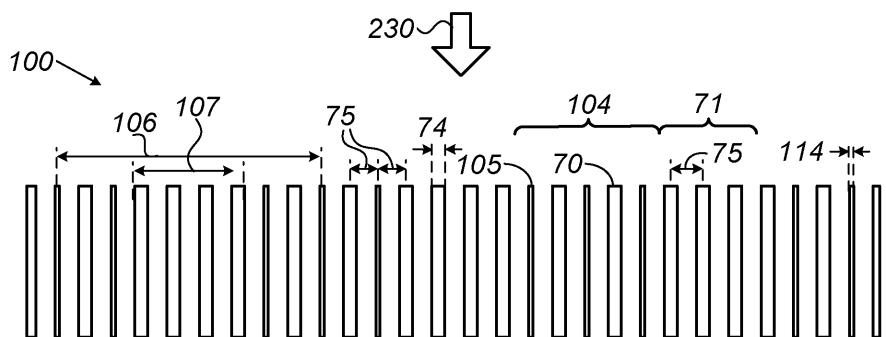

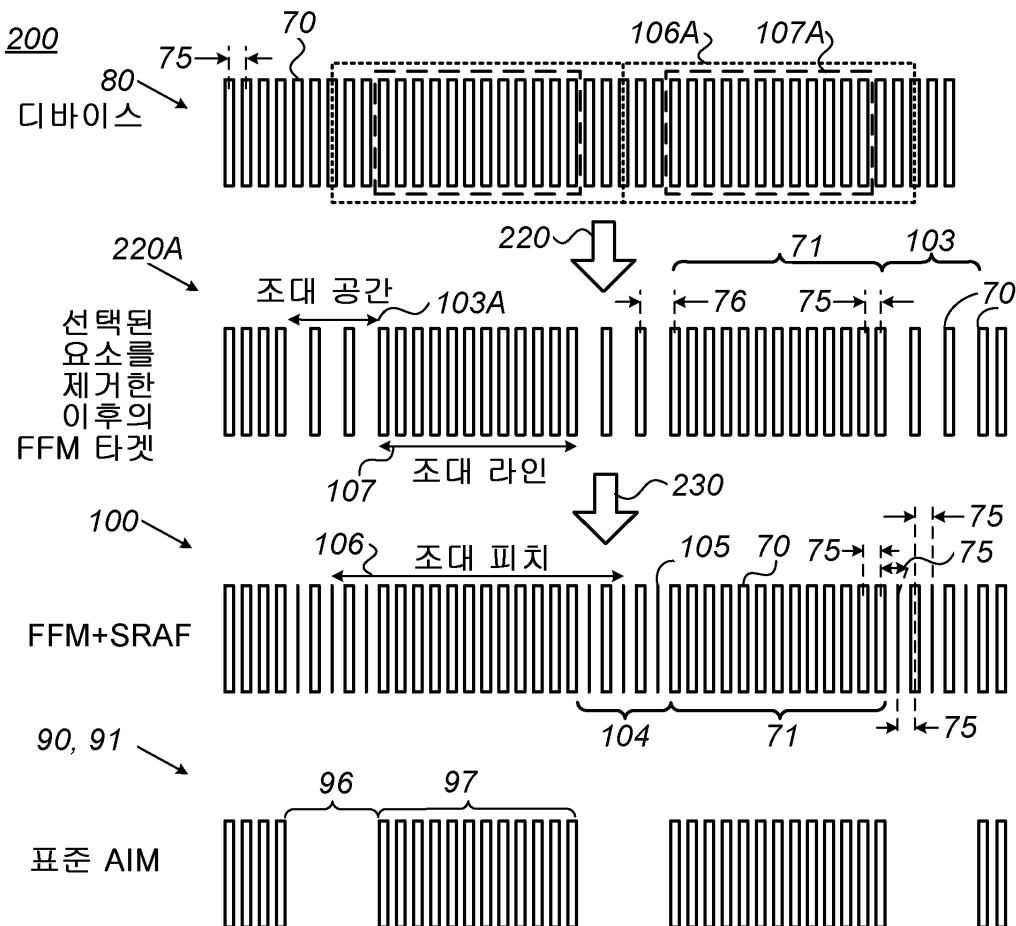

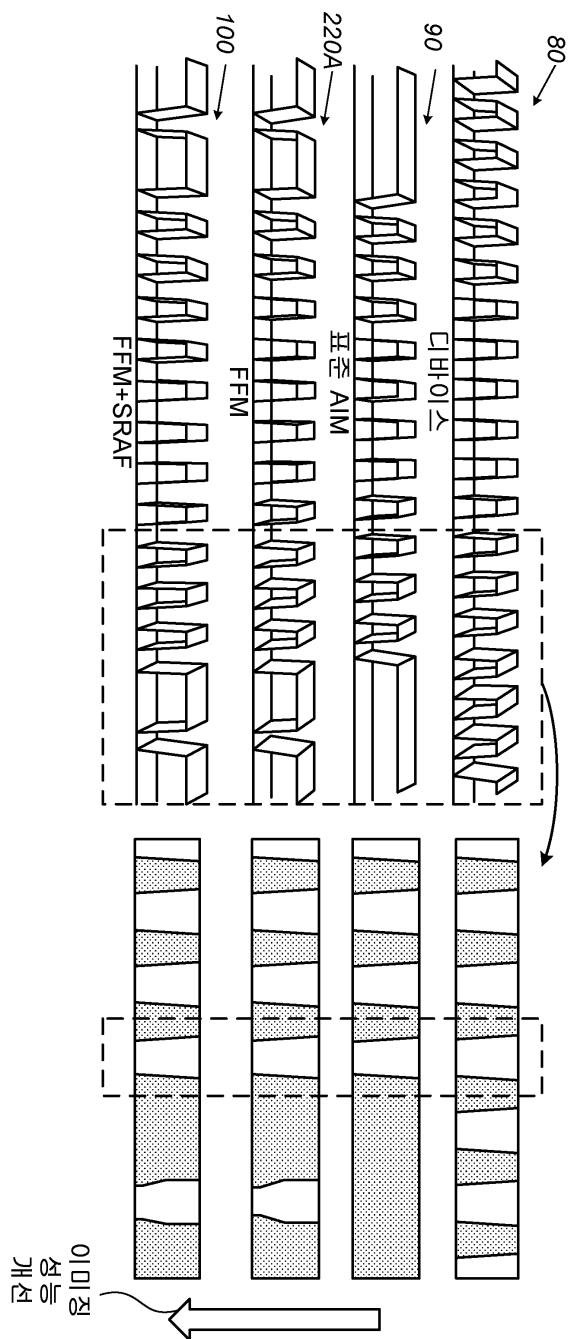

- [0023] 도 2a 및 도 2b는 본 발명의 일부 실시예에 따라, 타겟 설계 방법(200)에 의해 유도된 복합 주기적 타겟 구조물 설계(100)의 하이 레벨 개략도이다. 도 2a 및 도 2b는 명시야 마스크로서 스페이서 보조 사중 패터닝 필 팩터 변조(fill factor modulation; FFM) 세분화 방식을 개략적으로 도시하고, 요소(70)는 인쇄된 요소를 나타낸다.

- [0024] 방법(200)은 피치(75)(피치 p, 예를 들어 100nm의 스케일)로 요소(70)를 반복하는 것으로 구성된 주기적 구조물(80)(일반적인 디바이스 설계를 나타냄)로부터 시작하며, 이는 기본 그리드를 정의한다(요소(70)는 임계 치수(critical dimension; CD)(74)를 가짐). 이 시작점은 세분화된 주기적 구조물(90)로부터 시작하며 세그먼트(71) 사이의 갭(94)을 채우려고 시도하는 도 1b 내지 도 1f에 도시된 바와 같은 종래 기술과는 상이하다. 대조적으로, 본 발명에서는 구조물(105)의 단일 피치로서 피치(75)(동일한 피치 p)를 유지하는 복합 주기적 구조물(100)을 형성하기 위해, 주기적 패턴(80)의 요소(70)를 상기 요소와 적어도 하나의 기하학적 차이를 갖는 보조 요소(105)로 대체하여 타겟 요소(71)를 정의하고, 타겟 설계(100)에 도달한다.

- [0025] 대체는 장래의 갭(103)으로부터 요소(70)의 적어도 일부를 제거하여 이에 의해 중간 구조물(220A)에 피치(75)보

다 큰 캡(76)을 생성하는 단계(220), 및 구조물(100)에서 단일 피치 p로서 피치(75)를 재화립하기 위해 보조 요소(105)로 캡(76)을 채우는 단계(230)를 포함하는 것으로 보여질 수 있다. 따라서, 타겟 요소(71)는 동일한 기하학적 피처를 갖고 피치 p로 있는 요소(70)의 영역을 포함하고, 캡(104)은 동일한 피치 p를 유지하면서 상이한 기하학적 피처를 갖는 보조 요소(105)의 영역을 포함한다. 도 2b에 도시된 바와 같이, 결과적인 복합 주기적 구조물(100)은 조대 라인(107)을 제공하는 유닛(107A) 및 조대 피치(106)(예를 들어, 2000nm의 스케일)로 반복되는 베이스 유닛(106A)으로서 타겟 요소(71)를 가지며, 이는 충분히 커서 광학 해상도를 제공하고, 미세 피치(75)는 인쇄 가능성을 제공한다. 요소(70)와 보조 요소(105) 간의 기하학적 피처의 차이는 임계 치수(CD)일 수 있으며, 예를 들어, 보조 요소(105)는 요소(70)보다 좁을 수 있고 더 작은 보조 요소 CD(114) < 타겟 요소 CD(74)를 가질 수 있다.

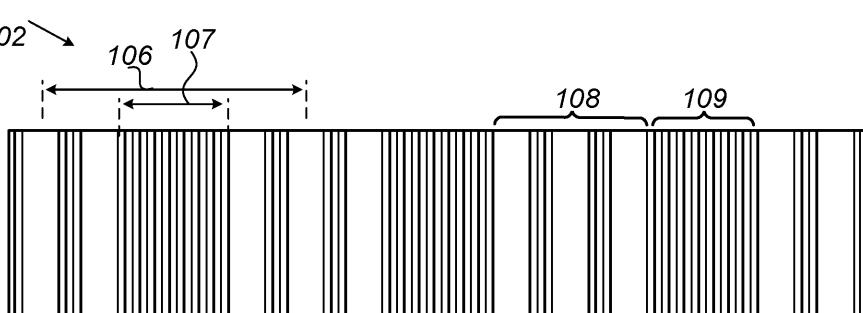

[0026] 결과적인 타겟(102)은 캡(108)과 충분히 구별되므로 (조대 라인(107) 및 조대 피치(106)로) 필요한 광학 해상도를 제공하는 타겟 요소(109)를 갖고, 타겟 설계(100)의 피치 p는 인쇄 문제로 인한 부정확성을 피하기 위해 설계 규칙을 준수한다.

[0027] 적어도 하나의 기하학적 피처가 상이하고 복합 주기적 타겟 구조물을 형성하기 위해 단일 피치 p로 배치되는 타겟 요소(71) 및 보조 요소(105)를 포함하는 복합 주기적 타겟 구조물 설계(100)는 풀 스케일 계측 타겟 설계를 위한 빌딩 블록으로 사용될 수 있으며, (표준 AIM, 고급 이미징 계측, 타겟 설계로 도 2b에서 예시된 바와 같이) 종래 기술 설계(90, 91)의 일부 또는 전부를 대체하기 위해 설계(100)를 사용할 수 있다.

[0028] 본 발명의 실시예는 종래 기술의 단점을 극복한다. 도시된 실시예는 비 제한적인 방식으로 자기 정렬 이중 및 사중 패터닝(각각, SADP 및 SAQP)과 관련하여 일반적으로 설명되며, 다른 통합 방식에도 역시 적용될 수 있다. 본 발명은 광학 해상도(2000nm의 스케일의 조대 피치를 필요로 함) 대 타겟 인쇄 가능성(100nm의 스케일의 미세 피치를 필요로 함)의 트레이드 오프 문제에 대한 새로운 해결책으로서 필 팩터 변조를 개시한다. 본 발명은 미세 피치(75)로 디바이스 세분화 격자 (또는 포토 리소그래피 및 제조 공정과 호환 가능한 미리 정의된 주기성)를 따르는 고밀도 아키텍쳐 설계를 개시하며, 여기서 반복 요소(70)의 일부는 완전히 제거되거나 또는 SRAF(sub-resolution assist feature; 서브 해상도 보조 피처) 요소(105)로 대체된다. 타겟 당 제거된 요소의 수와 위치는 특정 타겟 스택에 대해 최적화될 수 있다.

[0029] 도 2c는 본 발명의 일부 실시예에 따라, 미세 피치 선택의 하이 레벨 개략도이다. 피치(75)는 각각의 패터닝 공정에 따라 선택될 수 있으며, 특히 마스크에 SRAF 요소(105)의 도입은 스캐너 수차로 인한 인쇄된 패턴(102)과 디바이스 사이의 오프셋을 감소시키는 디바이스 피치(75)로 마스크 패턴(100)의 주기성을 지원할 수 있다.

[0030] 특정 실시예에서, 타겟 구조물(100)은 정렬시 공통 대칭 중심을 공유하도록 구성된 다수의 타겟 구조물(71)을 포함할 수 있으며, 각각의 타겟 구조물(71)은 방향 당 적어도 2개의 패턴 요소를 포함한다. 패턴 요소는 특정 패터닝 공정의 주기성과 일치하는 세분화 그리드 상의 위치에 제한되는 피처를 포함한다. 피처 존재 대 피처 부재의 필 팩터는 계측 센서에 의해 검출될 수 있는 주기성으로 콘트라스트를 생성하도록 조정될 수 있다.

[0031] 도 2a 내지 도 2c의 요소는 임의의 동작 가능한 조합으로 결합될 수 있고, 특정 도면에는 있지만 다른 도면들에는 없는 특정 요소의 예시는 단지 설명을 목적으로 제공되며 비 제한적이다.

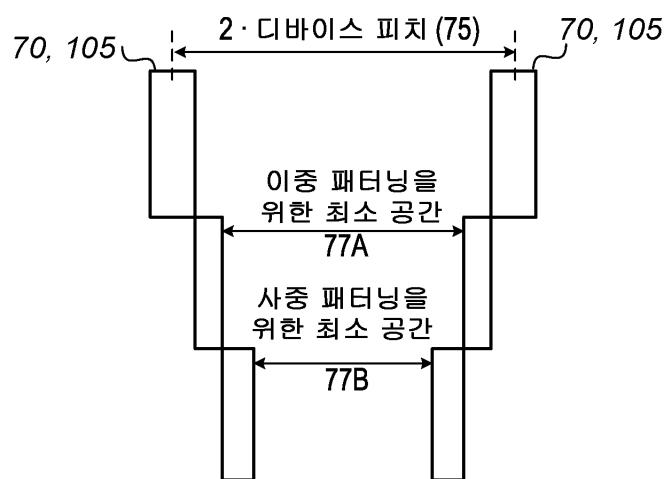

[0032] 제안된 접근법에 따라, 이중 및 사중 패터닝을 위한 최소 개방 공간 폭이 다음의 비 제한적인 예에서 정의된다. 이중 패터닝의 경우, 90nm의 리소그래피 피치(75)에 대한 최소 개방 공간 폭(77A)은  $3*45\text{nm} - 15\text{nm} = 120\text{nm}$ 인 반면, 사중 패터닝의 경우 최소 개방 공간 폭(77B)은  $5*22.5\text{nm} - 7\text{nm} \approx 105\text{nm}$ 이다. 이 최소 공간 폭은 조대 피치(106) 내에서 비주기적 세분화를 사용함으로써 더욱 감소될 수 있다. 인쇄된 패턴으로 남아 있는 개방 공간(77A, 77B)은 타겟 콘트라스트와 타겟의 공정 호환성 간의 트레이드 오프이다. 편광 또는 암시야 계측 또는 다른 콘트라스트 항상 광학 방식의 사용은 리소그래피 디바이스 피치(75) 아래의 개방 공간(77A, 77B)의 최대 폭의 감소를 허용할 수 있다.

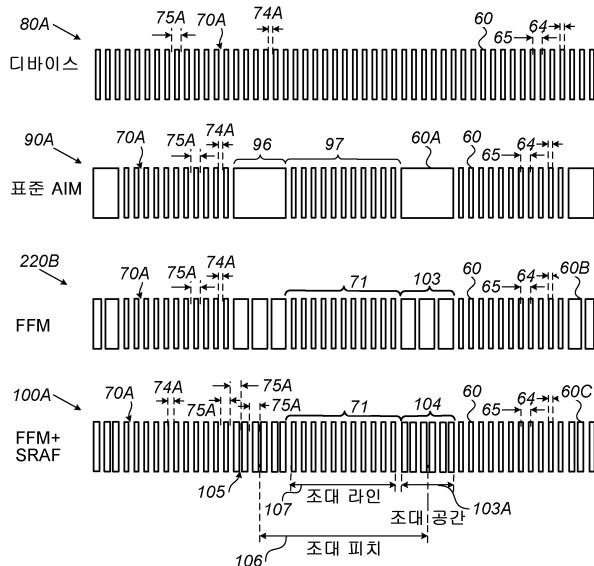

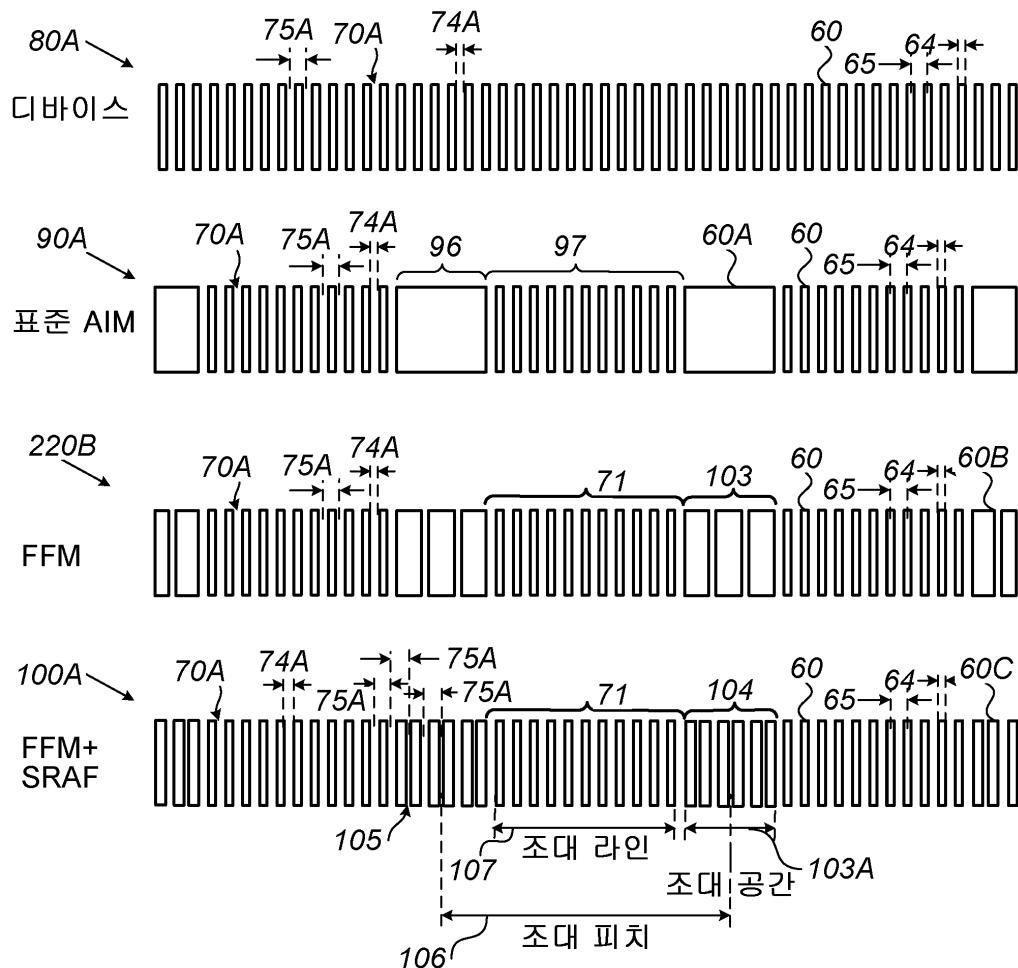

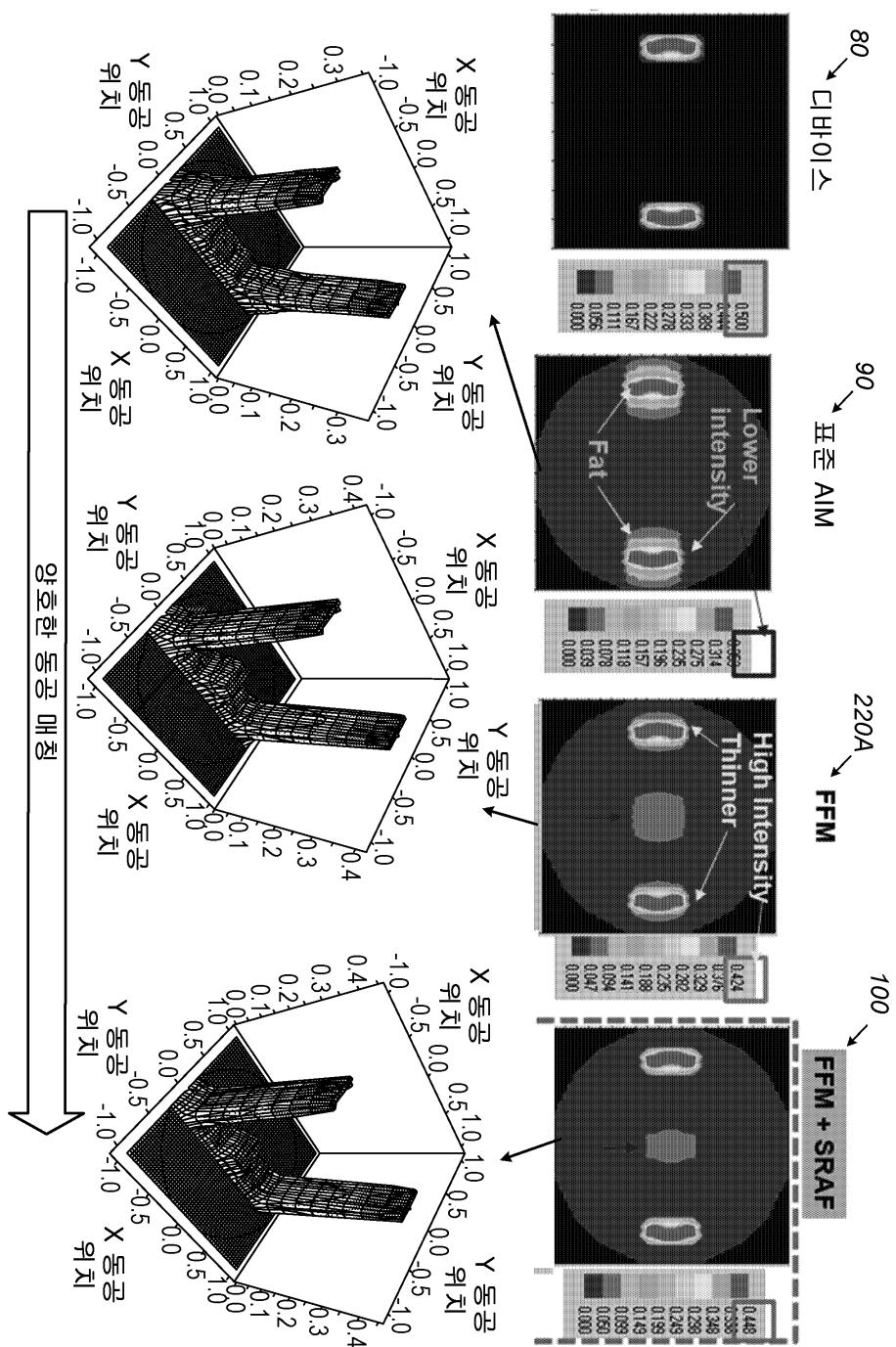

[0033] 도 3a 내지 도 3d는 본 발명의 일부 실시예에 따라, 디바이스, 종래 기술의 타겟 및 개시된 타겟 설계 간의 비교의 개략도이다. 비교는 개시된 타겟 설계(100)의 장점 및 앞에서 설명된 트레이드 오프와 관련하여 타겟 설계(100)를 최적화하는 방법을 비 제한적 방식으로 도시한다. 도 3a는 디바이스(80A)(디바이스(80)에 대응함), 표준 AIM 타겟(90A)(표준 AIM 타겟(90)에 대응함), FFM 타겟 요소(220B)(FFM 타겟(220A)에 대응함) 및 SRAF를 갖는 FFM 타겟 설계(100A)(SRAF를 갖는 FFM 타겟 설계(100)에 대응함)에 대한 각각의 마스크들을 개략적으로 도시한다. 마스크는 마스크의 레티를 내의 광 차단 (예를 들어, 크롬) 영역을 나타내는 요소(60, 60A, 60B, 60C)를 갖는 오버레이 타겟에 일반적으로 사용되는 암시야 마스크를 개략적으로 나타낸다.

- [0034] 도 3a는 본 발명의 일부 실시예에 따라, 타겟 설계 테스트에 사용된 예시적인 디바이스 마스크(80A), 표준 AIM 타겟 마스크(90A), 필 팩터 변조(FFM) 타겟 마스크(220B) 및 SRAF를 갖는 FFM 타겟 설계 마스크(100A)의 하이 레벨 개략도이다. 요소(70A), 피치(75A) 및 CD(74A)는 도 2a 및 도 2b에 도시된 요소(70), 피치(75) 및 CD(74)의 대응하는 위치에 개략적으로 도시되어 있다. 각각의 마스크(80A, 90A, 220B 및 100A)의 대응하는 요소(60), 피치(65) 및 CD(64)도 역시 개략적으로 도시되어 있으며, 타겟 요소(71) 및 캡(103, 104)도 마찬가지로 개략적으로 도시되어 있다.

- [0035] 예시적인 비 제한적인 치수로서, 디바이스 피치(75)는 100nm일 수 있고 디바이스 CD는 50nm일 수 있다. 타겟 설계(100)에서, 조대 피치(106)는 1700nm일 수 있고, 조대 라인(107)(예를 들어, 12개의 타겟 요소(70))은 1150nm일 수 있으며, 조대 공간(103A)은 650nm일 수 있어, 그 결과 조대 라인(107):조대 공간(103A)(L:S) 비율 = 1.77이 되고, 이는 인쇄 가능성 및 패턴 위치 결정 오차(pattern positioning error; PPE) 양자 모두를 향상 시킨다. 특정 실시예에서, 명시야 또는 암시야 마스크 설계에 대해, 1보다 큰 L:S 비율(L:S > 1)이 인쇄 가능성 및 PPE를 향상시키기 위해 사용될 수 있다.

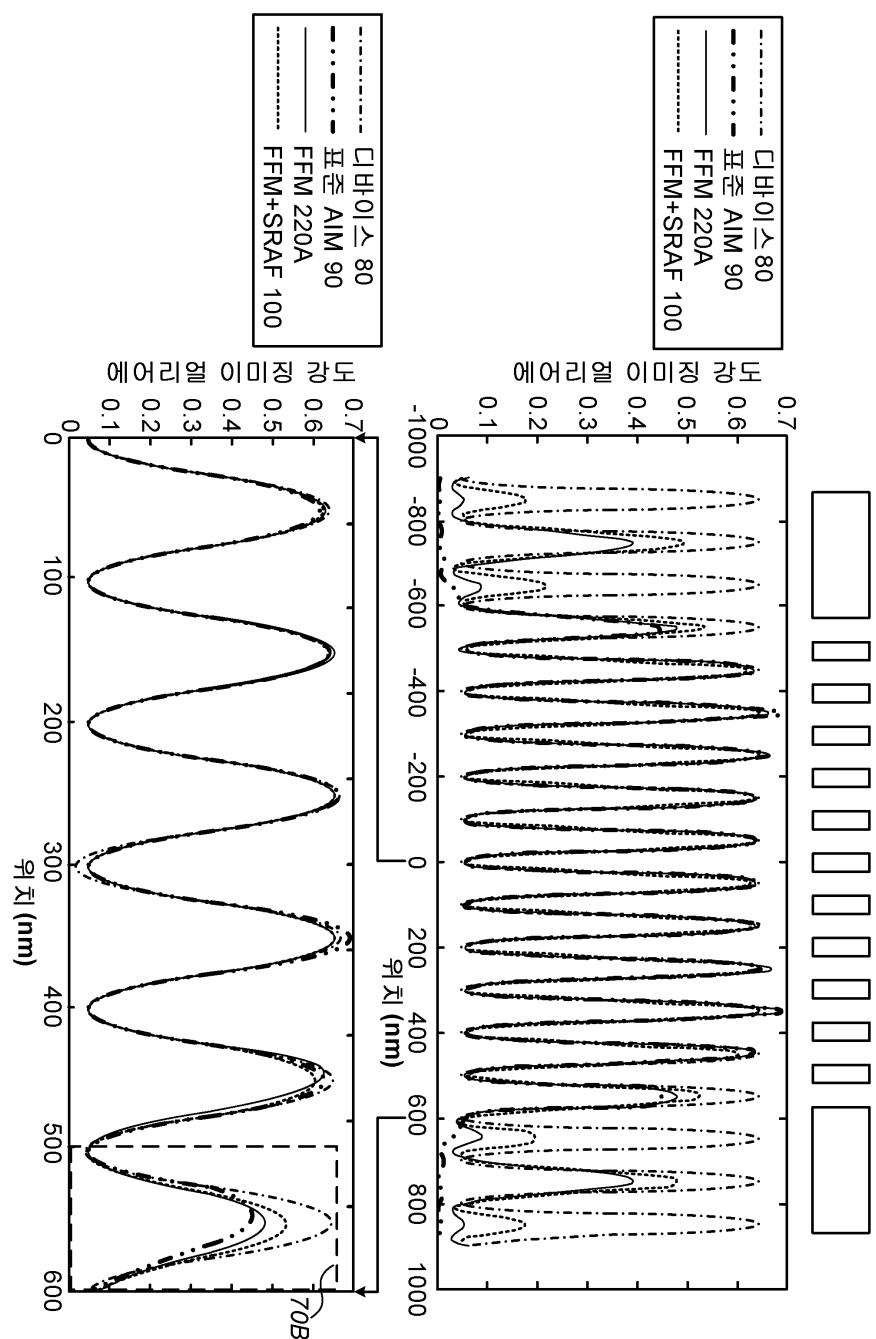

- [0036] 도 3b는 본 발명의 일부 실시예에 따라, 도 3a에 제시된 타겟 마스크 설계의 에어리얼 이미지 성능 테스트의 하이 레벨 개략도이다. 디바이스 상에 고정된 포지티브 톤 현상 및 암시야 바이너리 마스크를 갖는 최적화된 쌍극자 X 조명을 사용하고, Y 편광을 사용하여, 설계(80, 90, 220A 및 100)에 대한 에어리얼 이미지의 비교가 도시된다. 본 발명자들은 AIM 타겟(90) 및 FFM 타겟(220A)과 관련하여, FFM + SRAF 타겟(100)이 디바이스(80)에 가장 잘 일치하고 또한 가장 큰 프로세스 윈도우를 가지는 에어리얼 이미지를 제공한다고 지적한다. 이미징 성능의 차이는 이미징 성능에 특히 중요한 에지 라인(70B)에서 특히 주목할 만하다.

- [0037] 도 3c는 본 발명의 일부 실시예에 따라, 도 3a에 제시된 타겟 설계의 레지스트 이미징 성능 테스트의 하이 레벨 개략도이다. 본 발명자들은 AIM 타겟(90) 및 FFM 타겟(220A)과 관련하여, FFM + SRAF 타겟(100)이 도 3b에 제시된 결과와 일치하여 최상의 에지 라인 인쇄성을 제공한다고 지적한다. 도 3c는 AIM 타겟(90)으로부터 FFM 타겟(220A)을 통해 FFM + SRAF 타겟(100)으로 진행할 때, 결과적인 타겟 이미지 프로파일이 디바이스 이미지 프로파일(80)에 더 가까워짐에 따라 (디바이스(80)가 오버레이 타겟과 비교하여 설계상 더 양호한 리소그래피 성능을 가지기 때문에) 이미징 성능의 향상을 예시한다.

- [0038] 도 3d는 본 발명의 일부 실시예에 따라, 도 3a에 제시된 타겟 설계의 스캐너의 사출 동공의 회절 비교의 하이 레벨 개략도이다. 본 발명자들은 AIM 타겟(90) 및 FFM 타겟(220A)과 관련하여, FFM + SRAF 타겟(100)이 회절 신호의 최대 강도(이미지의 상부 라인) 및 가장 유사한 형상(이미지의 하부 라인)을 제공하기 때문에 PPE 바이어스를 감소시키는 보다 양호한 동공 매칭 결과(넓은 화살표로 도시됨)를 제공한다고 지적한다.

- [0039] 특정 실시예에서, 공간(104) 및/또는 피치(75)는 금지된 리소그래피 피치를 피하도록 조정될 수 있다. 다수의 복합 주기적 구조물(100)로 구성된 계측 오버레이 이미징 타겟에서, 공간(104) 및/또는 피치(75)는 모델 디바이스에 대한 타겟의 회절 패턴에서 근접 매칭을 얻기 위해 조정될 수 있다(예를 들어, 디바이스(80) 및 회절은 도 3d에 개략적으로 도시됨). 특정 실시예에서, 모델 디바이스에 대한 타겟의 회절 패턴에서 근접 매칭을 얻도록 구성된 SRAF 보조 요소(105)가 복합 주기적 구조물(100)에 추가될 수 있다(예를 들어, 디바이스(80) 및 회절 패턴은 도 3d에 개략적으로 도시됨). 리소그래피 시뮬레이션이 타겟 요소(71), 예를 들어, 도 3b 및 도 3c에 도시된 에지 요소(70B)의 에지 배치를 설계하는 데 사용될 수 있다.

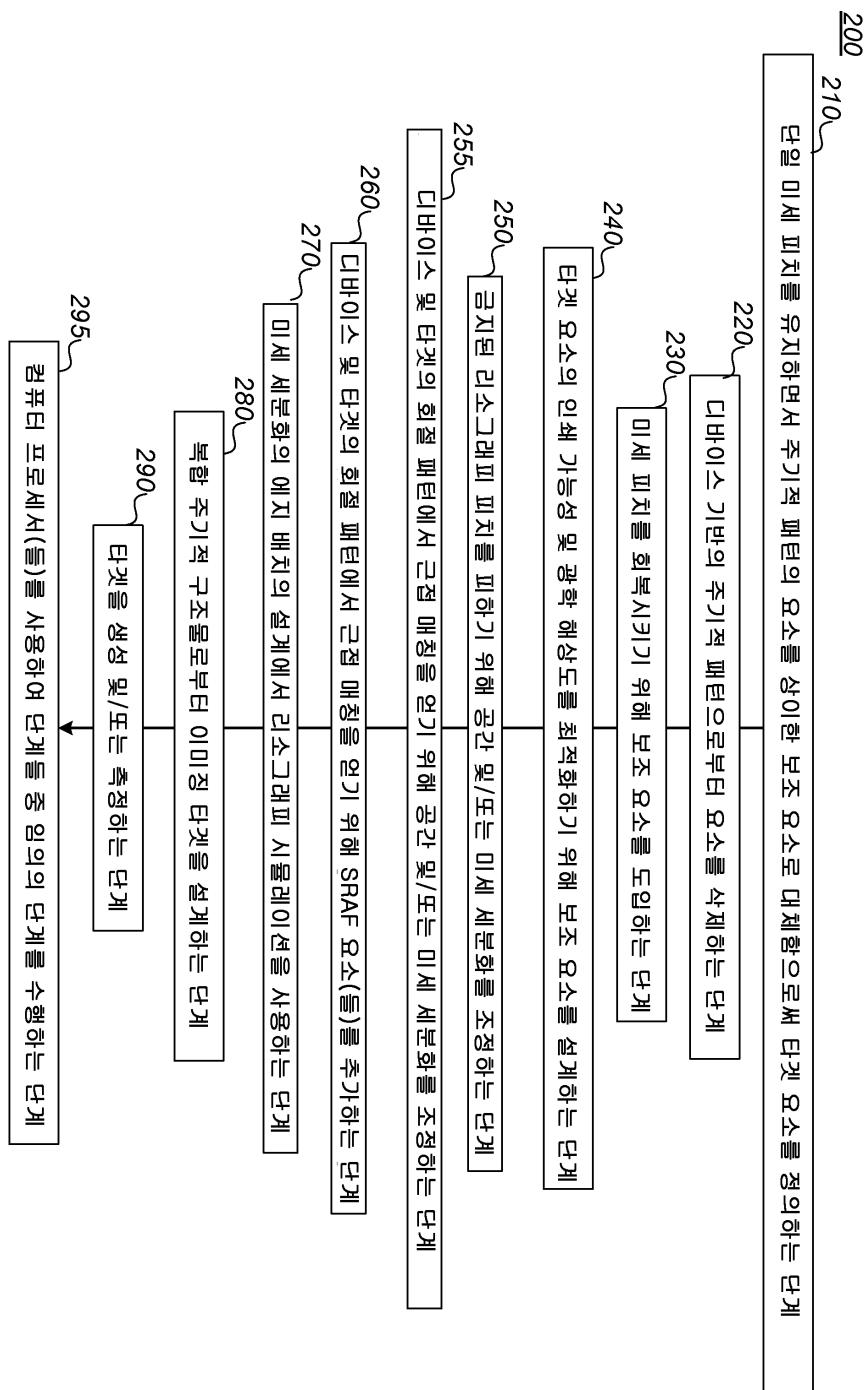

- [0040] 도 4는 본 발명의 일부 실시예에 따라, 방법(200)을 도시하는 하이 레벨 흐름도이다. 방법 단계들은 방법(200)을 구현하도록 선택적으로 구성될 수 있는 앞에서 설명한 타겟 구조물(100)에 대해 수행될 수 있다. 방법(200)은, 예를 들어, 계측 타겟 설계 모듈에서, 적어도 하나의 컴퓨터 프로세서에 의해 적어도 부분적으로 구현될 수 있다. 특정 실시예는 구현된 컴퓨터 판독 가능 프로그램을 갖는 컴퓨터 판독 가능 저장 매체를 포함하고 방법(200)의 관련 단계를 수행하도록 구성된 컴퓨터 프로그램 제품을 포함한다. 특정 실시예는 방법(200)의 실시예에 의해 설계된 각각의 타겟의 타겟 설계 파일을 포함한다.

- [0041] 방법(200)은 단일 피치로서 피치 p를 유지하는 복합 주기적 구조물을 형성하기 위해, 피치 p를 갖는 주기적 패턴의 요소를, 상기 요소와는 적어도 하나의 기하학적 차이를 갖는 보조 요소로 대체함으로써 타겟 요소를 정의하는 단계(단계 210)를 포함할 수 있다. 적어도 하나의 기하학적 차이는 임계 치수일 수 있다.

- [0042] 방법(200)은 디바이스 기반의 주기적 패턴으로부터 요소를 삭제하는 단계(단계 220), 미세 피치를 회복시키기 위해 보조 요소를 도입하는 단계(단계 230), 및 타겟 요소의 인쇄 가능성 및 광학 해상도를 최적화하기 위해 선택적으로 보조 요소를 설계하는 단계(단계 240)를 포함할 수 있다.

- [0043] 방법(200)은 금지된 리소그래피 피치를 피하기 위해 공간 및/또는 미세 세분화를 조정하는 단계(단계 250) 및/또는 디바이스 및 타겟의 회절 패턴에서 근접 매칭을 얻기 위해 공간 및/또는 미세 세분화를 조정하는 단계(단계 255)를 포함할 수 있다.

- [0044] 방법(200)은 디바이스 및 타겟의 회절 패턴에서 근접 매칭을 얻기 위해 SRAF 요소(들)를 추가하는 단계(단계 260)를 포함할 수 있다. 방법(200)은 미세 세분화의 에지 배치의 설계에서 리소그래피 시뮬레이션을 사용하는 단계(단계 270)를 포함할 수 있다.

- [0045] 방법(200)은 복합 주기적 구조물로부터 이미징 타겟을 설계하는 단계(단계 280) 및 타겟을 생성 및/또는 측정하는 단계(단계 290)를 더 포함할 수 있다. 방법(200)은 컴퓨터 프로세서(들)를 사용하여 단계들 중 임의의 단계를 수행하는 단계(단계 295)를 포함할 수 있다. 방법(200)은 컴퓨터 구현 방법, 캐리어 매체, 및 레티를 레이아웃에 대한 계측 타겟 구조물 설계를 생성하기 위한 시스템을 개시하고 그 전체가 참조에 의해 본 명세서에 포함된 미국 특허 제7,925,486호에 의해 교시된 단계들을 포함할 수 있다. 오버레이 스캐터로메트리 타겟은 개시된 원리 및 개시된 타겟 요소를 사용하여 설계될 수 있으며, 또한 본 발명개시의 일부분으로 고려된다는 것을 유념한다.

- [0046] 특정 실시예는 방법(200)에 의해 설계된 타겟(100) 및/또는 타겟의 계측 측정을 포함할 수 있으며, 아마도 편광 조명을 사용하여 측정된다.

- [0047] 유리하게, 타겟(100) 및 방법(200)은 타겟 내의 모든 요소의 위치를 세분화 그리드로 제한하기 때문에, 개선된 인쇄 가능성을 제공할 수 있다. 이러한 장점은 FFM 패턴(220A)에 대한 CD를 증가시킨 후에 SRAF 요소(105)를 추가하기에 충분한 공간을 제공하는 실시예에서 달성된다. 조대 피치와 미세 피치 사이의 균형 조건은 비 제한적인 것이 강조된다. 타겟(100) 및 방법(200)은 웨이퍼 피처들 간의 최소 간격을 유지하면서 모든 요소들을 디바이스 임계 치수로 제한함으로써 개선된 공정 호환성을 제공할 수 있다. 타겟(100) 및 방법(200)은 다양한 패턴의 존적(예컨대, 밀도, L/S 치수) 공정 단계(리소그래피, 예칭, CMP, 가능하게는 중착)에 대한 제안된 타겟 구조물의 디바이스 유사 응답으로 인해, 개선된 타겟 대 디바이스 매칭(타겟 대 디바이스 오프셋을 최소화함)을 제공할 수 있다.

- [0048] 본 발명의 양태들이 본 발명의 실시예들에 따른 방법, 장치(시스템) 및 컴퓨터 프로그램 제품의 순서도 및/또는 부분도를 참조하여 앞에서 설명되었다. 순서도 및/또는 부분도의 각각의 부분, 그리고 순서도 및/또는 부분도의 부분들의 조합은 컴퓨터 프로그램 명령어에 의해 구현될 수 있다는 것을 이해할 것이다. 이들 컴퓨터 프로그램 명령어는 범용 컴퓨터, 특수 목적 컴퓨터, 또는 머신을 생산하기 위한 기타의 프로그램 가능한 데이터 처리 장치의 프로세서에 제공될 수 있으며, 이로써 컴퓨터 또는 기타의 프로그램 가능한 데이터 처리 장치의 프로세서를 통하여 실행되는 이러한 명령어는 순서도 및/또는 부분도 또는 이의 부분들 내에서 명시된 기능/동작을 구현하기 위한 수단을 생성한다.

- [0049] 컴퓨터, 기타의 프로그램 가능한 데이터 처리 장치, 또는 기타의 디바이스들이 특정한 방식으로 기능하도록 지시할 수 있는 이러한 컴퓨터 프로그램 명령어는 컴퓨터 판독 가능 매체 내에 저장될 수 있으며, 이로써 컴퓨터 판독 가능 매체 내에 저장된 명령어는 순서도 및/또는 부분도 또는 이의 부분들 내에서 명시된 기능/동작을 구현하는 명령어를 포함하는 제조 물품을 생산할 수 있다.

- [0050] 컴퓨터 프로그램 명령어는 또한 일련의 동작 단계들이 컴퓨터, 기타의 프로그램 가능한 장치, 또는 기타의 디바이스들 상에서 수행되도록 하여 컴퓨터 구현된 프로세스를 생성하도록 컴퓨터, 기타의 프로그램 가능한 데이터 처리 장치, 또는 기타의 디바이스들에 로딩될 수 있으며, 이로써 컴퓨터 또는 기타의 프로그램 가능한 장치 상에서 실행된 명령어는 순서도 및/또는 부분도 또는 이의 부분들 내에서 명시된 기능/동작을 구현하기 위한 프로세스들을 제공할 수 있다.

- [0051] 전술한 흐름도 및 도면은 본 발명의 다양한 실시예에 따른 시스템, 방법 및 컴퓨터 프로그램 제품의 가능한 구현의 아키텍처, 기능 및 동작을 도시한다. 이와 관련하여, 흐름도 또는 부분도에서의 각각의 부분은, 명시된 논리적 기능(들)을 구현하기 위한 하나 이상의 실행 가능 명령어를 포함하는, 모듈, 세그먼트, 또는 코드의 일부분을 나타낼 수 있다. 또한, 일부 대안적인 구현예들에서, 부분에서 언급된 기능들은 도면에 언급된 순서를 벗어나 발생할 수도 있다는 것을 유념해야 한다. 예를 들어, 연속적으로 도시된 두 개의 부분들은, 사실상, 실질적으로 동시에 실행될 수 있거나, 또는 그 부분들은 관련된 기능에 따라 때때로 반대 순서로 실행될 수 있다. 또한, 부분도 및/또는 흐름도의 각각의 부분, 및 부분도 및/또는 흐름도에서의 부분들의 조합은 명시된 기능 또는 동작을 수행하는 특수 목적 하드웨어 기반의 시스템, 또는 특수 목적 하드웨어 및 컴퓨터 명령어의 조합에

의해 구현될 수 있다는 것도 유념해야 한다.

[0052]

상기 설명에서, 실시예는 본 발명의 일례 또는 구현예이다. "일 실시예", "실시예", "특정 실시예" 또는 "일부 실시예"의 다양한 출현은 반드시 모두 동일한 실시예를 나타내는 것은 아니다. 본 발명의 다양한 피처들이 단일 실시예와 관련하여 설명될 수 있지만, 피처들은 또한 개별적으로 또는 임의의 적절한 조합으로 제공될 수 있다. 반대로, 명확성을 위해 개별적인 실시예와 관련하여 본 발명을 설명할 수 있지만, 본 발명은 또한 단일 실시예에서 구현될 수 있다. 본 발명의 특정 실시예는 상기 개시된 상이한 실시예들의 피처들을 포함할 수 있고, 특정 실시예는 상기 개시된 다른 실시예들의 요소들을 포함할 수 있다. 특정 실시예와 관련하여 본 발명의 요소를 개시하는 것은 특정 실시예에서의 단독 사용으로 제한하는 것으로 간주되어서는 안 된다. 또한, 본 발명은 다양한 방식으로 수행되거나 실시될 수 있으며, 본 발명은 상기 설명에 약술된 것 이외의 특정 실시예에서 구현될 수 있음을 이해해야 한다.

[0053]

본 발명은 이들 도면 또는 대응하는 설명에 한정되지 않는다. 예를 들어, 흐름은 각각의 예시된 박스 또는 상태를 통해 또는 도시되고 설명된 것과 정확히 동일한 순서로 이동할 필요는 없다. 본 명세서에서 사용된 기술적 및 과학적 용어의 의미는 달리 정의되지 않는 한, 본 발명이 속하는 기술 분야의 당업자에 의해 일반적으로 이해될 것이다. 본 발명은 제한된 수의 실시예와 관련하여 설명되었지만, 이들은 본 발명의 범위를 제한하는 것으로 이해되어서는 안 되며, 오히려 바람직한 실시예 중 일부의 예시로서 이해되어야 한다. 다른 가능한 변형, 수정 및 적용이 또한 본 발명의 범위 내에 있다. 따라서, 본 발명의 범위는 지금까지 설명된 것에 의해 한정되어서는 안 되며, 첨부된 청구 범위 및 그 등가물에 의해 제한되어야 한다.

## 도면

### 도면 1a

종래기술

## 도면 1b

## 도면 1c

## 도면 1d

도면 1e

도면 1f

## 도면2a

200220A100102

## 도면2b

## 도면2c

도면3a

도면3b

도면 3c

도면3d

## 도면4