(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4480997号

(P4480997)

(45) 発行日 平成22年6月16日(2010.6.16)

(24) 登録日 平成22年3月26日(2010.3.26)

|                             |                           |

|-----------------------------|---------------------------|

| (51) Int.Cl.                | F 1                       |

| G 0 6 F   7/38   (2006.01)  | G 0 6 F   7/38      B     |

| G 0 6 F   7/496   (2006.01) | G 0 6 F   7/496           |

| G 0 6 F   9/305   (2006.01) | G 0 6 F   9/30    3 4 0 A |

| G 0 6 F   9/315   (2006.01) | G 0 6 F   9/30    3 4 0 D |

請求項の数 4 (全 32 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2003-425711 (P2003-425711) |

| (22) 出願日     | 平成15年12月22日 (2003.12.22)     |

| (65) 公開番号    | 特開2005-25718 (P2005-25718A)  |

| (43) 公開日     | 平成17年1月27日 (2005.1.27)       |

| 審査請求日        | 平成18年12月13日 (2006.12.13)     |

| (31) 優先権主張番号 | 610833                       |

| (32) 優先日     | 平成15年6月30日 (2003.6.30)       |

| (33) 優先権主張国  | 米国 (US)                      |

前置審査

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 593096712<br>インテル コーポレイション<br>アメリカ合衆国 95052 カリフォルニア州 サンタクララ ミッション カレッジ ブールバード 2200 |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                                                             |

| (74) 代理人  | 100091214<br>弁理士 大貫 進介                                                             |

| (74) 代理人  | 100107766<br>弁理士 伊東 忠重                                                             |

| (72) 発明者  | ジェイムズ シー アベル<br>アメリカ合衆国 アリゾナ州 85048 フェニックス イースト ロックレッジロード 2310                     |

最終頁に続く

(54) 【発明の名称】 SIMD 整数乗算上位丸めシフト

## (57) 【特許請求の範囲】

## 【請求項 1】

乗算上位丸めシフト処理を実行するためのコンピュータにより実現される方法であって、

当該方法は、L個のデータ要素の第1セットを有する第1レジスタにおける第1オペラントと、L個のデータ要素の第2セットを有する第2レジスタにおける第2オペラントとを特定する单一命令に応答して、

マイクロプロセッサが、

各ペアが、前記L個のデータ要素の第1セットからの第1データ要素と、前記L個のデータ要素の第2セットの対応するデータ要素位置からの第2データ要素とを有するL個のデータ要素ペアを掛け合わせ、L個の積のセットを生成するステップと、

前記L個の積のそれぞれを右に14ビットシフトし、L個のシフトされた値を18ビット長となるように生成するステップと、

前記L個のシフトされた値のそれぞれの最下位ビット位置に“1”を付加することによって、前記L個のシフトされた値のそれぞれを丸め処理し、L個の丸められた値を生成するステップと、

前記L個の丸められた値のそれぞれを右に1ビットだけスケーリングし、L個のスケーリングされた値のセットを生成するステップと、

L個の切り捨てられた値を取得するため、前記L個のスケーリングされた値から最下位の16ビットを選択することによって、前記L個のスケーリングされた値のそれぞれを切り

捨て処理し、L個の切り捨てられた値を生成するステップと、

前記单一命令の最終結果として、前記L個の切り捨てられた値を前記单一命令により示される宛先レジスタに格納するステップと、

を実行することによって前記单一命令を実行することからなり、

各切り捨て処理された値は、そのデータ要素のペアに対応するデータ要素位置に格納されることを特徴とする方法。

【請求項2】

单一命令を受け付け、該单一命令に応答して、マイクロプロセッサのハードウェア実行ユニットに2つのオペランドに対してPacked乗算上位丸めシフト処理を実行させるステップと、

10

前記マイクロプロセッサのハードウェア実行ユニットにおいて前記单一命令を実行し、切り捨て処理された結果のセットを生成するステップと、

Packedデータ要素として宛先レジスタに前記切り捨て処理された結果のセットを格納するステップと、

から構成される方法であって、

前記Packed乗算上位丸めシフト処理は、

Packedデータ要素の第1セットの各データ要素と、Packedデータ要素の第2セットの対応するデータ要素とを乗算し、積のセットを生成し、

前記積のセットのそれぞれを右に14ビットシフトし、その後に丸め処理して、18ビット長となるように結果のセットを生成し、

20

前記結果のそれから複数のビットを選択し、切り捨て処理された結果のセットを生成することから構成され、

前記单一命令は、

前記Packed乗算上位丸めシフト処理に関する情報を提供するため、前記Packed乗算上位丸めシフト処理に対する前記切り捨てられた結果のセットが、前記結果のセットの上位ビット又は下位ビットから構成されるか示すオペコードを指定する第1フィールドと、

前記Packedデータ要素の第1セットを有する第1オペランドに対して、第1ソースアドレスを指定する第2フィールドと、

前記Packedデータ要素の第2セットを有する第2オペランドに対して、第2ソースアドレスを指定する第3フィールドと、

30

から構成されるフォーマットを有することを特徴とする方法。

【請求項3】

单一命令に応答してPacked乗算丸めシフト処理を実行するマイクロプロセッサのハードウェア実行ユニットから構成される装置であって、

前記ハードウェア実行ユニットは、前記单一命令に応答して、

Packedデータ要素の第1セットの各データ要素と、Packedデータ要素の第2セットの対応するデータ要素とを乗算し、積のセットを生成し、

シフトされた値のそれぞれの最下位ビット位置に“1”を付加することによって、前記積のセットのそれぞれを丸め処理し、結果のセットを生成し、

前記結果のセットのそれぞれを右に14ビットシフトし、18ビット長となるように結果の中間セットを生成し、

40

前記結果の中間セットのそれから複数のビットを選択し、切り捨てられた結果のセットを生成し、

最終結果として前記切り捨てられた結果のセットを格納し、

前記单一命令は、

前記Packed乗算丸めシフト処理に関する情報を提供するため、前記Packed乗算上位丸めシフト処理に対する前記切り捨てられた結果のセットが、前記結果のセットの上位ビット又は下位ビットから構成されるか示すオペコードを指定する第1フィールドと、

前記Packedデータ要素の第1セットを有する第1オペランドに対して、第1ソースアドレスを指定する第2フィールドと、

50

前記Packedデータ要素の第2セットを有する第2オペランドに対して、第2ソースアドレスを指定する第3フィールドと、

から構成されるフォーマットを有することを特徴とする装置。

【請求項4】

第1命令を格納するメモリと、

前記メモリから前記第1命令をフェッチするプロセッサと、

から構成されるシステムであって、

前記プロセッサは、前記第1命令の実行に応答して、

Packedデータ要素の第1セットの各データ要素と、Packedデータ要素の第2セットの対応するデータ要素とを乗算し、積のセットを生成し、

シフトされた値のそれぞれの最下位ビット位置に“1”を付加することによって、前記積のセットのそれぞれを丸め処理し、一時的結果のセットを生成し、

前記一時的結果のセットのそれぞれをスケーリングし、スケーリングされた一時的結果のセットを生成し、

前記スケーリングされた一時的結果のそれぞれから複数のビットを選択し、切り捨て処理された結果のセットを生成し、

最終結果として前記切り捨て処理された結果のセットを格納し、

前記第1命令は、

前記Packed乗算丸めシフト処理に関する情報であって、符号付き整数のPacked乗算丸めシフト処理を示す情報を提供するオペコードであって、前記切り捨てられた結果のセットのそれぞれの上位ビットを選択するためのオペコードを指定する第1フィールドと、

前記Packedデータ要素の第1セットを有する第1オペランドに対して、第1ソースアドレスを指定する第2フィールドと、

前記Packedデータ要素の第2セットを有する第2オペランドに対して、第2ソースアドレスを指定する第3フィールドと、

から構成されるフォーマットを有することを特徴とするシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、数学的演算を実行する処理装置、関連ソフトウェア及びソフトウェアシーケンスの技術分野に関する。

【背景技術】

【0002】

今日の社会において、コンピュータシステムはますます広く普及しつつある。コンピュータ処理能力は、広い範囲の分野における労働者の効率性と生産性を高めてきた。コンピュータの購入及び所持コストが遞減するにつれ、より多くの消費者が最新のより高速なマシンを利用することが可能になった。さらに、多くの人々がノートブックコンピュータの利用をその利用に関する柔軟性により享受している。モバイルコンピュータにより、ユーザはオフィスから外出したり、あるいは出先でも、データを携帯し作業を行うことが容易にできる。このような場面は、マーケティングスタッフ、企業の役員、学生においてさえもよく見られるものである。

【0003】

プロセッサ技術の進歩に伴い、先端的なプロセッサを備えたマシン上で実行するための新たなソフトウェアコードが生成される。一般に、ユーザは、使用しているソフトウェアのタイプに関わらず、コンピュータからより高いパフォーマンスを期待及び要求する。ここで、プロセッサ内部において実行されている命令及び処理タイプにより生じる可能性のある1つの問題がある。すなわち、あるタイプの処理には処理の複雑さ及び／あるいは必要とされる回路の種類に基づき、その完了に多くの時間を要するものもある。このようなことから、プロセッサ内部での複雑な処理を実行する方法を最適化するという動機付けが生じる。

**【0004】**

メディアアプリケーションは、数十年もの間、マイクロプロセッサの発達を促進してきた。実際、近年における計算機の性能向上の多くはメディアアプリケーションにより促進されてきたものである。娛樂性を高めた教育及び通信目的のため、重大な進歩は企業部門において見出されてきたが、上記のような性能の向上は主として消費者部門において起こってきたものである。にもかかわらず、これからのメディアアプリケーションには、さらに高い計算能力が要求されるであろう。この結果、将来のパーソナルコンピュータ（PC）では、使い安さだけでなくより充実したオーディオビジュアル機能が実現されるであろう。さらに、より重要なものとしては計算機と通信の融合であろう。

**【0005】**

10

従って、現在の計算機においては、コンテンツとして総称される音声及び映像データの再生だけでなく画像の表示も、ますます一般的なアプリケーションとなりつつある。フィルタリング及び畳み込み処理は、画像、音声及び映像データのようなコンテンツデータに対し最もよく実行される処理である。これらの処理は大きな計算量を要することから、例えば、単一命令多重データ（ SIMD ）レジスタのような様々なデータ記憶装置を利用することにより、効率的な実行を行うための高いレベルでのデータ並列処理が提供されている。

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

20

既存のアーキテクチャの多くは不必要的データタイプの変更を必要とし、それによって、命令スループットの減少を招き、算術演算のためのデータ順序付けに要するクロックサイクル数を著しく増加させてしまう。

**【0007】**

本発明は、このような問題点に鑑み、 Packed 乗算上位丸めシフト処理を実行するための方法、装置、システム及びマシンによる読み出し可能な媒体を提供することを目的とする。

**【課題を解決するための手段】****【0008】**

上記課題を解決するために、本発明による方法は、 L 個のデータ要素の第 1 セットを有する第 1 オペランドを受信するステップと、 L 個のデータ要素の第 2 セットを有する第 2 オペランドを受信するステップと、各自が L 個のデータ要素の前記第 1 セットからの第 1 データ要素と L 個のデータ要素の前記第 2 セットの対応するデータ要素位置からの第 2 データ要素とを有する L 個のデータ要素のペアを掛け合わせ、 L 個の積のセットを生成するステップと、前記 L 個の積のそれぞれを丸め処理し、 L 個の丸められた値を生成するステップと、前記 L 個の丸められた値のそれぞれをスケーリングし、 L 個のスケーリングされた値を生成するステップと、宛先への格納のため、前記 L 個のスケーリングされた値のそれぞれを、そのデータ要素のペアに対応するデータ要素位置に格納されるよう切り捨て処理するステップからなることを特徴とする。

**【0009】**

40

上記課題を解決するために、本発明による方法は、 Packed データ要素の第 1 セットの各データ要素と Packed データ要素の第 2 セットの対応するデータ要素を掛け合わせ、積のセットを生成するステップと、前記積のセットのそれぞれを丸めシフトし、結果のセットを生成するステップと、前記結果のセットのそれぞれから複数のビットを選択し、切り捨てられた結果のセットを生成するステップからなる Packed 乗算丸めシフト処理を 2 つのオペランドに実行する命令を受信するステップと、前記命令を実行し、 Packed データ要素として宛先レジスタに格納するために前記切り捨てられた結果のセットを生成するステップからなる方法であって、前記命令は、前記 Packed 乗算丸めシフト処理についての情報を提供するオペコードを特定する第 1 フィールド、前記 Packed データ要素の第 1 セットを有する第 1 オペランドのための第 1 ソースアドレスを特

50

定する第2フィールド、前記Packedデータ要素の第2セットを有する第2オペランドのための第2ソースアドレスを特定する第3フィールドからなるフォーマットを有することを特徴とする。

#### 【0010】

上記課題を解決するために、本発明による装置は、Packed乗算丸めシフト処理を実行するための少なくとも1つの命令を含む命令セットの1つ以上の命令を実行する実行ユニットからなる装置であって、前記実行ユニットは、前記Packed乗算丸めシフト処理を実行する前記少なくとも1つの命令に応答して、Packedデータ要素の第1セットの各データ要素とPackedデータ要素の第2セットの対応するデータ要素を掛け合わせ、積のセットを生成し、前記積のセットのそれぞれを丸めシフト処理し、結果のセットを生成し、前記結果のそれから複数のビットを選択し、切り捨てられた結果のセットを生成し、前記少なくとも1つの命令は、前記Packed乗算丸めシフト処理についての情報を提供するためのオペコードを特定する第1フィールドと、前記Packedデータ要素の第1セットを有する第1オペランドのための第1ソースアドレスを特定する第2フィールドと、前記Packedデータ要素の第2セットを有する第2オペランドのための第2ソースアドレスを特定する第3フィールドからなるフォーマットを有することを特徴とする。

#### 【0011】

上記課題を解決するために、本発明によるシステムは、データ及び命令を格納するメモリと、バスを介し前記メモリに接続され、乗算丸めシフト命令に応答して、乗算丸めシフト処理を実行するプロセッサからなるシステムであって、前記プロセッサは、前記メモリから前記乗算丸めシフト命令を受信するバスユニットと、前記バスユニットに接続され、前記乗算丸めシフト命令を実行する実行ユニットから構成され、前記乗算丸めシフト命令は前記実行ユニットに、Packedデータ要素の第1セットの各データ要素とPackedデータ要素の第2セットの対応するデータ要素を掛け合わせることにより積のセットを生成させて、前記積のセットのそれぞれを丸めシフト処理することにより結果のセットを生成させて、及び前記結果のそれから複数のビットを選択することにより切り捨てられた結果のセットを生成させることを特徴とする。

#### 【0012】

上記課題を解決するために、本発明によるマシーン読み出し可能な媒体は、プログラムを格納するマシーン読み出し可能な媒体であって、マシーンにより実行可能な前記プログラムは、L個のデータ要素の第1セットを有する第1オペランドを受信するステップと、L個のデータ要素の第2セットを有する第2オペランドを受信するステップと、各自がL個のデータ要素の前記第1セットからの第1データ要素とL個のデータ要素の前記第2セットの対応するデータ要素位置からの第2データ要素とを有するL個のペアを掛け合わせ、L個の積のセットを生成するステップと、前記L個の積のそれぞれを丸め処理し、L個の丸められた値を生成するステップと、前記L個の丸められた値のそれぞれをスケーリングし、L個のスケーリングされた値を生成するステップと、宛先への格納のため、前記L個のスケーリングされた値のそれぞれを、そのデータ要素のペアに対応するデータ要素位置に格納されるよう切り捨て処理するステップからなる方法を実行することを特徴とする。

#### 【発明の効果】

#### 【0013】

以上のように、本発明によれば、Packed乗算上位丸めシフト処理を実行するための方法、装置、システム及びマシーンによる読み出し可能な媒体が得られる。

#### 【発明を実施するための最良の形態】

#### 【0014】

以下、本発明の実施の形態について図面に基づいて説明する。ここで、本発明は添付される図面に制限されるものではない。また図面中、同一の参照記号は同一の要素を示している。

10

20

30

40

50

## 【0015】

以下の説明は SIMD 整数乗算丸めシフト処理の実施例を説明する。以下の説明において、本発明のより完全なる理解を提供するために、プロセッサタイプ、マイクロアーキテクチャ状態、イベント、実施可能な機構などのような具体的な詳細が与えられる。しかしながら、本発明はこのような具体的な詳細以外でも実践可能であるということは当業者には認識されるであろう。さらに、周知の構成及び回路などは、本発明を必要に不明瞭にしないよう詳細には示されていない。

## 【0016】

以下の実施例はプロセッサに関し説明されるが、他の実施例では、他のタイプの集積回路及び論理装置に適用することもできる。本発明の同様なテクニック及び教示は、より高いパイプラインスループット及び性能を享受しうる他のタイプの回路あるいは半導体デバイスに容易に適用することができる。本発明の教示は、データ操作を実行する任意のプロセッサあるいはマシーンに適用可能である。しかしながら、本発明は、256ビット、128ビット、64ビット、32ビットあるいは16ビットデータ処理を実行するプロセッサあるいはマシーンに限定されるものでなく、Packedデータに対する操作が必要とされる任意のプロセッサ及びマシーンに適用することができる。

10

## 【0017】

以下の記述では、説明のため、本発明の完全な理解を提供するため様々な具体的な詳細が与えられる。本発明の実践に対し、これら具体的な詳細が必ずしも必要でないということは当業者には認識されるであろう。また、周知の電気構造及び回路は、本発明を必要に不明瞭にしないよう詳細には与えられていない。さらに、以下の説明は実施例を与えるものであり、添付される図面は例示のため様々な実施例を示している。しかしながら、これらの実施例は限定のためのものと解釈されるべきでない。これらの実施例は、本発明のすべての可能な実現を包括的に列挙するものでなく、単に本発明の一例を提供することを目的としている。

20

## 【0018】

以下の実施例は実行ユニットや論理回路に関する命令処理や配置を説明するが、本発明の他の実施例はソフトウェアにより達成可能である。一実施例において、本発明による方法は、マシーン実行可能な命令により実現される。これらの命令により、プログラム可能な汎用あるいは特定用途向けプロセッサが本発明の各ステップを実行する。本発明に従う処理を実行するコンピュータ（あるいは他の電子装置）をプログラムするのに利用される命令を格納したマシーンまたはコンピュータによる読み出し可能な媒体を含むコンピュータプログラムプロダクトまたはソフトウェアとして本発明は提供される。あるいは、本発明の各ステップは、これらのステップを実行する配線論理を含む特定のハードウェア要素により実行されてもよいし、あるいはプログラムされたコンピュータ構成要素及びカスタムハードウェア構成要素による任意の組み合わせにより実行されてもよい。このようなソフトウェアはシステム内のメモリに格納することが可能である。同じように、そのようなコードはネットワークを介し、あるいは他のコンピュータ読み出し可能な媒体により配信可能である。

30

## 【0019】

従って、マシーン読み出し可能な媒体は、以下に限定されるものではないが、フロッピーディスク（登録商標）、光ディスク、CD（Compact Disc）、CD-ROM（CD Read-Only Memory）、光磁気ディスク、ROM（Read-Only Memory）、RAM（Random Access Memory）、EEPROM（Erasable Programmable Read-Only Memory）、EEPROM（Electrically Erasable Programmable Read-Only Memory）、磁気あるいは光カード、フラッシュメモリ、インターネット上の送信、電子、光、音響あるいは他の搬送信号（例えば、搬送波、赤外線信号、デジタル信号など）などのマシーン（例えば、コンピュータ）により読み出し可能な形態での情報の格納及び送信のための任意の機構が含まれる。従って、コ

40

50

ンピュータ読み出し可能な媒体には、マシーン（例えば、コンピュータ）による読み出し可能な形態により電子的命令あるいは情報の格納または送信に適した任意のタイプのメディア／マシーン読み出し可能な媒体が含まれる。さらに、本発明はまた、コンピュータプログラムプロダクトとしてダウンロード可能であってもよい。その場合、プログラムはリモートコンピュータ（例えば、サーバ）からリクエストコンピュータ（例えば、クライアント）に転送される。プログラムの転送は、電子、光、音響あるいは搬送波で実現される他の形態のデータ信号、あるいは通信リンク（例えば、モデム、ネットワーク接続など）を介した他の伝搬媒体により実行されてもよい。

#### 【0020】

設計は、制作からシミュレーションそして製造と様々な段階を経ているかもしれない。設計を表すデータは様々な方法で当該設計を表しているかもしれない。まず、シミュレーションにおいて有益なように、ハードウェア記述言語や他の機能記述言語を使ってハードウェアが表現される。さらに、論理及び／あるいはトランジスタゲートによる回路レベルのモデルが設計処理のある段階において生成される。さらに、ある段階では、大部分の設計がハードウェアモデルの様々な装置の物理的配置を表すデータレベルに達する。従来の半導体製造技術が利用される場合、ハードウェアモデルを表すデータは、集積回路の生成に利用されるマスクのマスクレイヤに関する様々な特徴の有無を特定するデータであるかもしれない。任意の設計表現において、このデータは任意の形態のマシーン読み出し可能な媒体に格納することができる。このような情報の送信のため生成あるいは変調される光または電気波、メモリ、ディスクのような磁気または光記憶装置などは、マシーン読み出し可能な媒体である。これらの媒体の何れもが設計やソフトウェア情報を「搬送」または「表現」することができる。コードや設計を示し搬送する電気搬送波が送信されるとき、電気信号のコピー、バッファリングあるいは再送が実行される程度まで新たなコピーが行われる。従って、通信プロバイダやネットワークプロバイダは本発明のテクニックを実現するもの（搬送波）のコピーを行える。

#### 【0021】

今日のプロセッサでは、様々なコード及び命令の処理及び実行に多くの実行ユニットが利用されている。命令の中には即座に完了するものがある一方、膨大なクロックサイクルを要する命令もあるので、必ずしもすべての命令が等しく生成されることは限らない。命令のスループットが速くなるほど、プロセッサの全体的なパフォーマンスはより向上する。従ってできる限り多くの命令を高速に実行させることができが望ましい。しかしながら、より大きな複雑さを有し、より多くの実行時間及びプロセッサリソースを要する命令もある。例えば、浮動小数点命令、ロード／ストア処理、データ転送などが挙げられる。

#### 【0022】

ますます多くのコンピュータシステムがインターネットやマルチメディアアプリケーションにおいて利用されるに従い、追加的なプロセッササポートがこれまで導入されてきた。例えば、単一命令多重データ（S I M D）整数／浮動小数点命令やストリーミングS I M Dエクステンション（S S E）は、特定のプログラムタスクの実行に要する全体の命令数を減少させる命令である。これらの命令は、複数のデータ要素に対し並列処理を行うことにより、ソフトウェアパフォーマンスの高速化を可能にする。これにより、映像、音声、及び画像／フォト処理を含む広範なアプリケーションにおいてパフォーマンスの向上を達成することが可能となる。通常、マイクロプロセッサや類似の論理回路におけるS I M D命令の実現には多くの発行が伴う。さらに、S I M D処理の複雑さはしばしば、正確なデータ処理及び操作のための追加的回路の必要性を生じさせる。

#### 【0023】

2の補数表記（two's-complement notation）は符号付きの数を表現する効果的な方法である。2の補数の最上位ビットがその符号を表し、残りのビットがその大きさを表す。固定小数点数の計算はオーバーフローを引き起こすことなく整数プロセッサにおける乗算を可能にする。小数計算は、掛け算でのオーバーフローに関する問題がない場合、デジタル信号処理プログラミングにとって大いに有益なものである。

10

20

30

40

50

2つの16ビット数の乗算には結果のため32ビットが必要であり、2つの16ビット固定小数点数を乗じることにより生成される32ビットの結果は最小エラーの導入により16ビットに丸められる。16ビット整数の変換は、当該整数の小数値を32768により除することである。一実施例では、2つの小数を掛け合わせることにより生じる積の上位16ビットが着目される。しかしながら、結果の上位16ビットが期待される小数の結果の半分である。この積が結果に2を乗じるため左方向にシフトされる必要がある。これにより最終的な正しい積が得られる。小数演算はまた乗数及び被乗数の符号拡張を要する。

#### 【0024】

左方向へのシフトの必要性はまた、小数位置の配置として説明することができる。例えば、小数を掛け合わせるとき、小数点は無視され、最後に置かれる。この小数点は、乗数と被乗数の小数点の右側の合計桁数がそれらの積の小数点の右側の桁数に等しくなるよう配置される。同様に、小数演算のためのここでの「小数点」は最左（符号）ビットの右に位置し、この点の右には15ビット（桁）ある。しかしながら、ソースにおける小数点の右側には合計30ビットある。シフトがなければ、32ビットの結果における小数点の右側は31ビットとなるであろう。数を1ビットだけ左にシフトすることにより、小数点の右側のビット数を30に効果的に減らすことができる。

#### 【0025】

本発明の実施例は、固定点整数 SIMD 命令の精度を向上させることができる。固定点整数フォーマットは、固定点小数点数演算のものと類似している。一実施例の「1.15」の固定点フォーマットは、2進数点 (binary point) が第14ビットと第15ビットの間に位置する符号付きの値を有する数を表す。ここでは、ビット位置は最右ビットから0からカウントされる。従って、最右または最下位ビットは第0ポジションとなる。そのすぐ左のビット位置が第1ビット、そして以下同様となる。この1.N数値フォーマットはしばしばデジタル信号処理 (DSP) アプリケーションにおいて利用される。本発明による実施例はまた、丸め処理やシフト処理技術を通じさらなる精度の向上を提供する。本発明の実施例から得られるさらなる精度向上は、多くのアプリケーションのより容易なプログラミングに寄与する。さらに、このさらなる精度向上は、映像及び画像処理アプリケーションにおいてしばしば利用される離散コサイン変換 (DCT) のようなアルゴリズムのより高速な実行を可能にする。

#### 【0026】

SIMD 整数乗算上位丸めシフト命令 (SIMD integer multiply high with round and shift instruction) のための1例となるアプリケーションは高品質の映像においてである。16ビットの結果を有する  $16 \times 16$  ビット乗算は映像エンコーダ及びデコーダ、特に、逆DCT、DCT、量子化 (Q) 及び逆Qブロックにおいて非常によく利用される。乗算の精度は全体の画質に大きな影響がある。本発明の実施例によるパフォーマンス向上及び高速化は、逆DCT 計算においてより大きな影響力を有する。DCT 計算に加え、基本的に16ビットの乗算であるQ及び逆Q計算にも有益である。

#### 【0027】

一般に、コンピュータ産業では、 $8 \times 8$  逆離散コサイン変換の実現のため IEEEEE 規格 1180-1990 がよく利用されている。この規格はテレビ会議に関するものであるが、当該規格の一部は様々な MPEG フォーマットによるエンコーダ及びデコーダに適用されている。しかしながら、高いパフォーマンスを維持しながら IEEEEE 1180-1990 規格に準拠することは困難である。このトレードオフは、しばしば非準拠高パフォーマンスまたは準拠低パフォーマンスとなる。さらに、規格への符号化は、特に適切でないアルゴリズムが選ばれている場合には、時間のかかる繰り返しの処理である。

#### 【0028】

IEEEEEE 1180-1990 規格に準拠は、乗数上位丸めシフト命令の実施例により容易になる。本発明による SIMD 整数乗算上位丸めシフト命令の実施例は、Packed データ環境での入出力データ要素に同一の1.15データフォーマットを提供することが

10

20

30

40

50

できる。これにより、乗算上位丸めシフト処理の実施例を含む命令セットによるコード記述とプログラミングはより簡単化される。同じように、高レベル言語と関連するコンパイラのアクセス性もまた可能になる。映像、音声及び画像エンコーダ／デコーダ（コーデック）のパフォーマンス及び精度を向上させるために、開発者は整数乗算丸めシフトのような固定点 SIMD 命令の実施例により可能となる言語及びコンパイラを利用することができます。SIMD 機能を備えた命令セットは、類似データの繰り返し処理において以前に必要とされた冗長なアルゴリズムの回避に役立つ。

#### 【0029】

一実現形態における乗算への各入力は 1.15 フォーマットに従う。メモリを備えた乗算上位丸めシフト処理の一実施例において、2.16 フォーマットを有する仮の 18 ビット値が、2 つの 16 ビットデータ値の乗算による 32 ビットの積の上位ビットから生成される。この仮の 18 ビット値は、最下位ビットに「1」を加えることにより、精度のため丸められる。いくつかのテクニックではすべての下位ビットが単に破棄されるが、本発明の実施例による丸め処理は逆 D C T 符号化のためのある許容可能な閾値にエラーが収まることを可能にする。この丸められた値は、さらなる精度のためと、所望の出力フォーマットを得るために、1 ビットだけ左にシフトされる。1.15 フォーマットを有する 16 ビットの結果が、丸められたシフトされた 18 ビット値から抽出される。仮の値に対し実行された丸め及びシフト処理は、32 ビットの積の上位 16 ビットを単にとることにより、さらなる精度を有する 2 ビットを提供することができる。例えば、ここで説明される一般的な実施例では、丸め処理は、32 ビットの積からの上位 16 ビットの抽出により、さらなる精度を有する 1 ビットを提供する。同じように、シフト処理は、丸められた積に対しさらなる精度を有する 1 ビットを提供する。これらの説明は 16 ビット長の整数値に関し実施例を説明しているが、他の実施例は任意のビット長のデータ値に適用することができる。

#### 【0030】

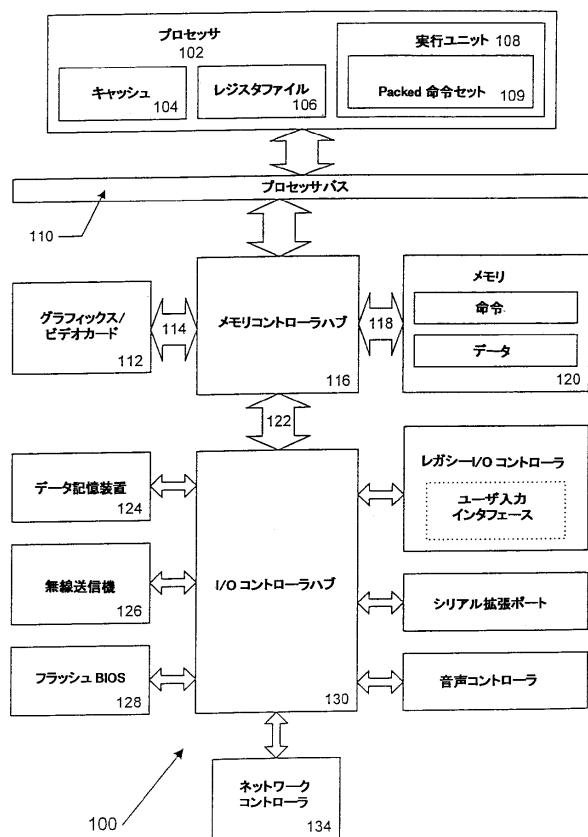

図 1A は、本発明の一実施例による乗算上位丸めシフト処理のための命令を実行する実行ユニットを含むプロセッサにより構成される一例となるコンピュータシステムのプロック図である。システム 100 は、ここで説明される実施例のような本発明によるデータ処理アルゴリズムを実行する論理を含む実行ユニットを利用するプロセッサ 102 のような構成要素を備える。システム 100 は、カリフォルニア州サンタクララのインテルコーポレーションより入手可能な PENTIUM (登録商標) I I I 、 PENTIUM (登録商標) 4 、 Xeon (商標) 、 Itanium (登録商標) 及び / または X Scale (商標) マイクロプロセッサに基づく処理システムにより代表される。しかしながら、（他のマイクロプロセッサ、エンジニアリング・ワークステーション、セットトップボックスなどを含む）他のシステムが利用されてもよい。一実施例では、サンプルシステム 100 は、ワシントン州レッドモンドのマイクロソフトコーポレーションから入手可能であるバージョンの WINDOWS (登録商標) オペレーティングシステムを実行してもよい。しかしながら、（例えば、 UNIX (登録商標) や Linux のような）他のオペレーティングシステム、埋め込みソフトウェア及び / またはグラフィカルユーザインターフェースが使われてもよい。本発明は、ハードウェア回路とソフトウェアの特定の組み合わせに限定されるものではない。

#### 【0031】

本発明の他の実施例では、携帯装置や埋め込みアプリケーションのような他の装置において利用可能である。携帯装置の例として、携帯電話、インターネットプロトコル装置、デジタルカメラ、PDA (Personal Digital Assistant) 、及び携帯型パーソナルコンピュータなどが含まれる。埋め込みアプリケーションには、マイクロコントローラ、デジタル信号プロセッサ (DSP) 、システムオンチップ、ネットワークコンピュータ (Net PC) 、セットトップボックス、ネットワークハブ、ワイドエリアネットワーク (WAN) スイッチ、あるいは複数のメモリコピーまたは移動を実行する他のシステムなどが含まれる。さらに、マルチメディアアプリケーションの効率向上

10

20

30

40

50

のため、同時に複数のデータに対し処理する命令を可能にするよう実現されたアーキテクチャがある。データタイプやデータ量が増大するに従い、より効率的な方法によりデータを操作できるようコンピュータ及びそのプロセッサの性能を向上させねばならない。

#### 【0032】

図1Aは、本発明による丸め及びシフト命令によるSIMD整数乗算上位を含むアルゴリズムを処理する1つ以上の実行ユニット108を備えるプロセッサ102により構成されるコンピュータシステム100のブロック図である。例えば、プロセッサ102は、Packedデータオペランドに対するSIMD乗算上位処理をリクエストするプログラム命令を受信することができる。本実施例は単一のプロセッサデスクトップまたはサーバシステムに関して説明されるが、他の実施例がマルチプロセッサシステムに含まれてもよい。システム100はハブアーキテクチャの一例である。コンピュータシステム100は、データ信号を処理するプロセッサ102を備える。プロセッサ102は、複合命令セットコンピュータ(CISC)マイクロプロセッサ、縮小命令セットコンピュータ(RISC)マイクロプロセッサ、VLIW(Very Long Instruction Word)マクロプロセッサ、命令セットの組み合わせを実現するプロセッサ、あるいはデジタル信号プロセッサのような他のプロセッサ装置でありうる。プロセッサ102は、プロセッサ102とシステム100内の他の構成要素との間のデータ信号を送信することができるプロセッサバス110に接続される。システム100の構成要素は、当業者には周知の既存の機能を実行する。

#### 【0033】

一実施例では、プロセッサ102はレベル1(L1)内部キャッシュメモリ104を含む。アーキテクチャに応じて、プロセッサ102は単一の内部キャッシュあるいは複数レベルの内部キャッシュを有する。また他の実施例では、キャッシュメモリはプロセッサ102の外部に設けられていてもよい。他の実施例ではまた、要求される実施形態に応じて、内部キャッシュと外部キャッシュの両方の組み合わせが含まれうる。レジスタファイル106は、様々なタイプのデータを整数レジスタ、浮動小数点レジスタ、ステータスレジスタ及び命令ポインタレジスタを含む様々なレジスタに格納することができる。

#### 【0034】

実行ユニット108は、整数及び浮動小数点処理を実行する論理を含み、プロセッサ102に設けられる。プロセッサ102はまた、あるマクロ命令のためのマイクロコードを格納するマイクロコード(ucode)ROMを備えていてもよい。本実施例では、実行ユニット108はPacked命令セット109を扱う論理を含んでいる。一実施例において、Packed命令セット109は、結果として得られる積の関連する上位部分を獲得するため、Packed乗算上位命令を含んでいる。汎用プロセッサ102の命令セットのPacked命令セット109を、命令を実行する関連回路と共に含めることにより、多くのマルチメディアアプリケーションにより利用される処理が、汎用プロセッサ102のPackedデータを使うことにより実行されてもよい。これにより、Packedデータに処理を実行するためのプロセッサのデータバスの全幅を使用することにより、多くのマルチメディアアプリケーションがより効率的に実行されうる。この結果、1つのデータ要素に1つ以上の処理を同時に実行するために、より小さいデータユニットをプロセッサのデータバスに送信する必要がなくなる。実行ユニット108の他の実施例はまた、マイクロコントローラ、埋め込みプロセッサ、グラフィックス装置、DSP及び他のタイプの論理回路において利用可能である。システム100はメモリ120を備える。メモリ120は、DRAM(Dynamic Random Access Memory)装置、SRAM(Static Random Access Memory)装置、フラッシュメモリ装置、あるいは他のメモリ装置であってもよい。メモリ120は、プロセッサ102により実行可能なデータ信号により表される命令及び/あるいはデータを格納することができる。

#### 【0035】

システム論理チップ116は、プロセッサバス110とメモリ120に接続される。例

10

20

30

40

50

示された実施例のシステム論理チップ116はメモリコントローラハブ(MCH)である。プロセッサ102は、プロセッサバス110を介しMCH116と通信することができる。MCH116は、命令及びデータの格納と、グラフィックスコマンド、データ及びテクスチャの格納のため、メモリ120への高帯域幅メモリバス118を与える。MCH116は、プロセッサ102、メモリ120及びシステム100の他の構成要素間においてデータ信号を導き、プロセッサバス110、メモリ120及びシステムI/O122間ににおいてデータ信号をブリッジする。いくつかの実施例では、システム論理チップ116は、グラフィックスコントローラ112への接続のために、グラフィックスポートを備える。MCH116は、メモリインターフェース118を介しメモリ120に接続される。グラフィックスカード112は、AGP(Accelerated Graphics Port)インターフェクト114を介しMCH116に接続される。10

#### 【0036】

システム100は、専用ハブインターフェースバス122を使って、MCH116をI/Oコントローラハブ(ICH)130に接続する。ICH130は、ローカルI/Oバスを介していくつかのI/O装置への直接の接続を提供する。ローカルI/Oバスは、周辺装置をメモリ120、チップセット及びプロセッサ102に接続する高速I/Oバスである。いくつかの例は、音声コントローラ、ファームウェアハブ(フラッシュBIOS)128、無線送信機126、データ記憶装置124、ユーザ入力及びキーボードインターフェースを含む既存のI/Oコントローラ、USB(Universal Serial Bus)のようなシリアル拡張ポート、及びネットワークコントローラ134である。データ記憶装置124は、ハードディスクドライブ、フロッピーディスク(登録商標)ドライブ、CD-ROM装置、フラッシュメモリ装置、または他の大容量記憶装置から構成される。20

#### 【0037】

システムの他の実施例では、Packed乘算上位命令を実行する実行ユニットはシステムオンチップと共に利用することができる。システムオンチップの一実施例は、プロセッサとメモリから構成される。そのようなシステムのためのメモリはフラッシュメモリである。フラッシュメモリは、プロセッサ及び他のシステム構成要素と同じチップ上に設けられる。さらに、メモリコントローラやグラフィックスコントローラのような他の論理ブロックがまた、システムオンチップ上に配置されうる。30

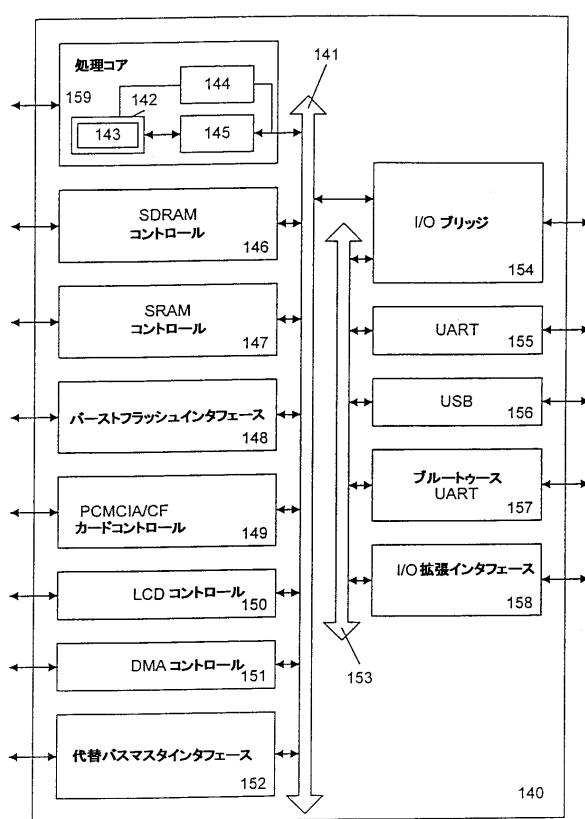

#### 【0038】

図1Bは、本発明の原理を実現するデータ処理システム140の他の実施例を示す。データ処理システム140の一実施例は、(「www.intel.com」にて説明されるような)インテルXScale(商標)技術によるインテル(登録商標)パーソナルインターネットクライアントアーキテクチャ(PCA)アプリケーションプロセッサである。ここで説明される実施例は、発明の範囲から逸脱することなく他の処理システムと共に利用することができるということは、当業者には認識されるであろう。

#### 【0039】

コンピュータシステム140は、乗算上位丸めシフトを含む SIMD処理を実行することができる処理コア159を備える。一実施例において、処理コア159は、CISC、RISC、VLIWタイプアーキテクチャに限定されることなく任意のタイプのアーキテクチャの処理ユニットを表す。処理コア159はまた、1以上の処理技術における製造に適したものであってもよいし、十分詳細にマシン読み出し可能なメディアに表されることにより、処理コア159はこの製造の容易化に適したものであってもよい。40

#### 【0040】

処理コア159は、実行ユニット142、レジスタファイルセット145、及びデコーダ144から構成される。処理コア159はまた、本発明の理解に必要でない追加的な回路(図示せず)を含んでもよい。実行ユニット142は、処理コア159により受信された命令の実行に利用される。典型的なプロセッサ命令の認識に加えて、実行ユニット142はPackedデータフォーマットに対する処理の実行のため、Packed命令セッ50

ト 1 4 3 における命令を認識することができる。Packed 命令セット 1 4 3 は、データマージ処理をサポートする命令を含み、またさらに他の Packed 命令を含んでいてもよい。実行ユニット 1 4 2 は内部バスによりレジスタファイル 1 4 5 に接続される。レジスタファイル 1 4 5 は、データを含む情報の格納のための処理コア 1 5 9 における記憶領域を表す。前述のように、Packed データの格納に利用される記憶領域が何であるかは重要ではないということは理解されるであろう。実行ユニット 1 4 2 はデコーダ 1 4 4 に接続される。デコーダ 1 4 4 は、処理コア 1 5 9 により受信された命令を制御信号及び／あるいはマイクロコード入力ポイントに復号するために利用される。これらの制御信号及び／あるいはマイクロコード入力ポイントに応答して、実行ユニット 1 4 2 は適切な処理を実行する。

10

#### 【0041】

処理コア 1 5 9 は、以下に限定されるものではないが、例えば、SDRAM (Synchronous Dynamic Random Access Memory) コントロール 1 4 6 、SRAM (Static Random Access Memory) コントロール 1 4 7 、バーストフラッシュメモリインターフェース 1 4 8 、PCMCIA (Personal Computer Memory Card International Association) / CF (Compact Flash) カードコントロール 1 4 9 、液晶 (LCD) コントロール 1 5 0 、DMA (Direct Memory Access) コントローラ 1 5 1 、及び代替バスマスタインターフェース 1 5 2 を含む他の様々なシステム装置と通信するためのバス 1 4 1 に接続される。一実施例では、データ処理システム 1 4 0 はまた、I/O バス 1 5 3 を介し様々な I/O 装置と通信するための I/O ブリッジ 1 5 4 を備える。このような I/O 装置は、以下に限定されるものではないが、例えば、UART (Universal Asynchronous Receiver/Transmitter) 1 5 5 、USB 1 5 6 、ブルートゥース無線 UART 1 5 7 、及び I/O 拡張インターフェース 1 5 8 から構成されてもよい。

20

#### 【0042】

データ処理システム 1 4 0 の一実施例は、モバイル、ネットワーク及び／あるいは無線通信のために、シフトマージ処理を含む SIMD 处理を実行することができる処理コア 1 5 9 を備える。処理コア 1 5 9 は、ウォルシュアダマール変換、高速フーリエ変換 (FFT) 、離散コサイン変換 (DCT) 及びそれら各自の逆変換などの離散変換と、色空間変換、映像符号化動き予測または映像復号化動き予測などの圧縮／解凍技術と、パルス符号変調 (PCM) のような変調／復調 (MODEM) 機能とを含む様々な音声、映像、画像形成及び通信アルゴリズムによりプログラムされてもよい。

30

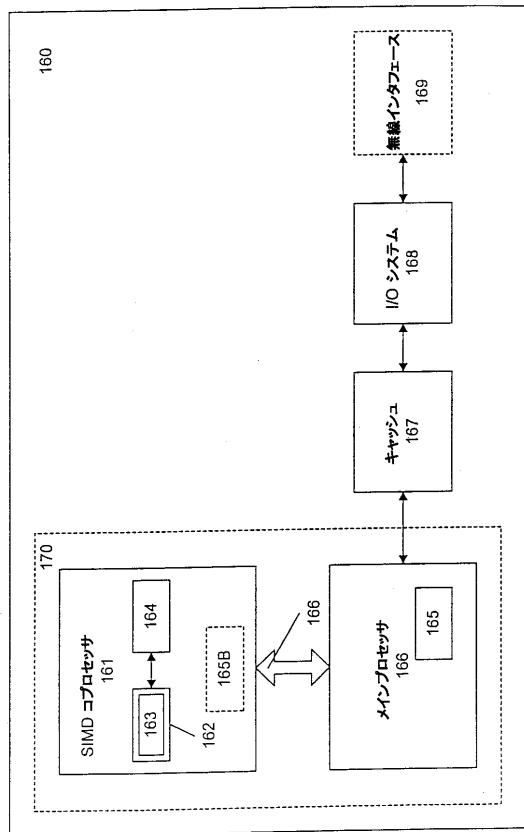

#### 【0043】

図 1 C は、SIMD 乗算上位処理を実行することができるデータ処理システムの他の実施例を示す。他の実施例によると、データ処理システム 1 6 0 は、メインプロセッサ 1 6 6 、SIMD コプロセッサ 1 6 1 、キャッシュメモリ 1 6 7 及び入出力システム 1 6 8 を備える。入出力システム 1 6 8 は、選択的に無線インターフェース 1 6 9 に接続されてもよい。SIMD コプロセッサ 1 6 1 は、乗算上位を含む SIMD 处理を実行することができる。処理コア 1 7 0 は、1 つ以上の処理技術における製造に適したものであってよいし、十分詳細にマシーン読み出し可能なメディアに表すことにより、処理コア 1 7 0 はそれを含んだデータ処理システム 1 6 0 のすべてあるいは一部の製造を容易化するのに適したものであってもよい。

40

#### 【0044】

一実施例において、SIMD コプロセッサ 1 6 1 は、実行ユニット 1 6 2 とレジスタファイルセット 1 6 4 から構成される。メインプロセッサ 1 6 5 の一実施例は、実行ユニット 1 6 2 による実行のため、SIMD Packed 乗算上位命令を含む命令セット 1 6 3 の命令を認識するデコーダ 1 6 5 を備える。他の実施例では、SIMD コプロセッサ 1 6 1 はまた、命令セット 1 6 3 の命令を復号するデコーダ 1 6 5 B の少なくとも一部を備える。処理コア 1 7 0 はまた、本発明の理解に必要でない追加的回路 (図示せず) を含む。

50

## 【0045】

動作中、メインプロセッサ166は、キャッシュメモリ167と入出力システム168との相互作用を含む一般的タイプのデータ処理動作を制御するデータ処理命令のストリームを実行する。S I M Dコプロセッサ命令は、データ処理命令のストリームに埋め込まれる。メインプロセッサ166のデコーダ165は、装着されたS I M Dコプロセッサ161により実行されるべきタイプとしてこれらのS I M Dコプロセッサ命令を発する。従つて、メインプロセッサ166は、これらのS I M Dコプロセッサ命令（あるいはS I M Dコプロセッサ命令を表す制御信号）をコプロセッサバス166において発行し、そこから装着されたS I M Dコプロセッサにより受信される。この場合、S I M Dコプロセッサ161は受信したS I M Dコプロセッサ命令を受領及び実行する。

10

## 【0046】

S I M Dコプロセッサ命令による処理のため、データは無線インターフェース169を介し受信されてもよい。一例として、音声通信はデジタル信号の形式で受け取られ、当該音声信号を表すデジタル音声サンプルを再生成するためS I M Dコプロセッサ命令により処理されてもよい。他の例として、圧縮された音声及び／または映像がデジタルビットストリーム形式で受信され、デジタル音声サンプル及び／または動き映像フレームを再生成するためS I M Dコプロセッサ命令により処理されてもよい。一実施例において、処理コア170、メインプロセッサ166及びS I M Dコプロセッサ161は、実行ユニット162、レジスタファイルセット164及びデコーダ165からなる単一の処理コア170に一体化され、S I M D乗算上位命令を含む命令セット163の命令を認識する。

20

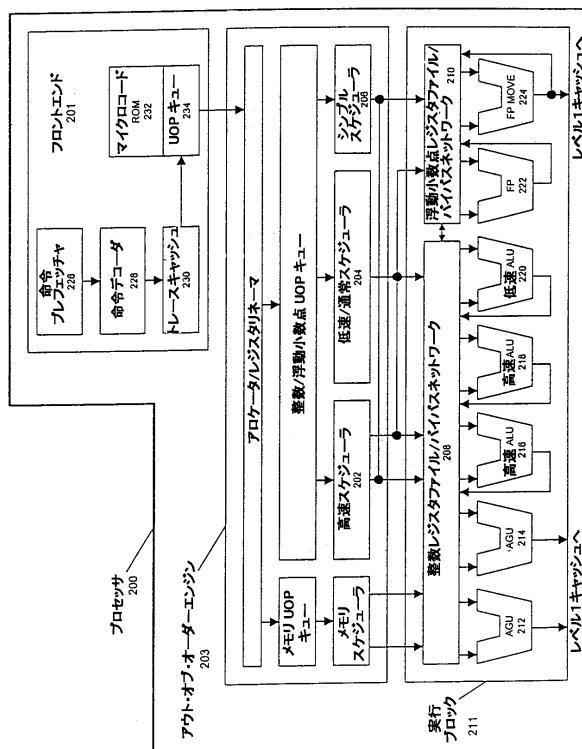

## 【0047】

図2は、本発明によるP a c k e d整数乗算上位丸めシフト処理を実行する論理回路を有する一実施例のプロセッサ200のためのマイクロアーキテクチャのブロック図である。丸め及びシフト処理によるS I M D整数乗算上位処理はまた、P a c k e d乗算上位丸めシフト処理（P M U L上位）、または乗算上位処理と呼ばれるかもしれない。P a c k e d乗算上位命令の一実施例において、当該命令により、2つのメモリブロックからデータが抽出され、仮の結果を得るために各ブロックから対応するデータ要素を掛け合わせ、この仮の結果を丸めシフトし、結果として得るマージされたデータブロックにおける格納のため、この中間結果を各積の所望の上位部分に切り捨てる。S I M D乗算上位命令はまた、P M U L H R S WあるいはP a c k e d乗算上位丸めシフトと呼ばれる。本実施例では、マージ処理はまた、バイト、ワード、ダブルワード、クアドワードなどのサイズを有するデータ要素での処理を行うために実行される。ここでの説明は整数及び整数処理に関するものであるが、本発明の他の実施例は浮動小数点数及び浮動小数点処理で利用されてもよい。

30

## 【0048】

イン・オーダーフロントエンド（i n - o r d e r f r o n t e n d）201は、実行対象のマクロ命令をフェッチし、プロセッサバイオペーラインにおける後の利用のため当該命令を用意するプロセッサ200の一部である。本実施例のフロントエンド201は複数のユニットを備えている。命令プリフェッチャ226は、メモリからマクロ命令をフェッチし、命令デコーダ228に供給し、マシーンにより実行可能なマイクロ命令あるいはマイクロ処理（または、マイクロo pあるいはu o pと呼ばれる）と呼ばれる要素に復号する。トレースキャッシュ230は、復号化されたu o pを受け取り、実行のためu o pキー234においてそれらが順序付けされたプログラムシーケンスあるいはトレースに分解する。トレースキャッシュ230が複雑なマクロ命令に直面すると、マイクロコードR O M 232が当該処理の完了に必要なu o pを提供する。

40

## 【0049】

多くのマクロ命令が1つのマイクロo pに変換される一方、他のマクロ命令は完全な処理の完了のため複数のマイクロo pを必要とする。一実施例では、マクロ命令の完了のため4より多くのマイクロo pが必要な場合、デコーダ228はマイクロコードR O M 232にアクセスし、マクロ命令を実行する。一実施例では、乗算上位丸めシフト命令が、命

50

令デコーダ 228 における処理のため少数のマイクロ op に復号される。他の実施例では、Packed 乗算上位丸めシフトアルゴリズムのための命令が、処理の完了に多数のマイクロ op が必要とされる場合、マイクロ ROM 232 に格納される。トレースキャッシュ 230 は、入力ポイント PLA (Programmable Logic Array) を参照し、マイクロコード ROM 232 におけるマージアルゴリズムのためのマイクロコードシーケンスを読み込むための正しいマイクロ命令ポインタを決定する。マイクロコード ROM 232 が現在のマクロ命令に対するマイクロ op の順序付けを完了すると、マシーンのフロントエンド 201 はトレースキャッシュ 230 からマイクロ op の取り込みを再開する。

## 【0050】

10

いくつかの SIMD 及び他のマルチメディアタイプの命令は複雑な命令とみなされる。浮動小数点に関する大部分の命令もまた複雑な命令である。さらに、命令デコーダ 228 が複雑なマクロ命令に直面すると、マイクロコード ROM 232 は当該マクロ命令のためのマイクロコードシーケンスを抽出するために、適当な位置でアクセスされる。このマクロ命令の実行に要する様々なマイクロ op が、適当な整数及び浮動小数点実行ユニットにおける実行のため、アウト・オブ・オーダー実行エンジン (out-of-order execution engine) 203 に通信される。

## 【0051】

アウト・オブ・オーダー実行エンジン 203 では、実行のためのマイクロ命令が用意されている。アウト・オブ・オーダー実行論理は、マイクロ命令がパイプラインに入り、実行のためスケジューリングされるとき、パフォーマンスを最適化するためマイクロ命令のフローを平滑化及び順序調整をするための複数のバッファを有する。割り当てまたはアロケータ論理は、各 uop が実行に必要とするマシーンバッファやリソースを割り当てる。レジスタリネーム論理は、レジスタファイルの入力の論理レジスタを改名する。割り当て論理はまた、メモリスケジューラ、高速スケジューラ 202、低速 / 通常浮動小数点スケジューラ 204、及びシンプル浮動小数点スケジューラ 206 の命令スケジューラの前に、メモリ処理及び非メモリ処理のための 2 つの uop キューの 1 つへの各 uop の入力を割り当てる。uop スケジューラ 202、204 及び 206 は、スケジューラの従属入力レジスタオペランドソースの準備状況と、uop が処理の遂行に必要とする実行リソースの利用可能状況に基づき、uop の実行準備がいつ整うかを判断する。本実施例の高速スケジューラ 202 がメインロックサイクルの半サイクルごとにスケジューリングを行う一方、その他のスケジューラはメインプロセッサロックサイクルあたり 1 回だけスケジューリングを行うことができる。スケジューラはディスパッチポートを調停して、実行のための uop をスケジューリングする。

20

## 【0052】

30

レジスタファイル 208 と 210 は、スケジューラ 202、204 及び 206 と、実行ブロック 211 の実行ユニット 212、214、216、218、220、222 及び 224 との間に配置される。整数及び浮動小数点演算のためにそれぞれレジスタファイル 208 と 210 がある。本実施例のレジスタファイル 208 と 210 のそれぞれはまた、まだレジスタファイルに書き込まれていない終了結果を新しい従属 uop にバイパスあるいは転送するバイパスネットワークを含む。整数レジスタファイル 208 と 浮動小数点レジスタファイル 210 はまた、互いにデータの通信を行うことができる。一実施例において、整数レジスタファイル 208 は 2 つのレジスタファイルに分割され、その一方は下位 32 ビットデータ用のレジスタファイルであり、もう一方は上位 32 ビットデータ用のレジスタファイルである。一実施例の浮動小数点レジスタファイルは 210 は、128 ビット幅の入力を有する。これは浮動小数点命令は典型的に、64 から 128 ビット幅のオペランドを有するからである。

40

## 【0053】

実行ブロック 211 は、命令を実際に実行する実行ユニット 212、214、216、218、220、222 及び 224 を含む。この部分は、マイクロ命令が実行に必要とす

50

る整数及び浮動小数点データオペランド値を格納するレジスタファイル208と210を含む。本実施例のプロセッサ200は、アドレス生成ユニット(AGU)212、AGU214、高速ALU216、高速ALU218、低速ALU220、浮動小数点ALU222及び浮動小数点移動ユニット224からなる複数の実行ユニットから構成される。本実施例において、浮動小数点実行ブロック222と224は、浮動小数点処理、MMX処理、SIMD処理及びSSE処理を実行する。本実施例の浮動小数点ALU222は、割算、平方根及び剰余に関するマイクロopを実行するための64ビット単位浮動小数点割算器を有する。本発明の実施例では、浮動小数に関する任意の処理は浮動小数点ハードウェアで行われる。例えば、整数形式と浮動小数形式間の変換には、浮動小数点レジスタファイルが関与する。同じように、浮動小数割算処理は浮動小数点割算器において行われる。

10

#### 【0054】

他方、非浮動小数点数及び整数タイプは整数ハードウェアリソースにより処理される。単純かつ頻繁に使用されるALU演算は、高速ALU実行ユニット216と218において処理される。本実施例の高速ALU216と218は、半分のクロックサイクルの効果的な待ち時間により高速処理を実行することができる。一実施例では、大部分の複雑な整数演算は低速ALU220に渡される。低速ALU220は、乗算、シフト、フラグ論理及び分岐処理のような長い待ち時間を要するタイプの処理用の整数実行ハードウェアを含む。メモリロード/ストア処理は、AGU212と214により実行される。本実施例では、整数ALU216、218及び220は、64ビットデータオペランドに対する整数処理の実行について説明される。他の実施例では、ALU216、218及び220は、16、32、128、256などの様々なデータビットをサポートするよう実現することができる。同じように、浮動小数点ユニット222と224は、様々なビット幅を有するオペランドをサポートするよう実現することができる。一実施例では、浮動小数点ユニット222と224は、SIMD及びマルチメディア命令について、128ビット幅のPackedデータオペランドにおいて実行される。

20

#### 【0055】

オペランドを特定するマクロ命令の一部として利用されるオン・ボードプロセッサ記憶領域を参照するのに、ここでは「レジスタ」という単語が使われる。言い換えると、ここで呼ばれるレジスタとは、プロセッサ外部から(プログラマーの視点から)見ることができるものである。しかしながら、一実施例のレジスタは特定タイプの回路に限定されない。むしろ一実施例のレジスタはデータの格納及び提供、及びここで説明される機能の実行が可能であればよい。ここで述べられるレジスタは、例えば、専用物理レジスタ、レジスタリネーミングを利用することによる動的に割り当てられた物理レジスタ、専用物理レジスタと動的に割り当てられる物理レジスタとを組み合わせたものなどの様々なテクニックを利用したプロセッサ内部の回路により実現することができる。一実施例では、整数レジスタは32ビット整数データを格納している。一実施例のレジスタファイルはまた、Packedデータのための8つのマルチメディア SIMD レジスタを含んでいる。以下の説明のため、レジスタは、カリフォルニア州サンタクララのインテルコーポレーションからのMMX技術が可能なマイクロプロセッサにおける64ビット幅MMX(商標)レジスタ(mmレジスタ)のようなPackedデータの保持が可能なデータレジスタであると解釈される。このようなMMXレジスタは、整数及び浮動小数点の両方の形式で利用可能であり、SIMDとSSE命令を伴うPackedデータ要素により動作可能である。同様に、SSE2技術に関する128ビット幅XMMレジスタもまた、そのようなPackedデータオペランドの保持に利用可能である。本実施例では、Packedデータと整数データの格納において、レジスタは2つのデータタイプ間での区別をする必要はない。

30

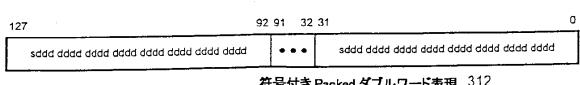

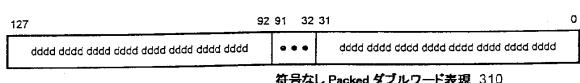

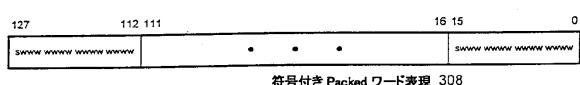

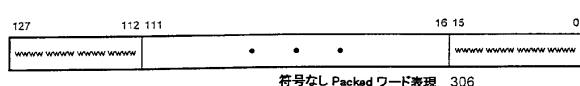

#### 【0056】

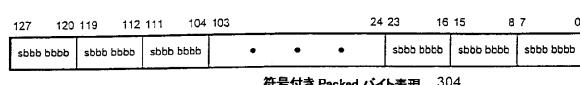

図3Aは、本発明の一実施例による128ビット幅のマルチメディアレジスタでの様々な符号付き及び符号なしPackedデータタイプ表現を示す。本実施例のPacked

40

50

バイトフォーマットは 6 つの Packed バイトデータ要素を含んでいる。バイトは 8 ビットデータとして定義される。符号なし Packed バイト表現 302 は、 SIMD レジスタへの符号なし Packed バイトの格納を示している。各バイトデータ要素の情報が、第 0 バイトに対しては第 7 ビットから第 0 ビットに、第 1 バイトに対しては第 15 ビットから第 8 ビットに、第 2 バイトに対しては第 23 ビットから第 16 ビットに、最後に第 15 バイトに対しては第 128 ビットから第 120 ビットにそれぞれ格納される。従って、利用可能なすべてのビットがレジスタにおいて利用される。この格納配置により、プロセッサの記憶効率の向上がもたらされる。16 のデータ要素がアクセスされると、1 つの処理が 16 のデータ要素に対し並列に実行される。

## 【0057】

10

符号付き Packed バイト表現 304 は符号付き Packed バイトの格納を示す。すべてのバイトデータ要素の第 8 ビットは符号標識である。本実施例の Packed ワードフォーマットは 8 つの Packed ワードデータ要素を含む。各 Packed ワードは 16 ビットの情報を含んでいる。符号なし Packed ワード表現 306 は、第 7 ワードから第 9 ワードが SIMD レジスタにどのように格納されているかを示している。符号付き Packed ワード表現 308 は符号なし Packed ワードイン・レジスタ表現 306 と同様である。ここで、各ワードデータ要素の第 16 ビットは符号標識である。Packed ダブルワードフォーマットは 128 ビット長であり、4 つの Packed ダブルワードデータ要素を含んでいる。各 Packed ダブルワード要素は 30 ビットの情報を含んでいる。符号なし Packed ダブルワード表現 310 は、ダブルワード要素がどのように格納されているかを示している。符号付き Packed ダブルワード表現 312 は符号なし Packed ダブルワードイン・レジスタ表現 310 と同様である。ここで、必要な符号ビットは各ダブルワードデータ要素の第 32 ビットである。Packed クアドワードは 128 ビット長であり、2 つの Packed クアドワードデータ要素を含んでいる。

20

## 【0058】

一般に、データ要素は、1 つのレジスタあるいはメモリ領域に同じ長さの他のデータ要素と共に格納されるデータ部分である。SSE2 技術に関する Packed データシーケンスにおいて、XMM レジスタに格納されるデータ要素数は、各データ要素のビット長により割られた 128 ビットである。同様に、MMX 及び SSE 技術に関する Packed データシーケンスでは、MMX レジスタに格納されるデータ要素数は、各データ要素のビット長により割られた 64 ビットである。図 3A に示されたデータタイプは 128 ビット長であるが、本発明の実施例はまた 64 ビット幅あるいは他のサイズのオペランドにおいて動作可能である。

30

## 【0059】

40

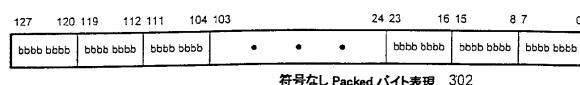

図 3B は、他のイン・レジスタデータ記憶フォーマットを示す。各 Packed データは複数の独立データ要素を含みうる。Packed ハーフ 341、Packed シングル 342 及び Packed ダブル 343 の 3 つの Packed データフォーマットが示される。Packed ハーフ 341、Packed シングル 342 及び Packed ダブル 343 の一実施例は定点データ要素を含んでいる。他の実施例では、Packed ハーフ 341、Packed シングル 342 及び Packed ダブル 343 の 1 つ以上が浮動小数点データ要素を含みうる。Packed ハーフ 341 の他の実施例は、8 つの 16 ビットデータ要素を含む 128 ビット長である。Packed シングル 342 の一実施例は、128 ビット長であり、4 つの 32 ビットデータ要素を含む。Packed ダブル 343 の一実施例は、128 ビット長であり、2 つの 64 ビットデータ要素を含む。このような Packed データフォーマットは、例えば、96 ビット、160 ビット、192 ビット、224 ビット、256 ビットあるいはそれ以上の他のレジスタ長にさらに拡張することが可能であるということは理解されるであろう。

## 【0060】

図 3C は、「www.intel.com/design/litcenter」を介し

50

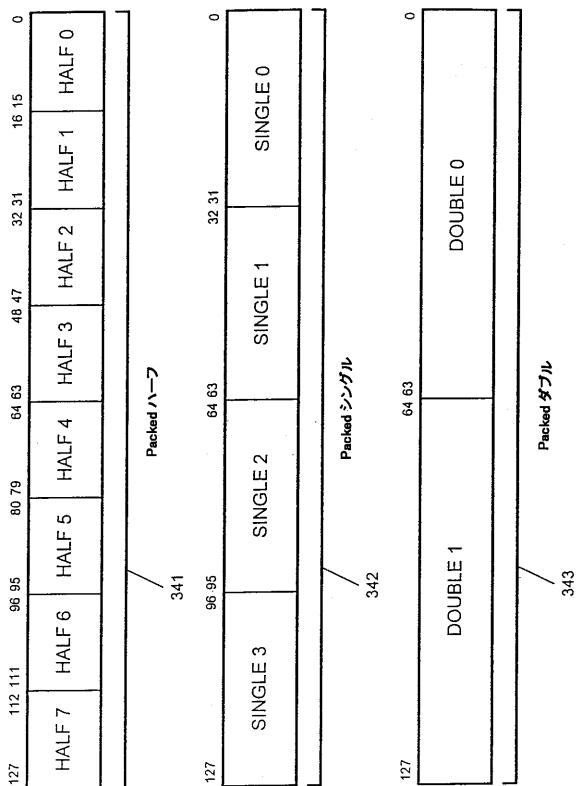

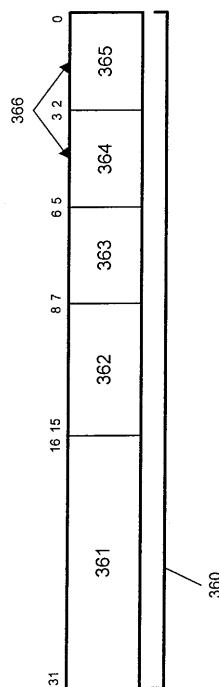

インテルコーポレーションから利用可能な「IA-32インテルアーキテクチャソフトウェア開発者のためのマニュアル2」において説明されている一タイプの処理符号化フォーマット(オペコード)に対応する32以上のビットを有する処理符号化フォーマットとレジスタ/メモリオペランドアドレッシングモードの一実施例を示す。丸めシフトによる乗算上位処理のタイプが、1つ以上のフィールド361と362により符号化される。2つまでのソースオペランド識別子364と365を含めて命令あたり2つまでのオペランドの位置が特定される。シフトマージ命令の一実施例において、宛先オペランド識別子366はソースオペランド識別子364と同一である。他の実施例においては、宛先オペランド識別子366はソースオペランド識別子365と同一である。従って、シフトマージ処理の一実施例において、ソースオペランド識別子364と365により特定されるソースオペランドの1つが乗算上位丸めシフト処理の結果により上書きされる。シフトマージ命令の一実施例において、オペランド識別子364と365は、64ビットソース及び宛先オペランドの特定に利用されうる。

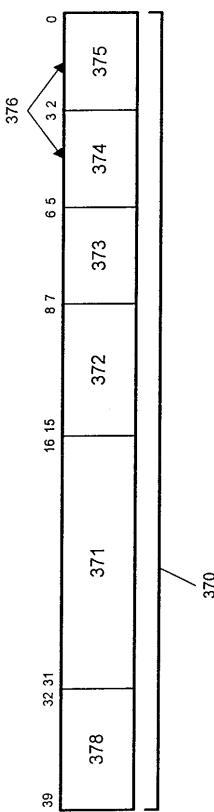

#### 【0061】

図3Dは、40ビット以上を有する他の処理符号化(オペコード)フォーマット370を示す。オペコードフォーマット370は、オペコードフォーマット360に対応し、選択的なプレフィックスバイト(prefix byte)378から構成される。乗算上位丸めシフト処理のタイプが1つ以上のフィールド378、371及び372により符号化される。命令あたり2つまでのオペランド位置がソースオペランド識別子374と375、及びプレフィックスバイト378により特定される。Packed乗算上位丸めシフトの一実施例において、128ビットソース及び宛先オペランドの特定にプレフィックスバイト378が利用される。乗算上位命令の一実施例において、宛先オペランド識別子376はソースオペランド識別子374と同じである。他の実施例において、宛先オペランド識別子376はソースオペランド識別子375と同じである。従って、乗算上位処理の実施例において、ソースオペランド識別子374と375により特定されるソースオペランドの1つが乗算上位処理の結果により上書きされる。オペコードフォーマット360と370はMODフィールド363と373及び選択的なスケール-インデックス-ベース(scale-index-base)及びディスプレースメント(displacement)バイトにより部分的に特定されるレジスタ・ツー・レジスタ(register to register)、メモリ・ツー・レジスタ(memory to register)、レジスタ・バイ・メモリ(register by memory)、レジスタ・バイ・レジスタ(register by register)、レジスタ・バイ・即値(register by immediate)、レジスタ・ツー・メモリ(register to memory)アドレッシングを可能にする。

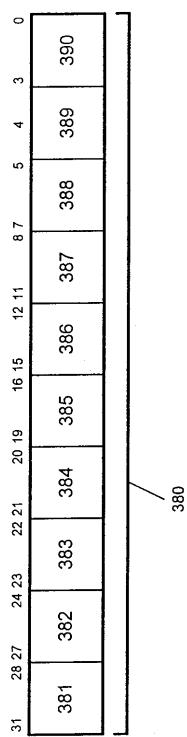

#### 【0062】

図3Eに示されるように、他の実施例では、64ビット単一命令多重データ(SIMD)算術処理が、コプロセッサデータ処理(CDP)命令を通じ実行される。処理符号化(オペコード)フォーマット380は、CDPオペコードフィールド382と389を有するCDP命令を示す。乗算上位丸めシフト処理の他の実施例では、CDP命令のタイプは1つ以上のフィールド383、384、387及び388により符号化される。2つまでのソースオペランド識別子385と390及び1つの宛先オペランド識別子386を含めて命令あたり3つまでのオペランド位置が特定される。コプロセッサの一実施例は、8、16、32及び64ビット値に対し動作することができる。一実施例において、固定点または整数データ要素に対し乗算上位処理が実行される。いくつかの実施例では、マージ命令が条件フィールド381を利用して条件付きで実行されてもよい。いくつかの乗算上位命令では、ソースデータのサイズがフィールド383により符号化される。シフトマージ命令のいくつかの実施例では、ゼロ(Z)、ネガティブ(N)、キャリー(C)及びオーバーフロー(V)の検出がSIMDフィールドにおいて実行される。いくつかの命令では、サチュレーション(saturation)のタイプがフィールド384により符号化される。

10

20

30

40

50

## 【0063】

本発明の一実施形態では、Packed乗算上位丸めシフトは、命令フォーマットPMULHRSWmm1、mm2/m64により表される。本例におけるPMULHRSWは、Packed乗算上位丸めシフトワードの記憶の助けとなるものである。この場合、2つのソースオペランドmm1とmm2/m64が付随する命令である。本実施形態の命令は、複数のより小さいデータ要素から構成される64ビットPackedデータブロックにより実行される。この場合、各データ要素は16ビットまたはワードの長さを有する。合計64ビットを形成する4つのワードが各Packedデータブロックに含まれる。第1ソースオペランド「mm1」は64ビットMMXレジスタである。本実施例では、第1ソースオペランドからの64ビットMMXレジスタ「mm1」はまた、Packed乗算上位丸めシフト処理の結果の宛先である。本例における第2ソースオペランド「mm2/m64」は、64ビットMMXレジスタ(mm2)あるいは64ビットメモリ位置(mm64)でありうる。10

## 【0064】

以下で説明される例は一般に64ビット長オペランドとデータブロックに関するものであるが、乗算上位丸めシフト命令の実施例はまた128ビットPackedデータブロックにより処理される。例えば、一実施例の命令フォーマットは、PMULHRSWxm1、xmm2/m128として表すことができる。この場合における2つのソースオペランドはそれぞれ128ビット長であり、それぞれは16ビットワードサイズの8つのデータ要素から構成される。第1ソースオペランド「xmm1」は128ビットXMMレジスタである。本実施例において、XMMレジスタ「xmm1」はまた結果の宛先である。本実施例における第2ソースオペランド「xmm2/m128」は、128ビットXMMレジスタ(xmm2)または128ビットメモリー(m128)である。本実施例では、各データブロックは符号付き整数を含むことができる。一実施例では、符号付き整数は2の補数フォーマットである。20

## 【0065】

さらに、ここで説明される実施例はワードサイズのデータ要素から構成されるPackedデータブロックに関するものであるが、他の様々なサイズのデータ要素もまた考慮される。例えば、Packed乗算上位丸めシフト命令の他の実施例が、バイト、ダブルワードまたはクアドワードの長さを有するデータ要素に対し実行されてもよい。同じように、データオペランドの長さは64及び128に制限されない。例えば、他の実施例による命令は256ビット長のPackedオペランドに対し実行される。30

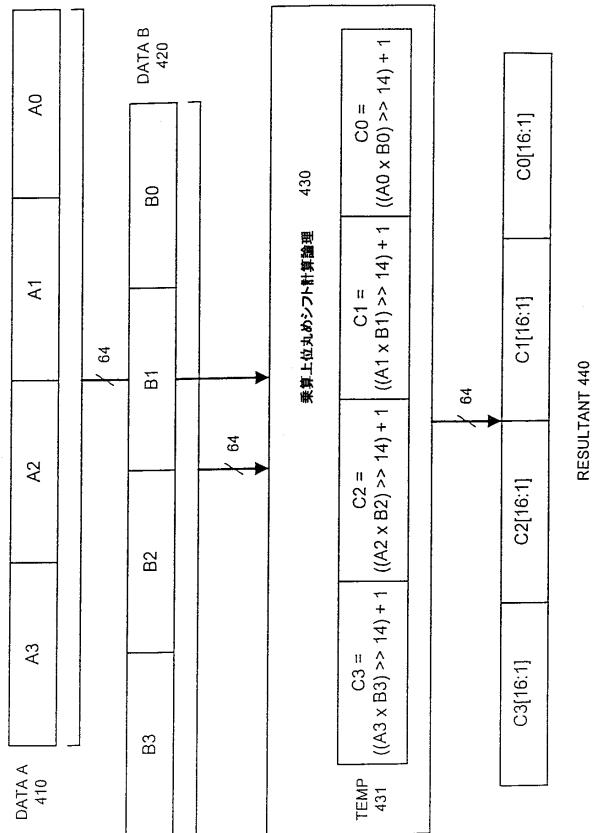

## 【0066】

図4Bは、本発明によるデータオペランドに対するSIMD整数乗算上位丸めシフト処理を実行するための論理の一実施例のブロック図である。本実施例による乗算上位丸めシフト処理(または簡単化のため、乗算上位)のためのPMULHRSWは、第1データオペランドDATAA410と第2データオペランドDATAB420の2つの情報から開始される。一実施例では、PMULHRSW乗算上位命令は1つのマイクロ処理に復号化される。他の実施例では、データオペランドに乗算上位処理を実行するため、当該命令は可変数のマイクロopに復号化される。40

## 【0067】

ここで、DATAA410、DATAB420とRESULTANT440は、以下に限定されるものではないが、一般にオペランドあるいはデータブロックと呼ばれ、レジスタ、レジスタファイル及びメモリ領域を含む。一実施例では、DATAA410とDATAB420は64ビット幅のMMXレジスタ(または、いくつかの例では、「mm」と呼ばれる)である。特定の実施形態に応じて、データオペランドは128または256ビットのような他の幅とすることができます。第1オペランド410と第2オペランド420は、x個のデータ要素を含むデータブロックであり、各データブロックが1バイト(8ビット)である場合、それぞれが合計8xビット幅を有する。従って、各データセグメントは8xビット幅となる。ここでxが8であるとき、各オペランドは8バイトまたは64ビットである。50

ト幅である。他の実施例では、データ要素は、ニブル(4ビット)、ワード(16ビット)、ダブルワード(32ビット)、クアドワード(64ビット)などであってもよい。他の実施例では、 $\times$ は16、32、64等のデータ要素幅であってもよい。

#### 【0068】

本実施例における第1 Packedオペランド410は、4つのデータ要素A3、A2、A1及びA0から構成される。第2 Packedオペランド420はまた、4つのデータ要素B3、B2、B1及びB0から構成される。ここでデータ要素は同じ長さを有し、それぞれ1ワード(16ビット)のデータから構成される。しかしながら、本発明の他の実施例は、各データセグメントが1バイト(8ビット)からなるより長い128ビットオペランドにおいて処理され、128ビット幅オペランドは16バイト幅のデータセグメントを有する。同様に、各データセグメントがダブルワード(32ビット)またはクアドワード(64ビット)である場合、128ビットオペランドはそれぞれ、4ダブルワード幅あるいは2クアドワード幅のデータセグメントを有する。本発明の実施例は特定の長さのデータオペランドあるいはデータセグメントに制限されず、各実施形態に適したサイズとすることができる。10

#### 【0069】

オペランド410と420は、レジスタ、メモリ領域、レジスタファイルあるいはそれらの組み合わせたものに配置される。データオペランド410と420は乗算上位丸めシフト命令と共に、プロセッサの実行ユニットの乗算上位丸めシフト計算論理430に送られる。PMULHRSW命令が実行ユニットに達するまで、プロセッサパイプラインにおいて当該命令は前もって復号されるべきである。従って、乗算上位命令はマイクロ処理(uop)あるいは他の復号化フォーマットの形式に従う。本実施例では、2つのデータオペランド410と420は、乗算上位丸めシフト計算論理430において受信される。本実施例は64ビット幅オペランドに対し実行されるので、仮のスペース431は128ビット幅の中間結果の積を保持する必要がある。128ビット幅のデータオペランドに対し、256ビット幅の仮スペースが必要とされる。20

#### 【0070】

本実施例の論理430はまず、積 $A \times B$ を得るために各要素位置において対応するデータ値を掛け合わせる。4つの位置に対する $A \times B$ の各中間32ビット値はそれぞれ18ビットに切り捨てられる。本実施例では、切り捨て(truncation)は各32ビット値を14ビットだけ右シフトし、これらのビットを取り除くことにより行われる。これにより、各仮の値には18ビットが残される。1つの「1」が丸め処理のため本実施例の最下位ビットに付け加えられる。丸められた各値の最上位ビットのすぐ右の16ビットが、結果440の各データ要素位置に出力される。本実施例における最左データ要素位置において、当該結果は「((A3 × B3) >> 14) + 1」のビット[16:1]に等しい。丸められた結果のビット[16:1]の選択は、小数演算と同じようにこの値を適切にスケーリングする。30

#### 【0071】

本発明の他の実施例は、例えば、128/256/512ビット幅のオペランド、ビット/バイト/ワード/ダブルワード/クアドワードサイズのデータセグメント、8/16/32ビット幅のシフトカウントのような他の長さのオペランド及びデータセグメントに対し実行可能である。従って、本発明の実施例は、特定の長さのオペランド、データセグメント及びシフトカウントに制限されるものでなく、各実施形態に適したサイズとすることができる。40

#### 【0072】

実行時、一実施例のPacked整数乗算上位丸めシフト命令は、第1ソースオペランド及び第2ソースオペランドのPacked符号付き整数ワードの SIMD 符号付き16ビット $\times$ 16ビットの乗算を実行し、正確な32ビット中間積を生成する。一実施例における中間積はまず上位18ビットに切り捨てられる。この18ビットの選択により、18ビットの中間精度が与えられる。18ビット値の最下位ビットに「1」を付け加えること50

により、この切り捨てられた値に対し丸め処理が行われる。言い換えると、丸め処理は、もとの32ビット中間積の第14ビットにおけるビット値に「1」を加えるというものである。18ビットの値の最上位ビットのすぐ右に16ビットを選択することにより最終的な結果が得られる。本実施例では、結果の各値は1つの符号ビットを含んでいる。本実施例の結果の各データ要素は「1.15」の固定点整数フォーマットを有することが可能である。本実施例の乗算上位丸めシフト命令は、各丸めシフトされた中間32ビット値の16ビットを宛先オペランドの適当な位置に格納する。

#### 【0073】

本実施例において、これと他のデータ要素位置の結果が、ソースデータオペランドと同じサイズのデータブロック結果にPackedされる。例えば、ソースPackedデータオペランドが64または128ビット幅である場合、結果として得られるPackedデータブロックもまたそれぞれ64または128ビット幅となる。さらに、符号処理に対するソースデータオペランドはレジスタまたはメモリ領域から得られる。本実施例では、結果として生じるPackedデータブロックは、ソースデータオペランドの1つのためにSIMDレジスタのデータを上書きする。

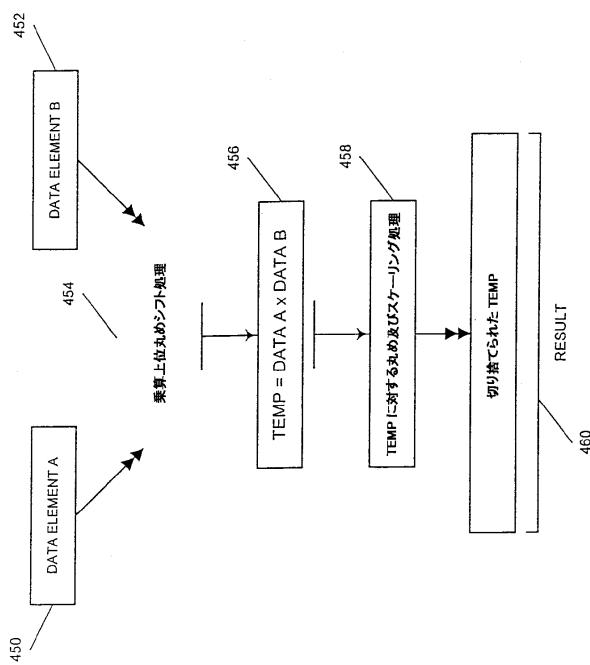

#### 【0074】

図4Bは、選択されたデータ要素位置に対する整数乗数上位丸めシフト処理の動作のブロック図である。DATA ELEMENT A450は第1ソースオペランドからのものである。DATA ELEMENT B452は第2ソースオペランドからのものである。本実施例の乗算上位丸めシフト処理454は、中間値TEMP456の積を生成するため、データ要素を掛け合わせることにより開始される。2つの16ビット幅ソースデータ要素に対し、積は32ビット中間値である。本実施例において、TEMP456の最上位18ビットが丸めスケーリング処理に利用される。18ビットを維持することにより、計算におけるさらなる精度が達成できる。乗算上位丸めシフト処理454は、最新の中間値458を得るために中間値456に対し丸め及びスケーリング処理実行することにより継続される。本実施例では、32ビット中間値TEMP456の第14ビットに「1」を加えることにより丸め処理は行われる。ところで、32ビット値の第14ビットはまた、興味のある18ビット幅部分の最下位ビットでもある。中間値をスケーリングするために、32ビットの丸められた値に対しシフト処理が行われる。最新の中間値458に到達するため、1ビットの左シフトが丸められた値に対し実行される。最新の中間値458は切り捨てられ、RESULT460が得られる。本実施例において、興味のあるビットは最新の32ビット中間値458の上位16ビットであり、RESULT460として格納される。下位16ビットは切り捨て処理において切り捨てられる。

#### 【0075】

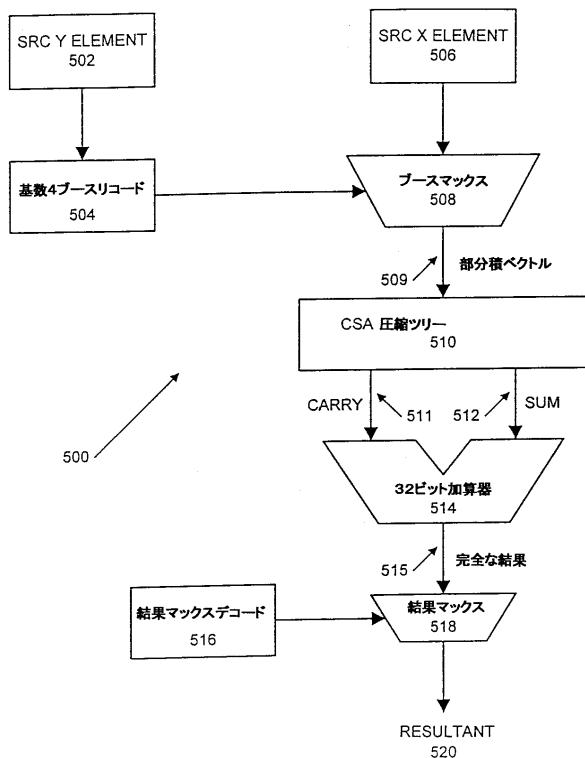

図5は、本発明による乗算上位丸めシフト処理を実行する回路500の一実施例のブロック図である。本実施例の回路500は、ベクトル複合整数ユニット(vector complex integer unit)内に設けられる。この整数ユニットはPMULHRSW命令を128ビットオペランドによる実施形態のため、それぞれが16ビット×16ビットの乗算を実行する8つのパートに分割される。64ビットオペランドによる実施形態では、4つのパートが必要とされる。図5では、SRC Y ELEMENT 502が基数4のブースリコード(radix-4 booth recode)ブロック504に送られる。SRC X ELEMENT 502はブースマックス(booth mux)508において受け取られる。ブースマックスは、9つの部分積ベクトル509を生成する。

#### 【0076】

手計算による掛け算処理において、あるオペランド(A)の最下位ビットを抽出し、このビットをもう一方のオペランド(B)の各桁とビット単位で掛け合わせることにより処理が開始される。乗算対象Aの各ビットに対し、1行の結果が生成される。これらの行のそれぞれは部分積として知られている。例えば、

10

20

30

40

【表1】

```

1001 (9)

x 0110 (6)

-----

0000

1001

1001

+ 0000

-----

0110110 (54)

```

10

大きな数の乗算ではすべての部分積を処理するために、多くのハードウェアが必要とされるので、計算の簡単化のために一実施例においてブースリコード技術が実行される。ブースリコード処理では、部分積の半数をわずかに上回る( $N$ ビット / 2 + 1)が、手計算と同じように生成される。例えば、上記4つの部分積を得る代わりに、ブースリコード処理は3つの部分積を生成する。従って、 $16 \times 16$ の乗数に対して、加えられるべき部分積は「16 / 2 + 1」、すなわち9となる。この方法は基数4とここで呼ばれる。各16ビット乗算配列は、基数4のブース符号化配列である。ブース符号化処理では9つの部分積が生成され、これは桁上げ和加算器(CSA)ツリー構造と加算器により低減された。一実施例では、CSAツリーの16ビット配列構造の全体は、以下のようなものである。

20

【 0 0 7 7 】

【表2】

```

4      4      33      2      1      10      0 bit

765432109876543210987654321098765432109876543210

pp      rowI_p1

ls=-----pp0000000000000000  I 8

ls=-----pp0000000000000000  H 7

ls=-----pp0000000000000000  G 6

ls=-----pp0000000000000000  F 5

ls=-----pp0000000000000000  E 4

ls=-----pp0000000000000000  D 3

ls=-----pp0000000000000000  C 2

ls=-----pp0000000000000000  B 1

sSS=-----A 0

```

30

本実施例は負の乗算を扱えるよう構成されている。「S」は符号を表し、「P」は前の部分積の下位2ビットを記述するのに利用されている。例えば、部分積1の「pp」は部分積0の最下位2ビットである。先頭の符号拡張の本質は、符号ビットをロールオフすることである。これは、乗算前に、負の数を正にする2の補数のビット反転と同様である。同じように、「P」ビットの本質は、負から正への変換の2の補数反転に対し+1を与えるということである。

40

【 0 0 7 8 】

ビット[31:16]は、乗算の上位結果ビットとしてみなすことができる。しかしながら、乗算上位丸めシフトでは、最終結果前に丸め処理とシフト処理が扱われる。一実施例では、丸め処理は配列のビット位置14に「1」を加えることに関する。しかしながら、部分積ツリーの第14ビットには「1」を容易に加えるための空き位置がない。第8行では、ビット13、12及び11が空き位置である。同じように、第7行のビット11に空き位置がある。以下のRビットに示されるように、「1」をこれら4つの位置のすべてに加えることは「1」をビット位置14まで拡げることになる。本実施例の丸め技術では

50

、CSA圧縮ツリー510は、以下のようになる。

【0079】

【表3】

|                                                  |   |    |   |   |    |   |         |    |

|--------------------------------------------------|---|----|---|---|----|---|---------|----|

| 4                                                | 4 | 33 | 2 | 1 | 10 | 0 |         |    |

| 765432109876543210987654321098765432109876543210 |   |    |   |   |    |   | rowI_pl |    |

| pp                                               |   |    |   |   |    |   |         |    |

| 1s-----ppRRR000000000000                         |   |    |   |   |    |   | I 8     |    |

| 1s-----ppR000000000000                           |   |    |   |   |    |   | H 7     |    |

| 1s-----pp000000000000                            |   |    |   |   |    |   | G 6     |    |

| 1s-----pp000000000000                            |   |    |   |   |    |   | F 5     |    |

| 1s-----pp000000000000                            |   |    |   |   |    |   | E 4     |    |

| 1s-----pp000000000000                            |   |    |   |   |    |   | D 3     |    |

| 1s-----pp000000000000                            |   |    |   |   |    |   | C 2     |    |

| 1s-----pp000000000000                            |   |    |   |   |    |   | B 1     | 10 |

| 1s-----pp000000000000                            |   |    |   |   |    |   | A 0     |    |

|                                                  |   |    |   |   |    |   |         |    |

| ---pmulhrsw---                                   |   |    |   |   |    |   |         |    |

本発明の実施例はCSAを利用して、32ビット加算器514前に部分積の項数を9から2に減らすのに役立つ。一実施例では、CSA圧縮ツリーは部分積の項数を(4:2CSAを利用して)まず9から6に、その後6から4に、最後に4から2に減らしていく。このテクニックは9つの32ビット加算器に対する必要性を回避する。本実施例におけるCSAツリー510の出力は、2に減じられた部分積の項である。1つは最後のCSAの合計項であり、もう1つは桁上がり「carry out」の項である。完全な結果を得るためにこれら2つの項を論理的に加えるために、桁上がり項は合計項と適切に一致するよう1ビット左にシフトされねばならない。例えば、桁上がり項の最下位ビットであるビット0は、合計項のビット1と並べられる必要がある。

【0080】

32ビット加算器514は、SUM512とCARRY511を加算することにより、FULL RESULT515を生成する。本実施例のSUM512はSUM[31:0]である。Carry511は1ビット左にシフトされたCarry[30:0]である。本実施例に関連するビットは、ビット[30:15]である。これら16ビットが、上記乗算の積から1ビットだけシフトされる。回路500の本実施例において、このシフト処理は、結果マックス518と結果マックスでコード516により実現される。従って、符号付き整数乗算上位丸めシフト処理のRESULTANT520は、FULL RESULT515の最上位ビットのすぐ右の16ビット、すなわち、FULL RESULT[30:16]となる。本実施例において、データ要素の各ペアに対して8つの配列構造のそれぞれからの結果が、最終的な128ビットの結果を得るために連結される。

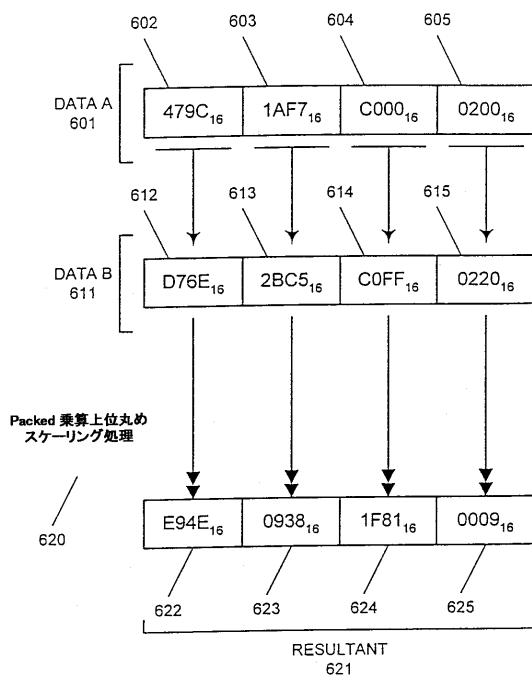

【0081】

図6Aは、本発明の第1実施例によるPacked乗算上位丸めシフト命令の動作を示す。64ビット幅のソースオペランドDATA\_A601は、それぞれが16進数479C<sub>16</sub>、1AF7<sub>16</sub>、C000<sub>16</sub>及び0200<sub>16</sub>を格納する4つのデータ要素602、603、604及び605から構成される。同様に、64ビット幅のソースオペランドDATA\_B611は、それぞれが16進数D76E<sub>16</sub>、2BC5<sub>16</sub>、C0FF<sub>16</sub>及び0220<sub>16</sub>を有する4つのデータ要素612、613、614及び615から構成される。ソースオペランドとしてDATA\_A601とDATA\_B611と共に、本発明の一実施例によるPacked乗算上位丸めスケーリング命令は、RESULTANTオペランド621を生成する。本実施例のPacked乗算上位丸めスケーリング処理620は、ソースデータ要素の対応する各ペアに対し結果を生成する。本実施例では、RESULTANT621の4つのデータ要素は、16進数E94E<sub>16</sub>622、0938<sub>16</sub>623、1F81<sub>16</sub>624及び0009<sub>16</sub>625を有する。

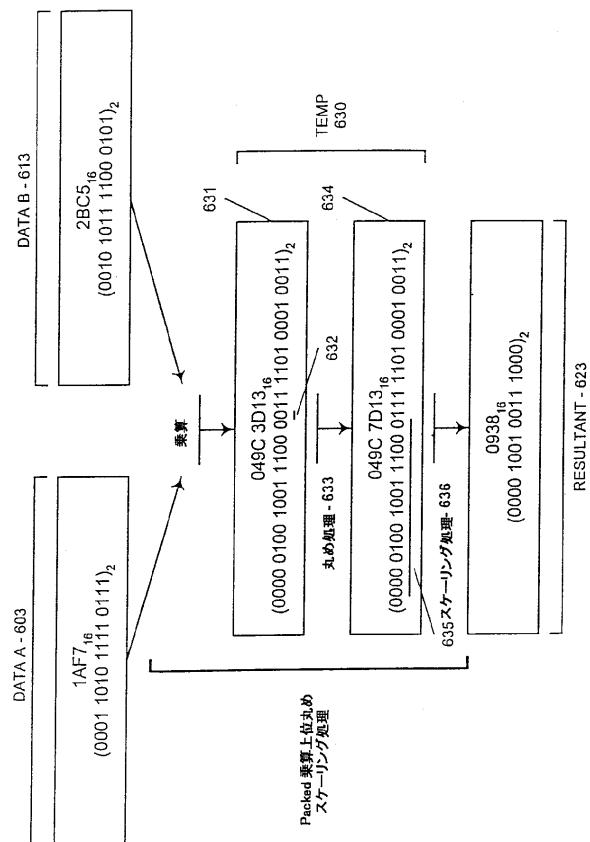

【0082】

図6Bは、図6Aの特定のデータ要素位置におけるPacked乗算上位命令のさらな

10

20

30

40

50

る詳細な動作を示す。図6 Aの例から継続して、ここでは左から2番目のデータ要素位置がより詳細に説明される。DATA A 6 0 1 の第2最左データ要素6 0 3 の値は1 A F 7<sub>16</sub> (あるいは、2進数では0 0 1 1 0 1 0 1 1 1 0 1 1 1) である。DATA B 6 1 1 の第2最左データ要素6 1 3 の値は2 B C 5<sub>16</sub> (あるいは、2進数では0 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1) である。Packed乗算上位丸めスケーリング処理において、これら2つの値はまず掛け合わされ、0 4 9 C 3 D 1 3<sub>16</sub> (0 0 0 0 0 1 0 0 1 1 1 0 0 0 0 1 1 1 1 0 1 0 0 0 1 0 0 1 1 2) の積6 3 1 が得られる。この積6 3 1 は、第1の仮の中間値TEMP 6 3 0 として扱われる。

#### 【0083】

この処理の丸め部分6 3 3 が積6 3 1 に対し実行される。本実施例では、丸め処理は、「1」を積6 3 1 の第14ビット6 3 2 に加えることである。丸め処理6 3 3 の結果6 3 4 は、新たなTEMP 6 3 0 を生成する。丸め処理による結果6 3 4 は0 4 9 C 7 D 1 3<sub>16</sub> (0 0 0 0 0 1 0 0 1 0 0 1 1 1 0 0 0 1 1 1 1 0 1 0 0 0 1 0 0 1 1 2) を有する。丸め処理の結果6 3 4 はスケーリングされ、本実施例における所望の結果が得られる。ここでスケーリング処理6 3 6 は、TEMP 6 3 0 の丸め処理の結果6 3 4 の1ビットの左シフトとして実行される。従って、ビット3 0 から1 5 がビット位置3 1 から1 6 にシフトアップされる。TEMP 6 3 0 は16ビット値に切り捨てられ、丸めシフトされた値の最上位16ビット(上位部分)がRESULTANT 6 2 3 として出力される。RESULTANT 6 2 3 は、Packed RESULTANT 6 1 2 の左から2番目のデータ要素位置である。本実施例では、RESULTANT 6 2 3 は0 9 3 8<sub>16</sub> (0 0 0 0 1 0 0 1 0 0 1 1 1 0 0 0 0 2) である。

#### 【0084】

64ビットオペランドのペアの第2データ要素位置でのPacked乗算上位丸めスケーリング(PMULHRSW)処理の例が以下のように示される。

#### 【0085】

#### 【表4】

```

0xAF7 x 0x2BC5 = 0x0938

temp = 0xAF7 x 0x2BC5 = 0x049C3D13

= 0000 0100 1001 1100 0011 1101 0001 0011

ROUND      + 0000 0000 0000 0000 0100 0000 0000 0000

-----

temp (rounded result) = 0000 0100 1001 1100 0111 1101 0001 0011

SHIFT << 1 BIT

temp (shifted result) = 0000 1001 0011 1000 1111 1010 0010 0110

TRUNCATE      -----

RESULT = 0000 1001 0011 1000 = 0x0938

```

10

20

30

40

上記例では、ソースデータオペランドの一方または両方は、MMX/SSE技術により可能なプロセッサにおける64ビットデータレジスタ、あるいはSSE2技術による128ビットデータレジスタとすることができます。実施形態に応じて、これらのレジスタは64/128/256ビット幅とすることができます。同様に、ソースオペランドの一方あるいは両方は、レジスタ以外のメモリ領域とすることができます。一実施例において、結果の宛先はMMXあるいはXMMデータレジスタである。さらに、結果の宛先はソースオペランドの1つと同じレジスタであってもよい。例えば、アーキテクチャでは、乗算上位丸めシフト命令は、第1ソースオペランドMM1と第2ソースオペランドMM2を有する。結果に対する所定の宛先は、この場合、第1ソースオペランドMM1のレジスタとするこ

50

とができる。

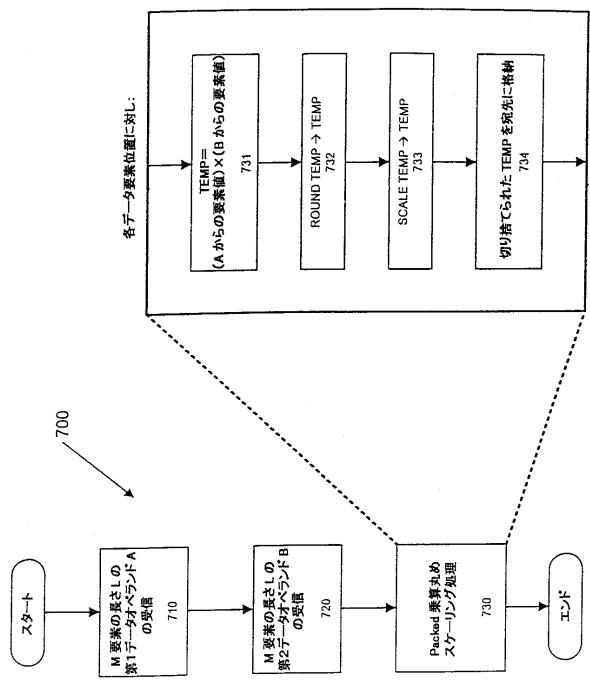

【0086】

図7Aは、積の上位部分を得るためにPackedデータオペランドに対する整数乗算丸めシフト処理を実行する方法の一実施例を示すフローチャート700である。長さLを使って、オペランドとデータブロックの幅が表される。特定の実施例に応じて、Lはデータセグメント数、ビット数、バイト数ワード数などに関する長さを示すのに利用される。ブロック710において、長さLの第1データオペランドAは、Packed整数乗算上位丸めシフト処理の実行のため受信される。ブロック720において、PMULHRSW処理のための長さLの第2データオペランドBが受信される。ブロック730において、乗算上位丸めシフトの実行命令が処理される。

10

【0087】

本実施例のブロック730における乗算上位丸めシフト処理の詳細が、各データ要素位置に対して発生するものに関してさらなる説明が与えられる。一実施例では、結果として生じるPackedデータ要素位置のすべてに対する乗算上位丸めシフト処理は並列に処理される。他の実施例では、データ要素のある部分が同時に処理される。ブロック731において、オペランドAからの要素の値とオペランドBからの要素の値を掛け合わせることにより仮の値TEMPが計算される。ブロック732において、この仮の値は丸められる。一実施例では、仮の値の上位18ビットがより高い精度のための計算に利用される。他の実施例では、他の個数のビットが対象となるかもしれない。ブロック732の丸め処理の後、ブロック733において仮の値がスケーリングされる。本実施例では、スケーリング処理は仮の値を1ビットだけ左にシフトすることである。ブロック734において、仮の値は必要なビット数に切り捨てられ、結果の値として宛先に格納される。ソースデータ要素の異なるペアのそれぞれに対する結果の値は、結果として生じるPackedオペランドのソース要素ペアに対応する適切なデータ要素位置に配置される。

20

【0088】

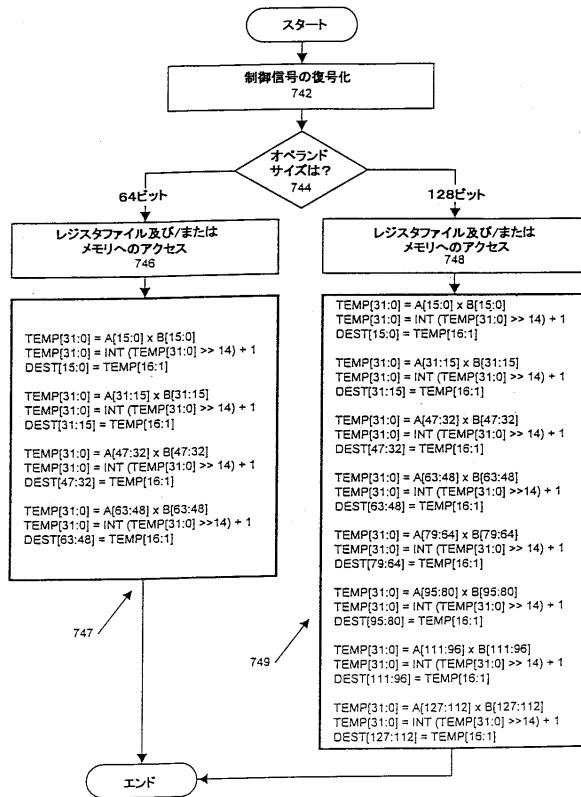

図7Bは、Packed整数乗算丸めシフト処理の結果として得られる積の関連する上位部分を獲得する方法の他の実施例を示すフローチャートである。本実施例において、オペランドはワードサイズのデータ要素から構成される。しかしながら、他の実施例は、例えば、バイト、ダブルワードあるいはクアドワードのような他のサイズのデータ要素により実現されるかもしれない。ブロック742において、乗算上位丸めシフト処理の制御信号が復号される。ブロック744において、当該処理におけるオペランドサイズの決定がチェックされる。一実施例では、オペランドサイズはブロック742で復号化された制御信号により決定することができる。例えば、オペランドサイズは命令により符号化することができる。オペランドサイズが64ビット長であると判断されれば、ブロック746においてレジスタファイル及び/またはメモリがアクセスされ、データのある場所に応じてオペランドデータが取得される。一実施例では、ソースオペランドは SIMDレジスタ及び/またはメモリ領域にあるかもしれない。本実施例の64ビット長のオペランドでは、各オペランドは4ワードサイズのデータ要素を有する。

30

【0089】

ソースデータ要素のこれら4つのペアの計算が、ブロック747の4つの式のセットとして示される。第1式の「TEMP[31:0] = A[15:0] × B[15:0]」は、ソースデータ要素の乗算を表す。第2式の「INT(TEMP[31:0] >> 14) + 1」は、中間結果の丸め処理を表す。本実施例では、仮の値は14ビット右シフトされ、最下位ビットに「1」が加えられる。言い換えると、中間結果の上位18ビットが保持され、もとの第14ビットに「1」が加えられる。第3式の「DEST[15:0] = TEMP[16:1]」は、丸められた結果のシフトおよび切り捨て処理を表す。この場合、結果として得られる各データ要素はワードであり、16ビットが必要とされる。残りの18ビットのビット[16:1]がここでは抽出される。本実施例では、左へのシフトは、最下位ビットのすぐ左の16ビットをとることにより行われた。切り捨てられた値は当該データ要素位置の結果として格納される。ブロック747において、ビット範囲が当該

40

50

位置の正しい値により満たされる場合を除き（すなわち、[ 15 : 0 ]、[ 31 : 15 ]、[ 47 : 32 ] 及び [ 63 : 48 ]）、この 3 つの式が各データ要素位置に対し繰り返される。

【 0090 】

ブロック 744 においてオペランドサイズが 128 ビット長であると判断されると、ブロック 748 においてレジスタファイル及び / またはメモリがアクセスされ、必要なオペランドデータが取得される。本実施例の 128 ビット長のオペランドに対し、各オペランドは 8 ワードサイズのデータ要素を有する。64 ビットバスと同様に、ブロック 749 においてソースデータ要素の 8 つのペアのそれぞれが上記 3 つの式のセットにより処理される。この 128 ビットバスの 8 つの式のセットに対する正しいビット範囲は、[ 15 : 0 ]、[ 31 : 15 ]、[ 47 : 32 ]、[ 63 : 48 ]、[ 79 : 64 ]、[ 95 : 80 ]、[ 111 : 96 ] 及び [ 127 : 112 ] である。本実施例で説明される 2 つのバスは 64 ビットオペランドと 128 ビットオペランドに関するものであるが、他の様々な長さのオペランドが他の実施例において利用されうる 6 つの 16 ビット値は、それぞれが各データ要素位置に対応し、DEST の各自のデータ要素位置に格納される。

10

【 0091 】

SIMD 整数乗算丸めシフトのテクニックが開示された。特定の実施例が添付された図面と共に説明及び示されたが、このような実施例は単なる例示のものであり、発明の範囲を限定するものではない。また、本発明は例示及び説明された特定の構成及び配置に制限されるものではなく、当業者により本開示に基づき他の様々な変更を行うことができるであろう。進歩のスピードが速く、さらなる進展が容易に予想できないこのような技術分野では、開示された実施例は、本開示の原理あるいは添付されたクレームの範囲を逸脱することなく、技術の進歩により促進されるような修正が可能である。

20

【 0092 】

本発明は上記特定の実施例に限定されるものではなく、本発明の要旨内において様々な変形・変更が可能である。

【 図面の簡単な説明 】

【 0093 】

【 図 1 A 】図 1 A は、本発明の一実施例による整数乗算上位丸めシフト処理のための SIMD 命令を実行する実行ユニットを有するプロセッサから構成されるコンピュータシステムのブロック図である。

30

【 図 1 B 】図 1 B は、本発明の他の実施例による他の一例となるコンピュータシステムのブロック図である。

【 図 1 C 】図 1 C は、本発明の他の実施例によるさらなる他の一例となるコンピュータシステムのブロック図である。

【 図 2 】図 2 は、本発明による Packed 整数乗算上位丸めシフト処理を実行する論理回路を有する一例となるプロセッサのマイクロアーキテクチャのブロック図である。

【 図 3 A 】図 3 A は、本発明の一実施例によるマルチメディアレジスタの様々な Packed データタイプ表現を示す。

【 図 3 B 】図 3 B は、他の実施例による Packed データタイプを示す。

40

【 図 3 C 】図 3 C は、Packed 乗算上位丸めシフト命令の処理符号化（オペコード）フォーマットの一実施例を示す。

【 図 3 D 】図 3 D は、他の処理符号化フォーマットを示す。

【 図 3 E 】図 3 E は、さらなる他の処理符号化フォーマットを示す。

【 図 4 A 】図 4 A は、本発明によるデータオペランドに対する SIMD 整数乗算上位丸めシフト処理を実行する論理の一実施例のブロック図である。

【 図 4 B 】図 4 B は、選択されたデータ要素位置に対する整数乗算上位丸めシフト処理の動作のブロック図である。

【 図 5 】図 5 は、本発明による乗算上位丸めシフト処理を実行する回路の一実施例のブロック図である。

50

【図6A】図6Aは、本発明の第1実施例によるPacked乗算上位丸めシフト命令の動作を示す。

【図6B】図6Bは、図6Aの特定のデータ要素位置におけるPacked乗算上位命令のさらなる詳細な動作を示す。

【図7A】図7Aは、積の上位部分を取得するためのPackedデータオペランドに対する整数乗算丸めシフト処理を実行する方法の一実施例を示すフローチャートである。

【図7B】図7Bは、Packed整数乗算丸めシフト処理の結果として生じる積の関連する上位部分を取得する方法の他の実施例を示すフローチャートである。

【符号の説明】

【0094】

|     |     |     |                      |    |

|-----|-----|-----|----------------------|----|

| 100 | 140 | 160 | コンピュータシステム           | 10 |

| 102 | 166 | 200 | プロセッサ                |    |

| 104 | 167 |     | キャッシュ                |    |

| 106 | 208 | 210 | レジスタファイル             |    |

| 108 |     |     | 実行ユニット               |    |

| 109 |     |     | Packed命令セット          |    |

| 110 |     |     | プロセッサバス              |    |

| 112 |     |     | グラフィックス/ビデオカード       |    |

| 114 |     |     | AGPインターフェース          |    |

| 116 |     |     | メモリコントローラハブ(MCH)     | 20 |

| 118 |     |     | メモリインターフェース          |    |

| 120 |     |     | メモリ                  |    |

| 122 |     |     | 専用ハブインターフェースバス       |    |

| 124 |     |     | データ記憶装置              |    |

| 126 |     |     | 無線送信機                |    |

| 128 |     |     | フラッシュBIOS            |    |

| 130 |     |     | I/Oコントローラハブ(ICH)     |    |

| 134 |     |     | ネットワークコントローラ         |    |

| 141 |     |     | バス                   |    |

| 142 | 162 |     | 実行ユニット               | 30 |

| 143 |     |     | Packed命令セット          |    |

| 144 | 165 |     | デコーダ                 |    |

| 145 | 164 |     | レジスタファイル             |    |

| 146 |     |     | SDRAMコントロール          |    |

| 147 |     |     | SRAMコントロール           |    |

| 148 |     |     | バーストフラッシュメモリインターフェース |    |

| 149 |     |     | PCMCIA/CFカードコントロール   |    |

| 150 |     |     | LCDコントロール            |    |

| 151 |     |     | DMAコントロール            |    |

| 152 |     |     | 代替バスマスティンタフェース       | 40 |

| 153 |     |     | I/Oバス                |    |

| 154 |     |     | I/Oブリッジ              |    |

| 155 |     |     | UART                 |    |

| 156 |     |     | USB                  |    |

| 157 |     |     | ブルートゥースUART          |    |

| 158 |     |     | I/O拡張インターフェース        |    |

| 159 | 170 |     | 処理コア                 |    |

| 161 |     |     | SIMDコプロセッサ           |    |

| 163 |     |     | 命令セット                |    |

| 168 |     |     | I/Oシステム              | 50 |

- 1 6 9 無線インターフェース

- 2 0 1 フロントエンド

- 2 0 2 高速スケジューラ

- 2 0 3 アウト・オブ・オーダーエンジン

- 2 0 4 低速 / 通常浮動小数点スケジューラ

- 2 0 6 シンプル浮動小数点スケジューラ

- 2 1 1 実行ブロック

- 2 1 2、2 1 4 アドレス生成ユニット ( A G U )

- 2 1 6、2 1 8 高速 A L U

- 2 2 0 低速 A L U

- 2 2 2 浮動小数点 A L U

- 2 2 4 浮動小数点移動ユニット

- 2 2 6 命令プリフェッチャ

- 2 2 8 命令デコーダ

- 2 3 0 トレースキャッシュ

- 2 3 2 マイクロコード R O M

- 2 3 4 u o p キュー

- 4 3 0 乗算上位丸めシフト計算論理

10

【 1 A 】

( 1 B )

【図1C】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4A】

【図4B】

【図5】

【図6A】

【図6B】

【図7A】

【図7B】

---

フロントページの続き

(72)発明者 デリン シー ウォルターズ

アメリカ合衆国 テキサス州 78758 オースティン メドウファイア ドライヴ 1193

1

(72)発明者 ジョナサン ジェイ タイラー

アメリカ合衆国 テキサス州 78728 オースティン ドリア ドライヴ 14921

審査官 緑川 隆

(56)参考文献 特表平11-500547(JP, A)

特表2002-527808(JP, A)

特表2001-516916(JP, A)

特開平03-268024(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 7 / 38

G 06 F 7 / 496

G 06 F 9 / 305

G 06 F 9 / 315