(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년06월23일

(11) 등록번호 10-1633008

(24) 등록일자 2016년06월17일

- (51) 국제특허분류(Int. Cl.)

*H03M 1/08* (2006.01) *H03M 1/68* (2006.01)

*H03M 1/74* (2006.01) *H03M 1/78* (2006.01)

(52) CPC특허분류

*H03M 1/0863* (2013.01)

*H03M 1/687* (2013.01)

(21) 출원번호 10-2015-7027325

(22) 출원일자(국제) 2014년03월04일

심사청구일자 2015년10월02일

(85) 번역문제출일자 2015년10월02일

(65) 공개번호 10-2015-0119479

(43) 공개일자 2015년10월23일

(86) 국제출원번호 PCT/US2014/020373

(87) 국제공개번호 WO 2014/138098

국제공개일자 2014년09월12일

(30) 우선권주장

13/791,536 2013년03월08일 미국(US)

(56) 선행기술조사문현

US20030001766 A1

US20110074615 A1

US20120050085 A1

(73) 특허권자

**퀄컴 인코포레이티드**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(72) 발명자

**서, 동원**

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

**이, 상민**

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(74) 대리인

**특허법인 남애드남**

(74) 대리인

특허법위 남애드남

전체 청구항 수 : 총 44 항

심사관 : 유선중

#### (54) 발명의 명칭 저 글리치-노이즈 DAC

(57) 요약

N-비트 DAC(digital-to-analog converter)는 N개의 입력 스테이지들을 포함하며, 이들 각각은 동일한 양의 전류를 생성하고, 차동 비트들에 응답하여 유사한 크기의 트랜지스터 스위치들의 쌍을 포함한다. DAC의 M 최상위 비트들과 연관되는  $2M-1$  입력 스테이지들은 병렬로 연결되고 DAC의 전류 합산 노드들에 그의 전류를 차별적으로 전달한다. 남은  $(N-M)$  스테이지들 각각은 DAC 내의 스테이지의 비트 포지션의 이진 가중치에 의해 정의된 전류를 공급하는 저항 네트워크를 포함한다.  $(N-M)$  스테이지들은 전류 합산 노드들에 그의 전류를 차별적으로 전달한다. DAC는 추가로 임피던스 감쇄기에 배치된 차동 증폭기의 이득에 의해 정의된 범위 내에서 전류 합산 노드 간의 전압 차이 및 전류 합산 노드들의 임피던스를 유지하도록 적응된 임피던스 감쇄기를 포함한다.

## 대표도 - 도4

(52) CPC특허분류

*H03M 1/747* (2013.01)

*H03M 1/785* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

N-비트 DAC(digital-to-analog converter)로서,

상기 DAC의  $M$  최상위 비트들과 연관되는  $2^M-1$  병렬 스테이지들 — 상기  $2^M-1$  스테이지들 각각은 전류를 생성하고, 상기 전류를, 차동 데이터에 응답하여 스위치들의 쌍을 통해 상기 DAC의 전류 합산 노드들의 쌍에 전달하도록 적응됨 —;

상기 DAC의  $(N-M)$  최하위 비트들과 연관되는  $(N-M)$  스테이지들 — 상기  $(N-M)$  스테이지들 각각은 전류를 생성하고, 저항 네트워크를 포함하고, 상기  $(N-M)$  스테이지들 각각은 추가로, 차동 데이터에 응답하여 상기 스테이지의 연관된 저항 네트워크로 상기 스테이지에서 생성된 전류를 전달하도록 적응된 스위치들의 쌍을 포함하고, 각각의 저항 네트워크는 자신이 수신한 전류를 스케일링하고 연관된 스테이지의 이진 가중치(binary weight)에 의해 정의된 스케일링된 전류를 전달하도록 동작 가능하고 상기  $(N-M)$  스테이지들은 그의 스케일링된 전류들을 전류 합산 노드들이 쌍에 전달함 —; 및

상기 합산 노드들의 쌍에 커플링되는 차동 증폭기를 포함하고, 상기 차동 증폭기의 이득에 의해 정의된 범위 내에서 상기 전류 합산 노드들 각각의 임피던스 및 상기 전류 합산 노드들 간의 전압 차이를 유지하도록 적응되는 임피던스 감쇄기

를 포함하는,

N-비트 DAC.

#### 청구항 2

제 1 항에 있어서,

상기  $(N-M)$  스테이지들 중 스테이지  $i$ 와 연관된 저항 네트워크는 상기  $(N-M)$  스테이지들 중 스테이지  $(i+1)$ 의 저항 네트워크에 커플링되고, 여기서  $i$ 는 상기 DAC 내에서 상기 스테이지의 비트 포지션(bit position)을 나타내는 정수인,

N-비트 DAC.

#### 청구항 3

제 2 항에 있어서,

상기  $(N-M)$  스테이지들 각각과 연관되는 저항 네트워크는 기준 전압을 수신하는,

N-비트 DAC.

#### 청구항 4

제 1 항에 있어서,

상기  $(N-M)$  스테이지들 각각과 연관되는 저항 네트워크는 R-2R 네트워크인,

N-비트 DAC.

#### 청구항 5

제 1 항에 있어서,

상기 임피던스 감쇄기는 추가로,

상기 전류 합산 노드들 중 제 1 전류 합산 노드에 커플링되는 소스 단자, 상기 DAC의 제 1 출력 단자에 커플링되는 드레인 단자 및 상기 증폭기의 제 1 출력 단자에 커플링되는 게이트 단자를 갖는 제 1 PMOS 트랜지스터;

및

상기 전류 합산 노드들 중 제 2 전류 합산 노드에 커플링되는 소스 단자, 상기 DAC의 제 2 출력 단자에 커플링되는 드레인 단자 및 상기 증폭기의 제 2 출력 단자에 커플링되는 게이트 단자를 갖는 제 2 PMOS 트랜지스터를 더 포함하는,

N-비트 DAC.

#### 청구항 6

제 1 항에 있어서,

상기 DAC의 N 스테이지들 각각은 상기 전류를 생성하는 캐스코드 전류 소스를 포함하는,

N-비트 DAC.

#### 청구항 7

제 1 항에 있어서,

상기 N 스테이지들 각각의 스위치들은 트랜지스터 스위치들이고, 이 트랜지스터들 중 하나는 상기 DAC에 의해 수신된 참(true) 데이터 비트를 나타내는 비트에 응답하고, 상기 트랜지스터들 중 하나는 상기 DAC에 의해 수신된 비트의 보완(complement)을 나타내는 비트에 응답하고, 모든 N 스테이지들의 트랜지스터 스위치들은 유사한 크기를 갖는,

N-비트 DAC.

#### 청구항 8

제 7 항에 있어서,

상기  $2^M-1$  스테이지들 중 적어도 하나는,

상기  $2^M-1$  스테이지들 중 적어도 하나에 배치된 트랜지스터 스위치들 중 제 1 트랜지스터 스위치와 상기 전류 합산 노드들 중 제 1 전류 합산 노드 사이에 배치되는 제 1 저항 엘리먼트; 및

상기  $2^M-1$  스테이지들 중 적어도 하나에 배치된 트랜지스터 스위치들 중 제 2 트랜지스터 스위치와 상기 전류 합산 노드들 중 제 2 전류 합산 노드 사이에 배치되는 제 2 저항 엘리먼트를 포함하는,

N-비트 DAC.

#### 청구항 9

제 1 항에 있어서,

상기 (N-M) 스테이지들의 단지 제 1 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 R-2R 네트워크인,

N-비트 DAC.

#### 청구항 10

제 8 항에 있어서,

상기 (N-M) 스테이지들의 제 2 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 상기 DAC의 전류 합산 노드들에 커플링되고, 상기 제 2 서브세트는 상기 제 1 서브세트를 포함하지 않는,

N-비트 DAC.

#### 청구항 11

제 1 항에 있어서,

상기 (N-M) 스테이지들 중 적어도 하나는 상기 전류 합산 노드들의 전압들을 트래킹하고 상기 (N-M) 스테이지들

중 적어도 하나의 저항 네트워크에 트래킹된 전압을 공급하도록 적응된 전압 트래킹 회로를 포함하는,

N-비트 DAC.

### 청구항 12

제 11 항에 있어서,

상기 전압 트래킹 회로는,

상기 전류 합산 노드들 중 제 1 전류 합산 노드에 커플링되는 제 1 입력 단자, 상기 (N-M) 스테이지들 중 적어도 하나와 연관되는 저항 네트워크에 배치되는 제 1 저항 엘리먼트에 커플링되는 제 2 입력 단자, 및 제 1 증폭기의 제 2 입력 단자에 커플링되는 출력 단자를 갖는 상기 제 1 증폭기; 및

상기 전류 합산 노드들 중 제 2 전류 합산 노드에 커플링되는 제 1 입력 단자, 상기 (N-M) 스테이지들 중 적어도 하나와 연관되는 저항 네트워크에 배치되는 제 2 저항 엘리먼트에 커플링되는 제 2 입력 단자, 및 제 2 증폭기의 제 2 입력 단자에 커플링되는 출력 단자를 갖는 상기 제 2 증폭기를 포함하는,

N-비트 DAC.

### 청구항 13

제 1 항에 있어서,

상기 (N-M) 스테이지들 중 적어도 하나는 상기 전류 합산 노드들과 상기 (N-M) 스테이지들 중 적어도 하나와 연관된 저항 네트워크에 전압을 공급하는 기준 전압 간의 전류 흐름을 소거하도록 적응된 왜곡 소거 회로를 포함하는,

N-비트 DAC.

### 청구항 14

제 1 항에 있어서,

상기 (N-M) 스테이지들의 제 1 서브세트의 각각의 스테이지는,

상기 스테이지와 연관되는 저항 네트워크의 제 1 저항 엘리먼트의 단자들 사이에 병렬로 커플링되는 제 1 용량 엘리먼트; 및

상기 스테이지와 연관되는 저항 네트워크의 제 2 저항 엘리먼트의 단자들 사이에 병렬로 커플링되는 제 2 용량 엘리먼트를 포함하는,

N-비트 DAC.

### 청구항 15

제 14 항에 있어서,

상기 N 스테이지들 각각의 스위치들은 MOS 트랜지스터들을 포함하고,

상기 (N-M) 스테이지들의 제 1 서브세트의 각각의 스테이지의 제 1 및 제 2 용량 엘리먼트들은 상기 MOS 트랜지스터들 중 하나의 드레인-기판 커패시턴스의 실질적으로 2배의 커패시턴스를 갖는,

N-비트 DAC.

### 청구항 16

DAC(digital-to-analog converter)로서,

상기 DAC의 최상위 비트들과 연관되는 제 1 복수의 병렬 스테이지들 – 상기 제 1 복수의 스테이지들 각각은 전류를 생성하고, 상기 전류를, 차동 데이터에 응답하여 스위치들의 쌍을 통해 상기 DAC의 전류 합산 노드들의 쌍에 전달하도록 적응됨 –;

상기 DAC의 최하위 비트들과 연관되는 제 2 복수의 스테이지들 – 상기 제 2 복수의 스테이지들 각각은 전류를

생성하고, 저항 네트워크를 포함하고, 상기 제 2 복수의 스테이지들 각각은 추가로, 차동 데이터에 응답하여 상기 스테이지의 연관된 저항 네트워크로 상기 스테이지에서 생성된 전류를 전달하도록 적응된 스위치들의 쌍을 포함하고, 각각의 저항 네트워크는 자신이 수신한 전류를 스케일링하고 연관된 스테이지의 이진 가중치에 의해 정의된 스케일링된 전류를 전달하도록 동작 가능하고 상기 제 2 복수의 스테이지들은 그의 스케일링된 전류들을 전류 합산 노드들이 쌍에 전달함 – 및

상기 합산 노드들의 쌍에 커플링되는 차동 증폭기를 포함하고, 상기 전류 합산 노드들 각각의 임피던스 및 상기 차동 증폭기의 이득에 의해 정의된 범위 내에서 상기 전류 합산 노드들 간의 전압 차이를 유지하도록 적응되는 임피던스 감쇄기

를 포함하는,

DAC.

### 청구항 17

DAC(digital-to-analog converter)에 의해, N-비트 디지털 신호를 아날로그 신호로 변환하는 방법으로서,

디지털 데이터의 M 최상위 비트들과 연관되는  $2^M-1$  병렬 스테이지들을 형성하는 단계;

상기  $2^M-1$  스테이지들 각각에서 전류를 생성하는 단계;

차동 데이터에 응답하여 제 1 쌍의 스위치들을 통해 전류 합산 노드들의 쌍에 상기  $2^M-1$  스테이지들 각각에서 생성된 전류를 전달하는 단계;

상기 디지털 데이터의 (N-M) 최하위 비트들과 연관되는 (N-M) 스테이지들을 형성하는 단계;

상기 (N-M) 스테이지들 각각에서 전류를 생성하는 단계;

상기 (N-M) 스테이지들의 상이한 스테이지와 각각 연관되는 (N-M) 저항 네트워크들을 형성하는 단계;

차동 데이터에 응답하여 제 2 쌍의 스위치들을 통해 연관된 스테이지에서 생성된 전류를 상기 (N-M) 저항 네트워크들 각각에 전달하는 단계;

상기 저항 네트워크의 연관된 스테이지의 이진 가중치에 따라 각각의 저항 네트워크에 의해 수신된 전류를 스케일링하는 단계;

스케일링된 전류를 상기 전류 합산 노드들의 쌍에 전달하는 단계;

이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 각각의 임피던스를 유지하는 단계; 및

상기 이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 간의 전압 차이를 유지하는 단계

를 포함하고,

상기 전류 합산 노드들에 전달되는 전류들에서의 차이들은 상기 아날로그 신호의 값을 정의하는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 18

제 17 항에 있어서,

상기 (N-M) 스테이지들 중 스테이지 i와 연관된 저항 네트워크를 상기 (N-M) 스테이지들 중 스테이지 (i+1)의 저항 네트워크에 커플링하는 단계

를 더 포함하고,

여기서 i는 상기 DAC 내에서 상기 스테이지의 비트 포지션을 나타내는 정수인,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 19

제 18 항에 있어서,

상기 (N-M) 스테이지들 각각에 기준 전압을 공급하는 단계

를 더 포함하는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

#### 청구항 20

제 18 항에 있어서,

상기 (N-M) 스테이지들의 제 2 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 상기 전류 합산 노드에 커플링되고, 상기 제 2 서브세트는 제 1 서브세트를 포함하지 않는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

#### 청구항 21

제 17 항에 있어서,

상기 (N-M) 스테이지들 각각과 연관되는 저항 네트워크는 R-2R 네트워크인,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

#### 청구항 22

제 17 항에 있어서,

상기 N 스테이지들 각각에서 캐스코드 전류 소스를 형성하는 단계; 및

상기 스테이지에서 형성된 캐스코드 전류 소스를 이용하여 상기 N 스테이지들 각각에서 전류를 생성하는 단계

를 더 포함하는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

#### 청구항 23

제 17 항에 있어서,

상기 N 스테이지들 각각의 스위치들은 트랜지스터 스위치들이고, 이 트랜지스터들 중 하나는 상기 DAC에 의해 수신된 참 데이터 비트를 나타내는 비트에 응답하고, 상기 트랜지스터들 중 하나는 상기 DAC에 의해 수신된 비트의 보완을 나타내는 비트에 응답하고, 모든 N 스테이지들의 트랜지스터 스위치들은 유사한 크기를 갖는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

#### 청구항 24

제 23 항에 있어서,

상기  $2^M-1$  스테이지들 중 적어도 하나의 트랜지스터 스위치들 중 제 1 트랜지스터 스위치와 상기 전류 합산 노드들 중 제 1 전류 합산 노드 사이에 제 1 저항 엘리먼트를 커플링하는 단계; 및

상기  $2^M-1$  스테이지들 중 적어도 하나의 트랜지스터 스위치들 중 제 2 트랜지스터 스위치와 상기 전류 합산 노드들 중 제 2 전류 합산 노드 사이에 제 2 저항 엘리먼트를 커플링하는 단계

를 더 포함하는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

#### 청구항 25

제 17 항에 있어서,

상기 (N-M) 스테이지들의 단지 제 1 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 R-2R 네트워크인, N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 26

제 17 항에 있어서,

상기 전류 합산 노드들의 전압들을 트래킹하는 단계; 및

상기 (N-M) 스테이지들 중 적어도 하나의 저항 네트워크에 트래킹된 전압들을 공급하는 단계

를 더 포함하는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 27

제 17 항에 있어서,

상기 전류 합산 노드들과 상기 (N-M) 스테이지들 중 적어도 하나와 연관된 저항 네트워크에 전압을 공급하는 기

준 전압 간의 전류 흐름을 소거하는 단계

를 더 포함하는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 28

제 17 항에 있어서,

상기 (N-M) 스테이지들 중 적어도 하나와 연관되는 저항 네트워크의 제 1 저항 엘리먼트의 단자들 사이에 병렬

로 제 1 용량 엘리먼트를 커플링하는 단계; 및

상기 (N-M) 스테이지들 중 적어도 하나와 연관되는 저항 네트워크의 제 2 저항 엘리먼트의 단자들 사이에 병렬

로 제 2 용량 엘리먼트를 커플링하는 단계

를 더 포함하는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 29

제 28 항에 있어서,

상기 N 스테이지들 각각의 스위치들은 MOS 트랜지스터들을 포함하고,

상기 (N-M) 스테이지들의 제 1 서브세트의 각각의 스테이지의 제 1 및 제 2 용량 엘리먼트들은 상기 MOS 트랜지

스터들 중 하나의 드레인-기판 커패시턴스의 실질적으로 2배의 커패시턴스를 갖는,

N-비트 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 30

DAC(digital-to-analog converter)에 의해, 디지털 신호를 아날로그 신호로 변환하는 방법으로서,

디지털 데이터의 최상위 비트들과 연관되는 제 1 복수의 병렬 스테이지들을 형성하는 단계;

상기 제 1 복수의 병렬 스테이지들 각각에서 전류를 생성하는 단계;

차동 데이터에 응답하여 제 1 쌍의 스위치들을 통해 전류 합산 노드들의 쌍에 상기 제 1 복수의 병렬 스테이지

들 각각에서 생성된 전류를 전달하는 단계;

상기 디지털 데이터의 최하위 비트들과 연관되는 제 2 복수의 스테이지들을 형성하는 단계;

상기 제 2 복수의 스테이지들 각각에서 전류를 생성하는 단계;

상기 제 2 복수의 스테이지들의 상이한 스테이지와 각각 연관되는 제 1 복수의 저항 네트워크들을 형성하는 단계;

차동 데이터에 응답하여 제 2 쌍의 스위치들을 통해 연관된 스테이지에서 생성된 전류를 상기 제 1 복수의 저항 네트워크들 각각에 전달하는 단계;

상기 저항 네트워크의 연관된 스테이지의 이진 가중치에 따라 상기 제 1 복수의 저항 네트워크 각각에 의해 수신된 전류를 스케일링하는 단계;

스케일링된 전류를 상기 전류 합산 노드들의 쌍에 전달하는 단계;

이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 각각의 임피던스를 유지하는 단계; 및

상기 이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 간의 전압 차이를 유지하는 단계를 포함하고,

상기 전류 합산 노드들에 전달되는 전류들에서의 차이들은 상기 아날로그 신호의 값을 정의하는, 디지털 신호를 아날로그 신호로 변환하는 방법.

### 청구항 31

디지털 신호를 아날로그 신호로 변환하도록 구성된 N-비트 DAC(digital-to-analog converter)로서,

디지털 데이터의  $M$  최상위 비트들과 연관되는  $2^M-1$  별별 스테이지들을 형성하기 위한 수단;

상기  $2^M-1$  스테이지들 각각에서 전류를 생성하기 위한 수단;

전류 합산 노드들의 쌍에 상기  $2^M-1$  스테이지들 각각에서 생성된 전류를 전달하기 위한 수단;

상기 디지털 데이터의 (N-M) 최하위 비트들과 연관되는 (N-M) 스테이지들을 형성하기 위한 수단;

상기 (N-M) 스테이지들 각각에서 전류를 생성하기 위한 수단;

상기 (N-M) 스테이지들의 상이한 스테이지와 각각 연관되는 (N-M) 저항 네트워크들을 형성하기 위한 수단;

연관된 스테이지에서 생성된 전류를 상기 (N-M) 저항 네트워크들 각각에 전달하기 위한 수단;

상기 저항 네트워크의 연관된 스테이지의 이진 가중치에 따라 각각의 저항 네트워크에 의해 수신된 전류를 스케일링하기 위한 수단;

스케일링된 전류를 상기 전류 합산 노드들의 쌍에 전달하기 위한 수단;

이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 각각의 임피던스를 유지하기 위한 수단; 및

상기 이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 간의 전압 차이를 유지하기 위한 수단을 포함하고,

상기 전류 합산 노드들에 전달되는 전류들에서의 차이들은 상기 아날로그 신호의 값을 정의하는,

N-비트 DAC.

### 청구항 32

제 31 항에 있어서,

상기 (N-M) 스테이지들 중 스테이지  $i$ 와 연관된 저항 네트워크를 상기 (N-M) 스테이지들 중 스테이지  $(i+1)$ 의 저항 네트워크에 커플링하기 위한 수단

을 더 포함하고,

여기서  $i$ 는 상기 DAC 내에서 상기 스테이지의 비트 포지션을 나타내는 정수인,

N-비트 DAC.

### 청구항 33

제 32 항에 있어서,

상기 (N-M) 스테이지들 각각에 기준 전압을 공급하기 위한 수단

을 더 포함하는,

N-비트 DAC.

### 청구항 34

제 32 항에 있어서,

상기 (N-M) 스테이지들의 단지 제 2 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 상기 전류 합산 노드들에 커플링되고, 상기 제 2 서브세트는 제 1 서브세트를 포함하지 않는,

N-비트 DAC.

### 청구항 35

제 31 항에 있어서,

상기 (N-M) 스테이지들 각각과 연관되는 저항 네트워크는 R-2R 네트워크인,

N-비트 DAC.

### 청구항 36

제 31 항에 있어서,

상기 N 스테이지들 각각에서 캐스코드 전류 소스를 형성하기 위한 수단; 및

상기 스테이지에서 형성된 캐스코드 전류 소스를 이용하여 상기 N 스테이지들 각각에서 전류를 생성하기 위한 수단

을 더 포함하는,

N-비트 DAC.

### 청구항 37

제 31 항에 있어서,

상기 N 스테이지들 각각의 스위치들은 트랜지스터 스위치들이고, 이 트랜지스터들 중 하나는 상기 DAC에 의해 수신된 참 데이터 비트를 나타내는 비트에 응답하고, 상기 트랜지스터들 중 하나는 상기 DAC에 의해 수신된 비트의 보완을 나타내는 비트에 응답하고, 모든 N 스테이지들의 트랜지스터 스위치들은 유사한 크기를 갖는,

N-비트 DAC.

### 청구항 38

제 37 항에 있어서,

상기  $2^M-1$  스테이지들 중 적어도 하나의 트랜지스터 스위치들 중 제 1 트랜지스터 스위치와 상기 전류 합산 노드들 중 제 1 전류 합산 노드 사이에 제 1 저항 엘리먼트를 커플링하기 위한 수단; 및

상기  $2^M-1$  스테이지들 중 적어도 하나의 트랜지스터 스위치들 중 제 2 트랜지스터 스위치와 상기 전류 합산 노드들 중 제 2 전류 합산 노드 사이에 제 2 저항 엘리먼트를 커플링하기 위한 수단

을 더 포함하는,

N-비트 DAC.

#### 청구항 39

제 31 항에 있어서,

상기 (N-M) 스테이지들의 단지 제 1 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 R-2R 네트워크인,

N-비트 DAC.

#### 청구항 40

제 31 항에 있어서,

상기 전류 합산 노드들의 전압들을 트래킹하기 위한 수단; 및

상기 (N-M) 스테이지들 중 적어도 하나의 저항 네트워크에 트래킹된 전압들을 공급하기 위한 수단

을 더 포함하는,

N-비트 DAC.

#### 청구항 41

제 31 항에 있어서,

상기 전류 합산 노드들과 상기 (N-M) 스테이지들 중 적어도 하나와 연관된 저항 네트워크에 전압을 공급하는 기

준 전압 간의 전류 흐름을 소거하기 위한 수단

을 더 포함하는,

N-비트 DAC.

#### 청구항 42

제 31 항에 있어서,

상기 (N-M) 스테이지들 중 적어도 하나와 연관되는 저항 네트워크의 제 1 저항 엘리먼트의 단자들 사이에 병렬

로 제 1 용량 엘리먼트를 커플링하기 위한 수단; 및

상기 (N-M) 스테이지들 중 적어도 하나와 연관되는 저항 네트워크의 제 2 저항 엘리먼트의 단자들 사이에 병렬

로 제 2 용량 엘리먼트를 커플링하기 위한 수단

을 더 포함하는,

N-비트 DAC.

#### 청구항 43

제 42 항에 있어서,

상기 N 스테이지들 각각의 스위치들은 MOS 트랜지스터들을 포함하고,

상기 (N-M) 스테이지들의 제 1 서브세트의 각각의 스테이지의 제 1 및 제 2 용량 엘리먼트들은 상기 MOS 트랜지

스터들 중 하나의 드레인-기판 커패시턴스의 실질적으로 2배의 커패시턴스를 갖는,

N-비트 DAC.

#### 청구항 44

디지털 신호를 아날로그 신호로 변환하도록 구성된 디지털-아날로그 변환기로서,

디지털 데이터의 최상위 비트들과 연관되는 제 1 복수의 병렬 스테이지들을 형성하기 위한 수단;

상기 제 1 복수의 병렬 스테이지들 각각에서 전류를 생성하기 위한 수단;

전류 합산 노드들의 쌍에 상기 제 1 복수의 병렬 스테이지들 각각에서 생성된 전류를 전달하기 위한 수단;

상기 디지털 데이터의 (N-M) 최하위 비트들과 연관되는 제 2 복수의 스테이지들을 형성하기 위한 수단;

상기 제 2 복수의 스테이지들 각각에서 전류를 생성하기 위한 수단;

상기 제 2 복수의 스테이지들의 상이한 스테이지와 각각 연관되는 제 1 복수의 저항 네트워크들을 형성하기 위한 수단;

연관된 스테이지에서 생성된 전류를 상기 제 1 복수의 저항 네트워크들 각각에 전달하기 위한 수단;

상기 저항 네트워크의 연관된 스테이지의 이진 가중치에 따라 각각의 저항 네트워크에 의해 수신된 전류를 스케일링하기 위한 수단;

스케일링된 전류를 상기 전류 합산 노드들의 쌍에 전달하기 위한 수단;

이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 각각의 임피던스를 유지하기 위한 수단; 및

상기 이득 값에 의해 정의된 범위 내에서 상기 전류 합산 노드들 간의 전압 차이를 유지하기 위한 수단을 포함하고,

상기 전류 합산 노드들에 전달되는 전류들에서의 차이들은 상기 아날로그 신호의 값을 정의하는,

디지털-아날로그 변환기.

#### 청구항 45

삭제

#### 청구항 46

삭제

#### 청구항 47

삭제

#### 청구항 48

삭제

#### 청구항 49

삭제

#### 청구항 50

삭제

#### 청구항 51

삭제

#### 청구항 52

삭제

#### 청구항 53

삭제

#### 청구항 54

삭제

#### 청구항 55

삭제

청구항 56

삭제

청구항 57

삭제

청구항 58

삭제

청구항 59

삭제

### 발명의 설명

#### 기술 분야

[0001] 35 U.S.C. § 119 하의 우선권 주장

[0002] [0001] 본 출원은 2013년 3월 8일 출원된 미국 특허 출원 일련 번호 제13/791,536호를 우선권으로 주장하며, 이 문서는 그 전체가 인용에 의해 본원에 포함된다.

#### 배경 기술

[0003] [0002] 본 개시는 전자 회로들에 관한 것으로서, 보다 구체적으로는 디지털-아날로그 변환기에 관한 것이다.

[0004] [0003] 디지털-아날로그 변환기(DAC)는 디지털 신호를 아날로그 신호로 변환하는 전자 회로이다. 다수의 파라미터들이 임의의 주어진 애플리케이션에 대한 DAC의 적합성을 결정하는데 이용된다. 이를 파라미터들 중에는 DAC가 디지털-아날로그 변환을 수행하는 속도, DAC의 분해능은 물론, DAC에 의해 생성된 노이즈가 있다.

[0005] [0004] 셀룰러 전화와 같은 무선 통신 디바이스는 종종, 통신 디바이스에 배치된 아날로그 회로들에 의한 추가의 프로세싱을 위해 디지털 신호를 아날로그 신호로 변환하기 위해 고속의 고분해능 DAC를 이용한다. 이러한 DAC에서 생성된 글리치(glitch)들은 노이즈 플로어(noise floor)를 증가시키며, 이는 결국 무선 통신 디바이스에 의해 전송된 신호들을 간섭할 수 있다. 글리치 노이즈의 주요한 소스들 중 하나는, DAC의 디지털 입력에서 천이가 발생할 때 DAC의 다양한 스테이지들 간에 존재하는 지연 차이들이다.

[0006] [0005] 저 노이즈, 저 전력, 광대역의 고분해능 DAC들은 롱텀 에볼루션(LTE) 표준과 같은 진보된 무선 표준들에 대해 점점 중요해진다. 라디오 주파수(RF) 애플리케이션들에서, 전송기 DAC에 의해 생성된 고주파수 글리치 노이즈는 수신기 채널에 딱 맞아떨어지고 이를 둔감화시킬 수 있는 대역외 노이즈이다. 저-전력, 고분해능의 광대역 DAC에서 글리치 노이즈를 제어하는 것은 도전과제로 남아있다.

#### 발명의 내용

[0007] [0006] 본 발명의 실시예에 따른 DAC(digital-to-analog converter)는 동일한 양의 전류를 생성하고, 유사한 크기의 트랜지스터 스위치들을 갖는 입력 스테이지들을 포함한다. 트랜지스터 스위치들을 통해 흐르는 전류들 및 글리치 노이즈는 이에 따라 DAC의 모든 입력 스테이지들에 대해 동일하다. DAC의 최하위 비트들에 대응하는 입력 스테이지들은 저항 네트워크들을 포함한다. 각각의 이러한 스테이지의 저항 네트워크는 DAC 내의 스테이지의 비트 포지션(bit position)의 이진 가중치에 따라 그것이 수신한 전류를 스케일링한다.

[0008] [0007] 본 발명의 일 실시예에 따른 N-비트 DAC는 부분적으로, DAC의 M 최상위 비트들과 연관되는  $2^M-1$  병렬 스테이지들, DAC의 (N-M) 최하위 비트들과 연관되는 (N-M) 스테이지들 및 임피던스 감쇄기를 포함한다.  $2^M-1$  스테이지들 각각은 스위치들의 쌍을 포함하며, 동일한 전류를 생성하고 그의 스위치 쌍을 통해 DAC의 전류 합산 노드들의 쌍에 이 전류를 전달하도록 적응된다. (N-M) 스테이지들 각각은 저항 네트워크를 포함하며,  $2^M-1$  스테이지들에서 생성된 것과 동일한 전류를 생성한다. (N-M) 스테이지들 각각은 MSB 스테이지들의 스위치들과 동일한 크기를 갖고 차동 데이터에 응답하여 스테이지와 연관된 저항 네트워크로 그 스테이지에서 생성된 전류를 전달

하도록 적응되는 스위치들의 쌍을 더 포함한다. 각각의 저항 네트워크는, 그의 연관된 스테이지의 이진 가중치에 따라, 자신이 수신한 전류를 스케일링하도록 동작 가능하다. (N-M) 스테이지들은 전류 합산 노드들의 쌍에 그의 스케일링된 전류들을 전달한다. 임피던스 감쇄기는 부분적으로, 전류 합산 노드들에 커플링되고 차동 증폭기의 이득에 의해 정의된 범위 내에서 전류 합산 노드들 간의 전압 차이 및 전류 합산 노드들 각각의 임피던스를 유지하도록 적응되는 차동 증폭기를 포함한다.

[0009] [0008] 일 실시예들에서, 비트 포지션들이 하나의 DAC 비트만큼 상이한 입력 스테이지들과 연관되는 저항 네트워크들은 서로 커플링된다. 일 실시예에서, 각각의 저항 네트워크는 기준 전압을 수신한다. 또 다른 실시예에서, 각각의 저항 네트워크는 R-2R 네트워크이다.

[0010] [0009] 일 실시예에서, 임피던스 감쇄기는 부분적으로, 제 1 및 제 2 PMOS 트랜지스터들을 더 포함한다. 제 1 PMOS 트랜지스터는 제 1 전류 합산 노드에 커플링되는 소스 단자, DAC의 제 1 출력 단자에 커플링되는 드레인 단자 및 증폭기의 제 1 출력 단자에 커플링되는 게이트 단자를 갖는다. 제 2 PMOS 트랜지스터는 제 2 전류 합산 노드에 커플링되는 소스 단자, DAC의 제 2 출력 단자에 커플링되는 드레인 단자 및 증폭기의 제 2 출력 단자에 커플링되는 게이트 단자를 갖는다.

[0011] [0010] 일 실시예에서, DAC의 N 스테이지들 각각은 그 스테이지의 트랜지스터 스위치들을 통과하는 동일한 전류를 생성하는 캐스코드 전류 소스를 포함한다. 일 실시예에서, N 스테이지들 각각의 트랜지스터 스위치들 중 하나는 DAC에 의해 수신되는 참(true) 데이터 비트를 나타내는 비트에 응답한다. N 스테이지들 각각의 다른 트랜지스터 스위치는 DAC에 의해 수신되는 비트의 보수(complement)를 나타내는 비트에 응답한다.

[0012] [0011] 일 실시예에서, (N-M) 스테이지들의 단지 제 1 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 R-2R 네트워크이다. 다른 실시예에서, (N-M) 스테이지들의 제 2 서브세트의 각각의 스테이지와 연관되는 저항 네트워크는 DAC의 전류 합산 노드들에 커플링된다. 제 2 서브세트는 제 1 서브세트를 포함하지 않는다.

[0013] [0012] 일 실시예에서, (N-M) 스테이지들 중 적어도 하나는 전류 합산 노드들의 전압들을 트래킹하고 그 스테이지의 저항 네트워크에 트래킹된 전압들을 공급하도록 적응된 전압 트래킹 회로를 더 포함한다. 일 실시예에서, 전압 트래킹 회로는 제 1 및 제 2 증폭기들을 포함한다. 제 1 증폭기는 제 1 전류 합산 노드에 커플링되는 제 1 입력 단자, 그 스테이지의 저항 네트워크에 배치되는 제 1 저항 엘리먼트에 커플링되는 제 2 입력 단자, 및 제 1 증폭기의 제 2 입력 단자에 커플링되는 출력 단자를 갖는다. 제 2 증폭기는 제 2 전류 합산 노드에 커플링되는 제 1 입력 단자, 그 스테이지의 저항 네트워크에 배치되는 제 2 저항 엘리먼트에 커플링되는 제 2 입력 단자, 및 제 2 증폭기의 제 2 입력 단자에 커플링되는 출력 단자를 갖는다.

[0014] [0013] 일 실시예에서, DAC의 (N-M) 스테이지들 중 적어도 하나는, 전류 합산 노드들과 그 스테이지의 저항 네트워크에 전압을 공급하는 기준 전압 간의 전류 흐름을 소거하도록 적응된 왜곡 소거 회로를 더 포함한다. 일 실시예에서, DAC의  $2^M-1$  스테이지들 중 적어도 하나는 제 1 및 제 2 저항 엘리먼트들을 더 포함한다. 제 1 저항 엘리먼트는 제 1 전류 합산 노드와 그 스테이지의 트랜지스터 스위치들 중 하나 간에 배치된다. 제 2 저항 엘리먼트는 제 2 전류 합산 노드와 그 스테이지의 트랜지스터 스위치들 중 다른 하나 간에 배치된다.

[0015] [0014] 일 실시예에서, (N-M) 스테이지들 각각은 제 1 및 제 2 용량 엘리먼트들을 더 포함한다. 각각의 이러한 스테이지의 제 1 용량 엘리먼트는 그 스테이지의 저항 네트워크에 배치된 제 1 저항 엘리먼트의 단자들 간에 병렬로 커플링된다. 각각의 이러한 스테이지의 제 2 용량 엘리먼트는 그 스테이지의 저항 네트워크에 배치된 제 2 저항 엘리먼트의 단자들 간에 병렬로 커플링된다. 이러한 실시예들에서, 각각의 이러한 스테이지의 제 1 및 제 2 용량 엘리먼트들은 DAC에 배치된 MOS 트랜지스터 스위치의 드레인-기판 커패시턴스의 실질적으로 2배인 커패시턴스를 갖는다.

[0016] [0015] 본 발명의 일 실시예에 따라, N-비트 디지털 신호를 아날로그 신호로 변환하는 방법은 부분적으로, 디지털 데이터의 M 최상위 비트들과 연관되는  $2^M-1$  병렬 스테이지들을 형성하는 단계, 2M-1 스테이지들 각각에서 동일한 전류를 생성하는 단계, 및 2M-1 스테이지들로부터의 전류를 각각의 이러한 스테이지에 배치된 스위치들의 쌍을 통해 제 1 및 제 2 전류 합산 노드들로 전달하는 단계를 포함한다. 방법은, 디지털 데이터의 (N-M) 최하위 비트들과 연관되는 (N-M) 스테이지들을 형성하는 단계, 및  $2^M-1$  스테이지들 각각에서 생성된 전류와 동일한 전류를 (N-M) 스테이지들 각각에서 생성하는 단계를 더 포함한다. 방법은, (N-M) 스테이지들 중 상이한 스테이지와 각각 연관되는 (N-M) 저항 네트워크들을 형성하는 단계, 스위치들의 쌍을 통해 그의 연관된 스테이지에서 생성된 전류를 (N-M) 저항 네트워크들 각각에 전달하는 단계, 저항 네트워크의 연관된 스테이지의 이진 가

중치에 따라 각각의 저항 네트워크에 의해 수신된 전류를 스케일링하는 단계, 및 스케일링된 전류들을 전류 합산 노드들의 쌍에 전달하는 단계를 더 포함한다. 방법은 이득 값에 의해 정의된 범위 내에서 전류 합산 노드들 각각의 임피던스를 유지하는 단계 및 이득 값에 의해 정의된 범위 내에서 전류 합산 노드들 간의 전압 차이를 유지하는 단계를 더 포함한다. 전류 합산 노드들에 전달되는 전류들의 차이는 아날로그 신호의 값을 정의한다.

### 도면의 간단한 설명

[0017]

[0016] 본 개시의 양상들은 예로서 예시된다. 첨부 도면들에서, 유사한 참조 번호들은 유사한 엘리먼트들을 나타낸다.

[0017] 도 1은 본 발명의 다양한 양상들이 실현될 수 있는 무선 통신 디바이스의 블록도이다.

[0018] 도 2는 본 발명의 일 예시적인 실시예에 따라 저 글리치 노이즈를 갖도록 적응된 전류 스티어링 DAC의 단순화된 블록도이다.

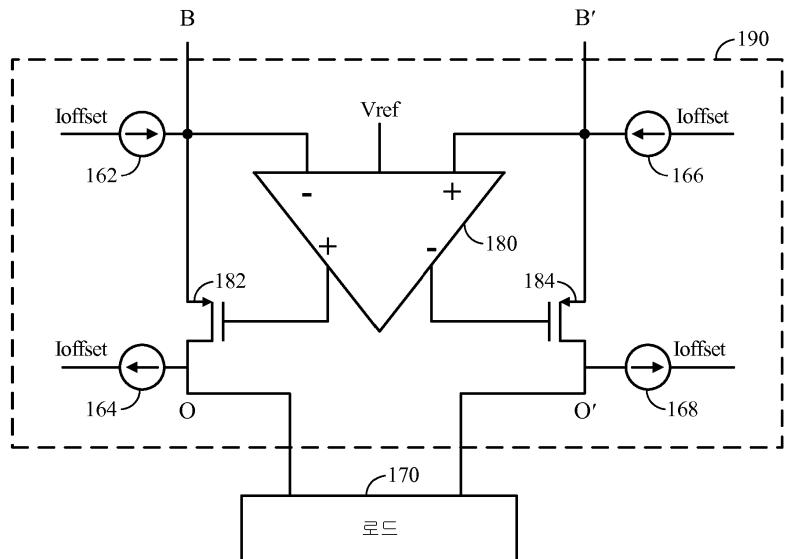

[0019] 도 3은 본 발명의 일 예시적인 실시예에 따라, 도 2에서 도시된 DAC의 임피던스 감쇄기의 단순화된 블록도이다.

[0020] 도 4는 본 발명의 다른 예시적인 실시예에 따라, 저 글리치 노이즈를 갖도록 적응된 전류 스티어링 DAC의 단순화된 블록도이다.

[0021] 도 5는 본 발명의 다른 예시적인 실시예에 따라 저 글리치 노이즈를 갖도록 적응된 전류-스티어링 DAC의 단순화된 블록도이다.

[0022] 도 6은 본 발명의 다른 예시적인 실시예에 따라, 전류-스티어링 DAC의 세그먼트의 단순화된 블록도이다.

[0023] 도 7은 본 발명의 다른 실시예에 따라 전류-스티어링 DAC의 세그먼트의 단순화된 블록도이다.

[0024] 도 8은 본 발명의 다른 예시적인 실시예에 따라 전류-스티어링 DAC의 세그먼트의 단순화된 블록도이다.

[0025] 도 9는 본 발명의 다른 예시적인 실시예에 따라 전류-스티어링 DAC의 세그먼트의 단순화된 블록도이다.

[0026] 도 10은 본 발명의 다른 예시적인 실시예에 따라, 전류-스티어링 DAC의 세그먼트의 단순화된 블록도이다.

[0027] 도 11은 본 발명의 다른 예시적인 실시예에 따라 저 글리치 노이즈를 갖도록 적응된 전류 스티어링 DAC의 단순화된 블록도이다.

[0028] 도 12는 본 발명의 일 실시예에 따라 디지털 신호를 아날로그 신호로 변환하기 위한 방법의 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0018]

[0029] 몇 개의 예시적인 실시예들은 그의 부분을 형성하는 첨부 도면들에 관하여 이제 설명될 것이다. 본 개시의 하나 또는 그 초과의 양상들이 구현될 수 있는 특정한 실시예들이 아래에서 설명되지만, 다른 실시예들이 이용될 수 있고, 다양한 변형들이 본 개시의 범위로부터 벗어남 없이 이루어질 수 있다.

[0019]

[0030] 본 발명의 실시예에 따라, 디지털-아날로그 변환기(DAC)는 동일한 양의 전류를 생성하고 유사한 크기의 트랜지스터 스위치들을 갖는 입력 스테이지를 포함한다. 트랜지스터 스위치들을 통해 흐르는 전류들은 이에 따라 DAC의 모든 입력 스테이지들에 대해 동일하다. DAC의 최하위 비트들에 대응하는 입력 스테이지들은 저항 네트워크들을 포함한다. 각각의 이러한 스테이지에서 저항 네트워크는 DAC 내의 스테이지의 비트 포지션의 이진 가중치에 따라 자신이 수신한 전류를 스케일링한다.

[0020]

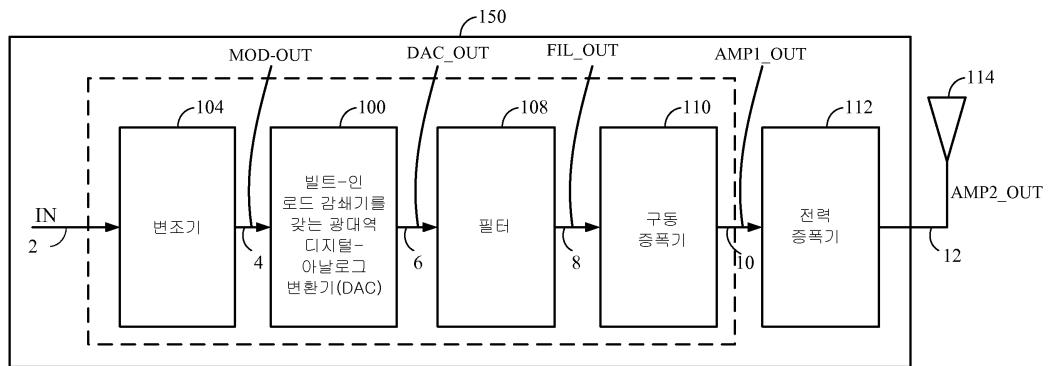

[0031] 도 1은 본 발명의 일 실시예에 따라, 무선 통신 시스템에서 이용되는 무선 통신 디바이스(150)(이하 대안적으로 디바이스로서 지칭됨)의 블록도이다. 디바이스(150)는 셀룰러 전화, 개인용 디지털 보조기기(PDA), 모뎀, 핸드헬드 디바이스, 랩톱 컴퓨터 등일 수 있다.

[0021]

[0032] 디바이스(150)는 임의의 주어진 시간에 다운링크(DL) 및/또는 업링크(UL) 상에서 하나 또는 그 초과의 기지국들과 통신할 수 있다. 다운링크(또는 순방향 링크)는 기지국으로부터 디바이스로의 통신 링크를 지칭한다. 업링크(또는 역방향 링크)는 디바이스로부터 기지국으로의 통신 링크를 지칭한다.

[0022]

[0033] 무선 통신 시스템은 이용 가능한 시스템 자원들(예를 들어, 대역폭 및 전송 전력)을 공유함으로써 다수의 사용자들과의 통신을 지원할 수 있는 다중-액세스 시스템일 수 있다. 이러한 시스템들의 예들은 CDMA(code

division multiple access) 시스템들, TDMA(time division multiple access) 시스템들, FDMA(frequency division multiple access) 시스템들, OFDMA(orthogonal frequency division multiple access) 시스템들 및 SDMA(spatial division multiple access) 시스템들을 포함한다.

[0023] [0034] 무선 통신 디바이스(150)는 LTE(long term evolution) 시스템들과 같은 무선 통신 시스템들에서 이용될 수 있다. 무선 통신 시스템(150)은 고(high) 데이터 레이트들 또는 대역폭들에서 연속적으로 동작될 수 있으며, 이에 따라 본 명세서에서 이용되는 DAC들에 대한 증가된 대역폭을 요구한다. 증가된 대역폭은 광범위한 주파수들 및 디지털 사전-왜곡 동작들을 핸들링할 수 있는, 시스템-온-칩 상에서 구현되는 광대역 DAC를 요구할 수 있다. 사전-왜곡 동작은 이러한 무선 시스템들에서 저-비용 비-선형 전력 증폭기의 이용을 가능케 할 수 있다.

[0024] [0035] 디바이스(150)는, 집합적으로 전송 채널을 형성하는 변조기(104), DAC(100), 필터(108) 및 증폭기(110)를 부분적으로 포함하는 것으로서 도시된다. 변조기(104)는 인입하는 디지털 신호(IN)(2)를 변조하고, 이에 응답하여 변조된 신호(MOD\_OUT)(4)를 생성하여 DAC(100)에 공급하도록 적응된다. 아래에서 추가로 설명되는 바와 같이, DAC(100)는 빌트-인 로드(임피던스) 감쇄기를 갖는다. DAC(100)에 의해 공급된 변환된 신호(DAC\_OUT)(6)는 필터(108)에 의해 수신되고 필터링된다. 필터(108)의 출력 신호(FIL\_OUT)(8)는 증폭기(110)에 의해 수신되고 증폭되며, 증폭기(110)는 이에 응답하여 신호(AMP1\_OUT)(10)를 생성한다. 증폭기(110)에 의해 생성된 신호(AMP1\_OUT)는 안테나(114)에 의해 전송되기 이전에 신호(AMP2\_OUT)를 생성하도록 전력 증폭기(112)를 이용하여 추가로 증폭될 수 있다.

[0025] [0036] 저-전력 무선 또는 소비자 디바이스들은 더 적은 전류로 동작하는 DAC를 요구할 수 있다. 이러한 애플리케이션들에서, SNDR(signal-to-noise distortion ratio), SFDR(spurious free dynamic range) 및 THD(total harmonic distortion)를 포함하는 동적 선형성 성능 메트릭들은 중요한 시스템 파라미터들이다.

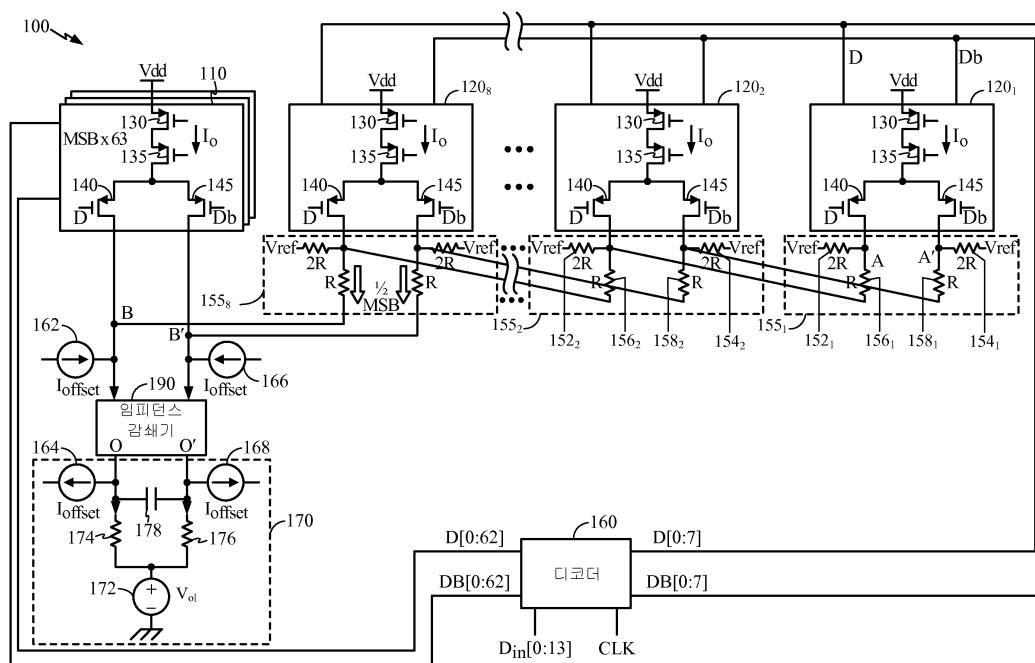

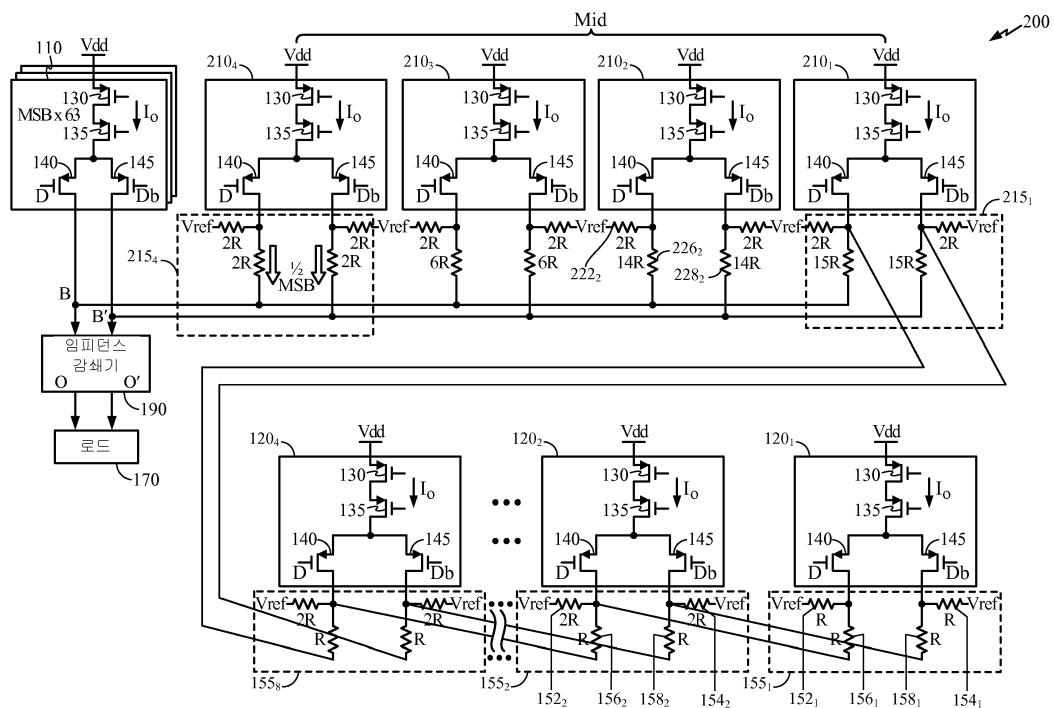

[0026] [0037] 도 2는 본 발명의 일 예시적인 실시예에 따라 저 글리치 노이즈를 갖도록 적응된 14-비트 전류 스티어링 DAC(100)의 블록도이다. DAC(100)는 도 1에서 도시된 디바이스(150)에서 이용될 수 있다. DAC(100)가 14-비트 분해능을 갖는 것으로서 도시되지만, 본 발명에 따른 저 글리치 노이즈 DAC는 14-비트보다 더 높거나 더 낮은 분해능을 가질 수 있다는 것이 이해된다. DAC(100)는 DAC의 6개의 최상위 비트들(MSB들)을 형성하도록 별별로 연결되는 63개의 유사한 입력 스테이지들( $110_j$ )을 포함(단순함을 위해, 스테이지들(110) 중 하나만이 도시됨)하며,  $j$ 는 1로부터 63으로 변동되는 정수이다. DAC(100)는 또한 DAC의 8개의 최하위 비트들(LSB들)을 형성하는 8개의 스테이지들( $120_i$ )을 포함하며, 여기서  $i$ 는 1로부터 8까지 변동되는 정수이다. 63개의 입력 스테이지들( $110_j$ )은 대안적으로 그리고 집합적으로 입력 스테이지(110)로서 지칭된다. 마찬가지로, 8개의 입력 스테이지들( $120_i$ )은 대안적으로 그리고 집합적으로 입력 스테이지(120)로서 지칭된다. 단순함을 위해, 입력 스테이지들( $120_i$ ) 중 3개만이 도시된다.

[0027] [0038] DAC(100)는 또한 아래에서 상세히 설명되는 출력 스테이지(190)를 포함하는 것으로서 도시된다. DAC(100)는 또한 14-비트 입력 신호( $D_{in}[13:0]$ )를 수신하고 다양한 입력 스테이지들(110, 120)의 트랜지스터들(140, 145)에 인가되는 다양한 참(D) 및 보수 비트들(DB)을 디코딩하는 디코더(160)를 포함하는 것으로서 도시된다.

[0028] [0039] 각각의 입력 스테이지( $120_i$ )는, 함께 캐스코드 전류 소스를 형성하는 트랜지스터들(130 및 135)의 쌍을 포함하는 것으로서 도시된다. 각각의 입력 스테이지( $120_i$ )는 또한 입력 스테이지와 연관되고 그에 의해 수신되는 차동 데이터(D 및 DB)의 쌍에 응답하는 트랜지스터 스위치들(140 및 145)의 쌍을 포함하는 것으로 도시된다. 각각의 입력 스테이지( $110_j$ )는 또한, 함께 캐스코드 전류 소스를 형성하는 트랜지스터(130 및 135)의 쌍을 포함하는 것으로서 도시된다. 각각의 입력 스테이지( $110_j$ )는 또한 그 입력 스테이지와 연관되고 그에 의해 수신된 차동 데이터(D 및 DB)의 쌍에 응답하는 트랜지스터 스위치들(140 및 145)의 쌍을 포함하는 것으로서 도시된다. 입력 스테이지들( $120_i$  및  $110_j$ )에 배치된 트랜지스터들(130)은 실질적으로 동일한 크기를 갖는다. 유사하게, 입력 스테이지들( $120_i$  및  $110_j$ )에서 생성된 전류들( $I_0$ )은 동일한 크기를 갖는다. 이에 따라, 스테이지들( $120_i$  및  $110_j$ )에서 생성된 전류들( $I_0$ )은 동일한 크기를 갖는다.

[0029] [0040] DAC(100)는 또한 8개의 LSB 스테이지들(120) 중 상이한 것과 각각 연관되는 8개의 저항 네트워크들( $155_i$ )을 포함하는 것으로서 또한 도시된다. 각각의 저항 네트워크( $155_i$ )는 입력 스테이지( $120_i$ )와 연관되고, 저

항 네트워크는 그의 연관된 입력 스테이지로부터 수신한 전류를 스케일링하도록 적응된다. 각각의 입력 스테이지와 연관된 저항 네트워크는 그 입력 스테이지에 배치된 트랜지스터 스위치들(140, 145)의 드레인 단자에서 볼 때 R-2R 네트워크를 형성한다. 예를 들어, 스테이지(120<sub>2</sub>)는 R-2R 저항 네트워크(155<sub>2</sub>)를 포함하는 것으로서 도시된다. 마찬가지로, 스테이지(120<sub>8</sub>)는 R-2R 저항 네트워크(155<sub>8</sub>)를 포함하는 것으로서 도시된다.

[0030] [0041] 도 2로부터 알 수 있는 바와 같이, 각각의 저항 네트워크(155<sub>i</sub>)는 4개의 레지스터들, 즉 레지스터들(152<sub>i</sub>, 154<sub>i</sub>, 156<sub>i</sub>, 및 158<sub>i</sub>)을 포함하는 것으로서 도시된다. 각각의 입력 스테이지(120<sub>i</sub>)의 레지스터들(152<sub>i</sub> 및 156<sub>i</sub>)은 그 입력 스테이지에 배치된 트랜지스터 스위치(140<sub>i</sub>)의 드레인 단자에 커플링된 공통 단자를 갖는다. 유사하게, 각각의 입력 스테이지(120<sub>i</sub>)의 레지스터들(154<sub>i</sub> 및 158<sub>i</sub>)은 그 입력 스테이지에 배치된 트랜지스터 스위치(145<sub>i</sub>)의 드레인 단자에 커플링되는 공통 단자를 갖는다. 레지스터들(152<sub>i</sub> 및 154<sub>i</sub>)의 제 2 단자들은 기준 전압( $V_{ref}$ )을 수신한다. 각각의 스테이지(120<sub>k</sub>)(여기서  $k$ 는 1 내지 7 범위의 정수)에 대해, 레지스터(156<sub>k</sub>)의 제 2 단자가 트랜지스터 스위치(140<sub>k+1</sub>), 즉, 참 입력 데이터( $D_{k+1}$ )를 수신하고 입력 스테이지(120<sub>k</sub>)의 비트 포지션보다 하나 더 높은 비트 포지션을 갖는 입력 스테이지(120<sub>k+1</sub>)에 배치되는 트랜지스터 스위치의 드레인 단자에 커플링된다. 마찬가지로, 레지스터(158<sub>k</sub>)의 제 2 단자는 트랜지스터 스위치(145<sub>k+1</sub>), 즉 보수 입력 데이터( $DB_{k+1}$ )를 수신하고 입력 스테이지(120<sub>k+1</sub>)에 배치된 트랜지스터 스위치의 드레인 단자에 커플링된다.

[0031] [0042] 예를 들어, 입력 스테이지(120<sub>2</sub>)와 연관된 저항 네트워크(155<sub>2</sub>)는 레지스터들(152<sub>2</sub>, 154<sub>2</sub>, 156<sub>2</sub>, 및 158<sub>2</sub>)을 포함하는 것으로서 도시된다. 레지스터들(152<sub>2</sub> 및 156<sub>2</sub>)은 입력 스테이지(120<sub>2</sub>)에 배치된 트랜지스터 스위치(140<sub>2</sub>)의 드레인 단자에 커플링되는 공통 단자를 갖는다. 유사하게, 입력 스테이지(120<sub>2</sub>)의 레지스터들(154<sub>2</sub> 및 158<sub>2</sub>)은 입력 스테이지(120<sub>2</sub>)에 배치된 트랜지스터 스위치(145<sub>2</sub>)의 드레인 단자에 커플링되는 공통 단자를 갖는다. 레지스터들(152<sub>2</sub> 및 154<sub>2</sub>)의 제 2 단자들은 기준 전압( $V_{ref}$ )을 수신한다. 레지스터(156<sub>2</sub>)의 제 2 단자는 트랜지스터 스위치(140<sub>3</sub>)의 드레인 단자에 커플링된다. 마찬가지로, 레지스터(158<sub>2</sub>)의 제 2 단자는 트랜지스터 스위치(145<sub>3</sub>)의 드레인 단자에 커플링된다.

[0032] [0043] 마지막 LSB 스테이지와 연관되는 저항 네트워크(155<sub>8</sub>)의 레지스터들(152<sub>8</sub> 및 156<sub>8</sub>)은 입력 스테이지(120<sub>8</sub>)에 배치된 트랜지스터 스위치(140<sub>8</sub>)의 드레인 단자에 커플링되는 공통 단자를 갖는다. 유사하게, 입력 스테이지(120<sub>8</sub>)의 각각의 레지스터들(154<sub>8</sub> 및 158<sub>8</sub>)은 입력 스테이지(120<sub>8</sub>)에 배치된 트랜지스터 스위치(145<sub>8</sub>)의 드레인 단자에 커플링되는 공통 단자를 갖는다. 레지스터들(152<sub>8</sub> 및 154<sub>8</sub>)의 제 2 단자들은 기준 전압( $V_{ref}$ )을 수신한다. 레지스터(156<sub>8</sub>)의 제 2 단자는 출력 스테이지(190)의 합산 노드(B)에 커플링된다. 마찬가지로, 레지스터(158<sub>8</sub>)의 제 2 단자는 출력 스테이지(190)의 합산 노드(B')에 커플링된다.

[0033] [0044] 레지스터들(156<sub>i</sub> 및 158<sub>i</sub>) 각각은 저항(R)을 갖는다. 레지스터들(152<sub>i</sub> 및 154<sub>i</sub>)은 또한 R의 저항을 갖는다. 남은 7개의 스테이지들의 레지스터들(152<sub>i</sub> 및 154<sub>i</sub>) 각각은 2R의 저항을 갖는다. 이에 따라, 각각의 입력 스테이지(120<sub>i</sub>)와 연관되는 저항 네트워크(155<sub>i</sub>)는, 그 입력 스테이지에 배치된 트랜지스터 스위치들(140<sub>i</sub> 및 145<sub>i</sub>)의 드레인 단자로부터 볼 때 R-2R 네트워크를 형성한다.

[0034] [0045] 각각의 저항 네트워크(155<sub>i</sub>)의 저항들은, 각각의 저항 네트워크를 통해 흐르는 전류가 저항 네트워크의 연관된 입력 스테이지(120<sub>i</sub>)의 이진 가중치에 비례하도록 선택된다. 이에 따라, 각각의 입력 스테이지의 캐스코드 트랜지스터들(130 및 135)을 통해 흐르는 전류가  $I_0$ 인 것으로 가정되는 경우, 예를 들어, (7번째 최상위 비트와 연관되는) 스테이지(120<sub>8</sub>)의 저항 네트워크(155<sub>8</sub>)에 배치된 레지스터들(156<sub>8</sub> 및 158<sub>8</sub>)을 통해 합산 노드(B, B')로 흐르는 전류는  $(1/2)*I_0$ 이다. 마찬가지로, (최하위 비트와 연관되는) 스테이지(120<sub>1</sub>)의 저항 네트워크(155<sub>1</sub>)를 통해 합산 노드(B, B')로 흐르는 전류는  $(1/256)*I_0$ 이다. 저항 네트워크들(150<sub>i</sub>)을 통해 흐르는 전류들은 입력 신호들을 출력 스테이지(190)에 제공하는 전류 합산 노드들(B, B')에 전달된다. DAC(100)의 예시적인 실시예에서, 저항 네트워크들은 R-2R 네트워크인 것으로서 도시되지만, 이진 가중치를 이용하여 전류를 스케일

령하도록 적응된 임의의 다른 저항 네트워크가 이용될 수 있다는 것이 이해된다.

[0035] [0046] 본 발명의 일 양상에 따른 출력 스테이지(190)는 임피던스 감쇄기(190)를 포함한다. 출력 스테이지(190)는 대안적으로 여기서 임피던스 감쇄기(190)로서 지칭된다. 임피던스 감쇄기(190)의 출력 노드들(0, 0')을 걸친 차동 전압은 DAC(100)의 출력 전압을 표현한다. 커패시터(178) 및 전압 소스(172)와 함께 레지스터들(174, 176)은 출력 로드(170)를 표현한다. 전류 소스들(162, 164)은 각각 노드들(B, B')에 전류( $I_{offset}$ )를 제공한다. 전류 싱크들(166 및 168)은 노드(0, 0')로부터 각각 전류( $I_{offset}$ )를 회수(withdraw)한다. 전류 소스들(162, 164) 및 전류 싱크들(166, 168)은 동작의 활성 영역에서 바이어싱된 감쇄기(190)에 배치되는 트랜지스터들을 유지하도록 적응된다.

[0036] [0047] DAC의 모든 입력 스테이지들(110, 120)에서 트랜지스터 스위치들(140 및 145)을 통해 흐르는 전류가 실질적으로 동일하고 그의 연관된 저항 네트워크들에 의해서만 스케일링되기 때문에(트랜지스터 스위치를 통과한 이후), 그리고 추가로 모든 스테이지들의 스위치들(140 및 145)이 동일한 크기를 갖기 때문에, DAC(100)의 MSB 와 LSB 스테이지들 간의 글리치 에너지는 매칭된다. DAC(100)는 이에 따라 종래의 DAC들보다 실질적으로 더 낮은 글리치 노이즈를 갖는다. 저항 네트워크들은 이진 가중치들을 이용하여 스위치들을 통과하는 전류들을 정확하게 분할한다. 예시적인 14-비트 DAC(106)에 대한 8-비트 정확도의 레지스터 매칭은 비교적 쉽게 달성 가능하다.

[0037] [0048] 각각의 입력 스테이지( $120_k$ )에 의해 인식되는 R-2R 네트워크로 인해, 각각의 입력 스테이지( $120_i$ )의 트랜지스터( $140_i$ )를 통해 흐르는 전류의 1/2는 전압( $V_{ref}$ )에 공급되는 반면에, 이 전류의 다른 1/2는 트랜지스터( $140_{(i+1)}$ )의 드레인 단자에 공급된다. 마찬가지로, 각각의 입력 스테이지( $120_i$ )의 트랜지스터( $145_i$ )를 통해 흐르는 전류의 1/2는 전압( $V_{ref}$ )에 공급되는 반면에, 이 전류의 다른 1/2는 트랜지스터( $145_{(i+1)}$ )의 드레인 단자에 공급된다. 그러므로, 각각의 저항 네트워크( $155_i$ )를 통해 흐르는 전류는 저항 네트워크( $155_{(i+1)}$ )를 통해 흐르는 전류의 1/2이다. 이에 따라, 각각의 입력 스테이지( $120_i$ )의 저항 네트워크를 통해 흐르는 전류는 DAC에서 저항 네트워크의 연관된 입력 스테이지( $120_i$ )의 이진 가중치에 비례한다.

[0038] [0049] 임피던스 감쇄기(190)는 유리하게는 출력 로드(170)가 가질 수 있는 임피던스들의 범위를 증가시킨다. 임피던스 감쇄기(190)는 추가로 프로세스, 전압 및 온도의 변동들로 인한 출력 로드 임피던스의 변화들을 참작하도록 적응된다. 결과적으로 DAC(100)의 모든 입력 스테이지들이 동일한 양의 전류를 생성하고 유사한 스위치 크기들을 갖기 때문에, DAC(100)는 종래의 DAC들보다 훨씬 더 적은, 프로세스, 전압 및 온도에 걸친 대역외 노이즈 변동을 갖는다. 또한, 본 발명에 따라, 임피던스 감쇄기(190)는 DAC(100)의 SFDR 및 SNDR이 원하는 값들 내에 있다는 것을 보장하도록 레지스터들( $152_i$ ,  $154_i$ ,  $156_i$  및  $158_i$ )의 저항들을 선택하는데 있어 더 나은 유연성을 제공한다. 즉, 본 발명에 따른 임피던스 감쇄기는 로드 저항으로부터 저항 네트워크들의 저항들을 디커플링한다.

[0039] [0050] 도 3은 로드(170)에 커플링되는 임피던스 감쇄기(190)의 단순화된 블록도이다. 임피던스 감쇄기(190)는 차동 입력들의 쌍, 및 차동 출력들의 쌍을 갖는 증폭기(180) 및 트랜지스터들(182, 184)을 포함하는 것으로서 도시된다. 임피던스 감쇄기는 미국 특허 번호 제8,169,353호에서 설명된다. 전류 소스들(162, 164)은 노드들(B, B')에 전류( $I_{offset}$ )을 각각 제공하고, 전류 싱크들(166 및 168)은 노드(0, 0')로부터 전류( $I_{offset}$ )를 각각 회수한다. 전류 소스들(162, 164) 및 전류 싱크들(166, 168)은 동작의 활성 영역에서 트랜지스터들(182, 184)을 유지하도록 적응된다.

[0040] [0051] 감쇄기(190)는 증폭기(180)의 DC 이득에 의해 정의된 비교적 작은 범위 내에서 노드들(B, B') 간의 전압 차이를 유지하도록 적응된다. 예를 들어, 증폭기(180)가 60dB의 DC 이득을 갖고, 출력 노드들(0, 0') 간의 전압 차이가 1V인 경우, 노드들(B, B') 간의 전압 차이는 아래에서 추가로 설명되는 바와 같이 거의 1mV로 유지된다.

[0041] [0052] 예를 들어, DAC(100)가 DAC의 입력의 변화에 응답하여 더 많은 전류를 노드 B에 스티어링한다고 가정한다. 이는 노드 B의 전압이 증가하게 한다. 증폭기(180)의 입력 단자들은 비교적 높은 임피던스를 갖기 때문에, 노드 B에 주입된 추가 전류는 트랜지스터(182)를 통해 흐르게 되고, 그에 따라 출력 노드(0)에서의 전압을 증가하게 한다. 증폭기(180)는 PMOS 트랜지스터(182)의 소스 전압을 비교적 일정하게 유지하도록 PMOS 트랜지스터(182)의 게이트 전압을 감소시키게 적응된다. 트랜지스터(182)의 소스 전압을 비교적 일정하게 유지함으로써, 노드들(B, B') 간의 전압 차이는 증폭기(180)의 DC 이득에 의해 정의된 매우 좁은 범위 내에서 유지된다. 노드

들(B, B')의 임피던스 대 노드들(0, 0')의 임피던스의 비는 증폭기(180)의 이득에 의해 또한 정의된다. 도 3의 임피던스 감쇄기(190)가 완전 차동 증폭기(180)를 포함하는 것으로 도시되지만, 다른 실시예들에서, 임피던스 감쇄기(190)는 미국 특히 번호 제8,169,353호에서 도시된 바와 같이, 단일-엔드 증폭기들의 쌍을 대신 포함할 수 있다는 것이 이해된다.

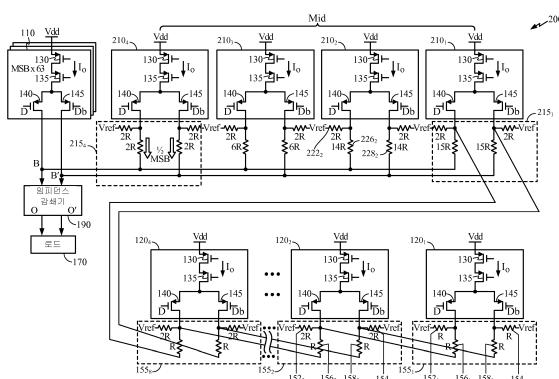

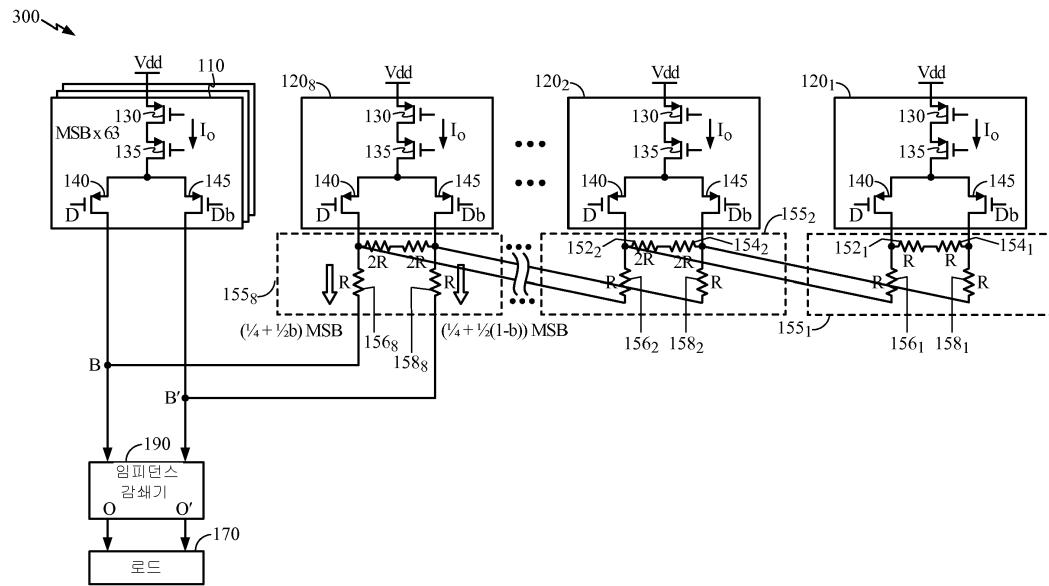

[0042] [0053] 도 4는 본 발명의 다른 예시적인 실시예에 따라 저 클리치 노이즈를 갖도록 적응된 전류 스티어링 DAC(200)의 단순화된 블록도이다. DAC(200)는, DAC(200)의 6개의 MSB들을 형성하기 위해 병렬로 연결되는 63개의 유사한 스테이지들(110<sub>j</sub>)(스테이지(110) 중 단지 하나만이 도시됨)을 부분적으로 포함하는 것으로서 도시된 14-비트 DAC이다. DAC(200)는 또한 DAC(200)의 4개의 중간 비트들(MID)을 형성하는 4개의 스테이지들(210<sub>1</sub>, 220<sub>2</sub>, 220<sub>3</sub>, 220<sub>4</sub>)(대안적으로 그리고 집합적으로 스테이지(210)로서 지칭됨)을 포함한다. DAC(200)는 또한 DAC의 4개의 LSB들을 형성하는 4개의 스테이지들(120<sub>1</sub>, 120<sub>2</sub>, 120<sub>3</sub>, 120<sub>4</sub>)(대안적으로 그리고 집합적으로 스테이지(120 또는 120<sub>i</sub>)로서 지칭됨)을 포함한다. 도시되지 않았지만, DAC(200)는 또한 도 2에서 도시된 것과 유사한 디코더를 포함한다는 것이 이해된다. DAC(200)는 또한 임피던스 감쇄기(190)를 포함한다. DAC(200)가 14-비트 DAC인 것으로서 도시되지만, 본 발명에 따른 저 클리치 노이즈 DAC는 14 비트보다 더 높거나 더 낮은 분해능을 가질 수 있다는 것이 이해된다.

[0043] [0054] 입력 스테이지들(120<sub>i</sub>, 110<sub>j</sub> and 210<sub>m</sub>)(<sub>m</sub>은 1에서 4까지 변동되는 정수)에 배치된 트랜지스터(130)는 실질적으로 동일한 크기를 갖는다. 유사하게, 입력 스테이지들(120<sub>i</sub> 및 110<sub>j</sub> 및 210<sub>m</sub>)에 배치된 트랜지스터들(135)은 실질적으로 동일한 크기를 갖는다. 이에 따라, 모든 스테이지들(120<sub>i</sub>, 110<sub>j</sub> 및 210<sub>m</sub>)에서 생성된 전류(I<sub>0</sub>)는 동일한 크기를 갖는다.

[0044] [0055] DAC(200)의 입력 스테이지들(120<sub>i</sub>)은 위에서 설명된 바와 같이 DAC(100)의 입력 스테이지들(120<sub>i</sub>)(도 2 참조)과 유사하다. DAC(200)의 각각의 MID 스테이지(210<sub>m</sub>)는, 저항 네트워크가 그 스테이지에 할당된 이진 가중치에 따라 그의 연관된 스테이지에 배치된 스위치들로부터 수신한 전류를 스케일링하는 저항 네트워크(215<sub>m</sub>)를 포함한다. 예를 들어, 스테이지(210<sub>4</sub>)는, 그의 연관된 스위치들(140<sub>4</sub> 및 145<sub>4</sub>)로부터 자신이 수신한 전류를 (1/2 x I<sub>0</sub>)로 스케일링하고 이 전류를 DAC(200)의 합산 노드들(B, B')에 전달하는 저항 네트워크(215<sub>4</sub>)를 포함하는 것으로서 도시된다. 입력 스테이지(210<sub>m</sub>)와 연관된 각각의 저항 네트워크의 저항들은, 각각의 이러한 저항 네트워크를 통해 흐르는 전류가 DAC에서 저항 네트워크의 연관된 입력 스테이지의 이진 가중치에 비례하도록 선택된다.

[0045] [0056] 각각의 저항 네트워크들(215<sub>m</sub>)은 4개의 레지스터들을 포함하는 것으로서 도시된다. 저항 네트워크(215<sub>m</sub>)의 레지스터들(222<sub>m</sub> 및 226<sub>m</sub>)은 입력 스테이지(210<sub>m</sub>)에 배치된 트랜지스터 스위치(140<sub>m</sub>)의 드레인 단자에 커플링되는 공통 단자를 갖는다. 유사하게, 각각의 입력 스테이지(210<sub>m</sub>)의 레지스터들(224<sub>8</sub> 및 228<sub>8</sub>)은 입력 스테이지(210<sub>m</sub>)에 배치된 트랜지스터 스위치(145<sub>m</sub>)의 드레인 단자에 커플링되는 공통 단자를 갖는다. 레지스터들(222<sub>m</sub> 및 224<sub>m</sub>)의 제 2 단자들은 기준 전압(V<sub>ref</sub>)을 수신한다. 레지스터(226<sub>m</sub>)의 제 2 단자는 임피던스 감쇄기(190)의 합산 노드(B)에 커플링된다. 마찬가지로, 레지스터(228<sub>m</sub>)의 제 2 단자는 출력 임피던스 감쇄기(190)의 합산 노드(B')에 커플링된다.

[0046] [0057] 저항 네트워크(215<sub>4</sub>)의 4개의 레지스터들(222<sub>4</sub>, 224<sub>4</sub>, 226<sub>4</sub> 및 228<sub>4</sub>) 각각은 2R의 저항을 갖는다. 이에 따라, 입력 스테이지(210<sub>4</sub>)의 트랜지스터들(140, 145)을 통과하는 전류(I<sub>0</sub>)의 절반은 전압(V<sub>ref</sub>)으로 흐르게 되는 반면에, 이 전류의 다른 절반은 합산 노드들(B, B')로 흐르게 된다. 저항 네트워크(215<sub>3</sub>)의 레지스터들(222<sub>3</sub>, 224<sub>3</sub>)은 2R의 저항을 갖는 것으로서 도시되고, 저항 네트워크(215<sub>3</sub>)의 레지스터들(226<sub>3</sub> 및 228<sub>3</sub>)은 6R의 저항을 갖는 것으로서 도시된다. 이에 따라, 입력 스테이지(210<sub>3</sub>)의 트랜지스터들(140<sub>3</sub>, 145<sub>3</sub>)을 통해 흐르는 전류(I<sub>0</sub>)의 3/4(즉, 6/(6+2))가 전압(V<sub>ref</sub>)으로 흐르게 되고, 입력 스테이지(210<sub>3</sub>)의 트랜지스터들(140<sub>3</sub>, 145<sub>3</sub>)을 통해 흐르는 전류(I<sub>0</sub>)의 1/4(즉, 2/(6+2))가 합산 노드들(B, B')로 흐르게 된다. 저항 네트워크(215<sub>2</sub>)의 레지스터들(222<sub>2</sub>, 224<sub>2</sub>)은 2R의 저항을 갖는 것으로서 도시되고 저항 네트워크(215<sub>2</sub>)의 레지스터들(226<sub>2</sub>, 228<sub>2</sub>)은 14R의 저

항을 갖는 것으로서 도시된다. 이에 따라, 입력 스테이지( $210_2$ )의 트랜지스터들( $140_2$ ,  $145_2$ )을 통해 흐르는 전류( $I_o$ )의  $7/8$ (즉,  $14/(14+2)$ )이 전압( $V_{ref}$ )으로 흐르게 되고, 입력 스테이지( $210_2$ )의 트랜지스터들( $140_1$ ,  $145_2$ )을 통해 흐르는 전류( $I_o$ )의  $1/8$ (즉,  $2/(14+2)$ )이 합산 노드들( $B$ ,  $B'$ )로 흐르게 된다. 저항 네트워크( $215_1$ )의 레지스터들( $222_1$ ,  $224_1$ )은  $2R$ 의 저항을 갖는 것으로서 도시되고 저항 네트워크( $215_1$ )의 레지스터들( $226_1$ ,  $228_1$ )은  $15R$ 의 저항을 갖는 것으로서 도시된다. 그러나 도 4로부터 알 수 있는 바와 같이, 입력 스테이지( $210_1$ )의 레지스터들( $222_1$  및  $224_1$ )은 또한 LSB 스테이지( $120_4$ )의 저항 네트워크( $155_4$ )에 연결된다. 이에 따라, 레지스터들( $222_1$ ,  $226_1$ )의 공통 단자와  $V_{ref}$ 간의 유효 저항은  $R$ 이다. 마찬가지로, 레지스터들( $224_1$ ,  $228_1$ )의 공통 단자와  $V_{ref}$ 간의 유효 저항은  $R$ 이다. 이에 따라, 입력 스테이지( $210_1$ )의 트랜지스터( $140_1$ ,  $145_1$ )를 통해 흐르는 전류( $I_o$ )의  $15/16$ (즉,  $15/(15+1)$ )은 전압( $V_{ref}$ )으로 흐르게 되고, 입력 스테이지( $210_1$ )의 트랜지스터들( $140_1$ ,  $145_1$ )을 통해 흐르는 전류( $I_o$ )의  $1/16$ (즉,  $1/(15+1)$ )은 합산 노드들( $B$ ,  $B'$ )로 흐르게 된다. 즉,  $R-2R$  네트워크들이 아니더라도, 스테이지들( $222_4$ ,  $224_4$ ,  $226_4$ ,  $228_4$ ) 각각과 연관되는 저항 네트워크는 DAC 내의 그 스테이지의 이진 가중치에 비례하여 합산 노드들( $B$ ,  $B'$ )에 전류를 제공한다.

[0047] [0058] 각각의 LSB 스테이지( $120_i$ )는 그의 연관된 입력 스테이지에 할당된 이진 가중치에 따라 그것을 통과하는 전류를 스케일링하는 저항 네트워크를 포함한다. 각각의 저항 네트워크에 의해 스케일링되는 전류는 비트 포지션이 1비트 만큼 더 높은 바로 선행 스테이지의 저항 네트워크에 전달된다. 예를 들어, 저항 네트워크( $155_4$ )에 의해 스케일링되는 전류는, 체인 유사 방식으로 그리고 도 4에서 도시된 바와 같이, MID 스테이지( $210_1$ )와 연관된 저항 네트워크( $215_1$ )에 전달되고; 저항 네트워크( $155_3$ )에 의해 스케일링되는 전류는 저항 네트워크( $155_4$ )에 전달되고; 저항 네트워크( $155_2$ )에 의해 스케일링되는 전류는 저항 네트워크( $155_3$ )에 전달되고; 저항 네트워크( $155_1$ )에 의해 스케일링되는 전류는 저항 네트워크( $155_2$ )에 전달된다.

[0048] [0059] 도 5는 본 발명의 다른 예시적인 실시예에 따라, 저 클리치 노이즈를 갖도록 적응되는 전류-스티어링 14-비트 DAC(300)의 단순화된 블록도이다. 도시되지 않았지만, DAC(300)는 또한 도 2에서 도시된 것과 유사한 디코더를 포함한다는 것이 이해된다. DAC(300)는 14 비트보다 더 높거나 더 낮은 분해능을 가질 수 있다는 것이 또한 이해된다.

[0049] [0060] DAC(300)는 DAC의 6개의 MSB들을 형성하도록 병렬로 연결되는 63개의 유사한 스테이지들( $110$ )을 포함하는 것으로서 도시된다. DAC(300)는 추가로 도 2의 DAC(100)와 유사한 방식으로 DAC의 8개의 LSB들을 형성하는 8개의 스테이지들( $120_i$ )을 포함한다. DAC(300)는 기준 전압( $V_{ref}$ )에 대한 필요성을 분배하고 차동 DAC이다. 도 5에서 도시된 바와 같이, 저항 네트워크들( $155_i$ ) 각각의 레지스터들( $152_i$  및  $154_i$ )은 전압 소스( $V_{ref}$ )에 커플링(도 2 참조)되는 대신 서로 커플링된다. 레지스터들( $152_i$ ,  $154_i$ ) 각각은  $2R$ 의 저항을 갖는 것으로서 도시된다. 레지스터들( $152_i$ ,  $154_i$ ) 각각은  $R$ 의 저항을 갖는 것으로서 도시된다.

[0050] [0061] 도 5로부터 알 수 있는 바와 같이, 예를 들어, 저항 네트워크( $155_8$ )의 레지스터들( $156_8$  및  $158_8$ )을 통해 흐르는 전류들은 각각  $[(1/4 + 1/2*b)*I_o]$  및  $[(1/4 + 1/2*(1-b))*I_o]$ 와 동일하게 도시되며, 여기서  $b$ 는 14-비트 DAC(300)의 비트 8의 이진 값이다. 도 5로부터 또한 알 수 있는 같이, 스테이지( $120_8$ ) 외에, 다른 스테이지들( $120_i$ ) 각각에서 생성된 전류는, 도 2의 DAC(100)와 관련하여 또한 기술되었던 것처럼, 스테이지의 연관된 저항 네트워크에 의해 스케일링되고, 그것이 전류를 수신한 스테이지의 비트 포지션보다 비트 포지션이 하나 더 높은 바로 선행 스테이지의 저항 네트워크에 전달된다. 예를 들어, 스테이지( $120_1$ )의 저항 네트워크( $155_1$ )에 의해 스케일링된 전류는 스테이지( $120_2$ )의 저항 네트워크( $155_2$ )에 전달된다.

[0051] [0062] DAC들(100, 200, 또는 300) 중 임의의 것의 임피던스 감쇄기( $190$ )에 배치된 증폭기는 제한된 이득-대역 폭(gain-bandwidth product)을 갖기 때문에, 노드들( $B$ ,  $B'$ )의 전압은 DAC 출력 전류가 변동될 때 변동될 수 있다. 도 3을 참조하면, PMOS 트랜지스터들( $182$ ,  $184$ )의 게이트-소스 커패시턴스가 비교적 크기 때문에, 임피던스 감쇄기의 출력 노드들, 즉, 트랜지스터들( $182$ ,  $184$ )의 게이트 단자들에서 비선형 전류 변동들은 임피던스 감쇄기( $B$ ,  $B'$ )의 입력 노드들에 커플링되게 될 수 있고, 그에 의해 노드들( $B$ ,  $B'$ )에서의 전류들이 비선형으로 변

동되게 한다. 이러한 비선형 전류들은 이어서 저항 네트워크들을 통해 전압 소스( $V_{ref}$ )로 흐를 수 있다. 저항 네트워크들의 저항(R)이 DAC 트랜지스터들의 기생 커패시턴스보다 더 작기 때문에, 이러한 전류 흐름은 DAC의 SFDR을 저하시킬 수 있다. 저항(R)이 더 낮을수록, 저하가 더 크다.

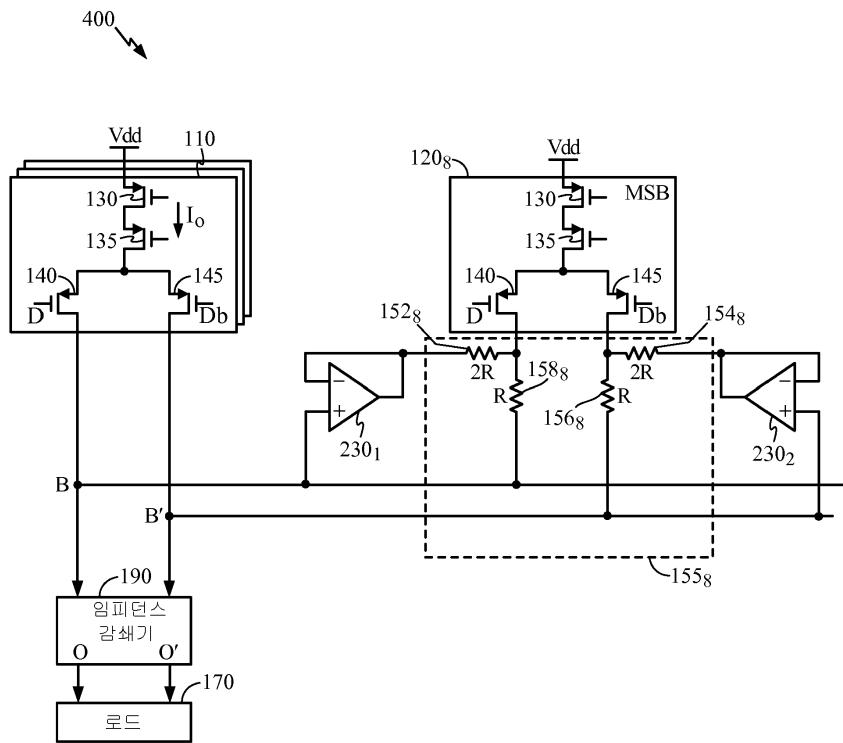

[0052] [0063] 본 발명의 일 실시예에 따라, 임피던스 감쇄기의 입력 노드들로의/로부터의 비선형 전류 흐름으로 인한 SFDR 저하를 최소화하기 위해, 레지스터 전압들이 트래킹된다. 도 6은 본 발명의 일 실시예에 따라 DAC(400)의 세그먼트의 단순화된 블록도이다. DAC(400)는 예를 들어, 도 2에서 도시된 DAC(100)의 세그먼트일 수 있다. DAC의 MSB 스테이지들 중 하나( $110_1$ ) 및 LSB 스테이지들 중 하나( $120_8$ )만이 도 6에서 도시되지만, DAC(400)는 훨씬 더 많은 입력 스테이지들을 갖는다는 것이 이해된다. 입력 스테이지( $120_8$ )의 저항 네트워크는 증폭기들( $230_1$  및  $230_2$ )의 쌍을 포함하도록 적응된다. 증폭기( $230_1$ )의 음의 입력 단자는 도시된 바와 같이 레지스터( $152_8$ )의 단자들 중 하나에 그리고 증폭기의 출력 단자에 커플링된다. 증폭기( $230_1$ )의 양의 입력 단자는 노드 B에 커플링된다. 마찬가지로, 증폭기( $230_2$ )의 음의 입력 단자는 도시된 바와 같이 레지스터( $154_8$ )의 단자들 중 하나에 그리고 증폭기의 출력 단자에 커플링된다. 증폭기( $230_2$ )의 양의 입력 단자는 노드 B'에 커플링된다. 2개의 증폭기들 각각의 2개의 입력 단자들 간의 가상 접지의 존재로 인해, 증폭기( $230_1$ )의 출력 전압은 노드 B의 전압을 트래킹하고 증폭기( $230_2$ )의 출력 전압은 노드 B'의 전압을 트래킹하여, SFDR 저하를 최소화한다. 즉, 노드 B에서의 전압의 변동들이 레지스터( $152_8$ )의 단자에 반영되고, 노드 B'에서의 전압의 변동들이 레지스터( $154_8$ )의 단자에 반영되기 때문에, 이러한 전압 변동들은 레지스터들을 통해 노드들(B 및 B')로부터  $V_{ref}$ 로 또는 그 반대로의 전류 흐름을 야기하지 않고, 그에 따라 SFDR 저하를 방지한다. 도 6에서 도시되지 않았지만, DAC(300)의 다른 스테이지들( $120_i$ ) 각각은 동일한 트래킹 회로를 공유할 것이라고 이해된다.

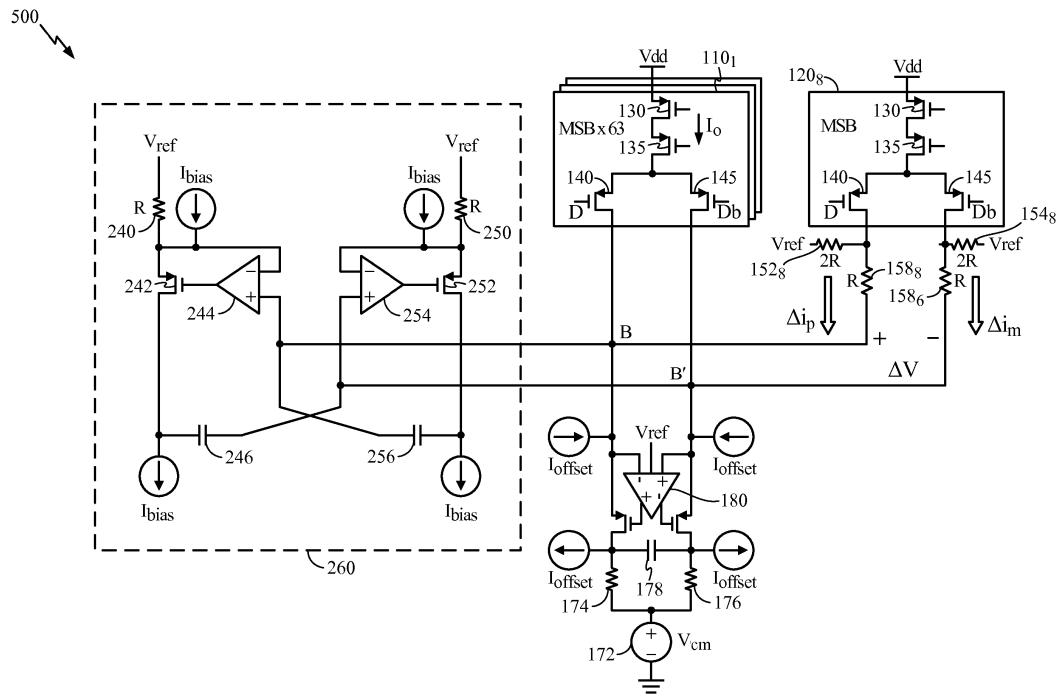

[0053] [0064] 도 7은 본 발명의 일 실시예에 따라 DAC(500)의 세그먼트의 단순화된 블록도이다. DAC(500)는 예를 들어, 도 2에서 도시된 DAC(100)의 세그먼트일 수 있다. DAC의 MSB 스테이지들 중 하나( $110_1$ ) 및 LSB 스테이지들 중 하나( $120_8$ )만이 도 7에서 도시되었지만, DAC(500)는 훨씬 더 많은 입력 스테이지들을 갖는다는 것이 이해된다. DAC(500)는 레지스터들(240, 250), 트랜지스터(242, 252), 증폭기들(244, 254) 및 커패시터들(244, 256)을 포함하는 왜곡 소거 회로(260)가 배치되어 있다.

[0054] [0065] 왜곡 소거 회로(260)는 아래에서 추가로 설명되는 바와 같이, 공급 전압( $V_{ref}$ )과 노드들(B, B') 간의 전류 흐름을 방해하고 소거하도록 적응된다. 노드 B(즉, 증폭기(244)의 양의 단자)에서의 전압( $V_p$ )의 임의의 감소는, 증폭기(244)의 입력 단자들 간의 가상 접지의 존재로 인해 증폭기(244)의 음의 단자(PMOS(242)의 소스 단자)에서의 전압을 감소시키고, 그에 의해 트랜지스터(242)를 통한 전류 흐름의 증가를 야기한다. 커패시터(246)를 통해 노드 B'에 AC 커플링되는 이 전류 증가는 노드 B'로 흐르고, 그에 의해 레지스터들( $152_8$  및  $158_8$ )을 통해  $V_{ref}$ 로부터 노드 B로의 차동 전류 흐름을 소거한다. 유사하게, 노드 B에서의 전압( $V_p$ )의 임의의 증가는 증폭기(244)의 음의 단자에서의 전압을 증가시키고, 그에 의해 트랜지스터(242)를 통한 전류 흐름의 감소를 야기한다. 커패시터(246)를 통해 노드 B'에 AC 커플링되는 이 전류 감소 노드 B'로 흐르고, 그에 의해 레지스터들( $152_8$  및  $158_8$ )을 통해  $V_{ref}$ 로부터 노드 B로의 차동 전류 흐름을 소거한다. 트랜지스터(242)의 소스 단자에서의 전압의 임의의 증가/감소는 또한 레지스터(240)를 통해  $V_{ref}$ 로의/로부터의 전류 흐름을 야기한다. 마찬가지로, 트랜지스터(252)의 소스 단자에서의 전압의 임의의 증가/감소는 또한 레지스터(250)를 통해  $V_{ref}$ 로의/로부터의 전류 흐름을 야기한다.

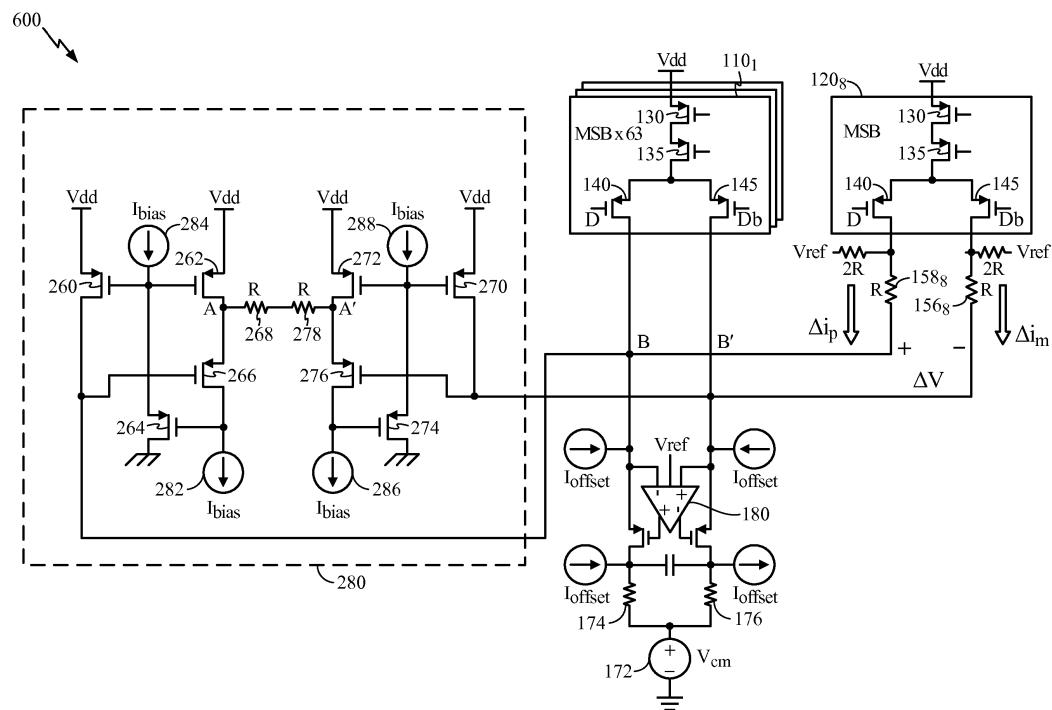

[0055] [0066] 도 8은 본 발명의 일 실시예에 따라 DAC(600)의 세그먼트의 단순화된 블록도이다. DAC(600)는 예를 들어, 도 2에서 도시된 DAC(100)의 세그먼트일 수 있다. DAC의 MSB 스테이지들 중 하나( $110_1$ ) 및 LSB 스테이지들 중 하나( $120_8$ )만이 도 8에서 도시되지만, DAC(600)는 훨씬 더 많은 입력 스테이지들을 갖는다는 것이 이해된다. DAC(600)는 트랜지스터들(260, 262, 264, 266, 270, 272, 274, 276), 레지스터들(268, 278) 및 전류 소스들(282, 284, 286, 및 288)을 포함하는 왜곡 소거 회로(280)가 배치되어 있다.

[0056] [0067] 그의 게이트에서 노드들(B, B')로부터 전압들( $V_p$  및  $V_m$ )을 각각 수신하는 트랜지스터들(266 및 276)은 왜곡 소거 회로(280)에 대한 입력 스테이지를 형성한다. 트랜지스터들(266 및 276)을 통한 전류가 전류 소스들

(282 및 286)에 의해 각각 세팅되기 때문에, 전압( $V_p$ )이 증가하고 전압( $V_m$ )이 변경되지 않은 채로 남아있는 경우, 노드 A에서 트랜지스터(266)의 소스 전압은 트랜지스터(266)의 게이트-소스 전압을 거의 일정하게 유지하도록 또한 증가한다. 노드 A'에서의 전압은 변경되지 않은 채로 남아있게 된다. 그러므로 전류는 노드 A로부터 노드 A'로 흐른다. 노드 A로부터 노드 A'로 흐르는 전류는 트랜지스터(262)에 의해 생성된다. 이러한 추가 전류를 수용하기 위해, 트랜지스터(262)의 게이트 전압은 감소되고, 결국 트랜지스터(260)를 통한 전류 흐름의 유사한 증가를 발생시킨다. 트랜지스터(262)와의 전류 미러를 형성하는 트랜지스터(260)를 통해 증가된 전류는 전압( $V_p$ )을 훨씬 더 증가시킨다. 그러나, 노드 B의 임피던스가 임피던스 감쇄기에 의해 비교적 낮은 값으로 유지되기 때문에, 전압( $V_p$ )은 단지 약간만 증가한다. 예를 들어,  $V_p=1.0002$ ,  $V_m=999.8$  mV라고 가정하면, 로드 임피던스는 1k-옴이고, 임피던스 감쇄기는 1옴만큼 로드의 임피던스를 감쇄한다. 이는 주입된 전류가 약 400nA가 되게 하고, 이에 따라 200nV((400nA/2\*1ohm))만큼 전압( $V_p$ )을 증가시킨다. 그러므로 루프 이득은 1(unity)보다 훨씬 더 작다. 왜곡 소거 회로(280)는 이에 따라 양의 피드백 회로를 이용하여 동작한다. 노드들(B, B')에서의 비교적 작은 입력 임피던스는, 이러한 피드백 루프의 이득이 안정성을 제공하고 동요(oscillation)를 방지하도록 1보다 더 작다는 것을 보장한다.

[0057]

[0068] 노드 A로부터 노드 A'로의 전류 흐름은 또한 트랜지스터(272)를 통한 전류가 감소하게 한다. 트랜지스터들(270 및 272)이 또한 전류 미러를 형성하기 때문에, 트랜지스터(272)를 통한 전류의 감소는 트랜지스터(270)를 통한 전류의 유사한 감소를 야기하고, 그에 의해 전압( $V_m$ )의 감소를 야기한다. 그러나 위에서 설명된 것처럼, 노드 B'가 비교적 작은 임피던스를 갖기 때문에, 전압( $V_m$ )의 감소는 비교적 작다.

[0058]

[0069] 트랜지스터(264)는 소스-팔로워 증폭기(source-follower amplifier)로서 구성된다. 그러므로, 트랜지스터(264)의 게이트 전압의 변화는 트랜지스터(264)의 소스에서 대응하는 전압 변화들에서 반영된다. 전류 소스(284)는 트랜지스터(264)를 통해 흐르도록 적응된다. 트랜지스터(274)는 또한 소스-팔로워 증폭기로서 구성된다. 그러므로 트랜지스터(274)의 게이트 전압의 변화들은 트랜지스터(274)의 소스에서의 대응하는 전압 변화들에서 반영된다. 전류 소스(288)는 트랜지스터(274)를 통해 흐르도록 적응된다. 소거 회로(280)는 잘 알려져 있고, IEEE, 국제 고상 회로를 컨퍼런스, 1193, 세션 7, 아날로그 기술, 논문 TA 7.2, 112-114페이지들에서 설명된다. 왜곡 소거 회로가 도 8을 참조하여 설명되지만, 유사한 일정한 전압-전류 변환을 수행하는 임의의 다른 왜곡 소거 회로가 이용될 수 있다는 것이 이해된다.

[0059]

[0070] 알려진 바와 같이, 글리치 노이즈 및 이에 따른 글리치 에너지는 DAC의 동작의 주파수가 감소할 때 증가한다. 예를 들어, 도 2를 참조하면, 동작의 주파수가 증가할 때, 글리치 에너지 중 일부는 트랜지스터(140, 145)의 드레인-기판 기생 커패시터들 또는 배선의 기생 커패시턴스를 통해 접지로 흐른다. 접지로 흐르는 글리치 에너지는 일반적으로 LSB들보다 MSB들에 대해 더 적다. DAC의 상이한 입력 스테이지들로부터 접지로 흐르는 글리치 에너지의 불균형은 글리치 노이즈를 추가로 증가시킬 수 있는 불균형을 생성할 수 있다.

[0060]

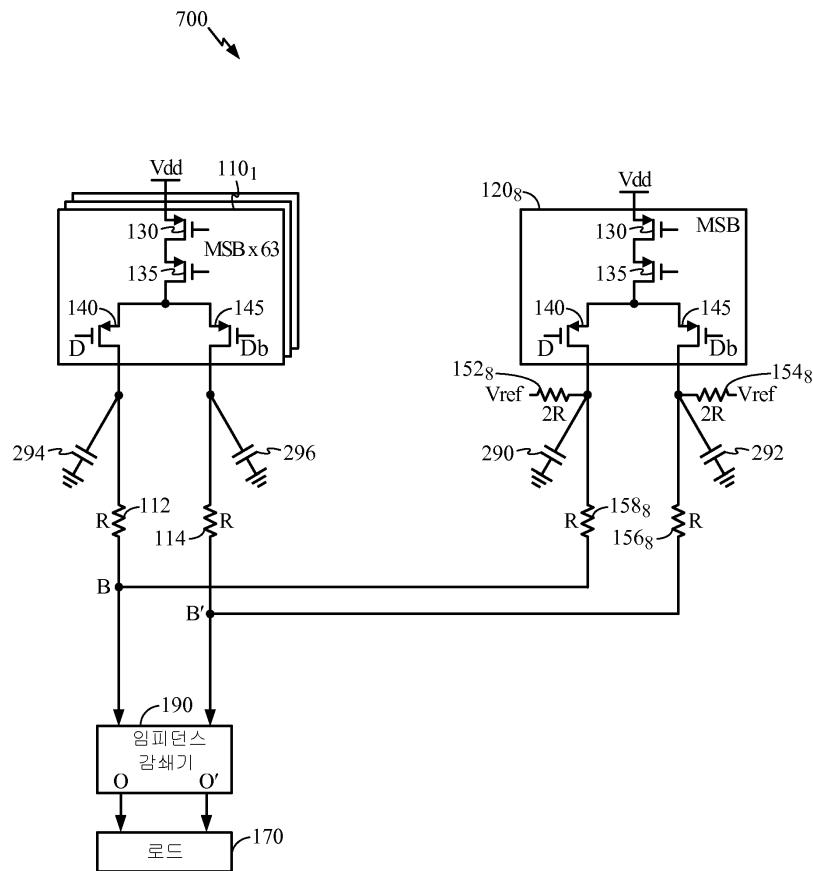

[0071] 도 9는 본 발명의 일 실시예에 따라 DAC(700)의 세그먼트의 단순화된 블록도이다. DAC(700)는 예를 들어, 도 2에서 도시된 DAC(100)의 세그먼트일 수 있다. DAC(700)의 MSB 스테이지들 중 하나( $110_1$ ) 및 LSB 스테이지들 중 하나( $120_8$ ) 만이 도 9에서 도시되지만, DAC(700)는 훨씬 더 많은 입력 스테이지들을 갖는다는 것이 이해된다. 도 9는 또한, 접지와 입력 스테이지( $120_8$ )의 트랜지스터들(140, 145)의 드레인 단자들 간에 존재하는 기생 커패시턴스들(290, 292)은 물론, 접지와 입력 스테이지( $110_1$ )의 트랜지스터들(140, 145)의 드레인 단자들 간에 존재하는 기생 커패시턴스들(294, 296)을 도시한다.

[0061]

[0072] 입력 스테이지들( $120_8$ ,  $110_1$ )로부터 접지로 흐르는 글리치 에너지의 불균형에 의해 야기되는 글리치 노이즈를 최소화하기 위해, 본 발명의 일 실시예에 따라, 레지스터들(112, 114)이 DAC(700)의 합산 노드들(B, B')과 MSB 스테이지( $110_1$ )의 트랜지스터들(140, 145)의 드레인 단자들 간에 배치된다. 레지스터(112 및 114) 각각은 R의 저항을 갖는다. 레지스터들(112, 114)은 입력 스테이지( $120_8$ )의 트랜지스터들(140, 145)의 드레인 단자에서 확인된 RC 값들이, 입력 스테이지( $110_1$ )의 트랜지스터들(140, 145)의 드레인 단자들에 의해 확인된 것들과 각각 매칭하게 한다. 이러한 RC 매칭은 접지로의 글리치 에너지 재분배의 불균형을 방지하고, 그에 따라 입력 스테이지( $110_1$ )로부터의 글리치 노이즈가 입력 스테이지( $120_8$ )로부터의 글리치 노이즈와 매칭하게 한다. DAC(700)의 병렬 스테이지들(110) 각각은 레지스터들(112, 114)을 포함할 수 있다는 것이 이해된다.

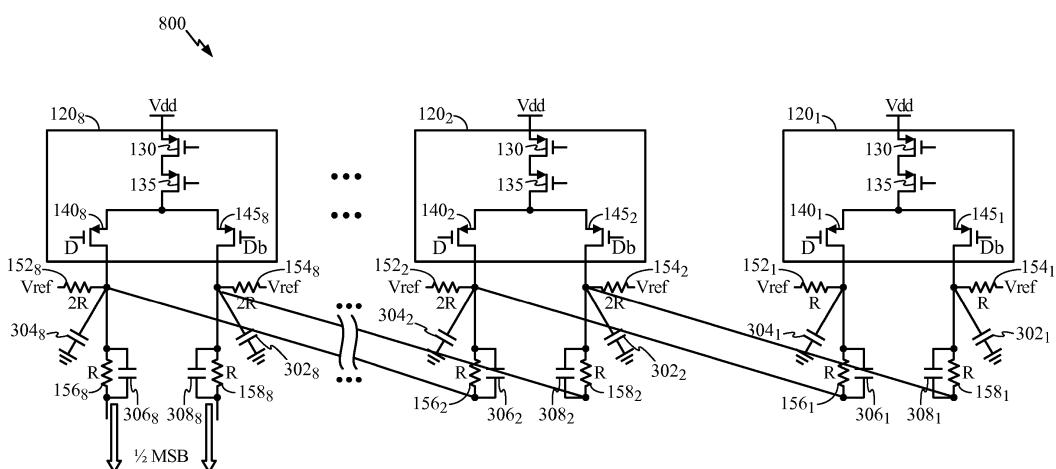

- [0062] [0073] 도 10은 본 발명의 일 실시예에 따라, DAC(800)의 세그먼트의 단순화된 블록도이다. DAC(800)는 예를 들어, 도 2에서 도시된 DAC(100)의 세그먼트일 수 있다. DAC(800)의 LSB 스테이지들( $120_1$  및  $120_2$ ) 중 3개만이 도 10에서 도시되었지만, DAC(800)는 훨씬 더 많은 입력 스테이지들을 갖는다는 것이 이해된다. 도 10은 또한 입력 스테이지( $120_1$ )의 트랜지스터들( $140_1$ ,  $145_1$ )과 연관되는 기생 커패시턴스들( $302_1$ ,  $304_1$ ), 입력 스테이지( $120_2$ )의 트랜지스터들( $140_2$ ,  $145_2$ )과 연관된 기생 커패시턴스들( $302_2$ ,  $304_2$ ), 및 입력 스테이지( $120_8$ )의 트랜지스터들( $140_8$ ,  $145_8$ )과 연관되는 기생 커패시턴스들( $302_8$ ,  $304_8$ )을 도시한다. 상이한 입력 스테이지들 간의 글리치 노이즈를 막기 위해, DAC(800)의 각각의 입력 스테이지는 그 스테이지의 레지스터들( $156_i$  및  $158_i$ ) 간에 병렬로 배치되는 커패시터들( $306_i$ ,  $308_i$ )의 쌍을 포함하도록 적응된다. 예를 들어, 도시된 바와 같이, 커패시터들( $306_1$ ,  $308_1$ )은 입력 스테이지( $120_1$ )의 레지스터들( $156_1$  및  $158_1$ ) 간에 병렬로 배치된다. 마찬가지로, 커패시터들( $306_8$ ,  $308_8$ )은 입력 스테이지( $120_8$ )의 레지스터들( $156_8$  및  $158_8$ ) 간에 병렬로 배치된다. 각각의 스테이지에서 커패시터들( $306_i$ ,  $308_i$ )은 그 스테이지의 기생 커패시턴스들( $302_i$ ,  $304_i$ )을 통한 접지로의 글리치 에너지 손실을 봉쇄하고 소거하도록 글리치 에너지를 피드포워드(feedforward)하도록 적응된다. 일 실시예에서, 커패시터들( $306_i$ ,  $308_i$ ) 각각은 커패시터들( $302_i$ ,  $304_i$ )의 기생 커패시턴스의 2배의 커패시턴스를 갖도록 선택된다.

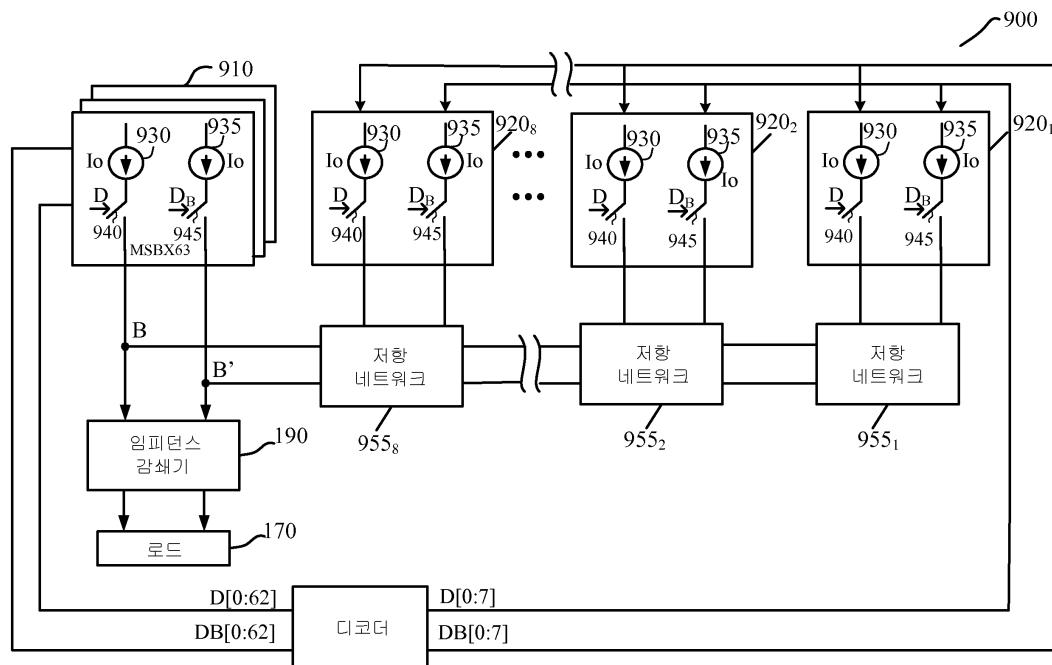

- [0063] [0074] 도 11은 본 발명의 다른 예시적인 실시예에 따라, 저 글리치 노이즈를 갖도록 적응된 14-비트 전류 스티어링 DAC(900)의 블록도이다. DAC(900)는 도 1에서 도시된 디바이스(150)에서 이용될 수 있다. DAC(900)가 14-비트 분해능을 갖는 것으로서 도시되었지만, 본 발명에 따른 저 글리치 노이즈 DAC는 14비트들보다 더 높거나 더 낮은 분해능을 가질 수 있다는 것이 이해된다. DAC(900)는 DAC의 6개의 최상위 비트들(MSB들)을 형성하기 위해 병렬로 연결되는 (단순함을 위해 스테이지들(910) 중 단지 하나만이 도시됨) 63개의 유사한 입력 스테이지들( $910_j$ )( $j$ 는 1로부터 63까지 변동되는 정수임)을 포함한다. DAC(900)는 또한 DAC의 8개의 최하위 비트들(LSB들)을 형성하는 8개의 스테이지들( $920_i$ )( $i$ 는 1로부터 8까지 변동되는 정수임)을 포함한다. 63개의 입력 스테이지들( $910_j$ )은 대안적으로 및 집합적으로 입력 스테이지(910)로서 지칭된다. 마찬가지로, 8개의 입력 스테이지들( $920_i$ )은 대안적으로 및 집합적으로 입력 스테이지(920)로서 지칭된다. 단순함을 위해, 입력 스테이지들( $920_i$ ) 중 3개만이 도시된다.

- [0064] [0075] DAC(900)는 아래에서 상세히 설명된 바와 같이, 임피던스 감쇄기(190)를 포함하는 것으로서 또한 도시된다. DAC(900)는 14-비트 입력 신호( $D_{in}[13:0]$ )를 수신하고, 다양한 스테이지들(910, 920)의 스위치들(940, 945)에 인가되는 다양한 참(D) 및 보수 비트들(DB)을 디코딩하는 디코더(160)를 포함하는 것으로서 또한 도시된다.

- [0065] [0076] 각각의 입력 스테이지( $920_i$ )는 전류 소스(930, 935)의 쌍을 포함하는 것으로서 도시된다. 각각의 입력 스테이지( $920_i$ )는 또한, 전류 소스들(930, 935)에 의해 공급되는 전류들은 물론, 입력 스테이지와 연관되고 그에 의해 수신되는 차동 데이터(D 및 DB)의 쌍에 응답하는 스위치들(940 및 945)의 쌍을 포함하는 것으로서 또한 도시된다. 스테이지들( $920_i$  및  $910_j$ )에서 전류 소스(930, 935)에 의해 생성된 전류들( $I_0$ )은 실질적으로 동일한 크기를 갖는다.

- [0066] [0077] DAC(900)는 8개의 LSB 스테이지들( $920$ )의 상이한 것과 각각 연관되는 8개의 저항 네트워크들( $955_i$ )을 포함하는 것으로서 또한 도시된다. 각각의 저항 네트워크( $955_i$ )는 입력 스테이지( $920_i$ )와 연관되고, 저항 네트워크가 그의 연관된 입력 스테이지로부터 수신한 전류를 스케일링하도록 적응된다. 일 실시예에서, 각각의 입력 스테이지와 연관되는 저항 네트워크는 그 입력 스테이지에 배치된 스위치들(940, 945)로부터 볼 때 R-2R 네트워크를 형성한다.

- [0067] [0078] 도 11로부터 알 수 있는 바와 같이, 각각의 스테이지( $920_k$ )(여기서  $k$ 는 1 내지 7 범위의 정수임)와 연관되는 저항 네트워크는 입력 스테이지( $920_k$ )의 비트 포지션보다 하나 더 높은 비트 포지션을 갖는 입력 스테이지( $920_{k+1}$ )의 저항 네트워크에 커플링된다. 예를 들어, 입력 스테이지( $920_2$ )와 연관되는 저항 네트워크( $955_2$ )는 입력 스테이지( $920_3$ )와 연관되는 저항 네트워크( $955_3$ )에 커플링되는 것으로서 도시된다. 저항 네트워크( $955_8$ )는 임피던스 감쇄기(190)의 합산 노드들(B, B')에 커플링된다.

- [0068] [0079] 각각의 저항 네트워크를 통해 흐르는 전류는 저항 네트워크의 연관된 입력 스테이지( $920_i$ )의 이진 가중치에 비례한다. 이에 따라, 각각의 입력 스테이지의 전류 소스들(930 및 935)을 통해 흐르는 전류가  $I_0$ 인 것으로 가정하는 경우, 예를 들어, (7번째 최상위 비트와 연관되는) 스테이지( $920_8$ )의 저항 네트워크( $955_8$ )를 통해 합산 노드( $B, B'$ )로 흐르는 전류는  $(1/2)*I_0$ 이다. 마찬가지로, (최하위 비트와 연관되는) 스테이지( $920_1$ )의 저항 네트워크( $955_1$ )를 통해 합산 노드들( $B, B'$ )로 흐르는 전류는  $(1/256)*I_0$ 이다. 저항 네트워크들( $955_i$ )을 통해 흐르는 전류들은 입력 신호를 감쇄기(190)에 제공하는 전류 합산 노드들( $B, B'$ )로 전달된다. 이진 가중치를 이용하여 전류를 스케일링하도록 적응된 임의의 저항 네트워크가 이용될 수 있다는 것이 이해될 것이다.

- [0069] [0080] DAC의 모든 입력 스테이지들(910, 920)의 스위치들(940 및 945)을 통해 흐르는 전류들은 실질적으로 동일하고, 그의 연관된 저항 네트워크에 의해서만 (트랜지스터 스위치를 통과한 이후) 스케일링되기 때문에, DAC(900)의 MSB 및 LSB 스테이지들 간의 글리치 에너지는 매칭된다. DAC(900)는 이에 따라 종래의 DAC들보다 실질적으로 더 낮은 글리치 노이즈를 갖는다. 저항 네트워크들은 이진 가중치들을 이용하여 스위치를 통과하는 전류들을 정확하게 분할한다. 예시적인 14-비트 DAC(900)에 대한 8-비트 정확도의 레지스터 매칭은 비교적 쉽게 달성 가능하다.

- [0070] [0081] 임피던스 감쇄기(190)는 유리하게는 출력 로드(170)가 가질 수 있는 임피던스들의 범위를 증가시킨다. 임피던스 감쇄기(190)는 프로세스, 전압 및 온도의 변동들로 인한 출력 로드 임피던스의 변화들을 참작하도록 추가로 적응된다. 결과적으로, DAC(900)의 모든 입력 스테이지들이 동일한 양의 전류를 생성하고 유사한 스위치 크기들을 갖기 때문에, DAC(900)는 종래의 DAC들보다 훨씬 더 적은, 프로세스, 전압 및 온도에 걸친 대역외 노이즈 변동을 갖는다.

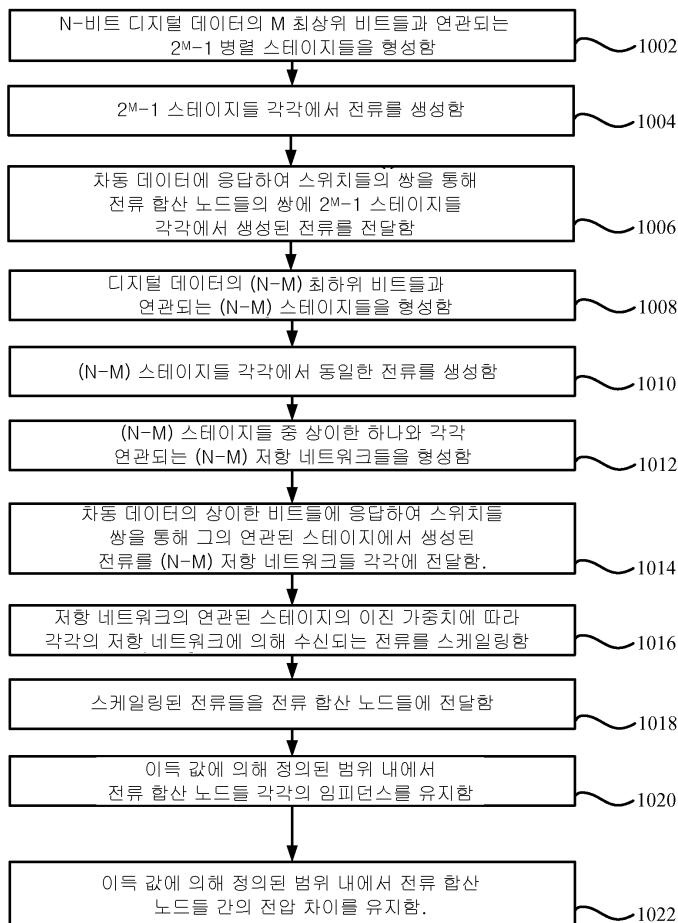

- [0071] [0082] 도 12는 본 발명의 일 실시예에 따라 N-비트 디지털 신호를 아날로그 신호로 변환하기 위한 방법의 흐름도(1000)이다. 이 변환을 달성하기 위해, 디지털 데이터의 M개의 최상위 비트들과 연관되는  $(2M-1)$ 개의 병렬 스테이지들이 형성된다(1002).  $(2M-1)$  스테이지들 각각에서, 전류가 생성되고(1004), 차동 데이터의 쌍에 응답하여 스위치들의 쌍을 통해 전류 합산 노드들의 쌍에 전달된다(1006). 추가로, 방법에 따라, 디지털 데이터의  $(N-M)$  최하위 비트들과 연관되는  $(N-M)$  스테이지들이 또한 형성된다(1008).  $(2M-1)$  병렬 스테이지들에서 생성된 것들과 동일한 레벨을 갖는 전류는  $(N-M)$  스테이지들 각각에서 또한 생성된다(1010).  $(N-M)$  스테이지들 중 상이한 하나와 각각 연관되는  $(N-M)$ 개의 저항 네트워크들이 또한 형성된다(1012).  $(N-M)$  스테이지들 각각에서 생성된 전류는 차동 데이터의 상이한 비트들에 응답하여 스위치들 쌍을 통해 그의 연관된 저항 네트워크에 전달된다(1014). 각각의 저항 네트워크에 의해 수신되는 전류는 저항 네트워크의 연관된 스테이지의 이진 가중치에 따라 스케일링되고(1016), 전류 합산 노드들에 전달된다(1018). 전류 합산 노드들 각각의 임피던스는 이득 값에 의해 정의된 범위 내에서 유지된다(1020). 또한, 전류 합산 노드들 간의 전압 차이는 이득 값에 의해 정의된 범위 내에서 또한 유지된다(1022). 전류 합산 노드들에 전달된 전류들의 차이는 변환된 아날로그 신호의 값을 정의한다.

- [0072] [0083] 본 발명의 위의 실시예들은 예시적이며 제한적이지 않다. 본 발명의 실시예들은 DAC의 분해능에 의해 정의되지 않는다. 본 발명의 실시예들은 입력 스테이지 스위치들과 전류 합산 노드들 간에 배치되는 저항 네트워크, R-2R, 또는 기타 등의 구성에 의해 제한되지 않는다. 본 발명의 실시예들은 DAC가 배치될 수 있는 디바이스, 무선, 또는 기타 등의 타입에 의해 제한되지 않는다. 다른 부가들, 차감들 또는 변형들은 본 개시를 고려하여 명백하며 첨부된 청구항들의 범위 내에 있는 것으로 의도된다.

## 도면

## 도면1

## 도면2

도면3

도면4

## 도면5

## 도면6

## 도면7

## 도면8

도면9

도면10

## 도면11

## 도면12