(12)发明专利

(10)授权公告号 CN 106123929 B

(45)授权公告日 2019.09.27

(21)申请号 201610526016.5

(74)专利代理机构 中国国际贸易促进委员会专

(22)申请日 2012.06.08

利商标事务所 11038

(65)同一申请的已公布的文献号

代理人 张鑫

申请公布号 CN 106123929 A

(51)Int.Cl.

G01D 5/24(2006.01)

(43)申请公布日 2016.11.16

G01R 27/26(2006.01)

(30)优先权数据

(56)对比文件

1155288 2011.06.16 FR

US 2008231292 A1,2008.09.25,

(62)分案原申请数据

FR 2756048 B1,1998.05.22,

201280029578.9 2012.06.08

FR 2608751 B1,1990.11.30,

(73)专利权人 快步科技有限责任公司

CN 101467265 A,2009.06.24,

地址 美国特拉华

审查员 金星池

(72)发明人 克里斯多夫·布隆丹

克丽汀·尼尔 迪迪埃·罗齐埃

权利要求书2页 说明书10页 附图4页

(54)发明名称

包括浮桥的用于电容式测量的集成电路

(57)摘要

本发明涉及包括浮桥的用于电容式测量的集成电路。提供了一种电容式测量设备，其包括：(i)第一电子系统，被电参考至保护电位，并且能够连接到电容性电极，(ii)第二电子系统，被电参考至接地电位，以及(iii)激励装置，分别连接到所述保护和接地电位，从而在这些电位之间施加AC电压差。所述设备还包括以接地为参考的集成电路，所述集成电路包括：在其中实现了所述第一电子系统的第一安装区域，以及在其中实现了所述第二电子系统的第二安装区域。本发明还涉及使用该设备的系统以及该设备的用途。

1. 一种电容式测量系统,包括:

包括衬底的芯片,所述芯片包括:

第一电子系统,在电气上以保护电位为参考,并且被配置为电容式检测一个或多个对象;

第二电子系统,不同于第一电子系统,并且在电气上以接地电位为参考,接地电位不同于保护电位;

激励电路,被耦合为产生第一电子系统处的保护电位;以及

解耦电路,所述解耦电路包括电容器并且被配置为在维持保护电位和接地电位之间的隔离的同时通信地耦合第一电子系统和第二电子系统,

其中:

所述激励电路被配置为在保护电位和接地电位之间产生AC电压差,并且

所述激励电路包括:

AC电压源,以接地电位为参考,并且被配置为产生AC电压;以及

电压供应电路,以保护电位为参考,并且被配置为接收来自AC电压源的AC电压以及产生用于以保护电位为参考的第一电子系统的供电电压。

2. 如权利要求1所述的电容式测量系统,还包括屏蔽平面,该屏蔽平面被保持在保护电位并且被配置为至少部分地屏蔽第一电子系统。

3. 如权利要求2所述的电容式测量系统,所述屏蔽平面被配置为至少部分地屏蔽第二电子系统。

4. 如权利要求1所述的电容式测量系统,其中第一电子系统包括获取电路,第二电子系统包括处理电路。

5. 如权利要求1所述的电容式测量系统,所述激励电路包括:

振荡器电路,以保护电位为参考,并且被配置为产生激励信号;以及

缓冲器电路,以接地电位为参考,并且被配置为接收激励信号和产生保护电位。

6. 如权利要求1所述的电容式测量系统,其中,所述芯片还包括所述激励电路。

7. 如权利要求1所述的电容式测量系统,还包括多个第一电子系统和多个第二电子系统,其中第二电子系统中的一个被配置为在主模式下操作,其余第一电子系统和第二电子系统被配置为在从模式下操作。

8. 如权利要求7所述的电容式测量系统,其中被配置为在主模式下操作的第二电子系统被进一步配置为将输出发送到被配置为在从模式下操作的第一电子系统。

9. 如权利要求1所述的电容式测量系统,其中,所述芯片还包括所述解耦电路。

10. 如权利要求1所述的电容式测量系统,其中,所述芯片还包括所述激励电路和所述解耦电路。

11. 一种电容式测量方法,包括:

产生与接地电位不同的保护电位,包括使用以接地电位为参考的AC电压源在保护电位和接地电位之间产生AC电压差;

利用在电气上以保护电位为参考的第一电子系统电容式检测一个或多个对象,其中第一电子系统被包括在包括衬底的芯片中;

接收来自AC电压源的AC电压以及产生用于以保护电位为参考的第一电子系统的供电

电压;以及

经由包括电容器的解耦电路将第一电子系统耦合到与第一电子系统不同的第二电子系统,其中,第二电子系统被包括在所述芯片中并且在电气上以接地电位为参考,所述耦合维持保护电位和接地电位之间的隔离。

12. 如权利要求11所述的方法,还包括利用保持在保护电位的屏蔽平面至少部分地屏蔽第一电子系统。

13. 如权利要求12所述的方法,还包括利用所述屏蔽平面至少部分地屏蔽第二电子系统。

14. 如权利要求11所述的方法,其中第一电子系统包括获取电路,第二电子系统包括处理电路。

15. 如权利要求11所述的方法,还包括:

利用以保护电位为参考的振荡器电路产生激励信号;以及

利用以接地电位为参考的缓冲器电路接收激励信号和产生保护电位。

16. 如权利要求11所述的方法,还包括在主模式下操作多个第二电子系统中的一个,在从模式下操作第一电子系统。

17. 如权利要求16所述的方法,还包括从在主模式下操作的第二电子系统将输出发送到在从模式下操作的第一电子系统。

## 包括浮桥的用于电容式测量的集成电路

[0001] 本申请是申请日为2012年6月8日、名称为“包括浮桥的用于电容式测量的集成电路”、申请号为201280029578.9的发明专利申请的分案申请。

### 技术领域

[0002] 本发明涉及一种包括浮桥(floating bridge)的用于电容式测量的电子设备，其能够以集成电路的形式产生。

[0003] 本发明的领域更具体地但非限制性是用于测量和检测的电子设备。

### 背景技术

[0004] 便携式系统、诸如电话、智能电话、平板电脑、计算机等的触摸或非接触界面常常基于电容式测量电容式测量技术。

[0005] 根据这些技术，屏幕或设备提供有电极，其可选地是透明的。当对象、诸如手指接近这些电极时，在代表电接地的此对象与电极之间产生电容型的电耦合。因此该电容性耦合的测量允许对对象进行定位。

[0006] 朝向非接触界面的发展要求开发具有非常高的灵敏度的电容式检测系统，对于该非接触界面而言必须在与界面表面相距相对长的距离处检测并定位对象。

[0007] 最初针对非常高准确度的测量应用而开发的电容式“浮桥”测量技术经证明特别适合于此类应用。

[0008] 例如在Rozière的文献FR 2 756 048中描述了这种技术。其使得可以消除在更常规的电容式测量方法中在电极与其环境之间出现的所有寄生电容。对于根据定义未知且波动的这些寄生电容被叠加于将在对象与电极之间测量的电容上来说，其显著地限制了根据常规方法进行的测量的灵敏度和准确度。

[0009] 为此，使得包括检测电极和最为灵敏的测量电子装置的第一级的一部分电子装置浮置。例如使用连接接地和保护电位的振荡器来使得其参考电位或保护电位相对于系统的一般接地而振荡。因此，灵敏级的电子装置的任何部分都未处于接地，并且其不能与接产地产生寄生电容。

[0010] 为了能够在便携式设备、诸如电话或平板电脑中实施电容式测量技术，必须能够以具有小的总尺寸和低功率消耗的集成电路的形式产生关联的电子装置。

[0011] 已知诸如在FR 2 756 048中公开的以具有分立部件的印刷或混合电路的形式产生测量系统。另一方面，在FR 2 756 048中描述的实施例不能以单个集成电路的形式产生。

[0012] 一个问题源自于这样的事实，即电子装置包括两个不同部分，具有不同的参考电位且相对于彼此而振荡。此产生以下约束：

[0013] -那两个部分不应引起互相干扰，并且特别地，接地元件不应与浮置元件相干扰；

[0014] -浮置和接地部分之间的信号传输要求解耦部件，诸如扼流线圈或光学耦合器，其不能被集成；

[0015] -必须生成浮置部分的电源或从接地电源传输，这再次地要求难以集成的解耦部

件(扼流线圈、DC/DC转换器)。

[0016] 已知Rozière的文献FR 2 893 711,其公开了一种通过基于集成电路的浮桥的用于电容式测量的设备。然而,在这种情况下,在浮置模式下被供电、或者换言之其处于保护电位的是整个集成电路。因此必须添加外部部件以便产生与以接地为参考的电子装置的对接,其因此也在测量集成电路的外部。此外,印刷电路的至少其上固定有外部部件的部分也必须以保护电位为参考。

[0017] 更一般地,当使用用于使寄生电容最小化或将其消除的保护装置来实现电容式电子装置时,必须将保护区域与能够产生杂散电容的电子装置的其余部分分离。在所有情况下,此约束引起集成困难。

[0018] 本发明的目的是提出一种包括保护装置的用于电容式测量的电子设备,其能够用以接地为参考的单个集成电路的形式产生,从而能够被容易地插入常规电子路上。

## 发明内容

[0019] 用一种电容式测量设备来达到此目的,其包括:

[0020] -第一电子系统,被电参考至保护电位,并且能够连接到电容性电极,

[0021] -第二电子系统,被电参考至接地电位,并且能够通过连接装置而连接到所述第一电子系统,以及

[0022] -激励装置,分别连接到所述保护和接地电位,从而在这些电位之间施加AC电压差,

[0023] 其特征在于其此外包括以接地为参考的集成电路,所述集成电路包括:

[0024] -第一安装区域,以保护电位为参考,并且在其中实现了所述第一电子系统,以及

[0025] -第二安装区域,以接地电位为参考,并且在其中实现了所述第二电子系统。

[0026] 当然必须以这样的意义来解释术语“连接”,即被相互连接的部件能够通过直接电连接直接地连接、或者经由附加电气或电子部件来连接。

[0027] 保护和接地电位的定义当然是非限制性的,接地电位还可以相对于诸如地球的另一参考是浮置或可变的。

[0028] 接地电位能够例如对应于根据本发明的设备被连接到的电子装置的参考电位和/或对集成电路进行供电的电压源的参考电位

[0029] 根据本发明的有利方面,根据本发明的设备的以保护电位为参考的部分能够本质上被包括在集成电路中,其本身以电压源为参考并由电压源供电,该电压源以接地电位为参考。因此,一般地大大促进了其到电子系统中的集成,并且使与以保护电位为参考的电子部分的存在有关系的约束最小化。

[0030] 根据本发明的设备此外能够包括:

[0031] -被电连接到保护电位的屏蔽表面,并布置成从而至少部分地且至少沿着一侧覆盖第一安装区域的表面;

[0032] -被电连接至保护电位的屏蔽表面,并布置成从而至少部分地且至少沿着一侧覆盖第一和第二安装区域的表面。

[0033] 屏蔽区域能够在集成电路的封装内部。其能够在实现包含于集成电路封装中的电子功能(芯片)的部件的衬底级别制造。其还能够在集成电路的封装外并在此封装被焊接到

其上面的印刷电路的级别制造。

[0034] 此屏蔽表面是用于集成电路的适当运行的重要元件。事实上，必须保护以保护电位为参考的第一电子系统或至少其最灵敏部分免于干扰，所述干扰诸如能够与以接地电位（其也是电容性电极必须检测的目标电位）为参考的元件形成的寄生电容。因此，在现有技术的设备中，始终以与以接地为参考的部件分开的不同部件的形式产生以保护电位为参考的部分。

[0035] 相反地，在本发明的范围内已经认识到用以保护电位为参考的屏蔽件来屏蔽集成电路有效地保护以保护电位为参考的第一电子系统免受其周围环境中的干扰，并且并未显著地干扰以接地为参考的第二电子系统，其本质上不包括非常灵敏的数字部件。

[0036] 根据实施例，集成电路能够包括：

[0037] -集成在同一封装中的两个不同芯片，该两个芯片分别包括第一和第二安装区域，或者

[0038] -在同一衬底上包括第一和第二安装区域的芯片。

[0039] 该集成电路能够包括通过实施以下技术中的至少一个而产生的至少一个芯片：CMOS、绝缘体上硅(SOI)。

[0040] SOI(绝缘体上硅)技术使得可以使用硅氧化物的电绝缘层产生例如处于不同参考电位的电路的各部分之间的电隔离。

[0041] 在CMOS技术的范围内，只能通过使用在相反方向上极化（其具有阻断P-N结的效果）的P掺杂衬底的部分与N掺杂衬底的部分之间产生的耗尽层来获得电隔离。因此，使用这种技术的发明的实现是常见的且具有相对适中的成本，其引起特定约束，并且要求找到允许与该隔离约束相容的浮置和非浮置电位的分布的架构。

[0042] 能够通过实施多阱CMOS技术产生该芯片。

[0043] 特别地能够通过实施三阱CMOS技术产生该芯片，包括：

[0044] -P掺杂衬底，连接到保护电位，

[0045] -第一N掺杂阱，

[0046] -两个N掺杂和P掺杂阱，包括在第一阱中，并且每个对应于第一和第二安装区域中的一个。

[0047] 能够通过实施以下技术中的至少一个产生集成电路：

[0048] -将一个或更多个并置芯片组装在封装中，

[0049] -芯片的3D堆叠（“芯片级封装”），

[0050] -芯片的直接连接（“倒装芯片”）。

[0051] 芯片的3D堆叠例如对应于称为“芯片级封装”的技术，其中将芯片叠加或堆叠。然后能够例如通过直通连接（“TSV、硅通孔”）来将其连接。

[0052] 在“倒装芯片”直接连接技术中，例如使用凸块矩阵，将芯片或各组芯片直接放置在印刷电路上或者直接焊接到那里。

[0053] 集成电路此外能够包括(i)第一连接元件，使得可以将第一电子系统连接到电容性电极和/或处于保护电位的元件，(ii)第二连接元件，使得可以一方面将第二电子系统连接到外部处理电子装置，并且另一方面对所述第二电子系统进行供电，该第一和第二连接元件被在保护电位下连接的至少一个连接元件分离。

[0054] 一般地,必须将到集成电路的内部连接以及此集成电路与外面之间的外部连接布置成避免以保护电位为参考的部分的灵敏元件与以接地电位为参考的元件之间的电容性耦合。为了做到这一点,能够适当地插入到保护电位的连接,并且使连接的布置和几何结构最优化。

[0055] 分别以保护电位和接地电位为参考的各部分本质上被合并到单个集成电路中的事实是本发明的优点,因为其允许集成电路设计期间的耦合的优化,这独立于其后续使用的环境。

[0056] 集成电路能够此外包括用于产生以保护电位为参考的至少一个电源的装置。

[0057] 因此,不必在集成电路外面产生以保护电位为参考的电源,并且能够本质上使电子装置的处于保护电位的部分局限于集成电路。

[0058] 处于接地电位的部分与处于保护电位的部分之间的DC电源的传输引起特定问题,因为其要求在低频下操作的连接装置,诸如电感器,这就空间要求而言是非常不利的。

[0059] 根据实施例,所述集成电路能够此外包括:

[0060] -AC源电压源,以接地电位为参考,其电路经由激励装置而闭合,以及

[0061] -整流和滤波装置,分别在其输入端处连接到所述AC源电压源和保护电位,从而通过AC源电压源的端子处的电压的整流而在输出端处生成以所述保护电位为参考的源电压。

[0062] 这样,因此在电力可用的一侧,使用以接地电位为参考的AC源电压源。

[0063] AC源电压源的电路经由激励装置而闭合,或者换言之,此电源的电流流过这些激励装置。

[0064] 被用于产生电源电压和因此的以参考电位为参考的电力的AC源电压源的电路因此能够在保护电位与接地电位之间闭合,而没有附加连接装置且未使两个参考电位短路。

[0065] 此配置是可能的,因为无论激励装置的配置什么,其基本上表现为完美的电压发生器,也称为戴维宁等效发生器。此发生器在接地和保护电位之间施加AC电压差,其使得可以保持其相对于彼此浮置,同时针对电源电流呈现出非常低的阻抗。此结果不能在不存在激励装置的情况下获得。

[0066] 能够将整流和滤波装置设计成仅包括能够被集成的部件,诸如电容器和无源开关装置(二极管等)或有源开关装置("开关"或基于晶体管的开关等)。

[0067] 其能够以任何相容形式产生,诸如,例如根据具有二极管的单整流器原理或Schenkel倍压整流器。

[0068] 根据实施例,根据本发明的设备的激励装置能够此外包括以下各组部件中的一个:

[0069] -电压跟随器缓冲器,以接地电位为参考且被以保护电位为参考的振荡器激励。

[0070] -振荡器,以接地电位为参考。

[0071] 在两种情况下,到激励装置的电力由以接地电位为参考的电源提供。缓冲器的实施使得可以使以保护电位为参考的振荡器可用,其具有低消耗且同样地可用于电容式测量期间的第一电子系统中的激励和/或同步。

[0072] 根据实施例,连接装置能够包括串联的电容器。

[0073] 事实上,为了在处于不同参考电位的各部分之间传输数字或模拟信号,根据非常适合于以集成电路的形式实施的技术,必须提供解耦装置。在现有技术、诸如在FR 2 893

711中所述的那些的设备中,常常使用不能被集成的电感。

[0074] 根据实施例,第一电子系统能够包括扫描装置,使得可以连续地对电容性电极进行轮询,以便测量电容。

[0075] 因此能够用单个数据获取系统来测量许多电极。

[0076] 根据本发明的设备能够此外包括与类似设备的通信装置,允许其在主或从属模式下操作,据此:

[0077] -配置在主模式下的设备的激励装置在已配置在从属模式下的设备的保护和接地电位之间施加类似AC电压差,以及

[0078] -配置在从属模式下的设备的激励装置被至少部分地无效。

[0079] 因此可以通过使用以主从模式(或同步地)配置的多个相同或类似集成电路来对比用单个集成电路能够实施的数目更大的数目的电极进行寻址。此外,电极全部以同一保护电位为参考,这对于测量质量而言是必不可少的。

[0080] 根据另一方面,提出了一种对象位置的检测和/或测量的系统,包括多个电容性电极和根据本发明的至少一个电容性测量设备。

[0081] 当实施多个电容性测量设备时,其能够以主从模式来配置。

[0082] 该系统能够包括布置在显示屏上的透明电极。

[0083] 根据本发明的设备能够在所有类型的电容式测量应用中实施或使用。

[0084] 根据另一方面,在以下应用中的任何一个中提出了根据本发明的至少一个设备的使用。

[0085] -人机触摸和/或非接触界面,

[0086] -尺寸测量系统,

[0087] -防碰撞系统,

[0088] -接近性检测器。

[0089] 根据本发明的设备因此能够例如被用于产生紧凑式电容式测量系统,或者能够在医学成像系统中用于驱动用于病人位置的电容式检测的天线。

## 附图说明

[0090] 在仔细阅读绝不是限制性的实施例的详细描述和附图后,本发明的其他优点和特性将变得明显,在所述附图中:

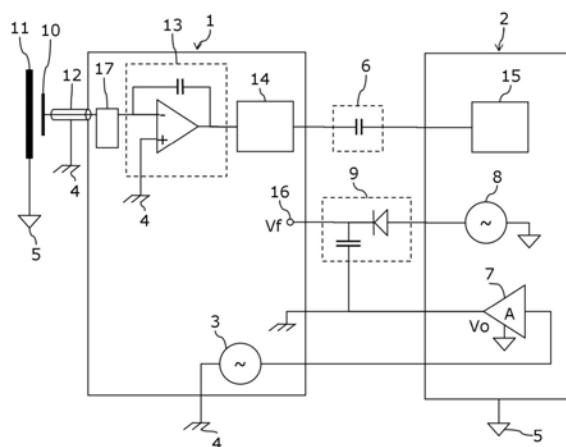

[0091] -图1示出了根据本发明的电容式测量设备的一般电气图,

[0092] -图2示出了在同一封装中包括两个单独芯片的集成电路形式的电容式测量设备的实施例,

[0093] -图3示出了以在同一封装中包括两个单独芯片的集成电路形式产生的电容式测量设备的内部布置,

[0094] -图4示出了包括单个芯片的集成电路形式的电容式测量设备的实施例,

[0095] -图5示出了以包括单个芯片的集成电路的形式产生的电容式测量设备的内部布置,

[0096] -图6示出了CMOS技术中的根据本发明的设备的实施例示例,

[0097] -图7示出了根据CMOS技术的本发明的设备的实施例示例中的电位水平的分布,

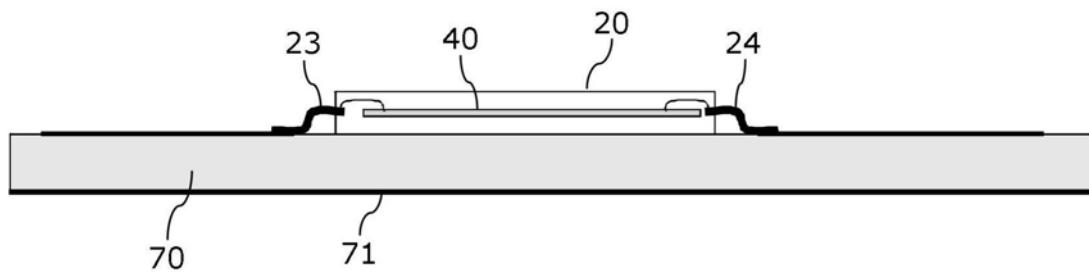

[0098] -图8示出了以集成电路形式产生的根据本发明的设备的安装。

## 具体实施方式

[0099] 参考图1,首先描述根据本发明的电容式测量设备的一般电气图。

[0100] 根据本发明的电容式测量设备基于在文献FR2 756 048中描述的浮桥配置。图1是其非常概略的图示,应理解的是在FR 2 756 048中所述的不同测量配置在本发明的范围内可适用。

[0101] 此类电容式测量系统使得可以测量处于连接到接地电位5的电位的目标11与至少一个测量电极10之间的电容信息的项目。

[0102] 电子装置包括以相对于接地电位5振荡的保护电位4为参考的第一电子获取系统1以及以接地电位5为参考的第二电子处理(或传输)系统2。当然,在没有任何限制性效果的情况下,为了本公开的明了起见而选择电子系统的命名。电子获取系统1能够特别地包括信号处理装置,包括数字的。电子处理系统2能够局限于与电子装置的其余部分的接口功能。

[0103] 该设备此外包括分别连接到保护4和接地5电位的激励(excitation)装置3、7。这些激励装置执行在这些电位4、5之间施加AC电压差、因此促使参考电位中的一个相对于另一个“浮置”的功能。

[0104] 在FR 2 756 048中,这些激励装置本质上包括以保护电位4为参考的振荡器3,并且包括连接到接地电位5的出口(outlet)。

[0105] 从产生激励电压的观点出发,振荡器3能够同样地以保护电位4或接地电位5为参考。然而,在其也被用于特别地在电极10上产生激励信号的情况下,其必须优选地以保护电位4为参考。

[0106] 在FR 2 756 048中实施的振荡器3必须消耗不可忽略的电力量以便保持参考电位4、5之间的AC电位差。现在,如先前所解释的,电力在以接地电位5为参考的一侧更容易可用。

[0107] 为此,在根据本发明的设备中,激励装置不同地分布。其包括以保护电位4为参考的振荡器3。振荡器产生能够在电子获取系统1中用作激励或时钟信号的AC信号。此信号能够根据应用而具有任何形状(例如,正弦、正方形或三角形)。

[0108] 根据本发明的设备还包括以接地电位5为参考的缓冲器7。此缓冲器7包括以运算放大器形式布置的基于晶体管而产生的放大器或电压跟随器(具有单位增益)。振荡器3的输出端被连接到缓冲器7的输入端。缓冲器7的输出端被连接到保护电位4。

[0109] 缓冲器7在输出端处发出激励信号 $V_o$ 。由于其内部电参考(或其电源的电参考)是接地电位5,所以其充当发出信号 $V_o$ 或者换言之在接地5和保护电位4之间产生AC电压差 $V_o$ 的电压源。

[0110] 通过以这种方式操作,获得以保护电位4为参考的振荡器3的优点,但是其电消耗被最小化,因为激励保护电位4所需的大部分的电力是由缓冲器7提供的,缓冲器7以接地电位5为参考并因此由处于接地电位5的部分进行供电。

[0111] 电子获取系统1完全以保护电位4为参考,从而避免了在测量电极10或其他灵敏部分与接地电位5之间出现寄生电容,目标或所检测对象11被连接到接地电位5。同样地,保护电极12保护测量电极10。与后者处于同一电位,其也避免了寄生电容的出现。

[0112] 测量电极10连接到电荷放大器13,其使得可以测量其电容。图1示出了电荷放大器13的非常概略的表示,其能够以所有形式产生,包括在FR2 756 048中所述的那些。电荷放大器13特别地能够使用其振幅能够被调制的振荡信号3以闭环系统的形式产生,以便用零点法来测量电容或倒电容(inverse capacitance)。

[0113] 根据应用,电子获取系统1能够包括处理信号14、以便例如发出表示测量电极10与目标11之间的距离的信号的步骤。

[0114] 该系统一般地被设计成对所有几何结构的多个电极10进行“读取”。因此其包括扫描仪17,该扫描仪17被插在电极10与电荷放大器13之间,并且使得可以连续地测量这些电极10的电容。此扫描仪17能够采取以保护电位4为参考且由电子控制单元控制的一系列模拟开关的形式。

[0115] 根据本发明的设备使得可以特别地产生用于诸如移动电话(智能电话)、平板电脑或计算机的设备的触摸或非接触界面。电极10能够是透明电极,例如由ITO(锡掺杂氧化铟)制成,沉积在显示屏或触控板上。其然后被用来检测命令对象11诸如手指的接近和/或接触。

[0116] 根据本发明的设备还包括电参考至接地电位5的电子处理系统2。此电子处理系统2还确保根据本发明的设备与电子装置的其余部分(当然不包括电极10)之间的接口功能。这使得可以本质上以集成电路的形式产生根据本发明的设备,该集成电路全局地以接地电位5为参考,并且由以接地电位5为参考的电源进行供电。

[0117] 电子处理系统2通过连接装置6而连接到电子获取系统1,连接装置6使得可以发送数字或模拟信号。这些连接装置6包括提供有解耦装置的电连接,从而至少在一定频率范围内确保接地和保护电位之间的隔离。在本发明的范围内,优选地使用电容器作为解耦装置,因为其能够被容易地集成并允许至少高频下传输信号(例如,数字的)。

[0118] 根据本发明的设备能够与根据本发明的其他设备或其他兼容设备同步,以便控制比单个设备可实现的更大数目的电极10。

[0119] 为了做到这一点,分别根据主或从属模式来配置设备,例如使用内部逻辑功能,从而:

[0120] -连接所有设备的保护电位4,

[0121] -使配置在从属模式下的设备的振荡器3和缓冲器7无效,

[0122] -将配置在主模式下的设备的振荡器3的输出和缓冲器7的输出传送至配置在从属模式下的设备。

[0123] 根据变体,如果不同设备的缓冲器7的增益是足够均匀的,则能够使用以下配置:

[0124] -使配置在从属模式下的设备的振荡器3无效,

[0125] -将配置在主模式下的设备的振荡器3的输出传送至配置在从属模式下的设备并将其缓冲器7用于每个从属设备。

[0126] 为了本质上以在全局以接地电位5为参考的集成电路的形式产生根据本发明的设备,必须在还在此设备中产生以保护电位4为参考的电源。此外,必须用能够容易地集成的部件产生这些电源。

[0127] 在图1中所示的所述实施例中,根据本发明的设备因此包括以保护电位4为参考的至少一个电源Vf,其包括以接地电位5为参考的AC源电压源8,以及整流和滤波装置9。

[0128] 整流和滤波装置9在其输入端处分别地连接到AC源电压源8和保护电位4。根据绝不是限制性的图1中的实施的示例，整流二极管连接到AC源电压源8，滤波电容器并联于以接地电位4为参考的电源Vf的输出端16。由于部件的输入阻抗，此滤波电容器还能够是等效电容器。

[0129] 为了使此类电路图工作，电流必须具有到AC源电压源8的返回路径。在根据本发明的设备中，通过缓冲器7的输出端而提供此返回路径。

[0130] 事实上由振荡器3控制的缓冲器7允许经由保护电位4与接地电位5之间的连接的用于供电电路的返回路径，而并不在振荡器3的激励信号频率下使这些参考电位短路。如先前所解释的，这种效果是由于由振荡器3控制的缓冲器7的戴维宁等效发生器工作而获得的，其在具有低阻抗的同时在保护4和接地5电位之间施加激励信号。

[0131] 电源Vf特别地能够用来对振荡器3以及例如电荷放大器13进行供电。

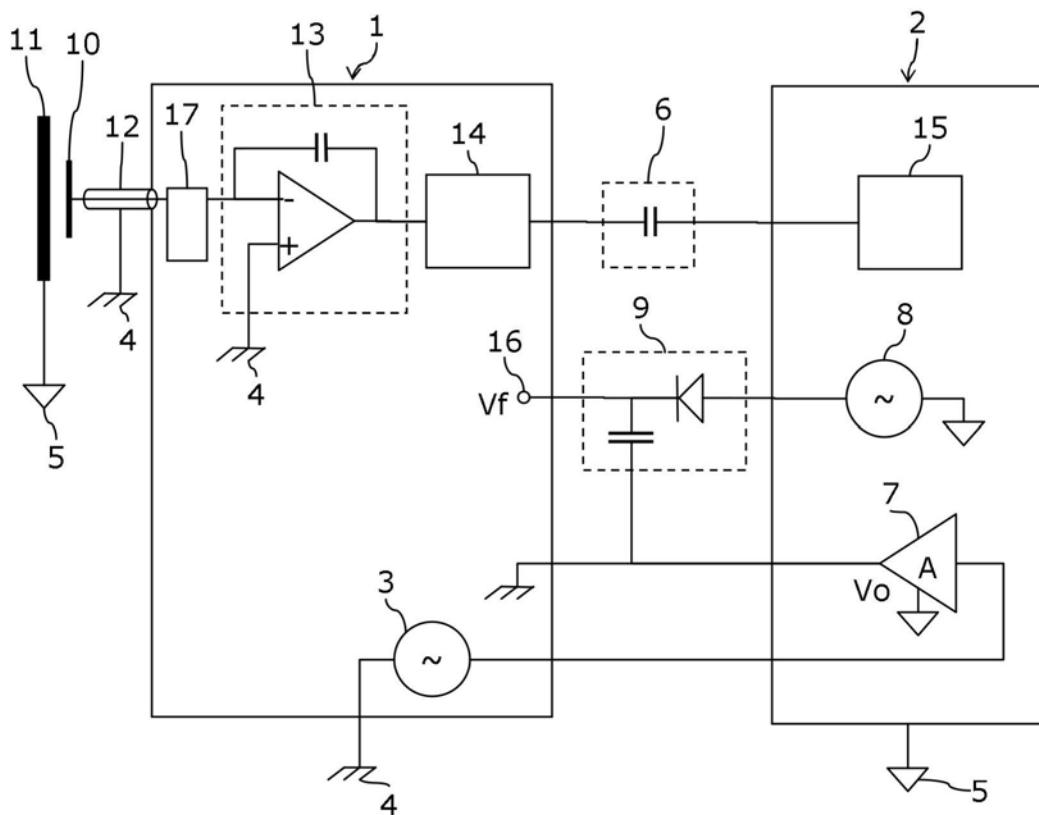

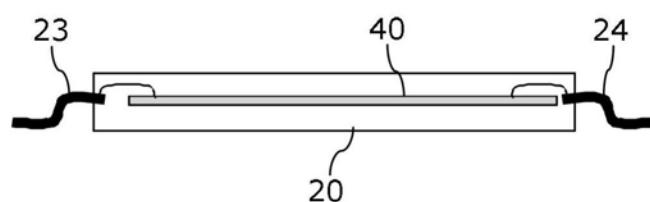

[0132] 参考图2，根据第一实施例，根据本发明的设备包括集成电路20，其本身包括集成在同一封装中的两个不同芯片21、22。

[0133] 在不失一般性的情况下，集成电路20是SMT (表面安装技术) 类型的，引脚23、24能够被焊接到印刷电路上。

[0134] 以保护电位4为参考的电子获取系统1是以第一安装区域或者第一芯片21中的获取区域38的形式实施的，并且以接地电位5为参考的电子处理系统2是以第二安装区域或第二芯片22中的处理区域39的形式实施的。

[0135] 本实施例的优点是显著地简化芯片21、22的产生，芯片21、22每个仅包括单个参考电位。

[0136] 芯片21、22被根据标准“键合(bonding)”技术的内部连接导线25连接。

[0137] 以保护电位4为参考的芯片21通过集成电路20的第一组引脚23而连接到测量电极10和以保护电位为参考的其他元件。

[0138] 以接地电位5为参考的芯片22通过集成电路20的第二组引脚24而连接到电子装置的其他元件。

[0139] 引脚23、24和内部连接导线25被布置成使得与以保护电位4为参考的灵敏部分的连接且特别是与电极10的连接仅仅被以保护电位4为参考的连接围绕。

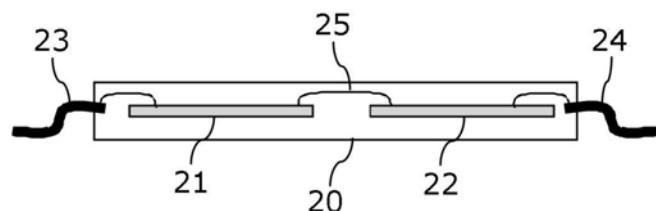

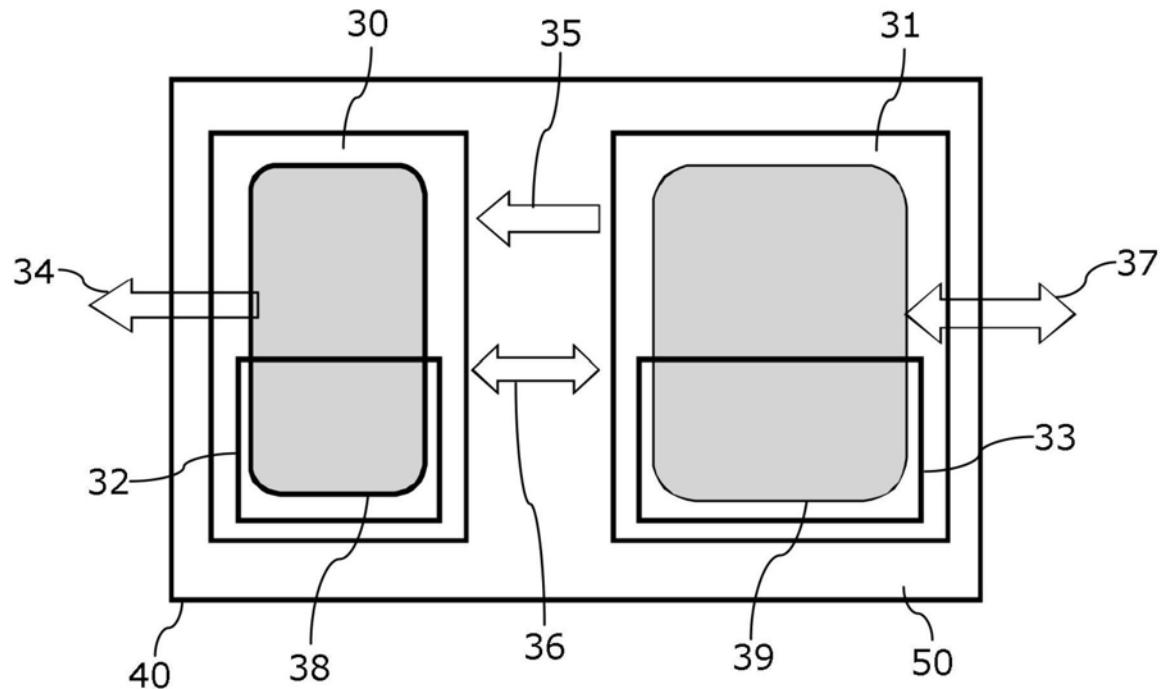

[0140] 图3示出了具有用CMOS技术产生的ASIC(专用集成电路)形式的单独芯片21、22的实施例的安装示例。

[0141] 芯片21特别地包括两个电源平面30、32以及其中实施电子获取系统1的获取区域38，所述两个电源平面30、32的衬底30被参考或连接至保护电位4。

[0142] 芯片22特别地包括两个电源平面31、33以及在其中实施了电子处理系统2的处理区域39，两个电源平面31、33包括被参考或连接至接地电位5的衬底31。

[0143] 芯片21、22之间的连接29包括到获取区域38的电源传输35和获取35与处理39区域之间的数据传输36。

[0144] 根据变体，能够用FPGA(现场可编程门阵列)逻辑电路产生包括电子处理系统2的芯片22。

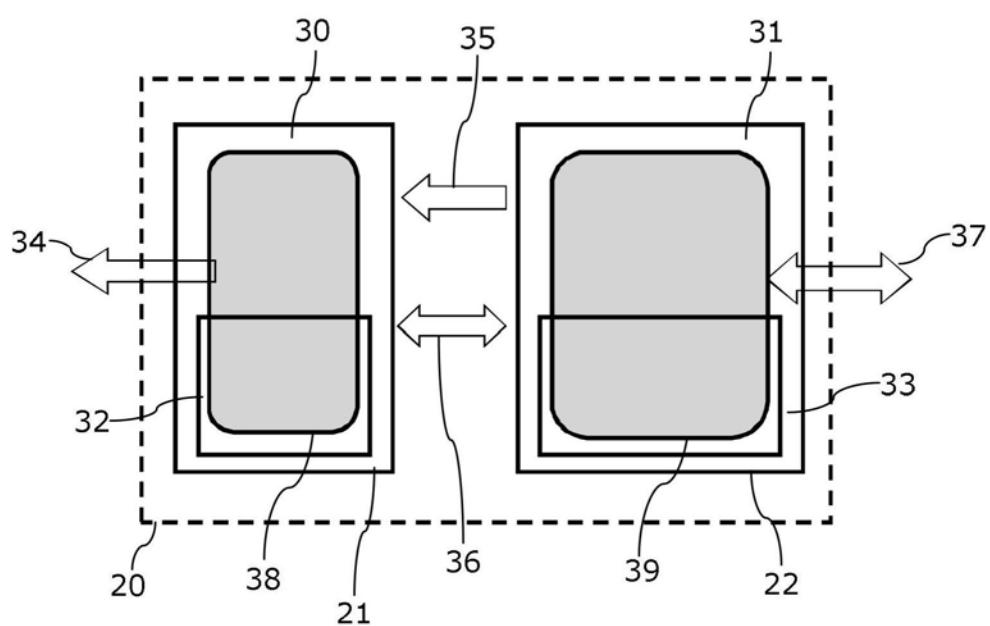

[0145] 参考图4，根据第二实施例，根据本发明的设备包括集成电路20，其包括单个芯片40。

[0146] 在不失一般性的情况下,集成电路20是SMT(表面安装技术)类型的,引脚23、24能够被焊接到印刷电路上。

[0147] 引脚23、24被布置成使得到以保护电位4为参考的灵敏部分的连接且特别是与电极10的连接仅仅被以保护电位4为参考的连接围绕。

[0148] 图5示出了具有用CMOS技术产生的ASIC(专用集成电路)或集成电路形式的芯片40的该实施例的安装示例。

[0149] 以保护电位4为参考的获取区域38以及以接地电位5为参考的处理区域39在同一芯片40中产生。

[0150] 芯片40的衬底50被连接到保护电位。此配置具有产生保护平面的优点,该保护平面覆盖全部的获取区域38和参考区域39,并且允许对寄生电容的灵敏度的显著降低。

[0151] 获取区域38被参考至或连接至保护电位4的电源平面30、32围绕。

[0152] 处理区域39被参考至或连接至接地电位5的电源平面31、33围绕。

[0153] 到获取区域38的电源传输35和获取35与处理39区域之间的数据传输36在芯片40上产生。

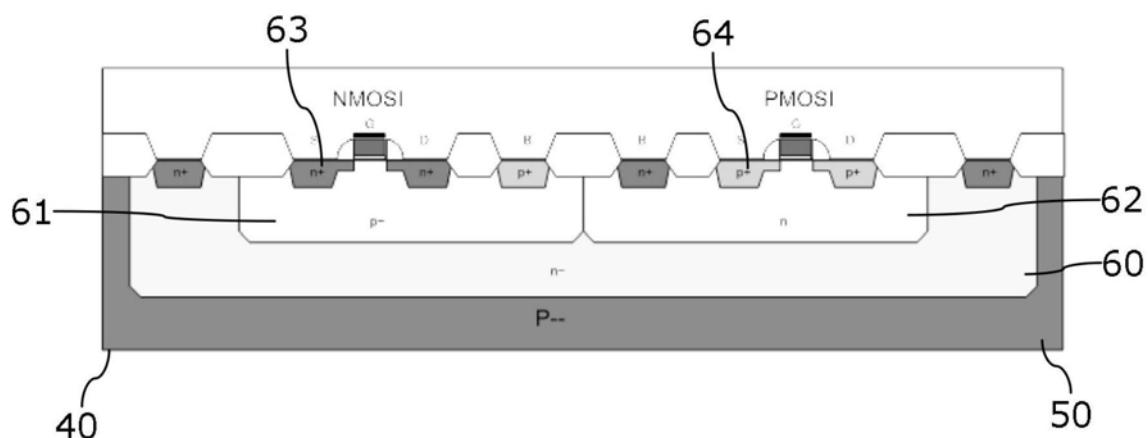

[0154] 参考图6,芯片40是用根据三阱技术的CMOS技术产生的。其包括:

[0155] -第一P掺杂阱50,对应于衬底50,其被连接在保护电位4处。

[0156] -第二N掺杂阱60,

[0157] -第三P掺杂阱61和第三N掺杂阱62,包括在第二阱60中并包括获取38和参考39区域的部件63、64。

[0158] 在P-N结的反向极化下能够获得组件的正确操作所需的电隔离以便将其阻断。为了做到这一点,必须遵守不同部分的参考电压4、5与电源电压之间的特定关系。

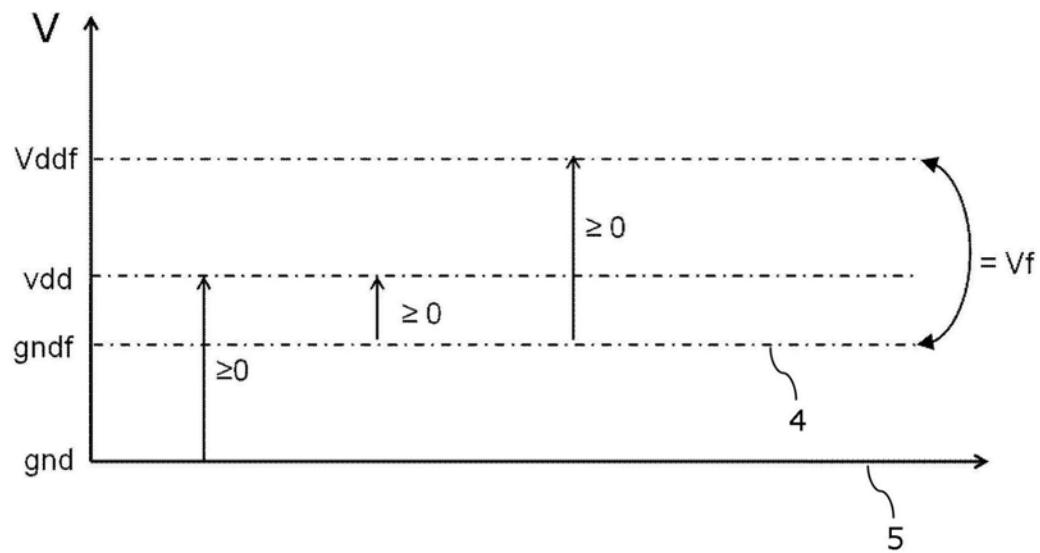

[0159] 图7示出了要考虑的电压水平。

[0160] 定义了以下各项:gnd,接地参考电位5;vdd,以接地5为参考的电源的电压水平;gndf,保护参考电位4;以及vddf,以保护电位4为参考的电源的电压水平。

[0161] 根据图7,施加以下条件:

[0162] (i)  $vdd \geq gnd$ ,

[0163] (ii) 在任何时刻,  $vdd \geq gndf$ ,因为gndf是相对于vdd振荡的电位,

[0164] (iii)  $vddf \geq gndf$ ,已知  $vddf - gndf = Vf$ ,以保护电位4为参考的电源电压。

[0165] 基于这些条件,能够如下分布阱的电位:

[0166] -P掺杂衬底50处于电位gndf,即处于保护电位4,

[0167] -第二N掺杂阱60和第三N掺杂阱62处于电位vddg,阱62的晶体管64处于电位gnd,这使得可以作为默认而使结被阻断,

[0168] -第三P掺杂阱61处于电位gndf,阱61的晶体管63处于电位vddf,这使得可以作为默认而使结被阻断。

[0169] 在此配置中,在阱61中实施以保护电位4为参考的获取区域38,并且在阱62中实施以接地电位5为参考的处理区域39。

[0170] 还能够用以下方式来分布电位,其基本上是等效的:

[0171] -P掺杂衬底50处于电位gndf,即处于保护电位4,

[0172] -第二N掺杂阱60和第三N掺杂阱62处于电位vddf,阱62的晶体管64处于电位gndf,

这使得可以作为默认而使结被阻断，

[0173] -第三P掺杂阱61处于电位gnd, 阵61的晶体管63处于电位vdd, 这使得可以作为默认而使结被阻断。

[0174] 在此配置中, 在阱62中实施以保护电位4为参考的获取区域38, 并且在阱61中实施以接地电位5为参考的处理区域39。

[0175] 参考图8, 能够有利地用处于保护电位4的屏蔽平面71来完成根据本发明的设备, 屏蔽平面71被放置在例如与印刷电路70的焊接集成电路的面相反的面上。

[0176] 根据变化实施方案,

[0177] -集成电路20能够包括所有类型的情况下, 包括例如具有与布置在各侧面的引脚23、24的侧面连接的封装或者具有与在封装下面布置成矩阵的引脚的矩阵连接的封装;

[0178] -芯片21、22或40能够通过导线或通过焊球(“球接合”)而连接到封装,

[0179] -能够根据“倒装芯片”技术来产生集成电路20, 根据该“倒装芯片”技术, 芯片在没有中间封装的情况下被直接连接到印刷电路,

[0180] -芯片20、21能够用3D组装技术(“芯片级封装”)来组装。

[0181] 当然, 本发明不限于刚刚已描述的实施例, 并且在不超过本发明的范围的情况下能够对这些示例进行许多调整。

图1

图2

图3

图4

图5

图6

图7

图8