## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

G11C 16/34 (2006.01) G06F 12/00 (2016.01) **G11C 16/10** (2006.01)

(21) 출원번호 10-2011-0133035

2011년12월12일 (22) 출원일자 심사청구일자 2016년11월17일

(65) 공개번호 10-2013-0066277 (43) 공개일자 2013년06월20일

(56) 선행기술조사문헌 KR1020100042885 A KR1020070026804 A US9239779 B1

US20130238837 A1

(24) 등록일자

(45) 공고일자

(11) 등록번호

2018년01월08일 (73) 특허권자

삼성전자주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

2018년01월15일

10-1818176

(72) 발명자

조숭덕

서울특별시 강남구 광평로51길 49 110동 622호 ( 수서동,주공아파트)

심호준

경기도 용인시 기흥구 흥덕2로118번길 25 806동 903호 (영덕동,흥덕마을8단지한국아델리움아파트)

정기조

경기도 과천시 희망4길 37-9 (중앙동)

(74) 대리인

특허법인 고려

전체 청구항 수 : 총 10 항

심사관 : 한선경

### (54) 발명의 명칭 메모리 시스템 및 그것의 동작 방법

#### (57) 요 약

여기에 개시되는 메모리 시스템은 데이터 정보를 저장하도록 구성된 불 휘발성 메모리 장치와; 그리고 상기 불 휘발성 메모리 장치를 제어하도록 구성된 메모리 제어기를 포함하며, 상기 메모리 제어기는 외부 요청과 무관하 게 내부적으로 요청된 프로그램 동작의 긴급 정도에 따라 가변되는 프로그램 속도 정보를 포함하는 프로그램 명 령 시퀀스를 상기 불 휘발성 메모리 장치로 전송하는 메모리 시스템.

### 대 표 도 - 도5

### 명 세 서

### 청구범위

### 청구항 1

데이터 정보를 저장하도록 구성된 불 휘발성 메모리 장치와; 그리고

상기 불 휘발성 메모리 장치를 제어하도록 구성된 메모리 제어기를 포함하며,

상기 메모리 제어기는 내부적으로 요청된 프로그램 동작의 긴급 정도에 따라 가변되는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스를 상기 불 휘발성 메모리 장치로 전송하는 메모리 시스템.

#### 청구항 2

제 1 항에 있어서,

상기 내부적으로 요청된 프로그램 동작은 외부 요청과 무관하며, 상기 메모리 제어기의 배경 동작, 서든 파워-오프와 관련된 동작, 또는 가비지 컬렉션을 포함하는 메모리 시스템.

#### 청구항 3

제 2 항에 있어서,

상기 배경 동작과 관련된 프로그램 동작을 수행하는 데 걸리는 프로그램 시간은 외부 요청에 따라 수행되는 프로그램 동작의 프로그램 시간 보다 긴 메모리 시스템.

#### 청구항 4

제 3 항에 있어서,

상기 서든 파워-오프와 관련된 프로그램 동작을 수행하는 데 걸리는 프로그램 시간은 상기 외부 요청에 따라 수행되는 프로그램 동작의 프로그램 시간 보다 짧은 메모리 시스템.

### 청구항 5

제 4 항에 있어서,

상기 프로그램 명령 시퀀스는 제 1 명령, 어드레스, 그리고 제 2 명령을 포함하며, 상기 제 2 명령의 값은 상기 외부 요청에 따라 수행되는 프로그램 동작과 상기 내부적으로 요청된 프로그램 동작들에 따라 다르게 결정되는 메모리 시스템.

### 청구항 6

제 4 항에 있어서,

상기 서든 파워-오프와 관련된 프로그램 동작을 통해 프로그램된 데이터는 메타 데이터인 메모리 시스템.

#### 청구항 7

제 6 항에 있어서,

상기 서든 파워-오프와 관련된 프로그램 동작을 통해 프로그램된 데이터는 상기 외부 요청에 따라 수행되는 프로그램 동작을 이용하여 재프로그램되는 메모리 시스템.

#### 청구항 8

제 1 항에 있어서,

상기 불 휘발성 메모리 장치는

프로그램 전압을 발생하는 전압 발생기와; 그리고

상기 전압 발생기를 제어하도록 구성된 제어 로직을 포함하며,

상기 제어 로직은 상기 프로그램 명령 시퀀스에 포함된 프로그램 속도 정보에 의거하여 상기 프로그램 전압의 시작 레벨 또는 상기 프로그램 전압의 증가분을 결정하는 메모리 시스템.

#### 청구항 9

제 1 항에 있어서,

상기 메모리 제어기와 상기 불 휘발성 메모리 장치는 메모리 카드 및 반도체 드라이브 중 하나를 구성하는 메모리 시스템.

### 청구항 10

불 휘발성 메모리 장치를 포함하는 메모리 시스템의 동작 방법에 있어서:

프로그램 동작이 외부 요청없이 내부적으로 요청되었는 지의 여부를 판별하고,

판별 결과에 따라 상기 요청된 프로그램 동작의 긴급 정도에 따라 가변되는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스를 상기 불 휘발성 메모리 장치로 전송하는 것을 특징으로 하는 동작 방법.

### 청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

### 발명의 설명

### 기 술 분 야

[0001] 본 발명은 불 휘발성 메모리 장치에 관한 것으로, 좀 더 구체적으로는 불 휘발성 메모리 장치를 포함하는 메모리 시스템에 관한 것이다.

#### 배경기술

- [0002] 반도체 메모리는, 일반적으로, 위성에서 소비자 전자 기술까지의 범위에 속하는 마이크로프로세서를 기반으로 한 응용 및 컴퓨터와 같은 디지털 로직 설계의 가장 필수적인 마이크로 전자 소자이다. 그러므로, 높은 집적도 및 빠른 속도를 위한 축소 (scaling)를 통해 얻어지는 프로세스 향상 및 기술 개발을 포함한 반도체 메모리의 제조 기술의 진보는 다른 디지털 로직 계열의 성능 기준을 확립하는 데 도움이 된다.

- [0003] 반도체 메모리 장치는 크게 휘발성 반도체 메모리 장치와 불 휘발성 반도체 메모리 장치로 나뉘어진다. 휘발성 반도체 메모리 장치에 있어서, 로직 정보는 스태틱 랜덤 액세스 메모리의 경우 쌍안정 플립-플롭의 로직 상태를 설정함으로써 또는 다이나믹 랜덤 액세스 메모리의 경우 커패시터의 충전을 통해 저장된다. 휘발성 반도체 메모리 장치의 경우, 전원이 인가되는 동안 데이터가 저장되고 읽혀지며, 전원이 차단될 때 데이터는 소실된다.

- [0004] MROM, PROM, EPROM, EEPROM 등과 같은 불 휘발성 반도체 메모리 장치는 전원이 차단되어도 데이터를 저장할 수 있다. 불 휘발성 메모리 데이터 저장 상태는 사용되는 제조 기술에 따라 영구적이거나 재프로그램 가능하다. 불

휘발성 반도체 메모리 장치는 컴퓨터, 항공 전자 공학, 통신, 그리고 소비자 전자 기술 산업과 같은 넓은 범위의 응용에서 프로그램 및 마이크로코드의 저장을 위해서 사용된다. 단일 칩에서 휘발성 및 불 휘발성 메모리 저장 모드들의 조합이 빠르고 재프로그램 가능한 불 휘발성 메모리를 요구하는 시스템에서 불 휘발성 RAM (nvRA M)과 같은 장치들에서 또한 사용 가능하다. 게다가, 응용 지향 업무를 위한 성능을 최적화시키기 위해 몇몇 추가적인 로직 회로를 포함하는 특정 메모리 구조가 개발되어 오고 있다.

[0005] 불 휘발성 반도체 메모리 장치에 있어서, MROM, PROM 및 EPROM은 시스템 자체적으로 소거 및 쓰기가 자유롭지 않아서 일반 사용자들이 기억 내용을 새롭게 하기가 용이하지 않다. 이에 반해 EEPROM은 전기적으로 소거 및 쓰기가 가능하므로 계속적인 갱신이 필요한 시스템 프로그래밍(system programming)이나 보조 기억 장치로의 응용이 확대되고 있다.

### 발명의 내용

#### 해결하려는 과제

[0006] 본 발명의 목적은 신뢰성을 향상시킬 수 있는 메모리 시스템 및 그것의 동작 방법을 제공하는 것이다.

### 과제의 해결 수단

- [0007] 본 발명의 일 특징은 데이터 정보를 저장하도록 구성된 불 휘발성 메모리 장치와; 그리고 상기 불 휘발성 메모리 장치를 제어하도록 구성된 메모리 제어기를 포함하며, 상기 메모리 제어기는 내부적으로 요청된 프로그램 동작의 긴급 정도에 따라 가변되는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스를 상기 불 휘발성 메모리 장치로 전송하는 메모리 시스템을 제공하는 것이다.

- [0008] 예시적인 실시예에 있어서, 상기 내부적으로 요청된 프로그램 동작은 외부 요청과 무관하며, 상기 메모리 제어 기의 배경 동작, 서든 파워-오프와 관련된 동작, 또는 카비지 컬렉션을 포함한다.

- [0009] 예시적인 실시예에 있어서, 상기 배경 동작과 관련된 프로그램 동작을 수행하는 데 걸리는 프로그램 시간은 외부 요청에 따라 수행되는 프로그램 동작의 프로그램 시간 보다 길다.

- [0010] 예시적인 실시예에 있어서, 상기 서든 파워-오프와 관련된 프로그램 동작을 수행하는 데 걸리는 프로그램 시간 은 상기 외부 요청에 따라 수행되는 프로그램 동작의 프로그램 시간 보다 짧다.

- [0011] 예시적인 실시예에 있어서, 상기 프로그램 명령 시퀀스는 제 1 명령, 어드레스, 그리고 제 2 명령을 포함하며, 상기 제 2 명령의 값은 상기 외부 요청에 따라 수행되는 프로그램 동작과 상기 내부적으로 요청된 프로그램 동 작들에 따라 다르게 결정된다.

- [0012] 예시적인 실시예에 있어서, 상기 서든 파워-오프와 관련된 프로그램 동작을 통해 프로그램된 데이터는 메타 데이터이다.

- [0013] 예시적인 실시예에 있어서, 상기 서든 파워-오프와 관련된 프로그램 동작을 통해 프로그램된 데이터는 상기 외부 요청에 따라 수행되는 프로그램 동작을 이용하여 재프로그램된다.

- [0014] 예시적인 실시예에 있어서, 상기 불 휘발성 메모리 장치는 프로그램 전압을 발생하는 전압 발생기와; 그리고 상기 전압 발생기를 제어하도록 구성된 제어 로직을 포함하며, 상기 제어 로직은 상기 프로그램 명령 시퀀스에 포함된 프로그램 속도 정보에 의거하여 상기 프로그램 전압의 시작 레벨 또는 상기 프로그램 전압의 증가분을 결정한다.

- [0015] 예시적인 실시예에 있어서, 상기 메모리 제어기와 상기 불 휘발성 메모리 장치는 메모리 카드 및 반도체 드라이 브 중 하나를 구성한다.

- [0016] 본 발명의 다른 특징은 불 휘발성 메모리 장치를 포함하는 메모리 시스템의 동작 방법을 제공하며, 동작 방법은 프로그램 동작이 외부 요청없이 내부적으로 요청되었는 지의 여부를 판별하고, 판별 결과에 따라 상기 요청된 프로그래램 동작의 긴급 정도에 따라 가변되는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스를 상기 불휘발성 메모리 장치로 전송하는 것을 포함한다.

- [0017] 예시적인 실시예에 있어서, 상기 내부적으로 요청된 프로그램 동작은 상기 메모리 제어기의 배경 동작 또는 서든 파워-오프와 관련된 동작을 포함한다.

- [0018] 예시적인 실시예에 있어서, 상기 배경 동작과 관련된 프로그램 동작을 수행하는 데 걸리는 프로그램 시간은 외

- 부 요청에 따라 수행되는 프로그램 동작의 프로그램 시간 보다 길다.

- [0019] 예시적인 실시예에 있어서, 상기 서든 파워-오프와 관련된 프로그램 동작을 수행하는 데 걸리는 프로그램 시간 은 상기 외부 요청에 따라 수행되는 프로그램 동작의 프로그램 시간 보다 짧다.

- [0020] 예시적인 실시예에 있어서, 상기 프로그램 명령 시퀀스는 제 1 명령, 어드레스, 그리고 제 2 명령을 포함하며, 상기 제 2 명령의 값은 상기 외부 요청에 따라 수행되는 프로그램 동작과 상기 내부적으로 요청된 프로그램 동작들에 따라 다르게 결정된다.

- [0021] 예시적인 실시예에 있어서, 상기 프로그램 속도는 상기 프로그램 명령 시퀀스에 포함된 프로그램 속도 정보에 의거하여 프로그램 전압의 시작 레벨 또는 상기 프로그램 전압의 증가분을 제어함으로써 가변된다.

### 발명의 효과

[0022] 본 발명에 의하면, 프로그램 동작의 긴급 정도에 따라 프로그램 시간을 가변적으로 제어하는 것이 가능하다.

### 도면의 간단한 설명

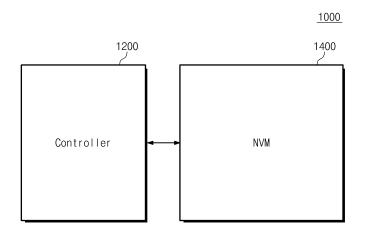

- [0023] 도 1은 본 발명의 실시예에 따른 메모리 시스템을 개략적으로 보여주는 블록도이다.

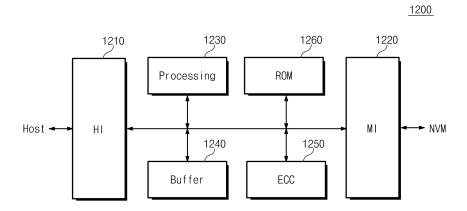

- 도 2는 도 1에 도시된 메모리 제어기를 개략적으로 보여주는 블록도이다.

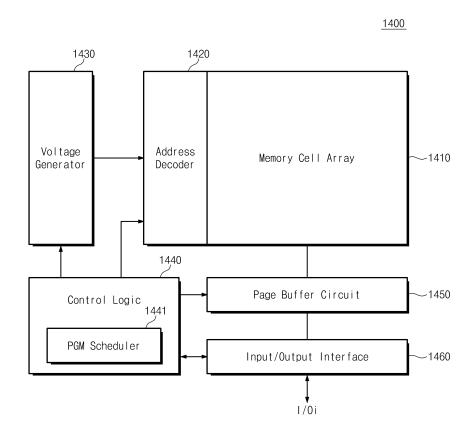

- 도 3는 도 1에 도시된 불 휘발성 메모리 장치를 개략적으로 보여주는 블록도이다.

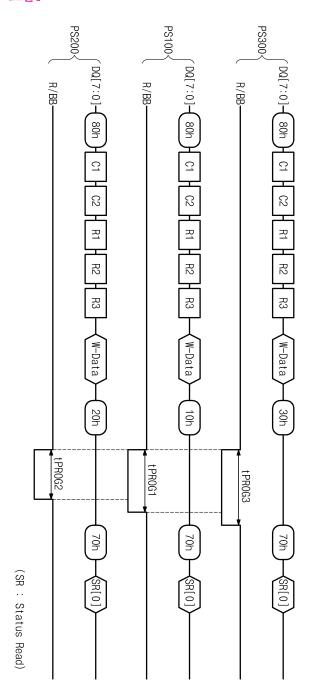

- 도 4는 본 발명의 실시예에 따른 다양한 프로그램 명령 시퀀스들을 보여주는 도면이다.

- 도 5는 본 발명의 실시에에 따른 메모리 시스템의 동작 방법을 개략적으로 설명하기 위한 도면이다.

- 도 6은 본 발명의 실시예에 따른 컴퓨팅 시스템을 개략적으로 보여주는 블록도이다.

- 도 7은 본 발명의 실시예에 따른 반도체 드라이브를 개략적으로 보여주는 블록도이다.

- 도 8은 도 7에 도시된 반도체 드라이브를 이용한 스토리지를 개략적으로 보여주는 블록도이다.

- 도 9는 도 7에 도시된 반도체 드라이브를 이용하 스트리지 서버를 개략적으로 보여주는 블록도이다.

- 도 10 내지 도 12는 본 발명의 실시예들에 따른 데이터 저장 장치가 적용되는 시스템들을 개략적으로 보여주는 도면들이다.

- 도 13은 본 발명의 실시예에 따른 메모리 카드(memory card)를 개략적으로 보여주는 블록도이다.

- 도 14는 본 발명의 실시예에 따른 디지털 스틸 카메라(digital still camera)를 개략적으로 보여주는 블록도이다.

- 도 15는 도 14의 메모리 카드가 사용되는 다양한 시스템을 설명하는 예시적 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0024] 본 발명의 이점 및 특징, 그리고 그것을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 통해 설명될 것이다. 그러나 본 발명은 여기에서 설명되는 실시 예들에 한정되지 않고 다른 형태로 구체 화될 수도 있다. 단지, 본 실시 예들은 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여 제공되는 것이다.

- [0025] 도면들에 있어서, 본 발명의 실시 예들은 도시된 특정 형태로 제한되는 것이 아니며 명확성을 기하기 위하여 과 장된 것이다. 또한 명세서 전체에 걸쳐서 동일한 참조번호로 표시된 부분들은 동일한 구성요소를 나타낸다.

- [0026] 본 명세서에서 '및/또는'이란 표현은 전후에 나열된 구성요소들 중 적어도 하나를 포함하는 의미로 사용된다. 또한, '연결되는/결합되는'이란 표현은 다른 구성요소와 직접적으로 연결되거나 다른 구성요소를 통해 간접적으로 연결되는 것을 포함하는 의미로 사용된다. 본 명세서에서 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 또한, 명세서에서 사용되는 '포함한다' 또는 '포함하는'으로 언급된 구성요소, 단계, 동작 및 소자는 하나 이상의 다른 구성요소, 단계, 동작, 소자 및 장치의 존재 또는 추가를 의미한다.

- [0027] 도 1은 본 발명의 실시예에 따른 메모리 시스템을 개략적으로 보여주는 블록도이다.

- [0028] 도 1을 참조하면, 본 발명의 실시예에 따른 메모리 시스템(1000)은 메모리 제어기(1200)와 불 휘발성 메모리 장치(1400)를 포함한다. 메모리 제어기(1200)는 외부(예를 들면, 호스트)로부터의 요청(예를 들면, 쓰기 요청, 읽기 요청, 등)에 응답하여 불 휘발성 메모리 장치(1400)를 제어한다. 메모리 제어기(1200)는 외부 요청없이 내부적인 요청(예를 들면, 서든 파워-오프와 관련된 동작, 배경 동작, 등)에 따라 불 휘발성 메모리 장치(1400)를 제어한다. 불 휘발성 메모리 장치(1400)는 메모리 제어기(1200)의 제어에 응답하여 동작하며, 데이터 정보를 저장하는 일종의 저장 매체로서 사용된다. 저장 매체는 하나 또는 그 보다 많은 메모리 칩들로 구성될 수 있다. 불 휘발성 메모리 장치(1400)와 메모리 제어기(1200)는 하나 또는 그 보다 많은 채널들을 통해 통신한다. 불 휘발성 메모리 장치(1400)는, 예를 들면, 낸드 플래시 메모리 장치를 포함한다.

- [0029] 메모리 제어기(1200)는 상이한 프로그램 속도들 중 어느 하나로 프로그램 동작이 수행되도록 불 휘발성 메모리 장치(1400)를 제어한다. 예시적인 실시예에 있어서, 메모리 제어기(1200)는 프로그램 동작시 불 휘발성 메모리 장치(1400)로 프로그램 속도 정보를 포함하는 프로그램 명령을 제공한다. 여기서, 프로그램 속도 정보는 다양한 방식들을 이용하여 프로그램 명령에 포함될 수 있다. 예를 들면, 불 휘발성 메모리 장치(1400)의 프로그램 동작은 메모리 제어기(1200)에서 제공되는 프로그램 명령 시퀀스, 즉, 일련의 제 1 명령, 어드레스, 프로그램 데이터, 그리고 제 2 명령에 따라 행해질 것이다. 제 1 명령(예를 들면, 80h)은 프로그램 데이터의 입력을 알리는 명령, 즉, 데이터 입력 명령이고, 제 2 명령은 프로그램 확인 명령이다. 프로그램 확인 명령으로서 제 2 명령이 입력되면, 불 휘발성 메모리 장치(1400)는 정해진 프로그램 시간(tPGM) 동안 프로그램 동작을 수행할 것이다.

- [0030] 예시적인 실시예에 있어서, 제 2 명령은 프로그램 속도 정보를 포함할 것이다. 프로그램 동작은 정상 프로그램 동작(또는, 디폴트 프로그램 속도), 빠른 프로그램 동작, 그리고 느린 프로그램 동작으로 구분될 것이다. 정상 프로그램 동작은 제품 명세서에 명기된 프로그램 속도(tPGM1)로 행해지는 프로그램 동작을 의미한다. 빠른 프로그램 동작은 정상 프로그램 동작의 프로그램 속도(tPGM1)보다 빠른 프로그램 속도(tPGM2)로 행해지는 프로그램 동작을 의미하고, 느린 프로그램 동작은 정상 프로그램 동작의 프로그램 동작의 프로그램 속도(tPGM3)로 행해지는 프로그램 속도(tPGM3)로 행해지는 프로그램 동작을 의미한다. 따라서, 프로그램 동작을 수행하는 데 걸리는 프로그램 시간은 메모리 제어기(1200)에서 불 휘발성 메모리 장치(1400)로 전송되는 제 2 명령에 따라 가변될 것이다.

- [0031] 정상 프로그램 동작을 위한 프로그램 명령 시퀀스는 외부 장치(예를 들면, 호스트)의 쓰기 요청에 따라 메모리 제어기(1200)에 의해서 생성되는 반면에, 빠른 그리고 느린 프로그램 동작들을 위한 프로그램 명령 시퀀스들은 외부 요청 없이 내부적인 요청에 따라 메모리 제어기(1200)에 의해서 생성될 수 있다. 여기서, 내부적인 요청은 배경 동작(예를 들면, 가비지 컬렉션, 주기적인 메타 데이터 갱신, 등), 서든 파워-오프와 관련된 동작(예를 들면, 메모리 제어기(1200)에서 불 휘발성 메모리 장치로의 메타 데이터 덤프, 등), 그리고 그와 같은 것을 포함할 것이다. 배경 동작은, 일반적으로, 유휴 시간에 행해지기 때문에 정상 프로그램 동작과 동일한 프로그램 시간을 필요로 하지 않는다. 이에 반해서, 서든 파워-오프와 관련된 동작은 가급적 빠른 시간 내에서 행해져야 한다. 본 발명에 따르면, 수행되어야 할 동작의 긴급 정도에 따라 프로그램 시간을 가변적으로 제어하는 것이 가능하다.

- [0032] 도 2는 도 1에 도시된 메모리 제어기를 개략적으로 보여주는 블록도이다. 도 2를 참조하면, 메모리 제어기 (1200)는 제 1 인터페이스로서 호스트 인터페이스(1210), 제 2 인터페이스로서 메모리 인터페이스(1220), CPU와 같은 처리 유니트(1230), 버퍼 메모리(1240), 에러 검출 및 정정 회로(1250), 그리고 롬(1260)을 포함한다.

- [0033] 호스트 인터페이스(1210)는 외부(또는, 호스트)와 인터페이스하도록 구성된다. 메모리 인터페이스(1220)는 도 1에 도시된 불 휘발성 메모리 장치(1400)와 인터페이스하도록 구성된다. 처리 유니트(1230), 예를 들면, CPU는 메모리 제어기(1200)의 전반적인 동작을 제어하도록 구성된다. 예를 들면, 처리 유니트(1230)는 플래시 변환 계층(Flash Translation Layer: FTL)과 같은 펌웨어를 운용하도록 구성된다. 버퍼 메모리(1240)는 호스트 인터페이스(1210)를 통해 외부로 전달되는 데이터를 임시 저장하는 데 사용된다. 버퍼 메모리(1240)는 메모리 인터페이스(1220)를 통해 불 휘발성 메모리 장치(1400)로부터 전달되는 데이터를 임시 저장하는 데 사용된다. 버퍼 메모리(1240)는 불 휘발성 메모리 장치(1400)를 제어하는 데 필요한 정보(예를 들면, 맵핑 정보(이하, 메타데이터 정보라 칭함))를 저장하는 데 사용된다. 에러 검출 및 정정 회로(1250)는 불 휘발성 메모리 장치(1400)에 저장될 데이터를 부호화하도록 그리고 불 휘발성 메모리 장치(1400)로부터 읽혀진 데이터를 복호화하도록 구성된다. 몸(1260)은 플래시 변환 계층(Flash Translation Layer: FTL)과 같은 펌웨어를 저장하는 데 사용될 수 있다. 다른 예로서, 롬(1260)을 포함하지 않도록 메모리 제어기(1200)를 구성하는 것이 가능하다. 이러한 경우, 롬에 저장되는 펌웨어는 메모리 제어기(1200)에 의해서 제어되는 불 휘발성 메모리 장치(1400)에 저장되며, 파워-업시 불 휘발성 메모리 장치(1400)에서 메모리 제어기(1200)로 로드될 것이다.

- [0034] 본 발명의 경우, 메모리 제어기(1200)는 프로그램 동작의 긴급 정도에 따라 프로그램 시간이 가변되도록 불 휘발성 메모리 장치(1400)를 제어한다. 디폴트 프로그램 시간을 갖는 프로그램 동작은 외부 요청에 따라 행해지는 반면에, 디폴트 프로그램 시간보다 짧거나 긴 프로그램 시간을 갖는 프로그램 동작은 외부 요청 없이 내부적인 요청에 따라 행해진다. 이는 이후 상세히 설명될 것이다.

- 실시예에 있어서, 호스트 인터페이스(1210)는 컴퓨터 버스 표준들, 스토리지 버스 표준들, iFCPPeripheral 버스 표준들, 등 중 하나 또는 그 보다 많은 것들의 조합으로 구성될 수 있다. 컴퓨터 버스 표준들(computer bus standards)은 S-100 bus, Mbus, Smbus, Q-Bus, ISA, Zorro II, Zorro III, CAMAC, FASTBUS, LPC, EISA, VME, VXI, NuBus, TURBOchannel, MCA, Sbus, VLB, PCI, PXI, HP GSC bus, CoreConnect, InfiniBand, UPA, PCI-X, AGP, PCIe, Intel QuickPath Interconnect, Hyper Transport, 등을 포함한다. 스토리지 버스 표준들(Storage bus standards)은 ST-506, ESDI, SMD, Parallel ATA, DMA, SSA, HIPPI, USB MSC, FireWire(1394), Serial ATA, eSATA, SCSI, Parallel SCSI, Serial Attached SCSI, Fibre Channel, iSCSI, SAS, RapidIO, FCIP, 등을 포함한다. iFCPPeripheral 버스 표준들(iFCPPeripheral bus standards)은 Apple Desktop Bus, HIL, MIDI, Multibus, RS-232, DMX512-A, EIA/RS-422, IEEE-1284, UNI/O, 1-Wire, I2C, SPI, EIA/RS-485, USB, Camera Link, External PCIe, Light Peak, Multidrop Bus, 등을 포함한다.

- [0036] 비록 도면에는 도시되지 않았지만, 메모리 제어기(1200)는 불 휘발성 메모리 장치(1400)에 저장될 데이터를 랜 덤화하도록 그리고 불 휘발성 메모리 장치(1400)로부터 읽혀진 데이터를 디-랜덤화하도록 구성되는 랜덤화기/디-랜덤화기를 더 포함할 수 있다. 랜덤화기/디-랜덤화기의 예가 미국특허공개번호 제2010/0088574호에 "DATA STORAGE SYSTEM AND DEVICE WITH RANDOMIZER/DE-RANDOMIZER"라는 제목으로 게재되어 있으며, 이 출원의 레퍼런 스로 포함된다.

- [0037] 도 3는 도 1에 도시된 불 휘발성 메모리 장치를 개략적으로 보여주는 블록도이다.

- [0038] 불 휘발성 메모리 장치(1400)는, 예를 들면, 낸드 플래시 메모리 장치일 것이다. 하지만, 본 발명이 낸드 플래시 메모리 장치에 국한되지 않음은 잘 이해될 것이다. 예를 들면, 불 휘발성 메모리 장치(1400)는 노아 플래시 메모리 장치, 저항성 램(Resistive Random Access Memory: RRAM) 장치, 상변화 메모리(Phase-Change Memory: PRAM) 장치, 자기저항 메모리(Magnetoresistive Random Access Memory: MRAM) 장치, 강유전체 메모리 (Ferroelectric Random Access Memory: FRAM) 장치, 스핀주입 자화반전 메모리(Spin Transfer Torque Random Access Memory: STT-RAM), 또는 그와 같은 것으로 구성될 수 있다. 또한, 본 발명의 불 휘발성 메모리 장치 (1400)는 3차원 어레이 구조를 갖도록 구현될 수 있다. 3차원 어레이 구조를 갖는 불 휘발성 메모리 장치는 수 직 낸드 플래시 메모리 장치라 불린다. 본 발명은 전하 저장층이 전도성 부유 게이트로 구성된 플래시 메모리 장치 뿐만 아니라, 전하 저장층이 절연막으로 구성된 차지 트랩형 플래시(Charge Trap Flash, "CTF"라 불림) 메모리 장치에도 모두 적용 가능하다.

- [0039] 도 3을 참조하면, 불 휘발성 메모리 장치(1400)는 메모리 셀 어레이(1410), 어드레스 디코더(1420), 전압 발생기(1430), 제어 로직(1440), 페이지 버퍼 회로(1450), 그리고 입출력 인터페이스(1460)를 포함한다.

- [0040] 메모리 셀 어레이(1410)는 행들(예를 들면, 워드 라인들)과 열들(예를 들면, 비트 라인들)의 교차 영역들에 배열된 메모리 셀들을 포함할 것이다. 메모리 셀들 각각은 1-비트 데이터 또는 멀티-비트 데이터를 저장할 것이다. 어드레스 디코더(1420)는 제어 로직(1440)에 의해서 제어되며, 메모리 셀 어레이(1410)의 행들(예를 들면, 워드 라인들, 스트링 선택 라인(들), 접지 선택 라인(들), 공통 소오스 라인, 등)의 선택 및 구동을 행한다. 전압 발생기(1430)는 제어 로직(1440)에 의해서 제어되며, 각 동작에 필요한 전압들(예를 들면, 고전압, 프로그램 전압, 읽기 전압, 검증 전압, 소거 전압, 패스 전압, 벌크 전압, 등)을 발생한다. 전압 발생기(1430)에 의해서 전압들은 어드레스 디코더(1420)를 통해 메모리 셀 어레이(1410)에 제공된다. 제어 로직(1440)은 불 휘발성 메모리 장치(1400)의 전반적인 동작을 제어하도록 구성된다. 페이지 버퍼 회로(1450)는 제어 로직(1440)에 의해서 제어되며, 메모리 셀 어레이(1410)로부터 데이터를 읽도록 또는 프로그램 데이터에 따라 메모리 셀 어레이(1410)의 열들(예를 들면, 비트 라인들)을 구동하도록 구성된다. 페이지 버퍼 회로(1450)는 비트 라인들 또는 비트 라인 쌍들에 각각 대응하는 복수의 페이지 버퍼들로 구성될 것이다. 페이지 버퍼들 각각은 복수의 래치들을 포함한다. 입출력 인터페이스(1460)는 제어 로직(1440)에 의해서 제어되며, 외부(예를들면, 도 1의 메모리 제어기)와 인터페이스하도록 구성된다.

- [0041] 본 발명에 따른 제어 로직(1440)은 프로그램 스케쥴러(1441)를 포함한다. 프로그램 스케쥴러(1441)는 불 휘발성 메모리 장치(1400)의 프로그램 동작을 제어할 것이다. 특히, 프로그램 스케쥴러(1441)는 메모리 제어기(1200)로 부터 제공되는 프로그램 명령 시퀀스에 따라 프로그램 속도를 가변적으로 결정할 것이다. 프로그램 속도는 다양

한 방법들을 이용하여 가변적으로 제어될 것이다. 예를 들면, 프로그램 전압의 시작 레벨을 제어함으로써 프로그램 속도가 가변될 수 있다. 또는, 증가형 스텝 펄스 프로그램 방식의 경우, 프로그램 전압의 증가분을 제어함으로써 프로그램 속도가 가변될 수 있다. 프로그램 속도의 가변이 여기에 개시된 것에 국한되지 않음은 잘 이해될 것이다. 프로그램 전압의 시작 레벨 또는 프로그램 전압의 증가분은 전압 발생기(1430)를 제어함으로써 가변될 것이다. 프로그램 스케쥴러(1441)는 프로그램 명령 시퀀스 특히, 프로그램 속도 정보를 포함하는 제 2 명령(또는, 프로그램 확인 명령)에 따라 프로그램 속도를 가변적으로 결정한다.

- [0042] 본 발명의 경우, 프로그램 동작의 긴급 정도에 따라 프로그램 시간을 결정함으로써 신뢰성/내구성을 향시킬 수 있다.

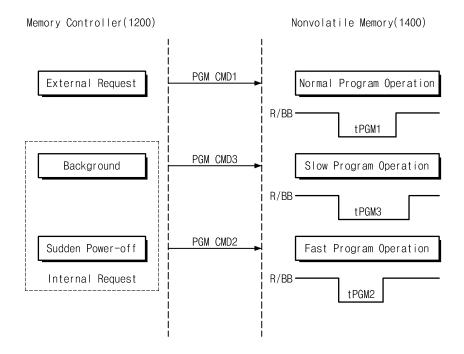

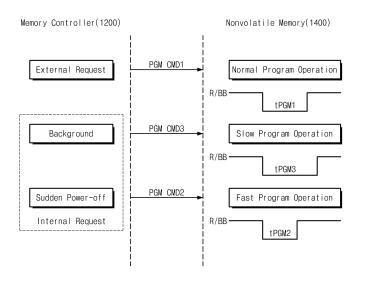

- [0043] 도 4는 본 발명의 실시예에 따른 다양한 프로그램 명령 시퀀스들을 보여주는 도면이다.

- [0044] 도 4을 참조하면, 프로그램 동작시, 프로그램 명령 시퀀스는 메모리 제어기(1200)에서 불 휘발성 메모리 장치 (1400)로 제공될 것이다. 앞서 언급된 바와 같이, 불 휘발성 메모리 장치(1400)의 프로그램 동작은 외부 요청에 따라 또는 메모리 제어기(1200)의 내부적인 요청에 따라 수행될 것이다. 외부로부터 쓰기 동작이 요청될 때, 메모리 제어기(1200)는 프로그램 명령 시퀀스(PS100)에 따라 제 1 명령(80h), 어드레스, 쓰기 데이터, 그리고 제 2 명령(10h)를 불 휘발성 메모리 장치(1400)로 순차적으로 전송한다. 프로그램 명령 시퀀스(PS100)의 전송 동안, 제어 신호(R/BB)는 하이로 유지된다. 프로그램 속도 정보를 포함하는 제 2 명령(10h)가 입력되면, 제어 신호(R/BB)는 로우 레벨로 천이한다. 제어 신호(R/BB)가 로우 레벨로 유지되는 시간 즉, 프로그램 시간(tPGM1) 동안, 프로그램 동작이 수행될 것이다. 제 2 명령의 값이 '10h'일 때, 디폴트 프로그램 시간(tPGM1) 동안 프로그램 동작이 수행될 것이다.

- [0045] 가비지 컬렉션과 같은 배경 동작은 메모리 시스템(1000)의 유휴 시간 동안 수행될 것이다. 배경 동작은 외부로부터 요청되는 것이 아니라 외부와 무관하게 메모리 제어기(1200) 내에서 요청될 것이다. 배경 동작은 외부로프로그램 동작이 요청될 때, 메모리 제어기(1200)는 프로그램 명령 시퀀스(PS300)에 따라 제 1 명령(80h), 어드레스, 쓰기 데이터, 그리고 제 2 명령(30h)를 불 휘발성 메모리 장치(1400)로 순차적으로 전송한다. 프로그램 명령 시퀀스(PS300)의 전송 동안, 제어 신호(R/BB)는 하이로 유지된다. 프로그램 속도 정보를 포함하는 제 2 명령(30h)가 입력되면, 제어 신호(R/BB)는 로우 레벨로 천이한다. 제어 신호(R/BB)가 로우 레벨로 유지되는 시간즉, 프로그램 시간(tPGM3) 동안, 프로그램 동작이 수행될 것이다. 제 2 명령의 값이 '30h'일 때, 디폴트 프로그램 시간(tPGM1)보다 긴 프로그램 시간(tPGM3) 동안 프로그램 동작이 수행될 것이다. 프로그램 시간의 조정은, 앞서 설명된 바와 같이, 프로그램 스케쥴러(1441)의 제어하에 행해질 것이다. 예를 들면, 전압 발생기(1430)에 의해서 생성되는 프로그램 전압의 시작 레벨, 프로그램 전압의 증가분, 또는 그와 같은 것이 프로그램 스케쥴러(1441)에 의해서 결정될 것이다. 프로그램 시간의 조정이 여기에 개시된 것에 국한되지 않음은 잘 이해될 것이다.

- [0046] 서든 파워-오프와 관련된 동작은 외부로부터 요청되는 것이 아니라 외부와 무관하게 메모리 제어기(1200) 내에서 요청될 것이다. 서든 파워-오프와 관련된 동작과 관련된 프로그램 동작(예를 들면, 메타데이터와 관련된 프로그램 동작)이 요청될 때, 메모리 제어기(1200)는 프로그램 명령 시퀀스(PS200)에 따라 제 1 명령(80h), 어드레스, 쓰기 데이터, 그리고 제 2 명령(20h)를 불 휘발성 메모리 장치(1400)로 순차적으로 전송한다. 프로그램 명령 시퀀스(PS200)의 전송 동안, 제어 신호(R/BB)는 하이로 유지된다. 프로그램 속도 정보를 포함하는 제 2 명령(20h)가 입력되면, 제어 신호(R/BB)는 로우 레벨로 천이한다. 제어 신호(R/BB)가 로우 레벨로 유지되는 시간즉, 프로그램 시간(tPGM2) 동안, 프로그램 동작이 수행될 것이다. 제 2 명령의 값이 '20h'일 때, 디폴트 프로그램 시간(tPGM1)보다 짧은 프로그램 시간(tPGM2) 동안 프로그램 동작이 수행될 것이다. 프로그램 시간의 조정은, 앞서 설명된 바와 같이, 프로그램 스케쥴러(1441)의 제어하에 행해질 것이다. 예를 들면, 전압 발생기(1430)에 의해서 생성되는 프로그램 전압의 시작 레벨, 프로그램 전압의 증가분, 또는 그와 같은 것이 프로그램 스케쥴러(1441)에 의해서 결정될 것이다. 프로그램 시간의 조정이 여기에 개시된 것에 국한되지 않음은 잘 이해될 것이다.

- [0047] 앞서의 설명에 따르면, 프로그램 명령 시퀀스는 아래의 표 1과 같이 요약될 것이다.

丑 1

[0048] address cycle function 1st set 2nd set normal page program 80h 5 10h 80h 5 20h fast page program 5 slow page program 80h 30h

- [0049] 메모리 제어기(1200)에서 불 휘발성 메모리 장치(1400)로 전송되는 프로그램 명령 시퀀스, 특히, 제 2 명령은 프로그램 속도 정보를 나타내도록 구별될 것이다. 도 4에 도시된 바와 같이, 제 2 명령의 값에 따라 프로그램 시간이 가변될 것이다. 여기서, 제품 명세서에 기재되어 있는 프로그램 시간의 최대값과 최소값 사이의 차이는 하나의 프로그램 시간 내에서 포함됨에 유의해야 할 것이다. 즉, 상이한 프로그램 시간들(tPGM1, tPGM2, tPGM3) 각각은 최대값과 최소값을 갖는다.

- [0050] 앞서 설명된 바와 같이, 빠른 프로그램 동작은 디폴트 프로그램 동작과 비교하여 볼 때 프로그램 전압의 시작 레벨을 높게 설정함으로써 달성될 수 있다. 프로그램 전압의 시작 레벨을 높게 설정함으로써 프로그램 루프들의 횟수가 줄어들며, 그 결과 프로그램 시간이 단축될 것이다. 이러한 경우, 비트 에러율(Bit Error Rate: BER)의 증가를 초래하는 오버 프로그래밍이 발생할 수 있다. 하지만, 에러 비트들의 수를 ECC 능력 내에서 관리함으로 써 빠른 프로그램 동작을 통해 프로그램된 데이터를 정상적인 데이터로 읽는 것이 가능하다. 추후, 읽기 리프레 쉬를 사용하여 정상 프로그램 동작을 수행하는 것이 가능하다. 빠른 프로그램 동작의 읽기 카운트 정책은 정상 프로그램 동작과 다르게 결정될 수 있다.

- [0051] 본 발명의 불 휘발성 메모리 장치(1400)는 제품 생산성을 향상하는 데에 유리하다. 예를 들면, 일반적으로, 불 휘발성 메모리 장치가 적용되는 제품에 따라 불 휘발성 메모리 장치의 프로그램 시간이 달리질 수 있다. 즉, 불 휘발성 메모리 장치가 동일한 공정을 이용하여 제조되더라도, 상이한 프로그램 시간이 적용되는 제품들에 따라 라인-업이 분류될 수 있다. 하지만, 추가되는 프로그램 명령 시퀀스들을 사용함으로써 동일 공정 조건에서 제공되고 다른 프로그램 시간을 갖는 불 휘발성 메모리 장치들의 라인-업을 하나로 통일함으로써 제품 생산성을 향상시킬 수 있다.

- [0052] 도 5는 본 발명의 실시예에 따른 메모리 시스템의 동작 방법을 개략적으로 설명하기 위한 도면이다.

- [0053] 도 5를 참조하면, 메모리 제어기(1200)는 프로그램 동작이 외부로부터 요청되었는 지 또는 내부에서 요청되었는 지의 여부를 판별할 것이다. 만약 프로그램 동작이 외부로부터 요청된 것으로 판별되면, 메모리 제어기(1200)는 제 1 프로그램 명령 시퀀스에 따라 제 1 명령, 어드레스, 그리고 제 2 명령을 불 휘발성 메모리 장치(1400)로 전송한다. 여기서, 제 2 명령은 프로그램 속도 정보를 포함하며, 불 휘발성 메모리 장치(1400)는 제 2 명령의 프로그램 속도 정보에 따라 프로그램 속도를 결정할 것이다. 즉, 불 휘발성 메모리 장치(1400)는 디폴트 프로그램 시간(tPGM1) 동안 프로그램 동작을 수행할 것이다.

- [0054] 만약 프로그램 동작이 메모리 제어기(1200)의 내부로부터 요청된 것으로 판별되면, 메모리 제어기(1200)는 요청된 프로그램 동작의 긴급 정도를 판단할 것이다. 요청된 프로그램 동작이 긴급한 경우, 메모리 제어기(1200)는 제 2 프로그램 명령 시퀀스에 따라 제 1 명령, 어드레스, 그리고 제 2 명령을 불 휘발성 메모리 장치(1400)로 전송한다. 여기서, 제 2 명령은 프로그램 속도 정보를 포함하며, 불 휘발성 메모리 장치(1400)는 제 2 명령의 프로그램 속도 정보에 따라 프로그램 속도를 결정할 것이다. 즉, 불 휘발성 메모리 장치(1400)는 디폴트 프로그램 시간(tPGM1)보다 짧은 프로그램 시간(tPGM2) 동안 프로그램 동작을 수행할 것이다.

- [0055] 요청된 프로그램 동작이 긴급하지 않은 경우, 메모리 제어기(1200)는 제 3 프로그램 명령 시퀀스에 따라 제 1 명령, 어드레스, 그리고 제 2 명령을 불 휘발성 메모리 장치(1400)로 전송한다. 여기서, 제 2 명령은 프로그램 속도 정보를 포함하며, 불 휘발성 메모리 장치(1400)는 제 2 명령의 프로그램 속도 정보에 따라 프로그램 속도 를 결정할 것이다. 즉, 불 휘발성 메모리 장치(1400)는 디폴트 프로그램 시간(tPGM1)보다 긴 프로그램 시간(tPGM3) 동안 프로그램 동작을 수행할 것이다.

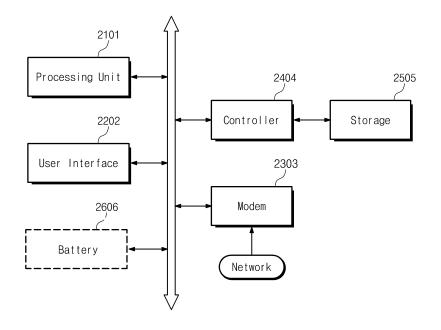

- [0056] 도 6은 본 발명의 실시예에 따른 컴퓨팅 시스템을 개략적으로 보여주는 블록도이다.

- [0057] 컴퓨팅 시스템은 프로세싱 유니트(2101), 사용자 인터페이스(2202), 베이스밴드 칩셋(baseband chipset)과 같은 모뎀(2303), 메모리 제어기(2404), 그리고 저장 매체로서 불 휘발성 메모리 장치(2505)를 포함한다. 메모리 제어기(2404)와 불 휘발성 메모리 장치(2505)는 도 1에 도시된 것과 실질적으로 동일하게 구성될 것이다. 즉, 메모리 제어기(2404)는 프로그램 동작의 긴급 정도에 따라 프로그램 시간이 가변되도록 불 휘발성 메모리 장치(2505)를 제어할 것이다. 이는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스들을 이용하여 달성될 것이다. 불 휘발성 메모리 장치(2505)에는 프로세싱 유니트(2101)에 의해서 처리된/처리될 N-비트 데이터(N은 1 또는 그 보다 큰 정수)가 메모리 제어기(2404)를 통해 저장될 것이다. 컴퓨팅 시스템이 모바일 장치인 경우, 컴퓨팅 시스템의 동작 전압을 공급하기 위한 배터리(2606)가 추가적으로 제공될 것이다. 비록 도면에는 도시되지 않 았지만, 본 발명에 따른 컴퓨팅 시스템에는 응용 칩셋(application chipset), 카메라 이미지 프로세서(Camera

Image Processor: CIS), 모바일 디램, 등이 더 제공될 수 있음은 잘 이해될 것이다.

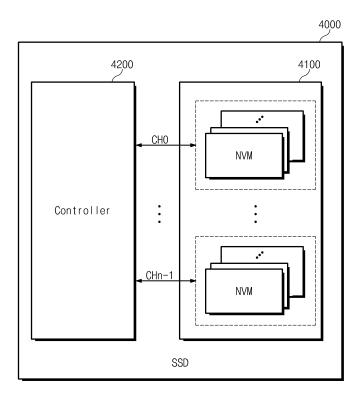

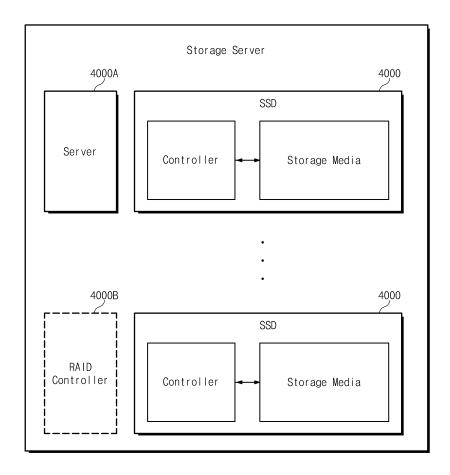

- [0058] 도 7은 본 발명의 실시예에 따른 반도체 드라이브를 개략적으로 보여주는 블록도이다.

- [0059] 도 7을 참조하면, 반도체 드라이브(4000)(SSD)는 저장 매체(4100)와 제어기(4200)를 포함할 것이다. 저장 매체 (4100)는 복수의 채널들을 통해 제어기(4200)와 연결될 것이다. 각 채널에는 복수의 불 휘발성 메모리들이 공통으로 연결될 것이다. 각 불 휘발성 메모리(NVM) 및 제어기(4200)는 도 1에 도시된 것과 실질적으로 동일하게 구성될 것이다. 즉, 제어기(4200)는 프로그램 동작의 긴급 정도에 따라 프로그램 시간이 가변되도록 불 휘발성 메모리 장치(NVM)를 제어할 것이다. 이는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스들을 이용하여 달성될 것이다.

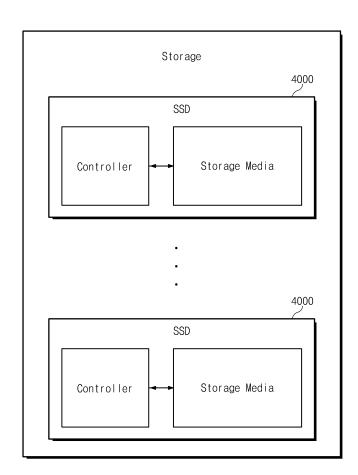

- [0060] 도 8은 도 7에 도시된 반도체 드라이브를 이용한 스토리지를 개략적으로 보여주는 블록도이고, 도 9는 도 7에 도시된 반도체 드라이브를 이용한 스트리지 서버를 개략적으로 보여주는 블록도이다.

- [0061] 본 발명의 실시예에 따른 반도체 드라이브(4000)는 스토리지를 구성하는 데 사용될 수 있다. 도 8에 도시된 바와 같이, 스토리지는 도 7에서 설명된 것과 실질적으로 동일하게 구성되는 복수의 반도체 드라이브들을 포함할 것이다. 본 발명의 실시예에 따른 반도체 드라이브(4000)는 스토리지 서버를 구성하는 데 사용될 수 있다. 도 9에 도시된 바와 같이, 스토리지 서버는 도 7에서 설명된 것과 실질적으로 동일하게 구성되는 복수의 반도체 드라이브들(4000), 그리고 서버(4000A)를 포함할 것이다. 또한, 이 분야에 잘 알려진 RAID 제어기(4000B)가 스토리지 서버에 제공될 수 있음은 잘 이해될 것이다.

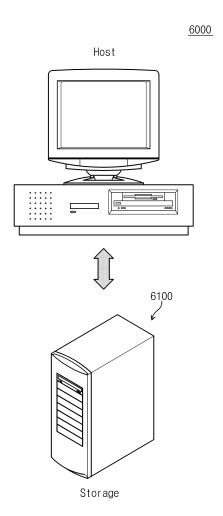

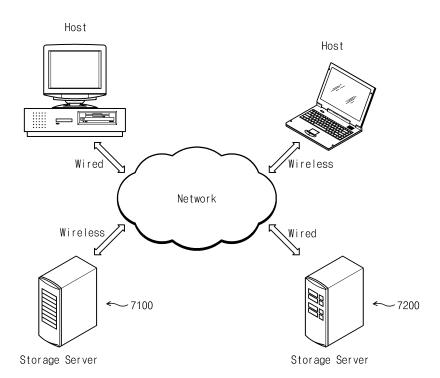

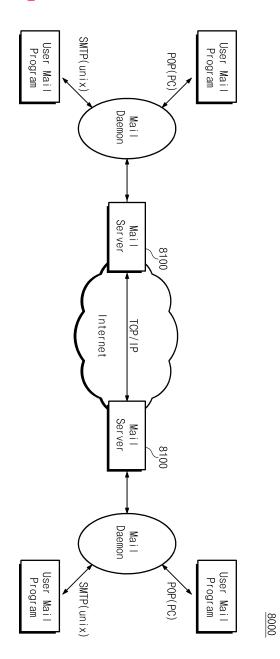

- [0062] 도 10 내지 도 12는 본 발명의 실시예들에 따른 데이터 저장 장치가 적용되는 시스템들을 개략적으로 보여주는 도면들이다.

- [0063] 본 발명의 실시예들에 따른 메모리 제어기 및 멀티-비트 메모리 장치들로 구성되는 데이터 저장 장치를 포함한 반도체 드라이브가 스토리지에 적용되는 경우, 도 10에 도시된 바와 같이, 시스템(6000)은 유선 그리고/또는 무선으로 호스트와 통신하는 스토리지(6100)를 포함할 것이다. 본 발명의 실시예들에 따른 데이터 저장 장치를 포함한 반도체 드라이브가 스토리지 서버에 적용되는 경우, 도 11에 도시된 바와 같이, 시스템(7000)은 유선 그리고/또는 무선으로 호스트와 통신하는 스토리지 서버들(7100, 7200)을 포함할 것이다. 또한, 도 12에 도시된 바와 같이, 본 발명의 실시예에 따른 데이터 저장 장치를 포함한 반도체 드라이브는 메일 서버(8100)에도 적용될수 있다.

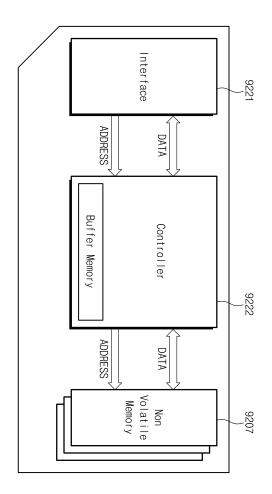

- [0064] 도 13은 본 발명의 실시예에 따른 메모리 카드(memory card)를 개략적으로 보여주는 블록도이다.

- [0065] 메모리 카드는 예를 들어, MMC 카드, SD카드, 멀티유즈(multiuse) 카드, 마이크로 SD카드, 메모리 스틱, 컴팩트 SD 카드, ID 카드, PCMCIA 카드, SSD카드, 칩카드(chipcard), 스마트카드(smartcard), USB카드 등일 수 있다.

- [0066] 도 13을 참조하면, 메모리 카드는 외부와의 인터페이스를 수행하는 인터페이스부(9221), 버퍼 메모리를 갖고 메모리 카드의 동작을 제어하는 제어기(9222), 하나 또는 그 보다 많은 불 휘발성 메모리 장치들(9207)을 포함할 것이다. 제어기(9222)는 프로세서로서, 불 휘발성 메모리 장치(9207)의 라이트 동작 및 리드 동작을 제어할 수 있다. 구체적으로, 컨트롤러(9222)는 데이터 버스(DATA)와 어드레스 버스(ADDRESS)를 통해서 불 휘발성 메모리 장치(9207) 및 인터페이스부(9221)와 커플링되어 있다. 제어기(9222)와 불 휘발성 메모리(9207)는 도 1에서 설명된 메모리 제어기와 불 휘발성 메모리 장치에 대응할 것이다. 즉, 제어기(9222)는 프로그램 동작의 긴급 정도에 따라 프로그램 시간이 가변되도록 불 휘발성 메모리 장치(9207)를 제어할 것이다. 이는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스들을 이용하여 달성될 것이다.

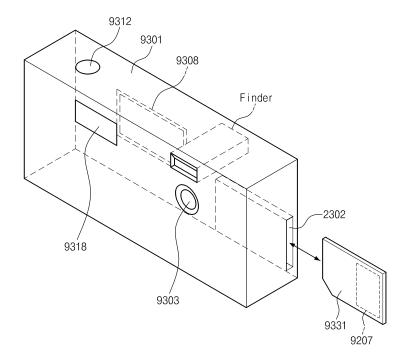

- [0067] 도 14는 본 발명의 실시예에 따른 디지털 스틸 카메라(digital still camera)를 개략적으로 보여주는 블록도이다.

- [0068] 도 14를 참조하면, 디지털 스틸 카메라는 바디(9301), 슬롯(9302), 렌즈(9303), 디스플레이부(9308), 셔터 버튼 (9312), 스트로브(strobe)(9318) 등을 포함한다. 특히, 슬롯(9308)에는 메모리 카드(9331)가 삽입될 수 있고, 메모리 카드(9331)는 도 1에서 설명된 메모리 제어기 및 불 휘발성 메모리 장치를 포함할 것이다. 즉, 제어기는 프로그램 동작의 긴급 정도에 따라 프로그램 시간이 가변되도록 불 휘발성 메모리 장치를 제어할 것이다. 이는 프로그램 속도 정보를 포함하는 프로그램 명령 시퀀스들을 이용하여 달성될 것이다. 예를 들면, 디지털 스틸 카메라의 연속 촬영 기능의 경우 보다 많은 사진을 저장하기 위해 빠른 속도의 명령어 시퀀스를 사용하고, 일반적인 사진 촬영의 경우 정상적인 속도의 명령어 시퀀스를 사용할 수 있다.

- [0069] 메모리 카드(9331)가 접촉형(contact type)인 경우, 메모리 카드(9331)가 슬롯(9308)에 삽입될 때 메모리 카드

(9331)와 회로 기판 상의 특정 전기 회로가 전기적으로 접촉하게 된다. 메모리 카드(9331)가 비접촉형(non-contact type)인 경우, 무선 신호를 통해서 메모리 카드(9331)가 액세스될 것이다.

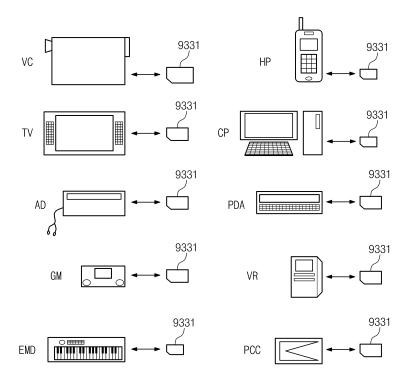

- [0070] 도 15는 도 14의 메모리 카드가 사용되는 다양한 시스템을 설명하는 예시적 도면이다.

- [0071] 도 15를 참조하면, 메모리 카드(9331)는 비디오 카메라(VC), 텔레비전(TV), 오디오 장치(AD), 게임장치(GM), 전자 음악 장치(EMD), 휴대폰(HP), 컴퓨터(CP), PDA(Personal Digital Assistant), 보이스 레코더(voice recorder)(VR), PC 카드(PCC), 등에 사용될 수 있다.

- [0072] 본 발명의 실시예에 있어서, 메모리 셀들은 가변 저항 메모리 셀로 구성될 수 있으며, 예시적인 가변 저항 메모리 셀 및 그것을 포함한 메모리 장치가 미국특허번호 제7529124호에 게재되어 있으며, 이 출원의 레퍼런스로 포함될 것이다.

- [0073] 본 발명의 다른 실시예에 있어서, 메모리 셀들은 전하 저장층을 갖는 다양한 셀 구조들 중 하나를 이용하여 구현될 수 있다. 전하 저장층을 갖는 셀 구조는 전하 트랩층을 이용하는 전하 트랩 플래시 구조, 어레이들이 다층으로 적층되는 스택 플래시 구조, 소오스-드레인이 없는 플래시 구조, 핀-타입 플래시 구조, 등을 포함할 것이다.

- [0074] 전하 저장층으로서 전하 트랩 플래시 구조를 갖는 메모리 장치가 미국특허 제6858906호, 미국공개특허 제2004-0169238호, 그리고 미국공개특허 제2006-0180851호에 각각 게재되어 있으며, 이 출원의 레퍼런스로 포함될 것이다. 소오스/드레인이 없는 플래시 구조는 대한민국특허 제673020호에 게재되어 있으며, 이 출원의 레퍼런스로 포함될 것이다.

- 본 발명에 따른 불 휘발성 메모리 장치 그리고/또는 메모리 제어기는 다양한 형태들의 패키지를 이용하여 실장될 수 있다. 예를 들면, 본 발명에 따른 플래시 메모리 장치 그리고/또는 메모리 컨트롤러는 PoP(Package on Package), Ball grid arrays(BGAs), Chip scale packages(CSPs), Plastic Leaded Chip Carrier(PLCC), Plastic Dual In-Line Package(PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board(COB), Ceramic Dual In-Line Package(CERDIP), Plastic Metric Quad Flat Pack(MQFP), Thin Quad Flatpack(TQFP), Small Outline(SOIC), Shrink Small Outline Package(SSOP), Thin Small Outline(TSOP), System In Package(SIP), Multi Chip Package(MCP), Wafer-level Fabricated Package(WFP), Wafer-Level Processed Stack Package(WSP), 등과 같은 패키지들을 이용하여 실장될 수 있다.

- [0076] 본 발명의 범위 또는 기술적 사상을 벗어나지 않고 본 발명의 구조가 다양하게 수정되거나 변경될 수 있음은 이 분야에 숙련된 자들에게 자명하다. 상술한 내용을 고려하여 볼 때, 만약 본 발명의 수정 및 변경이 아래의 청구항들 및 동등물의 범주 내에 속한다면, 본 발명이 이 발명의 변경 및 수정을 포함하는 것으로 여겨진다.

### 부호의 설명

[0077] 1000: 메모리 시스템

1200: 메모리 제어기

1400: 불 휘발성 메모리 장치

# 도면1