(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6243000号

(P6243000)

(45) 発行日 平成29年12月6日(2017.12.6)

(24) 登録日 平成29年11月17日(2017.11.17)

(51) Int.Cl.

G06F 17/16 (2006.01)

G06F 9/38 (2006.01)

F 1

G06F 17/16

G06F 9/38S

310G

請求項の数 28 (全 40 頁)

(21) 出願番号 特願2016-500908 (P2016-500908)

(86) (22) 出願日 平成26年3月7日 (2014.3.7)

(65) 公表番号 特表2016-517570 (P2016-517570A)

(43) 公表日 平成28年6月16日 (2016.6.16)

(86) 國際出願番号 PCT/US2014/022162

(87) 國際公開番号 WO2014/164367

(87) 國際公開日 平成26年10月9日 (2014.10.9)

審査請求日 平成29年2月3日 (2017.2.3)

(31) 優先権主張番号 13/798,641

(32) 優先日 平成25年3月13日 (2013.3.13)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】マルチモードベクトル処理を提供するためのプログラム可能データ経路構成を有するベクトル処理エンジン、ならびに関連ベクトルプロセッサ、システム、および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ベクトルデータのマルチモードベクトル処理を行うように構成されたベクトル処理エンジン(VPE)であって、

複数の入力データ経路中で、複数のベクトルデータ入力サンプルセットを与えるように構成された入力読み取り段と、

複数のベクトル処理ブロックを備える少なくとも1つのベクトル処理段と、前記複数のベクトル処理ブロックの中の各ベクトル処理ブロックは、

前記複数の入力データ経路の中の少なくとも2つの入力データ経路から、前記複数のベクトルデータ入力サンプルセットからの少なくとも2つのベクトルデータ入力サンプルセットを受信し、

前記少なくとも1つのベクトル処理段によって実行されるベクトル命令に従って、前記ベクトル処理ブロック用のプログラム可能データ経路構成に基づいて少なくとも1つのベクトル結果出力サンプルセットを与えるように、前記少なくとも2つのベクトルデータ入力サンプルセットを処理し、ここにおいて、前記ベクトル処理ブロックは複数の乗算器を備え、前記ベクトル処理ブロックによる前記少なくとも2つのベクトルデータ入力サンプルセットの前記処理は、第1の構成における前記複数の乗算器を使用して前記少なくとも2つのベクトルデータ入力サンプルセットに対して第1の乗算演算を実施することを備え、前記プログラム可能データ経路構成は、第2の乗算演算を実施するために前記複数の乗算器を第2の構成に再構成するように、プログラム可能に構成され、前記第1の乗算演

10

20

算と前記第2の乗算演算は、異なるビット長の乗算演算である。

複数の出力データ経路の中の少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される。

前記複数のベクトル処理ブロックの各々から前記少なくとも1つのベクトル結果出力サンプルセットを受信するように構成された出力処理段と、

を備えるVPE。

#### 【請求項2】

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理段によって実行される各ベクトル命令用に再構成されるように構成される、請求項1に記載のVPE。 10

#### 【請求項3】

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令の各クロック周期ごとに、クロック周期単位で再構成されるように構成される、請求項1に記載のVPE。

#### 【請求項4】

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、プログラム可能入力データ経路構成からなり、

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記プログラム可能入力データ経路構成に基づいて前記複数の入力データ経路の中の前記少なくとも2つの入力データ経路から前記少なくとも2つのベクトルデータ入力サンプルセットを受信するように構成される、請求項1に記載のVPE。 20

#### 【請求項5】

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、さらに、前記少なくとも1つのベクトル処理ブロック用のプログラム可能出力データ経路構成からなり、

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記プログラム可能出力データ経路構成に基づいて前記複数の出力データ経路の中の前記少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される、請求項4に記載のVPE。 30

#### 【請求項6】

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、さらに、前記少なくとも1つのベクトル処理ブロック用のプログラム可能ベクトル処理ブロックデータ経路構成からなり、

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記プログラム可能ベクトル処理ブロックデータ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与えるために、前記少なくとも2つのベクトルデータ入力サンプルセットを処理するように構成される、請求項5に記載のVPE。 40

#### 【請求項7】

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理ブロック用のプログラム可能出力データ経路構成からなり、

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記プログラム可能出力データ経路構成に基づいて前記複数の出力データ経路の中の前記少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される、請求項1に記載のVPE。 50

**【請求項 8】**

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理ブロック用のプログラム可能ベクトル処理ブロックデータ経路構成からなり、

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記プログラム可能ベクトル処理ブロックデータ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与えるために、前記少なくとも2つのベクトルデータ入力サンプルセットを処理するように構成される、請求項1に記載のVPE。

**【請求項 9】**

10

前記少なくとも1つのベクトル処理ブロックは、少なくとも1つの乗算器ブロックおよび少なくとも1つの累算器ブロックのうちの少なくとも1つからなる、請求項1に記載のVPE。

**【請求項 10】**

前記少なくとも1つのベクトル処理段は、複数のベクトル処理段からなる、請求項1に記載のVPE。

**【請求項 11】**

前記少なくとも1つのベクトル処理段は、複数の乗算器ブロックからなる少なくとも1つの乗算ベクトル処理段および複数の累算器ブロックからなる少なくとも1つの累算ベクトル処理段からなり、

20

前記複数の乗算器ブロックの中の各乗算器ブロックは、

前記複数のベクトルデータ入力サンプルセットからの第1のベクトルデータ入力サンプルセットと第2のベクトルデータ入力サンプルセットとを、前記複数の入力データ経路の中の第1の入力データ経路および第2の入力データ経路から受信し、

前記少なくとも1つの第1のベクトル処理段によって実行されるベクトル命令に従って、前記乗算器ブロック用のプログラム可能乗算データ経路構成に基づいて複数の乗算出力データ経路の中のある乗算出力データ経路中でベクトル乗算出力サンプルセットを与るために、前記第1のベクトルデータ入力サンプルセットを前記第2のベクトルデータ入力サンプルセットに乗算するように構成され、

前記複数の累算器ブロックの中の各累算器ブロックは、

30

複数の乗算出力データ経路の中の第1の乗算出力データ経路および第2の乗算出力データ経路から、それぞれ、第1の乗算出力サンプルセットと第2の乗算出力サンプルセットとを受信し、

少なくとも1つの第2のベクトル処理段によって実行されるベクトル命令に従って、前記累算器ブロック用のプログラム可能データ経路構成に基づいてベクトル累算結果サンプルセットを与るために、前記第1の乗算出力サンプルセットを前記第2の乗算出力サンプルセットと累算し、

前記複数の出力データ経路の中の前記出力データ経路中で前記ベクトル累算結果サンプルセットを与える

ように構成される、請求項1に記載のVPE。

40

**【請求項 12】**

前記少なくとも1つのベクトル処理ブロックは、前記少なくとも1つのベクトル結果出力サンプルセットをベクトルレジスタに記憶するように構成されない、請求項1に記載のVPE。

**【請求項 13】**

各ベクトル処理ブロックは、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて異なるビット幅の前記複数のベクトルデータ入力サンプルセットを処理するようにさらに構成される、請求項1に記載のVPE。

**【請求項 14】**

50

各ベクトル処理ブロックは、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて符号付きの少なくとも1つのベクトルデータ入力サンプルセットまたは符号なしの少なくとも1つのベクトルデータ入力サンプルセットを処理するようにさらに構成される、請求項1に記載のVPE。

#### 【請求項15】

前記少なくとも1つのベクトル処理段は、符号付きの演算命令からなる前記ベクトル命令を実行するように構成される、請求項1に記載のVPE。

#### 【請求項16】

前記少なくとも1つのベクトル処理段は、符号なし演算命令からなる前記ベクトル命令を実行するように構成される、請求項1に記載のVPE。 10

#### 【請求項17】

ベクトルデータのマルチモードベクトル処理を行うように構成されたベクトル処理エンジン(VPE)であって、

複数の入力データ経路中で、複数のベクトルデータ入力サンプルセットを与えるように構成された入力読み取り段手段と、

複数のベクトル処理手段を備える少なくとも1つのベクトル処理段手段と、前記複数のベクトル処理手段の中の各ベクトル処理手段は、

前記複数の入力データ経路の中の少なくとも2つの入力データ経路から、前記複数のベクトルデータ入力サンプルセットからの少なくとも2つのベクトルデータ入力サンプルセットを受信し、 20

前記少なくとも1つのベクトル処理段手段によって実行されるベクトル命令に従って、前記ベクトル処理手段用のプログラム可能データ経路構成に基づいて少なくとも1つのベクトル結果出力サンプルセットを与えるように、前記少なくとも2つのベクトルデータ入力サンプルセットを処理し、ここにおいて、前記ベクトル処理手段は複数の乗算器を備え、前記ベクトル処理手段による前記処理は、第1の構成における前記複数の乗算器を使用して前記少なくとも2つのベクトルデータ入力サンプルセットに対して第1の乗算演算を実施することを備え、前記プログラム可能データ経路構成は、第2の乗算演算を実施するために前記複数の乗算器を第2の構成に再構成するように、プログラム可能に構成され、前記第1の乗算演算と前記第2の乗算演算は、異なるビット長の乗算演算である。 30

複数の出力データ経路の中の少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される、

前記複数のベクトル処理手段の各々から前記少なくとも1つのベクトル結果出力サンプルセットを受信するように構成された出力処理手段と、

を備えるVPE。

#### 【請求項18】

ベクトル処理エンジン(VPE)中でベクトルデータを処理する方法であって、

入力処理段中の複数の入力データ経路中で、複数のベクトルデータ入力サンプルセットを与えることと、

少なくとも1つのベクトル処理段中の複数のベクトル処理ブロックにおいて、前記複数のベクトルデータ入力サンプルセットを処理することと、前記複数のベクトル処理ブロックの各々において、 40

前記複数の入力データ経路の中の少なくとも2つの入力データ経路から、前記複数のベクトルデータ入力サンプルセットからの少なくとも2つのベクトルデータ入力サンプルセットを受信することと、

前記少なくとも1つのベクトル処理段によって実行されるベクトル命令に従って、前記ベクトル処理ブロック用のプログラム可能データ経路構成に基づいて少なくとも1つのベクトル結果出力サンプルセットを与えるように、前記少なくとも2つのベクトルデータ入力サンプルセットを処理することと、ここにおいて、前記ベクトル処理ブロックは複数の乗算器を備え、前記少なくとも2つのベクトルデータ入力サンプルセットを処理するこ 50

とは、第1の構成における前記複数の乗算器を使用して前記少なくとも2つのベクトルデータ入力サンプルセットに対して第1の乗算演算を実施することを備える、

複数の出力データ経路の中の少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えることと、を備える、

出力処理段中の前記複数のベクトル処理ブロックの各々から前記少なくとも1つのベクトル結果出力サンプルセットを受信することと、

第2の乗算演算を実施するために前記ベクトル処理ブロックの前記複数の乗算器を第2の構成に再構成するように前記複数の処理ブロックの各々用の前記プログラム可能データ経路構成を再構成することと、ここにおいて、前記第1の乗算演算と前記第2の乗算演算は、異なるビット長の乗算演算である、

を備える方法。

#### 【請求項19】

前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記プログラム可能入力データ経路構成に基づいて前記複数の入力データ経路の中の前記少なくとも2つの入力データ経路から前記複数のベクトルデータ入力サンプルセットからの前記少なくとも2つのベクトルデータ入力サンプルセットを受信することと、

前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能入力データ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与えるように前記少なくとも1つのベクトルデータ入力サンプルセットを処理することと、を備える、請求項18に記載の方法。

#### 【請求項20】

前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、プログラム可能出力データ経路構成に基づいて前記複数の出力データ経路の中の前記少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを受信することを備える、請求項18に記載の方法。

#### 【請求項21】

前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用のプログラム可能ベクトル処理ブロックデータ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与えるように前記少なくとも2つのベクトルデータ入力サンプルセットを処理することを備える、請求項18に記載の方法。

#### 【請求項22】

最小の1つのベクトル結果出力サンプルセットをベクトルレジスタに記憶しないことをさらに備える、請求項18に記載の方法。

#### 【請求項23】

前記少なくとも2つのベクトルデータ入力サンプルセットを処理することは、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて異なるビット幅の前記複数のベクトルデータ入力サンプルセットを処理することを備える、請求項18に記載の方法。

#### 【請求項24】

前記少なくとも2つのベクトルデータ入力サンプルセットを処理することは、前記少なくとも1つのベクトル処理段によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて符号付きの少なくとも1つのベクトルデータ入力サンプルセットまたは符号なしの少なくとも1つのベクトルデータ入力サンプルセットを処理することを備える、請求項18に記載の方法。

#### 【請求項25】

前記ベクトル処理ブロックの各々において前記少なくとも2つのベクトルデータ入力サンプルセットを処理することは、

10

20

30

40

50

前記少なくとも 2 つのデータ入力サンプルセットに対して実施された前記第 1 の乗算演算によって与えられた乗算サンプルセットを、以前に与えられた乗算サンプルセットに加算することをさらに備える、請求項 1 8 に記載の方法。

**【請求項 2 6】**

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも 1 つのベクトル処理段によって実行される前記ベクトル命令に従って、2 つの 8 ビット × 8 ビット乗算器または 1 つの 16 × 16 ビット乗算器を形成するように前記複数の乗算器を構成するようにプログラムされる、請求項 1 に記載の VPE。

**【請求項 2 7】**

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも 1 つのベクトル処理段によって実行される前記ベクトル命令に従って、1 つの 16 ビット × 16 ビット乗算器または 1 つの 24 ビット × 8 ビット乗算器を形成するように前記複数の乗算器を構成するようにプログラムされる、請求項 1 に記載の VPE。10

**【請求項 2 8】**

前記複数のベクトル処理ブロックの各々は、前記複数の入力データ経路の中の前記入力データ経路のうちの少なくとも 4 つから、前記複数のベクトルデータ入力サンプルセットからの少なくとも 4 つのベクトルデータ入力サンプルセットを受信し、前記複数のベクトル処理ブロックの各々の前記複数の乗算器は、第 1 および第 2 の乗算器を備え、前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、

前記第 1 の乗算器の第 1 の入力に前記少なくとも 4 つのベクトル入力サンプルセットのうちの第 1 のベクトル入力サンプルセットを入力し、20

前記少なくとも 1 つのベクトル処理段によって実行される前記ベクトル命令に従って、前記第 1 の乗算器の第 2 の入力に、前記少なくとも 4 つのベクトルデータ入力サンプルセットのうちの第 2 のベクトルデータ入力サンプルセット、または前記少なくとも 4 つのベクトルデータ入力サンプルセットのうちの第 3 のベクトルデータ入力サンプルセットを入力し、

前記第 2 の乗算器の第 1 の入力に前記少なくとも 4 つのベクトル入力サンプルセットのうちの第 4 のベクトル入力サンプルセットを入力し、

前記少なくとも 1 つのベクトル処理段によって実行される前記ベクトル命令に従って、前記第 2 の乗算器の第 2 の入力に、前記少なくとも 4 つのベクトルデータ入力サンプルセットのうちの前記第 2 のベクトルデータ入力サンプルセット、または前記少なくとも 4 つのベクトルデータ入力サンプルセットのうちの前記第 3 のベクトルデータ入力サンプルセットを入力する。30

ように構成される、請求項 1 に記載の VPE。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

**関連出願**

[0001] 本出願は、2013年3月13日に出願し、参照によってその全体が本明細書に組み込まれている、「Vector Processing Engines Having Programmable Data Path Configurations For Providing Multi-Mode Radix-2<sup>X</sup> Butterfly Vector Processing Circuits, And Related Vector Processors, Systems, And Methods」と題する米国特許出願第13/798,599号(Quacomm 整理番号123247)に関連する。40

**【0002】**

[0002] 本出願は、2013年3月13日に出願し、参照によってその全体が本明細書に組み込まれている、「Vector Processing Carry-Save Accumulators Employing Redundant Carry-S」50

ave Format To Reduce Carry Propagation, And Related Vector Processors, Systems, And Methods」と題する米国特許出願第13/798,618号(Qua1comm整理番号123248)にも関連する。

#### 【0003】

[0003] 本開示の分野は、単一命令多重データ(SIMD)プロセッサと多重命令多重データ(MIMD)プロセッサを含む、ベクトルおよびスカラー演算を処理するためのベクトルプロセッサおよび関連システムに関する。

#### 【背景技術】

#### 【0004】

[0004] ワイヤレスコンピューティングシステムは、デジタル情報領域において最も普及した技術の1つに急速になりつつある。技術の進歩により、ワイヤレス通信デバイスは、より小型でより強力になった。たとえば、ワイヤレスコンピューティングデバイスは一般に、小型で軽量な、ユーザが容易に持ち運べるポータブルワイヤレス電話、携帯情報端末(PDA)、およびページングデバイスを含む。より具体的には、セルラー電話およびインターネットプロトコル(IP)電話などのポータブルワイヤレス電話は、ワイヤレスネットワークを介して音声およびデータパケットを通信することができる。さらに、多くのそのようなワイヤレス通信デバイスが、他のタイプのデバイスを含む。たとえば、ワイヤレス電話機は、デジタルスチルカメラ、デジタルビデオカメラ、デジタルレコーダ、および/またはオーディオファイルプレーヤを含み得る。また、ワイヤレス電話は、インターネットにアクセスするために使用できるウェブインターフェースを含むことができる。さらに、ワイヤレス通信デバイスは、設計されたワイヤレス通信技術規格(たとえば、符号分割多元接続(CDMA)、広帯域CDMA(WCDMA(登録商標))、およびロングタームエボリューション(LTE(登録商標)))に従って高速ワイヤレス通信データを処理するための複合処理リソースを含み得る。したがって、これらのワイヤレス通信デバイスはかなりのコンピューティング能力を含む。

#### 【0005】

[0005] ワイヤレスコンピューティングデバイスは、より小型でより強力になるにつれて、ますますリソースの制約を受けるようになる。たとえば、画面サイズ、利用可能なメモリおよびファイルシステム空間の量、ならびに入出力能力の量は、小さいデバイスのサイズによって制限されることがある。さらに、電池サイズ、電池によって供給される電力の量、および電池の寿命も制限される。デバイスのバッテリ寿命を増すための1つのやり方は、より少ない電力を消費するプロセッサを設計することである。

#### 【0006】

[0006] この点において、ベクトルプロセッサを含むベースバンドプロセッサが、ワイヤレス通信デバイス用に利用され得る。ベクトルプロセッサは、ベクトル、すなわちデータアレイに働きかけるハイレベル演算を提供するベクトルアーキテクチャを有する。ベクトル処理は、ベクトル命令を一度フェッチすることと、次いで、1つのデータセットに対してベクトル命令を実行し、次いで、ベクトル内の後続要素のためにベクトル命令をフェッチし直し、復号するのとは反対に、データ要素アレイ全体にわたってベクトル命令を複数回実行することとを伴う。このプロセスにより、他の要因の中でも、各ベクトル命令は、より少ない回数しかフェッチされる必要がないので、プログラムを実行するのに必要とされるエネルギーが低減される。ベクトル命令は、同時に複数のクロック周期にわたって長いベクトルに対して動作するので、簡易な順序ベクトル命令ディスパッチを用いて、高度の並列性が達成可能である。

#### 【0007】

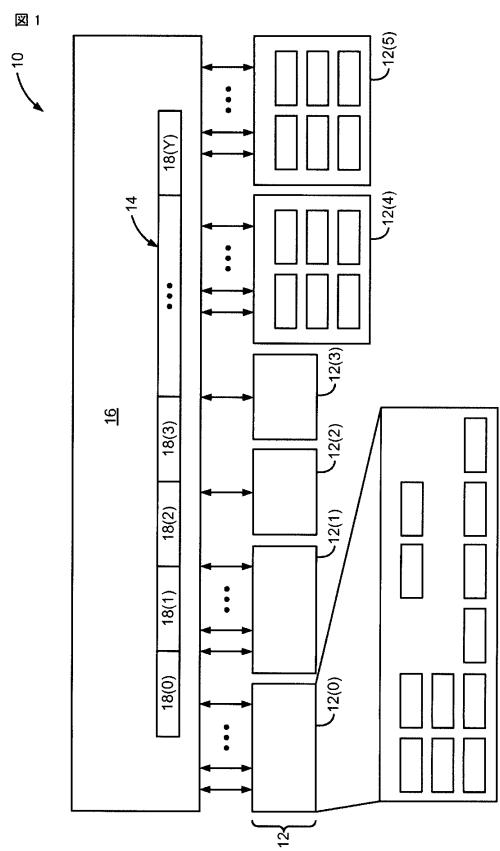

[0007] 図1は、ワイヤレスコンピュータデバイスなどのコンピューティングデバイス中で利用され得る例示的なベースバンドプロセッサ10を示す。ベースバンドプロセッサ10は、特定のアプリケーション用の関数固有ベクトル処理を提供するのに各々が専用である複数の処理エンジン(PE)12を含む。この例では、6つの別個のPE12(0)

10

20

30

40

50

～12(5)がベースバンドプロセッサ10中に設けられる。P E 12(0)～12(5)は各々、共有メモリ16からP E 12(0)～12(5)に与えられる固定Xビット幅のベクトルデータ14用のベクトル処理を提供するように構成される。たとえば、ベクトルデータ14は512ビット幅であり得る。ベクトルデータ14は、Xのより小さい倍数のビット幅のベクトルデータサンプルセット18(0)～18(Y)(たとえば、16ビットおよび32ビットサンプルセット)中で定義されてもよい。このようにして、P E 12(0)～12(5)は、高度の並列性を達成するように、P E 12(0)～12(5)に並列に与えられる複数のベクトルデータサンプルセットに対するベクトル処理を提供することが可能である。各P E 12(0)～12(5)は、ベクトルデータ14上で処理されるベクトル命令の結果を記憶するためのベクトルレジスタファイル(V R)を含み得る。

10

#### 【0008】

[0008] 図1のベースバンドプロセッサ10中の各P E 12(0)～12(5)は、特定のタイプの固定演算を効率的に実施するように特に設計された、特定の専用回路要素とハードウェアとを含む。たとえば、図1のベースバンドプロセッサ10は、別個の広帯域符号分割多元接続(W C D M A)P E 12(0)、12(1)とロングタームエボリューション(L T E)P E 12(4)、12(5)とを含むが、これは、W C D M AおよびL T Eは異なるタイプの特殊な演算を伴うからである。したがって、別個のW C D M A固有P E 12(0)、12(1)とL T E固有P E 12(4)、12(5)とを設けることによって、P E 12(0)、12(1)、12(4)、12(5)の各々は、高効率な演算のための、W C D M AおよびL T E用の頻繁に実施される関数に固有である、特殊な専用回路要素を含むように設計され得る。この設計は、より多数の無関係な演算を、比較的非効率的にではあるがサポートするために柔軟であるように設計された、より一般的な回路要素とハードウェアとを含むスカラー処理エンジンとは対照的である。

20

#### 【0009】

[0009] ベースバンドプロセッサ中に関数固有P Eを設けることは、頻繁に実行される特殊な演算には有利である。ただし、関数固有P Eを設けると、別個の関数固有P Eが各々、特殊な回路要素とメモリとを含むので、ベースバンドプロセッサ用に必要とされる面積および電力が増大する場合がある。

30

#### 【発明の概要】

#### 【0010】

[0010] 本明細書で開示する実施形態は、マルチモードベクトル処理を提供するためのプログラム可能データ経路構成を有するベクトル処理エンジン(V P E)を含む。関連ベクトルプロセッサ、システム、および方法についても開示する。本明細書で開示するV P Eは、ベクトル処理段によって実行されるベクトル命令に従ってベクトルデータを処理するように構成された少なくとも1つのベクトル処理段を含む。各ベクトル処理段は、実行されるベクトル命令に基づいてベクトルデータを処理するように構成された1つまたは複数のベクトル処理ブロックを含む。ベクトル処理ブロックの非限定的例は、乗算器および累算器である。ベクトル処理ブロックは、ベクトル処理ブロックのプログラム可能データ経路構成に基づいて、異なるタイプの命令向けの異なる関数を異なるモードで行うことが可能である。このようにして、V P Eには、実行されるベクトル命令に従って、異なるタイプの関数を実行するように再プログラム可能なデータ経路構成が与えられ得る。

40

#### 【0011】

[0011] その結果、より少ないV P Eが、所望の技術特質を提供することができ、したがって、ベースバンドプロセッサ中の面積を節約するとともに、スカラー処理エンジンと比較して、より少ないレジスタ書き込みおよびより速い命令実行というベクトル処理利点を依然として保有する。ベクトル処理ブロック用のデータ経路構成はまた、V P E中で、異なる特殊なベクトル演算の実行を異なるモードでサポートするように、V P Eにおけるベクトル命令実行中にプログラムされ、再プログラムされ得る。

#### 【0012】

50

[0012] 本明細書で開示するマルチモードベクトル処理のためのプログラム可能データ経路構成を有するVPEは、固定関数を提供するための固定データ経路構成を含むだけであるVPEとは区別可能である。本明細書で開示するベクトル処理のためのプログラム可能データ経路構成を有するVPEは、たとえばデジタル信号プロセッサ(DSP)中に設けられるようなスカラー処理エンジンとも区別可能である。スカラー処理エンジンは、異なるタイプの非固定関数を実施するが、ベクトル命令実行中の中間結果もレジスタファイルに書き込むための柔軟な共通回路要素と論理とを利用し、そうすることによって、追加電力を消費し、ベクトル命令実行回数を増大させる。

#### 【0013】

[0013] この点について、一実施形態では、VPEが提供される。VPEは、ベクトルデータのマルチモードベクトル処理を行うように構成される。VPEは、複数の入力データ経路の中のある入力データ経路中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセットを与えるように構成された入力読み取り段を備える。VPEは、複数のベクトル処理ブロックを備える少なくとも1つのベクトル処理段も備える。複数のベクトル処理ブロックの中の各ベクトル処理ブロックは、複数の入力データ経路の中の少なくとも1つの入力データ経路から、複数のベクトルデータ入力サンプルセットからの少なくとも1つのベクトルデータ入力サンプルセットを受信するように構成される。複数のベクトル処理ブロックの中の各ベクトル処理ブロックは、少なくとも1つのベクトル処理段によって実行されるベクトル命令に従って、各ベクトル処理ブロック用のプログラム可能データ経路構成に基づいて、少なくとも1つのベクトル結果出力サンプルセットを与えるように、少なくとも1つのベクトルデータ入力サンプルセットを処理するようにさらに構成される。複数のベクトル処理ブロックの中の各ベクトル処理ブロックは、複数の出力データ経路の中の少なくとも1つの出力データ経路中で少なくとも1つのベクトル結果出力サンプルセットを与えるようにさらに構成される。VPEは、複数のベクトル処理ブロックの各々から少なくとも1つのベクトル結果出力サンプルセットを受信するように構成された出力処理段も備える。

#### 【0014】

[0014] 別の実施形態では、ベクトルデータのマルチモードベクトル処理を行うように構成されたVPEが提供される。VPEは、複数の入力データ経路の中のある入力データ経路中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセットを与えるように構成された入力読み取り段手段を備える。VPEは、少なくとも1つのベクトル処理段手段も備える。少なくとも1つのベクトル処理段手段は、複数のベクトル処理手段を備える。複数のベクトル処理手段の中の各ベクトル処理手段は、複数の入力データ経路の中の少なくとも1つの入力データ経路から、複数のベクトルデータ入力サンプルセットからの少なくとも1つのベクトルデータ入力サンプルセットを受信するように構成される。複数のベクトル処理手段の中の各ベクトル処理手段は、少なくとも1つのベクトル処理段によって実行されるベクトル命令に従って、各ベクトル処理ブロック用のプログラム可能データ経路構成に基づいて、少なくとも1つのベクトル結果出力サンプルセットを与えるように、少なくとも1つのベクトルデータ入力サンプルセットを処理するようにさらに構成される。複数のベクトル処理手段の中の各ベクトル処理手段は、複数の出力データ経路の中の少なくとも1つの出力データ経路中で少なくとも1つのベクトル結果出力サンプルセットを与えるようにさらに構成される。VPEは、複数のベクトル処理手段の各々から少なくとも1つのベクトル結果出力サンプルセットを受信するように構成された出力処理手段も備える。

#### 【0015】

[0015] 別の実施形態では、ベクトル処理エンジン(VPE)中でベクトルデータを処理する方法が提供される。この方法は、入力処理段中の複数の入力データ経路の中のある入力データ経路中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセットを与えることを備える。方法は、少なくとも1つのベクトル処理段中の複数のベクトル処理ブロックにおいて、複数のベクトルデータ入力サンプルセットを処理することも備える。

10

20

30

40

50

方法は、複数のベクトル処理ブロックの各々において、複数の入力データ経路の中の少なくとも1つの入力データ経路から、複数のベクトルデータ入力サンプルセットからの少なくとも1つのベクトルデータ入力サンプルセットを受信すること、少なくとも1つのベクトル処理段によって実行されるベクトル命令に従って、各ベクトル処理ブロック用のプログラム可能データ経路構成に基づいて、少なくとも1つのベクトル結果出力サンプルセットを与えるように、少なくとも1つのベクトルデータ入力サンプルセットを処理することも備える。方法は、複数の出力データ経路の中の少なくとも1つの出力データ経路で少なくとも1つのベクトル結果出力サンプルセットを与えることをさらに備える。方法は、出力処理段中の複数のベクトル処理ブロックの各々から少なくとも1つのベクトル結果出力サンプルセットを受信することも備える。

10

#### 【0016】

[0016] 別の実施形態では、ベクトルプロセッサが提供される。ベクトルプロセッサは、ベクトルデータメモリからベクトルデータ入力サンプルセットを受信するように構成された少なくとも1つのベクトルレジスタを備える。ベクトルプロセッサは、ベクトル結果出力サンプルセットを記憶するように構成された少なくとも1つのベクトル結果レジスタも備える。ベクトルプロセッサは、複数のベクトル処理段を備える少なくとも1つのVPEも備える。複数のベクトル処理段は各々、少なくとも1つのベクトルレジスタから少なくとも1つのベクトルデータ入力サンプルセットを受信し、少なくとも1つのベクトルレジスタからの少なくとも1つのベクトルデータ入力サンプルセットを、各ベクトル処理段によって実行されるベクトル命令に従って、ベクトル処理段の各々のための少なくとも1つのデータ経路構成に基づいて、少なくとも1つのベクトル結果出力サンプルセットに処理し、少なくとも1つのベクトル結果出力サンプルセットを、少なくとも1つのベクトル結果レジスタに記憶されるように、少なくとも1つのベクトルレジスタに与えるように構成される。

20

#### 【図面の簡単な説明】

#### 【0017】

【図1】[0017] 固有アプリケーション向けの関数固有ベクトル処理を提供するのに各々が専用である、複数のベクトル処理エンジン（VPE）を含む例示的なベクトルプロセッサの配線図。

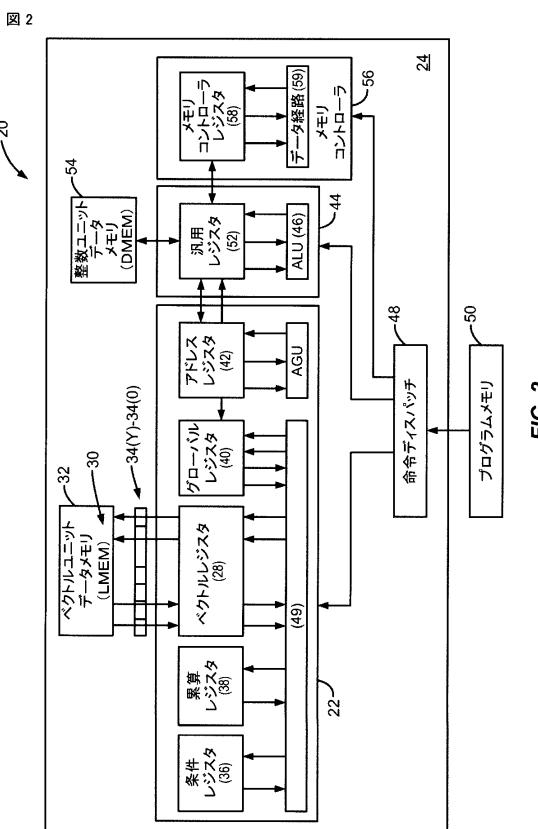

【図2】[0018] VPE中に設けられた共通回路要素およびハードウェアが、別個のVPEを設ける必要なく、複数のアプリケーションまたは技術のために特定のタイプのベクトル演算を高効率的に実施するための複数のモードでプログラムされ得るように、プログラム可能データ経路構成を有する共通VPEを含む例示的なベクトルプロセッサの配線図。

30

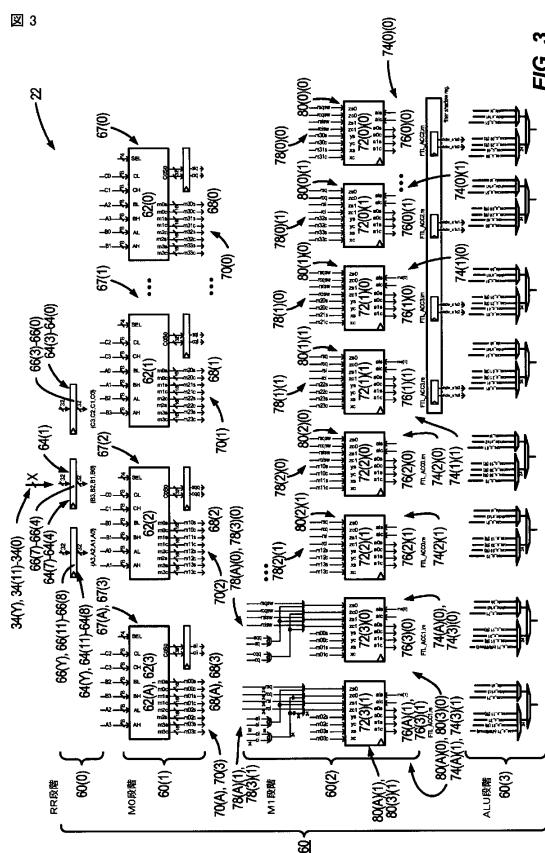

【図3】[0019] 図2のVPEに設けられる例示的なベクトル処理段の配線図であって、ベクトル処理段のうちのいくつかは、プログラム可能データ経路構成を有する例示的なベクトル処理ブロックを含む。

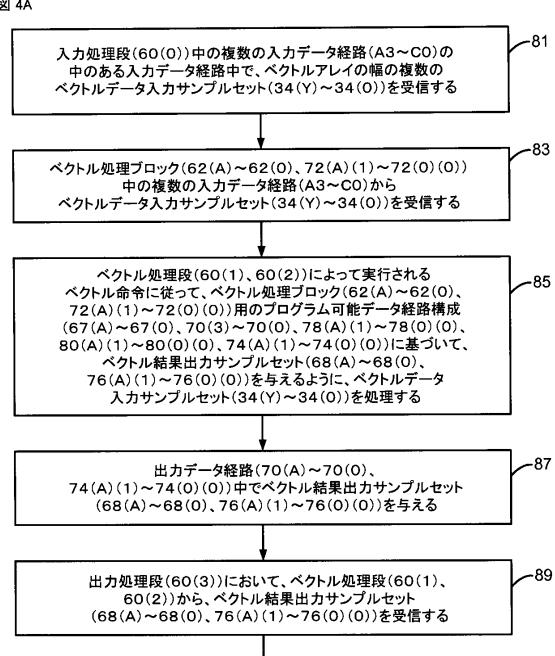

【図4A】[0020] 図2および図3の例示的なベクトルプロセッサ中に含まれるプログラム可能データ経路構成を有する少なくとも1つのベクトル処理ブロックの例示的なベクトル処理を示すフローチャート。

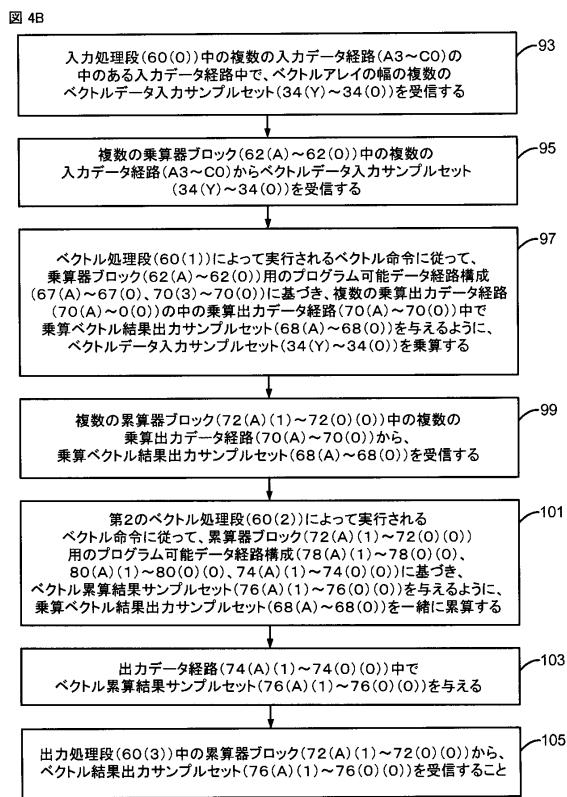

【図4B】[0021] プログラム可能データ経路構成を各々が有するとともに、図2および図3の例示的なベクトルプロセッサにおける異なるベクトル処理段において提供される乗算器ブロックおよび累算器ブロックの例示的なベクトル処理を示すフローチャート。

40

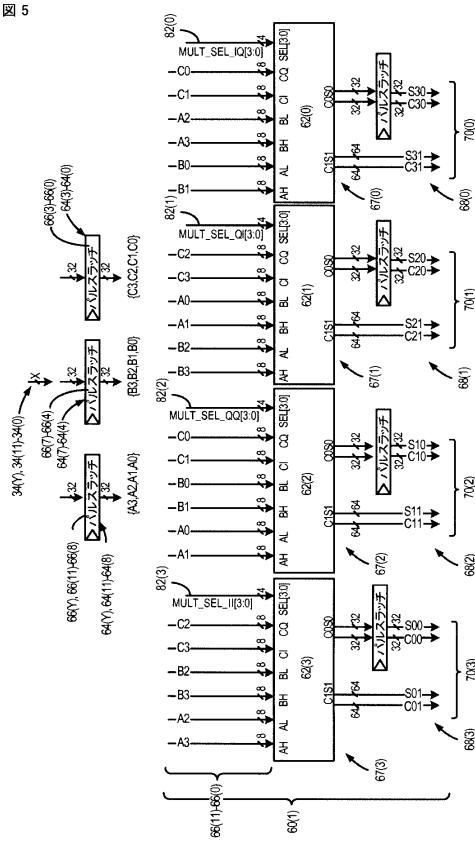

【図5】[0022] 図2および図3のVPEのベクトル処理段に設けられる複数の乗算器ブロックのより詳細な配線図であって、複数の乗算器ブロックは各々、複数の乗算器ブロックが、特定の異なるタイプのベクトル乗算演算を実施するための複数のモードでプログラムされ得るように、プログラム可能データ経路構成を有する。

【図6】[0023] 8ビット×8ビットベクトルデータ入力サンプルセットおよび16ビット×16ビットベクトルデータ入力サンプルセットについての乗算演算を行うようにプログラムされることが可能なプログラム可能データ経路構成を有する、図5の複数の乗算器ブロックの中のある乗算器ブロックの内部構成要素の配線図。

50

【図7】[0024] 図2および図3のVPE中の乗算器ブロックおよび累算器ブロックの一般化配線図であって、累算器ブロックは、桁上げ伝搬を低減するのに冗長桁上げ保存フォーマットを利用する桁上げ保存累算器構造を利用する。

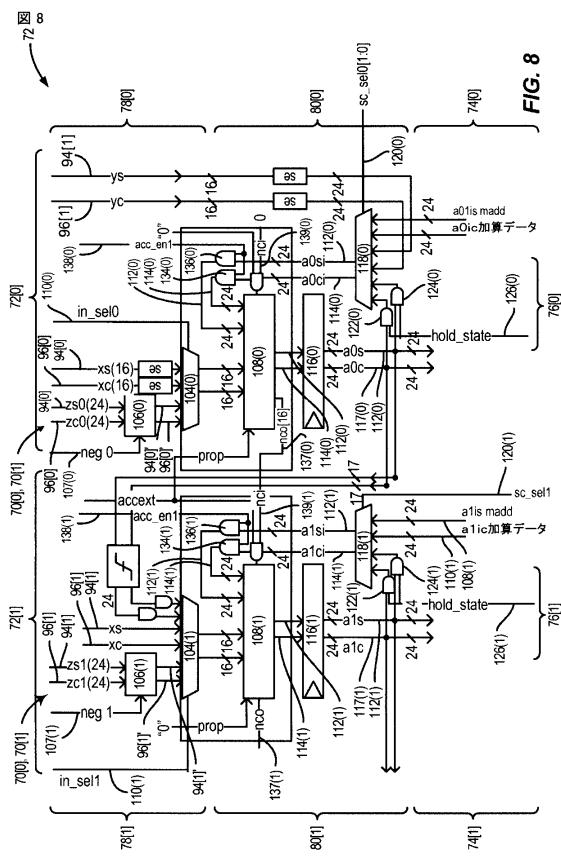

【図8】[0025] 図2および図3のVPE中に設けられる、図7の累算器ブロックの例示的な内部構成要素の詳細な配線図であって、累算器ブロックが、冗長桁上げ保存フォーマットで、特定の異なるタイプのベクトル累算演算を実施するための複数のモードでプログラムされ得るように、累算器ブロックはプログラム可能データ経路構成を有する。

【図9A】[0026] 二重24ビット累算器モードを提供するためにプログラムされたデータ経路構成を有する図8の累算器ブロックの配線図。

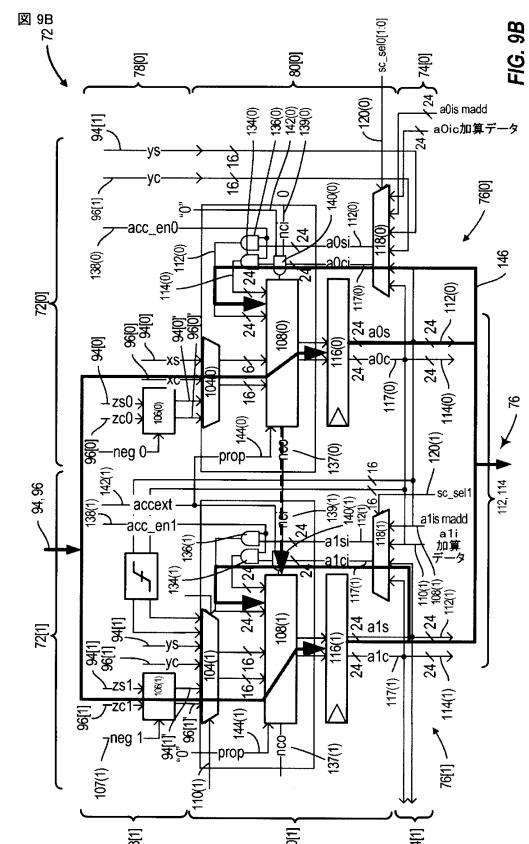

【図9B】[0027] 単一40ビット累算器モードを提供するためにプログラムされたデータ経路構成を有する図8の累算器ブロックの配線図。 10

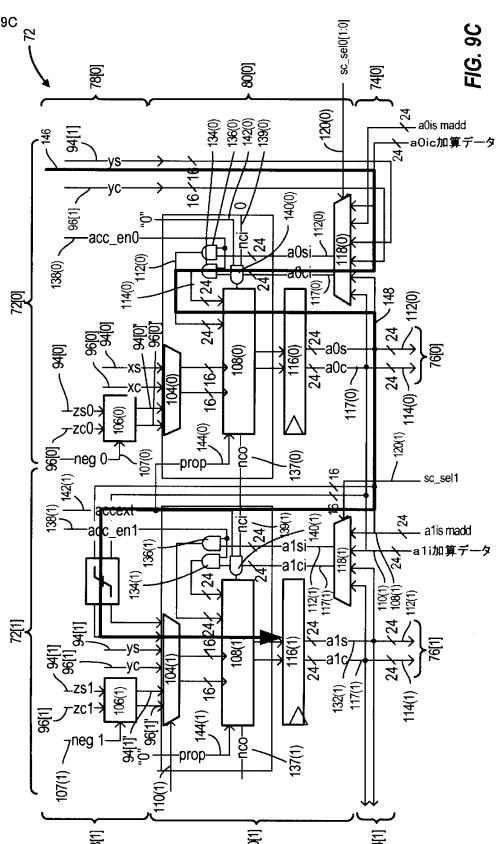

【図9C】[0028] 16ビット桁上げ保存加算器と、それに続く単一24ビット累算器モードを提供するためにプログラムされたデータ経路構成を有する図8の累算器ブロックの配線図。 20

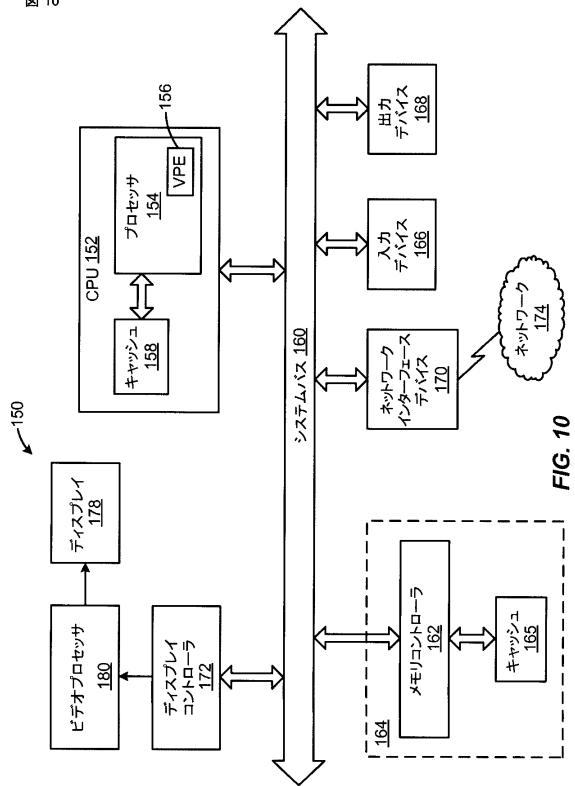

【図10】[0029] 本明細書で開示する実施形態による、プログラム可能データ経路構成を有するVPEを含むベクトルプロセッサを含むことができ、したがってVPE中の共通回路要素およびハードウェアが、別個のVPEを提供する必要なく、複数のアプリケーションまたは技術のために特定のタイプのベクトル演算を高効率的に実施するように設計された専用回路要素として作用するようにプログラムされ得る、例示的なプロセッサベースのシステムのブロック図。 20

#### 【発明を実施するための形態】

##### 【0018】

[0030] ここで図面を参照すると、本開示のいくつかの例示的な実施形態が記載される。「例示的な」という言葉は、本明細書中で、「例、事例、または例示として働くこと」を意味するように使用される。本明細書で「例示的な」として記載される任意の実施形態は、必ずしも、他の実施形態よりも好ましいまたは有利であると解釈されるべきでない。 30

##### 【0019】

[0031] 本明細書で開示する実施形態は、マルチモードベクトル処理を提供するためのプログラム可能データ経路構成を有するベクトル処理エンジン(VPE)を含む。関連ベクトルプロセッサ、システム、および方法についても開示する。本明細書で開示するVPEは、ベクトル処理段によって実行されるベクトル命令に従ってベクトルデータを処理するように構成された少なくとも1つのベクトル処理段を含む。各ベクトル処理段は、実行されるベクトル命令に基づいてベクトルデータを処理するように構成された1つまたは複数のベクトル処理ブロックを含む。ベクトル処理ブロックの非限定的例は、乗算器および累算器である。ベクトル処理ブロックは、ベクトル処理ブロックのデータ経路構成に基づいて、異なるタイプの命令向けの異なるベクトル演算を異なるモードで行うことが可能である。ベクトル処理ブロックのデータ経路構成は、実行される特定のベクトル命令に従って、異なるモードで特殊なベクトル処理演算を行うためにベクトルデータを異なるやり方で処理するようにプログラム可能であり、再プログラム可能であり(すなわち、再配線され)得る。 40

##### 【0020】

[0032] このようにして、VPEには、実行されるベクトル命令に従って異なるタイプのベクトル演算を実行するように再プログラム可能なデータ経路構成が与えられ得る。その結果、より少ないVPEが、ベクトルプロセッサ中で所望のベクトル処理演算を行うことができ、したがって、ベクトルプロセッサにおける面積を節約するとともに、スカラー処理エンジンに勝る、より少ないレジスタ書き込みおよびより速いベクトル命令実行回数というベクトル処理利点を依然として保有する。ベクトル処理ブロック用のデータ経路構成はまた、VPE中で、異なる特殊なベクトル演算の実行を異なるモードでサポートするように、VPEにおけるベクトル命令実行中にプログラムされ、再プログラムされ得る。

##### 【0021】

50

20

30

40

50

[0033] 本明細書で開示するマルチモードベクトル処理のためのプログラム可能データ経路構成を有するVPEは、固定関数を提供するための固定データ経路構成を含むだけであるVPEとは区別可能である。本明細書で開示するベクトル処理のためのプログラム可能データ経路構成を有するVPEは、たとえばデジタル信号プロセッサ(DSP)中に設けられるようなスカラー処理エンジンとも区別可能である。スカラー処理エンジンは、異なるタイプの非固定関数を実施するが、ベクトル命令実行中の中間結果もレジスタファイルに書き込むための柔軟な共通回路要素と論理とを利用し、そうすることによって、追加電力を消費し、ベクトル命令実行回数を増大させる。

#### 【0022】

[0034] この点において、図2は、ベクトル処理エンジン(VPE)22とも呼ばれる、例示的なベクトル処理ユニット22を含むベースバンドプロセッサ20の配線図である。<sup>10</sup> ベースバンドプロセッサ20およびそのVPE22は、半導体ダイ24中に設けられ得る。図3で始まる、後でより詳しく論じる本実施形態では、ベースバンドプロセッサ20は、プログラム可能データ経路構成を有する共通VPE22を含む。このように、VPE22は、ベースバンドプロセッサ20中に別個のVPEを設ける必要なく、異なる演算モードで異なる特定のタイプのベクトル演算を行うようにプログラムされ、再プログラムされ得る共通回路要素とハードウェアとを含む。VPE22はまた、ベースバンドプロセッサ20中に別個のVPEを設ける必要なく、複数のアプリケーションまたは技術のために、一般的な算術演算を高効率的に実施するためのベクトル算術モードでプログラムされ得る。<sup>20</sup>

#### 【0023】

[0035] 図3で始まる、ベクトルマルチモード処理のためにVPE22中に設けられるプログラム可能データ経路構成について論じる前に、図2のベースバンドプロセッサ20の構成要素について、最初に記載する。この非限定的例におけるベースバンドプロセッサ20は、512ビットベクトルプロセッサである。ベースバンドプロセッサ20は、VPE22がベースバンドプロセッサ20中でベクトル処理を行うのをサポートするための追加構成要素を、VPE22に加えて含む。ベースバンドプロセッサ20は、ベクトルユニットデータメモリ(LMEM)32からベクトルデータ30を受信し、記憶するように構成されたベクトルレジスタ28を含む。たとえば、ベクトルデータ30はXビット幅であり、「X」は、設計選択に従って定義される(たとえば、512ビット)。ベクトルデータ30は、ベクトルデータサンプルセット34に分割され得る。たとえば、ベクトルデータ30は、256ビット幅であってよく、より小さいベクトルデータサンプルセット34(Y)~34(0)を備えることができ、ここでベクトルデータサンプルセット34(Y)~34(0)の一部は16ビット幅であり、ベクトルデータサンプルセット34(Y)~34(0)のうちのそれ以外は32ビット幅である。VPE22は、高度の並列性を達成するように、VPE22に並列に与えられるいくつかの選ばれた乗算ベクトルデータサンプルセット34(Y)~34(0)に対して、ベクトル処理を行うことが可能である。ベクトルレジスタ28は、VPE22がベクトルデータ30を処理するときに生成される結果を記憶するようにも構成される。いくつかの実施形態では、VPE22は、より速いベクトル命令実行時間を可能にするようにレジスタ書き込みを低減するために、中間ベクトル処理結果をベクトルレジスタ28に記憶しないように構成される。この構成は、スカラー処理DSPなど、中間結果をレジスタに記憶するスカラー処理エンジンによって実行されるスカラー命令とは反対である。<sup>30</sup>

#### 【0024】

[0036] 図2のベースバンドプロセッサ20は、ベクトル命令の条件付き実行において使用するために、条件をVPE22に与えるように、およびアップデートされた条件をベクトル命令実行の結果として記憶するように構成された条件レジスタ36も含む。ベースバンドプロセッサ20はまた、累算レジスタ38と、グローバルレジスタ40と、アドレスレジスタ42とを含む。累算レジスタ38は、VPE22によって、累算された結果を、ベクトルデータ30に対していくつかの特殊な演算を実行した結果として記憶するのに<sup>40</sup>

使われるよう構成される。グローバルレジスタ40は、VPE22によってサポートされるいくつかのベクトル命令用のスカラーオペランドを記憶するよう構成される。アドレスレジスタ42は、ベクトルユニットデータメモリ32からベクトルデータ30を取り出し、ベクトル処理結果をベクトルユニットデータメモリ32に記憶するために、ベクトルロードによってアドレス指定可能なアドレスを記憶し、VPE22によってサポートされる命令を記憶するよう構成される。

#### 【0025】

[0037] 引き続き図2を参照すると、本実施形態におけるベースバンドプロセッサ20は、VPE22によって行われるベクトル処理に加え、ベースバンドプロセッサ20中でスカラー処理を行うためのスカラープロセッサ44（「整数ユニット」とも呼ばれる）も含む。高効率な演算のために実行される命令のタイプに基づいて、ベクトル演算とスカラーミニ演算の両方をサポートするよう構成されたCPUを設けることが所望され得る。 10

本実施形態では、スカラープロセッサ44は、非限定的例として、32ビット縮小命令セットコンピューティング（RISC）スカラープロセッサである。スカラープロセッサ44は、この例では、スカラー命令処理をサポートするための論理演算ユニット（ALU）46を含む。ベースバンドプロセッサ20は、プログラムメモリ50から命令をフェッチし、フェッチした命令を復号し、フェッチした命令を、命令タイプに基づいて、スカラープロセッサ44に、またはベクトルデータ経路49を通してVPE22に向けるように構成された命令ディスパッチ回路48を含む。 20

スカラープロセッサ44は、スカラー命令を実行するときにスカラープロセッサ44によって使用するための汎用レジスタ52を含む。スカラー命令実行のためにスカラープロセッサ44によってアクセスするために、メインメモリから汎用レジスタ52にデータを与えるように、整数ユニットデータメモリ（D MEM）54がベースバンドプロセッサ20中に含まれる。 D MEM54は、非限定的例として、キャッシュメモリであり得る。ベースバンドプロセッサ20は、メモリコントローラデータ経路59を通じ、メインメモリへのアクセスを求めるベクトル命令をスカラープロセッサ44が実行しているとき、汎用レジスタ52からメモリアドレスを受信するよう構成されたメモリコントローラレジスタ58を含むメモリコントローラ56も含む。

#### 【0026】

[0038] 図2のベースバンドプロセッサ20の例示的な構成要素について記載してきたので、共通回路要素およびハードウェアをもつ、複数の動作モードを提供するVPE22およびそのプログラム可能データ経路構成に関するさらなる詳細についてここで論じる。 30

この点において、図3は、図2のVPE22の例示的な配線図を示す。図3に示すように、および図4～図8Cにおいて以下でより詳細に説明するように、VPE22は、プログラム可能データ経路構成で構成され得る例示的なベクトル処理ブロックを有する複数の例示的なベクトル処理段60を含む。

後でより詳しく論じるように、ベクトル処理ブロック中に設けられたプログラム可能データ経路構成により、特定の回路およびハードウェアが、図2のベクトルユニットデータメモリ32から受信されたベクトルデータ30に対する異なる特定のベクトル処理演算の実施をサポートするようにプログラムされ、再プログラムされる。

#### 【0027】

[0039] たとえば、いくつかのベクトル処理演算は一般に、ベクトルデータ30の乗算、続いて、乗算されたベクトルデータ結果の累算を必要とし得る。そのようなベクトル処理の非限定的例には、ワイヤレス通信アルゴリズムのための高速フーリエ変換（FFT）演算を実施するために一般に使われる、フィルタリング演算、相関演算、ならびに基底2および基底4のバタフライ演算があり、ここで一連の並列乗算が、続いて乗算結果の一連の並列累算が行われる。 やはり図7～図9Cに関連して後でより詳しく論じるように、図2のVPE22は、桁上げ保存累算器において冗長桁上げ保存フォーマットを提供するための桁上げ保存累算器をもつ融合乗算器というオプションも有する。桁上げ保存累算器中で冗長桁上げ保存フォーマットを提供することにより、桁上げ伝搬経路と、各累算ステップ中の桁上げ伝搬加算演算とを提供する必要をなくすことができる。 40

50

## 【0028】

[0040] この点において、さらに図3を参照して、VPE22のM0乗算ベクトル処理段60(1)について最初に記載する。M0乗算ベクトル処理段60(1)は、プログラム可能データ経路構成を各々が有する、任意の所望の数の乗算器ブロック62(A)～62(0)の形の複数のベクトル処理ブロックを含む第2のベクトル処理段である。乗算器ブロック62(A)～62(0)は、VPE22中でベクトル乗算演算を実施するよう設けられる。複数の乗算器ブロック62(A)～62(0)は、最大12個の乗算ベクトルデータサンプルセット34(Y)～34(0)の乗算を行うために、M0乗算ベクトル処理段60(1)中に互いと並列に配置される。本実施形態では、「A」は3に等しく、この例では、M0乗算ベクトル処理段60(1)に4つの乗算器ブロック62(3)～62(0)が含まれることを意味する。乗算ベクトルデータサンプルセット34(Y)～34(0)は、VPE22中の第1のベクトル処理段60(0)である入力読み取り(RR)ベクトル処理段に設けられた複数のラッチ64(Y)～64(0)へのベクトル処理のためにVPE22中にロードされる。本実施形態では、VPE22中に12個のラッチ64(11)～64(0)があり、本実施形態では「Y」が11に等しいことを意味する。ラッチ64(11)～64(0)は、ベクトルレジスタ28(図2参照)から取り出された乗算ベクトルデータサンプルセット34(11)～34(0)をベクトルデータ入力サンプルセット66(11)～66(0)としてラッチするように構成される。この例では、各ラッチ64(11)～64(0)は8ビット幅である。ラッチ64(11)～64(0)は各々、乗算ベクトルデータ入力サンプルセット66(11)～66(0)を、総計96ビット幅のベクトルデータ30(すなわち、各々、12ラッチ×8ビット)を求めてラッチするようにそれぞれ構成される。10

20

## 【0029】

[0041] 引き続き図3を参照すると、複数の乗算器ブロック62(3)～62(0)は、ベクトル乗算演算を行うために、ベクトルデータ入力サンプルセット66(11)～66(0)のいくつかの組合せを受信することが可能ないように構成され、ここにおいて「Y」は、この例では11に等しい。乗算ベクトルデータ入力サンプルセット66(11)～66(0)は、VPE22の設計に従って、複数の入力データ経路A3～A0、B3～B0、およびC3～C0中で与えられる。ベクトルデータ入力サンプルセット66(3)～66(0)は、図3に示すように入力データ経路C3～C0に対応する。ベクトルデータ入力サンプルセット66(7)～66(4)は、図3に示すように入力データ経路B3～B0に対応する。ベクトルデータ入力サンプルセット66(11)～66(8)は、図3に示すように入力データ経路A3～A0に対応する。複数の乗算器ブロック62(3)～62(0)は、ベクトル乗算演算を行うために、それぞれ、受信ベクトルデータ入力サンプルセット66(11)～66(0)を、複数の乗算器ブロック62(3)～62(0)へと設けられた入力データ経路A3～A0、B3～B0、C3～C0に従って処理するように構成される。30

## 【0030】

[0042] 図4および図5に関連して後でより詳しく論じるように、図3の乗算器ブロック62(3)～62(0)中に設けられたプログラム可能内部データ経路67(3)～67(0)は、異なるデータ経路構成を有するようにプログラムされ得る。これらの異なるデータ経路構成は、各乗算器ブロック62(3)～62(0)へと設けられた特定の入力データ経路A3～A0、B3～B0、C3～C0に従って乗算器ブロック62(3)～62(0)に与えられる特定の受信ベクトルデータ入力サンプルセット66(11)～66(0)の異なる組合せおよび/または異なるビット長の乗算を可能にする。この点において、複数の乗算器ブロック62(3)～62(0)は、ベクトル乗算出力サンプルセット68(3)～68(0)を、ベクトルデータ入力サンプルセット66(11)～66(0)の特定の組合せを掛け合わせた乗算結果を備えるベクトル結果出力サンプルセットとして与える。40

## 【0031】

[0043] たとえば、乗算器ブロック 62(3)～62(0)のプログラム可能内部データ経路 67(3)～67(0)は、図2のベースバンドプロセッサ20の命令ディスパッチ48中のベクトル命令デコーダから与えられる設定に従ってプログラムされ得る。本実施形態では、乗算器ブロック 62(3)～62(0)の4つのプログラム可能内部データ経路 67(3)～67(0)がある。ベクトル命令は、VPE22によって実施されるべき特定タイプの演算を指定する。したがって、VPE22は、同じ共回路要素を用いて高効率的に異なるタイプのベクトル乗算演算を行うために、乗算器ブロック 62(3)～62(0)のプログラム可能内部データ経路 67(3)～67(0)を構成するようにプログラムされ、再プログラムされ得る。たとえば、VPE22は、乗算器ブロック 62(3)～62(0)のプログラム可能内部データ経路 67(3)～67(0)を、命令ディスパッチ48中の命令パイプライン中のベクトル命令の復号に従って、実行される各ベクトル命令ごとに周期かけるクロック周期ベースで構成し、再構成するようにプログラムされ得る。したがって、VPE22中のM0乗算ベクトル処理段60(1)が、ベクトルデータ入力サンプルセット66を毎クロック周期に処理するように構成されている場合、その結果、乗算器ブロック 62(3)～62(0)は、命令ディスパッチ48中の命令パイプライン中のベクトル命令の復号に従って、毎クロック周期でベクトル乗算演算を実施する。

### 【0032】

[0044] 乗算器ブロック 62 は、実数乗算と複素乗算とを実施するようにプログラムされ得る。引き続き図3を参照すると、あるベクトル処理ブロックデータ経路構成において、乗算器ブロック 62 が、2つの8ビットベクトルデータ入力サンプルセット 66 を掛け合わせるように構成され得る。1つの乗算ブロックデータ経路構成では、乗算器ブロック 62 が、2つの16ビットベクトルデータ入力サンプルセット 66 を掛け合わせるように構成されてよく、これらのセットは、8ビットベクトルデータ入力サンプルセット 66 の第1のペアに、8ビットベクトルデータ入力サンプルセット 66 の第2のペアを乗算して形成される。これについては、図6に示し、以下により詳細に説明する。やはり、乗算器ブロック 62(3)～62(0)中でプログラム可能データ経路構成を提供することにより、乗算器ブロック 62(3)～62(0)が、VPE22における面積を削減するとともに、可能な、所望のベクトル処理演算を実施するために、ベースバンドプロセッサ20中により少ないVPE22が設けられるようにするために、異なるタイプの乗算演算を実施するように構成され、再構成され得るという柔軟性がもたらされる。

### 【0033】

[0045] 図3に参照を戻すと、複数の乗算器ブロック 62(3)～62(0)は、プログラム可能出力データ経路 70(3)～70(0)中のベクトル乗算出力サンプルセット 68(3)～68(0)を、次のベクトル処理段60または出力処理段のいずれかに与えるように構成される。ベクトル乗算出力サンプルセット 68(3)～68(0)は、複数の乗算器ブロック 62(3)～62(0)によって実行されるベクトル命令に基づき、プログラムされた構成に従って、プログラム可能出力データ経路 70(3)～70(0)中で与えられる。この例では、プログラム可能出力データ経路 70(3)～70(0)中のベクトル乗算出力サンプルセット 68(3)～68(0)は、以下で論じるように、累算のためにM1累算ベクトル処理段60(2)に与えられる。VPE22のこの特定の設計では、複数の乗算器ブロック 62(3)～62(0)、続いて、ベクトルデータ入力の乗算、それに続く乗算結果の累算を要請する特殊なベクトル命令をサポートするための累算器を設けることが所望される。たとえば、FFT演算を行うのに一般に使われる、基底2および基底4のバタフライ演算は、一連の乗算演算、それに続く乗算結果の累算を含む。ただし、VPE22中に設けられるベクトル処理ブロックのこれらの組合せは例示であり、限定的でないことに留意されたい。プログラム可能データ経路構成を有するVPEは、ベクトル処理ブロックを有する1つまたは他のどの数のベクトル処理段を含むように構成されてもよい。ベクトル処理ブロックは、設計およびVPEによってサポートされるように設計された特定のベクトル命令に従って、どのタイプの演算を実施するように設けられ

10

20

30

40

50

てもよい。

#### 【0034】

[0046] 引き続き図3を参照すると、本実施形態では、ベクトル乗算出力サンプルセット68(3)～68(0)は、M1累算ベクトル処理段60(2)である次のベクトル処理段中に設けられた複数の累算器ブロック72(3)～72(0)に与えられる。複数の累算器ブロック72(A)～72(0)の中の各累算器ブロックは、2つの累算器72(X)(1)および72(X)(0)(すなわち、72(3)(1)、72(3)(0)、72(2)(1)、72(2)(0)、72(1)(1)、72(1)(0)、および72(0)(1)、72(0)(0))を含む。複数の累算器ブロック72(3)～72(0)は、ベクトル乗算出力サンプルセット68(3)～68(0)の結果を累算する。 図10

7～図9Cに関連して後でより詳しく論じるように、複数の累算器ブロック72(3)～72(0)は桁上げ保存累算器として設けられてよく、ここにおいて桁上げ積は本質的に、累算演算が完了されるまで、累算プロセス中は保存され、伝搬されない。複数の累算器ブロック72(3)～72(0)は、複数の累算器ブロック72(3)～72(0)中で冗長桁上げ保存フォーマットを提供するために、図4および図5の複数の乗算器ブロック62(3)～62(0)と融合されるという選択肢も有する。複数の累算器ブロック72(3)～72(0)中で冗長桁上げ保存フォーマットを提供することにより、複数の累算器ブロック72(3)～72(0)の各累算ステップ中に、桁上げ伝搬経路と桁上げ伝搬加算演算とを提供する必要をなくすことができる。M1累算ベクトル処理段60(2)およびその複数の累算器ブロック72(3)～72(0)を、ここで図3を参照して提起する。

#### 【0035】

[0047] 図3を参照すると、M1累算ベクトル処理段60(2)中の複数の累算器ブロック72(3)～72(0)は、累算器出力サンプルセット76(3)～76(0)(すなわち、76(3)(1)、76(3)(0)、76(2)(1)、76(2)(0)、76(1)(1)、76(1)(0)、および76(0)(1)、76(0)(0))を次のベクトル処理段60または出力処理段のいずれかにおいて与えるために、プログラム可能出力データ経路74(3)～74(0)(すなわち、74(3)(1)、74(3)(0)、74(2)(1)、74(2)(0)、74(1)(1)、74(1)(0)、および74(0)(1)、74(0)(0))中のベクトル乗算出力サンプルセット68(3)～68(0)を、プログラム可能出力データ経路構成に従って累算するように構成される。 この例では、累算器出力サンプルセット76(3)～76(0)は、ALU処理段60(3)である出力処理段に与えられる。たとえば、後でより詳しく論じるように、累算器出力サンプルセット76(3)～76(0)は、非限定的例として、図2のベースバンドプロセッサ20中のスカラープロセッサ44中のALU46にも与えられてよい。たとえば、ALU46は、より一般的な処理演算において使われるべき、VPE22によって実行される特殊なベクトル命令に従って、累算器出力サンプルセット76(3)～76(0)をとることができる。

#### 【0036】

[0048] 図3に参照を戻すと、累算器ブロック72(3)～72(0)のプログラム可能入力データ経路78(3)～78(0)および/またはプログラム可能内部データ経路80(3)～80(0)は、乗算器ブロック62(3)～62(0)から累算器ブロック72(3)～72(0)に与えられた、異なる組合せおよび/またはビット長のベクトル乗算出力サンプルセット68(3)～68(0)を受信するように再構成されるようにプログラムされ得る。各累算器ブロック72は、2つの累算器72(X)(1)、72(X)(0)からなるので、プログラム可能入力データ経路78(A)～78(0)は、78(3)(1)、78(3)(0)、78(2)(1)、78(2)(0)、78(1)(1)、78(1)(0)、および78(0)(1)、78(0)(0)として図3に示されている。同様に、プログラム可能内部データ経路80(3)～80(0)は、80(3)(1)、80(3)(0)、80(2)(1)、80(2)(0)、80(1)(1) 国50

、 80(1)(0)、80(0)(1)、80(0)(0)として図3に示されている。累算器ブロック72(3)～72(0)中にプログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)を設けることについては、図8～図9Cに関連して後でより詳しく論じる。このようにして、累算器ブロック72(3)～72(0)のプログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)に従って、累算器ブロック72(3)～72(0)は、累算されたベクトル乗算出力サンプルセット68(3)～68(0)のプログラムされた組合せに従って、累算器出力サンプルセット76(3)～76(0)を与えることができる。やはり、これにより、累算器ブロック72(3)～72(0)が、VPE22中での面積を削減するとともに、可能性としては、所望のベクトル処理演算を実施するのに、より少ないVPE22がベースバンドプロセッサ20中に設けられるようにするために、プログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)のプログラミングに基づいて異なるタイプの累算演算を実施するように構成され、再構成され得るという柔軟性が与えられる。

10

#### 【0037】

[0049]たとえば、ある累算器モード構成では、2つの累算器ブロック72のプログラム可能入力データ経路78および／またはプログラム可能内部データ経路80は、非限定的例として、単一40ビット累算器を提供するようにプログラムされ得る。これについては、図9Aに示し、以下でより詳細に説明する。別の累算器モード構成では、2つの累算器ブロック72のプログラム可能入力データ経路78および／またはプログラム可能内部データ経路80は、非限定的例として、二重24ビット累算器を提供するようにプログラムされ得る。これについては、図9Bに示し、以下でより詳細に説明する。別の累算器モード構成では、2つの累算器ブロック72のプログラム可能入力データ経路78および／またはプログラム可能内部データ経路80は、16ビット桁上げ保存加算器、それに続く単一24ビット累算器を提供するようにプログラムされ得る。これについては、図9Cに示し、以下でより詳細に説明する。乗算演算と累算演算の特定の異なる組合せも、乗算器ブロック62(3)～62(0)および累算器ブロック72(3)～72(0)(たとえば、16ビット累算を用いる16ビット複素乗算、および16ビット累算を用いる32ビット複素乗算)のプログラミングに従って、VPE22によってサポートされ得る。

20

30

#### 【0038】

[0050]累算器ブロック72(3)～72(0)のプログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)は、図2のベースバンドプロセッサ20の命令ディスパッチ48中のベクトル命令デコーダから与えられた設定に従ってプログラムされ得る。ベクトル命令は、VPE22によって実施されるべき特定タイプの演算を指定する。したがって、VPE22は、累算器ブロック72(3)～72(0)のプログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)を、命令ディスパッチ48中の命令パイプライン中のベクトル命令の復号に従って実行される各ベクトル命令用にプログラムし直すように構成され得る。ベクトル命令は、VPE22の1つまたは複数のクロック周期にわたって実行し得る。また、この例では、VPE22は、累算器ブロック72(3)～72(0)のプログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)を、ベクトル命令の各クロック周期ごとに、クロック周期単位でプログラムし直すように構成され得る。したがって、たとえば、VPE22中のM1累算ベクトル処理段60(2)によって実行されるベクトル命令が、ベクトル乗算出力サンプルセット68(3)～68(0)を毎クロック周期に処理する場合、その結果、累算器ブロック72(3)～72(0)のプログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)は、ベクトル命令の実行中、各クロック周期に再構成され得る。

40

50

## 【0039】

[0051] 図4Aおよび図4Bは、例示的なベクトル処理のさらなる説明を与えるための、図2および図3のVPE22中の乗算器ブロック62(A)～62(0)および累算器ブロック72(A)(1)～72(0)(0)の例示的なベクトル処理を示すフローチャートである。図4Aは、図2および図3の例示的なVPE中に含まれるプログラム可能データ経路構成を有する、乗算器ブロック62(A)～62(0)、累算器ブロック72(A)(1)～72(0)(0)、または両方のいずれであってもよい一般化ベクトル処理ブロックの例示的なベクトル処理を示すフローチャートである。図4Bは、各々がプログラム可能データ経路構成を有するとともに図2および図3の例示的なVPE22中の異なるベクトル処理段中に設けられる、乗算器ブロック62(A)～62(0)および累算器ブロック72(A)(1)～72(0)(0)の例示的なベクトル処理を示すフローチャートである。10

## 【0040】

[0052] この点において、図4Aに示すように、VPE22のプロセスは、入力処理段60(0)中の複数の入力データ経路の中のある入力データ経路(A3～C0)中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセット34(Y)～34(0)を受信することを含む(ブロック81)。ベクトル処理は次に、ベクトル処理ブロック62(A)～62(0)および/または72(A)(1)～72(0)(0)中の複数の入力データ経路A3～C0から、ベクトルデータ入力サンプルセット34(Y)～34(0)を受信することを備える(ブロック83)。ベクトル処理は次に、ベクトル処理段60(1)、60(2)によって実行されるベクトル命令に従って、ベクトル処理ブロック62(A)～62(0)、72(A)(1)～72(0)(0)用のプログラム可能データ経路構成67(A)～67(0)、70(3)～70(0)、78(A)(1)～78(0)(0)、80(A)(1)～80(0)(0)、74(A)(1)～74(0)(0)に基づいて、ベクトル結果出力サンプルセット68(A)～68(0)、76(A)(1)～76(0)(0)を与えるように、ベクトルデータ入力サンプルセット34(Y)～34(0)を処理することを含む(ブロック85)。ベクトル処理は次に、出力データ経路70(A)～70(0)、74(A)(1)～74(0)(0)中でベクトル結果出力サンプルセット68(A)～68(0)、76(A)(1)～76(0)(0)を与えることを含む(ブロック87)。ベクトル処理は次に、出力処理段60(3)において、ベクトル処理段60(1)、60(2)からベクトル結果出力サンプルセット68(A)～68(0)、76(A)(1)～76(0)(0)を受信することを含む(ブロック89)203040)。

## 【0041】

[0053] 図4Aに関連して上述したベクトル処理における各処理段60(0)～60(3)は、並列化ベクトル処理のために同時に起こり、ここにおいてベクトル処理ブロック62(A)～62(0)、72(A)(1)～72(0)(0)のプログラム可能データ経路構成67(A)～67(0)、70(3)～70(0)、78(A)(1)～78(0)(0)、80(A)(1)～80(0)(0)、74(A)(1)～74(0)(0)は、各クロック周期と同程度に頻繁に再プログラムされ得ることに留意されたい。上述したように、これにより、ベクトル処理ブロック62(A)～62(0)、72(A)(1)～72(0)(0)は、異なるベクトル命令用の異なる演算を、効率的に、および共通ベクトル処理ブロック62(A)～62(0)、72(A)(1)～72(0)(0)の使用により実施することができるようになる。50

## 【0042】

[0054] 図4Bは、乗算演算、それに続く累算演算を伴う、ベクトル命令のための、図3のVPE22中の乗算器ブロック62(A)～62(0)および累算器ブロック72(A)(1)～72(0)(0)の例示的なベクトル処理を示すフローチャートである。たとえば、FFTベクトル演算は、乗算演算と、それに続く累算演算を伴う。図4Bのフローチャートは、図4Aで上述した、VPE22の例示的な一般化ベクトル処理のさらなる

例示的な詳細を与える。この点において、ベクトル処理は、入力処理段 60(0) 中の複数の入力データ経路の中のある入力データ経路(A3 ~ C0) 中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセット 34(Y) ~ 34(0) を受信することを含む(ブロック 93)。ベクトル処理は次いで、複数の乗算器ブロック 62(A) ~ 62(0) 中の複数の入力データ経路 A3 ~ C0 からベクトルデータ入力サンプルセット 34(Y) ~ 34(0) を受信することを含む(ブロック 95)。ベクトル処理は次いで、ベクトル処理段 60(1) によって実行されるベクトル命令に従って、乗算器ブロック 62(A) ~ 62(0) 用のプログラム可能データ経路構成 67(A) ~ 67(0)、70(3) ~ 70(0) に基づき、複数の乗算出力データ経路 70(A) ~ 70(0) の中の乗算出力データ経路 70(A) ~ 70(0) 中で乗算ベクトル結果出力サンプルセット 68(A) ~ 68(0) を与えるように、ベクトルデータ入力サンプルセット 34(Y) ~ 34(0) を乗算することを含む(ブロック 97)。ベクトル処理は次に、複数の累算器ブロック 72(A)(1) ~ 72(0)(0) 中の複数の乗算出力データ経路 70(A) ~ 70(0) から乗算ベクトル結果出力サンプルセット 68(A) ~ 68(0) を受信することを含む(ブロック 99)。ベクトル処理は次に、第 2 のベクトル処理段 60(2) によって実行されるベクトル命令に従って、累算器ブロック 72(A)(1) ~ 72(0)(0) 用のプログラム可能データ経路 78(A)(1) ~ 78(0)(0)、80(A)(1) ~ 80(0)(0)、74(A)(1) ~ 74(0)(0) 構成に基づき、ベクトル累算結果サンプルセット 76(A)(1) ~ 76(0)(0) を与えるように、乗算ベクトル結果出力サンプルセット 68(A) ~ 68(0) を一緒に累算することを含む(ブロック 101)。ベクトル処理は次いで、出力データ経路 74(A)(1) ~ 74(0)(0) 中でベクトル累算結果サンプルセット 76(A)(1) ~ 76(0)(0) を与えることを含む(ブロック 103)。ベクトル処理は次いで、出力処理段 60(3) 中の累算器ブロック 72(A)(1) ~ 72(0)(0) からベクトル結果出力サンプルセット 76(A)(1) ~ 76(0)(0) を受信することを含む(ブロック 105)。

#### 【0043】

[0055] プログラム可能データ経路構成を有するベクトル処理ブロックを利用する、図 3 の例示的な VPE22 および図 4A および図 4B のベクトル処理の概観について記載したので、記述の残りでは、図 5 ~ 図 9C において、これらのベクトル処理ブロックのより例示的な、非限定的詳細について記載する。

#### 【0044】

[0056] この点において、図 5 は、図 3 の VPE22 の M0 乗算ベクトル処理段 60(1) 中の複数の乗算器ブロック 62(3) ~ 62(0) のより詳細な配線図である。図 6 は、図 5 の乗算器ブロック 62 の内部構成要素の配線図である。図 5 に示すように、特定の入力データ経路 A3 ~ A0、B3 ~ B0、C3 ~ C0 に従って乗算器ブロック 62(3) ~ 62(0) によって受信されるベクトルデータ入力サンプルセット 66(11) ~ 66(0) が示されている。図 6 に関連して後でより詳しく論じるように、この例における乗算器ブロック 62(3) ~ 62(0) の各々は、4 つの 8 ビット × 8 ビット乗算器を含む。図 5 に参照を戻すと、この例における乗算器ブロック 62(3) ~ 62(0) の各々は、被乗数入力「A」を、被乗数入力「B」または被乗数入力「C」のいずれかで乗算するように構成される。乗算器ブロック 62 中で掛け合わせられ得る被乗数入力「A」、および「B」または「C」は、図 5 に示すように、どの入力データ経路 A3 ~ A0、B3 ~ B0、C3 ~ C0 が乗算器ブロック 62(3) ~ 62(0) に接続されるかによって制御される。被乗数セレクタ入力 82(3) ~ 82(0) が、被乗数入力「B」それとも被乗数入力「C」が被乗数入力「A」で乗算されるために選択されるかを選択するために、各乗算器ブロック 62(3) ~ 62(0) 中のプログラム可能内部データ経路 67(3) ~ 67(0) を制御するための入力として、各乗算器ブロック 62(3) ~ 62(0) に与えられる。このようにして、乗算器ブロック 62(3) ~ 62(0) は、それらのプログラム可能内部データ経路 67(3) ~ 67(0) が、必要に応じて異なる乗算演算を行うように再プログラマされるという能力を備えている。

10

20

30

40

50

## 【0045】

[0057] 引き続き図5を参照すると、乗算器ブロック62(3)を一例として使うと、入力データ経路A3およびA2が、それぞれ入力AHおよびALに接続される。入力AHは、被乗数入力Aの上位ビットを表し、ALは、入力被乗数入力「A」の下位ビットを意味する。入力データ経路B3およびB2は、それぞれ入力BHおよびBLに接続される。入力BHは、被乗数入力「B」の上位ビットを表し、ALは、入力被乗数入力「B」の下位ビットを表す。入力データ経路C3およびC2は、それぞれ入力CIおよびCQに接続される。入力CIは、この例では入力被乗数入力「C」の実数ビット部分を表す。CQは、この例では入力被乗数入力「C」の虚数ビット部分を表す。図6に関連して後でより詳しく論じるように、被乗数セレクタ入力82(3)は、この例では、乗算器ブロック62(3)のプログラム可能内部データ経路67(3)が、被乗数入力「A」に対する8ビット乗算を被乗数入力「B」それとも被乗数入力「C」で実施するように構成されるか、または乗算器ブロック62(3)が、被乗数入力「A」に対する16ビット乗算を被乗数入力「B」それとも被乗数入力「C」で実施するように構成されるかも制御する。

10

## 【0046】

[0058] 引き続き図5を参照すると、乗算器ブロック62(3)～62(0)は、それらのプログラム可能内部データ経路67(3)～67(0)の構成に基づいて、乗算演算の桁上げ「C」および和「S」ベクトル出力サンプルセットとしてベクトル乗算出力サンプルセット68(3)～68(0)を各々が生成するように構成される。図7～図9Cに関連して後でより詳しく論じるように、ベクトル乗算出力サンプルセット68(3)～68(0)の桁上げ「C」および和「S」は融合され、桁上げ「C」および和「S」が、複数の累算器72(3)～72(0)中で冗長桁上げ保存フォーマットを提供するように、冗長桁上げ保存フォーマットで複数の累算器72(3)～72(0)に与えられることを意味する。後でより詳しく論じるように、複数の累算器72(3)～72(0)中で冗長桁上げ保存フォーマットを提供することにより、複数の累算器72(3)～72(0)によって実施される累算演算中に桁上げ伝搬経路と桁上げ伝搬加算演算とを提供する必要をなくすことができる。

20

## 【0047】

[0059] ベクトル乗算出力サンプルセット68(3)～68(0)を、それらのプログラム可能内部データ経路67(3)～67(0)の構成に基づいて乗算演算の桁上げ「C」および和「S」ベクトル出力サンプルセットとして生成する乗算器ブロック62(3)～62(0)の例を、図5に示す。たとえば、乗算器ブロック62(3)は、桁上げC00と和S00とを8ビット乗算用の32ビット値として、桁上げC01と和S01とを16ビット乗算用の64ビット値として生成するように構成される。他の乗算器ブロック62(2)～62(0)も、この例では同じ能力を有する。この点において、乗算器ブロック62(2)は、桁上げC10と和S10とを8ビット乗算用の32ビット値として、桁上げC11と和S11とを16ビット乗算用の64ビット値として生成するように構成される。乗算器ブロック62(1)は、桁上げC20と和S20とを8ビット乗算用の32ビット値として、桁上げC21と、和S21とを16ビット乗算用の64ビット値として生成するように構成される。乗算器ブロック62(0)は、桁上げC30と和S30とを8ビット乗算用の32ビット値として、桁上げC31と和S31とを16ビット乗算用の64ビット値として生成するように構成される。

30

40

## 【0048】

[0060] 図5の乗算器ブロック62中に設けられるプログラム可能データ経路構成のより例示的な詳細を説明するために、図6が挙げられる。図6は、8ビット×8ビットベクトルデータ入力サンプルセット66と、16ビット×16ビットベクトルデータ入力サンプルセット66とを乗算することが可能なプログラム可能データ経路構成を有する、図3および図4の乗算器ブロック62の内部構成要素の配線図である。この点において、乗算器ブロック62は、この例では4つの8×8ビット乗算器84(3)～84(0)を含む。任意の所望の数の乗算器84が設けられてよい。第1の乗算器84(3)が、8ビット

50

ベクトルデータ入力サンプルセット 66A[H]（入力被乗数入力「A」の上位ビットである）を受信し、ベクトルデータ入力サンプルセット 66A[H]を、8ビットベクトルデータ入力サンプルセット 66B[H]（入力被乗数入力「B」の上位ビットである）または8ビットベクトルデータ入力サンプルセット 66C[I]（入力被乗数入力「C」の上位ビットである）と乗算するように構成される。被乗数として乗算器 84(3)に与えている8ビットベクトルデータ入力サンプルセット 66B[H]または8ビットベクトルデータ入力サンプルセット 66C[I]のいずれかを選択するように構成されたマルチプレクサ 86(3)が設けられる。マルチプレクサ 86(3)は、本実施形態では、乗数セレクタ入力 82中の上位ビットである被乗数セレクタビット入力 82[3]によって制御される。このようにして、マルチプレクサ 86(3)および被乗数セレクタビット入力 82[3]は、8ビットベクトルデータ入力サンプルセット 66B[H]それとも8ビットベクトルデータ入力サンプルセット 66C[I]が、受信するベクトルデータ入力サンプルセット 66A[H]と乗算されるかを乗算器 84(3)が制御するためのプログラム可能な内部データ経路 67[0]構成を提供する。

10

#### 【0049】

[0061] 引き続き図6を参照すると、他の乗算器 84(2)～84(0)も、第1の乗算器 84(3)用に設けられるものと同様のプログラム可能な内部データ経路 67[2]～67[0]を含む。乗算器 84(2)は、被乗数入力「A」の下位ビットである8ビットベクトルデータ入力サンプルセット 66A[L]と乗算されるべき、8ビットベクトルデータ入力サンプルセット 66B[H]または8ビットベクトルデータ入力サンプルセット 66C[I]のいずれかをプログラム可能な内部データ経路 67[1]中で与えるための、プログラム可能な構成を有するプログラム可能な内部データ経路 67[2]を含む。選択は、本実施形態では、マルチプレクサ 86(2)によって、乗数セレクタ入力 82 中の被乗数セレクタビット入力 82[2]に従って制御される。乗算器 84(1)は、8ビットベクトルデータ入力サンプルセット 66A[H]と乗算されるべき、被乗数入力「B」の下位ビットである8ビットベクトルデータ入力サンプルセット 66B[L]、または被乗数入力「C」の下位ビットである8ビットベクトルデータ入力サンプルセット 66C[Q]のいずれかをプログラム可能な内部データ経路 67[1]中で与えるようにプログラム可能なプログラム可能な内部データ経路 67[1]を含む。選択は、本実施形態では、マルチプレクサ 86(1)によって、乗数セレクタ入力 82 中の被乗数セレクタビット入力 82[1]に従って制御される。さらに、乗算器 84(0)は、8ビットベクトルデータ入力サンプルセット 66A[L]と乗算されるべき、8ビットベクトルデータ入力サンプルセット 66B[L]または8ビットベクトルデータ入力サンプルセット 66C[Q]のいずれかをプログラム可能な内部データ経路 67[0]中で与えるようにプログラム可能なプログラム可能な内部データ経路 67[0]を含む。選択は、本実施形態では、マルチプレクサ 86(0)によって、乗数セレクタ入力 82 中の被乗数セレクタビット入力 82[0]に従つて制御される。

20

30

#### 【0050】

[0062] 引き続き図6を参照すると、上述したように、乗算器 84(3)～84(0)は、異なるビット長乗算演算を実施するように構成され得る。この点において、各乗算器 84(3)～84(0)は、それぞれビット長乗算モード入力 88(3)～88(0)を含む。この例では、各乗算器 84(3)～84(0)は、それぞれ、プログラム可能なデータ経路 90(3)～90(0)、91、および 92(3)～92(0)の構成を制御する入力に従つて、8ビット×8ビットモードでプログラムされ得る。各乗算器 84(3)～84(0)は、それぞれ、プログラム可能なデータ経路 90(3)～90(0)、91、および 92(3)～92(0)の構成を制御する入力に従つて、16ビット×16ビットモードと 24ビット×8ビットモードとを含む、より大きいビット乗算演算の一部を行うようにもプログラムされ得る。たとえば、各乗算器 84(3)～84(0)が、プログラム可能なデータ経路 90(3)～90(0)の構成に従つて8ビット×8ビット乗算モードで構成される場合、ユニットとしての複数の乗算器 84(3)～84(0)は、2つの個々

40

50

の 8 ビット × 8 ビット乗算器を、乗算器ブロック 6 2 の一部として備えるように構成され得る。各乗算器 8 4 ( 3 ) ~ 8 4 ( 0 ) が、プログラム可能データ経路 9 1 の構成に従って 16 ビット × 16 ビット乗算モードで構成される場合、ユニットとしての複数の乗算器 8 4 ( 3 ) ~ 8 4 ( 0 ) は、単一 16 ビット × 16 ビット乗算器を乗算器ブロック 6 2 の一部として備えるように構成され得る。乗算器 8 4 ( 3 ) ~ 8 4 ( 0 ) が、プログラム可能データ経路 9 2 ( 3 ) ~ 9 2 ( 0 ) の構成に従って 24 ビット × 8 ビット乗算モードで構成される場合、ユニットとしての複数の乗算器 8 4 ( 3 ) ~ 8 4 ( 0 ) は、1 つの 16 ビット × 24 ビット × 8 ビット乗算器を乗算器ブロック 6 2 の一部として備えるように構成され得る。

## 【0051】

10

[0063] 引き続き図 6 を参照すると、この例における乗算器 8 4 ( 3 ) ~ 8 4 ( 0 ) は、16 ビット × 16 ビット乗算モードで構成されるものとして示されている。16 ビット入力和 9 4 ( 3 )、9 4 ( 2 ) および入力桁上げ 9 6 ( 3 )、9 6 ( 2 ) が、それぞれ、各乗算器 8 4 ( 3 )、8 4 ( 2 ) によって生成される。16 ビット入力和 9 4 ( 1 )、9 4 ( 0 ) および入力桁上げ 9 6 ( 1 )、9 6 ( 0 ) が、それぞれ、各乗算器 8 4 ( 1 )、8 4 ( 0 ) によって生成される。16 ビット入力和 9 4 ( 3 )、9 4 ( 2 ) および入力桁上げ 9 6 ( 3 )、9 6 ( 2 ) はまた、入力和 9 4 ( 3 ) ~ 9 4 ( 0 ) と入力桁上げ 9 6 ( 3 ) ~ 9 6 ( 0 ) を加え合わせるように、16 ビット和の入力 9 4 ( 1 )、9 4 ( 0 ) および入力桁上げ 9 6 ( 1 )、9 6 ( 0 ) とともに 24 ビットの 4 : 2 圧縮器 109 に与えられる。加算された入力和 9 4 ( 3 ) ~ 9 4 ( 0 ) および入力桁上げ 9 6 ( 3 ) ~ 9 6 ( 0 ) は、プログラム可能データ経路 9 1 がアクティブであるとともに入力和 9 4 ( 3 ) ~ 9 4 ( 0 ) および入力桁上げ 9 6 ( 3 ) ~ 9 6 ( 0 ) とゲートされるとき、16 ビット × 16 ビット乗算モードで、単一和 9 8 と単一桁上げ 100 とをもたらす。プログラム可能データ経路 9 1 は、24 ビットの 4 : 2 圧縮器 109 に与えられるように、16 ビットワードとして、組み合わされた入力和 9 4 ( 3 )、9 4 ( 2 ) をもつ第 1 の AND ベースのゲート 102 ( 3 ) によって、および 16 ビットワードとして、組み合わされた入力桁上げ 9 6 ( 3 )、9 6 ( 2 ) をもつ第 2 の AND ベースのゲート 102 ( 2 ) によってゲートされる。プログラム可能データ経路 9 1 はまた、24 ビットの 4 : 0 圧縮器 109 に与えられるように、16 ビットワードとして、組み合わされた入力和 9 4 ( 1 )、9 4 ( 0 ) をもつ第 3 の AND ベースのゲート 102 ( 1 ) によって、および 16 ビットワードとして、組み合わされた入力桁上げ 9 6 ( 1 )、9 6 ( 0 ) をもつ第 4 の AND ベースのゲート 102 ( 2 ) によってゲートされる。乗算器ブロック 6 2 が 16 ビット × 16 ビットまたは 24 ビット × 8 ビット乗算モードで構成される場合、プログラム可能出力データ経路 70 [ 0 ] には、ベクトル乗算出力サンプルセット 68 [ 0 ] が、圧縮された 32 ビット和 S0 および 32 ビット桁上げ C0 部分積として与えられる。

20

30

40

## 【0052】

[0064] 乗算器ブロック 6 2 中の乗算器 8 4 ( 3 ) ~ 8 4 ( 0 ) が 8 ビット × 8 ビット乗算モードで構成される場合、プログラム可能出力データ経路 70 [ 1 ] 構成は、圧縮なしで、16 ビット入力和 9 4 ( 3 ) ~ 9 4 ( 0 ) および部分積としての対応する 16 ビット入力桁上げ 9 6 ( 3 ) ~ 9 6 ( 0 ) として提供される。乗算器ブロック 6 2 中の乗算器 8 4 ( 3 ) ~ 8 4 ( 0 ) が 8 ビット × 8 ビット乗算モードで構成される場合、プログラム可能出力データ経路 70 [ 1 ] は、圧縮なしで、16 ビット入力和 9 4 ( 3 ) ~ 9 4 ( 0 ) およびベクトル乗算出力サンプルセット 68 [ 1 ] としての対応する 16 ビット入力桁上げ 9 6 ( 3 ) ~ 9 6 ( 0 ) として提供される。乗算器ブロック 6 2 の乗算モードに依存するベクトル乗算出力サンプルセット 68 [ 0 ]、68 [ 1 ] は、実行されるベクトル命令に従って、和および桁上げ積の累算のために、累算器ブロック 72 ( 3 ) ~ 72 ( 0 ) に与えられる。

## 【0053】

[0065] プログラム可能データ経路構成を有する、図 4 および図 5 の乗算器ブロック 6 2 ( 3 ) ~ 6 2 ( 0 ) について記載したので、冗長桁上げ保存フォーマットで構成された

50

累算器ブロック 72(3)～72(0)と融合されるべき、VPE22中の乗算器ブロック 62(3)～62(0)の特徴について、図7に関連してここで概説する。

#### 【0054】

[0066] この点について、図7は、図2および図3のVPE中の乗算器ブロックおよび累算器ブロックの一般化配線図であり、ここにおいて、累算器ブロックは、桁上げ伝搬を低減するのに冗長桁上げ保存フォーマットを利用する桁上げ保存累算器構造を利用する。上述し、図7に示したように、乗算器ブロック62は、被乗数入力66[H]および66[L]を乗算し、少なくとも1つの入力和94と少なくとも1つの入力桁上げ96を、ベクトル乗算出力サンプルセット68としてプログラム可能出力データ経路70中で与えるように構成される。各累算ステップ用の累算器ブロック72中に桁上げ伝搬経路と桁上げ伝搬加算器とを設ける必要をなくするために、プログラム可能出力データ経路70中のベクトル乗算出力サンプルセット68中の少なくとも1つの入力和94および少なくとも1つの入力桁上げ96が、少なくとも1つの累算器ブロック72への冗長桁上げ保存フォーマットで融合される。言い換えると、ベクトル乗算出力サンプルセット68中の桁上げ96が、ベクトル入力桁上げ96として桁上げ保存フォーマットで累算器ブロック72に与えられる。このようにして、ベクトル乗算出力サンプルセット68中の入力和94および入力桁上げ96は、本実施形態では複合ゲート4:2圧縮器である累算器ブロック72の圧縮器108に与えられ得る。圧縮器108は、入力和94および入力桁上げ96を、それぞれ、以前の累算ベクトル出力和112および以前のシフトされた累算ベクトル出力桁上げ117と一緒に累算するように構成される。以前のシフトされた累算ベクトル出力桁上げ117は本質的に、累算演算中の保存された桁上げ累算である。10

#### 【0055】

[0067] このようにして、单一最終桁上げ伝搬加算器のみが、受信入力桁上げ96を、累算器ブロック72によって生成された累算の一部として、入力和94に伝搬するために、累算器ブロック72中に設けられることを求められるのではない。累算器ブロック72中の各累算ステップ中に桁上げ伝搬加算演算を実施することに関連した電力消費が、本実施形態では低減される。また、累算器ブロック72中の各累算ステップ中に桁上げ伝搬加算演算を実施することに関連したゲート遅延も、本実施形態ではなくなる。20

#### 【0056】

[0068] 引き続き図7を参照すると、圧縮器108は、冗長な形での入力和94および入力桁上げ96を、それぞれ、以前の累算ベクトル出力和112および以前のシフトされた累算ベクトル出力桁上げ117と一緒に累算するように構成される。シフトされた累算ベクトル出力桁上げ117は、次の受信入力和94および入力桁上げ96の次の累算が圧縮器108によって実施される前に、累算ベクトル出力桁上げ114をシフトすることによって、圧縮器108ビットによって生成された累算ベクトル出力桁上げ114によって生成される。最終的なシフトされた累算ベクトル出力桁上げ117は、累算器ブロック72に設けられた单一最終桁上げ伝搬加算器119によって最終累算ベクトル出力和112に加算され、最終的なシフトされた累算ベクトル出力桁上げ117を、最終累算ベクトル出力和112を最終累算器出力サンプルセット762の補数表現にコンバートするために桁上げ累算を伝搬する。最終累算ベクトル出力和112は、プログラム可能出力データ経路74中で累算器出力サンプルセット76として与えられる（図3参照）。30

#### 【0057】

[0069] 乗算器ブロック62と、冗長桁上げ保存フォーマットで構成された累算器ブロック72の融合を示す図7について説明したので、累算器ブロック72(3)～72(0)に関する、より例示的な詳細について、図8に関連してここで概説する。以下で説明する図9A～図9Cは、共通回路要素およびハードウェアを用いて異なるベクトル累算演算を行うための異なる累算モードにおける、冗長桁上げ保存フォーマットで構成された累算器ブロック72(3)～72(0)のより例示的な詳細を与える。40

#### 【0058】

[0070] 図8は、図3のVPE22中に設けられる累算器ブロック72の例示的な内部50

構成要素の詳細な配線図である。上述するとともに後でより詳しく論じるように、累算器ブロック72は、プログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)を有して構成され、そうすることによって累算器ブロック72は、特定の異なるタイプのベクトル累算演算を実施するように設計された専用回路要素として作用するようにプログラムされ得る。たとえば、累算器ブロック72は、符号付きおよび符号なし累算演算を含む、いくつかの異なる累算および加算を行うようにプログラムされ得る。異なるタイプの累算演算を行うように構成された累算器ブロック72中のプログラム可能入力データ経路78(3)～78(0)および／またはプログラム可能内部データ経路80(3)～80(0)の具体例が、後で論じる図9A～図9Cに示される。また、累算器ブロック72は、低減された組合せ論理で高速累算演算を行うために、桁上げ伝搬を回避または低減するために、冗長桁上げ算術を行うための桁上げ保存累算器72[0]、72[1]を含むように構成される。

10

#### 【0059】

[0071] 累算器ブロック72の例示的な内部構成要素が、図8に示される。そこに示されているように、本実施形態における累算器ブロック72は、第1の入力和94[0]および第1の入力桁上げ96[0]と、第2の入力和94[1]および第2の入力桁上げ96[1]とを、一緒に累算するために乗算器ブロック62から受信するように構成される。図8に関連して、入力和94[0]、94[1]および入力桁上げ96[0]、96[1]は、ベクトル入力和94[0]、94[1]およびベクトル入力桁上げ96[0]、96[1]は各々、長さが16ビットである。この例における累算器ブロック72は、2つの24ビット桁上げ保存累算器72[0]、72[1]として設けられ、各々が、共通要素番号をもつ同様の構成要素を含み、「[0]」は桁上げ保存累算器72[0]用に指定され、「[1]」は桁上げ保存累算器72[1]用に指定される。桁上げ保存累算器72[0]、72[1]は、ベクトル累算演算を同時に実施するように構成され得る。

20

#### 【0060】

[0072] 図8の桁上げ保存累算器72[0]を参照すると、ベクトル入力和94[0]およびベクトル入力桁上げ96[0]は、プログラム可能内部データ経路80[0]の一部として設けられたマルチプレクサ104(0)中の入力である。負のベクトル入力和94[0]と負のベクトル入力桁上げ96[0]とを必要とする累算演算のための、マルチプレクサ104(0)への入力としての入力107(0)に従って負のベクトル入力和94[0]と負のベクトル入力桁上げ96[0]とを生成する、排他的ORベースのゲートからなり得る否定回路106(0)も設けられる。マルチプレクサ104(0)は、ベクトル命令復号の結果として生成されたセレクタ入力110(0)に従って、圧縮器108(0)に与えられるべきベクトル入力和94[0]およびベクトル入力桁上げ96[0]または負のベクトル入力和94[0]および負のベクトル入力桁上げ96[0]のいずれかを選択するように構成される。この点において、セレクタ入力110(0)は、累算器ブロック72によって実施されるように構成された累算演算に従って、桁上げ保存累算器72[0]のプログラム可能入力データ経路78[0]を、ベクトル入力和94[0]およびベクトル入力桁上げ96[0]、または負のベクトル入力和94[0]および負のベクトル入力桁上げ96[0]のいずれかを、圧縮器108(0)に与えるようにプログラム可能にさせる。

30

40

#### 【0061】

[0073] 引き続き図8を参照すると、本実施形態における桁上げ保存累算器72[0]の圧縮器108(0)は、複合ゲート4:2圧縮器である。この点において、圧縮器108(0)は、冗長桁上げ保存演算において和と桁上げとを累算するように構成される。圧縮器108(0)は、現在のベクトル入力和94[0]およびベクトル入力桁上げ96[0]、または現在の負のベクトル入力和94[0]および負のベクトル入力桁上げ96[0]を、圧縮器108(0)への4つの入力として、以前の累算されたベクトル入力

50

和 9 4 [ 0 ] およびベクトル入力桁上げ 9 6 [ 0 ]、または累算された負のベクトル入力和 9 4 [ 0 ]' および負のベクトル入力桁上げ 9 6 [ 0 ]' と一緒に累算するように構成される。圧縮器 1 0 8 ( 0 ) は、累算ベクトル出力和 1 1 2 ( 0 ) と、累算ベクトル出力桁上げ 1 1 4 ( 0 ) とを、累算器出力サンプルセット 7 6 ( 3 ) ~ 7 6 ( 0 ) を与えるように、プログラム可能出力データ経路 7 4 [ 0 ] 中の累算器出力サンプルセット 7 6 [ 0 ] として与える（図 3 参照）。累算ベクトル出力桁上げ 1 1 4 ( 0 ) は、各累算ステップ中にビット幅成長を制御するための、シフトされた累算ベクトル出力桁上げ 1 1 7 ( 0 ) を与えるように、累算演算中にビットシフタ 1 1 6 ( 0 ) によってシフトされる。たとえば、本実施形態におけるビットシフタ 1 1 6 ( 0 ) は、冗長桁上げ保存フォーマットでの、圧縮器 1 0 8 ( 0 ) に融合されるバレルシフタである。このようにして、シフトされた累算ベクトル出力桁上げ 1 1 7 ( 0 ) は本質的に、累算器 7 2 [ 0 ] によって実施される累算演算中に、累算ベクトル出力和 1 1 2 ( 0 ) に伝搬される必要なく、保存される。このようにして、累算器 7 2 [ 0 ] 中の各累算ステップ中に桁上げ伝搬加算演算を実施することに関連した電力消費およびゲート遅延が、本実施形態ではなくなる。10

#### 【 0 0 6 2 】

[0074] 追加の後続ベクトル入力和 9 4 [ 0 ] およびベクトル入力桁上げ 9 6 [ 0 ]、または負のベクトル入力和 9 4 [ 0 ]' および負のベクトル入力桁上げ 9 6 [ 0 ]' は、現在の累算ベクトル出力和 1 1 2 ( 0 ) および現在の累算ベクトル出力桁上げ 1 1 7 ( 0 ) と累算され得る。ベクトル入力和 9 4 [ 0 ] およびベクトル入力桁上げ 9 6 [ 0 ]、または負のベクトル入力和 9 4 [ 0 ]' および負のベクトル入力桁上げ 9 6 [ 0 ]' は、ベクトル命令復号の結果として生成された和桁上げセレクタ 1 2 0 ( 0 ) に従って、プログラム可能内部データ経路 8 0 [ 0 ] の一部としてのマルチプレクサ 1 1 8 ( 0 ) によって選択される。現在の累算ベクトル出力和 1 1 2 ( 0 ) および現在のシフトされた累算ベクトル出力桁上げ 1 1 7 ( 0 ) は、桁上げ保存累算器 7 2 [ 0 ] が、アップデートされた累算ベクトル出力和 1 1 2 ( 0 ) と、累算ベクトル出力桁上げ 1 1 4 ( 0 ) とを与えるために、入力として圧縮器 1 0 8 ( 0 ) に与えられ得る。この点において、和桁上げセレクタ 1 2 0 ( 0 ) は、累算器 7 2 [ 0 ] のプログラム可能内部データ経路 8 0 [ 0 ] を、累算器ブロック 7 2 によって実施されるように構成された累算演算に従って、ベクトル入力和 9 4 [ 0 ] と、ベクトル入力桁上げ 9 6 [ 0 ] とを圧縮器 1 0 8 ( 0 ) に与えるようにプログラム可能にさせる。マルチプレクサ 1 1 8 ( 0 ) に、桁上げ保存累算器 7 2 [ 0 ] における累算の動作タイミングを制御するための保持状態入力 1 2 6 ( 0 ) に従って、累算ベクトル出力和 1 1 2 ( 0 ) およびシフトされた累算ベクトル出力桁上げ 1 1 7 ( 0 ) の現在の状態を保持するために、保持ゲート 1 2 2 ( 0 )、1 2 4 ( 0 ) も本実施形態では設けられる。2030

#### 【 0 0 6 3 】

[0075] 引き続き図 8 を参照すると、桁上げ保存累算器 7 2 [ 0 ] の累算ベクトル出力和 1 1 2 ( 0 ) およびシフトされた累算ベクトル出力桁上げ 1 1 7 ( 0 )、ならびに桁上げ保存累算器 7 2 [ 1 ] の累算ベクトル出力和 1 1 2 ( 1 ) およびシフトされた累算ベクトル出力桁上げ 1 1 7 ( 1 )、ならびには、それぞれ、制御ゲート 1 3 4 ( 0 )、1 3 6 ( 0 ) および 1 3 4 ( 1 )、1 3 6 ( 1 ) によってゲートされる。制御ゲート 1 3 4 ( 0 )、1 3 6 ( 0 ) および 1 3 4 ( 1 )、1 3 6 ( 1 ) は、それぞれ、圧縮器 1 0 8 ( 0 )、1 0 8 ( 1 ) に戻される、累算ベクトル出力和 1 1 2 ( 0 ) およびシフトされた累算ベクトル出力桁上げ 1 1 7 ( 0 ) と、累算ベクトル出力和 1 1 2 ( 1 ) およびシフトされた累算ベクトル出力桁上げ 1 1 7 ( 1 ) とを制御する。40

#### 【 0 0 6 4 】

[0076] 図 8 の累算器ブロック 7 2 の累算器 7 2 [ 0 ]、7 2 [ 1 ] のプログラム可能入力データ経路 7 8 [ 0 ]、7 8 [ 1 ] およびプログラム可能内部データ経路 8 0 [ 0 ]、8 0 [ 1 ] を要約すると、累算器ブロック 7 2 は異なるモードで構成され得る。累算器ブロック 7 2 は、図 8 に示す共通累算器回路要素を用いた特定のベクトル処理命令に従って、異なる累算演算を行うように構成され得る。共通累算器回路要素を用いた特定のベク50

トル処理命令に従って異なる累算演算を行うように構成される累算器ブロック72の例を、以下の図9A～図9Cに示す。

#### 【0065】

[0077] この点において、図9Aは、図8の同じ累算器ブロック72の配線図である。この例では、累算器ブロック72は、二重24ビット累算器モードを提供するようにプログラムされた、プログラム可能入力データ経路78[0]、78[1]と、プログラム可能内部データ経路80[0]、80[1]とを有する。図9Aの累算器ブロック72中の各桁上げ保存累算器72[0]、72[1]は、24ビット累算器を提供するように構成される。累算器72[0]、72[1]の24ビット累算容量は、圧縮器108(0)、108(1)のビット容量によって与えられる。図8に関連した累算器72[0]、72[1]の考察により、図9Aの累算器72[0]、72[1]によって行われる個々の24ビット累算について説明する。累算ブロック72において二重24ビット累算を行うためのバイ累算器72[0]、72[1]によって実施される累算の一般的なデータ経路が、それぞれ、図9Aの、プログラム可能累算データ経路132(0)および132(1)中に示されている。10

#### 【0066】

[0078] 引き続き図9Aを参照して、桁上げ保存累算器72[0]の例示的な構成要素を記載するが、桁上げ保存累算器72[1]にも等しく適用可能である。本実施形態では、桁上げ保存累算器72[0]の累算ベクトル出力和112(0)およびシフトされた累算ベクトル出力桁上げ117(0)、ならびに桁上げ保存累算器72[1]の累算ベクトル出力和112(1)およびシフトされた累算ベクトル出力桁上げ117(1)、ならびには、それぞれ、制御ゲート134(0)、136(0)および134(1)、136(1)によってゲートされる。制御ゲート134(0)、136(0)および134(1)、136(1)は、それぞれ、圧縮器108(0)、108(1)に戻される、累算ベクトル出力和112(0)およびシフトされた累算ベクトル出力桁上げ117(0)と、累算ベクトル出力和112(1)およびシフトされた累算ベクトル出力桁上げ117(1)とを制御する。ベクトル命令の復号から、制御ゲート134(0)、136(0)と134(1)、136(1)の両方に与えられた制御入力138(0)、138(1)は、それぞれ、累算ベクトル出力和112(0)と、シフトされた累算ベクトル出力桁上げ117(0)とを制御し、累算ベクトル出力和112(1)およびシフトされた累算ベクトル出力桁上げ117(1)は、それぞれ、圧縮器108(0)、108(1)に戻される。制御入力138(0)、138(1)および制御ゲート134(0)、136(0)は、累算器72[0]、72[1]が、図9Bおよび図9Cに関連して後でより詳しく論じるように、別個の累算演算それとも組み合わされた累算演算を各々が実施するようにプログラムされるかを制御する。したがって、制御入力138(0)、138(1)ならびに制御ゲート134(0)、136(0)および134(1)、136(1)は、本実施形態では、それぞれ、累算器72[0]、72[1]のプログラム可能内部データ経路80[0]、80[1]の一部を形成する。2030

#### 【0067】

[0079] 図8に参照を戻すと、累算器ブロック72のプログラム可能内部データ経路80[0]、80[1]はまた、個々の累算器72[0]、72[1]の24ビット容量よりも大きい累算演算を実施するようにプログラムされ、かつ／または再プログラムされ得る。この点において、累算器72[0]、72[1]のプログラム可能内部データ経路80[0]、80[1]は、単一ベクトル累算演算において一緒に利用されるべき両方の累算器72[0]、72[1]を提供するようにプログラムされ得る。累算器72[0]、72[1]は、累算器72[0]、72[1]の個々のビット累算容量よりも大きいビット容量の単一累算演算を行うようにプログラムされ得る。累算器72[0]、72[1]のプログラム可能内部データ経路80[0]、80[1]は、桁上げ保存累算器72[0]に、圧縮器108(0)から、次の桁上げ出力(NCO)137(0)としてオーバーフロー桁上げ出力を伝搬せんように構成され得る。NCO137(0)は、次の桁上げ4050

入力（N C I）139（1）として、桁上げ保存累算器72[1]中の圧縮器108（1）に与えられ得る。図8に関連して上で記載したように、本実施形態では、40ビット累算を行うための累算器72[0]、72[1]に、24ビット桁上げおよび和累算への24ビットオーバーフロー桁上げ伝搬を行わせるための、累算器72[0]、72[1]中でプログラム可能内部データ経路80[0]、80[1]として提供されるこの桁上げ伝搬構成能力。

#### 【0068】

[0080] この点において、図9Bは、図8の同じ累算器ブロック72の配線図である。

図9Bにおいて、累算器ブロック72が、単一累算演算モードで構成されて示されている。

10

図9Bにおいて、累算器72[0]、72[1]は、累算器ブロック72内で単一累算演算を行うために構成されたプログラム可能内部データ経路80[0]、80[1]を有する。累算器ブロック72の単一累算器モードのこの例において、累算器72[0]、72[1]は、単一40ビット累算ベクトル出力和112とシフトされた累算ベクトル出力桁上げ117とを累算する。単一累算ベクトル出力和112は、プログラム可能出力データ経路74[0]、74[1]中で累算器出力サンプルセット76として与えられる累算ベクトル出力和112(0)、112(1)からなる（図3も参照）。累算ベクトル出力和112(0)は、単一40ビット累算ベクトル出力和112の最下位ビットを備える。累算ベクトル出力和112(1)は、単一40ビット累算ベクトル出力和112の最上位ビットを備える。同様に、シフトされた累算ベクトル出力桁上げ117は、シフトされた累算出力桁上げ117(0)、117(1)からなる。シフトされた累算ベクトル出力桁上げ117(0)は、单一シフト累算ベクトル出力桁上げ117の最下位ビットを備える。累算ベクトル出力和114(1)は、単一40ビット累算ベクトル出力桁上げ114の最上位ビットを備える。累算ベクトル出力和114[0]およびシフトされた累算ベクトル出力桁上げ117(0)は、プログラム可能出力データ経路74[0]中に設けられる（図3参照）。

#### 【0069】

[0081] 引き続き図9Bを参照すると、累算器ブロック72が単一累算モード（たとえば、40ビット累算）で構成されるときに累算器72[0]、72[1]によって実施される累算演算の一般的なデータ経路が、プログラム可能累算データ経路146として示されている。この点において、累算器ブロック72は、上で記載したように、ベクトル入力和94とベクトル入力桁上げ96とを受信する。桁上げ保存累算器72[0]は、場合によっては、ベクトル入力和94[0]およびベクトル入力桁上げ96[0]、または負のベクトル入力和94[0]’および負のベクトル入力桁上げ96[0]の累算からの、累算ベクトル出力和112(0)と、累算ベクトル出力桁上げ114(0)との最下位ビットを累算する。桁上げ保存累算器72[1]は、場合によっては、ベクトル入力和94[0]およびベクトル入力桁上げ96[0]、または負のベクトル入力和94[0]’および負のベクトル入力桁上げ96[0]の累算からの、累算ベクトル出力和112(1)と、累算ベクトル出力桁上げ114(1)との最上位ビットを累算する。

#### 【0070】

[0082] 引き続き図9Bを参照すると、単一累算ベクトル出力和112と、累算ベクトル出力桁上げ114とを与えるように累算器72[0]、72[1]をプログラムするために、累算器72[0]、72[1]のプログラム可能内部データ経路80[0]、80[1]は、単一累算演算を行なうようにプログラムされる。この点において、桁上げ保存累算器72[0]の圧縮器108(0)のNCO137(0)および桁上げ保存累算器72[1]の圧縮器108(1)のNCI139(1)は、累算器ブロック72中に単一累算器（たとえば、40ビット累算器）を設けるために構成される。桁上げ保存累算器72[1]のNCI139(1)は、NCI制御入力142(1)を用いてNCIゲート140(1)によってゲートされる。このようにして、累算器ブロック72中の累算器72[0]、72[1]が、桁上げ保存累算器72[0]から桁上げ保存累算器72[1]へのオーバーフロー桁上げ伝搬を利用して単一累算演算を行うことを所望されるとき、NCI制

10

20

30

40

50

御入力 142(1) は、桁上げ保存累算器 72[1] のプログラム可能内部データ経路 80[1] の一部としてアクティブにされ得る。NCI 制御入力 142(1) は、NCI ゲート 140(1) に、圧縮器 108(0) から圧縮器 108(1) へのオーバーフロー桁上げ伝搬を許可させる。NCI 制御入力 142(1) は、圧縮器 108(0) に、圧縮器 108(1) への NCI 139(1) として NCO 137(0) を生成させるように、桁上げ保存累算器 72[0] 中の圧縮器 108(0) の桁上げ伝搬入力 144(0) にも結合される。これらの構成により、桁上げ保存累算器 72[1] は、単一累算ベクトル出力和 112 と、累算ベクトル出力桁上げ 114 とを与えるように、ベクトル入力和 94[1] と、ベクトル入力桁上げ 96[1] とを累算することができるようになる。

## 【0071】

10

[0083] 累算器ブロック 72 中の桁上げ保存累算器 72[1] は、図 9B に示すように、NCI 139(0) および NCI 制御入力 142(0) によってゲートされる NCI ゲート 140(0) も含むことに留意されたい。ただし、桁上げ保存累算器 72[0] が単一累算演算の最下位ビットを累算するので、NCI 制御入力 142(0) と NCI 139(0) の両方は、本実施形態では論理「0」に結び付けられる。桁上げ保存累算器 72[1] の圧縮器 108(0) は、桁上げ伝搬入力 144(1) も含むが、桁上げ伝搬入力 144(1) は、本実施形態では、累算器 72[1] に NCO 12(1) を生成させないために、論理「0」に結び付けられることにも留意されたい。桁上げ保存累算器 72[1] は、本実施形態では、次の累算器への桁上げ伝搬を実施する必要はなく、というのは、本実施形態において設けられる桁上げ保存累算器 72[1] を超える、累算器ブロック 72 の別の累算器がないからである。

## 【0072】

20

[0084] 図 9C は、図 8 の同じ累算器ブロック 72 の別の累算器モードの配線図である。この点において、図 9C は、桁上げ保存加算器と、それに続く、累算器ブロック 72 中で別の累算モードを提供するための単一累算器を提供するための、プログラムされたデータ経路構成を有する、図 8 の累算器ブロック 72 の概略図である。いくつかの累算演算は、複合算術を実施するための余剰加算器を必要とし得る。図 9C において、累算器 72[0]、72[1] は、16 ビット桁上げ保存加算器と、それに続く単一 24 ビット累算器を提供するために構成されたプログラム可能内部データ経路 80[0]、80[1] を有する。

30

## 【0073】

[0085] 図 9C を参照すると、累算器ブロック 72 が桁上げ保存加算器と、それに続く単一累算器中で構成されるときに累算器 72[0]、72[1] によって実施される累算の一般的なデータ経路が、プログラム可能データ経路 148 によって示されている。この点において、和桁上げセレクタ 120(0) は、マルチプレクサ 118(0) に、ベクトル入力和 94[1] と、ベクトル入力桁上げ 96[0] とを制御ゲート 134(0)、136(0) に与えさせるように、ベクトル命令復号の結果として生成される。制御入力 138(0) は、制御ゲート 134(0)、136(0) に、ベクトル入力和 94[1] と、ベクトル入力桁上げ 96[1] とを圧縮器 108(0) へ与えさせるように、桁上げ保存累算器 72[0] のプログラム可能内部データ経路 80[1] をプログラムするよう アクティブにされる。ベクトル入力和 94[1] およびベクトル入力桁上げ 96[1] は、累算ベクトル出力和 112(0) と、累算ベクトル出力桁上げ 114(0) とを与えるように、桁上げ保存累算器 72[0] の圧縮器 108(0) によって、ベクトル入力和 94[0] およびベクトル入力桁上げ 96[1] と累算される。累算ベクトル出力和 112(0) およびシフトされた累算ベクトル出力桁上げ 117(0) は、桁上げ保存加算器を設けるように、プログラム可能出力データ経路 74[0] (図 3 も参照) 中で累算器出力サンプルセット 76[0] として与えられる。シフトされた累算ベクトル出力桁上げ 117(0) は、24 ビット累算器としての、累算ベクトル出力和 112(1) と、シフトされた累算ベクトル出力桁上げ 117(1) とを、プログラム可能出力データ経路 74[1] (図 3 も参照) 中で累算器出力サンプルセット 76[1] として与えるようにベクトル

40

50

入力和 94 [1] およびベクトル入力桁上げ 96 [1] に累算されるために、マルチブレクサ 104 (1) によって圧縮器 108 (1) に与えられるように、プログラム可能データ経路 148 中に示される桁上げ保存累算器 72 [1] にも与えられる。

#### 【0074】

[0086] 図 2 および図 3 の VPE 22 を含むが、それに限定されない、ベクトル処理のためであるとともに、本明細書において論じた概念および実施形態によるプログラム可能データ経路構成を有する VPE は、どのプロセッサベースのデバイス中に設けられても、統合されてもよい。例としては、限定はしないが、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラーフォン、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末 (PDA)、モニタ、コンピュータモニタ、テレビジョン、チューナー、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク (DVD) プレーヤ、およびポータブルデジタルビデオプレーヤがある。

#### 【0075】

[0087] この点において、図 10 は、プロセッサベースのシステム 150 の例を示す。この例では、プロセッサベースのシステム 150 は、各々が 1 つまたは複数のプロセッサまたはコア 154 を含む、1 つまたは複数の処理装置 (PU) 152 を含む。PU 152 は、非限定的例として、図 2 のベースバンドプロセッサ 20 であってよい。プロセッサ 154 は、非限定的例として、図 2 に挙げたベースバンドプロセッサ 20 のようなベクトルプロセッサであってよい。この点において、プロセッサ 154 は、図 2 の VPE 22 を含むが、それに限定されない VPE 156 も含み得る。PU 152 は、一時的に記憶されたデータへの高速アクセスのためにプロセッサ 154 に結合されたキャッシュメモリ 158 を有し得る。PU 152 は、システムバス 160 に結合され、プロセッサベースのシステム 150 に含まれるマスタデバイスとスレーブデバイスとを相互結合し得る。よく知られているように、PU 152 は、システムバス 160 を介してアドレス、制御、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、PU 152 は、スレーブデバイスの例として、メモリコントローラ 162 にバストランザクション要求を通信することができる。図 10 には示されていないが、複数のシステムバス 160 が提供されてよく、ここにおいて、各システムバス 160 は異なる組織を構成する。

#### 【0076】

[0088] 他のマスタおよびスレーブデバイスが、システムバス 160 に接続され得る。図 10 に示すように、これらのデバイスは、例として、メモリシステム 164 と、1 つまたは複数の入力デバイス 166 と、1 つまたは複数の出力デバイス 168 と、1 つまたは複数のネットワークインターフェースデバイス 170 と、1 つまたは複数のディスプレイコントローラ 172 とを含み得る。メモリシステム 164 は、メモリコントローラ 162 によってアクセス可能なメモリ 165 を含み得る。入力デバイス 166 は、限定はしないが、入力キー、スイッチ、音声プロセッサなどを含む、任意のタイプの入力デバイスを含むことができる。出力デバイス 168 は、限定はしないが、オーディオ、ビデオ、他の視覚的インジケータなどを含む、任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス 170 は、ネットワーク 174 との間でデータの交換を可能にするように構成された任意のデバイスであり得る。ネットワーク 174 は、限定はしないが、ワイヤードまたはワイヤレスネットワーク、プライベートまたは公共ネットワーク、ローカルエリアネットワーク (LAN)、ワイドローカルエリアネットワーク (WLAN)、およびインターネットを含む、任意のタイプのネットワークであってよい。ネットワークインターフェースデバイス 170 は、所望の任意のタイプの通信プロトコルをサポートするように構成され得る。

#### 【0077】

[0089] CPU 152 は、1 つまたは複数のディスプレイ 178 に送られる情報を制御

10

20

30

40

50

するため、システムバス 160 を介してディスプレイコントローラ 172 にアクセスするようにも構成され得る。ディスプレイコントローラ 172 は、1つまたは複数のビデオプロセッサ 180 を介して表示されるべき情報をディスプレイ 178 に送り、1つまたは複数のビデオプロセッサ 180 は、表示されるべき情報をディスプレイ 178 に好適なフォーマットに処理する。ディスプレイ 178 は、限定はしないが、陰極線管 (CRT)、液晶ディスプレイ (LCD)、プラズマディスプレイなどを含む、任意のタイプのディスプレイを含むことができる。

#### 【0078】

[0090] 本明細書で開示する二重電圧ドメインメモリバッファの実施形態とともに説明する様々な例示的な論理プロック、モジュール、回路、およびアルゴリズムは、電子的なハードウェアとして、メモリもしくは別のコンピュータ可読媒体に記憶されプロセッサもしくは他の処理デバイスにより実行される命令として、またはこれら両方の組合せとして実装され得ることが、当業者にはさらに理解されよう。本明細書に記載されるアービタ、マスタデバイス、およびスレーブデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路 (IC)、またはICチップに採用され得る。本明細書で開示するメモリは、どのタイプおよびサイズのメモリでもよく、所望されるどのタイプの情報も記憶するように構成され得る。この互換性を明確に示すために、様々な例示的な構成要素、プロック、モジュール、回路、およびステップについて、上記では概してそれらの機能性について記載された。そのような機能性がどのように実装されるかは、特定の用途、設計選択、および / または全体的なシステムに課された設計制約に依存する。当業者は、各特定の用途について様々な様式で記載された機能性を実装することができるが、そのような実装決定は、本開示の範囲からの逸脱を引き起こすと解釈されるべきでない。10

#### 【0079】

[0091] 本明細書に開示された実施形態に関連して記載された、様々な例示的論理プロック、モジュール、および回路は、本明細書に記載の機能を実施するよう設計された、プロセッサ、DSP、特定用途向け集積回路 (ASIC)、FPGA または他のプログラマブル論理デバイス、個別ゲートまたはトランジスタロジック、個別ハードウェア構成要素、またはその任意の組合せを用いて実装または実施され得る。プロセッサはマイクロプロセッサであり得るが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであり得る。プロセッサはまた、コンピューティングデバイスの組合せ、たとえば、DSP とマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、DSP コアと連携する 1 つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成としても実装され得る。20

#### 【0080】

[0092] 本明細書で開示する実施形態は、ハードウェアにおいて、およびハードウェアに記憶された命令において実施されてよく、たとえば、ランダムアクセスメモリ (RAM)、フラッシュメモリ、読み取り専用メモリ (ROM)、電気的プログラマブル ROM (E PROM)、電気的消去可能プログラマブル ROM (EEPROM (登録商標))、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られている任意の他の形態のコンピュータ可読記憶媒体中に常駐し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み出し、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替形態において、記憶媒体はプロセッサと一体であってもよい。プロセッサおよび記憶媒体は ASIC 内に存在し得る。ASIC は遠隔局中に常駐し得る。代替として、プロセッサおよび記憶媒体は、個別構成要素として遠隔局、基地局、またはサーバ中に存在してよい。30

#### 【0081】

[0093] また、本明細書の例示的な実施形態のいずれかにおいて記載された動作ステップは、例および説明を提供するために記載されたものであることにやはり留意されたい。説明された動作は、例示された順序以外の多くの異なる順序で実施されてもよい。さらに、单一の動作ステップで説明される動作は、実際には、多くの異なるステップで実施され40

得る。加えて、例示的な実施形態において議論された1つまたは複数の動作ステップは組み合わされ得る。フローチャート図に示した動作ステップは、当業者には容易に明らかになるように、多数の様々な修正を受け得ることを理解されたい。情報および信号は、多種多様な技術および技法のいずれかを使用して表され得ることも、当業者には理解されよう。たとえば、上記の説明全体にわたって言及され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁界もしくは磁性粒子、光場もしくは光子、またはそれらの任意の組合せによって表され得る。

#### 【0082】

[0094] 本開示の前の記載は、当業者が本開示を製造または使用することを可能にするように提供される。本開示に対する様々な変更形態が、当業者には容易に明らかとなり、本明細書に規定の一般的な原理が、本開示の精神または範囲から逸脱することなく、他の変形形態に適用され得る。したがって、本開示は、本明細書に記載される例および設計に限定することを意図しておらず、本明細書に開示される、原理および新規の特徴と一致する最も広い範囲が与えられるべきである。10

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

#### [C1]

ベクトルデータのマルチモードベクトル処理を行うように構成されたベクトル処理エンジン（VPE）であって、

複数の入力データ経路の中のある入力データ経路中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセットを与えるように構成された入力読み取り段階と、20

複数のベクトル処理ブロックを備える少なくとも1つのベクトル処理段階と、前記複数のベクトル処理ブロックの中の各ベクトル処理ブロックは、

前記複数の入力データ経路中の少なくとも1つの入力データ経路から、前記複数のベクトルデータ入力サンプルセットからの少なくとも1つのベクトルデータ入力サンプルセットを受信し、

前記少なくとも1つのベクトル処理段階によって実行されるベクトル命令に従って、前記ベクトル処理ブロック用のプログラム可能データ経路構成に基づいて少なくとも1つのベクトル結果出力サンプルセットを与えるように、前記少なくとも1つのベクトルデータ入力サンプルセットを処理し、

複数の出力データ経路の中の少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される、30

前記複数のベクトル処理ブロックの各々から前記少なくとも1つのベクトル結果出力サンプルセットを受信するように構成された出力処理段階と、を備えるVPE。

#### [C2]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に基づいて再構成されるように構成される、C1に記載のVPE。

#### [C3]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理段階によって実行される各ベクトル命令用に再構成されるように構成される、C2に記載のVPE。40

#### [C4]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令の各クロック周期において再構成されるように構成される、C2に記載のVPE。

#### [C5]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、プログラム可能入力データ経路構成からなり、

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記プログラム可能入力データ経路構成に50

基づいて前記複数の入力データ経路の中の前記少なくとも1つの入力データ経路から前記少なくとも1つのベクトルデータ入力サンプルセットを受信するように構成される、C 1に記載のV P E。

[ C 6 ]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、さらに、前記少なくとも1つのベクトル処理ブロック用のプログラム可能出力データ経路構成からなり。

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記プログラム可能出力データ経路構成に基づいて前記複数の出力データ経路の中の前記少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される、C 5に記載のV P E。 10

[ C 7 ]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、さらに、前記少なくとも1つのベクトル処理ブロック用のプログラム可能ベクトル処理ブロックデータ経路構成からなり。

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記プログラム可能ベクトル処理ブロックデータ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与るために、前記少なくとも1つのベクトルデータ入力サンプルセットを処理するように構成される、C 6に記載のV P E。 20

[ C 8 ]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理ブロック用のプログラム可能出力データ経路構成からなり。

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記プログラム可能出力データ経路構成に基づいて前記複数の出力データ経路の中の前記少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される、C 1に記載のV P E。 30

[ C 9 ]

前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成は、前記少なくとも1つのベクトル処理ブロック用のプログラム可能ベクトル処理ブロックデータ経路構成からなり。

前記複数のベクトル処理ブロックの各々は、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記プログラム可能ベクトル処理ブロックデータ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与るために、前記少なくとも1つのベクトルデータ入力サンプルセットを処理するように構成される、C 1に記載のV P E。 40

[ C 1 0 ]

前記少なくとも1つのベクトル処理ブロックは、少なくとも1つの乗算器ブロックおよび少なくとも1つの累算器ブロックのうちの少なくとも1つからなる、C 1に記載のV P E。

[ C 1 1 ]

前記少なくとも1つのベクトル処理段階は複数のベクトル処理段階からなる、C 1に記載のV P E。

[ C 1 2 ]

前記少なくとも1つのベクトル処理段階は、複数の乗算器ブロックからなる少なくとも1つの乗算ベクトル処理段階および複数の累算器ブロックからなる少なくとも1つの累算ベクトル処理段階からなり、 50

前記複数の乗算器ブロックの中の各乗算器ブロックは、

前記複数のベクトルデータ入力サンプルセットからの第1のベクトルデータ入力サンプルセットと第2のベクトルデータ入力サンプルセットとを、前記複数の入力データ経路の中の第1の入力データ経路および第2の入力データ経路から受信し、

前記少なくとも1つの第1のベクトル処理段階によって実行されるベクトル命令に従って、前記乗算器ブロック用のプログラム可能乗算データ経路構成に基づいて複数の乗算出力データ経路の中のある乗算出力データ経路中でベクトル乗算出力サンプルセットを与えるために、前記第1のベクトルデータ入力サンプルセットを前記第2のベクトルデータ入力サンプルセットに乗算するように構成され、

前記複数の累算器ブロックの中の各累算器ブロックは、

10

複数の乗算出力データ経路の中の第1の乗算出力データ経路および第2の乗算出力データ経路から、それぞれ、第1の乗算出力サンプルセットと第2の乗算出力サンプルセットとを受信し、

前記少なくとも1つの第2のベクトル処理段階によって実行されるベクトル命令に従って、前記累算器ブロック用のプログラム可能データ経路構成に基づいてベクトル累算結果サンプルセットを与えるために、前記第1の乗算出力サンプルセットを前記第2の乗算出力サンプルセットと累算し、

前記複数の複数の出力データ経路の中の前記出力データ経路中で前記ベクトル累算結果サンプルセットを与えるように構成される、C1に記載のVPE。

[ C 1 3 ]

20

前記少なくとも1つのベクトル処理ブロックは、最小の1つのベクトル結果出力サンプルセットをベクトルレジスタに記憶するように構成されない、C1に記載のVPE。

[ C 1 4 ]

各ベクトル処理ブロックは、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて異なるビット幅の前記複数のベクトルデータ入力サンプルセットを処理するようにさらに構成される、C1に記載のVPE。

[ C 1 5 ]

各ベクトル処理ブロックは、前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて符号付きの少なくとも1つのベクトルデータ入力サンプルセットまたは符号なしの少なくとも1つのベクトルデータ入力サンプルセットを処理するようにさらに構成される、C1に記載のVPE。

30

[ C 1 6 ]

前記少なくとも1つのベクトル処理段階は、符号付きの演算命令からなる前記ベクトル命令を実行するように構成される、C1に記載のVPE。

[ C 1 7 ]

前記少なくとも1つのベクトル処理段階は、符号なし演算命令からなる前記ベクトル命令を実行するように構成される、C1に記載のVPE。

[ C 1 8 ]

40

ベクトルデータのマルチモードベクトル処理を行うように構成されたベクトル処理エンジン(VPE)であって、

複数の入力データ経路の中のある入力データ経路中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセットを与えるように構成された入力読み取り段階手段と、

複数のベクトル処理手段を備える少なくとも1つのベクトル処理段階手段と、前記複数のベクトル処理手段の中の各ベクトル処理手段は、

前記複数の入力データ経路の中の少なくとも1つの入力データ経路から、前記複数のベクトルデータ入力サンプルセットからの少なくとも1つのベクトルデータ入力サンプルセットを受信し、

前記少なくとも1つのベクトル処理段階手段によって実行されるベクトル命令に従つ

50

て、前記ベクトル処理手段用のプログラム可能データ経路構成に基づいて少なくとも1つのベクトル結果出力サンプルセットを与えるように、前記少なくとも1つのベクトルデータ入力サンプルセットを処理し、

複数の出力データ経路の中の少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えるように構成される、

前記複数のベクトル処理手段の各々から前記少なくとも1つのベクトル結果出力サンプルセットを受信するように構成された出力処理段階手段と、を備えるVPE。

#### [ C 19 ]

ベクトル処理エンジン(VPE)中でベクトルデータを処理する方法であって、

入力処理段階中の複数の入力データ経路の中のある入力データ経路中で、ベクトルアレイの幅の複数のベクトルデータ入力サンプルセットを与えることと、10

少なくとも1つのベクトル処理段階中の複数のベクトル処理ブロックにおいて、前記複数のベクトルデータ入力サンプルセットを処理することと、前記複数のベクトル処理ブロックの各々において、

前記複数の入力データ経路の中の少なくとも1つの入力データ経路から、前記複数のベクトルデータ入力サンプルセットからの少なくとも1つのベクトルデータ入力サンプルセットを受信することと、

前記少なくとも1つのベクトル処理段階によって実行されるベクトル命令に従って、前記ベクトル処理ブロック用のプログラム可能データ経路構成に基づいて少なくとも1つのベクトル結果出力サンプルセットを与えるように、前記少なくとも1つのベクトルデータ入力サンプルセットを処理することと、20

複数の出力データ経路の中の少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを与えることと、を備える、

出力処理段階中の前記複数のベクトル処理ブロックの各々から前記少なくとも1つのベクトル結果出力サンプルセットを受信することと、を備える方法。

#### [ C 20 ]

前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に基づいて、前記複数のベクトル処理ブロックの各々用の前記プログラム可能データ経路構成を再構成することをさらに備える、C 19 に記載の方法。

#### [ C 21 ]

前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記プログラム可能入力データ経路構成に基づいて前記複数の入力データ経路の中の前記少なくとも1つの入力データ経路から前記複数のベクトルデータ入力サンプルセットからの前記少なくとも1つのベクトルデータ入力サンプルセットを受信することと、

前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能入力データ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与えるように前記少なくとも1つのベクトルデータ入力サンプルセットを処理することと、を備える、C 19 に記載の方法。

#### [ C 22 ]

前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、プログラム可能出力データ経路構成に基づいて前記複数の出力データ経路の中の前記少なくとも1つの出力データ経路中で前記少なくとも1つのベクトル結果出力サンプルセットを受信することを備える、C 19 に記載の方法。

#### [ C 23 ]

前記少なくとも1つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用のプログラム可能ベクトル処理ブロックデータ経路構成に基づいて前記少なくとも1つのベクトル結果出力サンプルセットを与えるように前記少なくとも1つのベクトルデータ入力サンプルセットを処理することを備える、C 19 に記載の方法。

#### [ C 24 ]

10

20

30

40

50

最小の 1 つのベクトル結果出力サンプルセットをベクトルレジスタに記憶しないことをさらに備える、C 19 に記載の方法。

[ C 25 ]

前記少なくとも 1 つのベクトルデータ入力サンプルセットを処理することは、前記少なくとも 1 つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて異なるビット幅の前記複数のベクトルデータ入力サンプルセットを処理することを備える、方法 C 19。

[ C 26 ]

前記少なくとも 1 つのベクトルデータ入力サンプルセットを処理することは、前記少なくとも 1 つのベクトル処理段階によって実行される前記ベクトル命令に従って、前記ベクトル処理ブロック用の前記プログラム可能データ経路構成に基づいて符号付きの少なくとも 1 つのベクトルデータ入力サンプルセットまたは符号なしの少なくとも 1 つのベクトルデータ入力サンプルセットを処理することを備える、C 19 に記載の方法。10

[ C 27 ]

前記入力処理段階における前記複数の入力データ経路の中の前記入力データ経路中で、第 2 の幅の前記ベクトルアレイの第 2 の複数のベクトルデータ入力サンプルセットを与えることと、

前記少なくとも 1 つのベクトル処理段階中の前記複数のベクトル処理ブロックにおいて前記第 2 の複数のベクトルデータ入力サンプルセットを処理することと、前記複数のベクトル処理ブロックの各々において、20

前記複数の入力データ経路の中の前記第 2 の少なくとも 1 つの入力データ経路から、前記第 2 の複数のベクトルデータ入力サンプルセットからの少なくとも 1 つのベクトルデータ入力サンプルセットを受信することと、

前記少なくとも 1 つのベクトル処理段階によって実行される第 2 のベクトル命令に従って、前記ベクトル処理ブロック用の第 2 のプログラム可能データ経路構成に基づいて第 2 の少なくとも 1 つのベクトル結果出力サンプルセットを与えるように、前記第 2 の少なくとも 1 つのベクトルデータ入力サンプルセットを処理することと、

前記複数の出力データ経路の中の前記少なくとも 1 つの出力データ経路中で前記第 2 の少なくとも 1 つのベクトル結果出力サンプルセットを与えることと、を備え、30

前記出力処理段階中の前記複数のベクトル処理ブロックの各々から前記第 2 の少なくとも 1 つのベクトル結果出力サンプルセットを受信することと、をさらに備える、C 19 に記載の方法。

[ C 28 ]

前記第 1 の幅とは異なる前記第 2 の幅の前記ベクトルアレイの前記第 2 の複数のベクトルデータ入力サンプルセットを、前記入力処理段階における前記複数の入力データ経路の中の前記入力データ経路中で与えることを備える、C 27 に記載の方法。

[ C 29 ]

前記複数のベクトル処理ブロック中で前記複数のベクトルデータ入力サンプルセットを処理することは、前記複数の乗算器ブロック中で前記複数のベクトルデータ入力サンプルセットを処理することを備え、40

前記複数のベクトル処理ブロック中で前記第 2 の複数のベクトルデータ入力サンプルセットを処理することは、前記複数の累算器ブロック中で前記第 2 の複数のベクトルデータ入力サンプルセットを処理することを備える、C 27 に記載の方法。

[ C 30 ]

前記複数の乗算器ブロックでの前記複数のベクトルデータ入力サンプルセットの処理は、前記複数の累算器ブロック中で前記第 2 の複数のベクトルデータ入力サンプルセットを処理することを備える、前記複数のベクトル処理ブロックでの前記第 2 の複数のベクトルデータ入力サンプルセットの前記処理と同時に起こる、C 29 に記載の方法。

【図1】

【図2】

FIG. 1

FIG. 2

【図3】

【図4A】

FIG. 4A

【図4B】

FIG. 4B

【図5】

【図 8】

【図 9 A】

FIG. 9A

【図 9 B】

【図 9 C】

FIG. 9C

【図10】

図10

FIG. 10

---

フロントページの続き

(72)発明者 カーン、ラヘル

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 田中 幸雄

(56)参考文献 特表2009-505215(JP,A)

特開2009-181509(JP,A)

特開2006-39790(JP,A)

米国特許出願公開第2007/0185953(US,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 17/16

G06F 9/38