(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

COURBEVOIE

(11) Nº de publication : **3 024 930**

(à n'utiliser que pour les commandes de reproduction)

(21) Nº d'enregistrement national : **14 57764**

(51) Int Cl<sup>8</sup> : **H 03 M 1/00 (2014.01)**

(12)

## BREVET D'INVENTION

**B1**

(54) LIAISON SERIE A HAUT DEBIT.

(22) Date de dépôt : 12.08.14.

(30) Priorité :

(43) Date de mise à la disposition du public de la demande : 19.02.16 Bulletin 16/07.

(45) Date de la mise à disposition du public du brevet d'invention : 09.08.19 Bulletin 19/32.

(56) Liste des documents cités dans le rapport de recherche :

*Se reporter à la fin du présent fascicule*

(60) Références à d'autres documents nationaux apparentés :

Demande(s) d'extension :

(71) Demandeur(s) : STMICROELECTRONICS SA Société anonyme — FR.

(72) Inventeur(s) : GALY PHILIPPE.

(73) Titulaire(s) : STMICROELECTRONICS SA Société anonyme.

(74) Mandataire(s) : CABINET BEAUMONT.

### **LIAISON SERIE A HAUT DEBIT**

#### Domaine

La présente demande concerne le domaine de la transmission de données entre des circuits, et plus particulièrement une liaison de données série.

#### 5 Exposé de l'art antérieur

La transmission de données entre circuits à l'intérieur ou à l'extérieur d'une puce utilise généralement une interface parallèle ou une interface série.

Une interface parallèle a l'avantage de permettre un

10 débit de transmission de données relativement élevé, mais comme il faut  $N$  lignes et une ligne d'horloge pour transmettre  $N$  bits de données en parallèle, une telle solution occupe une relativement grande surface d'une puce, nécessite un grand nombre de broches d'entrée/sortie, et/ou entraîne une consommation relativement élevée due à la charge et à la décharge de la capacité de

15 chaque ligne.

Une interface série a l'avantage d'utiliser très peu de lignes de données, mais ne peut pas atteindre le même débit de données qu'une interface parallèle. En effet, le débit de

20 transmission maximal d'une ligne de données est limité par la capacité de la ligne, dont l'effet est de créer un filtre passe-bas. En outre, à cause de la charge et de la décharge de la

capacité de ligne à chaque changement d'état des données transmises, les interfaces série tendent à consommer une énergie relativement élevée.

Il existe donc un besoin dans la technique d'une interface de transmission et d'un procédé de transmission de données qui n'aient pas au moins l'un des inconvénients ci-dessus.

#### Résumé

Un objet de modes de réalisation de la présente description est de répondre au moins partiellement à un ou plusieurs besoins de l'art antérieur.

Selon un aspect, il est prévu un circuit de transmission de données transmettant un signal de données sur une ligne de transmission, ce circuit comprenant un convertisseur numérique-analogique, DAC, capable de générer  $2^N$  niveaux de tension continue différents, dans lequel le DAC est adapté à recevoir des valeurs numériques de N bits, et pour chaque valeur numérique, à sélectionner, en se basant sur les valeurs numériques, l'un des  $2^N$  niveaux de tension continue et à appliquer le niveau de tension continue sélectionné sur la ligne de transmission.

Selon un mode de réalisation, le DAC est adapté à appliquer, pour des valeurs numériques consécutives, les niveaux de tension continue sélectionnés lors des fronts montants et descendants d'un signal d'horloge.

Selon un mode de réalisation, le circuit de transmission de données comprend en outre un multiplexeur adapté à recevoir une pluralité de valeurs numériques de N bits en parallèle, et à multiplexer temporellement la pluralité des valeurs numériques de N bits et à les fournir en série au DAC.

Selon un mode de réalisation, le multiplexeur est adapté à recevoir deux groupes de valeurs numériques de N bits en parallèle, et à multiplexer temporellement les deux groupes de valeurs numériques de N bits lors des fronts montants et descendants d'un signal d'horloge.

Selon un mode de réalisation, le DAC comprend un amplificateur ayant une sortie couplée à la ligne transmission, l'amplificateur étant adapté à avoir  $2^N$  niveaux de gains différents pour générer  $2^N$  niveaux de tension continue 5 différents.

Selon un mode de réalisation, le circuit de transmission de données comprend en outre une ligne de sortie d'horloge transmettant un signal d'horloge vers un circuit de réception.

10 Selon un autre aspect, il est prévu un circuit de réception de données recevant un signal de données transmis sur une ligne de transmission, le circuit comprenant un convertisseur analogique-numérique, ADC, capable de différencier  $2^N$  niveaux de tension continue différents, dans lequel l'ADC est 15 adapté à détecter des niveaux de tension continue sur la ligne de transmission, à convertir chaque niveau de tension continue détecté en une valeur de données de N bits correspondante et à fournir des valeurs de données de N bits à une sortie de l'ADC.

20 Selon un mode de réalisation, l'ADC est adapté à générer des valeurs numériques consécutives de N bits, en se basant sur des niveaux de tension continue consécutifs, lors des fronts montants et descendants d'un signal d'horloge.

25 Selon un mode de réalisation, le circuit de transmission de données comprend en outre un démultiplexeur adapté à recevoir en série des valeurs de données de N bits à la sortie de l'ADC et à générer une pluralité de valeurs numériques de N bits en parallèle en démultiplexant temporellement une pluralité des valeurs numériques de N bits.

30 Selon un mode de réalisation, le démultiplexeur est adapté, à générer deux valeurs numériques de N bits en parallèle en démultiplexant temporellement la pluralité de valeurs numériques de N bits lors des fronts montants et descendants d'un signal d'horloge.

35 Selon un mode de réalisation, l'ADC comprend un réseau de résistances adapté à générer  $2^N-1$  niveaux de tension de réfé-

rence, et  $2^N-1$  comparateurs adaptés à comparer l'un des niveaux de tension de référence correspondant à chaque niveau de tension continue détecté sur la ligne de transmission.

5 Selon un autre aspect, il est prévu une interface de transmission de données intégrée à un circuit intégré comprenant le circuit de transmission de données ci-dessus ; le circuit de réception de données ci-dessus ; et une ligne de transmission connectant le circuit de transmission de données au circuit de réception de données.

10 Selon un autre aspect, il est prévu une interface de transmission de données transmettant des données entre des circuits intégrés comprenant un premier circuit intégré comprenant le circuit de transmission de données ci-dessus ; un second circuit intégré comprenant le circuit de réception de données 15 ci-dessus ; et une ligne de transmission connectant le circuit de transmission de données au circuit de réception de données.

Selon un autre aspect, il est prévu un procédé de transmission d'un signal de données sur une ligne de transmission, ce procédé comprenant la réception, par un convertisseur numérique-analogique, DAC, capable de générer  $2^N$  niveaux de tension continue différents, des valeurs numériques de N bits ; et, pour chaque valeur numérique la sélection, sur la base de la valeur numérique, d'un des  $2^N$  niveaux de tension de référence ; et l'application du niveau de tension continue 25 sélectionné sur la ligne de transmission.

Selon un autre aspect, il est prévu un procédé de réception d'un signal de données transmis sur une ligne de transmission, le procédé comprenant la détection, par un convertisseur analogique-numérique, ADC, capable de différencier  $2^N$  30 niveaux de tension continue, de niveaux de tension continue sur la ligne de transmission ; la conversion de chaque niveau de tension continue détecté en une valeur de données de N bits correspondante, et la fourniture des valeurs de données de N bits à une sortie de l'ADC.

Brève description des dessins

Ces caractéristiques et avantages, ainsi que d'autres, seront exposés en détail dans la description suivante de modes de réalisation particuliers faite à titre illustratif et non limitatif en relation avec les figures jointes parmi lesquelles :

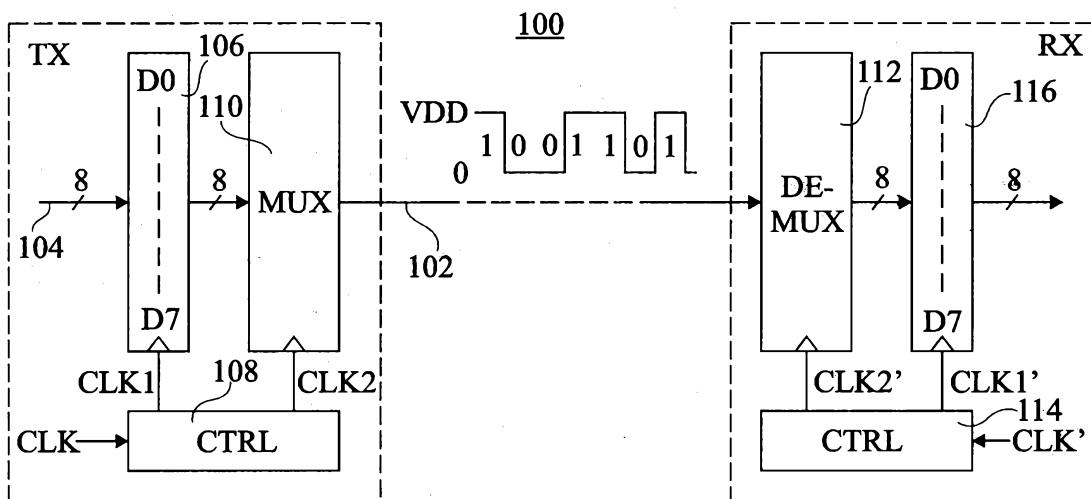

la figure 1 représente schématiquement un exemple de système de transmission de données série ;

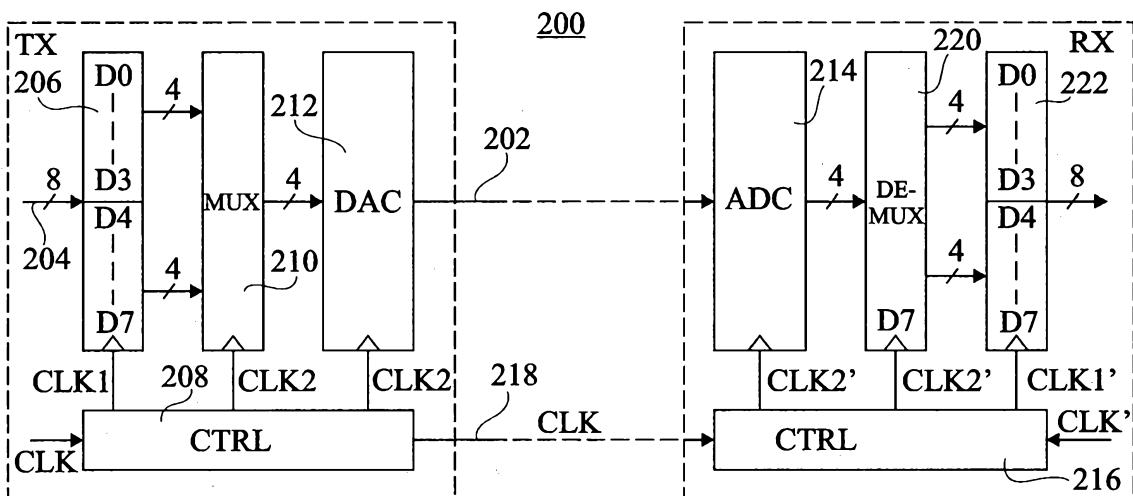

la figure 2 représente schématiquement un système de transmission de données série utilisant plusieurs niveaux de tension selon un exemple de réalisation de la présente description ;

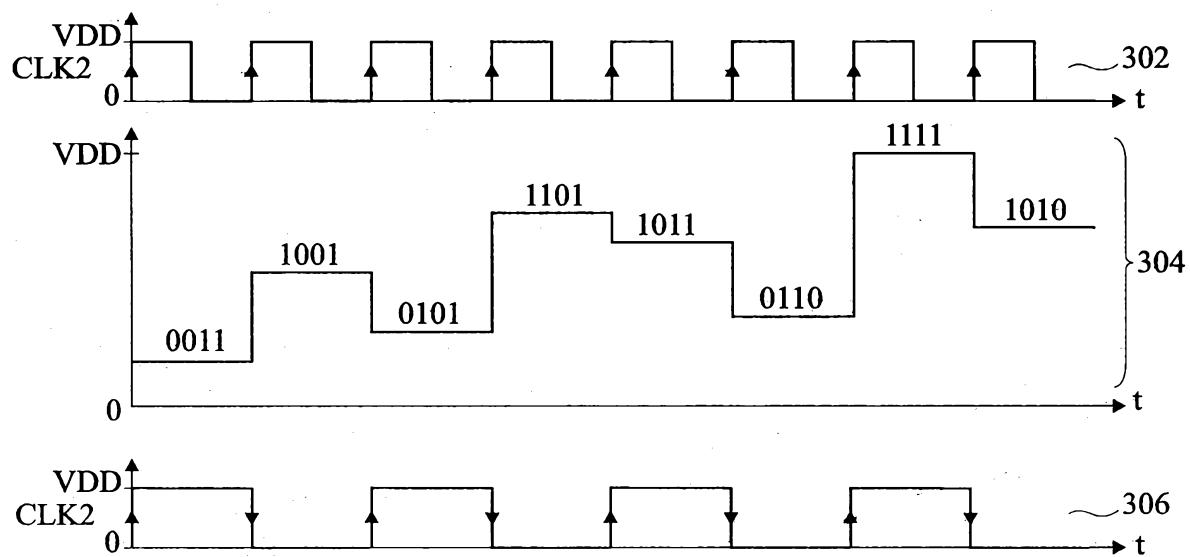

la figure 3 est un chronogramme illustrant des signaux du circuit de la figure 2 selon un exemple de réalisation de la présente description ;

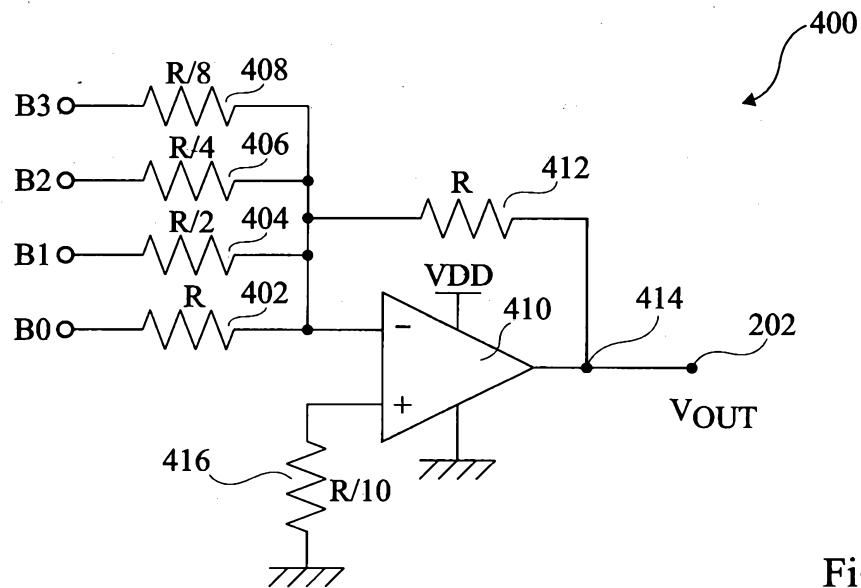

la figure 4 représente schématiquement et plus en détail un convertisseur numérique-analogique du circuit de la figure 2 selon un exemple de réalisation de la présente description ; et

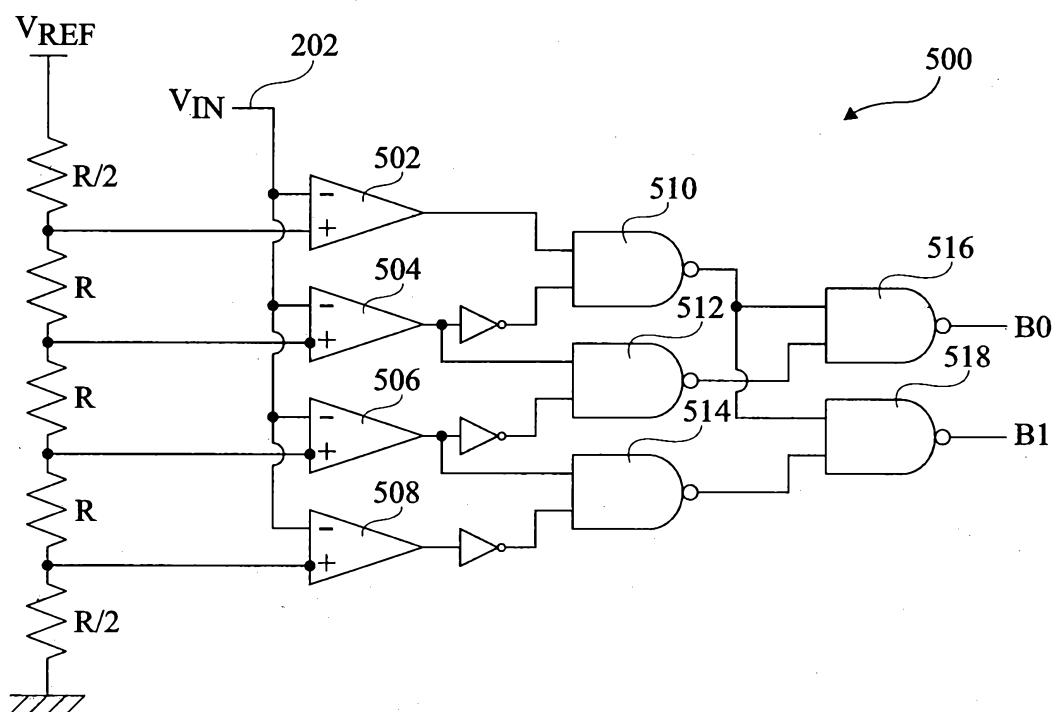

la figure 5 représente schématiquement et plus en détail un convertisseur analogique-numérique du circuit de la figure 2 avec plus de détails selon un exemple de réalisation de la présente description.

Description détaillée

Tout au long de la description suivante, le terme "connecté" est utilisé pour désigner une connexion directe entre deux éléments, tandis que le terme "couplé" est utilisé pour désigner une connexion qui peut être directe ou être réalisée par l'intermédiaire d'un ou de plusieurs éléments intermédiaires tels que des résistances, des condensateurs ou des transistors.

La figure 1 représente schématiquement un système de transmission de données série 100 comprenant un côté transmission TX lié à un côté réception RX par l'intermédiaire d'une ligne de transmission 102.

Le côté transmission TX comprend un bus 8 bits 104 ayant des bits de données D0 à D7 synchronisés par une bascule

106 sur la base d'un signal d'horloge CLK1 fourni par un bloc de commande (CTRL) 108. La sortie 8 bits de la bascule 106 est connectée à un multiplexeur 110, qui transforme le signal parallèle en un signal série par multiplexage temporel des 8 bits D0

5 à D7 sur la ligne de transmission 102 sur la base d'un signal d'horloge CLK2 fourni également par le bloc de commande 108. Le signal d'horloge CLK2 a une fréquence huit fois plus grande que celle du signal d'horloge CLK1. Le bloc de commande 108 génère les signaux d'horloge CLK1 et CLK2 sur la base d'un signal

10 d'horloge CLK du côté transmission.

Le côté réception RX comprend un démultiplexeur 112, qui démultiplexe le signal série venant de la ligne de transmission 102 pour régénérer un signal de données parallèle de 8 bits sur la base d'un signal d'horloge CLK2' fourni par un bloc 15 de commande (CTRL) 114. Les 8 bits D0 à D7 fournis par le démultiplexeur 112 sont ensuite synchronisés par une bascule 116 sur la base d'un signal d'horloge CLK1'. Les signaux d'horloge CLK1' et CLK2' sont fournis par le bloc de commande 114 sur la base d'un signal d'horloge CLK' du côté réception. Par exemple,

20 un protocole basé sur des bits de début et de fin transmis sur la ligne de transmission 102 est utilisé pour permettre la génération de l'horloge CLK2' sans liaison directe.

Un exemple du signal série généré pour un groupe de huit bits D0 à D7 est représenté en figure 1 au-dessus de la ligne de transmission 102 selon un code NRZ (Pas de Retour à Zéro / Non-Return-to-Zero). Comme cela est représenté, le signal est par exemple au niveau de la masse 0 lorsque le bit de données est un 0 logique, et au niveau d'une tension d'alimentation VDD lorsque le bit de données est un 1 logique. Le débit de transmission 30 maximum de bits est défini en se basant sur le cas le plus défavorable dans lequel le signal présente une transition à chaque front d'horloge significatif, et comme cela a été expliqué dans la section de l'art antérieur ci-dessus, ce débit est limité par la capacité de la ligne de transmission 102. Par 35 conséquent, pour augmenter le débit de transmission, il n'est

pas possible d'augmenter simplement la fréquence de transmission.

La figure 2 représente schématiquement un système de transmission de données 200 selon un exemple de réalisation. Le système 200 comprend un côté transmission TX lié à un côté réception RX par l'intermédiaire d'une ligne de transmission 202. Dans certains modes de réalisation, les côtés transmission et réception correspondent à deux portions différentes d'un même circuit intégré, et la ligne de transmission 202 correspond par exemple à une piste conductrice couplant les deux portions. Dans des variantes de réalisation, les côtés transmission et réception appartiennent à des circuits intégrés différents, et la ligne de transmission 202 est une piste ou un fil conducteur connectant des broches d'entrée/sortie des circuits intégrés.

Le côté transmission TX comprend par exemple un bus de données parallèles 204 fournissant un signal de données parallèles à une bascule 206. Dans l'exemple de la figure 2, le signal de données parallèles est un signal 8 bits, bien que différentes tailles puissent être prévues. La bascule 206 est cadencée par un signal d'horloge CLK1 fourni par un bloc de commande (CTRL) 208. La bascule 206 fournit par exemple le signal parallèle en M blocs de N bits à un multiplexeur 210. M et N sont par exemple des entiers dont chacun est égal à 2 ou plus. Dans l'exemple de la figure 2, M est égal à 2 et N est égal à 4. Le multiplexeur 210 multiplexe temporellement les M blocs de bits afin de générer un flux de N bits, sur la base d'un signal d'horloge CLK2 fourni par le bloc de commande 208. La fréquence du signal d'horloge CLK2 est par exemple M fois plus grande que celle du signal d'horloge CLK1. A titre de variante, dans certains modes de réalisation, le multiplexeur fournit des valeurs de données de N bits sur les fronts montants et descendants du signal d'horloge CLK2, auquel cas le signal d'horloge CLK2 a par exemple une fréquence égale à M/2 fois la fréquence du signal d'horloge CLK1. Le bloc de commande 208 génère par exemple les signaux d'horloges CLK1 et CLK2 sur la

base d'un signal d'horloge CLK. Dans d'autres variantes de réalisation, M peut être égal à 1, et le multiplexeur 210 peut alors être omis.

Le côté transmission TX comprend aussi un convertisseur numérique-analogique (DAC) 212, qui reçoit les valeurs numériques des N bits et convertit chaque valeur numérique en des niveaux de tension correspondants de 1 à  $2^N$  niveaux de tension continue. En particulier, le DAC est par exemple capable de générer  $2^N$  niveaux de tension continue différents, et de sélectionner l'un de ces niveaux de tension sur la base de chaque valeur de données à N bits. Le DAC applique ces niveaux de tension continue directement sur la ligne de transmission 202. En d'autres termes, il n'y a pas de modulation de porteuse, mais la ligne de transmission est amenée au niveau de chaque niveau de tension continue pendant la durée de transmission associée à chaque valeur de données.

Le côté réception RX comprend par exemple un convertisseur analogique-numérique (ADC) 214, qui détecte les niveaux de tension continue sur la ligne de transmission 202, et reconvertisit chaque niveau de tension continue en une valeur de données de N bits correspondante. En particulier, l'ADC 214 est par exemple apte à différencier  $2^N$  niveaux de tension continue différents. La conversion est par exemple basée sur le signal d'horloge CLK2' fourni par un bloc de commande (CTRL) 216, qui est à la même fréquence que le signal d'horloge CLK2 du côté transmission. Dans certains modes de réalisation, le signal d'horloge CLK2' est généré par un bloc de commande 216 à partir d'un signal d'horloge CLK' du côté réception. Par exemple, un protocole est mis en oeuvre dans lequel des bits de début et de fin sont transmis sur la ligne de transmission 202 pour permettre la génération du signal d'horloge CLK2' à partir du signal d'horloge CLK' sans liaison directe entre les côtés transmission et réception. Dans des variantes de réalisation, le signal d'horloge CLK2' peut être généré par le bloc de commande

216 sur la base d'un signal d'horloge CLK fourni par le côté transmission TX sur une ligne de transmission d'horloge 218.

Les valeurs numériques à N bits générées par l'ADC 214 sont par exemple fournies par un démultiplexeur 220, qui 5 démultiplexe temporellement le signal sur la base du signal d'horloge CLK2' pour générer un signal de données parallèle ayant M groupes de N bits. Le signal de données parallèle est par exemple fourni par l'intermédiaire d'une bascule 222 cadencée par le signal d'horloge CLK1' fourni par le bloc de 10 commande 216. Le signal d'horloge CLK1' a par exemple la même fréquence que le signal d'horloge CLK1 du côté transmission.

La figure 3 est un chronogramme illustrant, en 302, un exemple d'un signal d'horloge CLK2, et en 304 un exemple d'un signal série généré par le DAC 212, dans le cas où N est égal à 15 4 et M est égal à 2. L'exemple de la figure 3 illustre 8 valeurs de données consécutives de quatre bits ayant respectivement les valeurs 0011, 1001, 0101, 1101, 1011, 0110, 1111 et 1010. Chaque valeur numérique est convertie en un niveau de tension continue, et dans l'exemple de la figure 3, la valeur 0000 est représentée 20 par la masse, et la valeur 1111 est représentée par le niveau de tension d'alimentation VDD, qui est par exemple comprise entre 1 et 5 V. Les 14 autres valeurs de données numériques à 4 bits possibles, de 0001 à 1110, sont représentées par des niveaux de tension continue intermédiaires correspondants entre la masse et 25 VDD. Chaque niveau de tension continue est par exemple appliqué à partir d'un front montant du signal d'horloge CLK2 pendant toute la période d'horloge jusqu'au front montant suivant du signal d'horloge CLK2.

On notera à partir de la figure 3 qu'il sera généralement relativement rare que le niveau de tension continue varie de l'amplitude de VDD d'une valeur de données à une autre. Ceci est avantageux pour l'efficacité énergétique et pour réduire la contrainte de la fréquence de transmission maximum. Dans certains modes de réalisation, un codage autre que celui de la 35 figure 3 peut être appliqué selon lequel on affecte aux valeurs

des données apparaissant le plus fréquemment des valeurs de tension similaires, afin de réduire encore les variations de tension entre niveaux de tension continue successifs dans le signal.

5 La figure 3 illustre aussi, en 306, un exemple de signal d'horloge CLK2 selon une variante de réalisation dans laquelle les niveaux de tension continue changent lors des fronts montants et descendants du signal d'horloge CLK2. Ainsi, chaque niveau de tension continue est appliqué sur la ligne de

10 transmission 202 seulement pendant une demi-période d'horloge et, pour une fréquence d'horloge donnée, les données peuvent être transmises à un débit deux fois plus rapide que celui des données transmises seulement sur un front d'horloge montant ou sur un front d'horloge descendant.

15 La figure 4 représente schématiquement un exemple d'un DAC 400 qui est par exemple utilisé pour implémenter le DAC 212 de la figure 2. Le DAC 400 est un DAC à bits pondérés convertissant une valeur de 4 bits [B0...B3] en l'un de 16 niveaux de tension continue. Cependant, l'homme de l'art saura comment

20 modifier le DAC 400 pour convertir un signal d'entrée à N bits en  $2^N$  niveaux continuos correspondants.

Le DAC 400 est basé sur un amplificateur ayant un gain choisi en fonction des valeurs de données. En particulier, le circuit comprend quatre nœuds d'entrée recevant les bits B0 à

25 B3. Les quatre nœuds d'entrée sont respectivement couplés à une borne de résistances 402, 404, 406 et 408 respectivement, qui ont des valeurs correspondantes de R, R/2, R/4 et R/8. Les autres bornes des résistances 402 à 408 sont couplées à la borne d'entrée négative d'un amplificateur opérationnel 410. La borne d'entrée négative de l'amplificateur opérationnel 410 est aussi couplée par l'intermédiaire d'une résistance 412 à un nœud de sortie 414 de l'amplificateur qui fournit la tension de sortie V<sub>OUT</sub> du DAC. La résistance 412 a par exemple une valeur R. Le nœud de sortie 414 est par exemple connecté directement à la ligne de transmission 202. La borne d'entrée positive de

30

l'amplificateur opérationnel 410 est par exemple couplée à la masse par l'intermédiaire d'une résistance 416, qui a par exemple une valeur  $R/10$ . Dans un mode de réalisation, R est une valeur comprise entre 5 et 20 kohms.

5 La figure 5 illustre un convertisseur analogique-numérique flash à 2 bits adapté à implémenter l'ADC à 4 bits 214 de la figure 2. L'homme de l'art saura comment adapter le circuit de la figure 5 pour convertir des niveaux de tension continue en des valeurs numériques de N bits.

10 L'ADC 500 comprend un réseau de résistances générant  $2^N$  niveaux de tension de référence sur la base d'une tension de référence  $V_{REF}$ . Le réseau de résistances comprend par exemple  $2^N+1$  résistances couplées en série entre la tension  $V_{REF}$  et la masse. Dans l'exemple de la figure 5, N est égal à 2, et il y a donc cinq résistances. Chaque résistance a une valeur R, excepté la première et la dernière résistance de la série, qui ont des valeurs  $R/2$ . La valeur R est par exemple comprise entre 1 et 10 kilo-ohms. Les quatre nœuds intermédiaires entre les résistances fournissent quatre niveaux de tension de référence, qui sont respectivement couplés aux entrées positives de quatre comparateurs 502 à 508. Les comparateurs 502 à 508 comparent les niveaux de référence respectifs à la tension d'entrée  $V_{IN}$  reçue depuis la ligne de transmission 202. En particulier, l'entrée négative de chaque comparateur 502 est par exemple connectée directement à la ligne de transmission 202. Le comparateur 502 reçoit la plus haute tension de référence et a sa sortie couplée à une entrée d'une porte NON ET 510. L'autre entrée de la porte NON ET 510 est couplée à la sortie du comparateur 504 par l'intermédiaire d'un inverseur. La sortie du comparateur 504 est aussi couplée à une entrée d'une porte NON ET 512, dont l'autre entrée est couplée à la sortie du comparateur 506 par l'intermédiaire d'un inverseur. La sortie du comparateur 506 est aussi couplée à une entrée d'une porte NON ET 514, dont l'autre entrée est couplée à la sortie du comparateur 508 par l'intermédiaire d'un inverseur. La sortie de la porte NON ET 510 est couplée à

une entrée d'une porte NON ET 516, et à une entrée d'une porte NON ET 518. L'autre entrée de la porte NON ET 516 est couplée à la sortie de la porte NON ET 512. L'autre entrée de la porte NON ET 518 est couplée à la sortie de la porte NON ET 514. Les 5 portes NON ET 516 et 518 fournissent des bits de sortie respectivement B0 et B1 de l'ADC 500.

Un avantage des modes de réalisation décrits ici est que le débit de transmission de données d'une interface série peut être amélioré sans augmenter la fréquence d'horloge, et par 10 conséquent une telle augmentation ne provoque pas de dépassement des limites physiques de la ligne de transmission. Par exemple, dans le cas où N est égal à 2, le débit de données peut être doublé pour une fréquence d'horloge donnée sans augmenter la fréquence du signal appliquée sur la ligne de transmission. En 15 effet, étant donné que les changements de tension sur la ligne de transmission sont susceptibles d'être inférieurs à l'excursion de tension de VDD, les contraintes de fréquence sur la ligne de transmission sont réduites. De plus, étant donné qu'un unique niveau continu représente plus d'un bit de données, il y 20 aura aussi une réduction significative de la consommation d'énergie.

Un avantage de l'utilisation d'un DAC à bits pondérés et/ou d'un ADC flash est que de tels convertisseurs fonctionnent très rapidement, provoquant seulement un faible ralentissement 25 des transmissions de données.

Au vu du mode de réalisation illustratif décrit, des variantes, modifications et améliorations apparaîtront facilement à l'homme de l'art.

Par exemple, il apparaîtra à l'homme de l'art que la 30 tension d'alimentation VDD dans les diverses réalisations peuvent avoir n'importe quel niveau, par exemple entre 1 et 5 V, plutôt que d'être à 0 V, la masse peut aussi être considérée comme une tension d'alimentation qui pourrait avoir n'importe quel niveau, tel qu'un niveau négatif.

Il apparaîtra aussi à l'homme de l'art que, bien que l'on ait donné des exemples dans lesquels les fronts montants du signal d'horloge constituent le front temporel significatif, dans des variantes de réalisation, le front significatif peut 5 être un front descendant, ou des fronts descendants et montants. De plus, il apparaîtra à l'homme de l'art que des informations temporelles peuvent être fournies depuis le côté transmission vers le côté réception par un signal d'horloge fourni en liaison directe ou, à titre de variante qu'un protocole adapté, par 10 exemple sur la base de bits de début et de fin, pourrait être utilisé sur les lignes de transmission afin que les informations temporelles puissent être déterminées du côté réception.

De plus, il apparaîtra à l'homme de l'art que les circuits des figures 4 et 5 sont uniquement des exemples de 15 réalisation d'un DAC et d'un ADC, respectivement, et que plusieurs variantes de réalisation peuvent être possibles.

En outre, l'homme de l'art notera que les diverses caractéristiques décrites en relation avec les divers modes de réalisation peuvent être combinées, dans des variantes de réalisation, selon des combinaisons quelconques. 20

REVENDICATIONS

1. Circuit de transmission de données pour transmettre un signal de données sur une ligne de transmission (202), ce circuit comprenant :

5        un multiplexeur (210) adapté à recevoir une pluralité de valeurs numériques de N bits en parallèle, et à multiplexer temporellement la pluralité de valeurs numériques de N bits et à les fournir en série à un convertisseur numérique-analogique, DAC, (212);

10        dans lequel le DAC (212) est capable de générer  $2^N$  niveaux de tension continue différents, et est adapté à recevoir des valeurs numériques de N bits, et pour chaque valeur numérique, à sélectionner, en se basant sur les valeurs numériques, l'un des  $2^N$  niveaux de tension continue et à appliquer le niveau de tension 15 continue sélectionné sur la ligne de transmission (202).

2. Circuit de transmission de données selon la revendication 1, dans lequel le DAC (212) est adapté à appliquer, pour des valeurs numériques consécutives, les niveaux de tension continue sélectionnés sur un front montant et un front descendant 20 d'un signal d'horloge (CLK2).

3. Circuit de transmission de données selon la revendication 1 ou 2, dans lequel le multiplexeur (210) est adapté à recevoir deux groupes de valeurs numériques de N bits en parallèle, et à multiplexer temporellement les deux groupes de valeurs 25 numériques de N bits sur des fronts montants et descendants d'un signal d'horloge (CLK2).

4. Circuit de transmission de données selon l'une quelconque des revendications 1 à 3, dans lequel le DAC (212) comprend un amplificateur (402 à 412) ayant une sortie (414) couplée à la 30 ligne transmission (202), l'amplificateur étant adapté à avoir  $2^N$  niveaux de gains différents pour générer les  $2^N$  niveaux de tension continue différents.

5. Circuit de transmission de données selon l'une quelconque des revendications 1 à 4, comprenant en outre une ligne

de sortie d'horloge (218) pour transmettre un signal d'horloge vers un circuit de réception (RX).

6. Circuit de réception de données pour recevoir un signal de données transmis sur une ligne de transmission (202),

5 le circuit comprenant :

un convertisseur analogique-numérique, ADC, (214) capable de différencier  $2^N$  niveaux de tension continue différents, dans lequel l'ADC (214) est adapté à détecter des niveaux de tension continue sur la ligne de transmission (202), à convertir 10 chaque niveau de tension continue détecté en une valeur de données de N bits correspondante et à fournir les valeurs de données de N bits à une sortie de l'ADC (214) ; et

15 un démultiplexeur (220) adapté à recevoir en série des valeurs de données de N bits à la sortie de l'ADC (214) et à générer une pluralité de valeurs numériques de N bits en parallèle en démultiplexant temporellement une pluralité de valeurs de données de N bits.

7. Circuit de réception de données selon la revendication 6, dans lequel l'ADC (214) est adapté à générer des valeurs numériques consécutives de N bits, en se basant sur des niveaux de tension continue consécutifs, sur un front montant et un front descendant d'un signal d'horloge.

25 8. Circuit de réception de données selon la revendication 6 ou 7, dans lequel le démultiplexeur (220) est adapté à générer deux valeurs numériques de N bits en parallèle en démultiplexant temporellement la pluralité de valeurs de données de N bits sur des fronts montants et descendants d'un signal d'horloge.

30 9. Circuit de réception de données selon l'une quelconque des revendications 6 à 8, dans lequel l'ADC (214) comprend un réseau de résistances adapté à générer  $2^{N-1}$  niveaux de tension de référence, et  $2^{N-1}$  comparateurs (502 à 508) adaptés à comparer l'un correspondant des niveaux de tension de référence à chaque niveau de tension continue détecté sur la ligne de 35 transmission (202).

10. Interface de transmission de données intégrée à un circuit intégré comprenant :

le circuit de transmission de données (TX) selon l'une quelconque des revendications 1 à 5 ;

5 le circuit de réception de données (RX) selon l'une quelconque des revendications 6 à 9 ; et

une ligne de transmission (202) connectant le circuit de transmission de données (TX) au circuit de réception de données (RX) .

10 11. Interface de transmission de données pour transmettre des données entre des circuits intégrés comprenant :

un premier circuit intégré comprenant le circuit de transmission de données (TX) selon l'une quelconque des revendications 1 à 5 ;

15 un second circuit intégré comprenant le circuit de réception de données (RX) selon l'une quelconque des revendication 6 à 9 ; et

une ligne de transmission (202) connectant le circuit de transmission de données (TX) au circuit de réception de données (RX) .

20 12. Procédé de transmission d'un signal de données sur une ligne de transmission (202), ce procédé comprenant :

la réception, par un multiplexeur (210), d'une pluralité de valeurs numériques de N bits en parallèle ;

25 le multiplexage temporel de la pluralité de valeurs numériques de N bits et leur fourniture en série à un convertisseur numérique-analogique, DAC (212) ;

30 la réception, par le convertisseur numérique-analogique, DAC, (212) capable de générer  $2^N$  niveaux de tension continue différents, des valeurs numériques de N bits ; et

pour chaque valeur numérique :

la sélection, sur la base de la valeur numérique, d'un des  $2^N$  niveaux de tension de référence ; et

35 l'application du niveau de tension continue sélectionné sur la ligne de transmission (202).

13. Procédé de réception d'un signal de données transmis sur une ligne de transmission (202), le procédé comprenant :

la détection par un convertisseur analogique-numérique, ADC, (214) capable de différencier  $2^N$  niveaux de tension continue,

5 de niveaux de tension continue sur la ligne de transmission (202)

;

la conversion de chaque niveau de tension continue détecté en une valeur de données de N bits correspondante ;

10 la fourniture des valeurs de données de N bits à la sortie de l'ADC (214) ;

la réception en série, par un démultiplexeur (220), des valeurs de données de N bits à la sortie de l'ADC (214) ; et

15 la génération, par le démultiplexeur (220), d'une pluralité de valeurs numériques de N bits en parallèle en démultiplexant temporellement une pluralité de valeurs de données de N bits.

Fig 1

Fig 2

Fig 3

Fig 4

Fig 5

# RAPPORT DE RECHERCHE

articles L.612-14, L.612-53 à 69 du code de la propriété intellectuelle

## OBJET DU RAPPORT DE RECHERCHE

L'I.N.P.I. annexe à chaque brevet un "RAPPORT DE RECHERCHE" citant les éléments de l'état de la technique qui peuvent être pris en considération pour apprécier la brevetabilité de l'invention, au sens des articles L. 611-11 (nouveauté) et L. 611-14 (activité inventive) du code de la propriété intellectuelle. Ce rapport porte sur les revendications du brevet qui définissent l'objet de l'invention et délimitent l'étendue de la protection.

Après délivrance, l'I.N.P.I. peut, à la requête de toute personne intéressée, formuler un "AVIS DOCUMENTAIRE" sur la base des documents cités dans ce rapport de recherche et de tout autre document que le requérant souhaite voir prendre en considération.

## CONDITIONS D'ETABLISSEMENT DU PRESENT RAPPORT DE RECHERCHE

[x] Le demandeur a présenté des observations en réponse au rapport de recherche préliminaire.

□ Le demandeur a maintenu les revendications.

[x] Le demandeur a modifié les revendications.

□ Le demandeur a modifié la description pour en éliminer les éléments qui n'étaient plus en concordance avec les nouvelles revendications.

□ Les tiers ont présenté des observations après publication du rapport de recherche préliminaire.

□ Un rapport de recherche préliminaire complémentaire a été établi.

## DOCUMENTS CITES DANS LE PRESENT RAPPORT DE RECHERCHE

La répartition des documents entre les rubriques 1, 2 et 3 tient compte, le cas échéant, des revendications déposées en dernier lieu et/ou des observations présentées.

[x] Les documents énumérés à la rubrique 1 ci-après sont susceptibles d'être pris en considération pour apprécier la brevetabilité de l'invention.

□ Les documents énumérés à la rubrique 2 ci-après illustrent l'arrière-plan technologique général.

□ Les documents énumérés à la rubrique 3 ci-après ont été cités en cours de procédure, mais leur pertinence dépend de la validité des priorités revendiquées.

□ Aucun document n'a été cité en cours de procédure.

**1. ELEMENTS DE L'ETAT DE LA TECHNIQUE SUSCEPTIBLES D'ETRE PRIS EN

CONSIDERATION POUR APPRECIER LA BREVETABILITE DE L'INVENTION**

EP 0 407 031 A2 (ADVANCED MICRO DEVICES INC [US]) 9 janvier 1991 (1991-01-09)

MUNEHIKO NAGATANI ET AL: "A 32-GS/s 6-Bit Double-Sampling DAC in InP HBT Technology", COMPOUND SEMICONDUCTOR INTEGRATED CIRCUIT SYMPOSIUM, 2009. CISC 2009. ANNUAL IEEE, IEEE, PISCATAWAY, NJ, USA, 11 octobre 2009 (2009-10-11), pages 1-4, XP031560501, ISBN: 978-1-4244-5191-3

US 2005/231399 A1 (FOWLER MICHAEL L [US] ET AL) 20 octobre 2005 (2005-10-20)

I-HSIN WANG ET AL: "A 4-bit 10GSample/sec flash ADC with merged interpolation and reference voltage", SOLID-STATE CIRCUITS CONFERENCE, 2008. A-SSCC '08. IEEE ASIAN, IEEE, PISCATAWAY, NJ, USA, 3 novembre 2008 (2008-11-03), pages 377-380, XP031373041, ISBN: 978-1-4244-2604-1

**2. ELEMENTS DE L'ETAT DE LA TECHNIQUE ILLUSTRANT L'ARRIÈRE-PLAN

TECHNOLOGIQUE GENERAL**

NEANT

**3. ELEMENTS DE L'ETAT DE LA TECHNIQUE DONT LA PERTINENCE DEPEND

DE LA VALIDITE DES PRIORITES**

NEANT