(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-45404

(P2004-45404A)

(43) 公開日 平成16年2月12日(2004.2.12)

(51) Int.Cl.<sup>7</sup>

G O 1 R 31/28

F 1

G O 1 R 31/28

テーマコード(参考)

V

2 G 1 3 2

審査請求 未請求 請求項の数 1 O L (全 19 頁)

(21) 出願番号 特願2003-189236 (P2003-189236)

(22) 出願日 平成15年7月1日 (2003.7.1.)

(31) 優先権主張番号 10/193949

(32) 優先日 平成14年7月11日 (2002.7.11.)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100075513

弁理士 後藤 政喜

(74) 代理人 100084537

弁理士 松田 嘉夫

最終頁に続く

(54) 【発明の名称】監視回路要素

## (57) 【要約】

【課題】アナログ及び混合信号ICをテストする廉価なシステムと回路要素を提供する。

【解決手段】本発明の監視回路要素(12)には比較回路(40)があり、互いに連係動作する1組の制御トランジスタ(46及び48)と1組のセンス・トランジスタ(44及び50)とを備える。制御トランジスタは、電流 $I_1$ 、 $I_2$ の関係のテスト条件を設定するため基準信号を受信する。センス・トランジスタは、前記DUTからサンプル値信号を受信しバイアスがかかると、前記信号関係が変化し、その変化によって、DUTの動作状態が表わされる。比較回路に作用的に結合されたセンス増幅器(42)は信号関係の変化を加速する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

被測定物（D U T）の動作状態を識別するための監視回路要素であって、

1組の制御トランジスタ、及び、1組のセンス・トランジスタを備え、前記制御トランジスタの制御入力端子が、第1の電流と第2の電流との間の信号関係に関するテスト条件を設定するための基準信号を受信するように接続され、前記センス・トランジスタが、前記制御トランジスタと連係動作可能であり、センス入力端子を備えていて、前記D U Tから受信するサンプル値信号で前記センス入力端子にバイアスをかけると、前記信号関係が変化し、前記信号関係の変化によって、前記D U Tの前記動作状態が表わされるようになっている、比較回路と、

前記比較回路に作用的に結合されており、前記信号関係の前記変化を加速するように構成されているセンス増幅器と

が含まれている監視回路要素。

**【発明の詳細な説明】****【0 0 0 1】****【発明の属する技術分野】**

本発明は、一般に、集積回路（I C）に関するものであり、とりわけ、アナログ及び／または混合信号I Cをテストするための、監視回路要素及び動作状態識別方法とに関するものである。

**【0 0 0 2】****【従来の技術】**

アナログ及び混合信号集積回路（I C）の複雑度及び密度が増し続けることによって、回路内の回路要素のテストに難題が課せられるようになった。特定の回路設計は、信号応答に特定の「シグナチュア」を示す可能性がある。デジタルI C内における故障検出は、シグナチュア・アナリシスを利用することによって成功したが、シグナチュア・アナリシスによる、アナログ及び混合信号I C内における故障の検出は、いまだに未熟な状態にある。

**【0 0 0 3】**

現行のアナログ及び混合信号I Cテスト技法の場合、テスト用のアナログ信号が、オフ・チップ環境に信号を転送する必要があるために歪を生じる場合が多い。テスト・バス（例えば、I E E E 1 1 4 9 . 4 規格）、走査回路要素、オシロスコープ、及び、信号処理アルゴリズムが必要とされる場合が多く、このため、寄生負荷及び寄生結合に遭遇する問題が付加されることになる。

**【0 0 0 4】**

オフ・チップ環境に信号を転送することを必要とせずに、アナログ及び混合信号I Cをテストするためのアプローチの1つは、ビルト・イン・セルフテスト（B I S T）法を実施することである。解析は、オン・チップで実施されるので、オフ・チップ・テストに関連した問題の多くが解消される。先行技術文献にはこれについて論じたものがある（例えば、非特許文献1参照）。このシステムによれば、ゾーン検出器は、I Cのシグナチュアが示されたリサジューの図形を掃引する制御線を発生するために利用される。各所定の期間毎に、ゼロ交差検出器及びカウンタが、制御線がリサジューの図形を横切る回数をカウントする。所定の期間における横断数は、そのI Cの動作状態を示す。制御線を発生するゾーン検出器は、順次段をなすように構成された3つの演算増幅器（o p - a m p）から構成されている。o p - a m p の利用に関する問題の1つは、各o p - a m p が、実施のためにかなりの量の回路要素を必要とするので、被測定I Cに比べて、o p - a m p が必要とする領域は法外なものになるという点である。もう1つの問題は、o p - a m p 内の回路要素によって、製造の複雑性及びコストが増すという点である。

**【0 0 0 5】****【非特許文献1】**

osal for Mixed-Signal Circuits」、ITC International Test Conference, IEEE (2000)

### 【0006】

#### 【発明が解決しようとする課題】

本発明の目的は、製造サイズ、複雑性、及び、コストが減少するように、アナログ及び混合信号ICをテストするためのシステム及び方法とそのための回路要素を提供することにある。

### 【0007】

#### 【課題を解決するための手段】

被測定物(DUT)の動作状態を識別するための監視回路要素には、比較回路とセンス増幅器が含まれている。比較回路には、1組の制御トランジスタと、1組のセンス・トランジスタが含まれている。制御トランジスタには、基準信号を受信するための制御入力端子が含まれている。制御信号は、第1の電流と第2の電流との信号関係で特徴付けられるテスト条件を設定する。センス・トランジスタは、制御トランジスタと連係動作し、DUTから受信するサンプル値信号によってセンス・トランジスタのセンス入力端子にバイアスをかけると、第1の電流と第2の電流との信号関係が変化するようになっている。信号関係の変化は、センス増幅器によって加速される。信号関係の変化は、サンプル値信号を取得するサンプリング段階におけるDUTの動作状態を表わしている。

### 【0008】

実施例の1つでは、比較回路には、2つの制御トランジスタ及び2つのセンス・トランジスタを含む、協働して並列構造をなすように構成された4つのトランジスタが含まれている。第1の電流のための第1の伝導経路が、4つのトランジスタのうち2つのトランジスタのソース／ドレイン領域に結合されている。第2の電流のための第2の伝導経路が、他の2つのトランジスタのソース／ドレイン領域に結合されている。第1及び第2の伝導経路は、並列構造の4つのトランジスタからセンス増幅器に並列に結合されている。

### 【0009】

並列構造は、(1)2つの制御トランジスタが、第1の伝導経路に接続され、2つのセンス・トランジスタが、第2の伝導経路に接続されるように、(2)2つの制御トランジスタが、第2の伝導経路に接続され、2つのセンス・トランジスタが、第1の伝導経路に接続されるように、及び、(3)1つの制御トランジスタ及び1つのセンス・トランジスタが、第1の伝導経路に接続され、一方、もう1つの制御トランジスタ及びもう1つのセンス・トランジスタが、第2の伝導経路に接続されるように構成することが可能である。従って、伝導経路は、それぞれ、(1)2つの制御トランジスタ、(2)2つのセンス・トランジスタ、または、(3)1つの制御トランジスタ及び1つのセンス・トランジスタのソース／ドレイン領域に結合することが可能である。

### 【0010】

テストに先立って、2つのサンプル値信号が、特定の信号関係条件を満たす場合、第1の伝導経路における第1の電流が、第2の伝導経路における第2の電流に等しくなるように、監視回路要素の初期設定が行われる。サンプリング段階では、2つの制御トランジスタの制御入力端子において、1組の基準信号を受信する。基準信号は、2つの制御トランジスタによって導通される電流を制御するための定電圧とすることが可能である。基準信号は、第1の電流と第2の電流との信号関係に関するテスト条件を設定する。x-y平面において、基準信号は、2つの識別可能なゾーンを分割する境界を表わしている。

### 【0011】

テスト段階では、2つのセンス・トランジスタのセンス入力端子において、1組のサンプル値信号を受信する。サンプル値信号は、2つのセンス・トランジスタによって導通される電流を決定することになるアナログ信号である。サンプル値信号は、第1の電流と第2の電流との信号関係を変化させる。サンプル値信号によって、x-y平面における座標が決まる。信号関係の変化は、境界に対する座標位置を表わす。テスト・シナリオの1つでは、変化は、第1の電流が第2の電流を超えるという理由で、座標が境界の一方の側にあ

10

20

30

40

50

ることを表わすか、または、第2の電流が第1の電流を超えるという理由で、座標が境界のもう一方の側にあることを表わすことになる。

#### 【0012】

第1と第2の電流間の信号関係の変化が、センス増幅器によって加速される。センス増幅器は、第1の電流が第2の電流を超える場合には、第1のノードのノード電圧を増幅するように、あるいは、第2の電流が第1の電流を超える場合には、第2のノードのノード電圧を増幅するように構成されている。

#### 【0013】

監視回路要素には、出力インバータを含むことも可能である。第1の出力インバータは、第1のノードに結合されて、第1のノードのノード電圧を反転し、第1のデジタル出力を送り出す。第2の出力インバータは、第2のノードに結合されて、第2のノードのノード電圧を反転し、第2のデジタル出力を送り出す。第1のデジタル出力と第2のデジタル出力は、相補性デジタル出力である。

#### 【0014】

本発明の方法によれば、一連の第1及び第2のデジタル出力が、順次サンプル値信号を利用して発生する。さらに、基準信号を調整することによって、x-y平面における他の境界を決めることが可能である。後続の下流処理では、第1及び第2のデジタル出力の少なくとも1つと対応する所定の基準デジタル信号を比較して、DUTの動作状態が決定される。

#### 【0015】

本発明の利点は、DUTの動作状態が、比較的単純な装置で決定できるという点にある。装置を単純化すると、テストに必要なハードウェア要件が緩和されるので、これは、重要な可能性を秘めている。従って、DUTのテスト状態は、比較的短い時間期間で決定される。さらに、製造諸経費が、先行技術に対して大幅に低下する。

#### 【0016】

##### 【発明の実施の形態】

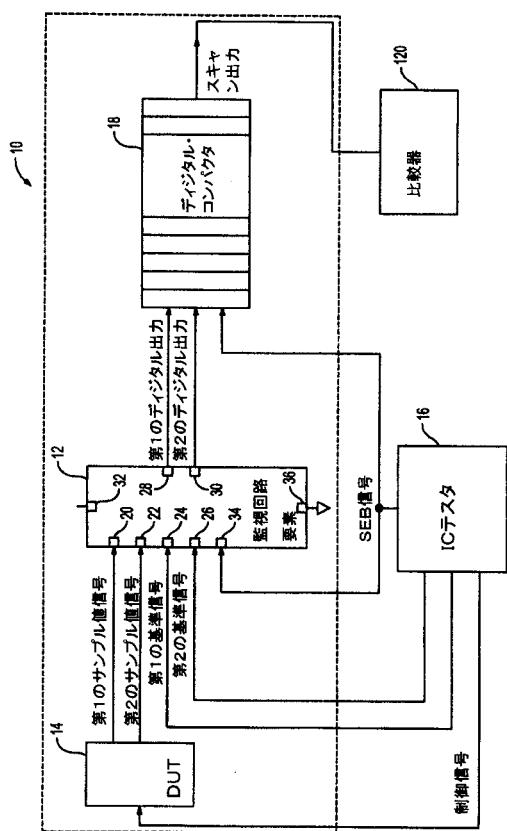

図1には、監視回路要素12が、DUTの動作状態を決定するため、被測定物(DUT)14から第1のサンプル値信号及び第2のサンプル値信号を受信するように構成された、オン・チップ・システム10が示されている。DUT14は、混合信号装置またはアナログ信号装置とすることが可能である。システムには、I Cテスタ16、デジタル・コンパクタ18、及び、比較器120も含まれている。比較器は、オフ・チップ(すなわち、点線外)のように示されているが、オン・チップとすることも可能である。

#### 【0017】

監視回路要素12は、とりわけ、オン・チップ環境におけるビルト・イン・セルフテスト(BIST)装置として利用するのに適している。監視回路要素12には、第1のサンプリング端子20及び第2のサンプリング端子22、第1の基準端子24及び第2の基準端子26、第1の出力端子28及び第2の出力端子30、供給電圧(V<sub>DD</sub>)入力端子32、サンプル及びリセット(SEB)端子34、及び、接地端子36が含まれている。

#### 【0018】

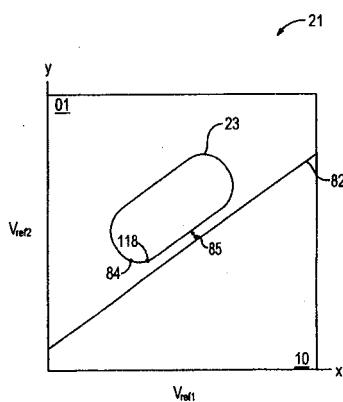

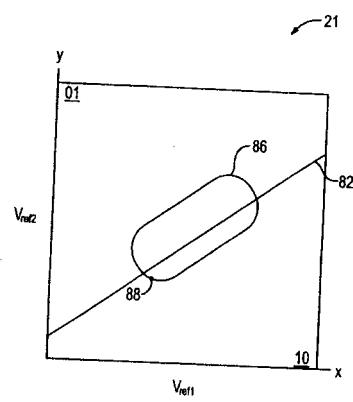

I Cテスタ16は、DUT14に結合されて、制御信号を送信する。制御信号は、DUTから監視回路要素12への第1及び第2のサンプル値信号の転送をトリガする。第1のサンプル値信号は、第1のサンプリング端子20において監視回路要素によって受信される。第2のサンプル値信号は、第2のサンプリング端子22において監視回路要素によって受信される。サンプル値信号は、アナログ信号であり、DUT内における2つの内部電圧を表わしている。ある時間期間にわたるサンプル値信号によって、x-y平面にリサジーの図形を形成することが可能である。オシロスコープのx-yモードを利用すると、リサジーの図形を視覚化することが可能になる。図2には、DUTの特性であるリサジーの図形を備えたx-y平面21が示されている。線形特性を備えたDUTの場合、リサジーの図形は、橢円の可能性が高い。

#### 【0019】

10

20

30

40

50

図1の監視回路要素12の場合、第1の基準端子24及び第2の基準端子26は、テスタ16に結合されて、第1の基準信号及び第2の基準信号を受信する。さらに詳細に後述するように、基準信号は、監視回路要素12内におけるテスト条件を設定する。異なる実施例の場合、第1及び第2の基準信号は、テスタからではなく、DUTから受信する。DUTから受信する基準信号は、個別ハード配線電圧値を有する分圧器に基づく論理回路に結合された基準点に関連づけることが可能である。

#### 【0020】

監視回路要素12のSEB端子34は、テスタ16からSEB信号を受信して、DUT14のテストをトリガするように接続されている。一連のサンプリング時間の各サンプリング時間毎に、第1の出力端子28において、第1のデジタル出力が発生し、第2の出力端子30において、第2のデジタル出力が発生する。第1及び第2のデジタル出力は、データ圧縮のため、次々にデジタル・コンパクタ18に転送される。

#### 【0021】

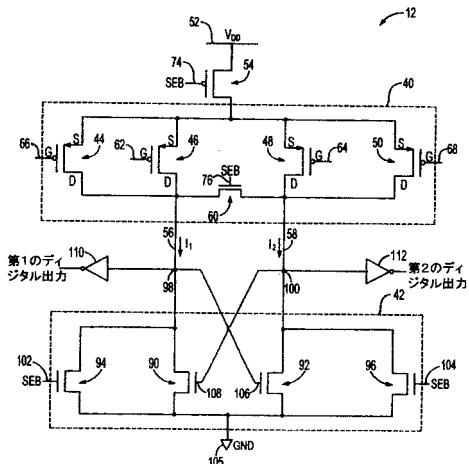

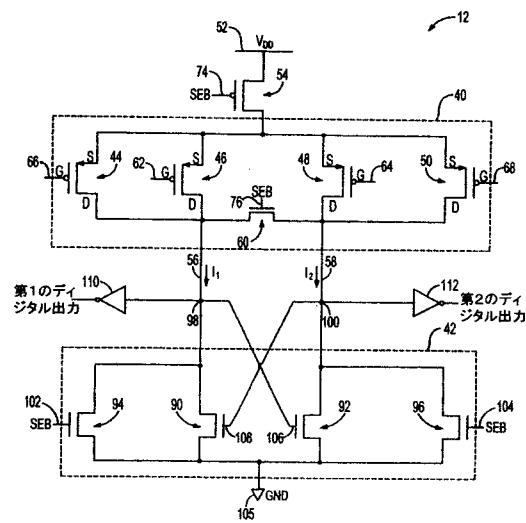

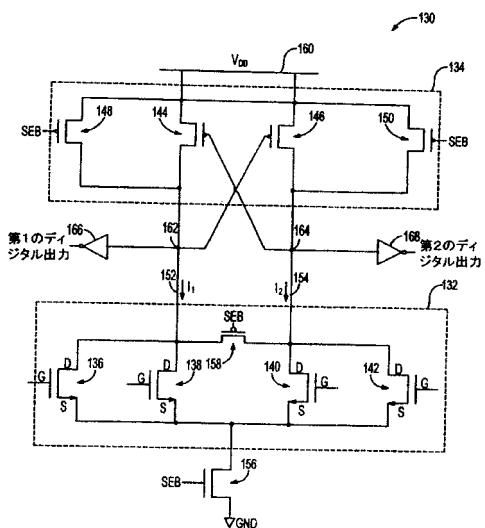

本発明の第1の実施例によれば、図3には、図1の監視回路要素12の概略図が示されている。監視回路要素12には、比較回路40（点線のブロックとして示された）とセンス増幅器42（やはり、点線のブロックとして示された）が含まれている。図3の実施例の場合、比較回路には、トランジスタ44、46、48、及び、50として識別される4つのトランジスタが含まれているが、他の実施例では、異なる数のトランジスタを用いることが可能である。4つのトランジスタは、協働して並列構造をなすように構成されている。4つのトランジスタは、従来のPチャネル金属酸化膜半導体（PMOS）トランジスタとすることが可能である。

#### 【0022】

供給電圧（V<sub>DD</sub>）レール52が、図1の供給電圧入力端子32に結合されている。第1のスイッチング・トランジスタ54が、V<sub>DD</sub>レールと4つのトランジスタ44-50のソース領域（S）間に配置されている。第1のスイッチング・トランジスタ54は、その選択的操作によって、電流が4つのトランジスタを導通できるようにするか、または、4つのトランジスタを導通できないようにすることが可能な構成が施されている。第1のスイッチング・トランジスタ54は、NチャネルMOS（NMOS）トランジスタであるが、これは重要ではない。

#### 【0023】

第1の電流（I<sub>1</sub>）を伝導させるための第1の伝導経路56は、トランジスタ44及び46のドレイン領域（D）に結合されている。第2の電流（I<sub>2</sub>）を伝導させるための第2の伝導経路58は、トランジスタ48及び50のドレイン領域（D）に結合されている。第2のスイッチング・トランジスタ60は、第1の伝導経路及び第2の伝導経路に結合されている。第2のスイッチング・トランジスタは、その選択的操作によって、第1の伝導経路と第2の伝導経路の間に短絡状態または開路状態を生じさせることが可能な構成を提供する。第2のスイッチング・トランジスタは、NMOSトランジスタとすることが可能である。

#### 【0024】

比較回路40内において、4つのトランジスタ44-50のうち2つを制御トランジスタまたはセンス・トランジスタに選択することが可能である。典型的な実施例の1つでは、トランジスタ46は、第1の制御トランジスタに選択され、トランジスタ48は、第2の制御トランジスタに選択される。第1の制御トランジスタ46は、図1の第1の基準端子24に結合されて、ゲート領域62で第1の基準信号を受信する。第2の制御トランジスタ48は、図1の第2の基準端子26に結合されて、ゲート領域64で第2の基準信号を受信する。同じ典型的な実施例において、残りのトランジスタ44及び50は、第1及び第2のセンス・トランジスタである。第1のセンス・トランジスタ44は、図1の第2のサンプリング端子20に結合されて、ゲート領域66で第1のサンプル値信号を受信する。第2のセンス・トランジスタ50は、図1のサンプリング端子22に結合されて、ゲート領域68で第2のサンプル値信号を受信する。

10

20

30

40

50

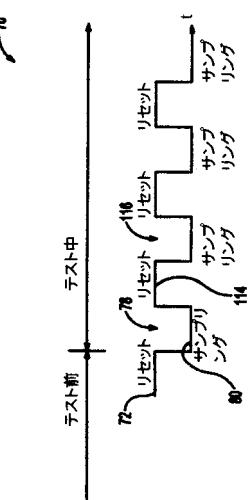

## 【0025】

図3の監視回路要素12及び図4のタイミング図70を参照して、比較回路40について述べることにする。テストに先立って、比較回路40をリセットするため、監視回路要素12に高レベル(すなわち、論理高)のSEB信号72が加えられる。高レベルのSEB信号は、第1のスイッチング・トランジスタ54のゲート領域74、及び、第2のスイッチング・トランジスタ60のゲート領域76において受信される。第1のスイッチング・トランジスタ及び第2のスイッチング・トランジスタは、相補性のスイッチング・トランジスタであるため、第2のスイッチング・トランジスタが非活性化すると、第1のスイッチング・トランジスタが活性化し、第2のスイッチング・トランジスタが活性化すると、第1のスイッチング・トランジスタが非活性化するようになっている。第1のスイッチング・トランジスタのゲート領域74で高レベルのSEB信号を受信すると、第1のスイッチング・トランジスタは非活性化して、 $V_{DD}$ レール52と4つのトランジスタ44-50間が開路状態になる。従って、リセット期間中、4つのトランジスタのどれにも電流は流れない。第2のスイッチング・トランジスタ60のゲート領域76で高レベルのSEB信号を受信すると、第2のスイッチング・トランジスタが活性化して、第1の伝導経路56と第2の伝導経路58間が短絡状態になる。短絡状態中、第1の伝導経路における第1の電流( $I_1$ )は、第2の伝導経路における第2の電流( $I_2$ )に等しい。

10

## 【0026】

図4の第1のサンプリング段階78において、低レベル(論理低)のSEB信号80が、図3の監視回路要素12に加えられる。低レベルSEB信号は、第1のスイッチング・トランジスタ54のゲート領域74、及び、第2のスイッチング・トランジスタ60のゲート領域76において受信される。第1のスイッチング・トランジスタのゲート領域74で低レベルのSEB信号を受信すると、第1のスイッチング・トランジスタが活性化して、 $V_{DD}$ レール52と4つのトランジスタ44-50間がほぼ短絡状態になる。従って、トランジスタを通る電流レベルを制御するためそれぞれのゲート領域に加えられる電圧レベルに従って、4つのトランジスタ44-50に電流が流れることになる。第2のスイッチング・トランジスタ60のゲート領域76で低レベルのSEB信号を受信すると、第2のスイッチング・トランジスタが非活性化して、第1の伝導経路56と第2の伝導経路58間が開路状態になる。開路状態中、第1の伝導経路は、第1のセンス・トランジスタ44及び第1の制御トランジスタ46に電気的に結合される。第2の伝導経路は、第2の制御トランジスタ48及び第2のセンス・トランジスタ50に電気的に結合される。従って、サンプリング段階では、第1の電流( $I_1$ )は、第1のセンス・トランジスタ及び第1の制御トランジスタの導通によって決まる。第2の電流( $I_2$ )は、第2の制御トランジスタ及び第2のセンス・トランジスタの導通によって決まる。

20

30

40

## 【0027】

第1の電流( $I_1$ )と第2の電流( $I_2$ )との信号関係で特徴づけられるテスト条件は、第1の制御トランジスタ46を通る特定レベルの電流と第2の制御トランジスタ48を通る特定レベルの電流によって設定される。第1の制御トランジスタを通る電流レベルは、ゲート領域62で受信する第1の基準信号の電圧レベルによって調節される。第2の制御トランジスタを通る電流レベルは、ゲート領域64で受信する第2の基準信号の電圧レベルによって調節される。第1及び第2の基準信号は、固定電圧である。図2のx-y平面21において、境界82は、テスト条件を表わしている。境界は、2つの識別可能なゾーンを形成する直線によって表わされている。境界の一方の側のゾーンは、ゾーン01として識別可能であり、境界のもう一方の側のゾーンは、ゾーン10として識別可能である。境界は、図2に示すようにラインで表わされるが、連続したサンプリング段階毎に基準信号を変化させることによって生成可能な曲線とすることも可能である。

## 【0028】

同じ第1のサンプリング段階78(図4)において、第1のセンス・トランジスタ44を通る電流のレベルは、ゲート領域66における第1のサンプル値信号の電圧レベルによって制御される。第2のセンス・トランジスタ50を通る電流のレベルは、ゲート領域68

50

における第2のサンプル値信号の電圧レベルによって制御される。サンプリング段階中に、第1及び第2のサンプル値信号によって、図2のx-y平面21における座標84が決まる。座標は、リサジューの図形を形成する第1及び第2のサンプル値信号の一方のサンプリング中に識別されるので、リサジューの図形23上にあるように示されている。境界82は、リサジューの図形からある距離だけ離れた位置85にあるように示されている。この距離は、DUT14が示すパラメータ変動を考慮した、バッファ・ゾーンを現している。

#### 【0029】

図3の監視回路要素12は、座標84が境界82を超えるゾーン01にあるか、あるいは、境界未満のゾーン10にあるかを表わす出力を送り出すように設計されている。ただ単なる例として、境界によって設定されるテスト条件は、第2のサンプル値信号のサンプル( $V_{ref2}$ )が、同時に得られるサンプル( $V_{ref1}$ )の2倍を超える条件とすることが可能である。設定されるテスト条件に関して、監視回路要素の出力は、各座標が異なるサンプリング時間に対応する、異なるサンプリング時間に得られたサンプルによって決まる座標位置に基づいて変化することになる。監視回路要素の出力は、第1と第2の電流( $I_1$ 及び $I_2$ )の信号関係を検知することによって、座標の相対位置及び境界を表わす。

#### 【0030】

第1の電流( $I_1$ )と第2の電流( $I_2$ )の信号関係は、第1のセンス・トランジスタ44及び第2のセンス・トランジスタ50の少なくとも一方からの供給が変化すると変化する。図2のx-y平面21における信号関係の変化は、サンプリング段階における境界82に対する座標84の位置を表わしている。あるテスト・シナリオでは、この変化は、第1の電流が第2の電流を超えるという理由で、座標がゾーン01内に位置するか、あるいは、第2の電流が第1の電流を超えるという理由で、座標がゾーン10内に位置するかを表示する。

#### 【0031】

第1の電流( $I_1$ )と第2の電流( $I_2$ )の信号関係の変化は、DUT14のテスト状態を表わしている。一例として、図2には、第1のサンプリング段階78(図4)においてゾーン01内に位置する座標84が示されている。さらに詳細に後述するように、信号関係の変化は、引き続き、1対のデジタル出力をなすようにデジタル化される。次に、出力対からの少なくとも一方のデジタル出力と、欠陥のないICから得られる対応するデジタル基準信号を比較して、DUTのテスト状態が決定される。これが、一連の出力対に関して繰り返される。

#### 【0032】

DUT14の状態は、欠陥のないICの信号関係が、第1の電流が第2の電流を超える関係である場合に、同じ第1のサンプリング段階78において、その信号関係が、第2の電流が第1の電流を超える関係である場合に、不適当と決定することが可能である。一例として、図5には、図2と同じテスト条件境界を有するx-y平面21が示されている。図5のx-y平面には、欠陥のあるDUTのリサジューの図形86が含まれている。リサジューの図形86は、欠陥のあるDUTを表わすので、図2のリサジューの図形23と異なる位置にある。同じ第1のサンプリング段階において、座標88は、欠陥のないICから得られたので、ゾーン01内ではなく、ゾーン10内であると決定される。異なる座標位置は、第2の電流が第1の電流を超える場合の信号関係を特徴とする。この信号関係は、DUTに欠陥の可能性があることを表わしている。

#### 【0033】

第1の電流( $I_1$ )と第2の電流( $I_2$ )との信号関係は、図3のセンス増幅器42によって加速される。センス増幅器は、比較回路40から第1及び第2の伝導経路56及び58に結合されている。センス増幅器には、第1の加速トランジスタ90及び第2の加速トランジスタ92と、第1のイネーブル・トランジスタ94及び第2のイネーブル・トランジスタ96が含まれている。第1及び第2の加速トランジスタは、NMOSトランジスタ

10

20

30

40

50

とすることが可能である。第1及び第2のイネーブル・トランジスタは、N M O Sトランジスタとすることが可能である。センス増幅器は、第1の電流が第2の電流を超える場合に、第1のノード98におけるノード電圧を増幅し、第2の電流が第1の電流を超える場合に、第2のノード100におけるノード電圧を増幅するように構成されている。第1のノード98は、第1の伝導経路56と関連しており、一方、第2のノード100は、第2の伝導経路58と関連している。

#### 【0034】

図3の監視回路要素12、及び、図4のタイミング図70を参照して、センス増幅器42の動作について述べることにする。テストに先行して、第1のスイッチング・トランジスタ54及び第2のスイッチング・トランジスタ60における高レベルのS E B信号72が、センス増幅器においても受信され、センス増幅器がリセットされる。高レベルのS E B信号は、第1のイネーブル・トランジスタ94のゲート領域102及び第2のイネーブル・トランジスタ96のゲート領域104に結合される。ゲート領域102の高レベルのS E B信号によって、第1のイネーブル・トランジスタが活性化し、第1の伝導経路56と電気的アース105の間が短絡状態になる。同様に、ゲート領域104の高レベルのS E B信号によって、第2のイネーブル・トランジスタが活性化し、第2の伝導経路58と電気的アースの間が短絡状態になる。従って、第1の伝導経路及び第2の伝導経路は、両方とも、リセット期間中に第2のスイッチング・トランジスタ60によって生じる短絡状態によってリンクされるだけではなく、アースに対して短絡させられる。従って、第1の電流は、第2の電流と等しくなる。

10

20

30

40

#### 【0035】

図4の第1のサンプリング段階78において、第1のスイッチング・トランジスタ54及び第2のスイッチング・トランジスタ60における低レベルのS E B信号が、第1のイネーブル・トランジスタ94のゲート領域102及び第2のイネーブル・トランジスタ96のゲート領域104においても受信される。低レベルのS E B信号によって、第1及び第2のイネーブル・トランジスタ94及び96が非活性化し、第1及び第2のイネーブル・トランジスタが開路状態になる。従って、第1の伝導経路56及び第2の伝導経路58のそれぞれが、第1及び第2の加速トランジスタ90及び92に結合される。

#### 【0036】

第1及び第2の加速トランジスタ90及び92は、協働して、第1のノード98と第2のノード100間ににおける電圧差を増幅することで、第1の電流( $I_1$ )と第2の電流( $I_2$ )との信号関係の変化を加速するように構成されている。信号関係の変化の加速については、第1の電流( $I_1$ )が第2の電流( $I_2$ )を超える例によって解説することにする。高レベルの第1の電流は、第1のノード98及び第2の加速トランジスタ92のゲート領域106における高電圧レベルに反映される。低レベルの第2の電流は、第2のノード100及び第1の加速トランジスタ90のゲート領域108における低電圧レベルに反映される。ゲート領域106の高電圧レベルによって、第2の加速トランジスタ92が活性化し、第2のノード100と電気的アース105との間が導通状態になる。第2の加速トランジスタが活動している間に、第2の電流がアースに流れれる。従って、第2のノード100におけるノード電圧は、大地電位と等しくなる。第2の電流がアースに流れているので、第1の加速トランジスタ90のゲート領域108における電圧レベルは、第2の電流から第1の加速トランジスタのゲート領域への電流供給がなくなるため、さらに低下する。ゲート領域108の電圧が降下すると、第1の加速トランジスタ90が非活性化し、第1のノード98とアース間が開路状態になる。第1の加速トランジスタが開路状態にある間に、第1のノード98のノード電圧が、第1のセンストランジスタ44と第1の制御トランジスタ46の和電圧に等しくなる。第2のノード100におけるノード電圧は、大地電位と等しいので、第1のノード98におけるノード電圧は、第2のノードにおけるノード電圧と比べると、増幅されることになる。

#### 【0037】

監視回路要素12には、第1の出力インバータ110及び第2の出力インバータ112も

50

含まれている。第1の出力インバータは、第1のノードにおけるノード電圧を反転して、第1のデジタル出力にするように、第1のノード98に結合されている。第2の出力インバータ112は、第2のノードにおけるノード電圧を反転して、第2のデジタル出力にするように、第2のノード100に結合されている。第1のデジタル出力及び第2のデジタル出力は、相補性デジタル出力であり、それぞれの第1及び第2の出力端子28及び30を介してデジタル・コンパクタ18(図1)に伝送される。対をなす第1及び第2のデジタル出力は、SEB信号と同じ速度でストローブ可能である。デジタル・コンパクタは、複数の第1及び第2のデジタル信号を記憶して、1組の第1及び第2のデジタル出力を発生するように構成されている。

## 【0038】

10

第1及び第2のデジタル出力の発生に引き続き、図3の監視回路要素12に図4の高レベルのSEB信号114が加えられ、第2のサンプリング段階116における次のサンプリングの許可に備えて、監視回路要素12がリセットされる。第2のサンプリング段階では、比較回路40において、新しいサンプル値信号対を受信する。新しいサンプル値信号対は、第1の電流( $I_1$ )と第2の電流( $I_2$ )との信号関係を変化させる。典型的な実施例の1つでは、新しいサンプル値信号によって、図2のx-y平面21内における座標118が決まる。第1の電流が第2の電流を超えるので、この信号関係の変化は、座標がゾーン01内にあることを表わしている。この変化は、センス増幅器によって加速される。新しい1対のデジタル出力が生じ、デジタル・コンパクタ18に送られる。引き続き、別のサンプル値信号対についてテスト・シーケンスが反復され、第1と第2のデジタル出力が生じる。実施例の1つでは、監視回路要素は、100MHzの速度で動作するように構成されている。すなわち、監視回路要素は、1秒の間隔内において、リサジューの図形からの5000万のサンプリングに対する処理が可能である。

20

## 【0039】

20

第1及び第2のデジタル出力のしきい値数に達すると、組をなす第1及び第2のデジタル出力が、デジタル・コンパクタ18から図1の比較器120にスキャン・アウトされる。実施例の1つでは、比較器は、組をなす第1及び第2のデジタル出力と対応する組をなす第1及び第2の所定のデジタル基準信号を比較して、DUTの動作状態を決定するように構成されている。もう1つの実施例では、第1及び第2のデジタル出力が相補性のデジタル出力であるため、組をなす第1及び第2のデジタル出力のうちの第1または第2のデジタル出力だけが、その第1または第2の所定のデジタル基準信号と比較される。前述のように、欠陥のあるDUTの信号関係が、第2の電流が第1の電流を超えるようになっている場合、「間違った」信号関係は、デジタル出力によって表わされることになる。デジタル出力と所定のデジタル基準信号を比較すると、不一致が認められる。実施例の1つでは、比較シーケンスは、DUTが故障と宣言されるまでの、有限範囲の不一致については容認する。

30

## 【0040】

30

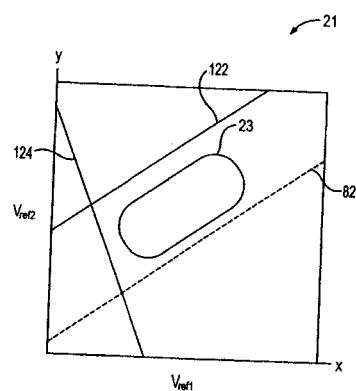

図3の監視回路12の第1及び第2の制御トランジスタ46及び48を流れる特定レベルの電流によって、テスト条件を決める図2の境界82が設定されるが、第1及び第2の制御トランジスタ46及び48を流れる電流のレベルを変化させることによって、異なる境界を設定し、新しいテスト条件を決めることも可能である。電流レベルの変更は、それぞれの第1及び第2の制御トランジスタ46及び48のゲート領域62及び64に異なる固定電圧を印加することによって実現可能である。この変更によって、異なるx-yオフセットが生じ、境界の勾配を変化させるか、または、x-y平面内において境界を上方または下方に移動させることができる。図6には、図2の境界82に対して上方に移動したx-y平面21の境界122が示されている。図6の境界82は、上方移動を全体的に把握できるように点線で示されている。新しい境界122によって、2つの識別可能なゾーンが形成され、リサジューの図形23(DUT14を表わしている)の複数サンプリングによって、リサジューの図形が2つの識別可能なゾーンの一方に含まれるか否かを決定することが可能になる。新しい境界122は、図6に示すように直線で表わされているが

40

50

、曲線も可能である。

【0041】

もう1つの実施例の場合、新しい境界は、図3の監視回路要素12内における第1の伝導経路56及び第2の伝導経路58に対する基準信号及びサンプル値信号の接続順を変更することによって設定可能である。図6に示すように、接続順を変更すると、境界82の勾配が変化し、新しい境界124が形成されることになる。ある接続順の場合、新しい境界は、トランジスタ44及び46がそれぞれの第1及び第2の制御トランジスタになるように、トランジスタ48及び50がそれぞれの第1及び第2のセンス・トランジスタになるように選択することによって設定される。こうして、第1の伝導経路が2つの制御トランジスタに結合され、第2の伝導経路が2つのセンス・トランジスタに結合される。もう1つの接続順の場合、新しい境界は、トランジスタ44及び46がそれぞれの第1及び第2のセンス・トランジスタになるように、トランジスタ48及び50がそれぞれの第1及び第2の制御トランジスタになるように選択することによって設定される。さらにもう1つの接続順の場合、新しい境界は、トランジスタ46及び48がそれぞれの第1及び第2のセンス・トランジスタになるように、トランジスタ44及び50がそれぞれの第1及び第2の制御トランジスタになるように選択することによって設定される。この接続順に対する変更は、スイッチング・マルチブレクサによって実施可能である。

10

【0042】

監視回路要素は、さまざまな境界について同じサンプリング・シーケンスをテストするため、複数回数にわたる調整が可能である。代替案として、等しい数の監視回路によってさまざまな境界を設定することも可能である。

20

【0043】

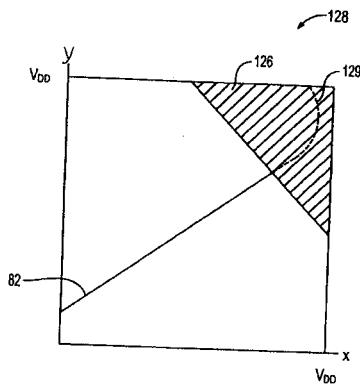

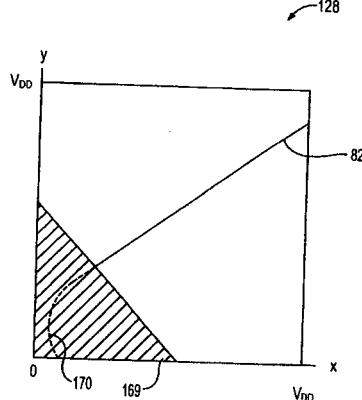

前述のように、図3の比較回路40のトランジスタ44-50は、PMOSトランジスタである。PMOSトランジスタに固有の限界のため、4つのトランジスタ44-50のそれぞれに印加される電圧レベルが $V_{DD}$ に近い場合には、比較回路の性能は劣化する。こうした場合、x-y平面内に、2つのゾーンを形成する境界を有効に設定することができない、処理の行き届かないゾーンが存在する。従って、リサジューの図形も処理の行き届かないゾーン内にある場合には、リサジューの図形を表わした座標位置が、2つの所定のゾーンの一方内にあると適正に識別することができない。図7には、x-y平面128における処理の行き届かないゾーン126（クロスハッティングで表示）が示されている。処理の行き届かないゾーンには、境界82の非線形部分129（点線で表示）が含まれている。非線形部分の辺りでは、2つのゾーンを設定するための境界を有効に設定することはできない。

30

【0044】

処理の行き届かないゾーン内に境界を適正に形成することに関連した問題は、NMOSトランジスタを利用した比較回路によって解決される。図8には、本発明の第2の実施例による監視回路要素130の概略図が示されている。監視回路要素130には、比較回路132とセンス增幅器134が含まれている。比較回路には、NMOSトランジスタ136、138、140、及び、142として識別される4つのトランジスタが含まれている。これらの増幅器には、NMOSトランジスタである第1の加速トランジスタ144及び第2の加速トランジスタ146と、PMOSトランジスタである第1のイネーブル・トランジスタ148及び第2のイネーブル・トランジスタ150が含まれている。

40

【0045】

図3の比較回路40と同様、図8の比較回路132の4つのトランジスタのうち任意の2つを、制御トランジスタまたはセンス・トランジスタに選択することが可能である。典型的な実施例の1つでは、トランジスタ138は、第1の制御トランジスタに選択され、トランジスタ140は、第2の制御トランジスタに選択される。トランジスタ136は、第1のセンス・トランジスタに選択され、トランジスタ142は、第2のセンス・トランジスタに選択される。第1の電流( $I_1$ )用の第1の伝導経路152及び第2の電流( $I_2$ )用の第2の伝導経路154は、比較回路132とセンス增幅器134の間に結合される

50

。第1の伝導経路152は、第1のセンス・トランジスタ136及び第1の制御トランジスタ138のドレン領域(D)において比較回路に結合されている。第2の伝導経路154は、第2の制御トランジスタ140及び第2のセンス・トランジスタ142のドレン領域(D)において比較回路に結合されている。

#### 【0046】

動作中、第1のスイッチング・トランジスタ156及び第2のスイッチング・トランジスタ158において、高レベルのSEB信号を受信する。第1のスイッチング・トランジスタ156における高レベルのSEB信号によって、第1のスイッチング・トランジスタが活性化し、4つのトランジスタ136-142のソース領域とアースの間が短絡状態になり、 $V_{DD}$ レール160からアースに電流を流すことが可能になる。第2のスイッチング・トランジスタ158において受信する高レベルのSEB信号によって、第2のスイッチング・トランジスタが非活性化し、開路状態になる。開路状態の間、第1の伝導経路152は、第1のセンス・トランジスタ136及び第1の制御トランジスタ138に電気的に結合される。第2の伝導経路154は、第2の制御トランジスタ140及び第2のセンス・トランジスタ142に電気的に結合される。

#### 【0047】

第1の伝導経路152を通る第1の電流( $I_1$ )と第2の伝導経路154を通る第2の電流( $I_2$ )との信号関係で特徴付けられるテスト条件は、第1の制御トランジスタ138を通る特定レベルの電流及び第2の制御トランジスタ140を通る特定レベルの電流によって設定される。該テスト条件は、図2のx-y平面21内における境界82によって表わすことが可能である。前述のように、境界によって、x-y平面内に2つの識別可能なゾーン(例えば、ゾーン01及びゾーン10)が形成される。信号関係は、第1のセンス・トランジスタ136及び第2のセンス・トランジスタ142にサンプルが加えられると、検討される。第1のセンス・トランジスタを通る電流は、第1のセンス・トランジスタのゲート領域における第1のサンプル値信号によって制御される。第2のセンス・トランジスタを通る電流は、第2のセンス・トランジスタのゲート領域における第2のサンプル値信号によって制御される。典型的な実施例の1つでは、第1及び第2のサンプル値信号によって、x-y平面21内に座標84が形成される。信号関係の変化は、境界82に対する座標位置を表わしている。テスト・シナリオの1つでは、この変化は、第1の電流が第2の電流を超えるという理由で、座標が境界の一方の側のゾーン01内にあるか、あるいは、第2の電流が第1の電流を超えるという理由で、座標が境界のもう一方の側ゾーン10内にあるかを表わすことになる。

#### 【0048】

第1の電流( $I_1$ )と第2の電流( $I_2$ )との信号関係は、図8のセンス増幅器134によって加速される。センス増幅器は、第1及び第2の伝導経路152及び154に結合される。図3のセンス増幅器42と同様、センス増幅器134は、第1の電流が第2の電流を超えると、第1のノード162のノード電圧を増幅し、第2の電流が第1の電流を超えると、第2のノード164のノード電圧を増幅する。第1の出力インバータ166は、第1のノード162に結合されて、第1のノードのノード電圧を反転し、第1のデジタル出力を発生する。第2の出力インバータ168は、第2のノード164に結合されて、第2のノードのノード電圧を反転し、第2のデジタル出力を発生する。第1のデジタル出力及び第2のデジタル出力は、図1のデジタル・コンパクタ18に伝送される相補性デジタル出力である。

#### 【0049】

図8の比較回路132は、4つのトランジスタ136-142のそれぞれに印加される電圧が $V_{DD}$ に近い場合には、2つの識別可能なゾーンを形成する境界を有効に設定することができるが、電圧がゼロに近い場合には、比較回路の性能が劣化する。性能の劣化は、NMOSトランジスタ136-142に固有の限界によるものである。電圧レベルがゼロに近くになると、x-y平面内に、2つのゾーンを形成する境界を有効に設定することができない、処理の行き届かないゾーンが生じる。従って、リサジューの図形も処理の行き届

10

20

30

40

50

かないゾーン内にある場合には、リサジューの図形を表わした座標位置が、2つの所定のゾーンの一方にあると適正に識別することができなくなる。図9には、x-y平面128における処理の行き届かないゾーン169（クロスハッチングで表示）が示されている。処理の行き届かないゾーンには、境界82の非線形部分170（点線で表示）が含まれている。非線形部分の辺りでは、2つのゾーンを設定するための境界を有効に設定することはできない。しかし、処理の行き届かないゾーン内に適正に境界を形成することに関連した問題は、図3の比較回路40内のPMOSトランジスタを利用することによって解決される。

#### 【0050】

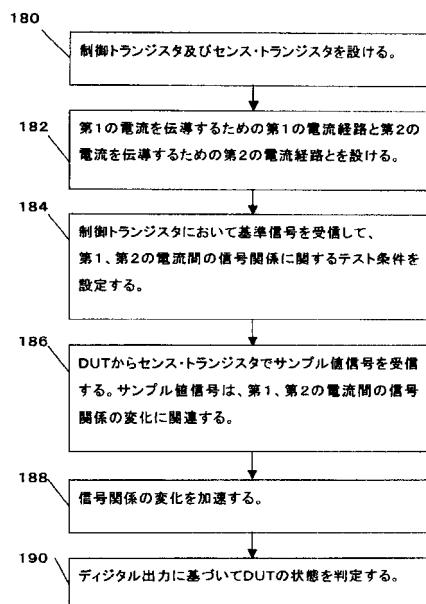

DUTの動作状態を識別するための方法については、図10のプロセス流れ図に関連して述べることにする。ステップ180では、制御トランジスタ及びセンス・トランジスタが設けられる。図3の監視回路要素12に示すように、2つの制御トランジスタ及び2つのセンス・トランジスタが設けられている。4つのトランジスタは、並列に構成されている。監視回路要素において、トランジスタ46は、第1の制御トランジスタであり、トランジスタ48は、第2の制御トランジスタである。トランジスタ44は、第1のセンス・トランジスタであり、トランジスタ50は、第2のセンス・トランジスタである。

#### 【0051】

ステップ182では、第1の電流を伝導するための第1の電流経路( $I_1$ )が設けられる。第2の電流を伝導するための第2の電流経路( $I_2$ )も設けられる。第1の電流経路及び第2の電流経路を設けるステップには、第1の電流経路を4つのトランジスタのうちの任意の2つのソース／ドレイン領域に接続するステップと、第2の電流経路と他の2つのトランジスタのソース／ドレイン領域に接続するステップが含まれている。図3の監視回路要素12において、第1の伝導経路56は、第1のセンス・トランジスタ44及び第1の制御トランジスタ46のドレイン領域に結合されている。第2の伝導経路58は、第2の制御トランジスタ48及び第2のセンス・トランジスタ50のドレイン領域に結合されている。

#### 【0052】

ステップ184では、制御トランジスタにおいて基準信号を受信して、第1の電流と第2の電流との間の信号関係に関するテスト条件が設定される。基準信号は、制御トランジスタを流れる電流を制御するための定レベルの電圧である。基準信号によって、図2のx-y平面内21のゾーン01及びゾーン10を含む、x-y平面内のいくつかの領域を形成することが可能である。

#### 【0053】

ステップ186では、DUTからサンプル値信号を受信する。サンプル値信号は、センス・トランジスタを通る電流を制御するために加えられるアナログ信号である。サンプル値信号によって、図2のx-y平面21内に示す座標84のような、x-y平面内における座標が決まる。サンプル値信号によって、第1の電流と第2の電流との信号関係が変化する。結果生じる信号関係は、サンプル値座標が位置する領域を表している。図2の実施例では、信号関係が、第1の電流が第2の電流を超えるようになっている場合、座標84は、ゾーン01内に位置するものと識別される。

#### 【0054】

ステップ188では、信号関係の変化が、図3のセンス増幅器42のようなセンス増幅器によって加速される。最後に、ステップ190では、DUTの状態が監視回路要素からのデジタル出力に基づいて決定される。

#### 【0055】

以上、実施例に即して本発明を説明したが、本発明の広範な応用の可能性に鑑み、以下に本発明の実施態様の一部を開示して、大方の参考に供する。

#### 【0056】

##### (実施態様1)

被測定物(DUT)(14)の動作状態を識別するための監視回路要素(12；130)

10

20

30

40

50

であって、1組の制御トランジスタ(46及び48；138及び140)、及び、1組のセンス・トランジスタ(44及び50；136及び142)を備え、前記制御トランジスタの制御入力端子(62及び64)が、第1の電流( $I_1$ )と第2の電流( $I_2$ )との間の信号関係に関するテスト条件を設定するための基準信号を受信するように接続され、前記センス・トランジスタが、前記制御トランジスタと連係動作可能であり、センス入力端子(66及び68)を備えていて、前記DUTから受信するサンプル値信号で前記センス入力端子にバイアスをかけると、前記信号関係が変化し、前記信号関係の変化によって、前記DUTの前記動作状態が表わされるようになっている、比較回路(40；132)と、前記比較回路(40；132)に作用的に結合されており、前記信号関係の前記変化を加速するように構成されているセンス増幅器(42；134)とが含まれている監視回路要素。

10

【 0 0 5 7 】

## ( 実施態様 2 )

前記制御トランジスタ（46及び48；138及び140）及び前記センス・トランジスタ（44及び50；136及び142）が、2つの前記制御トランジスタ及び2つの前記センス・トランジスタを含む並列構造をなすように構成されていることを特徴とする、実施態様1に記載の監視回路要素（12；130）。

【 0 0 5 8 】

### ( 実施態様 3 )

さらに、前記第1の電流( $I_1$ )を伝導する第1の伝導経路(56;152)と前記第2の電流( $I_2$ )を伝導する第2の伝導経路(58;154)が含まれることと、前記第1及び第2の伝導経路が、前記並列構造と前記センス増幅器(42;134)の間ににおいて並列に構成されていることと、前記第1及び第2の伝導経路が、それぞれ、(1)2つの前記制御トランジスタ、または、(2)2つの前記センス・トランジスタ、または、(3)1つの前記制御トランジスタ及び1つの前記センス・トランジスタのソース/ドレイン領域に結合されていることを特徴とする、実施態様1または2に記載の監視回路要素(12;130)。

20

[ 0 0 5 9 ]

### ( 実施態様 4 )

前記制御トランジスタ（46及び48；138及び140）の制御入力端子（62及び64）で受信する前記基準信号が、前記制御トランジスタを流れる電流を制御するための一一定レベルの電圧であることを特徴とする、実施態様1、2、または、3に記載の監視回路要素（12；130）。

30

( 0 0 6 0 )

( 実施態様 5 )

前記基準信号が、 $x - y$  平面 ( $21 ; 128$ ) における境界 ( $82 ; 122 ; 124$ ) を決めるように選択されることと、前記境界によって、前記  $x - y$  平面における 2 つのゾーン ( $01$  及び  $10$ ) を識別できるようにすることを特徴とする、実施態様 1、2、3、または、4 に記載の監視回路要素 ( $12 : 130$ )。

40

( 0 0 6 1 )

( 実施熊様 6 )

前記サンプル値信号が、サンプリング段階（78及び116）において、前記センス・トランジスタ（44及び50；136及び142）のセンス入力端子（66及び68）で受信され、前記信号関係に前記変化を生じさせることと、前記サンプル値信号が、前記センス・トランジスタを通る電流を制御するために加えられるアナログ信号であることと、前記サンプル値信号によって、前記x-y平面における座標（84及び118；88）が決まることを特徴とする、実施態様5に記載の監視回路要素（12；130）。

〔 0 0 6 2 〕

( 実施態様 7 )

前記変化が、前記境界 ( 8 2 : 1 2 2 : 1 2 4 ) に対する前記座標 ( 8 4 及び 1 1 8 : 8

50

8 ) の位置を表わすことを特徴とする、実施態様 5 または 6 に記載の監視回路要素 ( 1 2 ; 1 3 0 )。

【 0 0 6 3 】

( 実施態様 8 )

前記センス増幅器 ( 4 2 ; 1 3 4 ) が、前記第 1 の電流 (  $I_1$  ) が前記第 2 の電流 (  $I_2$  ) を超える場合には、第 1 のノード ( 9 8 ; 1 6 2 ) における第 1 のノード電圧を増幅するように構成されていることと、前記センス増幅器が、前記第 2 の電流が前記第 1 の電流を超える場合には、第 2 のノード ( 1 0 0 ; 1 6 4 ) における第 2 のノード電圧を増幅するようにも構成されていることと、前記第 1 のノードが、前記第 1 の伝導経路 ( 9 8 ; 1 6 2 ) に関連しており、前記第 2 のノードが、前記第 2 の伝導経路 ( 5 8 ; 1 5 4 ) に関連していることを特徴とする、実施態様 1 、 2 、 3 、 4 、 5 、 6 、または、 7 に記載の監視回路要素 ( 1 2 ; 1 3 0 )。 10

【 0 0 6 4 】

( 実施態様 9 )

さらに、第 1 の出力インバータ ( 1 1 0 ; 1 6 6 ) と、第 2 の出力インバータ ( 1 1 2 ; 1 6 8 ) が含まれることと、前記第 1 の出力インバータが、前記第 1 のノード ( 9 8 ; 1 6 2 ) に結合されて、前記第 1 のノード電圧を反転し、第 1 のデジタル出力を生成するように構成されていることと、前記第 2 の出力インバータが、前記第 2 のノード ( 1 0 0 ; 1 6 4 ) に結合されて、前記第 2 のノード電圧を反転し、第 2 のデジタル出力を生成するように構成されていることと、前記第 1 及び第 2 のデジタル出力が、相補性デジタル信号であることを特徴とする、実施態様 8 に記載の監視回路要素 ( 1 2 ; 1 3 0 )。 20

【 0 0 6 5 】

( 実施態様 1 0 )

前記第 1 及び第 2 の出力インバータが、前記第 1 及び第 2 のデジタル出力の少なくとも一つと対応する第 1 及び第 2 の所定の基準デジタル信号を比較して、前記 D U T ( 1 4 ) の前記動作状態を決定するための処理装置 ( 1 2 0 ) に作用的に結合されていることを特徴とする、実施態様 9 に記載の監視回路要素 ( 1 2 ; 1 3 0 )。

【 0 0 6 6 】

( 実施態様 1 1 )

被測定物 ( D U T ) の動作状態を識別するための方法であって、制御トランジスタ ( 4 6 及び 4 8 ; 1 3 8 及び 1 4 0 ) 、及び、センス・トランジスタ ( 4 4 及び 5 0 ; 1 3 6 及び 1 4 2 ) を含む複数のトランジスタを設ける ( 1 8 0 ) ステップと、前記制御トランジスタにおいて基準信号を受信し ( 1 8 4 ) 、第 1 の電流 (  $I_1$  ) と第 2 の電流 (  $I_2$  ) との信号関係に関してテスト条件を設定するステップと、前記センス・トランジスタにおいて、前記第 1 の電流と前記第 2 の電流との信号関係を決定するために加えられる、前記 D U T からの信号サンプルを受信する ( 1 8 6 ) ステップと、前記信号サンプルが加えられた後、前記信号関係に基づいて、前記 D U T の前記動作状態を決定する ( 1 9 0 ) ステップと

が含まれている動作状態識別方法。

【 0 0 6 7 】

( 実施態様 1 2 )

さらに、前記第 1 の電流 (  $I_1$  ) を伝導するための第 1 の電流経路 ( 5 6 ; 1 5 2 ) と、第 2 の電流 (  $I_2$  ) を伝導するための第 2 の電流経路 ( 5 8 ; 1 5 4 ) を設ける ( 1 8 2 ) ステップが含まれており、このステップに、前記第 1 の電流経路を任意の 2 つの前記トランジスタのソース / ドレイン領域に接続し、前記第 2 の電流経路を他の 2 つの前記トランジスタのソース / ドレイン領域に接続するステップが含まれることを特徴とする、実施態様 1 1 に記載の動作状態識別方法。

【 0 0 6 8 】

( 実施態様 1 3 )

前記基準信号の受信ステップ ( 1 8 4 ) に、前記制御トランジスタ ( 4 6 及び 4 8 ; 1 3 50

8 及び 140) によって導通される電流を制御するための定電圧を受けるステップが含まれることと、前記基準信号によって、x - y 平面 (21 ; 128) における複数の領域 (01 及び 10) が決まることを特徴とする、実施態様 11 または 12 に記載の動作状態識別方法。

**【0069】**

(実施態様 14)

前記信号サンプルの受信ステップ (186) に、前記センス・トランジスタ (44 及び 50 ; 136 及び 142) によって導通される電流を制御するためのアナログ信号を受信するステップが含まれることと、前記信号サンプルによって、前記 x - y 平面 (21 ; 128) における座標 (84 及び 118 ; 88) が決まることを特徴とする、実施態様 11、12、または、13 に記載の動作状態識別方法。

10

**【0070】**

(実施態様 15)

さらに、前記信号関係を識別することによって、前記 x - y 平面 (21 ; 128) における複数の領域 (01 及び 10) 内の 1 つに位置するように前記座標 (84 及び 118 ; 88) を設定するステップが含まれることと、前記信号関係が、前記第 1 の電流 (I<sub>1</sub>) が前記第 2 の電流 (I<sub>2</sub>) を超える関係か、または、前記第 2 の電流が前記第 1 の電流を超える関係であることを特徴とする、実施態様 11、12、13、または、14 に記載の動作状態識別方法。

**【図面の簡単な説明】**

【図 1】被測定物 (DUT) から第 1 のサンプル値信号及び第 2 のサンプル値信号を受信して、DUT の動作状態を決定するように構成された監視回路要素を備えるシステムを示すプロック図である。

【図 2】図 1 の監視回路要素のテスト条件を表わした境界に関連したリサジューの図形を示す x - y 平面を表わした図である。

【図 3】本発明の第 1 の実施例による図 1 の監視回路要素の概略回路図である。

【図 4】図 3 の監視回路要素の動作シーケンスを例示したタイミング図である。

【図 5】リサジューの図形の座標が特定ゾーン内にある場合、DUT に欠陥の可能性があることを示す、図 2 の x - y 平面を表わした図である。

【図 6】複数の異なる境界を例示する図 2 の x - y 平面を表わした図である。

【図 7】図 3 の監視回路要素による境界の有効な設定ができない、処理の行き届かないゾーンを備える x - y 平面を表わした図である。

【図 8】本発明の第 2 の実施例による図 1 の監視回路要素の概略回路図である。

【図 9】図 8 の監視回路要素による境界の有効な設定ができない、処理の行き届かないゾーンを備える x - y 平面を表わした図である。

【図 10】本発明に従って DUT のテスト状態を識別するためのプロセスの流れ図である。

**【符号の説明】**

12 監視回路要素

14 DUT

21 x - y 平面

40 比較回路

42 センス増幅器

44 センス・トランジスタ

46、48 制御トランジスタ

50 センス・トランジスタ

56 第 1 の伝導経路

58 第 2 の伝導経路

62、64 制御入力端子

66、68 センス入力端子

20

30

40

50

8 2 境界

8 4、1 1 8、8 8 x - y 平面における座標

9 8 第1のノード

1 0 0 第2のノード

1 1 0 第1の出力インバータ

1 1 2 第2の出力インバータ

1 2 0 処理装置

1 2 2、1 2 4 境界

1 2 8 x - y 平面

1 3 0 監視回路要素

1 3 2 比較回路

1 3 4 センス増幅器

1 3 6 センス・トランジスタ

1 3 8、1 4 0 制御トランジスタ

1 4 2 センス・トランジスタ

1 5 2 第1の伝導経路

1 5 4 第2の伝導経路

1 6 2 第1のノード

1 6 4 第2のノード

1 6 6 第1の出力インバータ

1 6 8 第2の出力インバータ

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

## フロントページの続き

(72)発明者 ジョーン フィグラス

スペイン国 シトゲス 08870 アンジェル・ヴィダル 22

(72)発明者 フィデル マラダリ

アメリカ合衆国 カリフォルニア 94040 マウンテン・ビュー コンチネンタル・サークル

707

F ターム(参考) 2G132 AA12 AB02 AC03 AG09 AK09 AK10 AK22 AK29