(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-14904

(P2011-14904A)

(43) 公開日 平成23年1月20日(2011.1.20)

(51) Int.Cl.

H01L 21/768 (2006.01)

H01L 23/522 (2006.01)

F 1

H01L 21/90

B

テーマコード(参考)

5FO33

審査請求 未請求 請求項の数 20 O L (全 18 頁)

(21) 出願番号 特願2010-142938 (P2010-142938)

(22) 出願日 平成22年6月23日 (2010.6.23)

(31) 優先権主張番号 12/494564

(32) 優先日 平成21年6月30日 (2009.6.30)

(33) 優先権主張国 米国(US)

(71) 出願人 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】 ピアガウジングされた相互接続構造体及びその製造方法

## (57) 【要約】

【課題】 ピア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ピア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ピア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりピア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ピア開口部、次いでガウジング構造部を形成することによって、ピア開口部の底部内にガウジング構造部を提供することにより達成される。

【選択図】 図14

## 【特許請求の範囲】

## 【請求項 1】

少なくとも 1 つの導電性構造部が内部に埋め込まれた第 1 の誘電体材料を含む下部相互接続レベルと、

前記第 1 の誘電体材料及び前記少なくとも 1 つの導電性構造部の全てではなく一部分の上に配置された誘電体キャッピング層と、

少なくとも 1 つの導電性充填ビア及び上にある導電性充填ラインが内部に配置された第 2 の誘電体材料を含む上部相互接続レベルであって、前記少なくとも 1 つの導電性充填ビアは、ガウジング構造部によって前記下部相互接続レベルの前記少なくとも 1 つの導電性構造部の露出面と接触しており、前記少なくとも 1 つの導電性充填ラインは、前記少なくとも 1 つの導電性充填ラインを前記第 2 の誘電体材料の上部から分離する、トレンチ拡散バリアと、組み合わされたトレンチ及びビア拡散バリアとを含み、一方、前記少なくとも 1 つの導電性充填ビアは、前記少なくとも 1 つの導電性充填ビアの下部と前記第 2 の誘電体材料を分離する前記組み合わされたトレンチ及びビア拡散バリアのみを含み、前記組み合わされたトレンチ及びビア拡散バリアは、前記少なくとも 1 つの導電性充填ビアの下部と前記第 1 の誘電体材料内に埋め込まれた前記少なくとも 1 つの導電性構造部との間の前記ガウジング構造部にも配置される、上部相互接続レベルと、

を含む半導体相互接続構造体。

## 【請求項 2】

前記第 1 及び第 2 の誘電体材料は、4.0 以下の誘電率を有する同じ又は異なる低 k 誘電体を含む、請求項 1 に記載の半導体相互接続構造体。

## 【請求項 3】

前記誘電体キャッピング層は、SiC、Si<sub>4</sub>NH<sub>3</sub>、SiO<sub>2</sub>、炭素ドープ酸化物、窒素及び水素ドープ炭化シリコン SiC (N, H)、又はそれらの多層構造の 1 つを含む、請求項 1 に記載の半導体相互接続構造体。

## 【請求項 4】

前記少なくとも 1 つの導電性充填ビア及び前記少なくとも 1 つの上にある導電性充填ラインは、Cu 又は Cu 含有合金を含む、請求項 1 に記載の半導体相互接続構造体。

## 【請求項 5】

前記トレンチ拡散バリアは、TaN、Ta、Ti、TiN、RuTa、RuTaN、W、Ru、Co、Rh、Ir、又はそれらの任意の組み合わせを含む、請求項 1 に記載の半導体相互接続構造体。

## 【請求項 6】

前記組み合わされたトレンチ及びビア拡散バリアは、Ta<sub>N</sub>、Ta、Ti、TiN、RuTa、RuTaN、W、Ru、Co、Rh、Ir、又はそれらの任意の組み合わせを含む、請求項 1 に記載の半導体相互接続構造体。

## 【請求項 7】

前記組み合わされたトレンチ及びビア拡散バリア上に配置されためっきシード層をさらに含む、請求項 1 に記載の半導体相互接続構造体。

## 【請求項 8】

前記めっきシード層は、Ru、TaRu、Ir、Rh、Pt、Pd、Ta、Cu、又はそれらの合金のうちの 1 つ若しくは組み合わせを含む、請求項 7 に記載の半導体相互接続構造体。

## 【請求項 9】

前記ガウジング構造部に配置され、かつ、前記組み合わされたトレンチ及びビア拡散バリアと前記第 1 の誘電体材料内の前記下にある少なくとも 1 つの導電性構造部との間に配置された金属界面層をさらに含む、請求項 1 に記載の半導体相互接続構造体。

## 【請求項 10】

前記金属界面層は、Co、Ta<sub>N</sub>、Ta、Ti、TiN、Ru、Ir、Au、Rh、Pt、Pd、Ag、又はそれらの合金を含む、請求項 9 に記載の半導体相互接続構造体。

10

20

30

40

50

## 【請求項 1 1】

半導体相互接続構造体を形成する方法であって、

少なくとも 1 つの導電性構造部が内部に埋め込まれた第 1 の誘電体材料と、前記第 1 の誘電体材料の上方に配置された第 2 の誘電体材料とを含む構造体を準備するステップであって、前記第 1 の誘電体材料は、トレンチ拡散バリアでライニングされた少なくとも 1 つのライン開口部が内部に配置されている、ステップと、

前記第 2 の誘電体材料内に少なくとも 1 つの拡張されたビア開口部を形成するステップと、

前記少なくとも 1 つの導電性構造部内に少なくとも 1 つのガウジング構造部を形成するステップと、

前記少なくとも 1 つのライン開口部及び前記少なくとも 1 つの拡張されたビア開口部内、及び、前記少なくとも 1 つのガウジング構造部の上に、組み合わされたトレンチ及びビア拡散バリアを形成するステップと、

前記少なくとも 1 つのライン開口部及び前記少なくとも 1 つのビア開口部を相互接続導電性材料で充填するステップと、

を含む方法。

## 【請求項 1 2】

前記少なくとも 1 つの拡張されたビア開口部を形成する前記ステップは、

前記少なくとも 1 つのライン開口部内、及び、前記第 2 の誘電体材料の上に、平坦化材料を形成するステップと、

前記平坦化材料の上面上にパターン形成された酸化物含有材料を形成するステップであって、前記パターン形成された酸化物含有材料は、少なくとも 1 つの初期ビア・パターンを内部に有する、ステップと、

前記少なくとも 1 つの平坦化層、前記トレンチ拡散バリア及び前記第 2 の誘電体材料を通って前記少なくとも 1 つの初期ビア・パターンを延ばし、前記第 2 の誘電体材料内に前記少なくとも 1 つの拡張されたビア開口部を提供するステップと、

を含む、請求項 1 1 に記載の方法。

## 【請求項 1 3】

前記少なくとも 1 つのガウジング構造部を形成する前記ステップは、Ar、He、Ne、Xe、N<sub>2</sub>、H<sub>2</sub>、NH<sub>3</sub>、N<sub>2</sub>H<sub>2</sub>、又はそれらの混合物の 1 つを含むガス・スパッタリングを含む、請求項 1 1 に記載の方法。

## 【請求項 1 4】

前記ガス・スパッタリングは、前記第 1 の誘電体材料と前記第 2 の誘電体材料との間に配置された誘電体キャッピング層をも開口する、請求項 1 3 に記載の方法。

## 【請求項 1 5】

前記誘電体キャッピング層は、前記第 1 の誘電体材料と前記第 2 の誘電体材料との間に配置され、前記少なくとも 1 つの拡張されたビア開口部を形成する前記ステップと前記ガウジング構造部を形成する前記ステップとの間にエッチング・ステップを行って、前記誘電体キャッピング層をパターン形成する、請求項 1 1 に記載の方法。

## 【請求項 1 6】

半導体相互接続構造体を形成する方法であって、

少なくとも 1 つの導電性構造部が内部に埋め込まれた第 1 の誘電体材料と、前記第 1 の誘電体材料の上方に配置された第 2 の誘電体材料とを含む構造体を準備するステップであって、前記第 1 の誘電体材料は少なくとも 1 つのライン開口部を有する、ステップと、

前記第 2 の誘電体材料内に少なくとも 1 つの拡張されたビア開口部を形成するステップと、

前記少なくとも 1 つの導電性構造部内に少なくとも 1 つのガウジング構造部を形成するステップと、

前記少なくとも 1 つのライン開口部及び前記少なくとも 1 つの拡張されたビア開口部内、及び、前記少なくとも 1 つのガウジング構造部の上に、組み合わされたトレンチ及びビ

10

20

30

40

50

ア拡散バリアを形成するステップと、

前記少なくとも1つのライン開口部及び前記少なくとも1つのビア開口部を相互接続導電性材料で充填するステップと、

を含む方法。

【請求項17】

前記少なくとも1つの拡張されたビア開口部を形成する前記ステップは、

前記少なくとも1つのライン開口部内、及び、前記第2の誘電体材料の上に、平坦化材料を形成するステップと、

前記平坦化材料の上面上にパターン形成された酸化物含有材料を形成するステップであって、前記パターン形成された酸化物含有材料は、少なくとも1つの初期ビア・パターンを内部に有する、ステップと、

前記少なくとも1つの平坦化層及び前記第2の誘電体材料を通って前記少なくとも1つの初期ビア・パターンを延ばし、前記第2の誘電体材料内に前記少なくとも1つの拡張されたビア開口部を提供するステップと、

を含む、請求項16に記載の方法。

【請求項18】

前記少なくとも1つのガウジング構造部を形成する前記ステップは、Ar、He、Ne、Xe、N<sub>2</sub>、H<sub>2</sub>、NH<sub>3</sub>、N<sub>2</sub>H<sub>2</sub>、又はそれらの混合物の1つを含むガス・スパッタリングを含む、請求項16に記載の方法。

【請求項19】

前記ガス・スパッタリングは、前記第1の誘電体材料と前記第2の誘電体材料との間に配置された誘電体キャッピング層をも開口する、請求項18に記載の方法。

【請求項20】

前記誘電体キャッピング層は、前記第1の誘電体材料と前記第2の誘電体材料との間に配置され、前記少なくとも1つの拡張されたビア開口部を形成する前記ステップと前記ガウジング構造部を形成する前記ステップとの間にエッチング・ステップを行って、前記誘電体キャッピング層をパターン形成する、請求項16に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体構造体及びその製造方法に関する。より具体的には、本発明は、ビア開口部の底部に配置されたガウジング構造部 (gouging feature) を含む半導体相互接続構造体、及びその製造方法に関する。

【背景技術】

【0002】

一般に、半導体デバイスは、半導体基板上に製造された、集積回路を形成する複数の回路を含む。基板の表面上に分布する回路素子を接続するために、信号経路の複雑なネットワークが通常、経路設定される。デバイス全体にわたるこれらの信号の効率的な経路設定は、例えば、シングル又はデュアル・ダマシン配線構造のような多重レベル又は多層方式の形成を必要とする。典型的な相互接続構造体内において、金属ビアは、半導体基板に対して垂直に延び、金属ラインは、半導体基板に対して平行に延びる。

【0003】

何百万というデバイス及び回路が1つの半導体チップ上に詰め込まれるに従って、世代を経るごとに配線密度及び金属レベルの数の両方が増大される。高い信号速度に対して低いRCを提供するために、二酸化シリコンより低い誘電率を有する低k誘電体材料、及び、銅含有ラインが不可欠なものになりつつある。歩留まり及び信頼性を確実にするために、従来のダマシン・プロセスによって形成された薄い金属配線及びスタッドの品質は、極めて重要である。今日、この領域において直面する主要な問題は、低k誘電体材料内に埋め込まれたディープ・サブミクロン (deep submicron) の金属スタッドの機械的完全性が不十分であることであり、このことが、相互接続構造体内に不満足な熱サイクル及びスト

10

20

30

40

50

レスマイグレーション耐性をもたらすことがある。この問題は、新しいメタライゼーション手法又は多孔性低 k 誘電体材料のいずれかが用いられるとき、より深刻になる。

【0004】

相互接続構造体内に銅ダマシン及び低 k 誘電体材料を用いながら、この脆弱な機械的強度の問題を解決するために、半導体業界により、いわゆる「ビア・パンチスルー(via punch-through)」技術が採用された。ビア・パンチスルーは、相互接続構造体内にビア・ガウジング構造部(すなわち、アンカー領域)を提供するものである。こうしたビア・ガウジング構造部は、適度なコンタクト抵抗、及び、コンタクト・スタッドの機械的強度の増大を達成することが報告されている。

【0005】

しかしながら、従来技術においてビア・ガウジングを生成するのに用いられるアルゴン・スパッタリング技術は、トレンチ(すなわち、ライン開口部)底部から、例えばTaNなどの堆積されたライナ材料を除去するだけではなく、低 k 誘電体材料に損傷も与える。ガウジング構造部を生成する要件のために、最終的な相互接続構造体は、トレンチ底部におけるライナ被覆率が低いだけではなく、Arスパッタリング・プロセスにより、低 k 誘電体材料内に深刻な損傷が生じた。このことは、高度なチップ製造に関する主な歩留まり低下原因及び信頼性の問題になっている。

【0006】

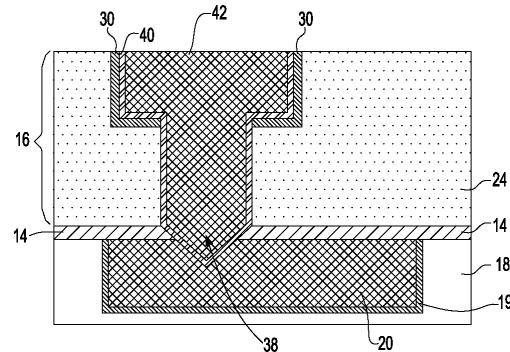

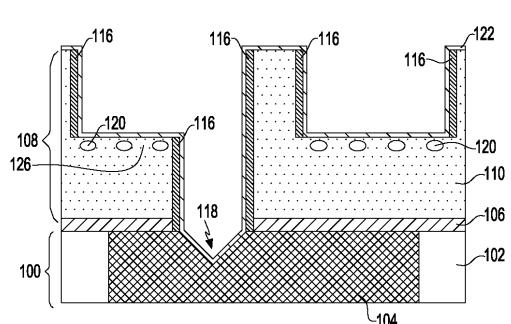

ビア・ガウジングについての既存の従来技術手法の詳細な処理ステップが、図1-図5に示され、ここで以下に説明される。最初に、下部相互接続レベル100の上に配置された上部相互接続レベル108のデュアル・ダマシンをパターン形成した後に形成される、従来技術の構造体を示す図1を参照する。下部相互接続レベル100は、内部に金属、すなわちCuの構造部104を含む第1の低 k 誘電体材料102を含む。下部相互接続レベル100は、キャッピング層106によって、上部相互接続レベル108から部分的に分離されている。上部相互接続レベル108は、内部に配置されたライン開口部112及びビア開口部114の両方を含む第2の低 k 誘電体材料110を含む。図1に示されるように、ビア開口部114の下方にある、下部相互接続レベル100の金属構造部104の表面は露出されている。

【0007】

図2は、露出面の全ての上に、例えばTaNなどの拡散バリア116を形成した後の図1の従来技術の構造体を示す。次に、図3に示されるようなアルゴン・スパッタリングを行なって、ビア開口部114内の底部の水平面を洗浄し、かつ、下部相互接続レベル100の金属構造部104内にガウジング構造部(すなわち、アンカー領域)118を形成する。ガウジング構造部118は、示される種々の相互接続レベル間の相互接続強度を強化ために用いられる。Arスパッタリング・プロセス中、ライン開口部112の各々の底部から拡散バリア116が除去され、誘電体の損傷120(第2の低 k 誘電体材料110内の丸印で示される)が、ライン開口部112の各々の底部に形成される。スパッタリング・プロセス中に形成される誘電体の損傷120は、従来技術のスパッタリング・プロセス固有の攻撃的な性質に起因するものである。

【0008】

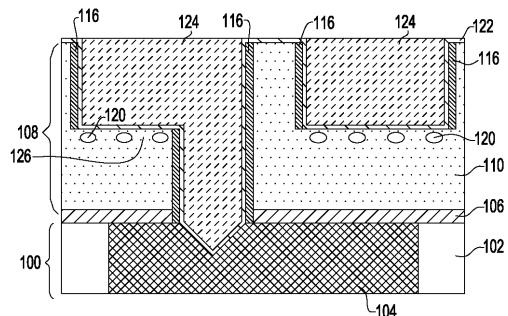

図4は、その露出面上に、例えばTa、Ru、Ir、Rh、又はPtなどの金属ライナ層122を形成した後の図3の従来技術の構造体を示す。図5は、ライン開口部112及びビア開口部114を、例えばCuなどの導電性金属124で充填し、平坦化した後の従来技術の構造体を示す。図5に示されるように、従来技術の構造体は、金属充填ラインの底部における拡散バリア116の被覆率(参照番号126で示される)が低く、第2の低 k 誘電体材料110内に形成された損傷120の結果として構造部の底部が粗い。これらの特性の両方が、拡散バリア116の品質を低下させ、全体的な配線の信頼性を低下させる。さらに、前述の特性の両方により、高レベルの金属間漏れを示す構造体がもたらされる。

【発明の概要】

10

20

30

40

50

## 【発明が解決しようとする課題】

## 【0009】

従来の相互接続構造体に関する上記の欠点に鑑みて、相互接続誘電体材料内に形成されたライン開口部の水平面から拡散バリアが除去されるのを回避し、それにより、相互接続誘電体材料内に損傷が生じない、新しい改善された統合スキームを開発することに対する必要性が存在する。

## 【課題を解決するための手段】

## 【0010】

本発明は、ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。本発明の方法は、ビア開口部の上に配置されたライン開口部内の堆積された拡散バリアの被覆率に影響を与える、及び／又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。本発明によれば、こうした相互接続構造体は、最初に相互接続誘電体材料内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

## 【0011】

本発明においては、ビア開口部及びガウジング構造部を形成する前にライン開口部が形成されるが、少なくとも平坦化材料、及び隨意的なトレンチ拡散バリアによってビア開口部及びガウジング構造部を形成する間、ライン開口部の部分が保護されるので、相互接続誘電体材料の損傷は生じない。従って、本発明の方法は、図1-図5に示された技術を用いて製造されるもののような従来技術の相互接続構造体よりも配線が改善され、金属間の漏れのレベルが低い、ビア開口部の底部のガウジング構造部を含む相互接続構造体を提供する。

## 【0012】

本発明の一実施形態においては、少なくとも1つの導電性構造部が内部に埋め込まれた第1の誘電体材料を含む下部相互接続レベルと、第1の誘電体材料及び少なくとも1つの導電性構造部の全てではなく一部分の上に配置された誘電体キャッピング層と、少なくとも1つの導電性充填ビア (conductively filled via) 及び上にある導電性充填ライン (conductively filled line) が内部に配置された第2の誘電体材料を含む上部相互接続レベルとを含み、少なくとも1つの導電性充填ビアは、ガウジング構造部、すなわちアンカー領域によって、第1の相互接続レベルの少なくとも1つの導電性構造部の露出面と接触している。

## 【0013】

本発明の構造体において、少なくとも1つの導電性充填ラインは、第2の誘電体材料の上部から少なくとも1つの導電性充填ラインを分離するトレンチ拡散バリア及び組み合わされたトレンチ及びビア拡散バリアを含み、少なくとも1つの導電性充填ビアは、少なくとも1つの導電性充填ビアの下部と第2の誘電体材料を分離する組み合わされたトレンチ及びビア拡散バリアのみを含み、組み合わされたトレンチ及びビア拡散バリアは、少なくとも1つの導電性充填ビアの下部と第1の誘電体材料内に埋め込まれた少なくとも1つの導電性構造部との間のガウジング構造部にも配置される。

## 【0014】

「組み合わされたトレンチ及びビア拡散バリア (combined trench and via diffusion barrier)」という用語は、導電性充填ライン、導電性充填ビア及びガウジング構造部内に存在する連続的な拡散バリアを示すことが認められる。これは、本発明の相互接続構造体の導電性充填ライン内にのみ存在するトレンチ拡散バリアのものとは異なる層又は材料スタックを表す。

## 【0015】

本発明の別の態様は、上述の相互接続構造体を製造する方法に関する。本発明の方法は、少なくとも1つの導電性構造部が内部に埋め込まれた第1の誘電体材料と、第1の誘電

体材料の上方に配置された第2の誘電体とを含む構造体を準備するステップであって、第1の誘電体材料は、トレンチ拡散バリアでライニングされた（line、内側が覆われた）、少なくとも1つのライン開口部が内部に配置されている、ステップと、第2の誘電体材料内に少なくとも1つの拡張されたビア開口部を形成するステップと、少なくとも1つの導電性構造部内に少なくとも1つのガウジング構造部を形成するステップと、少なくとも1つのライン開口部及び少なくとも1つの拡張されたビア開口部内、及び、少なくとも1つのガウジング構造部の上に、組み合わされたトレンチ及びビア拡散バリアを形成するステップと、少なくとも1つのライン開口部及び少なくとも1つのビア開口部を相互接続導電性材料で充填するステップとを含む。

【0016】

10

本発明の幾つかの実施形態においては、トレンチ拡散バリアを省略することができる。トレンチ拡散バリアが用いられないとき、処理ステップは、少なくとも1つの導電性構造部が内部に埋め込まれた第1の誘電体材料と、第1の誘電体材料の上方に配置された第2の誘電体とを含む構造体を準備するステップであって、第1の誘電体材料は少なくとも1つのライン開口部を有する、ステップと、第2の誘電体材料内に少なくとも1つの拡張されたビア開口部を形成するステップと、少なくとも1つの導電性構造部内に少なくとも1つのガウジング構造部を形成するステップと、少なくとも1つのライン開口部及び少なくとも1つのガウジング構造部の上に、組み合わされたトレンチ及びビア拡散バリアを形成するステップと、少なくとも1つのライン開口部及び少なくとも1つのビア開口部を相互接続導電性材料で充填するステップとを含む。

20

【図面の簡単な説明】

【0017】

【図1】相互接続構造体を形成する際に従来技術に用いられる基本的な処理ステップを示す図形的表示（断面図による）である。

【図2】相互接続構造体を形成する際に従来技術に用いられる基本的な処理ステップを示す図形的表示（断面図による）である。

【図3】相互接続構造体を形成する際に従来技術に用いられる基本的な処理ステップを示す図形的表示（断面図による）である。

【図4】相互接続構造体を形成する際に従来技術に用いられる基本的な処理ステップを示す図形的表示（断面図による）である。

30

【図5】相互接続構造体を形成する際に従来技術に用いられる基本的な処理ステップを示す図形的表示（断面図による）である。

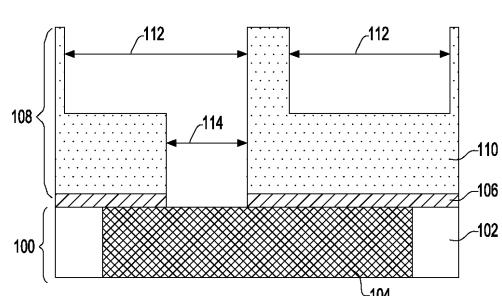

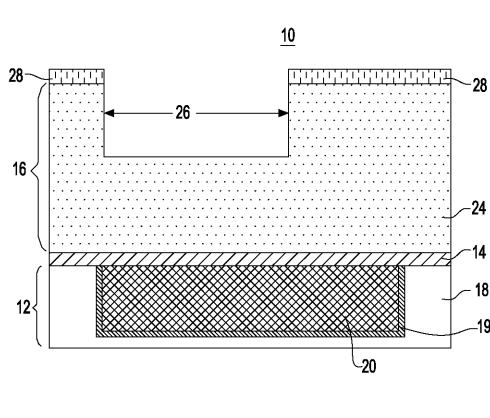

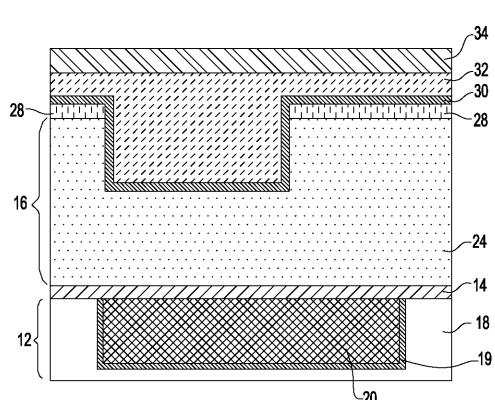

【図6】初期構造体の上部相互接続レベル内にライン開口部を形成した後の、本発明の初期構造体を示す図形的表示（断面図による）である。

【図7】少なくともライン開口部内にトレンチ拡散バリアを形成した後の、図6の構造体を示す図形的表示（断面図による）である。

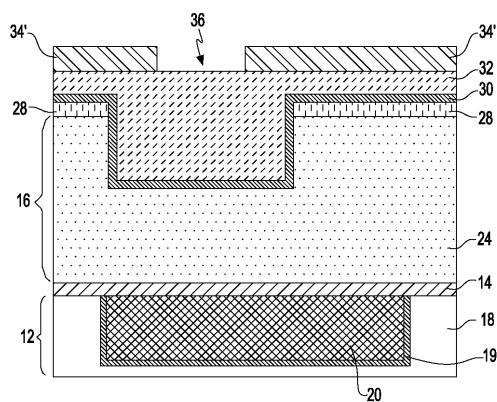

【図8】平坦化層及び酸化物含有層を形成した後の、図7の構造体を示す図形的表示（断面図による）である。

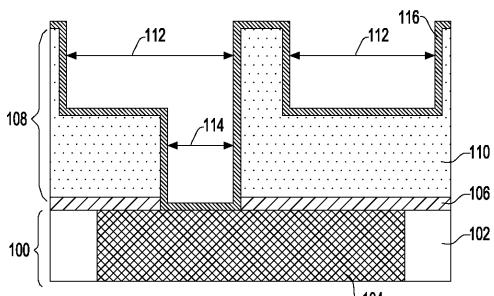

【図9】酸化物含有層内にビア開口部を形成した後の、図8の構造体を示す図形的表示（断面図による）である。

40

【図10】ビア開口部を下にある下部相互接続レベル内の導電性構造部まで延長した後の、図9の構造体を示す図形的表示（断面図による）である。

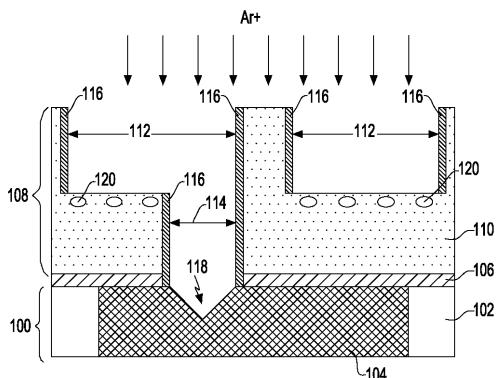

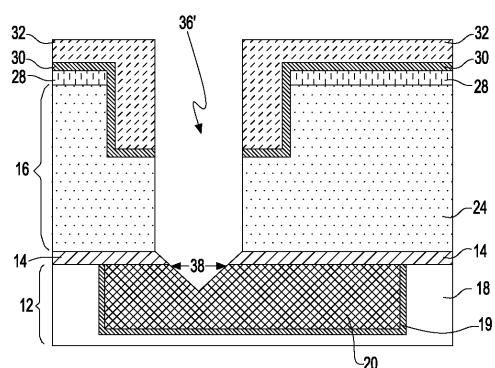

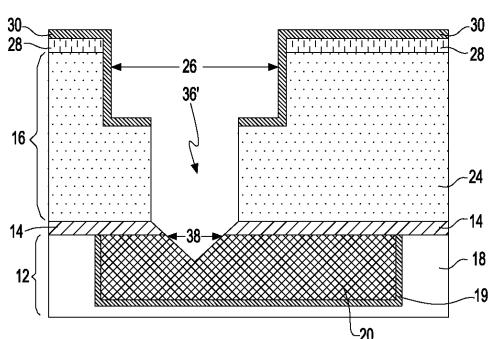

【図11】下にある下部相互接続レベル内の導電性構造部の中にガウジング構造部を形成した後の、図10の構造体を示す図形的表示（断面図による）である。

【図12】ライン開口部から残りの平坦化材料を除去した後の、図11の構造体を示す図形的表示（断面図による）である。

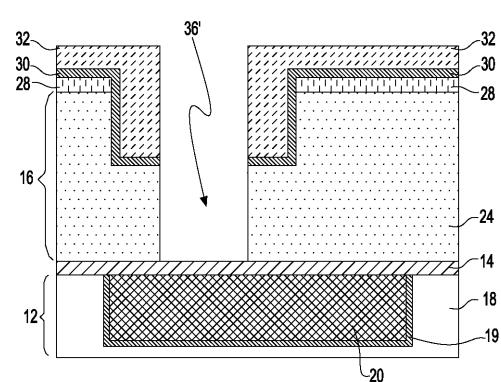

【図13】ビア開口部及びライン開口部の両方の内部に組み合わされたトレンチ及びビア拡散バリアを形成した後の、図12の構造体を示す図形的表示（断面図による）である。

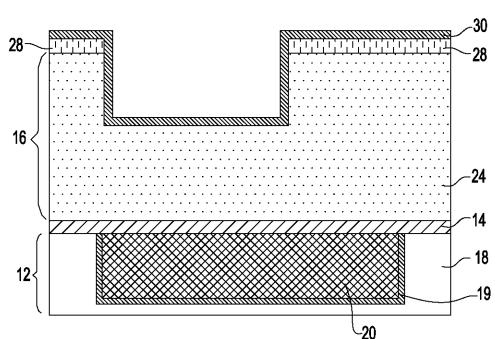

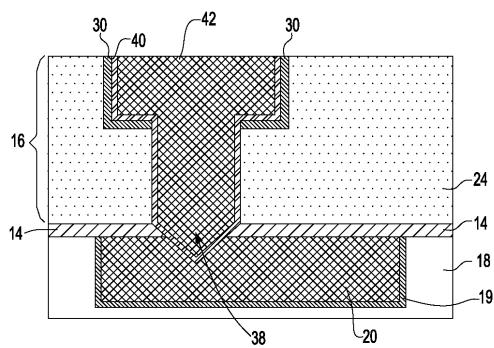

【図14】ビア開口部及びライン開口部の両方を相互接続導電性材料で充填し、平坦化し

50

た後の、図13の構造体を示す図形的表示（断面図による）である。

【発明を実施するための形態】

【0018】

本発明は、ガウジングされた（掘られた）ビア構造部（すなわち、固定されたビア底部（anchored via bottom））を含む相互接続構造体、及びその製造方法を提供するものであり、ここで以下の議論及び本出願に添付の図面を参照することによってより詳細に説明される。本明細書で以下に詳細に言及される本出願の図面は、例示のために提供されるものであり、従って、一定の縮尺では描かれていない。

【0019】

以下の説明において、本発明の完全な理解を提供するために、特定の構造体、構成要素、材料、寸法、処理ステップ及び技術のような多数の具体的な詳細が説明される。しかしながら、これらの具体的な詳細なしで本発明を実施できることが当業者には理解されるであろう。他の例において、本発明を曖昧にするのを避けるために、周知の構造体又は処理ステップは詳細には説明されない。

【0020】

層、領域、又は基板のような要素が、別の要素「上に（on）」又は「の上に（over）」あるものとして言及されるとき、該要素が他の要素の直接上にあってもよく、又は介在する要素が存在してもよいことが理解されるであろう。対照的に、要素が別の要素の「直接上に（directly on）」又は「直接上方に（directly over）」あるものとして言及されるとき、介在する要素は存在しない。要素が別の要素に「接続する（connect）」又は「結合する（couple）」ものとして言及されるとき、該要素が他の要素に直接接続しても又は結合してもよく、或いは、介在する要素が存在してもよいことが理解されるであろう。対照的に、要素が別の要素に「直接接続する（directly connect）」又は「直接結合する（directly couple）」ものとして言及されるとき、介在する要素は存在しない。

【0021】

本発明のプロセス・フローは、図6に示される初期相互接続構造体10を準備することで開始する。具体的には、図6に示される初期相互接続構造体10は、誘電体キャッピング層14によって分離される下部相互接続レベル12及び上部相互接続レベル16を含む多重レベル相互接続部を含む。半導体基板（図示せず）の上方に配置することができ、1つ又は複数の半導体デバイスを含む下部相互接続レベル12は、バリア層によって第1の誘電体層18から分離される少なくとも1つの導電性構造部（すなわち、導電性領域）20を有する第1の誘電体材料18を含む。上部相互接続レベル16は、少なくとも1つのライン開口部26が内部に配置された第2の誘電体材料24を含む。示されるように、少なくとも1つのライン開口部26は、第2の誘電体材料内で停止し、下にある導電性構造部20の一部の上方に配置されている。上部相互接続レベル16の上には、パターン形成されたハーデマスク28がある。図6に示される構造体は単一のライン開口部26を示すが、本発明は、第2の誘電体材料24内に、第2の誘電体材料24内で停止し、下部相互接続レベル12内に含まれる他の導電性構造部の上に配置される任意の数のこうしたライン開口部を形成することも考慮する。

【0022】

図6に示される初期構造体10は、当業者には周知の従来技術を用いて作製される。例えば、初期相互接続構造体は、最初に第1の誘電体材料18を基板（図示せず）の表面に適用することによって形成することができる。基板は、図示されていないが、半導体材料、絶縁材料、導電性材料、又はそれらのいずれかの組み合わせを含むことができる。基板が半導体材料で構成される場合、Si、SiGe、SiGeC、SiC、Ge合金、GaAs、InAs、InP、及び他のII/VI族又はII/VI族化合物半導体のような任意の半導体を用いることができる。これらの列挙されたタイプの半導体材料に加えて、本発明は、半導体基板が、例えばSi/SiGe、Si/SiC、シリコン・オン・インシュレータ（SOI）、又はシリコンゲルマニウム・オン・インシュレータ（SGOI）のような層状半導体である場合も考慮する。

10

20

30

40

50

## 【0023】

基板が絶縁材料である場合、絶縁材料は、有機絶縁体、無機絶縁体、又は多層構造を含むそれらの組み合わせとすることができます。基板が導電性材料である場合、基板は、例えば、ポリSi、元素金属(elemental metal)、元素金属の合金、金属シリサイド、金属窒化物、又は多層構造を含むそれらの組み合わせを含むことができる。基板が半導体材料を含む場合、例えば、相補型金属酸化膜半導体(CMOS)デバイスのような1つ又は複数の半導体デバイスをその上に製造することができる。

## 【0024】

下部相互接続レベル12の第1の誘電体材料18は、無機誘電体又は有機誘電体を含むどのような層間誘電体又は層内誘電体を含んでもよい。第1の誘電体材料18は、多孔性であっても、又は非多孔性であってもよく、本発明の幾つかの実施形態においては、多孔性誘電体は、2.8以下の誘電率を有することが非常に好ましい。第1の誘電体材料18として使用できる好適な誘電体の幾つかの例として、これらに限定されるものではないが、SiO<sub>2</sub>、シリセスキオキサン、Si、C、O及びH原子を含むCドープ酸化物(すなわち、オルガノシリケート)、熱硬化性ポリアリーレンエーテル、又はそれらの多層構造が挙げられる。「ポリアリーレン」という用語は、本出願においては、結合、縮合環、又は、例えば酸素、硫黄、スルホン、スルホキシド、カルボニルなどのような不活性結合基によって互いに結合された、アリール部分又は不活性置換されたアリール部分を示すために使用される。

10

## 【0025】

第1の誘電体材料18は、典型的には約4.0以下の誘電率を有し、約2.8以下の誘電率がさらにより典型的である。これらの誘電体は、一般に、誘電率が4.0より高い誘電体材料に比べて、寄生クロストークが低い。第1の誘電体材料18の厚さは、使用される誘電体材料、及び下部相互接続レベル12内の誘電体の正確な数に応じて変わり得る。典型的には、通常の相互接続構造体に関して、第1の誘電体材料18は、200nmから450nmまでの厚さを有する。

20

## 【0026】

下部相互接続レベル12はまた、第1の誘電体材料18内に埋め込まれた(すなわち、内部に配置された)少なくとも1つの導電性構造部20も有する。導電性構造部20は、バリア層19によって第1の誘電体材料18から分離される導電性材料を含む。導電性構造部20は、リソグラフィを行ない(すなわち、フォトレジストを第1の誘電体材料18の表面に塗布し、そのフォトレジストを所望の放射パターンに露光し、従来のレジスト現像剤を用いて露光されたレジストを現像する)、第1の誘電体材料18内に開口部をエッチング(乾式エッチング又は湿式エッチング)し、そのエッチングされた領域をバリア層19で、次いで導電性材料で充填して、導電性領域を形成することによって形成される。バリア層19は、Ta、TaN、Ti、TiN、Ru、RuN、W、WN、又は導電性材料がバリア層を通じて拡散するのを防止するためのバリアとして作用できる他のいずれかの材料を含むことができ、例えば、原子層堆積(ALD)、化学気相堆積(CVD)、プラズマ強化化学気相堆積(PECVD)、物理気相堆積(PVD)、スパッタリング、化学溶液堆積、又はめっきのような堆積プロセスによって形成される。

30

## 【0027】

バリア層19の厚さは、堆積プロセスの正確な手段、並びに使用される材料に応じて変わり得る。典型的には、バリア層19は、4nmから40nmまでの厚さを有し、7nmから20nmまでの厚さがより典型的である。

40

## 【0028】

バリア層19の形成に続いて、第1の誘電体材料18内の開口部の残りの領域が導電性材料で充填され、導電性構造部20を形成する。導電性構造部20を形成するに使用される導電性材料は、例えば、ポリSi、導電性金属、少なくとも1つの導電性金属を含む合金、導電性金属シリサイド、又はそれらの組み合わせを含む。導電性構造部20を形成するに使用される導電性材料は、Cu、W、又はAlのような導電性金属であることが

50

好ましく、本発明においては、Cu又はCu合金(A1Cuのような)が非常に好ましい。これらに限定されるものではないが、CVD、PECVD、スパッタリング、化学溶液堆積、又はめっきを含む従来の堆積プロセスを用いて、第1の誘電体材料18内の残りの開口部の中に導電性材料が充填される。これらの堆積の後、例えば、化学機械研磨(CMP)のような従来の平坦化プロセスを用いて、バリア層19及び導電性構造部20のそれぞれが第1の誘電体材料18の上面と実質的に同一平面である上面を有する構造体を提供することができる。

## 【0029】

少なくとも1つの導電性構造部20を形成した後、例えば、CVD、PECVD、化学溶液堆積、又は蒸着のような従来の堆積プロセスを用いて、下部相互接続レベル12の表面上にプランケット誘電体キャッピング層14が形成される。この誘電体キャッピング層14は、例えば、SiC、Si<sub>4</sub>NH<sub>3</sub>、SiO<sub>2</sub>、炭素ドープ酸化物、窒素及び水素ドープ炭化シリコンSiC(N, H)、又はそれらの多層構造のような、任意の好適な誘電体キャッピング材料を含む。誘電体キャッピング層14の厚さは、これを形成するのに用いられる技術並びに層の材料構成に応じて変わり得る。典型的には、誘電体キャッピング層14は、15nmから55nmまでの厚さを有し、25nmから45nmまでの厚さがより典型的である。

10

## 【0030】

次に、第2の誘電体材料24を誘電体キャッピング層14の上部露出面に塗布することによって、上部相互接続レベル16が形成される。第2の誘電体材料24は、下部相互接続レベル12の第1の誘電体材料18のものと同じ又は異なる誘電体材料、好ましくは同じ誘電体材料を含むことができる。第1の誘電体材料18に関する処理技術及び厚さの範囲は、第2の誘電体材料24にも適用可能である。第2の誘電体材料24はまた、2つの異なる誘電体材料を含むこともでき、すなわち、最初に1つの誘電体材料を堆積させ、続いて異なる誘電体材料を堆積させることができる。本発明の一実施形態において、第2の誘電体材料24は、2つの異なる低k誘電体材料を含み、従って、上部相互接続レベル16は、多孔性誘電体材料内に埋め込まれた、後で充填される導電性充填ラインと、高密度の(すなわち、非多孔性の)誘電体材料内に埋め込まれた、後で充填されるビアとを有するハイブリッド構造体を有する。このような実施形態において、多孔性低k誘電体は、約2.8以下の誘電率を有し、高密度低k誘電体は、約4.0以下の誘電率を有する。

20

## 【0031】

次に、最初に第2の誘電体材料24の上面の上にプランケット・ハードマスク材料を形成することによって、第2の誘電体材料24内に少なくとも1つのライン開口部26が形成される。プランケット・ハードマスク材料は、酸化物、窒化物、酸窒化物、又はそれらの多層構造を含む任意の組み合わせを含む。典型的には、ハードマスク材料は、SiO<sub>2</sub>のような酸化物、又はSi<sub>3</sub>N<sub>4</sub>のような窒化物である。プランケット・ハードマスク材料は、例えば、CVD、PECVD、化学溶液堆積、又は蒸着のような従来の堆積プロセスを用いて形成される。堆積されたままのハードマスク材料の厚さは、形成されるハードマスク材料のタイプ、ハードマスク材料を構成する層の数、及びこれを形成するのに用いられる堆積技術に応じて変わり得る。典型的には、堆積されたままのハードマスク材料は、約10nmから約80nmまでの厚さを有し、約20nmから約60nmまでの厚さがさらにより典型的である。

30

## 【0032】

ハードマスク材料のプランケット層を形成した後、例えば、CVD、PECVD、スピノン・コーティング、化学溶液堆積、又は蒸着のような従来の堆積プロセスを用いて、ハードマスク材料の上にフォトレジスト(図示せず)が形成される。フォトレジストは、ポジティブ・トーン材料、ネガティブ・トーン材料、又はそれらのハイブリッド材料とすることができる、それらの各々が当業者には周知のものである。次いで、フォトレジストを放射パターンに露光し、従来のレジスト現像剤を用いて露光されたレジストを現像することを含むリソグラフィ・プロセスが、フォトレジストに施される。リソグラフィ・ステップ

40

50

は、ハードマスク材料の上に、ライン開口部 26 の幅を定めるパターン形成されたフォトレジストを提供する。

【0033】

パターン形成されたフォトレジストを提供した後、1つ又は複数のエッチング・プロセスを用いて、ハードマスク材料内に、次いで引き続き第2の誘電体材料24内に、ライン・パターンが転写される。ハードマスク内にライン・パターンを転写し、パターン形成されたハードマスク28を形成した直後、従来の剥離プロセスを用いて、パターン形成されたフォトレジストを剥離することができる。代替的に、最初にライン・パターンをハードマスク内に形成してパターン形成されたハードマスク28を形成し、次に、第2の誘電体材料24内に転写した後に、パターン形成されたフォトレジストを剥離することもできる。ライン・パターンを転写するのに用いられるエッチングは、乾式エッチング・プロセス、湿式化学エッチング・プロセス、又はそれらの組み合わせを含むことができる。ここで用いられる「乾式エッチング」という用語は、反応性イオン・エッチング、イオン・ビーム・エッチング、プラズマ・エッチング、又はレーザ・アブレーションのようなエッチング技術を示すために用いる。

10

【0034】

図6に示される初期相互接続構造体10を形成した後、次いで、初期相互接続構造体の露出面の全ての上にトレンチ拡散バリア30を形成し、例えば図7に示されるような構造体を提供する。本発明の幾つかの実施形態においては、ライン開口部26内へのトレンチ拡散バリア30の形成は省略され、プロセスは、図8に示される次のステップに続く。こうした実施形態は可能であるが、ライン開口部26内にトレンチ拡散バリアを形成することが好みしい。

20

【0035】

示されるように、トレンチ拡散バリア30は、パターン形成されたハードマスク28の露出面、及び、ライン開口部26内の第2の誘電体材料24の露出面（例えば、共通の底壁まで延びる側壁）を覆う。本発明によれば、トレンチ拡散バリア30は、その厚さが典型的には0.5nmから20nmまでの範囲内にあり、1nmから10nmまでの厚さがよりいっそう典型的である、薄い層である。トレンチ拡散バリア30は、これらに限定されるものではないが、CVD、PVD、ALD、又はスピノン・コーティングを含む従来の堆積プロセスを用いて形成される。トレンチ拡散バリア30は、例えば、TaN、Ta、Ti、TiN、RuTa、RuTaN、W、Ru、Co、Rh、又はIr、或いはそれらのいずれかの組み合わせを含む、金属拡散に対して耐性があるいずれかの材料を含む層又は材料スタックを含む。

30

【0036】

次に、図8に示されるように、ライン開口部26を充填し、パターン形成されたマスク28の表面上に位置するトレンチ拡散バリア30の上方に延びるように、平坦化層32が堆積される。トレンチ誘電体30が使用されない実施形態においては、平坦化層32は、第2の誘電体材料24の露出した壁部分、及び、パターン形成されたハードマスク28の上面に直接接触する。

40

【0037】

平坦化層32は、例えば、CVD、PECVD、スピノン・コーティング、蒸着、又は化学溶液堆積を含む従来の堆積プロセスを用いて堆積される。平坦化材料は、従来の反射防止コーティング材料又はスパンガラス材料を含む。

【0038】

さらに図8を参照すると、平坦化層32を形成した後、次いで、平坦化層32の表面上に、低温酸化物などの酸化物含有層34が形成される。酸化物含有層34は、これらに限定されるものではないが、堆積温度が500より低いCVD及びPECVDを含むいずれかの従来の堆積プロセスを用いて形成される。酸化物含有層34は、典型的には5nmから100nmまでの厚さを有し、20nmから50nmまでの厚さがより典型的である。

50

## 【0039】

次に、堆積及びリソグラフィによって、酸化物含有層34の上面に、ビア開口部パターンを含むパターン形成されたフォトレジスト(具体的には示されない)が形成される。次いで、ビア開口部のパターンを、パターン形成されたフォトレジストから少なくとも酸化物含有層34内に転写するエッチング・ステップが行なわれる。ビア開口部パターンの転写は、ライン開口部26を第2の誘電体材料24内に形成する際の上述したエッチング・ステップのうちの1つを用いて行なわれる。ビア・パターンを酸化物含有層34内に転写した後、例えばアッシング(ashing)のような従来のレジスト剥離プロセスを用いて、パターン形成されたフォトレジストが剥離される。これらのステップを行なった後に形成される結果として得られる構造体が、例えば、図9に示される。図9において、パターン形成された酸化物含有層は、参考番号34'で表され、初期ビア開口部は、参考番号36で表される。

10

## 【0040】

次に、図10に示されるように、初期ビア開口部36が、平坦化層32の一部、存在する場合はトレンチ拡散バリア30の一部、及び下にある第2の誘電体材料24の一部を通じて下方に延び、誘電体キャッピング層14の表面の上で停止し、拡張されたビア開口部36'を形成する。幾つかの実施形態においては、エッチング・ステップは、誘電体キャッピング層14の一部をパンチスルーする(punch through)、すなわち除去し、導電性構造部20の表面の上で停止することができる。初期ビア開口部36の延長は、図10に示される構造体を形成できる1つ又は複数のエッチング・プロセスを含む。示されるように、少なくとも残りの平坦化層32によって保護されるライン開口部26は、拡張されたビア開口部36'の上方に配置され、これに接続される。1つ又は複数のエッチング・ステップ中、図10に示されるように、パターン形成された酸化物含有層34'も除去されることが認められる。

20

## 【0041】

次に、最初に誘電体キャッピング層14を開口するかどうかに関係なく、図10に示される構造体にArスパッタリング・プロセスを施し、このArスパッタリング・プロセスにより、前もって除去されていない場合には、拡張されたビア開口部36'の底部から誘電体キャッピング層の一部を除去し、下にある導電性構造部20をパンチスルーして、導電性構造部20内にガウジング構造部(すなわち、アンカー領域)38を生成する。Arスパッタリングの後に結果として得られる構造体が、例えば、図11に示される。第2の誘電体材料24は、少なくとも残りの平坦化層32、存在する場合にはトレンチ拡散バリア30及びパターン形成されたハードマスク層28によって保護されているので、このプロセス中に損傷を受けない。

30

## 【0042】

ガウジング構造部38を形成するのに用いられるArスパッタリング・プロセスは、こうした構造部を形成するために相互接続技術において典型的に用いられる任意の従来のArスパッタリング・プロセスを含む。例証として、Arスパッタリングは、次の限定されない条件、すなわち20sccmのArガス流、25°の温度、400KHz及び750Wの上部電極バイアス、13.6MHz及び400Wのテーブルバイアス、並びに0.6mtorrのプロセス圧力を用いて行なうことができる。説明のためにArが示されているが、スパッタリング・プロセスのために、He、Ne、Xe、N<sub>2</sub>、H<sub>2</sub>、NH<sub>3</sub>、N<sub>2</sub>H<sub>2</sub>、又はそれらの混合物のような他の任意のガスを用いることもできる。

40

## 【0043】

本発明の幾つかの実施形態(具体的には示されない)においては、導電性構造部20の少なくともガウジングされた表面上に金属界面層を形成することができる。存在する場合、金属界面層は、例えば、CVD、PECVD、化学溶液堆積、蒸着、有機金属堆積、ALD、スパッタリング、PVD、又はめっき(無電解又は電解)を含む、任意の従来の堆積プロセスを用いて形成される。金属界面層の厚さは、使用される正確な金属界面材料、及び、金属界面層を形成するのに用いられる堆積技術に応じて変わり得る。典型的には、

50

金属界面層は、0.5 nmから40 nmまでの厚さを有し、1 nmから10 nmまでの厚さがさらにより典型的である。金属界面層は、例えば、Co、TaN、Ta、Ti、TiN、Ru、Ir、Au、Rh、Pt、Pd、又はAgなどの金属バリア材料を含む。こうした材料の合金も考慮される。

【0044】

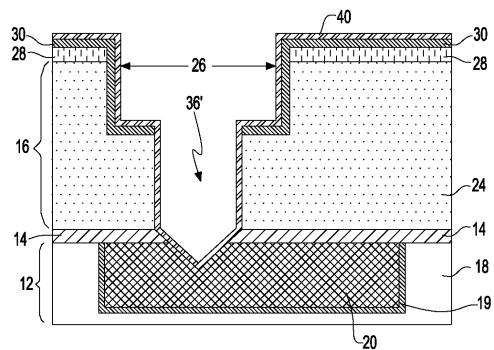

図12は、残りの平坦化層32がライン開口部26内から剥離された後の、図11の構造体を示す。残りの平坦化層32の剥離は、化学湿式エッチング・プロセス、又は構造体から平坦化材料を選択的に除去する化学アッシング・プロセスのいずれかを用いて行なわれる。

【0045】

本発明の幾つかの実施形態においては、酸化物又はエッチング残留物(図示せず)が、ガウジング構造部38内に残ることがある。このような場合、酸化物又はエッチング残留物は、化学湿式エッチング・プロセス及び/又は少量のAr衝撃(bombardment)を含むことができる表面洗浄プロセスを用いて、ガウジング構造部38から除去することができる。Ar衝撃の条件は、ガウジング構造部38を形成するのに用いられるものほど厳しくないので、この場合、損傷は生じない。典型的には、この場合に用いられる表面洗浄だけのためのプロセス時間は、従来技術において用いられる、ガウジング構造部を生成するための10秒以上に比べて、5秒未満である。例証として、Arスパッタリングは、次の限20定されない条件、すなわち20 sccmのArガス流、25°の温度、400 KHz及び400 Wの上部電極バイアス、13.6 MHz及び200 Wのテーブルバイアス、及び0.6 mtorrのプロセス圧力を用いて行なうことができる。説明のためにArが示されたが、スパッタリング・プロセスのために、He、Ne、Xe、N<sub>2</sub>、H<sub>2</sub>、NH<sub>3</sub>、N<sub>2</sub>H<sub>2</sub>、又はそれらの混合物のような任意の他のガスを用いることもできる。

【0046】

本発明の幾つかの実施形態において、エッチング残留物が、少なくとも1つのライン開口部26及び少なくとも拡張されたビア開口部36'から除去される。1つの実施形態においては、O<sub>2</sub>、H<sub>2</sub>、N<sub>2</sub>、CO、CO<sub>2</sub>、又はNH<sub>3</sub>の少なくとも1つ又は組み合わせを含むプラズマ・エッチングが用いられる。別の実施形態においては、エッチング残留物は、HF、HCl、H<sub>2</sub>SO<sub>4</sub>、又はHNO<sub>3</sub>の少なくとも1つ又は組み合わせを含む湿式洗浄によって除去される。

【0047】

本発明の方法のこの時点で、組み合わされたトレーニチ及びビア拡散バリア40が、図12に示される構造体内に形成され、図13に示される構造体を提供する。示されるように、組み合わされたトレーニチ及びビア拡散バリア40は、ライン開口部26及拡張されたビア開口部36'の両方の中に存在し、一方、存在する場合、トレーニチ拡散バリア30は、ライン開口部26内にのみ存在する。トレーニチ拡散バリア30が存在するとき、組み合わされたトレーニチ及びビア拡散バリア40は、ライン開口部内のトレーニチ拡散バリア30の上、拡張されたビア開口部36'内の第2の誘電体材料24の露出された壁面の上、及び導電性構造部20のガウジングされた面の上に配置される。

【0048】

組み合わされたトレーニチ及びビア拡散バリア40は、導電性材料がそこを通って拡散するのを防止するためのバリアとして作用できるいずれかの材料を含む。例証として、組み合わされたトレーニチ及びビア拡散バリア40は、TaN、Ta、Ti、TiN、RuTa、RuTaN、W、Ru、Co、Rh、又はIr、或いはそれらの任意の組み合わせの層又は材料スタックを含む。組み合わされたトレーニチ及びビア拡散バリア層40は、トレーニチ拡散バリア30とは異なる層又は材料スタックを表すことが認められる。

【0049】

組み合わされたトレーニチ及びビア拡散バリア40は、ライン開口部及び拡張されたビア開口部の両方の中に存在する連続的な層であり、例えば、原子層堆積(ALD)、化学気相堆積(CVD)、プラズマ強化化学気相堆積(PECVD)、物理気相堆積(PVD)

10

20

30

40

50

、スパッタリング、化学溶液堆積、又はめっきなどの堆積プロセスを用いて形成される。

【0050】

組み合わされたトレーニチ及びビア拡散バリア40の厚さは、バリア内の材料層の数、拡散バリアを形成するのに使用される技術、並びに拡散バリア自体の材料に応じて変わり得る。典型的には、組み合わされたトレーニチ及びビア拡散バリア40は、4nmから40nmまでの厚さを有し、7nmから20nmまでの厚さがさらにより典型的である。

【0051】

本発明の幾つかの実施形態においては、ここで、図13に示される構造体内にめっきシード層(図示せず)が形成される。使用される場合、このめっきシード層は、Cu、或いは元素周期表のVIIIA族からの金属又は金属合金から成る。めっきシード層のための好適なVIIIA族元素の例として、これらに限定されるものではないが、Ru、TaRu、Ir、Rh、Pt、Pd及びそれらの合金が挙げられる。幾つかの実施形態においては、めっきシード層としてCu、Ru、Ir、又はRhを用いることが好ましい。

10

【0052】

めっきシード層は、例えば、化学気相堆積(CVD)、プラズマ強化化学気相堆積(PECVD)、原子層堆積(ALD)、めっき、スパッタリング、及び物理気相堆積(PVP)を含む従来の堆積プロセスによって形成される。めっきシード層の厚さは、例えば、めっきシード層の組成材料、及びめっきシード層を形成するのに使用された技術を含む多数の要因に応じて変わり得る。典型的には、めっきシード層は、約0.5nmから約10nmまでの厚さを有し、6nm未満の厚さがさらにより典型的である。

20

【0053】

次に、図13に示される構造体は、めっきシード層の有無に関係なく、相互接続導電性材料42で充填され、平坦化されて、図14に示される平坦化された構造体を提供する。示されるように、相互接続導電性材料は、拡張されたビア開口部36'、ライン開口部26、並びにガウジング構造部38を充填する。相互接続導電性材料42は、導電性構造部20のものと同じ又は異なる導電性材料、好ましくは同じ導電性材料を含むことができる。Cu、Al、W、又はそれらの合金が使用されることが好ましく、Cu又はAlCuが最も好ましい。相互接続導電性材料42は、導電性構造部20を形成する際に上述されたものと同じ堆積プロセスを用いて形成され、導電性材料の堆積に続いて、構造体に平坦化が施される。化学機械研磨及び/又は研削を含む平坦化プロセスにより、上部相互接続レベル16の第2の誘電体材料24の上に配置された、例えば組み合わされたトレーニチ及びビア拡散バリア40、トレーニチ拡散バリア30、及びパターン形成されたハードマスク28などの種々の材料が除去される。

30

【0054】

本出願の方法は、図14に示されるレベルの上に付加的な相互接続レベルを形成するのにも適用可能である。種々の相互接続レベルの各々が、前述のガウジング構造部を含む。

【0055】

上述の統合処理スキームのために、ガウジング構造部38の形成中、第2の誘電体材料24内に損傷領域は形成されない。

40

【0056】

本発明をその好ましい実施形態について特に示し、説明したが、当業者であれば、本発明の精神及び範囲から逸脱することなく、形態及び細部について前述及び他の変更をなし得ることを理解するであろう。従って、本発明は、説明され図示された通りの正確な形態及び細部に限定されるものではなく、添付の特許請求の範囲内であることが意図される。

【符号の説明】

【0057】

10：初期相互接続構造体

12：下部相互接続レベル

14：誘電体キャッピング層

16：上部相互接続レベル

50

- 1 8 : 第 1 の誘電体材料

1 9 : バリア層

2 0 : 導電性構造部

2 4 : 第 2 の誘電体材料

2 6 : ライン開口部

2 8 : パターン形成されたハードマスク

3 0 : トレンチ拡散バリア

3 2 : 平坦化層

3 4 : 酸化物含有層

3 4' : パターン形成された酸化物含有層

3 6 : 初期ビア開口部

3 6' : 拡張されたビア開口部

3 8 : ガウジング構造部 (アンカー領域)

4 0 : 組み合わされたトレンチ及びビア拡散バリア

4 2 : 相互接続導電性材料

10

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図 1 3】

【図 1 4】

---

フロントページの続き

(72)発明者 チーチャオ・ヤン

アメリカ合衆国 12203 ニューヨーク州 アルバニー フラー・ロード 257

(72)発明者 テオドラス・エドワーダス・スタンダート

アメリカ合衆国 12203 ニューヨーク州 アルバニー フラー・ロード 257

(72)発明者 ダニエル・シー・エデルスタン

アメリカ合衆国 10598 ニューヨーク州 ヨークタウン・ハイツ ルート134 キッチャ

ワンロード 1101

F ターム(参考) 5F033 GG01 GG02 GG03 HH07 HH08 HH09 HH11 HH13 HH14 HH15

HH18 HH19 HH21 HH31 HH32 HH33 JJ01 JJ07 JJ08 JJ09

JJ11 JJ12 JJ13 JJ14 JJ15 JJ18 JJ19 JJ21 JJ31 JJ32

JJ33 KK04 KK07 KK08 KK11 KK12 KK14 KK15 KK18 KK19

KK21 KK32 KK33 KK34 MM01 MM02 MM08 MM12 MM13 NN06

NN07 NN13 NN30 PP06 PP11 PP12 PP14 PP15 PP26 PP27

PP28 PP33 QQ04 QQ08 QQ09 QQ11 QQ12 QQ13 QQ14 QQ16

QQ19 QQ21 QQ22 QQ25 QQ28 QQ37 QQ48 QQ92 QQ93 QQ94

RR01 RR04 RR06 RR21 RR23 RR29 SS10 SS11 SS15 SS21

TT01 WW09 XX00 XX02 XX24 XX28