(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-109889

(P2012-109889A)

(43) 公開日 平成24年6月7日(2012.6.7)

(51) Int.Cl.

H04L 1/00 (2006.01)

H03M 13/35 (2006.01)

F 1

H04L 1/00

H03M 13/35

H04L 1/00B

E

テーマコード(参考)

5 J 0 6 5

5 K 0 1 4

審査請求 未請求 請求項の数 15 O L (全 20 頁)

(21) 出願番号

(22) 出願日特願2010-258569 (P2010-258569)

平成22年11月19日 (2010.11.19)(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 新橋 龍男

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 舟本 一久

東京都港区港南1丁目7番1号 ソニー株

式会社内

最終頁に続く

(54) 【発明の名称】送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システム

## (57) 【要約】

【課題】装置内でのデータの送受信を効率的に行うことができるようとする。

【解決手段】送信側ブロック11と受信側ブロック12は、デジタルカメラ、携帯電話機、パソコンなどの同じ装置内に設けられるブロックであり、1本の伝送路を介して接続される。データの送信時、送信側ブロック11においては、送信対象のデータに基づいて誤り訂正符号の計算が行われ、送信データに付加されることによって誤り訂正符号化が行われる。誤り訂正符号が付加された送信データを受信した受信側ブロック12においては、伝送路上において生じた送信データの誤りが、送信データに付加されている誤り訂正符号を用いて訂正される。本発明は、複数のLSI間でデータの送受信を行う装置に適用することができる。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

データ長が可変である誤り訂正符号のデータ長を設定する設定手段と、

送信対象のデータを情報語として、前記設定手段により設定されたデータ長の前記誤り

訂正符号を計算する誤り訂正符号計算手段と、

前記誤り訂正符号計算手段による計算によって求められた前記誤り訂正符号を前記送信

対象のデータに付加して得られた符号語のデータである符号化データを、同じ装置内にある

受信装置に送信する送信手段と

を備える送信装置。

## 【請求項 2】

前記設定手段は、前記送信装置を構成する回路の入力端子に外部から入力された信号に

従って前記誤り訂正符号のデータ長を設定する

請求項 1 に記載の送信装置。

## 【請求項 3】

前記設定手段は、外部との通信用のバスを介して外部から入力された信号に従って前記

誤り訂正符号のデータ長を設定する

請求項 1 に記載の送信装置。

## 【請求項 4】

前記設定手段はプロセッサであり、所定のプログラムに従って前記誤り訂正符号のデータ

長を設定する

請求項 1 に記載の送信装置。

## 【請求項 5】

前記設定手段はプロセッサであり、前記受信装置のプロセッサから送信されてきた情報

に基づいて、前記送信対象のデータの誤り訂正の状況に基づいて前記受信装置のプロセッ

サにより決定された前記誤り訂正符号のデータ長を設定する

請求項 1 に記載の送信装置。

## 【請求項 6】

データ長が可変である誤り訂正符号のデータ長を設定し、

送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、

計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号

語のデータである符号化データを、同じ装置内にある受信装置に送信する

ステップを含む送信方法。

## 【請求項 7】

データ長が可変である誤り訂正符号のデータ長を設定し、

送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、

計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号

語のデータである符号化データを、同じ装置内にある受信装置に送信する

ステップを含む処理をコンピュータに実行させるプログラム。

## 【請求項 8】

データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語と

して、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正

符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送

信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信する受信

手段と、

前記誤り訂正符号のデータ長を設定する設定手段と、

前記符号化データに含まれる、前記設定手段により設定されたデータ長の前記誤り訂正

符号に基づいて前記送信対象のデータの誤り訂正を行う誤り訂正手段と、

前記誤り訂正後の前記送信対象のデータの処理を行う処理手段と

を備える受信装置。

## 【請求項 9】

10

20

30

40

50

前記設定手段は、前記受信装置を構成する回路の入力端子に外部から入力された信号に従って前記誤り訂正符号のデータ長を設定する

請求項 8 に記載の受信装置。

【請求項 1 0】

前記設定手段は、外部との通信用のバスを介して外部から入力された信号に従って前記誤り訂正符号のデータ長を設定する

請求項 8 に記載の受信装置。

【請求項 1 1】

前記設定手段はプロセッサであり、所定のプログラムに従って前記誤り訂正符号のデータ長を設定する

10

請求項 8 に記載の受信装置。

【請求項 1 2】

前記設定手段はプロセッサであり、前記誤り訂正手段による前記誤り訂正の状況に基づいて前記誤り訂正符号のデータ長を決定し、決定したデータ長を表す情報を、前記送信装置において前記誤り訂正符号のデータ長を設定する、前記送信装置のプロセッサに送信する

請求項 8 に記載の受信装置。

【請求項 1 3】

データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信し、

20

前記誤り訂正符号のデータ長を設定し、

前記符号化データに含まれる、設定したデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行い、

前記誤り訂正後の前記送信対象のデータの処理を行う

ステップを含む受信方法。

【請求項 1 4】

データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信し、

30

前記誤り訂正符号のデータ長を設定し、

前記符号化データに含まれる、設定したデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行い、

前記誤り訂正後の前記送信対象のデータの処理を行う

ステップを含む処理をコンピュータに実行させるプログラム。

【請求項 1 5】

送信装置と受信装置とを含む伝送システムにおいて、

40

前記送信装置は、

データ長が可変である誤り訂正符号のデータ長を設定する設定手段と、

送信対象のデータを情報語として、前記設定手段により設定されたデータ長の前記誤り訂正符号を計算する誤り訂正符号計算手段と、

前記誤り訂正符号計算手段による計算によって求められた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを前記受信装置に送信する送信手段と

を備え、

前記受信装置は、

前記符号化データを受信する受信手段と、

50

前記誤り訂正符号のデータ長を設定する設定手段と、

前記符号化データに含まれる、前記設定手段により設定されたデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行う誤り訂正手段と、

前記誤り訂正後の前記送信対象のデータの処理を行う処理手段と

を備える

伝送システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システムに関し、特に、装置内でのデータの送受信を効率的に行うことができるようとした送信装置、送信方法、受信装置、受信方法、プログラム、および伝送システムに関する。 10

【背景技術】

【0002】

情報の大容量化に伴い、信号処理LSI(Large Scale Integrated Circuit)間のインターフェースの伝送速度の高速化が必要になってきている。

【0003】

この要求に応えるため、信号処理の多並列化、インターフェースのクロック周波数の向上、信号の低電圧化などの手法が採用されているが、これらの手法によれば、ノイズ耐性が劣化し、データを正しく伝送することが難しくなる。

【0004】

モバイル機器向けの信号処理LSI間のインターフェースなどの消費電力を抑えることが要求されるインターフェースにおいても、伝送速度の高速化はそれほど要求されないものの、低電圧化が進められており、データを正しく伝送することが難しい。 20

【0005】

このような問題を解決するため、従来、CDR(Clock Data Recovery)回路やイコライザの高性能化などの伝送チャネルの電気的な性能改善が行われ、また、ノイズによって生じた誤りを受信側で検出する誤り検出符号も用いられている。誤りを検出した受信側のLSIが、送信側のLSIに対してデータの再送を要求し、データの送受信を再度行うことによってエラー対策が確保されるようになされている。

【先行技術文献】 30

【非特許文献】

【0006】

【非特許文献1】Serial ATA: High Speed Serialized AT Attachment Revision 1.0a

7-January-2003

【発明の概要】

【発明が解決しようとする課題】

【0007】

信号処理LSI間のインターフェースに要求される伝送容量が加速度的に増大してきている。再送信を行う従来の方法は、比較的容量の大きいデータバッファを受信側のLSIに用意する必要があり、また、データが再送されてくるのを待っていては受信側のLSIにおける処理が時間的に間に合わないこともあって、現実的な実装方法ではなくなりつつある。 40

【0008】

本発明はこのような状況に鑑みてなされたものであり、装置内でのデータの送受信を効率的に行うことができるようとするものである。

【課題を解決するための手段】

【0009】

本発明の第1の側面の送信装置は、データ長が可変である誤り訂正符号のデータ長を設定する設定手段と、送信対象のデータを情報語として、前記設定手段により設定されたデータ長の前記誤り訂正符号を計算する誤り訂正符号計算手段と、前記誤り訂正符号計算手段による計算によって求められた前記誤り訂正符号を前記送信対象のデータに付加して得

られた符号語のデータである符号化データを、同じ装置内にある受信装置に送信する送信手段とを備える。

【0010】

前記設定手段には、前記送信装置を構成する回路の入力端子に外部から入力された信号に従って前記誤り訂正符号のデータ長を設定させることができる。

【0011】

前記設定手段には、外部との通信用のバスを介して外部から入力された信号に従って前記誤り訂正符号のデータ長を設定させることができる。

【0012】

前記設定手段はプロセッサであり、所定のプログラムに従って前記誤り訂正符号のデータ長を設定させることができる。

【0013】

前記設定手段はプロセッサであり、前記受信装置のプロセッサから送信されてきた情報に基づいて、前記送信対象のデータの誤り訂正の状況に基づいて前記受信装置のプロセッサにより決定された前記誤り訂正符号のデータ長を設定させることができる。

【0014】

本発明の第1の側面の送信方法は、データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを、同じ装置内にある受信装置に送信するステップを含む。

【0015】

本発明の第1の側面のプログラムは、データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを、同じ装置内にある受信装置に送信するステップを含む処理をコンピュータに実行させる。

【0016】

本発明の第2の側面の受信装置は、データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信する受信手段と、前記誤り訂正符号のデータ長を設定する設定手段と、前記符号化データに含まれる、前記設定手段により設定されたデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行う誤り訂正手段と、前記誤り訂正後の前記送信対象のデータの処理を行う処理手段とを備える。

【0017】

前記設定手段には、前記受信装置を構成する回路の入力端子に外部から入力された信号に従って前記誤り訂正符号のデータ長を設定させることができる。

【0018】

前記設定手段には、外部との通信用のバスを介して外部から入力された信号に従って前記誤り訂正符号のデータ長を設定させることができる。

【0019】

前記設定手段はプロセッサであり、所定のプログラムに従って前記誤り訂正符号のデータ長を設定させることができる。

【0020】

前記設定手段はプロセッサであり、前記誤り訂正手段による前記誤り訂正の状況に基づいて前記誤り訂正符号のデータ長を決定し、決定したデータ長を表す情報を、前記送信装置において前記誤り訂正符号のデータ長を設定する、前記送信装置のプロセッサに送信させることができる。

10

20

30

40

50

## 【0021】

本発明の第2の側面の受信方法は、データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信し、前記誤り訂正符号のデータ長を設定し、前記符号化データに含まれる、設定したデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行い、前記誤り訂正後の前記送信対象のデータの処理を行うステップを含む。

## 【0022】

本発明の第2の側面のプログラムは、データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データを受信し、前記誤り訂正符号のデータ長を設定し、前記符号化データに含まれる、設定したデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行い、前記誤り訂正後の前記送信対象のデータの処理を行うステップを含む処理をコンピュータに実行させる。

10

## 【0023】

本発明の第3の側面の伝送システムは、送信装置と受信装置とを含む伝送システムにおいて、前記送信装置は、データ長が可変である誤り訂正符号のデータ長を設定する設定手段と、送信対象のデータを情報語として、前記設定手段により設定されたデータ長の前記誤り訂正符号を計算する誤り訂正符号計算手段と、前記誤り訂正符号計算手段による計算によって求められた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを前記受信装置に送信する送信手段とを備え、前記受信装置は、前記符号化データを受信する受信手段と、前記誤り訂正符号のデータ長を設定する設定手段と、前記符号化データに含まれる、前記設定手段により設定されたデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正を行う誤り訂正手段と、前記誤り訂正後の前記送信対象のデータの処理を行う処理手段とを備える。

20

## 【0024】

本発明の第1の側面においては、データ長が可変である誤り訂正符号のデータ長が設定され、送信対象のデータを情報語として、設定されたデータ長の前記誤り訂正符号が計算される。また、計算によって求められた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データが、同じ装置内にある受信装置に送信される。

30

## 【0025】

本発明の第2の側面においては、データ長が可変である誤り訂正符号のデータ長を設定し、送信対象のデータを情報語として、設定したデータ長の前記誤り訂正符号を計算し、計算によって求めた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データを送信する同じ装置内に設けられる送信装置から送信された前記符号化データが受信される。また、前記誤り訂正符号のデータ長が設定され、前記符号化データに含まれる、設定されたデータ長の前記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正が行われ、前記誤り訂正後の前記送信対象のデータの処理が行われる。

40

## 【0026】

本発明の第3の側面においては、送信装置により、データ長が可変である誤り訂正符号のデータ長が設定され、送信対象のデータを情報語として、設定されたデータ長の前記誤り訂正符号が計算され、計算によって求められた前記誤り訂正符号を前記送信対象のデータに付加して得られた符号語のデータである符号化データが受信装置に送信される。また、受信装置により、前記送信装置から送信された前記符号化データが受信され、前記誤り訂正符号のデータ長が設定され、前記符号化データに含まれる、設定されたデータ長の前

50

記誤り訂正符号に基づいて前記送信対象のデータの誤り訂正が行われ、前記誤り訂正後の前記送信対象のデータの処理が行われる。

【発明の効果】

【0027】

本発明によれば、装置内でのデータの送受信を効率的に行うことができる。

【図面の簡単な説明】

【0028】

【図1】伝送システムの第1の構成例を示す図である。

【図2】送信データの並び替えの例を示す図である。

【図3】誤り訂正符号化の例を示す図である。

10

【図4】伝送フレームのフレーム構成を示す図である。

【図5】誤り訂正復号の例を示す図である。

【図6】送信側ブロックの送信処理について説明するフローチャートである。

【図7】受信側ブロックの受信処理について説明するフローチャートである。

【図8】送信側ブロックと受信側ブロックの構成の変形例を示す図である。

【図9】伝送システムの第2の構成例を示す図である。

【図10】伝送システムの第3の構成例を示す図である。

【図11】伝送システムの第4の構成例を示す図である。

【図12】伝送システムの第5の構成例を示す図である。

20

【図13】送信側ブロックのパリティ数設定処理について説明するフローチャートである

。

【図14】受信側ブロックのパリティ数設定処理について説明するフローチャートである

。

【図15】コンピュータの構成例を示す図である。

【発明を実施するための形態】

【0029】

<第1の実施の形態>

[ブロックの構成]

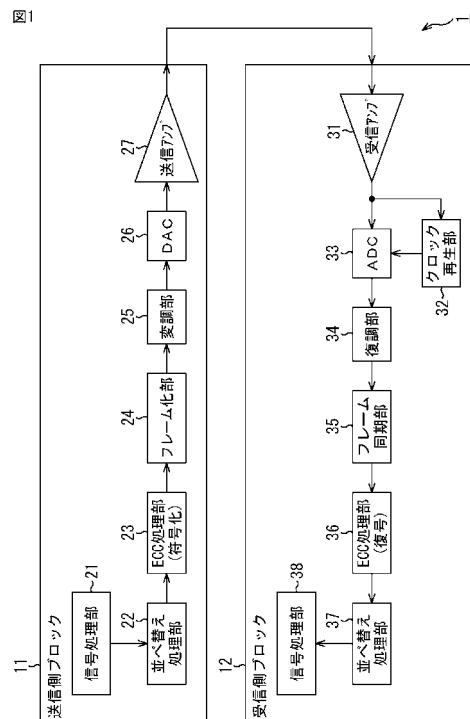

図1は、本発明の一実施形態に係る伝送システムの第1の構成例を示す図である。

【0030】

30

図1の伝送システム1は、送信側ブロック11と受信側ブロック12から構成される。送信側ブロック11と受信側ブロック12は、例えば、それぞれ異なるLSIにより、または同じLSIにより実現され、デジタルカメラ、携帯電話機、パソコンコンピュータなどの、情報を処理する同じ装置内に設けられる。図1の例においては、送信側ブロック11と受信側ブロック12は1本の伝送路を介して接続されている。送信側ブロック11と受信側ブロック12の間の伝送路は有線の伝送路であってもよいし、無線の伝送路であってもよい。

【0031】

送信側ブロック11は、信号処理部21、並べ替え処理部22、ECC処理部23、フレーム化部24、変調部25、DAC26、および送信アンプ27から構成される。

【0032】

信号処理部21は、各種の信号処理を行い、信号処理を行うことによって得られた画像データ、テキストデータ、オーディオデータなどの、送信対象のデータである送信データを並べ替え処理部22に出力する。

【0033】

送信データが送信側ブロック11の外部の回路から並べ替え処理部22に入力されるようにすることも可能である。例えば、CMOS(Complementary Metal Oxide Semiconductor)などの外部の撮像素子により撮像された画像を構成する画素データが、1画素のデータずつ順に送信データとして入力されるようにしてもよい。

【0034】

40

50

並べ替え処理部 2 2 は、信号処理部 2 1 から供給された送信データを取得し、取得した送信データの並び替えを行う。例えば、送信データが 12 ビットなどの所定の数のビットで 1 シンボルを構成するデータである場合、並べ替え処理部 2 2 においては、データの並び替えが行われることによって 8 ビット単位のデータに変換される。

【0035】

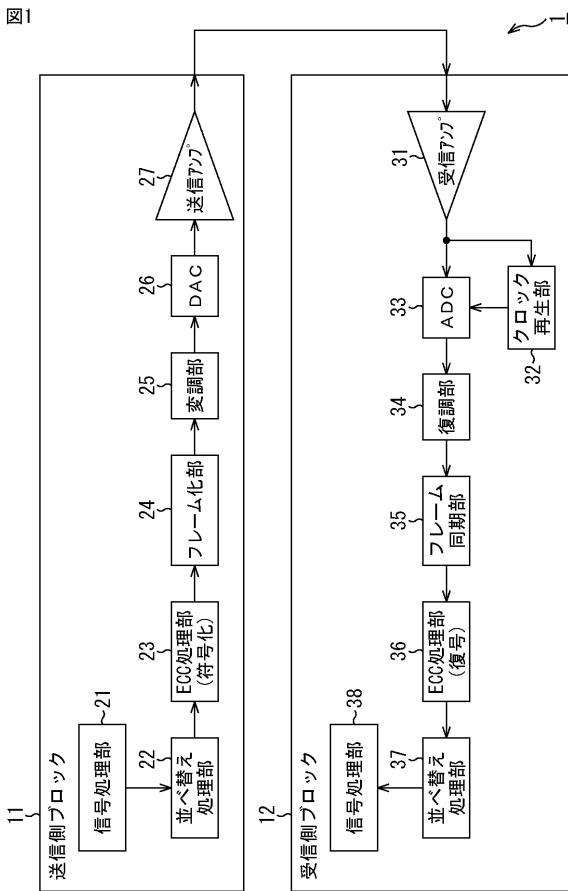

図 2 は、送信データの並び替えの例を示す図である。

【0036】

図 2 の左側に示す縦長の 4 つのブロックは、それぞれ 12 ビットのデータであるシンボル  $s_1$  乃至  $s_4$  を表す。各ブロックの縦方向の長さが 12 ビットを表す。

【0037】

例えば、シンボル  $s_1$  乃至  $s_4$  が送信データとして入力された場合、並べ替え処理部 2 2 においては、入力された順に 8 ビットずつ集められ、矢印の先に示すような 8 ビット単位のデータであるシンボル  $s_1$  乃至  $s_6$  に並び替えられる。

【0038】

シンボル  $s_1$  は、シンボル  $s_1$  の 1 ビット目から 8 ビット目までの 8 ビットにより構成される。シンボル  $s_2$  は、シンボル  $s_1$  の 9 ビット目から 12 ビット目までの 4 ビットと、シンボル  $s_2$  の 1 ビット目から 4 ビット目までの 4 ビットとの 8 ビットにより構成される。シンボル  $s_3$  は、シンボル  $s_2$  の 5 ビット目から 12 ビット目までの 8 ビットにより構成される。シンボル  $s_4$  は、シンボル  $s_3$  の 1 ビット目から 8 ビット目までの 8 ビットにより構成される。シンボル  $s_5$  は、シンボル  $s_3$  の 9 ビット目から 12 ビット目までの 4 ビットと、シンボル  $s_4$  の 1 ビット目から 4 ビット目までの 4 ビットとの 8 ビットにより構成される。シンボル  $s_6$  は、シンボル  $s_4$  の 5 ビット目から 12 ビット目までの 8 ビットにより構成される。

【0039】

送信データを構成する各シンボルが 12 ビット以外のビット数で表されることもある。並べ替え処理部 2 2 においては、送信データの各シンボルがどのようなビット数で表される場合であっても後段の処理部において同じ処理で伝送フレームを生成できるように、送信データを 8 ビット単位のデータに区切り直す処理が行われる。並べ替え処理部 2 2 は、並び替えを行うことによって得られた 8 ビット単位の送信データを ECC 処理部 2 3 に出力する。

【0040】

ECC(Error Correcting Code)処理部 2 3 は、並べ替え処理部 2 2 から供給された 8 ビット単位の送信データに基づいて、送信データの誤り訂正に用いられる誤り訂正符号を計算する。また、ECC 処理部 2 3 は、計算により求めた誤り訂正符号であるパリティを送信データに付加することによって誤り訂正符号化を行う。誤り訂正符号として例えば Reed Solomon 符号が用いられる。

【0041】

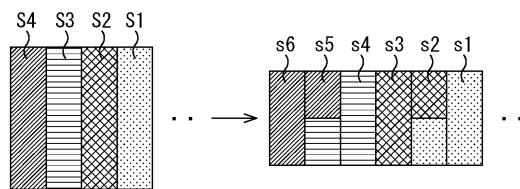

図 3 は、ECC 処理部 2 3 による誤り訂正符号化の例を示す図である。

【0042】

ECC 処理部 2 3 は、所定の数の 8 ビット単位の送信データを情報語として生成多項式に適用し、パリティの計算を行う。例えば、ECC 処理部 2 3 により求められるパリティも 8 ビット単位のデータとされる。ECC 処理部 2 3 は、白抜き矢印の先に示すように、計算により求めたパリティを情報語に付加し、符号語を生成する。ECC 処理部 2 3 は、生成した符号語のデータである符号化データをフレーム化部 2 4 に出力する。

【0043】

フレーム化部 2 4 は、ECC 処理部 2 3 から供給された符号化データをペイロードに格納し、送信データに関する情報を含むヘッダとフッタを付加することによってパケットを生成する。また、フレーム化部 2 4 は、パケットの先頭にパケットデータの開始位置を表す開始コードを付加し、パケットの末尾にパケットデータの終了位置を表す終了コードを付加することによって伝送フレームを生成する。

10

20

30

40

50

## 【0044】

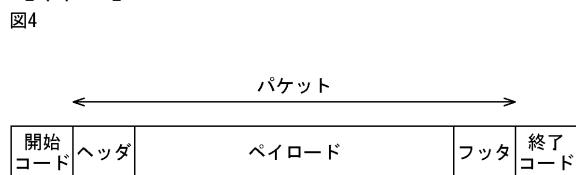

図4は、伝送フレームのフレーム構成を示す図である。

## 【0045】

図4に示すように、符号化データが格納されたペイロードにヘッダとフッタが付加されることによって1パケットが構成される。また、パケットに開始コードと終了コードが付加されることによって伝送フレームが構成される。

## 【0046】

フレーム化部24は、図4に示すようなフレーム構成を有する伝送フレームのデータであるフレームデータを先頭のデータから順に変調部25に出力する。

## 【0047】

変調部25は、フレーム化部24から供給されたフレームデータを所定の方式で変調し、変調後のフレームデータをDAC26に出力する。

## 【0048】

DAC(Digital Analog Converter)26は、変調部25から供給されたフレームデータに対してD/A変換を施し、D/A変換を施すことによって得られたアナログ信号を送信アンプ27に出力する。

## 【0049】

送信アンプ27は、DAC26から供給された信号の信号電圧を調整し、調整後の信号を送信する。

## 【0050】

受信側ブロック12は、受信アンプ31、クロック再生部32、ADC(Analog Digital Converter)33、復調部34、フレーム同期部35、ECC処理部36、並べ替え処理部37、および信号処理部38から構成される。送信側ブロック11の送信アンプ27から出力された信号は受信アンプ31に入力される。

## 【0051】

受信アンプ31は、送信側ブロック11から送信してきた信号を受信し、信号電圧を調整して出力する。受信アンプ31から出力された信号はクロック再生部32とADC33に入力される。

## 【0052】

クロック再生部32は、入力信号のエッジを検出することによってビット同期をとり、エッジの検出周期に基づいてクロック信号を再生する。クロック再生部32は、再生したクロック信号をADC33に出力する。

## 【0053】

ADC33は、クロック再生部32により再生されたクロック信号に従って入力信号のサンプリングを行い、サンプリングによって得られたフレームデータを復調部34に出力する。

## 【0054】

復調部34は、送信側ブロック11の変調部25における変調方式に対応する方式でフレームデータの復調を行い、復調後のフレームデータをフレーム同期部35に出力する。

## 【0055】

フレーム同期部35は、復調部34から供給されたフレームデータから開始コードと終了コードを検出し、フレーム同期をとる。フレーム同期部35は、開始コードから終了コードまでのデータをパケットデータとして検出し、ペイロードに格納されている符号化データをECC処理部36に出力する。

## 【0056】

ECC処理部36は、フレーム同期部35から供給された符号化データに含まれるパリティに基づいて誤り訂正演算を行うことによって送信データの誤りを検出し、検出した誤りの訂正を行う。

## 【0057】

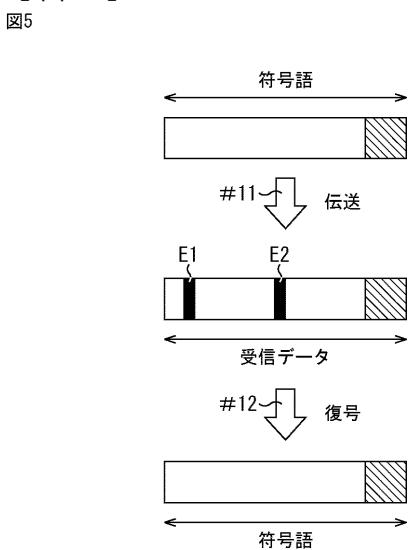

図5は、ECC処理部36による誤り訂正復号の例を示す図である。

10

20

30

40

50

## 【0058】

例えば、図5の上段に示す符号語のデータが符号化データとして送信側ブロック11から送信され、白抜き矢印#11の先に示すようなデータが受信された場合について説明する。図5の受信データ中のビットE1, E2は、誤りのあるビットを表す。

## 【0059】

この場合、ECC処理部36においては、パリティに基づく誤り訂正演算が行われることによってビットE1, E2が検出され、白抜き矢印#12の先に示すように訂正される。ECC処理部36は、各符号語を対象として誤り訂正復号を行い、誤り訂正後の送信データを並べ替え処理部37に出力する。

## 【0060】

並べ替え処理部37は、ECC処理部36から供給された8ビット単位の送信データを、送信側ブロック11の並べ替え処理部22による並び替えの順番と逆順で並び替える。すなわち、並べ替え処理部37においては、図2を参照して説明した処理と逆の処理が行われることによって、8ビット単位の送信データが、12ビットなどの所定のビット数単位の送信データに変換される。並べ替え処理部37は、並び替えを行うことによって得られた送信データを信号処理部38に出力する。

10

## 【0061】

信号処理部38は、並べ替え処理部37から供給された送信データを用いて各種の処理を行う。例えば、送信データが1フレームの画像を構成する画素データである場合、信号処理部38においては、画素データに基づいて1フレームの画像が生成され、画像データの圧縮、画像の表示、記録媒体に対する画像データの記録などの各種の処理が行われる。

20

## 【0062】

## [プロックの動作]

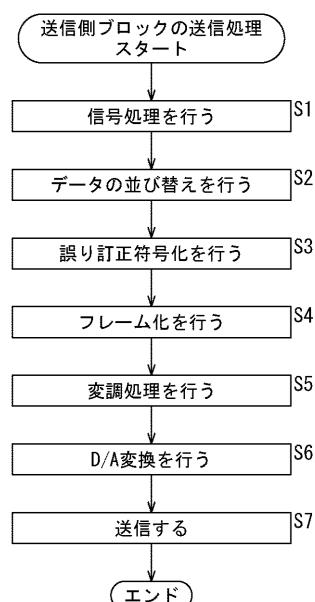

ここで、図1の構成を有する送信側ブロック11と受信側ブロック12の一連の処理について説明する。はじめに、図6のフローチャートを参照して送信側ブロック11の送信処理について説明する。

## 【0063】

ステップS1において、信号処理部21は信号処理を行い、信号処理を行うことによって得られた送信データを出力する。

30

## 【0064】

ステップS2において、並べ替え処理部22は、信号処理部21から供給された送信データを取得し、図2を参照して説明したようにしてデータの並び替えを行う。

## 【0065】

ステップS3において、ECC処理部23は、並び替えによって得られた8ビット単位の送信データに基づいてパリティを計算し、送信データに付加することによって誤り訂正符号化を行う。

40

## 【0066】

ステップS4において、フレーム化部24は、誤り訂正符号化によって得られた符号化データをペイロードに格納し、ヘッダとフッタを付加することによってパケットを生成する。また、フレーム化部24は、パケットの先頭に開始コードを付加し、末尾に終了コードを付加することによってフレーム化を行う。

## 【0067】

ステップS5において、変調部25は、フレーム化によって得られた传送フレームを構成するフレームデータを対象として変調処理を行う。

## 【0068】

ステップS6において、DAC26は、変調処理を行うことによって得られたフレームデータにD/A変換を施す。

## 【0069】

ステップS7において、送信アンプ27は、D/A変換によって得られた信号を受信側ブロック12に送信する。ステップS2乃至S7の処理は、信号処理部21から出力された

50

送信データに基づいて生成されたフレームデータを表す信号の送信が終了するまで繰り返し行われる。

【0070】

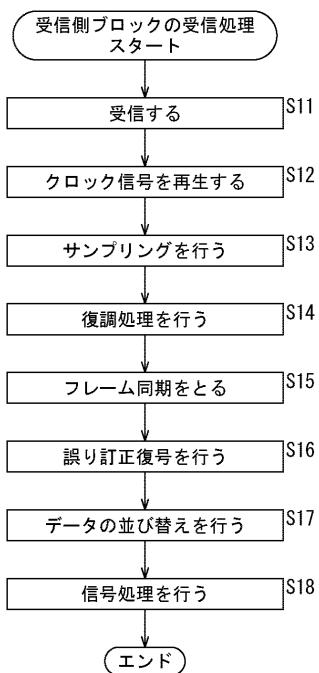

次に、図7のフローチャートを参照して受信側ブロック12の受信処理について説明する。

【0071】

ステップS11において、受信アンプ31は、送信側ブロック11から送信されてきた信号を受信し、信号電圧を調整する。

【0072】

ステップS12において、クロック再生部32は、受信アンプ31から供給された信号のエッジを検出し、クロック信号を再生する。

【0073】

ステップS13において、ADC33は、クロック再生部32により再生されたクロック信号に従ってサンプリングを行う。

【0074】

ステップS14において、復調部34は、サンプリングにより得られたフレームデータを対象として復調処理を行う。

【0075】

ステップS15において、フレーム同期部35は、復調部34から供給されたフレームデータから開始コードと終了コードを検出することによってフレーム同期をとる。フレーム同期部35は、ペイロードに格納されている符号化データをECC処理部36に出力する。

【0076】

ステップS16において、ECC処理部36は、符号化データに基づいて誤り訂正復号を行い、送信データの誤りを訂正する。

【0077】

ステップS17において、並べ替え処理部37は、誤り訂正後の送信データの並び替えを行い、送信側ブロック11において信号処理部21から出力されたデータと同じ所定のビット数単位の送信データを生成する。ステップS11乃至S17の処理は、送信側ブロック11から送信されてきたフレームデータを表す信号の処理が終了するまで繰り返し行われる。

【0078】

フレームデータを表す信号の処理が終了したとき、ステップS18において、信号処理部38は、並べ替え処理部37から供給された送信データに基づいて信号処理を行う。信号処理部38は、信号処理が終了したとき、処理を終了する。

【0079】

以上のように、送信側ブロック11と受信側ブロック12からなる伝送システム1においては、伝送路上において生じた送信データの誤りが、送信データに付加されている誤り訂正符号を用いて訂正される。これにより、送信データの誤りが生じた場合に送信データの再送を送信側ブロック11に対して要求する必要がないため、エラー対策を確保しつつ、データ伝送のリアルタイム性を確保することができる。また、再送要求用の伝送路を設ける必要がないため、回路構成の簡易化、コストの削減を図ることができる。

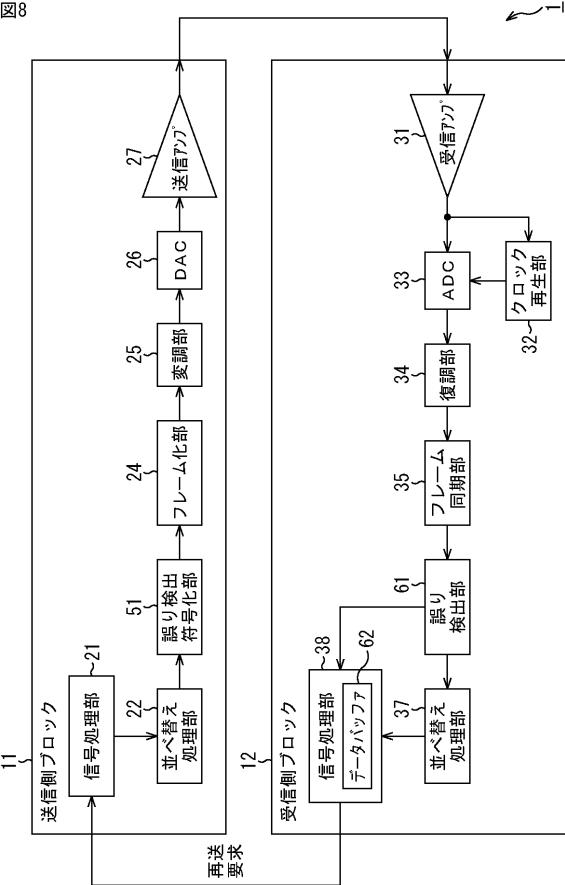

【0080】

図8に、ECC処理部が設けられていない送信側ブロック11と受信側ブロック12の構成を示す。図8の送信側ブロック11には、ECC処理部23に代えて誤り検出符号化部51が設けられ、受信側ブロック12には、ECC処理部36に代えて誤り検出部61が設けられている。

【0081】

送信側ブロック11の誤り検出符号化部51は、並べ替え処理部22から供給された送信データに基づいて誤り検出符号の計算を行い、計算により求めた誤り検出符号を送信デ

10

20

30

40

50

ータに付加する。送信側ブロック11のフレーム化部24、変調部25、DAC26、および送信アンプ27においては上述した処理と同様の処理が行われ、誤り検出符号が付加された送信データが、伝送フレームを用いて受信側ブロック12に送信される。

【0082】

受信側ブロック12に供給された送信データに対しては、受信アンプ31、ADC33、復調部34、およびフレーム同期部35において上述した処理と同様の処理が施され、誤り検出符号が付加された送信データが誤り検出部61に供給される。誤り検出部61は、誤り検出符号に基づいて送信データの誤りを検出し、検出結果を表す情報を信号処理部38に出力する。検出結果を表す情報は信号処理部38のデータバッファ62に格納される。

10

【0083】

信号処理部38は、送信データの誤りが検出されたか否かをデータバッファ62に格納されている情報に基づいて判定し、誤りが検出されたと判定した場合、送信側ブロック11の信号処理部21に対してデータの再送を要求する。

【0084】

送信側ブロック11と受信側ブロック12が図8に示すような構成を有している場合、伝送エラーが生じたときには受信側ブロック12が送信側ブロック11に対してデータの再送を要求する必要があり、リアルタイム性を確保できず、回路構成も複雑になってしまう。

【0085】

20

<第2の実施の形態>

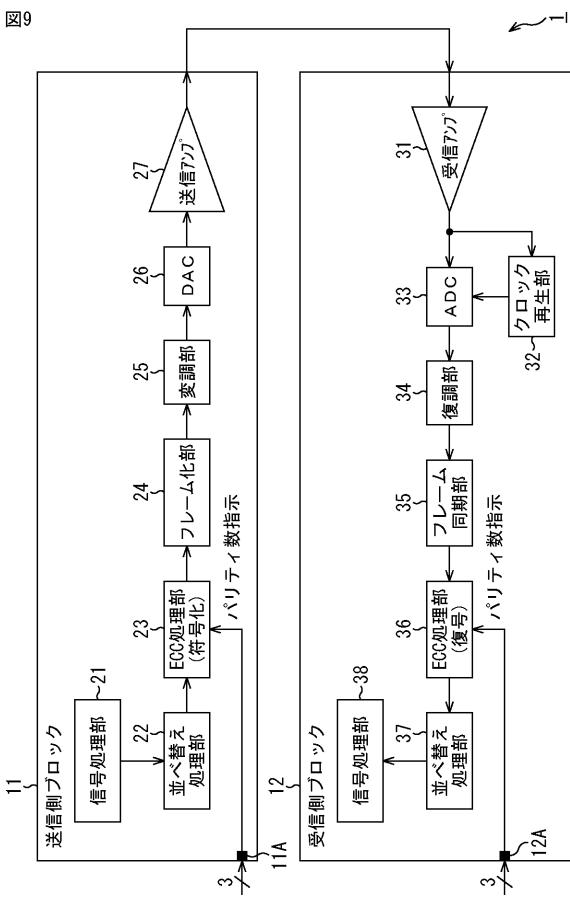

図9は、伝送システム1の第2の構成例を示す図である。

【0086】

図9に示す構成のうち、図1に示す構成と同じ構成には同じ符号を付してある。重複する説明については適宜省略する。

【0087】

図9の伝送システム1においては、誤り訂正の能力を規定するパリティ数が可変となっており、ブロックの外部から設定することができるようになされている。送信側ブロック11、受信側ブロック12とともに同じ装置内に設けられる回路から出力されたパリティ数指示情報は、送信側ブロック11の外部ピン11Aを介してECC処理部23に入力され、受信側ブロック12の外部ピン12Aを介してECC処理部36に入力される。

30

【0088】

パリティ数指示情報は、例えば0, 1, 2, 3, 4バイトの中から選択されたいずれかのパリティ数（パリティのデータ長）を指示する信号である。パリティ数を0バイトとした場合、冗長なデータであるパリティを付加しない代わりに誤り訂正能力がない。一方、パリティ数を1バイトとした場合、1符号語中、1バイトの誤り検出のみが可能となる。パリティ数を2バイトまたは3バイトとした場合、1符号語中、1バイトの誤り訂正が可能となり、パリティ数を4バイトとした場合、1符号語中、2バイトの誤り訂正が可能となる。ここでは、Reed Solomon符号として1, 2, 3, 4バイトのパリティを用いる場合について説明しているが、パリティ数はこれらのサイズに限られるものではない。

40

【0089】

送信側ブロック11のECC処理部23は、パリティ数指示情報により表されるパリティ数を設定し、設定したパリティ数のパリティを送信データに付加するようにして誤り訂正符号化を行う。送信側ブロック11によるデータ送信時の処理は、図6のフローチャートを参照して説明した処理と同じ処理である。

【0090】

一方、受信側ブロック12のECC処理部36は、パリティ数指示情報により表されるパリティ数を設定し、設定したパリティ数のパリティを検出して送信データの誤り訂正を行う。受信側ブロック12によるデータ受信時の処理は、図7のフローチャートを参照して説明した処理と同じ処理である。

50

## 【0091】

これにより、パリティ数を伝送路の誤り率などに応じて適切に設定することが可能となる。伝送路の誤り率は、送信側ブロック11の伝送インターフェースの電気的性能、受信側ブロック12の伝送インターフェースの電気的性能、ブロック間の接続における伝送性能、および伝送途中の電磁気的ノイズ環境などによって定まる。送信側ブロック11と受信側ブロック12の設計時にパリティ数を固定しないで、同じ装置に組み込む送信側ブロック11と受信側ブロック12の仕様が決まってからパリティ数を設定できるようにすることにより、適切なパリティ数を後から設定することが可能になる。

## 【0092】

一般に、パリティのデータ長が長いほど高い誤り訂正能力が得られる。一方、パリティは冗長なデータであるからそれを送信することは伝送速度の観点で好ましくなく、また、誤り訂正のための消費電力も増大する。従って、パリティ数を可変とし、伝送路の誤り率に応じた適切なパリティ数を設定することができるようによることによって、高速のデータ伝送を可能としつつ、消費電力を抑えることが可能となる。

10

## 【0093】

<第3の実施の形態>

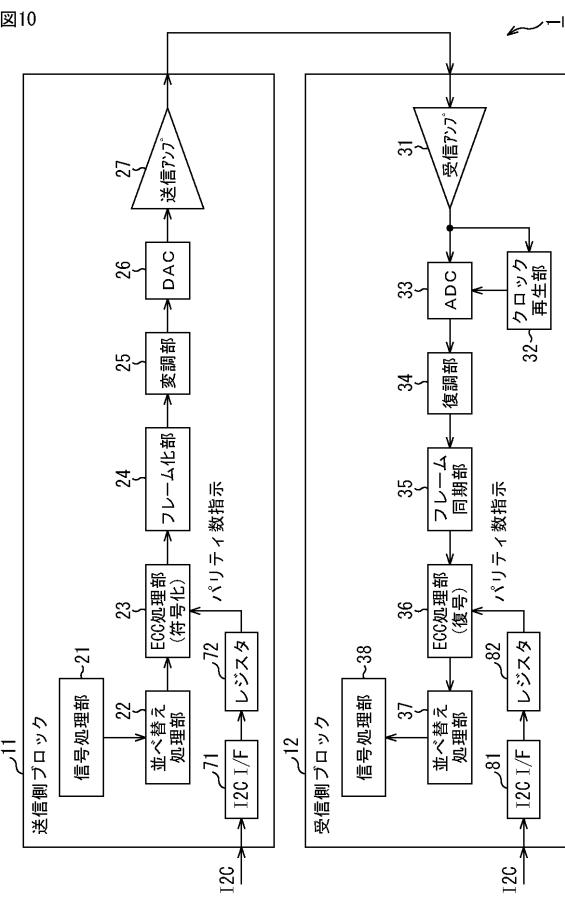

図10は、伝送システム1の第3の構成例を示す図である。

## 【0094】

図10に示す構成のうち、図1に示す構成と同じ構成には同じ符号を付してある。重複する説明については適宜省略する。図10に示す送信側ブロック11の構成は、I2C I/F71とレジスタ72が設けられている点で図1の構成と異なり、受信側ブロック12の構成は、I2C I/F81とレジスタ82が設けられている点で図1の構成と異なる。

20

## 【0095】

図10の伝送システム1においては、パリティ数をブロックの外部ピンを介して設定するのではなく、外部の回路との通信用のバスのインターフェースであるI2Cインターフェースを介して設定することができるようになされている。送信側ブロック11、受信側ブロック12とともに同じ装置内に設けられる回路から出力されたパリティ数指示情報は、送信側ブロック11のI2C I/F71を介してレジスタ72に記憶され、受信側ブロック12のI2C I/F81を介してレジスタ82に記憶される。

30

## 【0096】

送信側ブロック11のECC処理部23は、レジスタ72に記憶されているパリティ数指示情報を読み出し、パリティ数指示情報により表されるパリティ数のパリティを送信データに付加するようにして誤り訂正符号化を行う。送信側ブロック11によるデータ送信時の処理は、図6のフローチャートを参照して説明した処理と同じ処理である。

## 【0097】

一方、受信側ブロック12のECC処理部36は、レジスタ82に記憶されているパリティ数指示情報を読み出し、パリティ数指示情報により表されるパリティ数のパリティを検出して送信データの誤り訂正を行う。受信側ブロック12によるデータ受信時の処理は、図7のフローチャートを参照して説明した処理と同じ処理である。

40

## 【0098】

図10の構成によっても、可変のパリティ数を伝送路の誤り率などに応じて適切に設定することが可能となる。

## 【0099】

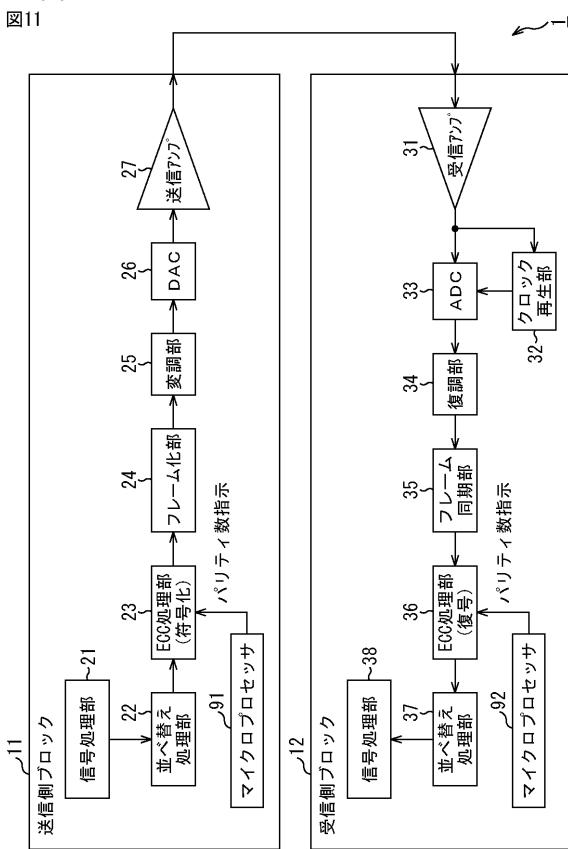

<第4の実施の形態>

図11は、伝送システム1の第4の構成例を示す図である。

## 【0100】

図11に示す構成のうち、図1に示す構成と同じ構成には同じ符号を付してある。重複する説明については適宜省略する。図11に示す送信側ブロック11の構成は、マイクロプロセッサ91が設けられている点で図1の構成と異なり、受信側ブロック12の構成は、マイクロプロセッサ92が設けられている点で図1の構成と異なる。

50

## 【0101】

図11の伝送システム1においては、パリティ数をブロックの外部ピンを介して設定するのではなく、ブロックの内部のマイクロプロセッサから設定することができるようになされている。

## 【0102】

送信側ブロック11のマイクロプロセッサ91は、所定のプログラム(ファームウェア)を実行し、所定のパリティ数を表すパリティ数指示情報をECC処理部23に出力する。

## 【0103】

ECC処理部23は、マイクロプロセッサ91から供給されたパリティ数指示情報に従ってパリティ数を設定し、設定したパリティ数のパリティを送信データに付加するようにして誤り訂正符号化を行う。送信側ブロック11によるデータ送信時の処理は、図6のフローチャートを参照して説明した処理と同じ処理である。10

## 【0104】

一方、受信側ブロック12のマイクロプロセッサ92も同様に、プログラムを実行し、パリティ数指示情報をECC処理部36に出力する。マイクロプロセッサ92が输出するパリティ数指示情報により表されるパリティ数は、送信側ブロック11のマイクロプロセッサ91が输出するパリティ数指示情報により表されるパリティ数と同じである。

## 【0105】

ECC処理部36は、マイクロプロセッサ92から供給されたパリティ数指示情報に従ってパリティ数を設定し、設定したパリティ数のパリティを検出して送信データの誤り訂正を行う。受信側ブロック12によるデータ受信時の処理は、図7のフローチャートを参照して説明した処理と同じ処理である。20

## 【0106】

図11の構成によても、パリティ数を伝送路の誤り率などに応じて適切に設定することが可能となる。また、マイクロプロセッサ91とマイクロプロセッサ92のファームウェアを更新することによってパリティ数を変更することも可能になる。

## 【0107】

<第5の実施の形態>

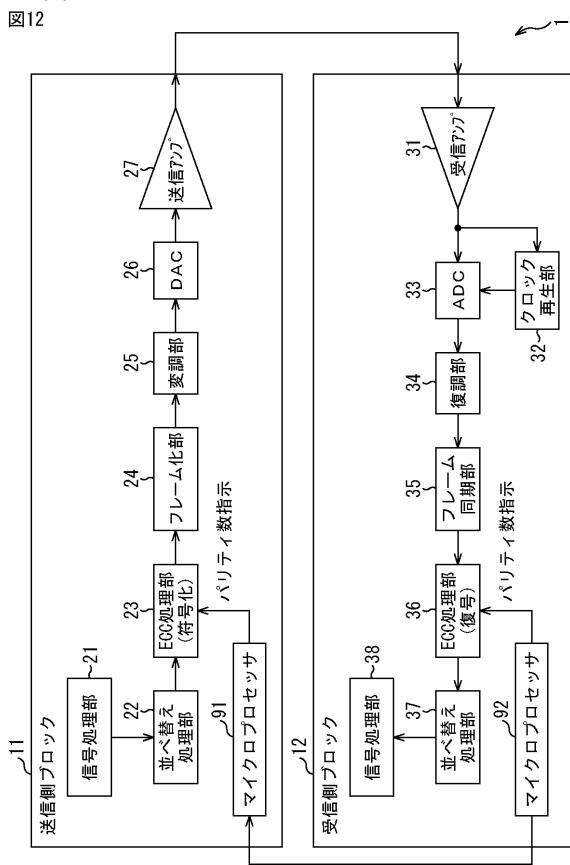

図12は、伝送システム1の第5の構成例を示す図である。

## 【0108】

図12に示す構成のうち、図11に示す構成と同じ構成には同じ符号を付してある。重複する説明については適宜省略する。30

## 【0109】

図12の伝送システム1においては、送信側ブロック11のマイクロプロセッサ91と受信側ブロック12のマイクロプロセッサ92が信号線を介して接続されている。マイクロプロセッサ92からマイクロプロセッサ91に対しては、例えば、マイクロプロセッサ92において検出されたデータの誤り訂正の確率に応じたパリティ数を表すパリティ数指示情報が送信される。

## 【0110】

送信側ブロック11のマイクロプロセッサ91は、マイクロプロセッサ92から供給されたパリティ数指示情報を受信し、ECC処理部23に出力する。40

## 【0111】

ECC処理部23は、マイクロプロセッサ91から供給されたパリティ数指示情報に従ってパリティ数を設定し、設定したパリティ数のパリティを送信データに付加するようにして誤り訂正符号化を行う。

## 【0112】

一方、受信側ブロック12のマイクロプロセッサ92は、パリティ数指示情報をECC処理部36に出力する。マイクロプロセッサ92が送信するパリティ数指示情報により表されるパリティ数は、送信側ブロック11のマイクロプロセッサ91が输出するパリティ数指示情報により表されるパリティ数と同じである。50

**【0113】**

また、マイクロプロセッサ92は、ECC処理部36により行われる誤り訂正処理を監視し、例えば、受信データに対する誤り訂正の対象になったデータの割合を誤り訂正の確率として記憶する。マイクロプロセッサ92は、記憶しておいた誤り訂正の確率に基づいて、送信側ブロック11のECC処理部23と受信側ブロック12のECC処理部36におけるパリティ数を更新する。

**【0114】**

例えば、マイクロプロセッサ92は、記憶しておいた誤り訂正の確率が閾値より高く、現在のパリティ数ではノイズ耐性を保証できないと判定した場合、より長くなるようにパリティ数を更新する。また、マイクロプロセッサ92は、記憶しておいた誤り訂正の確率が閾値より低い場合、より短くなるようにパリティ数を更新する。マイクロプロセッサ92は、更新後のパリティ数を表すパリティ数指示情報をマイクロプロセッサ91に送信する。

10

**【0115】**

ECC処理部36は、マイクロプロセッサ92から供給されたパリティ数指示情報を従つてパリティ数を設定し、設定したパリティ数のパリティを検出して送信データの誤り訂正を行う。

**【0116】**

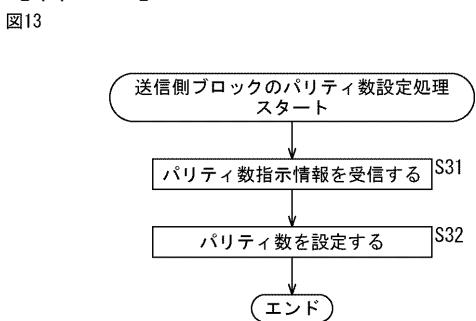

ここで、図13のフローチャートを参照して、送信側ブロック11のパリティ数設定処理について説明する。図13の処理は、例えば図6の処理が行われている間、図6の処理と並行して繰り返し行われる。

20

**【0117】**

ステップS31において、送信側ブロック11のマイクロプロセッサ91は、マイクロプロセッサ92から供給されたパリティ数指示情報を受信する。

**【0118】**

ステップS32において、マイクロプロセッサ91は、受信したパリティ数指示情報をECC処理部23に出力し、パリティ数を設定する。その後、処理は終了される。ECC処理部23においては、マイクロプロセッサ91から供給されたパリティ数指示情報により表されるパリティ数のパリティを送信データに付加するようにして誤り訂正符号化が行われる。

30

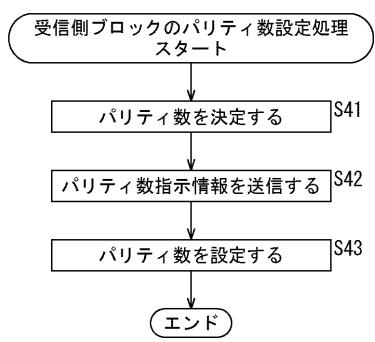

**【0119】**

次に、図14のフローチャートを参照して、受信側ブロック12のパリティ数設定処理について説明する。図14の処理は、例えば図7の処理が行われている間、図7の処理と並行して繰り返し行われる。

**【0120】**

ステップS41において、受信側ブロック12のマイクロプロセッサ92は、ECC処理部36における誤り訂正を監視し、誤り訂正の確率に基づいて、新たなパリティ数を決定する。

**【0121】**

ステップS42において、マイクロプロセッサ92は、決定した更新後のパリティ数を表すパリティ数指示情報をマイクロプロセッサ91に送信する。

40

**【0122】**

ステップS43において、マイクロプロセッサ92は、更新後のパリティ数を表すパリティ数指示情報をECC処理部36に出力し、パリティ数を設定する。その後、処理は終了される。ECC処理部36においては、マイクロプロセッサ92から供給されたパリティ数指示情報により表されるパリティ数のパリティを検出して送信データの誤り訂正が行われる。

**【0123】**

このように、受信側ブロック12から送信側ブロック11に対して信号を返す経路を設けることによって、誤り訂正の能力を実際の伝送状況に応じて自律的に設定することが可

50

能となる。

【0124】

[コンピュータの構成例]

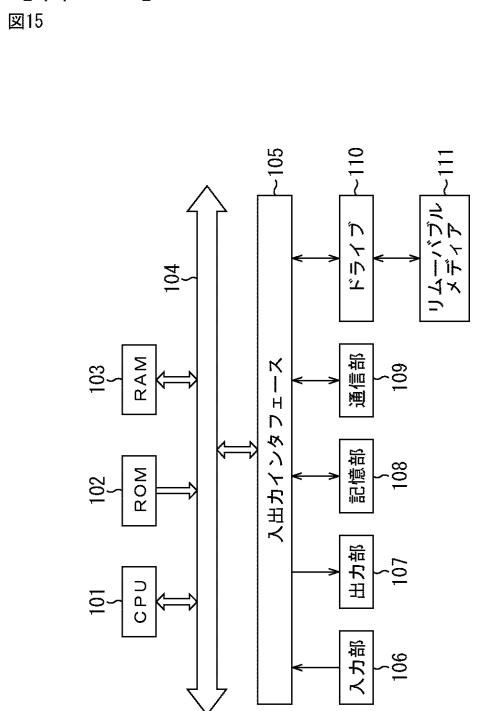

上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または汎用のパーソナルコンピュータなどに、プログラム記録媒体からインストールされる。

【0125】

図15は、上述した一連の処理をプログラムにより実行するコンピュータのハードウェアの構成例を示すプロック図である。

【0126】

CPU(Central Processing Unit)101、ROM(Read Only Memory)102、RAM(Random Access Memory)103は、バス104により相互に接続されている。

【0127】

バス104には、さらに、入出力インターフェース105が接続されている。入出力インターフェース105には、キーボード、マウスなどよりなる入力部106、ディスプレイ、スピーカなどよりなる出力部107が接続される。また、入出力インターフェース105には、ハードディスクや不揮発性のメモリなどよりなる記憶部108、ネットワークインターフェースなどよりなる通信部109、リムーバブルメディア111を駆動するドライブ110が接続される。

【0128】

以上のように構成されるコンピュータでは、CPU101が、例えば、記憶部108に記憶されているプログラムを入出力インターフェース105及びバス104を介してRAM103にロードして実行することにより、上述した一連の処理が行われる。

【0129】

CPU101が実行するプログラムは、例えばリムーバブルメディア111に記録して、あるいは、ローカルエリアネットワーク、インターネット、デジタル放送といった、有線または無線の伝送媒体を介して提供され、記憶部108にインストールされる。

【0130】

なお、コンピュータが実行するプログラムは、本明細書で説明する順序に沿って時系列に処理が行われるプログラムであっても良いし、並列に、あるいは呼び出しが行われたとき等の必要なタイミングで処理が行われるプログラムであっても良い。

【0131】

本発明の実施の形態は、上述した実施の形態に限定されるものではなく、本発明の要旨を逸脱しない範囲において種々の変更が可能である。

【符号の説明】

【0132】

1 伝送システム, 11 送信側プロック, 12 受信側プロック, 21 信号処理部, 22 並べ替え処理部, 23 ECC処理部, 24 フレーム化部, 25 40 变調部, 26 DAC, 27 送信アンプ, 31 受信アンプ, 32 クロック再生部, 33 ADC, 34 復調部, 35 フレーム同期部, 36 ECC処理部, 37 並べ替え処理部, 38 信号処理部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

四

【 図 8 】

四 8

【 四 9 】

四 9

【 図 1 0 】

图 10

【図 1 1】

【図 1 3】

【図 1 4】

【図 1 2】

【図 1 5】

---

フロントページの続き

(72)発明者 松本 英之

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 城下 寛司

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 丸子 健一

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 杉岡 達也

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 越坂 直弘

神奈川県横浜市保土ヶ谷区神戸町134番地 ソニー・エルエスアイ・デザイン株式会社内

(72)発明者 佐々木 茂寿

神奈川県横浜市保土ヶ谷区神戸町134番地 ソニー・エルエスアイ・デザイン株式会社内

(72)発明者 田森 正人

神奈川県横浜市保土ヶ谷区神戸町134番地 ソニー・エルエスアイ・デザイン株式会社内

F ターム(参考) 5J065 AD03 AH01

5K014 BA05 FA13