(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7123522号**

**(P7123522)**

(45)発行日 令和4年8月23日(2022.8.23)

(24)登録日 令和4年8月15日(2022.8.15)

(51)国際特許分類

|         |                |     |         |      |         |

|---------|----------------|-----|---------|------|---------|

| G 0 9 G | 3/20 (2006.01) | F I | G 0 9 G | 3/20 | 6 2 3 B |

| G 0 2 F | 1/133(2006.01) |     | G 0 9 G | 3/20 | 6 2 3 C |

| G 0 9 F | 9/30 (2006.01) |     | G 0 9 G | 3/20 | 6 2 3 F |

| G 0 9 F | 9/46 (2006.01) |     | G 0 9 G | 3/20 | 6 2 3 G |

| G 0 9 G | 3/30 (2006.01) |     | G 0 9 G | 3/20 | 6 2 3 H |

請求項の数 8 (全43頁) 最終頁に続く

(21)出願番号 特願2016-184931(P2016-184931)

(22)出願日 平成28年9月22日(2016.9.22)

(65)公開番号 特開2017-62474(P2017-62474A)

(43)公開日 平成29年3月30日(2017.3.30)

審査請求日 令和1年9月20日(2019.9.20)

審判番号 不服2021-11048(P2021-11048/J

1)

審判請求日 令和3年8月19日(2021.8.19)

(31)優先権主張番号 特願2015-188757(P2015-188757)

(32)優先日 平成27年9月25日(2015.9.25)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 小林 英智

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

(72)発明者 高橋 圭

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

合議体

審判長 中塚 直樹

審判官 濱本 穎広

審判官 居島 一仁

最終頁に続く

(54)【発明の名称】 ドライバIC、および電子機器

**(57)【特許請求の範囲】****【請求項1】**

第1出力端子および第2出力端子が設けられており、

外部からデジタル信号が入力され、

前記デジタル信号のデータには少なくとも第1乃至第3データがあり、

外部から入力される画像信号から第1アナログ信号を生成する機能と、

前記画像信号から第2アナログ信号を生成する機能と、

前記デジタル信号のデータが前記第1データである場合、前記第1アナログ信号を交流電圧信号として前記第1出力端子から出力し、かつ前記第2アナログ信号を直流電圧信号として前記第2出力端子から出力する機能と、

前記デジタル信号のデータが前記第2データである場合、前記第1アナログ信号を交流電圧信号として前記第1出力端子から出力し、かつ前記第2アナログ信号を交流電圧信号として前記第2出力端子から出力する機能と、

前記デジタル信号のデータが前記第3データである場合、前記第1アナログ信号を直流電圧信号として前記第1出力端子から出力し、かつ前記第2アナログ信号を直流電圧信号として前記第2出力端子から出力する機能と、を備えるドライバIC。

**【請求項2】**

請求項1において、

前記画像信号および前記デジタル信号は、それぞれ差動信号であるドライバIC。

**【請求項3】**

表示パネル、およびドライバを有する電子機器であって、

前記ドライバは、前記表示パネルに電気的に接続され、

前記ドライバは、請求項 1 又は 2 に記載のドライバ I C を 1 または複数有する電子機器。

**【請求項 4】**

表示パネル、ドライバ、照度センサ、および画像プロセッサを有する電子機器であって、

前記ドライバは、前記表示パネルに電気的に接続され、請求項 1 乃至 3 の何れか 1 項に

記載のドライバ I C を 1 または複数有し、

前記画像プロセッサは、

前記画像信号を生成する機能と、

前記照度センサの検知信号に応じて、前記画像信号の階調データを決定する機能と、を

備える電子機器。 10

**【請求項 5】**

請求項 3 又は 4 に記載の表示パネルは、複数のサブ画素を有し、

前記複数のサブ画素は、それぞれ、交流駆動される第 1 表示素子、および直流駆動され

る第 2 表示素子を有する電子機器。

**【請求項 6】**

請求項 3 又は 4 に記載の表示パネルは、複数のサブ画素を有し、

前記複数のサブ画素は、それぞれ、交流駆動される第 1 表示素子、直流駆動される第 2

表示素子、第 1 トランジスタ、および第 2 トランジスタを有し、

前記第 1 トランジスタは前記第 1 表示素子と電気的に接続され、

前記第 2 トランジスタは前記第 2 表示素子と電気的に接続され、

前記第 1 トランジスタおよび前記第 2 トランジスタは同じ絶縁表面上に設けられている

電子機器。 20

**【請求項 7】**

請求項 6 において、

前記第 1 トランジスタのチャネル形成領域は、金属酸化物を有し、

前記第 2 トランジスタのチャネル形成領域は、金属酸化物を有する電子機器。

**【請求項 8】**

請求項 5 乃至 7 の何れか 1 項において、

前記第 1 表示素子は液晶素子であり、

前記第 2 表示素子はエレクトロルミネセンス素子である電子機器。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の一形態は、表示装置の技術の分野に属しており、例えば、表示装置の駆動回路、

駆動方法などに関する。なお、ここで記載する技術分野は例示であり、本発明の一形態が

適用可能な技術分野は、これに限定されるものではない。

**【背景技術】**

**【0002】**

アクティブマトリクス型表示装置の多階調化、及び高精細化等に対応するため、アクティ

ブマトリクス型表示装置のドライバ回路、特に、映像信号からデータ信号を生成するため

のソースドライバには専用の I C ( ドライバ I C ) が採用されている。例えば、特許文献

1 には液晶表示装置用のドライバ I C が開示され、特許文献 2 には E L ( エレクトロルミ

ネセンス ) 表示装置用のドライバ I C が開示されている。 40

**【0003】**

1 のサブ画素に液晶素子と発光素子が設けられているハイブリッド ( 複合型 ) 表示装置が

提案されている ( 例えば、特許文献 3 - 5 ) 。

**【先行技術文献】**

**【特許文献】**

**【0004】**

【文献】特開2007-286525号公報

特開2009-223070号公報

特開2003-157026号公報

国際公開第2004/053819号

国際公開第2007/041150号

【発明の概要】

【発明が解決しようとする課題】

【0005】

反射型液晶表示装置は、バックライトを必要としないため低消費電力であるが、明るい外光が得られる場所（明るい屋外、照明された屋内など）でないと、良好な表示を行えない。EL素子が自発光素子であるため、EL表示装置は暗い場所で良好な表示ができる一方、明るい場所では、視認性が低下してしまう。特許文献3-5で開示されるハイブリッド表示装置は、反射型液晶表示装置とEL表示装置の特長が生かされており、使用場所の明るさによらず使用することができる。

10

【0006】

特許文献3等に記載されているように、液晶表示装置とEL表示装置とでは駆動方法が異なる。液晶表示装置では、液晶の焼き付きを防止するために液晶（LC）素子を交流駆動させる必要がある。EL表示装置では、EL素子を直流駆動しており、EL素子のアノード電極とカソード電極間の電流の大きさを調節することで、EL素子の輝度を制御している。

20

【0007】

よって、ハイブリッド表示装置では、同じ階調データから、LC素子用とEL素子用とで個別にデータ信号を生成することが求められる。この課題の単純な解決方法は、液晶表示装置用ソースドライバICと、EL表示装置用ソースドライバICとを用いることである。この方法だと、ハイブリッド表示装置の小型化、軽量化、および薄型化の妨げになる。また、2種類のソースドライバICを用いることは、コストの増加につながる。

【0008】

そこで、本発明の一形態の課題は、表示装置を駆動するための新規な回路を提供すること、または、新規な表示装置を提供すること、または表示装置の新規な駆動方法を提供することである。または、本発明の一形態の課題は、汎用性の高いドライバを提供すること、もしくは、表示装置のサイズ、重量、厚さ、またはコストの増加を抑えることである。

30

【0009】

なお、複数の課題の記載は、互いの課題の存在を妨げるものではない。なお、本発明の一形態は、これらの課題の全て解決する必要はない。列記した以外の課題が、明細書、図面、請求項（以下、「本明細書等」と呼ぶ。）の記載から、自ずと明らかとなるものであり、これらの課題も、本発明の一形態の課題となり得る。

【課題を解決するための手段】

【0010】

(1) 本発明の一形態は、ソース線を駆動する機能を有するドライバICであって、出力ピンを有し、外部から入力される画像信号から、アナログデータ信号を生成する機能と、前記アナログデータ信号を前記出力ピンから出力する機能と、外部から入力されるデジタル信号のデータに応じて、前記出力ピンから出力させるアナログデータ信号を交流電圧信号として出力するか、直流電圧信号として出力するかを設定する機能を備えるドライバICである。

40

【0011】

(2) 本発明の一形態は、第1出力ピンおよび第2出力ピンが設けられており、外部からデジタル信号が入力され、前記デジタル信号のデータには少なくとも第1乃至第3データがあり、外部から入力される画像信号から第1アナログデータ信号を生成する機能と、前記画像信号から第2アナログデータ信号を生成する機能と、前記デジタル信号のデータが前記第1データである場合、前記第1アナログデータ信号を交流電圧信号として、前記第

50

1出力ピンから出力し、かつ前記第2アナログデータ信号を直流電圧信号として前記第2出力ピンから出力する機能と、前記デジタル信号のデータが前記第2データである場合、前記第1アナログデータ信号を交流電圧信号として、前記第1出力ピンから出力し、かつ前記第2アナログデータ信号を交流電圧信号として前記第2出力ピンから出力する機能と、前記デジタル信号のデータが前記第3データである場合、前記第1アナログデータ信号を直流電圧信号として、前記第1出力ピンから出力し、かつ前記第2アナログデータ信号を直流電圧信号として前記第2出力ピンから出力する機能とを備えるドライバICである。

#### 【0012】

(3) 本発明の一形態は、第1出力ピン、第2出力ピン、ロジック回路、シフトレジスタ、ラッチ回路、デジタルーアナログ変換回路、マルチプレクサ、および增幅回路を有するドライバICであって、ロジック回路は、第1乃至第3制御信号を生成する機能と、外部から入力される画像信号から第1デジタルデータ信号および第2デジタルデータ信号を生成する機能と、を備え、ラッチ回路は、シフトレジスタの出力信号に従い、第1デジタルデータ信号および第2デジタルデータ信号をラッチする機能と、第1制御信号に従い、第1デジタルデータ信号、および第2デジタルデータ信号を出力する機能と、を備え、デジタルーアナログ変換回路は、第1デジタル信号のデータに基づき、極性が正の信号と負の信号とでなる第1アナログデータ信号対を生成する機能と、第2デジタル信号のデータに基づき、極性が正の信号と負の信号とでなる第2アナログデータ信号対を生成する機能とを備え、マルチプレクサは、第2制御信号のデータに基づき、第1アナログデータ信号対の一方を増幅回路に出力する機能と、第3制御信号のデータに基づき、第2アナログデータ信号対の一方を増幅回路に出力する機能とを備え、増幅回路は、マルチプレクサから出力された第1アナログデータ信号を増幅して、第1出力ピンに出力する機能と、マルチプレクサから出力された第2アナログデータ信号を増幅して、第2出力ピンに出力する機能とを備えるドライバICである。

#### 【0013】

(4) 本発明の一形態は、表示パネル、およびソースドライバを有する電子機器であって、ソースドライバは表示パネルに電気的に接続され、ソースドライバは上掲形態(1)-(3)の何れか1のドライバICを1または複数有する。

#### 【0014】

本明細書等において、半導体装置とは、半導体特性を利用した装置であり、半導体素子(トランジスタ、ダイオード、フォトダイオード等)を含む回路、同回路を有する装置等をいう。また、半導体特性を利用して機能しうる装置全般をいう。例えば、集積回路、集積回路を備えたチップや、パッケージにチップを収納した電子部品は半導体装置の一例である。また、記憶装置、表示装置、発光装置、照明装置及び電子機器等は、それ自体が半導体装置であり、半導体装置を有している場合がある。

#### 【0015】

本明細書等において、XとYとが接続されていると記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。X、Yは、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層など)であるとする。

#### 【0016】

トランジスタは、ゲート、ソース、およびドレインと呼ばれる3つの端子を有する。ゲートは、トランジスタの導通状態を制御する制御ノードである。ソースまたはドレインとして機能する2つの入出力ノードは、トランジスタの型及び各端子に与えられる電位の高低によって、一方がソースとなり他方がドレインとなる。このため、本明細書等においては、ソースとドレインの用語は、入れ替えて用いることができるものとする。また、本明細書等では、ゲート以外の2つの端子を第1端子、第2端子と呼ぶ場合や、第3端子、第4端子と呼ぶ場合などがある。

10

20

30

40

50

**【 0 0 1 7 】**

ノードは、回路構成やデバイス構造等に応じて、端子、配線、電極、導電層、導電体、不純物領域等と言い換えることが可能である。また、端子、配線等をノードと言い換えることが可能である。

**【 0 0 1 8 】**

電圧は、ある電位と、基準の電位（例えば接地電位、ソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。なお、電位とは相対的なものである。よって、GNDと記載されても、必ずしも0Vを意味しない場合がある。

**【 0 0 1 9 】**

本明細書等において、「第1」、「第2」、「第3」などの序数詞は、順序を表すために使用される場合がある。または、構成要素の混同を避けるために使用する場合があり、この場合、序数詞の使用は構成要素の個数を限定するものではなく、順序を限定するものでもない。また、例えば、「第1」を「第2」または「第3」に置き換えて、本発明の一形態を説明することができる。

**【発明の効果】****【 0 0 2 0 】**

本発明の一形態は、表示装置を駆動するための新規な回路を提供すること、または、新規な表示装置を提供すること、または、表示装置の新規な駆動方法を提供することを可能にする。または、本発明の一形態は、汎用性の高いドライバを提供することを可能にする。または、本発明の一形態は、表示装置のサイズ、重量、厚さ、またはコストの増加を抑えることができる。

**【 0 0 2 1 】**

複数の効果の記載は、他の効果の存在を妨げるものではない。また、本発明の一形態は、必ずしも、例示した効果の全てを有する必要はない。また、本発明の一形態について、上記以外の課題、効果、および新規な特徴については、本明細書の記載および図面から自ずと明らかになるものである。

**【図面の簡単な説明】****【 0 0 2 2 】**

【図1】表示装置の構成例を示す図。

30

【図2】表示装置の構成例を示す分解斜視図。

【図3】表示モジュールの構成例を示す模式図。

【図4】A、B：表示モジュール（タッチパネルモジュール）の構成例を示す模式図。

【図5】A - D：画素部の構成例を示す回路図。

【図6】画素部および周辺回路の構成例を示す図。

【図7】ソースドライバICの構成例を示すブロック図。

【図8】ソースドライバICの動作の概要を説明する図。

【図9】ソースドライバICの構成例を示すブロック図。

【図10】電圧生成回路の構成例を示す回路図。

【図11】A、B：パストランジスタロジック回路のマルチプレクサの構成例を示す回路図。

40

【図12】A、B：パストランジスタロジック回路のマルチプレクサの構成例を示す回路図。

【図13】ピンの極性制御の例を説明する図。

【図14】ピンの極性制御の例を説明する図。

【図15】ピンの極性制御の例を説明する図。

【図16】ピンと画素部の接続構造の一例を説明する図。

【図17】A - C：ドライバICの構成例を示すブロック図。

【図18】A、B：表示装置の動作例を説明する図。

【図19】A - F：電子機器の構成例を示す図。

50

【図20】A - D : 電子機器の構成例を示す図。

【図21】A、B : 電子機器の構成例を示す図。

【図22】A、B : 表示モジュールの構成例を示す平面図。

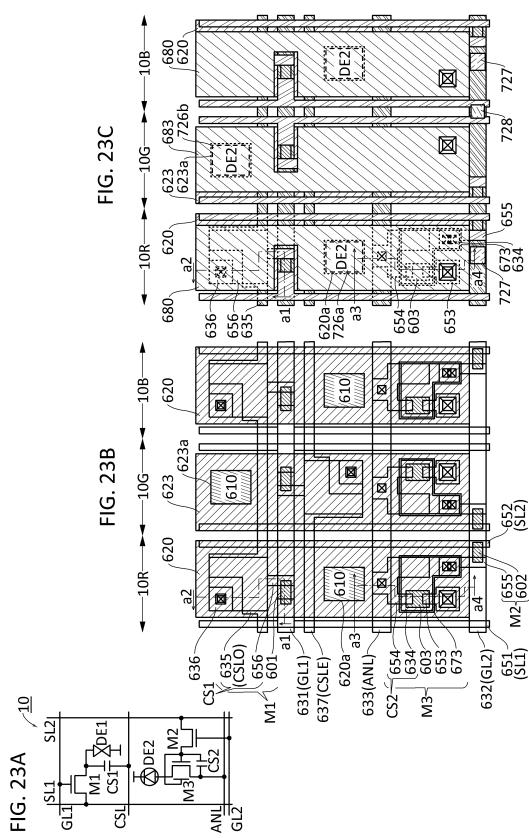

【図23】A : サブ画素の構成例を示す回路図。B、C : サブ画素の構成例を示すレイアウト図。

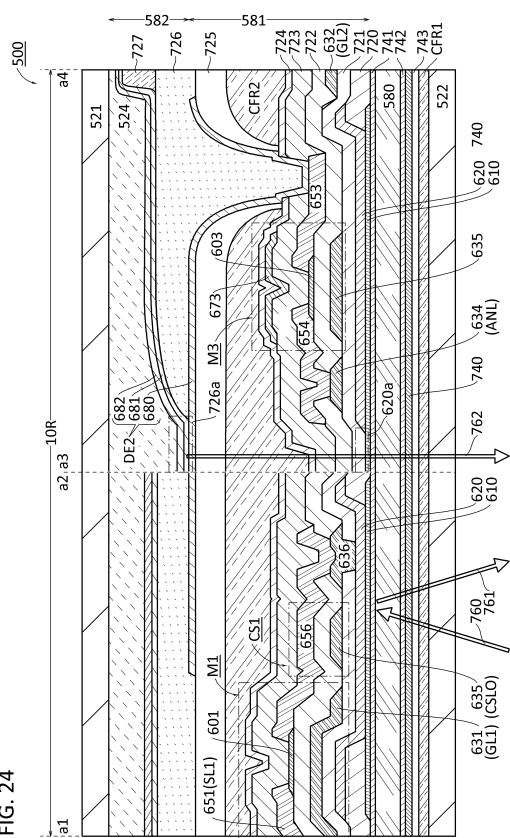

【図24】表示モジュール(サブ画素)の構成例を示す断面図。

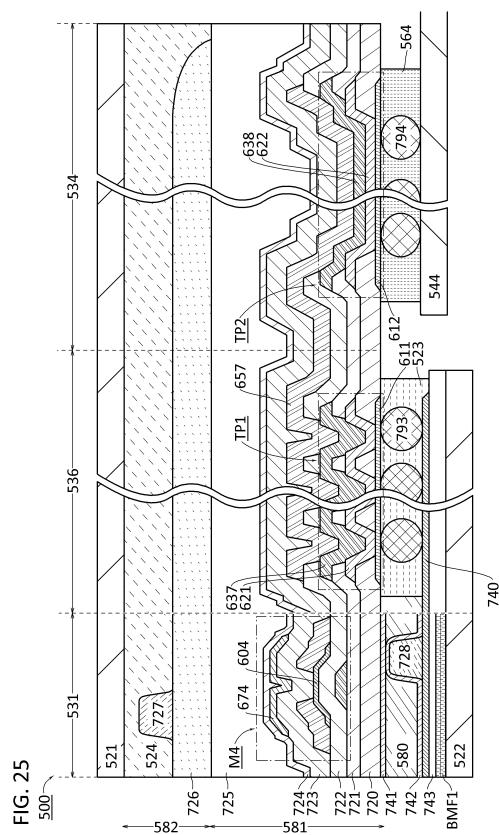

【図25】表示モジュール(ゲートドライバ、コモンコンタクト部、端子部)の構成例を示す断面図。

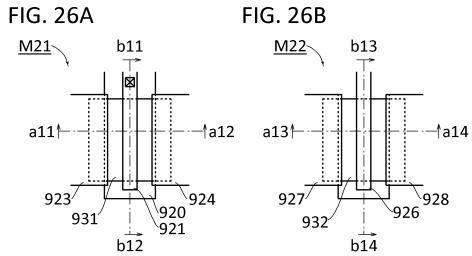

【図26】A、B : OSトランジスタの構成例を示す平面図。C、D : OSトランジスタの構成例を示す断面図。

【図27】トランジスタの構成例を示す断面図。

【発明を実施するための形態】

【0023】

なお、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている場合がある。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

【0024】

本明細書等において、「膜」という言葉と「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を「導電膜」という用語に変更することが可能な場合がある。例えば、「絶縁膜」という用語を「絶縁層」という用語に変更することが可能な場合がある。

【0025】

図面において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。

【0026】

以下に、本発明の実施の形態例を説明する。ただし、本発明の一形態は、以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明の一形態は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0027】

また、以下に示される複数の実施の形態は適宜組み合わせることが可能である。また1の実施の形態の中に、複数の構成例(作製方法例、動作方法例等も含む。)が示される場合は、互い構成例を適宜組み合わせること、および他の実施の形態に記載された1または複数の構成例と適宜組み合わせることも可能である。

【0028】

〔実施の形態1〕

ここでは、1つのサブ画素に液晶素子と発光素子とが設けられているハイブリッド型表示装置について説明する。

【0029】

<<表示装置>>

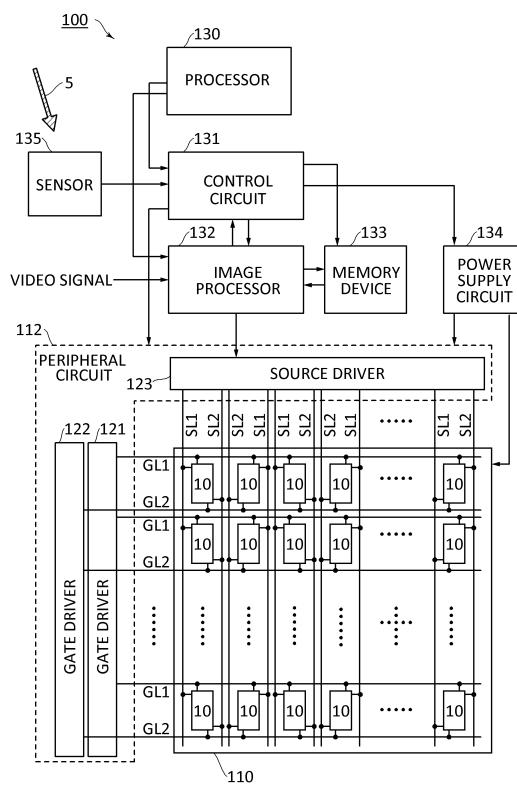

図1は表示装置の構成例を示すブロック図である。表示装置100は、画素部110、周辺回路112、プロセッサ130、制御回路131、画像プロセッサ132、記憶装置133、電源回路134、センサ135を有する。

【0030】

プロセッサ130は、命令を実行し、表示装置100を統括的に制御するための回路である。プロセッサ130には、CPU、MPUなどの各種プロセッサを適用できる。また、表示装置100が、表示部を構成する電子部品として電子機器に組み込まれている場合、プロセッサ130は、電子機器(ホスト装置)のプロセッサであってもよい。

10

20

30

40

50

**【 0 0 3 1 】**

プロセッサ 130 が実行する命令は、外部から入力される命令、および内部メモリに格納された命令である。プロセッサ 130 は、制御回路 131、画像プロセッサ 132 を制御する信号を生成する。プロセッサ 130 の制御信号、センサ 135 の検知信号等に基づき、制御回路 131 は、表示装置 100 の動作を制御する。制御回路 131 は、プロセッサ 130 が決定した処理が実行されるように、周辺回路 112、画像プロセッサ 132、電源回路 134、および記憶装置 133 を制御する。制御回路 131 には、例えば、画面の書き換えのタイミングを決定する各種の同期信号が入力される。同期信号としては、例えば水平同期信号、垂直同期信号、および基準クロック信号等があり、制御回路 131 は、これらの信号から周辺回路 112 の制御信号を生成する。

10

**【 0 0 3 2 】**

表示装置 100 は、使用環境の明るさに応じて、画面の明るさの調節、及び表示モード (E L 素子による表示、L C 素子による表示) の変更等が可能となっている。センサ 135 はこのために設けられている。センサ 135 は外光 5 を検知して検知信号を生成する光センサを有する。制御回路 131 は検知信号に基づいて、周辺回路 112 および画像プロセッサ 132 の制御信号を生成する。例えば、センサ 135 は照度を検出する照度センサとすることができる。画像プロセッサ 132 はセンサ 135 の検知信号に応じた、信号処理が可能であるので、例えば、画像プロセッサ 132 は、照度に応じて、画像信号の階調データを設定することができる。なお、センサ 135 の検知信号をプロセッサ 130 に入力するようにしてもよいし、画像プロセッサ 132 に入力してもよい。

20

**【 0 0 3 3 】**

電源回路 134 は、画素部 110、周辺回路 112 に電源電圧を供給する機能を有する。

**【 0 0 3 4 】**

画素部 110 は、複数のサブ画素 10、複数の配線 G L 1、S L 1、G L 2、S L 2 を有する。複数のサブ画素 10 はアレイ状に配列されている。複数の配線 G L 1、S L 1、G L 2、S L 2 は、複数のサブ画素 10 の配列に応じて設けられている。各サブ画素 10 は、L C 素子および E L 素子を有しており、対応する行の配線 G L 1、G L 2 と電気的に接続され、対応する列の配線 S L 1、S L 2 と電気的に接続されている。配線 G L 1、S L 1 は L C 素子を駆動するための配線であり、配線 G L 2、S L 2 は E L 素子を駆動するための配線である。配線 G L 1、G L 2 をゲート線、走査線、または選択信号線等と呼ぶことができる。また、配線 S L 1、S L 2 をソース線、データ線、またはデータ信号線等と呼ぶことができる。

30

**【 0 0 3 5 】**

周辺回路 112 は、画素部 110 を駆動するドライバとして機能する。周辺回路 112 は、ゲートドライバ 121、122、およびソースドライバ 123 を有する。ゲートドライバ 121 は配線 G L 1 を駆動するための回路であり、配線 G L 1 に供給する信号を生成する機能を有する。ゲートドライバ 122 は配線 G L 2 を駆動するための回路であり、配線 G L 2 に供給する信号を生成する機能を有する。ソースドライバ 123 は配線 S L 1、S L 2 を駆動するため回路であり、配線 S L 1、S L 2 に供給する信号を生成する機能を有する。

40

**【 0 0 3 6 】**

画像プロセッサ 132 は、外部から入力される映像信号を処理して、ソースドライバ 123 が処理する画像信号を生成する機能を有する。画像信号は階調データをもつデジタル信号である。画像プロセッサ 132 は、画像信号を補正する機能を有する。ソースドライバ 123 は、画像信号を処理して、配線 S L 1、S L 2 に供給するデータ信号を生成する機能を有する。

**【 0 0 3 7 】**

記憶装置 133 は、画像プロセッサ 132 が処理を行うために必要なデータを格納するために設けられている。記憶装置 133 には、例えば、画像信号、外部から入力される映像信号等が格納される。

50

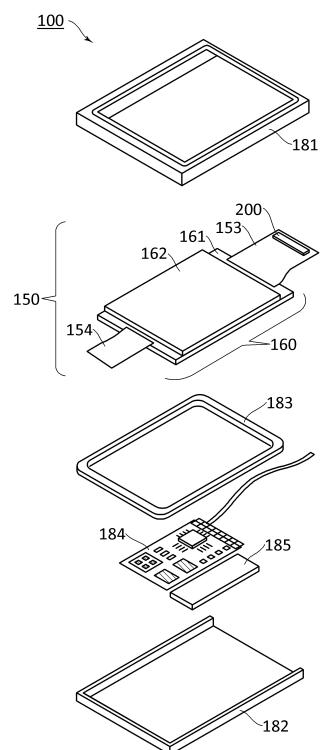

### 【0038】

図2は、表示装置100の構成例を示す分解斜視図である。表示装置100は、上部カバー181と下部カバー182との間に、各種の部品を有する。図2の例では、表示装置100は、表示モジュール150、フレーム183、プリント基板184、およびバッテリ185を有する。フレーム183、バッテリ185等は設けられていない場合もある。表示装置100に、表示パネル160を照明する照明装置（例えば、フロントライトユニット）を設けてもよい。

### 【0039】

プリント基板184には、画素部110および周辺回路112以外の回路を設けることができる。例えば、プリント基板184には、プロセッサ130、制御回路131、画像プロセッサ132、記憶装置133、電源回路134を設けることができる。電源回路134に電力を供給する電源としては、外部の商用電源であっても良いし、バッテリ185であってもよい。

10

### 【0040】

フレーム183は、表示パネル160の保護機能の他、プリント基板184で発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム183は、放熱板の機能を有していてもよい。表示パネル160のサイズに合わせて、上部カバー181の形状、寸法を適宜変更することができる。下部カバー182およびフレーム183も同様である。

### 【0041】

20

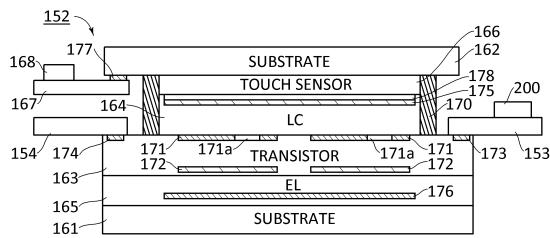

#### （表示モジュール）

表示モジュール150は、ソースドライバIC200、FPC（Flexible Printed Circuit）153、154、および表示パネル160を有する。表示パネル160は基板161、162を有する。基板161と基板162間に、画素部110、ゲートドライバ121、122が設けられている。ソースドライバ123はソースドライバIC200に組み込まれている。FPC153は、表示パネル160の端子部に電気的に接続され、FPC154は他の端子部に電気的に接続されている。FPC153には、ソースドライバIC200が電気的に接続されている。FPC153によって、ソースドライバIC200は外部回路（例えば、制御回路131、画像プロセッサ132、電源回路134）と電気的に接続される。FPC154によって、画素部110、ゲートドライバ121、122は外部回路（例えば、制御回路131、電源回路134）と電気的に接続される。

30

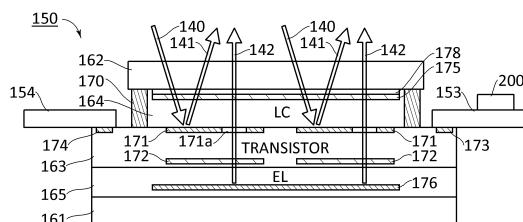

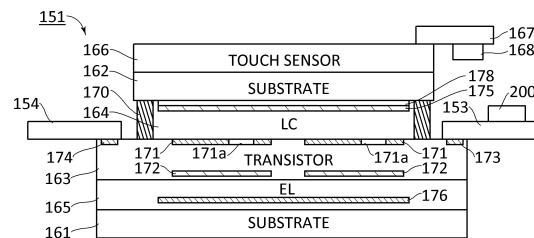

### 【0042】

図3は、表示モジュール150の構成の概要を説明するための断面図である。表示モジュール150は、基板161と基板162の間に、トランジスタ層163、LC層164、EL素子層165を有する。LC層164は、基板162とトランジスタ層163との間に封止材170によって設けられた隙間に存在する。

### 【0043】

トランジスタ層163は、画素部110、およびゲートドライバ121、122を構成する各種の素子が設けられる層である。素子としては、トランジスタ、容量素子、整流素子、抵抗素子等がある。トランジスタ層163には、画素電極171、画素電極172、および端子部173、174が設けられている。画素電極171はLC用画素電極であり、反射電極である。そのため、EL素子の光を取り出すために画素電極171は開口171aを有する。画素電極172はEL用画素電極であり、光を透過する透過電極である。

40

### 【0044】

基板162にはコモン電極175、カラーフィルタ178等が設けられている。EL素子層165には、EL層、コモン電極176等が設けられている。コモン電極175はLC用コモン電極であり、透過電極である。コモン電極176はEL用コモン電極であり、反射電極である。

### 【0045】

50

表示モジュール 150 は、外光を利用した反射型 LC 表示モジュールと、EL 素子の発光を利用した EL 表示モジュール（自発光型表示モジュール）双方の機能を備えるハイブリッド表示モジュールである。外光 140 は基板 162 から入射し、カラーフィルタ 178、コモン電極 175 および LC 層 164 を経て画素電極 171 で反射される。画素電極 171 で反射された光 141 は LC 層 164、コモン電極 175、カラーフィルタ 178 を通り、基板 162 から射出する。光 141 の輝度は画素電極 171 とコモン電極 175 間の電位差によって決まる。光 142 は EL 素子層 165 で生じた光である。光 142 の輝度は、EL 素子層 165 を流れる電流によって決まる。光 142 は、コモン電極 176 で反射され、画素電極 171 の開口 171a を通り、LC 層 164、コモン電極 175、カラーフィルタ 178 を経て、基板 162 から取り出される。

10

#### 【0046】

基板 162 の外光 140 が入射する表面に、光学フィルム（例えば、偏光フィルム、位相差フィルム、プリズムシート、反射防止フィルム）などを設けてもよい。

#### 【0047】

表示モジュール 150 にタッチセンサを設けてもよい。そのような例を図 4A、図 4B に示す。図 4A に示す表示モジュール 151 は、表示モジュール 150 にオンセル型タッチパネルを設けた電子部品であり、図 4B に示す表示モジュール 152 はインセル型タッチパネルを設けた電子部品である。表示モジュール 151、152 は、タッチパネルモジュールと呼ぶことができる。

20

#### 【0048】

表示モジュール 151 は、タッチセンサ 166、FPC 167、タッチセンサドライバ IC 168 を有する。タッチセンサ 166 は基板 162 の外側の面（光 141、142 が取り出される面）に設けられている。

#### 【0049】

タッチセンサ 166 には、抵抗膜方式タッチセンサ、静電容量方式タッチセンサ等を用いることができる。タッチセンサドライバ IC 168 は、タッチセンサ 166 を駆動する機能を有する。タッチセンサドライバ IC 168 は FPC 167 に電気的に接続され、FPC 167 はタッチセンサ 166 の端子部に電気的に接続されている。

#### 【0050】

表示モジュール 152 は、FPC 167、タッチセンサドライバ IC 168、タッチセンサ 166、端子 177 を有する。タッチセンサ 166 は、基板 162 とコモン電極 175 の間に設けられている。端子 177 は、タッチセンサ 166 の作製工程において、基板 162 に形成される。タッチセンサ 166 は、端子 177、FPC 167 を介してタッチセンサドライバ IC 168 と電気的に接続される。

30

#### 【0051】

図 3、図 4 において、ソースドライバ IC 200 の実装方式は COF (Chip on Flexible) 方式であるが、実装方式に特段の制約はなく、COG (Chip on Glass) 方式、TAB (Tape Automated Bonding) 方式でもよい。タッチセンサドライバ IC 168 についても同様である。

40

#### 【0052】

基板 161 はトランジスタ層 163、EL 素子層 165 を作製するために使用した支持基板（ガラス基板や石英基板など）と異なる基板である。トランジスタ層 163、および EL 素子層 165 を作製した後、または作製工程中に、支持基板を剥離し、接着層により基板 161 を EL 素子層 165 に取り付けている。支持基板を剥離することで、FPC 153 と接続される端子、および FPC 154 と接続される端子を露出させることができる。

#### 【0053】

基板 161、162 を可撓性基板としてすることで、可撓性の表示パネル 160 を得ることができる。表示部に可撓性の表示パネル 160 を用いることで、画面を曲げて使用できる電子機器を提供することが可能である。

#### 【0054】

50

表示パネル 160 の基板 161、162 に適用可能な基板としては、例えば、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルムなどが挙げられる。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート (P E T)、ポリエチレンナフタレート (P E N)、ポリエーテルサルファン (P E S) に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムには、ポリプロピレン、ポリエステル、ポリフッ化ビニル、ポリ塩化ビニル等からなるフィルム、または無機蒸着フィルムなどを用いることもできる。フィルム基材としては、ポリエステル樹脂、ポリアミド樹脂、ポリイミド樹脂、アラミド樹脂、エポキシ樹脂、および紙類などがある。

#### 【0055】

基板 161 に使用できる基板（フィルムも含む）は、トランジスタ層 163 および E L 素子層 165 を支持する機能、および E L 素子層 165 を保護する機能等を備えていればよい。また、基板 162 に使用できる基板（フィルムも含む）は、可視光を透過する機能、L C 層 164 を封止できる機能等を備えていればよい。例えば、基板 162 には、光学フィルム（円偏光フィルム）を用いることができる。これにより、基板 162 に光学フィルムを固定する場合よりも、表示モジュール 150 を軽量化、薄型化することができる。

#### 【0056】

図 3 に示す表示モジュール 150 では、1 のトランジスタ層 163 によって、画素部 110 を構成することができる。そのため、ソースドライバ 123 を L C 用ドライバ I C と E L 用ドライバ I C とで構成するという制約はなく、1 種類のソースドライバ I C 200 で、L C 用ソース線 (S L 1) および E L 用ソース線 (S L 2) を駆動させることができる。以下、そのような機能を備えたソースドライバ I C について説明する。

#### 【0057】

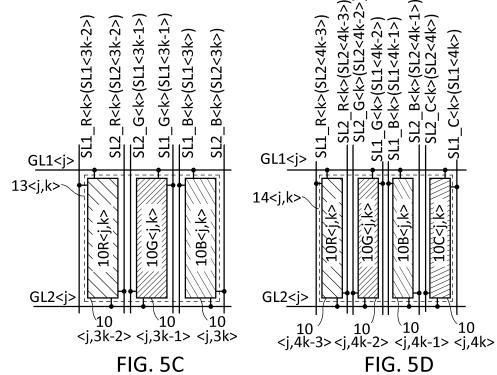

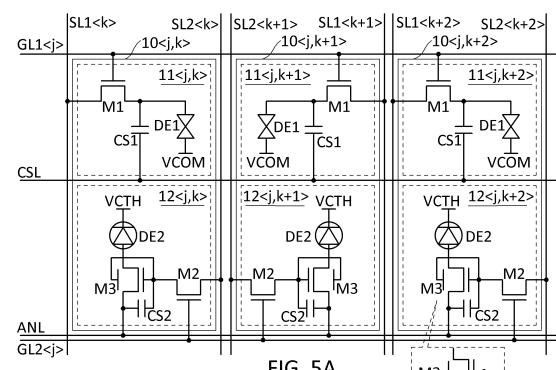

##### （画素部 110）

ソースドライバ I C の構成例、動作例を説明する前に、まず、画素部 110 の回路構成について説明する。図 5 A に画素部 110 の回路構成例を示す。図 5 A には代表的に 1 行 3 列に配列された 3 のサブ画素 10 を示している。サブ画素 10 < j、k > とは、第 j 行第 k 列のサブ画素 10 であることを示し、配線 G L 1 < j > は第 j 行の配線 G L 1 であることを示し、配線 S L 2 < k > は、第 k 列の配線 S L 2 であることを示している。j、k は 1 よりも大きい整数である。

#### 【0058】

サブ画素 10 はサブ画素 11、12 を有する。サブ画素 11 は L C 表示パネル用サブ画素であり、トランジスタ M1、容量素子 C S 1、L C 素子 D E 1 を有する。サブ画素 11 は、配線 G L 1、S L 1、C S L と電気的に接続されている。配線 C S L は、画素部 110 の全てのサブ画素 11 に共通な配線であり、各サブ画素 11 の容量素子 C S 1 と電気的に接続されている。V C O M は、L C 素子 D E 1 のコモン電極に入力される電圧である。

#### 【0059】

ここでは、サブ画素 11 は反射型液晶表示パネルのサブ画素と同じ構成を持つ画素であるが、サブ画素 11 の構成はこれに限定されない。サブ画素 11 は外光を利用して表示ができる構造を有していればよい。例えば、L C 素子 D E 1 の代わりに、電気泳動方式の表示素子、粒子移動方式の表示素子、または粒子回転方式の表示素子などを、サブ画素 11 に設けてもよい。

#### 【0060】

サブ画素 12 は E L 表示パネル用のサブ画素であり、トランジスタ M2、M3、容量素子 C S 2、E L 素子 D E 2 を有する。サブ画素 12 は、配線 G L 2、S L 2、A N L と電気的に接続されている。配線 A N L は、画素部 110 の全てのサブ画素 12 に共通な配線であり、各サブ画素 12 の容量素子 C S 2 と電気的に接続されている。V C T H は E L 素子

10

20

30

40

50

D E 2 のコモン電極（ここでは、カソード電極）の電圧であり、サブ画素 1 2 のコモン電圧である。配線 A N L には、V C T H よりも高い電圧が入力される。

#### 【 0 0 6 1 】

トランジスタ M 2 は選択トランジスタと呼ばれ、トランジスタ M 3 は駆動トランジスタと呼ばれる。容量素子 C S 2 はトランジスタ M 3 のゲート電圧を保持するために設けられている。トランジスタ M 3 はバックゲートを有する。トランジスタ M 3 のゲートにバックゲートを電気的に接続していることで、トランジスタ M 3 の電流駆動能力を向上させている。また、図 5 B に示すように、トランジスタ M 3 のドレインとバックゲートを電気的に接続することでも、同様の効果が得られる。

#### 【 0 0 6 2 】

E L 素子 D E 2 は、一対の電極（アノード電極、カソード電極）、および一対の電極に挟まれた E L 層を有する。図 5 A の例では E L 素子 D E 2 の画素電極がアノード電極であり、コモン電極がカソード電極である。E L 層は、発光性の物質を含む層（発光層）を少なくとも含む。E L 層には、その他に、電子輸送物質を含む層（電子輸送層）、正孔輸送物質を含む層（正孔輸送層）など、他の機能層を適宜設けることができる。E L 素子は、発光物質が有機物である場合は有機 E L 素子と呼ばれ、無機物である場合は無機 E L 素子と呼ばれる。なお、ここでは、E L 素子をサブ画素 1 1 に設けたが、発光素子は E L 素子に限定されない。発光ダイオード、発光トランジスタ等でもよい。

10

#### 【 0 0 6 3 】

表示装置 1 0 0 がカラー表示を行う場合、所定の数のサブ画素によって、1 の画素が構成される。例えば、赤色（R）、緑色（G）、青色（B）を表示する 3 のサブ画素 1 0 で、1 画素を構成することができる。図 5 C は、このような画素を持つ画素部 1 1 0 の構成例を示している。画素 1 3 < j , k > は、サブ画素 1 0 R < j , k >、1 0 G < j , k >、1 0 B < j , k > で構成される。図 5 C の例では、画素部 1 1 0 の同じ列には、同じ色を表示するサブ画素 1 0 が設けられていることとなり、画素部 1 1 0 のサブ画素 1 1 の配列は、縦方向（列方向）の R G B ストライプ配列である。

20

#### 【 0 0 6 4 】

また、表示色が異なる 4 個のサブ画素 1 0 で単位画素を構成することもできる。この場合 4 色の表示色の組み合わせとして、[ R , G , B , Y ( 黄色 ) ]、[ R , G , B , C ( シアン ) ] などが挙げられる。図 5 D に、4 個 ( R G B C ) のサブ画素 1 0 で 1 画素が構成される例を示す。画素 1 4 < j , k > は、サブ画素 1 0 R < j , k >、1 0 G < j , k >、1 0 B < j , k >、1 0 C < j , k > を有する。ここでは、サブ画素 1 0 の配列は縦方向の R G B C ストライプ配列である。

30

#### 【 0 0 6 5 】

4 のサブ画素 1 0 で画素を構成する場合、例えば、1 のサブ画素 1 0 R、1 のサブ画素 1 0 G、2 のサブ画素 1 0 B で画素を構成することもできる。例えば、この場合、サブ画素 1 0 の配列は、R B G B ストライプ配列とすればよい。

#### 【 0 0 6 6 】

本明細書では、サブ画素の表示色を用いて、構成要素を区別する場合、R、\_R 等の識別記号を付すことにする。例えば、サブ画素 1 0 R は赤色のサブ画素 1 0 を表す。配線 S L 1 \_ G < k > とは、緑色のデータ信号が入力される第 k 列の配線 S L 1 を表している。よって、図 5 C において、表示色を区別しない場合、配線 S L 1 \_ R < k > は、第 3 k - 2 列の配線 S L 1 であり、配線 S L 1 \_ G < k > は第 3 k - 1 列の配線 S L 1 であり、配線 S L 1 \_ B < k > は第 3 k 列の配線 S L 1 である。配線 S L 2 も同様である。図 5 D にも、サブ画素 1 0 、配線 S L 1 、S L 2 について、表示色を区別する場合と、区別しない場合の符号を記載している。

40

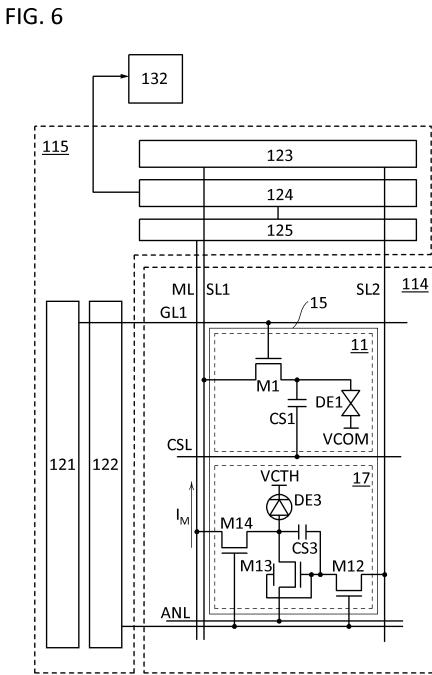

#### 【 0 0 6 7 】

なお、画素部 1 1 0 のサブ画素の回路構成は、図 5 A、図 5 B に限定されるものでなく、1 のサブ画素に、L C 素子と E L 素子とを有していればよい。図 6 に画素部および周辺回路の他の構成例を示す。図 6 に示す画素部 1 1 4 はサブ画素 1 5 を有する。なお、図 6 で

50

は、1のサブ画素15のみ示しているが、画素部110と同様に、画素部114には、複数のサブ画素15が行列状に配列されている。また、画素部114には、複数の配線G L 1、C S L、A N L、S L 1、S L 2、M Lが設けられる。サブ画素15は対応する行の配線G L 1、C S Lと電気的に接続され、かつ対応する列の配線S L 1、S L 2、M Lと電気的に接続されている。

#### 【0068】

サブ画素15はサブ画素10の変形例であり、サブ画素12に代えてサブ画素17が設けられている。サブ画素17は、E L素子D E 3、容量素子C S 3、トランジスタM 1 2 M 1 4を有する。トランジスタM 1 2は、トランジスタM 1 3のゲートと配線S L 2間を接続するパストランジスタである。トランジスタM 1 4は、配線M LとE L素子D E 3のアノード間を接続するパストランジスタである。トランジスタM 1 3は駆動トランジスタであり、E L素子D E 3に供給される電流の電流源として機能する。容量素子C S 3は、E L素子D E 3のアノードとトランジスタM 1 3のゲート間の電圧を保持する保持容量である。

#### 【0069】

トランジスタM 1 4を設けることで、サブ画素17からトランジスタM 1 4のドレイン電流（電流I M）を配線M Lに出力させることが可能となる。電流I MはE L素子D E 3を流れる電流に対応する。したがって、配線M Lに流れるアナログ信号（電流I M）を解析し、解析結果に基づき、配線S L 2に入力されるデータ信号の電圧を補正することで、E L素子D E 3の輝度のずれを補正することができる。

#### 【0070】

周辺回路115は、周辺回路112に、信号処理回路124、出力回路125を追加したものである。出力回路125は、複数の配線M Lと電気的に接続されている。出力回路125は、配線M Lを流れるアナログ信号の信号処理回路124への出力を制御する機能を有する。出力回路125は、外部から入力される制御信号に従って、複数の配線M Lを選択し、選択した複数の配線M Lを信号処理回路124の入力端子と電気的に接続する。つまり、出力回路125はデマルチプレクサとして機能している。

#### 【0071】

信号処理回路124は出力回路125を介して画素部114から入力されるアナログ信号を処理して、画像プロセッサ132が処理するデジタル信号を生成する機能を有する。例えば、信号処理回路124にはアナログ-デジタル変換回路（A D C）を設ければよい。A D Cにおいて、画素部114から入力されるアナログ信号を処理してデジタル信号に変換する。画像プロセッサ132では、信号処理回路124から出力されるデジタル信号を解析して、配線S L 2に書き込む階調データを補正する。

#### 【0072】

例えば、周辺回路115において、ゲートドライバ121、122、出力回路125は、画素部114のトランジスタM 1、M 1 2 - 1 4と共にトランジスタ層163に設けることができる。この場合、ソースドライバI C 2 0 0には、ソースドライバ123と信号処理回路124とを設ければよい。

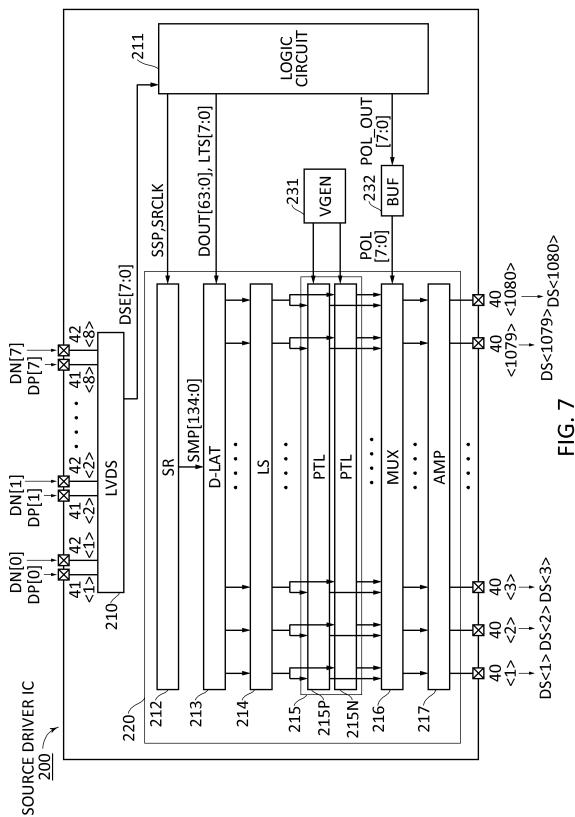

#### 【0073】

<<ソースドライバI C >>

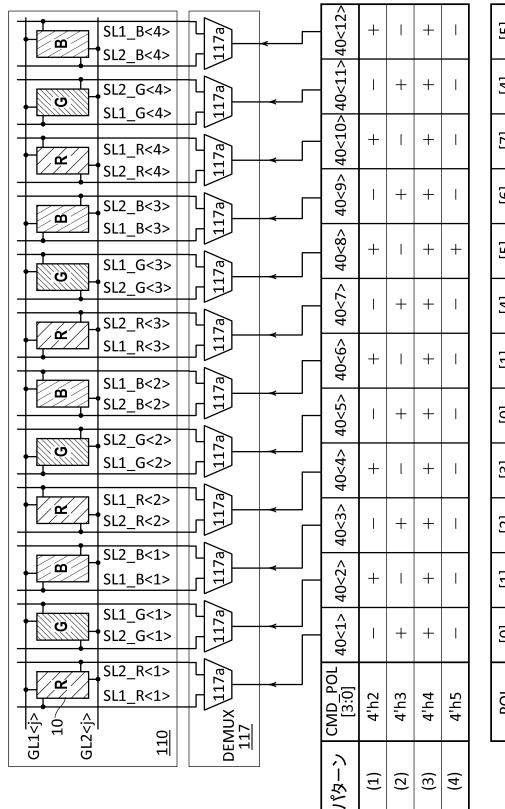

図7に、ソースドライバI C 2 0 0の構成例を示す。ここでは、本実施の形態の理解を容易にするため、ソースドライバI C 2 0 0および表示パネル160の仕様を次のように設定する。ソースドライバI C 2 0 0に伝送される画像信号はシリアル形式の8ビットデジタル信号である。8ビットデジタル信号のデータが階調レベルを表す。また、画像信号の伝送方式は差動方式である。差動形式の画像信号の一方が画像信号D P [ 7 : 0 ]であり、他方が画像信号D N [ 7 : 0 ]である。データ信号用の出力ピンの数は1080である。

#### 【0074】

画素部110の画素は3（R G B）のサブ画素10で構成されている（図5C）。表示パネル160に用いられるソースドライバI C 2 0 0の数は、表示パネル160の水平方向

10

20

30

40

50

のサブ画素 10 の数によって決まる。例えば、水平方向のサブ画素 10 の数が 1080 ( $= 360 \times 3$  (RGB)) であれば、ソースドライバ I C 200 の使用数は 2 である。

#### 【0075】

ソースドライバ I C 200 は、1080 のピン 40、8 のピン 41、8 のピン 42、LVDS (小振幅差動信号) レシーバ 210、ロジック回路 211、回路 220、電圧生成回路 231 (以下、「VGEN231」と呼ぶ。)、バッファ回路 (BUF) 232 を有する。回路 220 は、シフトレジスタ (SR) 212、ラッチ回路 213 (以下、「DLAT213」と呼ぶ。)、レベルシフタ (LS) 214、パストランジスタロジック回路 (PTL) 215、マルチプレクサ (MUX) 216、増幅回路 (AMP) 217 を有する。

10

#### 【0076】

ピン 40 は、データ信号用の出力ピンであって、配線 SL1 または配線 SL2 と電気的に接続される。ピン 41、42 は、差動信号用の入力ピンである。例えば、ピン 42 <1> には、ピン 41 <1> の入力信号の論理を反転した信号が入力される。ピン 41、42 に入力される差動信号は画像プロセッサ 132 で生成される。例えば、ピン 41 <1> - 41 <8> には画像信号 DP[0] - DP[7] がそれぞれ入力され、ピン 42 <1> - 42 <8> には画像信号 DN[0] - DN[7] がそれぞれ入力される。

#### 【0077】

ピン 41、42 は画像信号 DP[7:0]、DN[7:0] の入力だけでなく、コマンド信号の入力にも用いられる。ソースドライバ I C 200 には、ピン 40 - 42 の他に、電源電圧の入力用ピン、各種信号の入力用ピン、各種信号の出力用ピンが設けられている。

20

#### 【0078】

LVDS レシーバ 210 は、入力された差動信号をシングルエンド方式の信号に変換する機能を有する。ここでは、LVDS レシーバ 210 によって、画像信号 DP[7:0]、DN[7:0] は、シングルエンド方式の画像信号 DSE[7:0] に変換される。

#### 【0079】

ロジック回路 211 は、外部から入力されるコマンド信号等に従い、回路 220 を制御する。具体的には、ロジック回路 211 は信号 SSP、SRCLK、LTS[7:0]、POL\_OUT[7:0] 等を生成する。信号 SSP、SRCLK は、SR212 の制御信号である。信号 LTS[7:0] は DLAT213 の制御信号である。信号 POL\_OUT[7:0] は MUX216 の制御信号である。

30

#### 【0080】

ロジック回路 211 は、シリアル形式の画像信号をパラレル形式の画像信号に変換する機能 (シリアル-パラレル変換機能) を有する。具体的には、ロジック回路 211 は信号 DSE[7:0] を 8 の 8 ビットデジタル信号 (DOUT[63:0]) に変換する。信号 DOUT[8 + 7, 8] (8 は 0 乃至 7 の整数) のデータは、配線 SL1 または配線 SL2 に書き込まれる 8 ビットの階調データである。

#### 【0081】

なお、ソースドライバ I C 200 には、様々な機能回路を設けることができる。例えば、使用する環境の温度や劣化による EL 素子 DE2 の輝度の変化を補正する機能を有する補正回路を、ソースドライバ I C 200 に設けてよい。より具体的には、補正回路は、配線 SL2 に出力されるデータ信号 DS を補正する機能を有する。

40

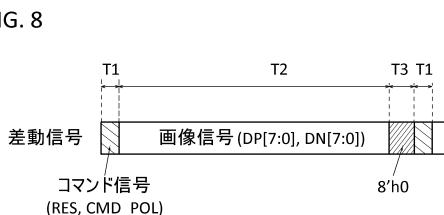

#### 【0082】

図 8 を用いて、ソースドライバ I C 200 の動作の概要を説明する。図 8 に示すように、ソースドライバ I C 200 の動作は、3 つに大別される。期間 T1 は、コマンド信号の処理期間である。期間 T1 では、ロジック回路 211 は、ピン 41、42 から入力される差動信号をコマンド信号として処理する。期間 T1 の長さは入力するコマンド信号の数によって決まる。少なくとも、ソースドライバ I C 200 をリセットするためのコマンド信号 (RES)、および、ピン 40 の極性を決定するためのコマンド信号 (CMD\_POL) が入力される。また、ここでは、コマンド信号のデータ幅は 1 乃至 8 ビットとすることが

50

できる。

#### 【 0 0 8 3 】

本明細書において、ピン40の極性とは、ピン40から出力されるデータ信号DSの極性のことを指す。データ信号DSの電圧がVCOM( LC素子DE1のコモン電圧)以上であれば、データ信号DSの極性は正であり、これがVCOM未満であれば、その極性は負であるとする。画素が3(RGB)のサブ画素10で構成される場合は、ピン40<1>-40<1080>の極性は、12(3(RGB)×2(SL1、SL2)×2(正負の極性))のピン毎に変化する。

#### 【 0 0 8 4 】

期間T2は画像信号処理期間である。期間T2では、ソースドライバIC200は、ピン41、42から入力される差動信号を画像信号として処理する。つまり、期間T2で、画像信号DP[7:0]、DN[7:0]からデータ信号DS<1>-DS<1080>が生成される。期間T2において、画像信号DP[7:0]がピン41に、画像信号DN[7:0]がピン42に入力され、LVDSレシーバ210で信号DSE[7:0]に変換される。ロジック回路211は、LVDSレシーバ210から出力される信号DSE[7:0]を画像信号として処理し、回路220を制御して、回路220でデータ信号DS<1>-DS<1080>を生成させる。

10

#### 【 0 0 8 5 】

期間T3は、ブランク期間である。期間T3では、例えば、8'h0の差動信号をピン41、42に入力すればよい。期間T3では、ソースドライバIC200は待機状態である。期間T3の後、信号RESの入力で次の期間T1が開始する。信号RESは、ロジック回路211でコマンド信号処理のトリガーとなる信号でもある。

20

#### 【 0 0 8 6 】

回路220は、信号DO<sub>UT</sub>[63:0]を処理して、1080のデータ信号DSを生成する。データ信号DSは、階調データを表すアナログ信号である。データ信号DS<1>-DS<1080>は、それぞれ、ピン40<1>-40<1080>から出力される。

#### 【 0 0 8 7 】

ここでは、SR212は、135段のフリップフロップ回路(以下、「SR FF」と呼ぶ。)を有する。1段目のSR - FFに信号SSP(スタートパルス信号)を入力することで、各段のSR - FFから所定のタイミングで1ビットの信号SMP(サンプリング信号)が出力される。したがって、SR212から、135ビットの信号SMP[134:0]が出力される。各段のSR - FFが信号SMPを出力するタイミングは、クロック信号SRCLKによって制御される。

30

#### 【 0 0 8 8 】

信号SMP[134:0]に従い、D-LAT213は信号DO<sub>UT</sub>[63:0]をサンプリングする。これにより、D-LAT213は、1080の8ビットのデータ信号を記憶する。D-LAT213からの1080のデータ信号の出力のタイミングは、信号LT<sub>S</sub>[7:0]によって制御される。LS214はD-LAT213から出力された1080のデータ信号をそれぞれレベルシフトする。

40

#### 【 0 0 8 9 】

PTL215はデジタルアナログ(D-A)変換機能を持つ回路である。ここでは、PTL215は、LS214の出力信号のデータをもとに、1080のアナログ信号対を生成する。アナログ信号対は、極性が正のアナログ信号と負のアナログ信号からなる。アナログ信号の極性は、LC素子DE1を駆動するための交流電圧信号の極性に対応している。

#### 【 0 0 9 0 】

PTL215は、PTL215P、215Nを有する。PTL215Pは、LS214の出力信号を正のアナログ信号に変換する機能を有し、PTL215Nはこれを負のアナログ信号に変換する機能を有する。VGEN231は、PTL215P、215NがD-A変換を行うための基準電圧を生成するための回路である。

#### 【 0 0 9 1 】

50

MUX216には、1080の正負のアナログ信号対が入力される。MUX216は、信号POL[7:0]に従い、アナログ信号対のうちの何れか一つを選択し、AMP217に出力する。BUF232は信号POL\_OUTをバッファし、かつレベルシフトして出力する。BUF232の出力信号が信号POL[7:0]である。

#### 【0092】

AMP217はMUX216から出力される1080のアナログ信号をそれぞれ増幅する。AMP217の1080の出力信号がデータ信号DS<1>-DS<1080>である。

#### 【0093】

ソースドライバIC200は、1の階調データをもつデジタル信号から正負の極性をもつアナログ信号対を生成し、アナログ信号対の一方を選択的に1のピン40から出力することができます。そのため、例えば、1水平期間に、奇数列のピン40から交流駆動用のデータ信号DS(交流電圧信号)を、偶数列のピン40から直流駆動用のデータ信号DS(直流電圧信号)を出力させることができます。1のサブ画素に交流駆動される表示素子と直流駆動される表示素子とを組み込んだハイブリッド型表示パネルを、1種類のソースドライバIC200によって駆動することが可能である。したがって、ソースドライバIC200の提供により、ハイブリッド型表示装置の小型化、および製造コスト削減ができる。また、1水平期間に、全てのピン40から、直流駆動用または交流駆動用のデータ信号DSを出力できるため、ソースドライバIC200は液晶表示装置、およびEL表示装置を駆動することも可能であり、汎用性が高い。以下、図9-図16を参照して、ソースドライバIC200の構成例および動作例についてより詳細に説明する。

10

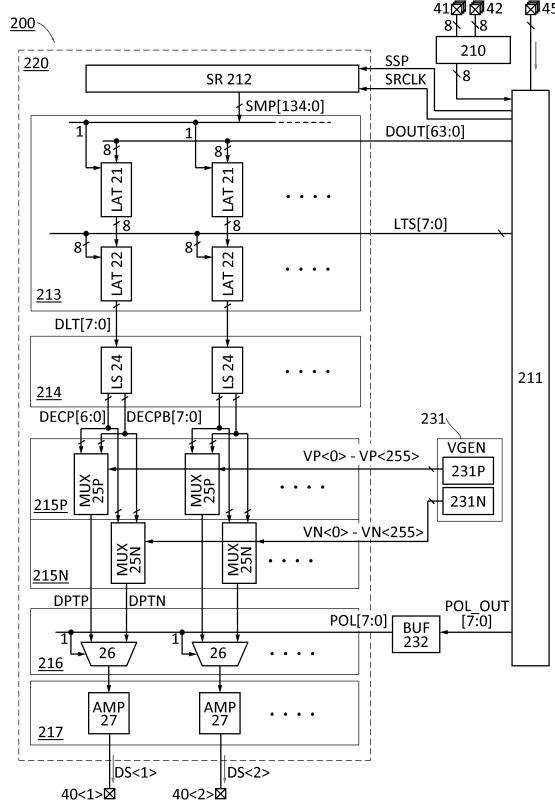

#### 【0094】

図9は、ソースドライバIC200の構成例を示すブロック図であり、回路220については、第1列、第2列の回路要素を代表的に示している。図9に示す複数のピン45は、ロジック回路211を制御するための制御信号の入力に用いられる。ここでは、ピン45はシングルエンド方式のデジタル信号の入力用端子である。ピン45は適宜設ければよい。例えば、ピン40の極性を設定するための制御信号をピン45から入力すればよい。これについては後述する。

20

#### 【0095】

##### (D-LAT213)

図9に示すように、D-LAT213は、列ごとに、LAT21、22を有する。LAT21、22はそれぞれ8ビットのデータを記憶できるラッチ回路である。信号SMP[134:0]の各1ビットで8のLAT21が制御される。LAT22は、対応する列のLAT21の出力信号をラッチする。LAT22から出力される信号DLT[7:0]は、LAT21が保持しているデータと同じ論理を持つ信号である。各LAT22には、ラッチ信号として信号LTS[7:0]が入力される。アクティブなラッチ信号が入力されることで、LAT22のデータが更新される。

30

#### 【0096】

なお、図9において、符号として用いられていないアラビア数字(1、8)は、信号のビット幅を表している。例えば、図9では、LAT21には、8ビットの信号DOOUTがロジック回路211から入力され、SR212からは1ビットの信号SMPが入力されることを示している。

40

#### 【0097】

##### (LS214)

LS214は、列ごとにLS24を有する。各列において、LS24は、信号DLT[7:0]をレベルシフトし、信号DEC\_P[7:0]、DEC\_P\_B[7:0]を生成する。信号DEC\_P[7:0]は信号DLT[7:0]と同じ論理を持ち、信号DEC\_P\_B[7:0]は信号DEC\_P[7:0]の反転信号である。なお、ここでは、信号DEC\_P[7:0]のうち、下位7ビットの信号DEC\_P[6:0]がPTL215P、215Nに出力される。なお、LS214の出力信号の構成は、D-A変換処理を行う回路の構成によって、適宜設定される。

50

**【0098】**

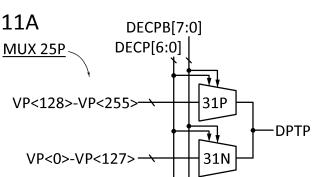

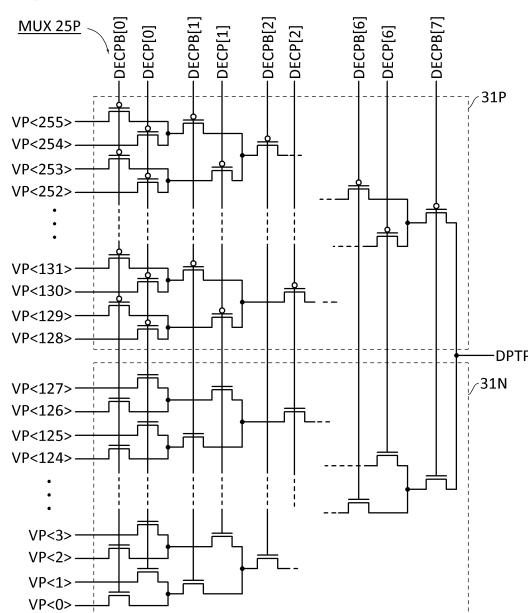

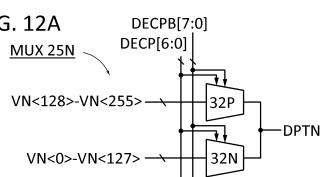

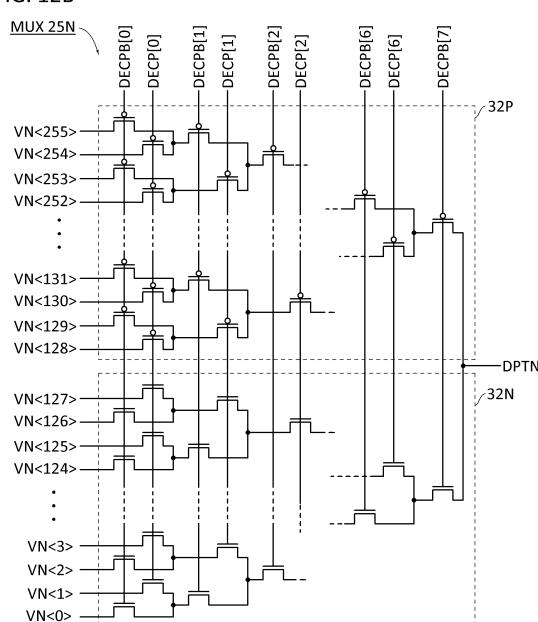

(PTL215P、215N)

PTL215Pは列ごとに、MUX25Pを有し、PTL215Nは列ごとにMUX25Nを有する。MUX25P、25Nは、それぞれ、LS24の出力信号をアナログ信号に変換する機能を有する。ここでは、MUX25Pは、信号DEC PB[7:0]をアナログ変換して、信号DPTPを生成し、MUX25Nは、信号DEC PB[7:0]をアナログ変換して、信号DPTNを生成する。信号DPTP、DPTNは階調データに対応する電圧を持つアナログ信号である。信号DPTPは正極性のデータ信号DSに対応し、信号DPTNは負極性のデータ信号DSに対応する。

**【0099】**

(MUX216、AMP217)

MUX216は列ごとに選択回路(SEL)26を有し、AMP217は列ごとにAMP27を有する。SEL26は、制御信号に従って、信号DPTP、DPTNの何れか一方をAMP27に出力する。信号POL[7:0]の何れか1ビットが制御信号として、SEL26に入力される。入力される1ビットの信号POLのデータが“1”であれば、SEL26は信号DPTPを出力し、データが“0”であれば、信号DPTNを出力する。

**【0100】**

SEL26の出力信号はAMP27で増幅され、出力される。信号DPTPをAMP27で増幅することで、正のデータ信号DSが得られ、信号DPTNをAMP27で増幅することで、負のデータ信号DSが得られる。つまり、信号DSの極性は、対応する列のSEL26を制御する信号POLのデータ(“0”/“1”)によって決定することができる。

**【0101】**

(VGEN231)

VGEN231は、VGEN231P、231Nを有する。VGEN231Pは電圧VP<0>-VP<255>を生成し、VGEN231Nは電圧VN<0>-VN<255>を生成する。電圧VP<0>-VP<255>はPTL215Pのデジタルーアナログ変換処理のための基準電圧であり、それぞれ、階調レベル0-255に対応する。電圧VN<0>-VN<255>はPTL215Nのデジタルーアナログ変換処理のための基準電圧であり、それぞれ、階調レベル0-255に対応する。

**【0102】**

電圧VP<255>は電圧VP<0>よりも大きく、電圧VN<255>は電圧VN<0>よりも小さい。例えば、電圧VP<0>、電圧VN<0>をそれぞれVCOM(LC素子DE1のコモン電圧)と同じ電圧とすることで、MUX25Pは電圧がVCOM以上のアナログ信号を生成でき、MUX25Nは、電圧がVCOM以下のアナログ信号を生成できる。

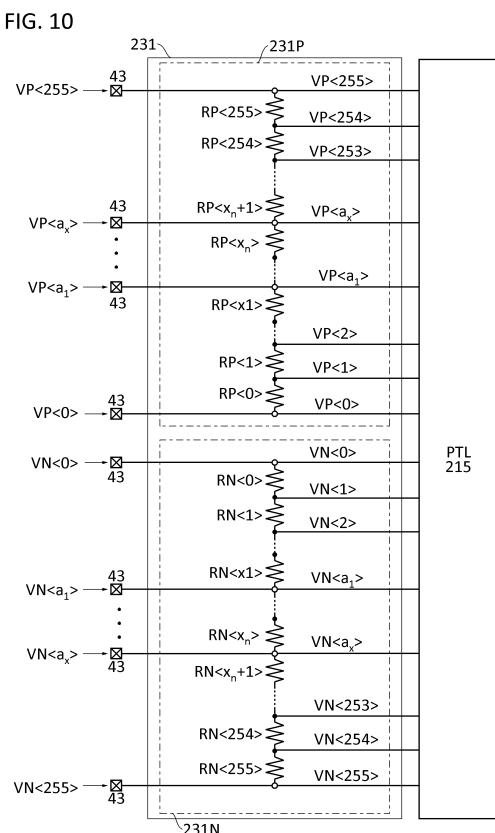

**【0103】**

&lt;デジタルーアナログ変換&gt;

図10 図12Bを参照して、PTL215P、215NのD-A変換機能を説明する。図10にVGEN231の構成例を示し、図11A、図11BにMUX25Pの構成例を示し、図12A、図12BにMUX25Nの構成例を示す。

**【0104】**

(VGEN231)

図10に示すようにVGEN231は2の抵抗分圧回路を含む。2の抵抗分圧回路のうち、一方がVGEN231Pであり、他方がVGEN231Nである。VGEN231に基づく電圧を供給するための複数のピン43が、ソースドライバIC200に設けられている。

**【0105】**

VGEN231Pは電圧VP<0>-VP<255>を生成するため、電気的に直列に接続された抵抗RP<0>-RP<255>を有する。

**【0106】**

電圧VP<0>、VP<255>はピン43から与えられる電圧である。電圧VP<0>

10

20

30

40

50

は抵抗 R P < 0 > に印加され、電圧 V P < 2 2 5 > は抵抗 R P < 2 5 5 > に印加される。ここでは、電圧 V P < 0 > - V P < 2 5 5 > が液晶のガンマ特性（駆動電圧 透過率特性）に適するように、抵抗 R P < 0 > - R P < 2 5 5 > の抵抗値が設定される。かつ、電圧 V P < 1 > - V P < 2 5 4 > のうちの複数の電圧（例えば、V P < a 1 >、V P < a x >など）がピン 4 3 から与えられる。ピン 4 3 に入力する基準電圧を調節することによって、L C 素子 D E 1 により適したガンマ補正が行える。

#### 【 0 1 0 7 】

V G E N 2 3 1 N は、電圧 V N < 0 > - V N < 2 5 5 > を生成するため、電気的に直列に接続された抵抗 R N < 0 > - R N < 2 5 5 > を有する。V G E N 2 3 1 N は V G E N 2 3 1 P と同様の回路構成を持つため、V G E N 2 3 1 N については、V G E N 2 3 1 P の説明を参照する。10

#### 【 0 1 0 8 】

( M U X 2 5 P、 2 5 N )

図 1 1 A に示すように、M U X 2 5 P は M U X 3 1 P、3 1 N を有する。M U X 3 1 P、3 1 N は、それぞれ 1 2 8 入力 1 出力のマルチプレクサである。信号 D E C P B [ 7 : 0 ]、D E C P [ 6 : 0 ] は、M U X 3 1 P、3 1 N の制御信号である。これら信号によつて、M U X 3 1 P または M U X 3 1 N の何れか一方の出力信号が信号 D P T P として M U X 2 5 P の出力端子から出力される。

#### 【 0 1 0 9 】

図 1 1 B に示すように、M U X 3 1 P は p チャネル型トランジスタでなるパストランジスタロジック回路であり、M U X 3 1 N は n チャネル型トランジスタでなるパストランジスタロジック回路である。M U X 3 1 P の 1 2 8 の入力端子には電圧 V P < 1 2 8 > - V P < 2 5 5 > がそれぞれ入力され、M U X 3 1 N の 1 2 8 の入力端子には電圧 V P < 0 > - V P < 1 2 7 > がそれぞれ入力される。20

#### 【 0 1 1 0 】

図 1 2 A に示すように、M U X 2 5 N は M U X 3 2 P、3 2 N を有する。M U X 3 2 P、3 2 N は、それぞれ 1 2 8 入力 1 出力のマルチプレクサであり、M U X 3 1 P、3 1 N と同様の回路構成を有する。M U X 3 2 P の 1 2 8 の入力端子には電圧 V N < 1 2 8 > - V N < 2 5 5 > がそれぞれ入力され、M U X 3 2 N の 1 2 8 の入力端子には電圧 V N < 0 > - V N < 1 2 7 > がそれぞれ入力される。30

#### 【 0 1 1 1 】

例えば、信号 D L T [ 7 : 0 ] のデータが 8 ' h 2 であれば、つまり、信号 D E C P B [ 7 : 0 ] のデータが “ 1 1 1 1 1 1 0 1 ” であれば、M U X 2 5 P は電圧 V P < 2 > を出力し、M U X 2 5 N は電圧 V N < 2 > を出力する。つまり、M U X 2 5 P は、L A T 2 2 が保持している階調データに対応する正極性のアナログ電圧を出力する。このように、M U X 2 5 P はデコーダとして機能しており、階調データをデコードし、階調データに対応する正極性のアナログ電圧を生成する。M U X 2 5 N も同様であり、階調データをデコードし、負極性のアナログ電圧を生成する機能を有する。

#### 【 0 1 1 2 】

<< ピンの極性の制御 >>

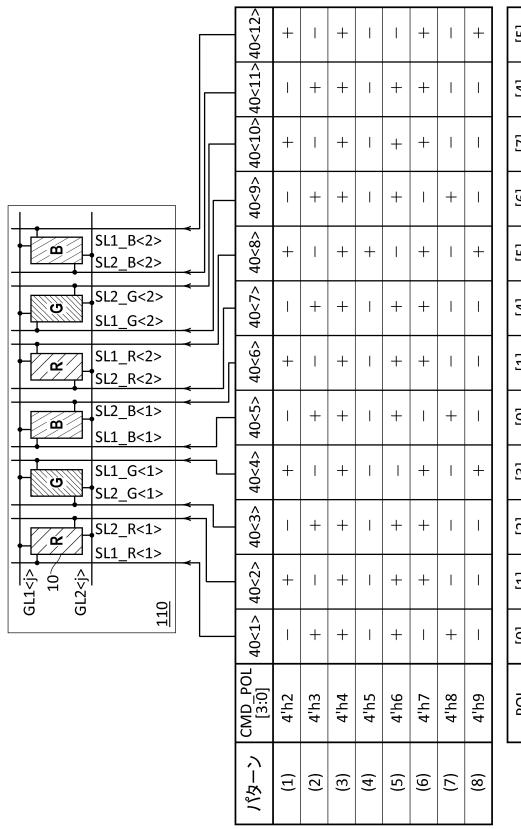

表示パネル 1 6 0 の画素が 3 ( R G B ) のサブ画素 1 0 で構成される場合は、ピン 4 0 < 1 > - 4 0 < 1 0 8 0 > の極性は、1 2 ( 3 ( R G B ) × 2 ( S L 1、S L 2 ) × 2 ( 正負の極性 ) ) 周期で変化する。そこで、ここでは、1 2 のピン 4 0 < 1 > - 4 0 < 1 2 > に着目して、コマンド信号によるピン 4 0 の極性の制御について説明する。図 1 3 には、信号 C M D \_ P O L のデータとピン 4 0 < 1 > - 4 0 < 1 2 > の極性との関係、ピン 4 0 < 1 > - 4 0 < 1 2 > と信号 P O L [ 7 : 0 ] のビットとの対応を示している。例えば、ピン 4 0 < 1 > の極性を制御するために、信号 P O L [ 0 ] が第 1 列の S E L 2 6 に入力されることを示している。40

#### 【 0 1 1 3 】

また、図 1 3 には、ピン 4 0 < 1 > - 4 0 < 1 2 > と、表示パネル 1 6 0 の配線 S L 1、

50

S L 2との接続構造の一例を示す。図13に示すように、ピン40<1>、40<4>、40<5>は、第1列の単位画素を駆動するための配線S L 1\_R<1>、S L 1\_G<1>、S L 1\_B<1>とそれぞれ電気的に接続されている。ピン40<2>、40<3>、40<6>は、第1列の画素を駆動するための配線S L 2\_R<1>、S L 2\_G<1>、S L 2\_B<1>とそれぞれ接続されている。同様に、ピン40<7>-40<12>は第2列の画素を駆動するための配線S L 1または配線S L 2と電気的に接続されている。

#### 【0114】

ピン40<1>-40<12>に接続されるソース線の属性（例えば、駆動する表示素子の種類、色）などを考慮して、ピン40<1>-40<12>の極性が設定される。10 ここでは、ピン40<1>-40<12>の極性パターンは8通りある。便宜上、これら8の極性パターンをパターン(1)-(8)と呼ぶこととする。信号CMD\_POL[4:0]によって、ピン40<1>-40<12>の極性は、パターン(1)-(8)の何れか1に設定される。例えば、信号CMD\_POLのデータが4'h5（“0101”）であれば、ピン40<1>-40<12>からは、正の極性のデータ信号DS<1>-DS<12>が出力されることとなる。ここでは、極性パターンを設定するコマンド信号(CMD\_POL)のデータ幅は4ビットであるが、これは、ロジック回路211が設定可能な極性パターンの数によって決定すればよい。

#### 【0115】

パターン(1)、(2)はLC表示パネル用の極性パターンである。1フレーム期間ごとに、信号CMD\_POLのデータを“0010”(4'h2)と“0011”(4'h3)とで切り替えると、駆動方式はソースライン反転方式となり、このデータの切り替えを1水平期間ごとに行うと、駆動方式はドット反転方式となる。20

#### 【0116】

パターン(3)、(4)は、EL表示パネル用の極性パターンである。パターン(3)は、画素電極がEL素子のアノードを構成しているときのパターンであり、パターン(4)は、画素電極がEL素子のカソードを構成しているときのパターンである。

#### 【0117】

パターン(5)-(8)は、ハイブリッド表示パネル用の極性パターンである。パターン(5)、(6)では、配線S L 2に入力されるデータ信号の極性は正であり、パターン(7)、(8)では、それが負である。30

#### 【0118】

例えば、1フレーム期間ごとに、信号CMD\_POL[3:0]のデータを4'h6と4'h7とで切り替えると、LC素子DE1の駆動方式はソースライン反転方式となり、EL素子DE2には正のデータ信号が書き込まれる。また、このようなデータの切り替えを1水平期間ごとに行うと、LC素子DE1の駆動方式はドット反転方式となる。

#### 【0119】

以上述べたように、ソースドライバIC200は、3種類の表示パネルを駆動することが可能であり、汎用性の高いソースドライバICである。

#### 【0120】

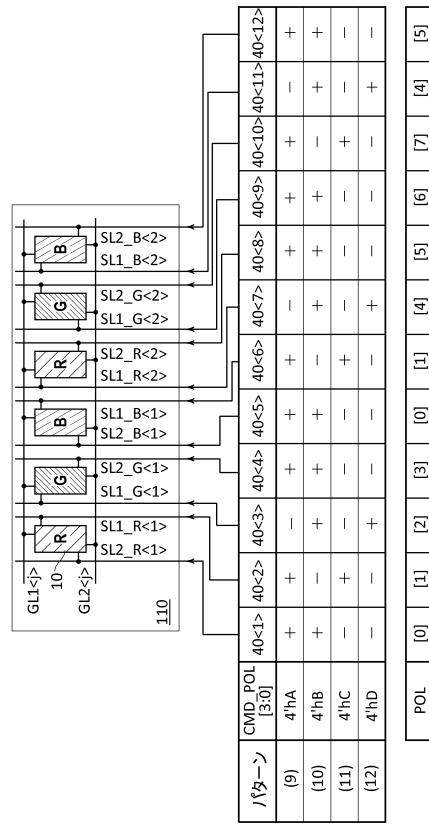

極性パターンは図13の例に限定されない。上述したように、ピン40<1>-40<12>に接続されるソース線の属性などを考慮して、ピン40<1>-40<12>の極性パターンが設定される。よって、例えば、配線S L 1、S L 2が図14に示すように配置しているハイブリッド表示パネルを駆動するためには、パターン(9)-(12)を設定すればよい。40

#### 【0121】

信号CMD\_POL[3:0]による極性パターンの設定とは、より具体的には、信号CMD\_POL[3:0]のデータに従って、ロジック回路211が信号POL\_OUT[7:0]のデータを設定することである。例えば、信号CMD\_POL[3:0]のデータが4'h7であれば、ロジック回路211は、データ“011110110”をもつ信号P50

`OL_OUT[7:0]` を生成する。

#### 【0122】

ここでは、パターン(1)-(12)に対して4対のピン40が同じ極性を持つため、8ビットの信号`POL_OUT`によって、12のピン40の極性パターンを設定することができる。なお、信号`POL_OUT`のデータ幅は8ビットに限らず、例えば、12ビットとしてもよい。信号`POL_OUT`のデータ幅を12ビットとすることで、信号`POL`を伝送するための配線、およびロジック回路211の素子数が増加してしまうが、ピン40<1>-40<12>の極性を独立して制御できるため、ピン40<1>-40<12>の極性パターンの冗長性が増す。そのため、ソースドライバ`IC200`が駆動できる画素部の仕様の制約が少なくなるので、ソースドライバ`IC200`の汎用性が向上する。

10

#### 【0123】

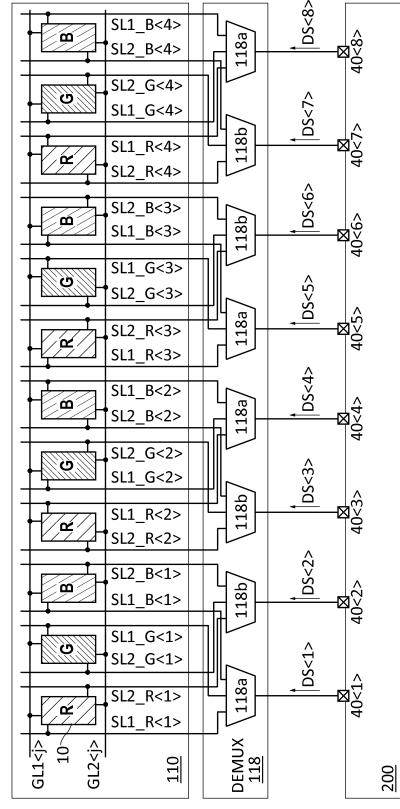

図13、図14の例では、1のピン40は、画素部110の特定の1本のソース線（配線`SL1`または配線`SL2`）に電気的に接続されている。そのため、表示パネル160の端子部173には、少なくとも配線`SL1`と配線`SL2`の総数の端子を設ける必要がある。例えば、周辺回路112にデマルチプレクサ(`DEMUX`)を設けることで、端子部173の端子の数を低減することができる。図15、図16に`DEMUX`の構成例を示す。

#### 【0124】

図15に示す`DEMUX117`は、複数の回路117aを有する。回路117aは、1入力2出力`DEMUX`として機能する。外部から入力される制御信号に従い、回路117aはピン40から出力されるデータ信号`DS`を、何れか一方の出力端子から出力する。

20

#### 【0125】

`DEMUX117`を構成するトランジスタ等の素子は、画素部110と共に、トランジスタ層163に作製される。`DEMUX117`を設けることで、端子部173の端子数を低減できる。また、図15に示すように、12のピン40から出力される信号`DS`によって、4列の画素を駆動することができる。

#### 【0126】

図15の例では、1水平期間において、データ信号`DS`を書き込むタイミングを配線`SL1`と配線`SL2`とで異ならせればよい。そのため、表示パネル160がハイブリッド表示パネルであるが、パターン(5)-(12)は用いられない。例えば、データ信号`DS`を、まず配線`SL1`に書き込み、次に配線`SL2`に書き込む。具体的には、次のようにピン40の極性パターンを制御すればよい。1水平期間において、データが4'h2である信号`CMD_POL[3:0]`をソースドライバ`IC200`に入力し、各ピン40から交流駆動用のデータ信号`DS`を出力させる。次に、所定のタイミングで、データが4'h4である信号`CMD_POL[3:0]`をソースドライバ`IC200`に入力し、各ピン40から直流駆動用のデータ信号`DS`を出力させる。

30

#### 【0127】

図16に示す`DEMUX118`は複数の回路118a、118bを有する。なお、図16には、`DEMUX118`とピン40<1>-40<8>との接続関係を示している。

#### 【0128】

回路118aは1入力3出力の`DEMUX`として機能する。外部から入力される制御信号に従い、各回路118aはピン40から出力される信号`DS`を何れか1の出力端子から出力する。回路118bは回路118aと同じ回路構成を持ち、同様に機能する。ここでは、回路118aは、1画素の3の配線`SL1`(`SL1_R`、`SL1_B`、`SL1_G`)の何れか1を選択し、ピン40と電気的に接続する機能を有する。回路118bは、1画素の3の配線`SL2`(`SL2_R`、`SL2_B`、`SL2_G`)の何れか1を選択し、ピン40と電気的に接続する機能を有する。`DEMUX118`を設けることで、2つのピン40から出力される信号`DS`によって、1列の画素を駆動できる。

40

#### 【0129】

パターン(1)-(12)の設定は、ピン41、42から入力される差動方式のコマンド信号によって行っているが、これに限らない。例えば、極性パターンを制御するためのシ

50

ングルエンド方式のデジタル信号を、1または複数のピン45からロジック回路211に入力するようにしてもよい。極性パターン制御に用いられるデジタル信号のデータ幅が4ビットであれば、4のピン45が極性パターンを制御するためのデジタル信号の入力用ピンに用いられる。

#### 【0130】

このような場合、コマンド信号として、信号CMD\_POLを有効にするか、無効にするかを決定するための信号CMD\_SWを用いる。期間T1において信号CMD\_SWは信号CMD\_POLよりも先にピン41、42に入力される。信号CMD\_SWによって、信号CMD\_POLが無効とされた場合、ロジック回路211は、ピン45から入力されるデジタル信号のデータに基づいて、信号POL\_OUT[7:0]を生成する。

10

#### 【0131】

以上述べたように、ソースドライバIC200は、様々な構成の表示パネルを駆動することができる汎用性の高いドライバICである。

#### 【0132】

<< ドライバIC >>

以上では、表示パネルの周辺回路にソースドライバIC200を適用した例を説明したが、周辺回路112に適用できるドライバICは、ソースドライバICに限定されない。例えば、ゲートドライバ121、122をそれぞれ、ゲートドライバICで構成してもよい。以下、図17を用いて、周辺回路112に適用できるドライバICの幾つかの例を示す。

20

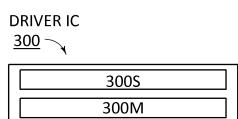

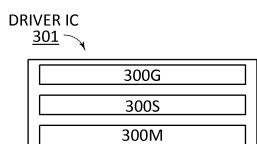

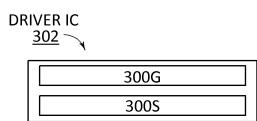

#### 【0133】

図17Aに示すドライバIC300はソースドライバIC200の変形例であって、ソースドライバに回路300Mを追加したドライバICである。回路300Sがソースドライバであり、ソースドライバIC200の内部回路と同様の回路構成を有する。回路300Mは、画素部114から入力されるアナログ信号を処理する信号処理回路であり、信号処理回路124の機能を備える。ドライバIC300は、画素部114(図6)のソースドライバに好適である。

#### 【0134】

また、ドライバIC300にゲートドライバを組み込んでもよい。そのような例を図17Bに示す。図17Bに示すドライバIC301は、回路300S、300M、300Gを有する。回路300Gはゲートドライバである。例えば、画素部114を駆動するために2のドライバIC301を用いる場合、一方のドライバIC301の回路300Gをゲートドライバ121として動作させ、他方のドライバIC301の回路300Gをゲートドライバ122として動作させればよい。画素部114の列数に応じて、ドライバIC302とドライバIC300の両方を用いればよい。

30

#### 【0135】

また、画素部110を駆動するドライバICには、回路300Mを設けていないドライバIC302(図17C)を用いればよい。画素部110の列数に応じて、画素部110を駆動するドライバICには、ドライバIC302だけでなく、ソースドライバIC200を用いればよい。画素部110を駆動するために2のドライバIC302を用いる場合、一方のドライバIC302の回路300Gをゲートドライバ121として動作させ、他方のドライバIC302の回路300Gをゲートドライバ122として動作させればよい。

40

#### 【0136】

<< 表示モード >>

表示装置100は3の表示モードを有することができる。第1の表示モードはLC素子DE1とEL素子DE2双方によって表示を行うモード(ハイブリッドモード)である。第2はLC素子DE1のみで表示を行うモード(LCモード)であり、第3はEL素子DE2のみで表示を行うモード(ELモード)である。図3に示す表示モジュール150の表示原理によれば、LCモードは反射モードと呼ぶことができ、ELモードは自発光モードまたは、透過モードと呼ぶことができる。ここでも、ピン40<1>-40<12>に着目して、各表示モードにおける表示装置100の動作について説明する。

50

**【 0 1 3 7 】**

表示モードの決定は、例えば、制御回路 131 で行うことができる。制御回路 131 は、センサ 135 の検知信号や、使用者の操作等に基づくプロセッサ 130 の割り込み信号等によって表示モードを決定する。例えば、明るい環境（例えば、晴天の昼間の屋外）では表示モードは LC モードに設定され、暗い環境（例えば、夜間の屋外）では EL モードに設定される。外光の照度が低い環境（例えば、照明器具で照明された室内、曇天の屋外）、つまり LC 素子 DE1 での反射光のみでは、良好な表示品位が得られないような環境では表示モードはハイブリッドモードに設定される。

**【 0 1 3 8 】**

また、制御回路 131 は、決定した表示モードを実行するため、画像プロセッサ 132 に制御信号を送信する。画像プロセッサ 132 は、制御信号に従い、表示モードおよび駆動する表示パネルの構造に応じたコマンド信号、および、画像信号を生成する。以下では、ピン 40<1> - 40<12> と配線 SL1、SL2 の接続構造が図 13 に示す接続構造である場合を例に、各表示モードを説明する。

10

**【 0 1 3 9 】**

## &lt; LC モード &gt;

LC モードが設定された場合、EL 素子 DE2 を発光させないデータ信号 DS を配線 SL2 に入力すればよい。別言すると、EL 素子 DE2 が黒表示を行うためのデータ信号 DS を配線 SL2 に入力する。そのため、ピン 40<2>、40<3>、40<6>、40<7>、40<10>、40<11> からは、階調レベルが 0 のデータ信号 DS がそれぞれ出力される。

20

**【 0 1 4 0 】**

## &lt; EL モード &gt;

EL モードが設定された場合、LC 素子 DE1 が黒表示を行うためのデータ信号 DS を配線 SL2 に入力する。そのため、ピン 40<1>、40<4>、40<5>、40<8>、40<9>、40<12> からは、階調レベルが 0 (ノーマリブラックの場合)、または 255 (ノーマリホワイトの場合) のデータ信号 DS がそれぞれ出力される。

**【 0 1 4 1 】**

## &lt; ハイブリッドモード &gt;

画素部 110 の構造上、各サブ画素 10 において LC 素子 DE1 と EL 素子 DE2 とは共通の画像データに由来するアナログ信号が入力される。VGEN231 は、LC 素子 DE1 の駆動に適したアナログ電圧を生成している。そのため、同じ PTL215 で、第 1 列の MUX25N, MUX25P と、第 2 列の MUX25N, 25P で、同じ階調レベルの信号 DEC\_P[7:0] をアナログ変換した場合、サブ画素 10R<j, 1> では、EL 素子 DE2 が適切な輝度で発光できない場合があり、表示装置 100 の表示品位が劣化してしまう。このような不具合を解消するため、配線 SL2 に接続されるピン 40 が存在する列、ここでは、列番号 2、3、4、7、10、11 の LAT21 に格納されるデータ信号が、EL 素子 DE2 に適した階調レベルをもつようとする。

30

**【 0 1 4 2 】**

## (階調変換処理)

そのため、画像プロセッサ 132 において、画像信号 DP[7:0]、DN[7:0] を生成するための処理の 1 つとして、画像信号の階調レベルを変更する処理を行えばよい。例えば、LC 素子 DE1 用の階調レベルと EL 素子 DE2 用の階調レベルとの対応を示す階調変換テーブルを画像プロセッサ 132 に記憶させておき、階調変換テーブルを参照することで、EL 素子 DE2 のデータ信号 DS に対応する画像信号 DP[7:0]、DN[7:0] の階調レベルを変換すればよい。

40

**【 0 1 4 3 】**

また、ハイブリッドモードでは、サブ画素 10 の輝度は、LC 素子 DE1 による外光 5 の反射光の輝度と、EL 素子 DE2 の発光の輝度とで決定される。使用環境の明るさに応じてサブ画素 10 の輝度を調節することで、表示装置 100 の表示品位の向上と、消費電力

50

の低減が図れる。そのため、センサ 135 の検知信号に基づいて、EL 素子 DE2 の輝度を調節するようすればよい。例えば、使用環境の照度に応じた複数の階調変換テーブルを画像プロセッサ 132 に設け、センサ 135 の検知信号によって、参照する階調変換テーブルを決定すればよい。

#### 【0144】

もちろん、ハイブリッドモードでの階調変換処理において、LC 素子 DE1 のデータ信号 DS に対応する画像信号 DP [7:0]、DN [7:0] の階調レベルを調節してもよい。また、LC モード用、EL モード用にそれぞれ 1 又は複数の階調変換テーブルを用意し、それぞれのモードにおいて、画像プロセッサ 132 で階調変換処理を行うようにすることもできる。EL モードは、使用環境が暗い場合に実行される表示モードであるので、ハイブリッドモードよりも EL 素子 DE2 の輝度を低くすることができます。そのため、階調変換処理は EL 素子 DE2 の長寿命化に有効である。

10

#### 【0145】

したがって、表示装置 100 の表示品位の向上、省電力化、EL 素子 DE2 の長寿命化等のため、表示色、表示素子の種類、表示モード、および使用環境の照度等を考慮して、階調変換テーブルの数、そのデータ構造を決定すればよい。表示装置 100 の表示モード、または照度に応じて、画像プロセッサ 132 が参照する階調変換テーブルが決定される。

#### 【0146】

ここでは、画像信号の階調レベルを変更する信号処理の一例として、階調変換テーブルを用いた処理を説明したが、もちろん信号処理の方法はこれに限定されない。また、センサ 135 に、外光 5 の色温度を検出するセンサを設けてもよい。これにより、環境の照度および色温度に応じて、画像信号の階調レベルを調節することが可能になる。

20

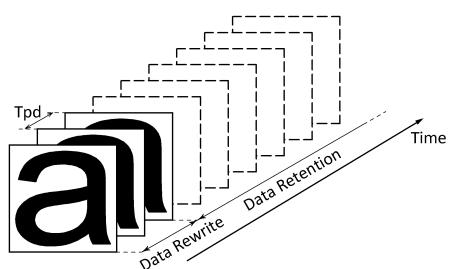

#### 【0147】

##### (IDS 駆動)

静止画は、フレームごとの画像信号のデータに変化がないため、1 フレームごとに、サブ画素 10、特にサブ画素 11 のデータの書き換えを行なう必要がない。そこで、LC モードで静止画を表示する際は、1 フレーム期間よりも長い時間、サブ画素 11 のデータの書き換えを一時的に停止するような駆動方法を実行させてもよい。ここでは、このような駆動方法を、「アイドリング・ストップ (IDS) 駆動」と呼ぶこととする。

30

#### 【0148】

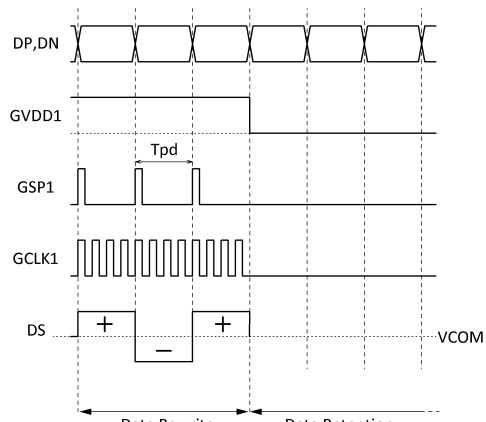

図 18A は、IDS 駆動による静止画の表示方法を説明する図である。図 18B は IDS 駆動方法の一例を示すタイミングチャートである。図 18B において、GVD1 はゲートドライバ 121 の高電源電圧であり、信号 GSP1、GCLK1 は、それぞれ、ゲートドライバ 121 に入力されるスタートパルス信号、クロック信号である。

#### 【0149】

通常の駆動方法では、1 フレーム期間 (期間 Tpd) ごとに、サブ画素 11 のデータの書き換えが行われる。信号 GSP1 の入力をトリガーにして、ゲートドライバ 121 は、信号 GCLK1 に従い配線 GL1 を選択するゲート信号を生成し、配線 GL1 に出力する。ソースドライバ IC200 は、信号 RES の入力をトリガーに、画像信号 DP、DN から信号 DS を生成し、配線 SL1 に出力する。

40

#### 【0150】

図 18A、図 18B に示すように、IDS 駆動による処理は、データの書き換え処理（または、書き込み処理とも呼ぶこともできる。）と、データ保持に分かれる。まず、通常駆動と同じリフレッシュレートで、データの書き換えが 1 回または複数回実行され、サブ画素 11 にデータが書き込まれる。図 18A、図 18B は、書き換え回数は 3 回の例である。データ書き込みの後、ゲートドライバ 121 では、配線 GL1 用のゲート信号の生成を停止し、サブ画素 11 のデータの書き換えを停止する。また、データ保持期間にゲートドライバ 121 への GVD1 の供給を停止することで、表示装置 100 の消費電力を削減できる。

#### 【0151】

50

データ書き換え処理でのデータ書き換え回数は、リフレッシュレート等を考慮して設定すればよい。また、IDS 駆動におけるデータ保持時間は、液晶の焼き付きを考慮し、最長 1 秒間とし、0.5 秒以下、または 0.2 秒以下程度とすることが好ましい。

#### 【0152】

また、IDS 駆動でも通常駆動と同じ表示品位を保つために、容量素子 CS1 からの電荷のリークをできるだけ少なくすることが望ましい。電荷がリークしてしまうと、LC 素子 DE1 に印加される電圧が変動して、サブ画素 11 の透過率が変化してしまうからである。そのため、トランジスタ M1 にはオフ電流が小さいトランジスタであることが好ましい。そのようなトランジスタには、チャネルが酸化物半導体で形成されているトランジスタ（以下、OS トランジスタと呼ぶ。）がある。OS トランジスタが Si トランジスタよりもオフ電流が小さいのは、酸化物半導体のバンドギャップが Si、Ge よりも広い（3.0 eV 以上）であるからである。10

#### 【0153】

OS トランジスタの半導体層を形成する酸化物には、In - Sn - Ga - Zn 酸化物、In - Ga - Zn 酸化物、In - Sn - Zn 酸化物、In - Al - Zn 酸化物、Sn - Ga - Zn 酸化物、Al - Ga - Zn 酸化物、Sn - Al - Zn 酸化物、In - Zn 酸化物、Sn - Zn 酸化物、Al - Zn 酸化物、Zn - Mg 酸化物、Sn - Mg 酸化物、In - Mg 酸化物や、In - Ga 酸化物、In 酸化物、Sn 酸化物、Zn 酸化物等の金属酸化物を用いることができる。また、これら金属酸化物に、他の材料、例えば、SiO<sub>2</sub> を含ませてもよい。OS トランジスタの酸化物半導体は、In、Zn の少なくとも一方を含むものが好ましい。20

#### 【0154】

電子供与体（ドナー）となる水分または水素等の不純物を低減し、かつ酸素欠損も低減することで、酸化物半導体を i 型（真性半導体）にする、あるいは i 型に限りなく近づけることができる。ここでは、このような酸化物半導体を高純度化酸化物半導体と呼ぶことにする。高純度化酸化物半導体でチャネルを形成することで、チャネル幅で規格化された OS トランジスタのオフ電流を数 yA / μm 以上数 zA / μm 以下程度に低くすることができます。

#### 【0155】

OS トランジスタのオフ電流が極めて小さいのは、金属酸化物でなる半導体のバンドギャップが 3.0 eV 以上であるからである。チャネル形成領域に金属酸化物を有するため OS トランジスタは、熱励起によるリーク電流が小さく、またオフ電流が極めて小さい。30

#### 【0156】

OS トランジスタに好適な酸化物半導体は、二次イオン質量分析法（SIMS）により得られる水素濃度が、2 × 10<sup>20</sup> atoms / cm<sup>3</sup> 以下であり、好ましくは 5 × 10<sup>19</sup> atoms / cm<sup>3</sup> 以下、より好ましくは 1 × 10<sup>19</sup> atoms / cm<sup>3</sup> 以下、より好ましくは 5 × 10<sup>18</sup> atoms / cm<sup>3</sup> 未満、より好ましくは 1 × 10<sup>18</sup> atoms / cm<sup>3</sup> 以下、さらに好ましくは 1 × 10<sup>16</sup> atoms / cm<sup>3</sup> 以下である酸化物半導体である。

#### 【0157】

IDS 駆動で静止画表示を行う表示装置 100 の好適な用途としては、電子書籍を読む、デジタルカメラで撮影した写真を鑑賞する、等である。つまり、同じ画面である状態が比較的長く、また使用者の操作により画面全体の表示を切り換えることで、表示装置 100 を使用する場合に、IDS 駆動で静止画を表示することが好ましい。また IDS 駆動では、画面の切り替え回数を減らすことができるため、画面の切り替え時によるちらつきの低減に効果的である。40

#### 【0158】

また、IDS 駆動は、LC モードだけでなくハイブリッドモードでも実行することができる。ハイブリッドモードにおいて、静止画を表示する場合は、サブ画素 12 はフレーム期間ごとにデータを書き換え、サブ画素 11 は IDS 駆動でデータを書き換えればよい。

10

20

30

40

50

**【 0 1 5 9 】**

表示装置 100 は、使用環境の照度に応じた 3 つの表示モード（LC、EL、ハイブリッド）を持つため、気象（晴天、雨天、曇天）、時間（昼、夜）等に制約されず、高品質（高コントラスト、高い色再現性）の表示が可能である。そのため、様々な場所で利用される携帯型の電子機器の表示部に好適である。また、実施の形態 1 の表示装置は消費電力を低減できるため、バッテリで動作する電子機器の使用時間を長くすることができますことも、理由の一つである。

**【 0 1 6 0 】**

もちろん、表示装置 100 は、携帯型電子機器に限らず、様々な電子機器の表示部に適用することができる。実施の形態 2 において、表示装置 100 が適用可能な電子機器の幾つかの具体例を示す。10

**【 0 1 6 1 】****[ 実施の形態 2 ]**

本実施の形態では、表示部を備えた電子機器等について説明する。

**【 0 1 6 2 】**

電子機器としては、例えば、テレビジョン装置（テレビ、又はテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。可携性の電子機器は、家屋やビルなどの建築物の内壁もしくは外壁、又は、自動車の内装もしくは外装の曲面に沿って組み込むことも可能である。図 19 A 図 21 B に電子機器の構成例を示す。図 19 A 図 21 B に示す電子機器の表示部には、実施の形態 1 の表示装置、およびこの表示装置にタッチセンサを設けたタッチパネルを適用することができる。20

**【 0 1 6 3 】**

図 19 A に示す情報端末 2010 は、筐体 2011 に組み込まれた表示部 2012 の他、操作ボタン 2013、外部接続ポート 2014、スピーカ 2015、マイクロフォン 2016 を有する。ここでは、表示部 2012 の表示領域は、湾曲している。情報端末 2010 は、バッテリで駆動する携帯型情報端末であり、タブレット型情報端末、あるいはスマートフォンとして使用することができる。情報端末 2010 は、電話、電子メール、手帳、インターネット接続、音楽再生等の機能を有する。指などで表示部 2012 に触ることで、情報を入力することができる。また、電話を掛ける、或いは文字を入力するなどの操作は、指などで表示部 2012 に触れることにより行うことができる。また、マイクロフォン 2016 から音声を入力することで、情報端末 2010 を操作することもできる。また、操作ボタン 2013 の操作により、電源のオン／オフ動作や、表示部 2012 の画面切り替え動作などを行うことができる。例えば、メール作成画面から、メインメニュー画面に切り替えることができる。30

**【 0 1 6 4 】**

図 19 B に腕時計型の情報端末の一例を示す。情報端末 2030 は、筐体 2031、表示部 2032、リュウズ 2033、ベルト 2034、検知部 2035 を有する。リュウズ 2033 を回転することで情報端末 2030 を操作することができる。また、表示部 2032 にタッチパネルを設けてもよい。これにより、表示部 2032 を指で触ることで、情報端末 2030 を操作することができる。40

**【 0 1 6 5 】**

検知部 2035 は、使用環境の情報や、使用者生体情報を取得する機能を備える。検知部 2035 は少なくとも照度センサを備えている。その他に、マイクロフォン、撮像素子、加速度センサ、方位センサ、圧力センサ、温度センサ、湿度センサ、測位センサ（例えば、GPS（全地球測位システム））等を検知部 2035 に設けてもよい。

**【 0 1 6 6 】**

情報端末 2010 および情報端末 2030 に同じ規格の無線通信装置を組み込み、無線 2020 により双方向の通信を行うようにしてもよい。このようにすることで、例えば、情50

報端末 2010 が電子メールや電話などを着信すると、情報端末 2030 の表示部 2032 に着信を知らせる情報を表示させることができる。

【0167】

図 19C に示すノート型パーソナルコンピュータ 2050 は、筐体 2051、表示部 2052、キーボード 2053、ポインティングデバイス 2054 を有する。

【0168】

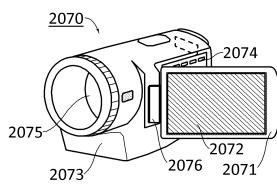

図 19D に示すビデオカメラ 2070 は、筐体 2071、表示部 2072、筐体 2073、操作キー 2074、レンズ 2075、接続部 2076 を有する。表示部 2072 は筐体 2071 に設けられ、操作キー 2074 およびレンズ 2075 は筐体 2073 に設けられている。筐体 2071 と筐体 2073 とは、接続部 2076 により接続されており、筐体 2071 と筐体 2073 間の角度は、接続部 2076 により変更が可能である。接続部 2076 における筐体 2071 と筐体 2073 間の角度に従って、表示部 2072 の映像を切り替える構成としてもよい。10

【0169】

図 19E に示す表示装置 2090 は、筐体 2091、表示部 2092、支持台 2093 等を有する。表示装置 2090 は、コンピュータ、遊技機等のモニタとして用いることができる。表示装置 2090 にテレビジョン放送の受信装置を組み込むことで、表示装置 2090 をテレビ受像（TV）装置として動作させることができる。

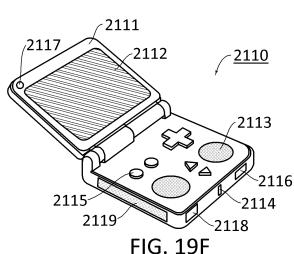

【0170】

図 19F に示す携帯型遊技機 2110 は、筐体 2111、表示部 2112、スピーカ 2113、LED ランプ 2114、操作キー 2115、接続端子 2116、カメラ 2117、マイクロフォン 2118、記録媒体読込部 2119 を有する。20

【0171】

図 20A に示す情報端末 2130 は、筐体 2131、表示部 2132 を有する。情報端末 2130 はバッテリで駆動する携帯型情報端末であり、スマートフォン、タブレット型情報端末等として用いることができる。情報端末 2130 は、電話、電子メール、手帳、インターネット接続、音楽再生等の機能を有する。表示部 2132 が湾曲しているため、情報端末 2130 は 3 面以上に情報を表示することができる。ここでは、情報 2141 - 2143 が表示部 2132 の異なる面に表示されている。例えば、使用者は、衣服の胸ポケットに情報端末 2130 を収納した状態で、表示部 2132 の上端部の表示（ここでは情報 2142）を確認することができる。そのため使用者は、情報端末 2130 を胸ポケットから取り出さなくても、情報 2142 を確認して、電話を受けるか否かを判断できる。30

【0172】

情報 2141 - 2143 としては、例えば、SNS（ソーシャル・ネットワーキング・サービス）の通知、電子メールや電話などの着信を知らせる表示、電子メールなどの題名、電子メールなどの送信者名、日付、時刻、バッテリの残量、アンテナ受信の強度などがある。

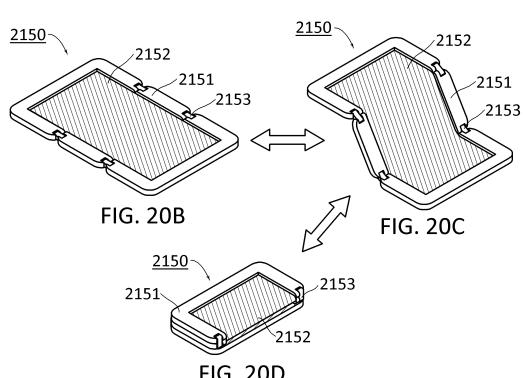

【0173】

図 20B に、折りたたみ可能な情報端末の構成例を示す。図 20B に示す情報端末 2150 は、筐体 2151、表示部 2152、ヒンジ 2153 を有する。情報端末 2150 も携帯型情報端末であり、情報端末 2130 と同様の機能を有する。図 20B は、展開された状態の情報端末 2150 を示している。図 20D は、折りたたんだ状態の情報端末 2150 を示す。図 20C の情報端末 2150 の状態は、展開中の状態、あるいは折り畳み中の状態である。折りたたむことで情報端末 2150 の携帯性が向上し、展開することで、広い表示画面を得られるため、情報端末 2150 の利便性が向上する。40

【0174】

表示部 2152 はヒンジ 2153 によって連結された 8 つの筐体 2151 に支持されている。ヒンジ 2153 を介して 2 つの筐体 2151 間を屈曲させることで、情報端末 2150 を展開した状態から折りたたんだ状態に可逆的に変形できる。表示部 2152 は、例え

10

20

30

40

50

ば、曲率半径 1 mm 以上 150 mm 以下で曲げることができる。

#### 【 0175 】

表示部 2152 が折り畳まれた状態（図 20D）であることを検知して、検知情報を供給するセンサを備える構成としてもよい。また、センサで、同様に、表示部 2152 が展開された状態（図 20B）を検知してもよい。表示部 2152 が折りたたまれていることを検知すると、折りたたまれた部分（又は折りたたまれて使用者に視認されない部分）の表示を停止してもよい。または、タッチセンサによる検知を停止してもよい。また、表示部 2152 が展開された状態であることを示す情報を取得して、表示やタッチセンサによる検知を再開するような制御を行ってもよい。

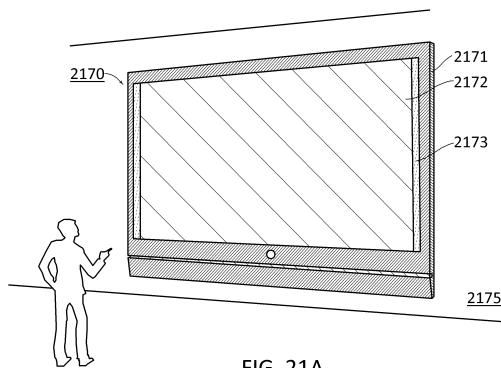

#### 【 0176 】

図 21A、図 21B に電子看板（デジタルサイネージとも呼ぶ）の構成例を示す。図 21A に示す電子看板 2170 は、筐体 2171、表示部 2172、スピーカ 2173 を有する。実施の形態 1 の表示装置は、軽量、薄型化ができるため、表示部 2172 の大画面化が容易である。よって、大画面化しても電子看板 2170 の設置場所の制約が少ない。図 21A は、電子看板 2170 を壁面 2175 に取り付けた例を示す。設置方法はこれに限らず、電子看板 2170 を天井から吊り下げるてもよい。表示部 2172 を可撓性の表示パネルで構成することで、電子看板を曲げた状態で設置できる。そのような例を図 21B に示す。

10

#### 【 0177 】

図 21B に示す電子看板 2190 は、円柱状の柱 2195 に取り付けられている。2192 は電子看板 2190 の表示部である。電子看板 2190 に無線通信装置を設けてもよい。これにより、表示させる情報を無線によって、電子看板 2190 に送信することができる。また、無線 2196 によって、電子看板 2190 から、他の情報端末 2197 に情報（例えば、表示されている情報、およびそれに関連する情報）を送信することができる。また、電子看板 2170 に無線通信装置を設けることで、電子看板 2190 と同様に動作させることができる。

20

#### 【 0178 】

##### 〔 実施の形態 3 〕

本実施の形態では、ハイブリッド型表示パネルおよびハイブリッド型表示モジュールについて説明する。本実施の形態の表示パネル、および表示モジュールは、実施の形態 1 の表示装置に適用することができる。

30

#### 【 0179 】

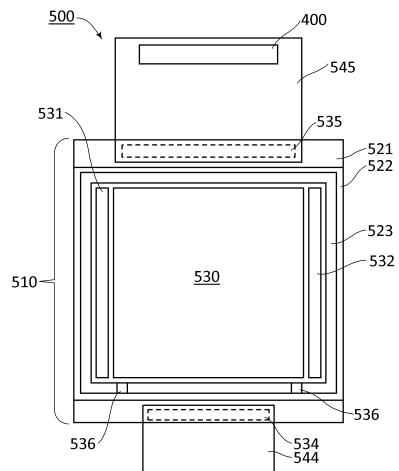

##### << 表示モジュールの構成例 1 >>

図 22A は表示モジュールの構成例を示す平面図である。図 22A に示す表示モジュール 500 は、ソースドライバ IC 400、表示パネル 510、FPC 544、545 を有する。表示モジュール 500 の断面構造は、図 3 に示す表示モジュール 150 と同様である。表示パネル 510 は一対の基板 521、522、封止材 523 を有する。基板 521 は、トランジスタ層および EL 素子層の支持基板である。トランジスタ層に、画素部 530、ゲートドライバ（GD）531、532、端子部 534、535 が設けられている。

40

#### 【 0180 】

ここでは、画素部 530 の構成は、図 5A、図 5C に示す画素部 110 と同様とし、3（RGB）のサブ画素 10 によって画素 13 が構成されていることとする。GD 531 は、配線 GL 1 を駆動するための回路であり、GD 532 は配線 GL 2 を駆動するための回路である。GD 531、GD 532 は、それぞれ、複数のフリップフロップが電気的に接続されているシフトレジスタで構成することができる。画素部 530 が画素部 110 と同様な回路構成を有する場合、GD 531 と GD 532 は同じ回路構成であってもよい。

#### 【 0181 】

基板 521 は、サブ画素 11（LC 用画素）のコモン電極およびカラーフィルタを支持する機能を持つ。封止材 523 は、基板 522 と基板 521 を貼り合わせる機能を持つ。封止材 523 によって基板 521 と基板 522 間に液晶層が封止されている。

50

**【0182】**

端子部 534、535 は、複数の端子を有する。端子部 534 には FPC544 が電気的に接続されている。FPC544 によって、信号および電圧が画素部 530、GD531、532 に入力される。端子部 535 には FPC545 が電気的に接続され、ソースドライバ I/C400 が FPC545 に電気的に接続されている。FPC545 は、ソースドライバ I/C400 と画素部 530 を電気的に接続する機能、およびソースドライバ I/C400 に信号および電圧等を入力する機能を有する。

**【0183】**

トランジスタ層の封止材 523 が形成される領域に、コモンコンタクト部 536 が設けられる。基板 522 に設けられている LC 素子 D E 1 のコモン電極と、基板 521 に設けられている端子部 534 とを電気的に接続するために、コモンコンタクト部 536 が設けられている。なお、コモンコンタクト部 536 は、封止材 523 の内側の領域に設けることもできる。コモンコンタクト部 536 を封止材 523 が形成される領域に設けることは、表示パネル 510 の狭額縁化に有効である。

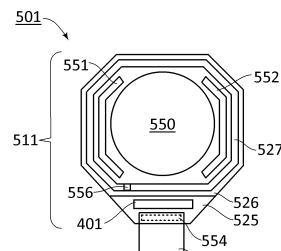

10

**【0184】**

<< 表示モジュールの構成例 2 >>

表示パネル 510 は四角形の表示領域を持つが、表示領域の形状は四角形に限定されない。例えば、円形とすることができます。そのような例を図 22B に示す。図 22B に示す表示モジュール 501 は、図 19B の情報端末 2030 の表示部 2032 に用いることができる。

20

**【0185】**

表示モジュール 501 は、ソースドライバ I/C401、表示パネル 511、FPC544 を有する。表示パネル 511 は、基板 525、526、封止部材 527、画素部 550、GD551、GD552、端子部 554、コモンコンタクト部 556 を有する。

30

**【0186】**

画素部 550 の平面形状は円形であり、基板 525、526 の平面形状は 8 角形状である。GD551 は基板 521 の端部に沿って屈曲している。GD552 も同様である。GD551 は配線 S L 1 を駆動するための回路であり、GD552 は配線 S L 2 を駆動するための回路である。ソースドライバ I/C401 は、COG 方式で、表示パネル 511 に実装されている。FPC544 は端子部 554 と電気的に接続されている。FPC544 を経て、外部から入力される信号および電源電圧が、画素部 550、GD551、552、ソースドライバ I/C401 に供給される。

**【0187】**

<< 表示モジュール 500、表示パネル 510 >>

以下、図 23A 図 25 を参照して、表示モジュール 500、特に表示パネル 510 のより具体的な構成について説明する。ここでは、サブ画素 10 によって画素部 530 が構成されていることとする。

30

**【0188】**

図 23B、図 23C は、3 つのサブ画素 10 (10R、10G、10B) のレイアウト例を表している。これら 3 のサブ画素 10 によって 1 画素 13 が構成される。なお、本実施の形態の理解を容易にするため、重複するが、図 23A にサブ画素 10 の回路図を示す。

40

**【0189】**

図 24、図 25 は、表示モジュール 500 の構成例を示す断面図である。なお図 3 の表記と異なり、図 24、図 25 は、基板 522、液晶層 580、トランジスタ層 581、EL 素子層 582、基板 521 の順にこれらが積層した図面となっている。図 23B、図 23C は、サブ画素 10 のトランジスタ層 581、EL 素子層 582 に設けられる要素のレイアウト例を示している。図 23B は、EL 用画素電極の下層に設けられる要素のレイアウト例を示しており、一部の要素にハッチングを付けている。なお、図 23C には、基板 522 に設けられている絶縁層 728 も記載している。

**【0190】**

50

また、図23B、図23Cのレイアウト例では、配線C S Lが奇数列と偶数列で異なっている。奇数列の配線C S Lが配線C S L Oであり、偶数列のものは配線C S L Eである。これは、奇数列と偶数列とで、E L素子D E 2の発光領域の配置を異ならせるためである。偶数列のサブ画素10の容量素子C S 1が形成される領域は、奇数列のサブ画素10ではE L素子D E 2の発光領域が形成され、偶数列のサブ画素10のE L素子D E 2の発光領域が形成される領域は、奇数列のサブ画素10では容量素子C S 1が形成される。実施の形態1で述べたように、サブ画素10において、E L素子D E 2の光を取り出す領域は、L C素子D E 1の画素電極の開口によって規定される。ここでは、導電層620が奇数列の画素電極であり、導電層623が偶数列の画素電極である。導電層620の開口620aは配線G L 1と配線A N Lの間に設けられ、導電層623の開口623aは隣の行の配線G L 2と配線G L 1の間に設けられる。また、E L素子E D 2の画素電極も奇数列と偶数列では、平面形状が異なる。ここでは、導電層680が奇数列の画素電極であり、導電層683が偶数列の画素電極である。

#### 【0191】

なお、本実施の形態では、便宜上、サブ画素10Rの列を奇数列、サブ画素10Bの列を偶数列と呼ぶが、サブ画素10Rの列が偶数列であってもよい。

#### 【0192】

図24は、サブ画素10Rの断面構造を示しており、a1-a2線、a3-a4線で切ったサブ画素10Rの断面図を示している。サブ画素10G、10Bの断面構造もサブ画素10Rと同様である。図25は、G D 5 3 1および、コモンコンタクト部536、端子部534の断面構造を示している。なお、ここではG D 5 3 1として、代表的にトランジスタM4を示している。

#### 【0193】

<トランジスタ層581、E L素子層582>

トランジスタ層581は、半導体層601-604、導電層610-612、導電層620-623、導電層631-638、導電層651-657、導電層680、683、絶縁層720-725、カラーフィルタ層C F R 2を有する。E L素子層582は、絶縁層726、727、E L層681、導電層682を有する。

#### 【0194】

トランジスタ層581に設けられるトランジスタ、容量素子等の各種素子のデバイス構造には、特段の制約はない。画素部530およびG D 5 3 1、532のそれぞれの機能に適したデバイス構造を選択すればよい。例えば、トランジスタのデバイス構造としては、トップゲート型、ボトムゲート型、およびゲート(フロントゲート)とボトムゲート双方を備えたデュアルゲート型、1つの半導体層に対して複数のゲート電極を有するマルチゲート型が挙げられる。トランジスタの活性層(チャネル形成領域)を構成する半導体の種類(組成や結晶構造等)にも特段の制約はない。活性層に用いられる半導体としては、単結晶半導体、非単結晶半導体に大別される。非単結晶としては、多結晶半導体、微結晶半導体、非晶質半導体などが挙げられる。半導体材料には、S i、G e、C等の第14族元素を1種または複数含む半導体(例えば、シリコン、シリコンゲルマニウム、炭化シリコン等)、酸化物半導体、窒化ガリウム等の化合物半導体等が挙げられる。

#### 【0195】

ここでは、画素部530およびG D 5 3 1、532が、同じ導電型のトランジスタで構成されている例を示している。ここでは、トランジスタ層581に設けられるトランジスタM1-M4が、nチャネル型トランジスタであり、かつO Sトランジスタである例を示している。ここでは、トランジスタM1-M4はボトムゲート型トランジスタである。トランジスタM1、M2はバックゲートのないO Sトランジスタであり、トランジスタM3はバックゲートを有するO Sトランジスタである。トランジスタM4はトランジスタM3と同様のデバイス構造をもつO Sトランジスタであり、バックゲートとゲートが互いに電気的に接続されている。トランジスタM1-M4のチャネル形成領域は、それぞれ、半導体層601-604に設けられる。

10

20

30

40

50

**【 0 1 9 6 】**

トランジスタ層 581、EL 素子層 582 の作製には、基板 521、522 とは異なるトランジスタ製造用基板（ここでは「仮基板」と呼ぶ）が用いられる。仮基板には、例えば、EL 表示パネル製造用のマザーガラスを用いることができる。仮基板上に分離層を形成し、分離層上にトランジスタ層 581 を形成し、トランジスタ層 581 上に EL 素子層 582 を形成する。封止材 524 によって、EL 素子層 582 の上方に基板 521 を固定する。しかる後、分離層と共に仮基板をトランジスタ層 581 から分離する。次いで、液晶表示パネル製造工程と同様のセル工程を行う。分離工程によって露出されたトランジスタ層 581 の表面に配向膜 741 を形成する。基板 522 に、導電層 740、配向膜 742 等を形成する。次いで、封止材 523 によってトランジスタ層 581 と基板 522との間に液晶層 580 を封止する。

10

**【 0 1 9 7 】**

封止材 523 には、例えば、反応硬化型接着剤、光硬化型接着剤、熱硬化型接着剤、嫌気型接着剤等を用いることができる。具体的には、エポキシ樹脂、アクリル樹脂、シリコーン樹脂、フェノール樹脂、ポリイミド樹脂、イミド樹脂、PVC（ポリビニルクロライド）樹脂、PVB（ポリビニルブチラル）樹脂、EVA（エチレンビニルアセテート）樹脂等を含む接着剤を封止材 523 に用いることができる。

**【 0 1 9 8 】**

絶縁層 720 はトランジスタ層 581 のパッシベーション膜として機能する。絶縁層 721 はトランジスタ M1 - M4 の下地絶縁層として機能する。導電層 620 は、LC 素子 D E1 の画素電極であり、開口 620a を有する。導電層 621 はコモンコンタクト部 536 の端子 TP1 を構成し、導電層 622 は端子部 534 の端子 TP2 を構成する。端子部 534 は複数の端子 TP2 を有する。

20

**【 0 1 9 9 】**

導電層 610 - 612 は、絶縁層 720 のエッティング工程においてエッチトップ層として機能する。エッティング工程によって、絶縁層 720 において、導電層 620 - 622 が形成される領域には開口が設けられている。導電層 610 - 612 が存在することで、エッティング工程で分離層が損傷することを防ぐことができる。

**【 0 2 0 0 】**

例えば、分離層にタンゲステン層を用いた場合、導電層 610 - 612 を In - Ga - Zn 酸化物で形成することができる。また、導電層 610 - 612 は、仮基板の分離工程において導電層 620 - 623 の保護層として機能する。分離層から分離しやすい導電材料で導電層 610 - 612 を形成することで、導電層 620 - 623 を損傷させずに、仮基板を分離することができる。また、導電層 610 - 612 を設けることで、導電層 620 - 623 を構成する導電材料の制約が少なくなる。

30

**【 0 2 0 1 】**

導電層 630 - 638 は絶縁層 721 上に設けられている。導電層 631 は配線 GL1 を構成し、トランジスタ M1 のゲート電極として機能する領域を有する。導電層 632 は配線 GL2 を構成し、トランジスタ M2 のゲート電極として機能する領域を有する。導電層 633、635、637 はそれぞれ配線 ANL、CSLO、CSLE を構成する。導電層 636 は導電層 620 と電気的に接続されている。

40

**【 0 2 0 2 】**

絶縁層 722 上に導電層 651 - 657 が設けられている。絶縁層 722 によって、トランジスタ M1 - M4 のゲート絶縁層が構成される。導電層 651 は配線 SL1 を構成し、トランジスタ M1 のソース電極およびドレイン電極として機能する領域を有する。導電層 652 は配線 SL2 を構成し、トランジスタ M2 のソース電極およびドレイン電極として機能する領域を有する。導電層 653、654 はそれぞれ、トランジスタ M3 のソース電極およびドレイン電極を構成する。導電層 654 は導電層 633 と電気的に接続されている。導電層 655 はトランジスタ M2 のソース電極およびドレイン電極を構成し、導電層 634 と電気的に接続されている。導電層 656 はトランジスタ M1 のソース電極および

50

ドレイン電極を構成し、導電層 636 と電気的に接続されている。

【0203】

導電層 635、絶縁層 722 および導電層 656 が重なっている領域が容量素子 C S 1 として機能し、導電層 634、絶縁層 722、導電層 654 が重なっている領域が容量素子 C S 2 として機能する。また、偶数列では、導電層 637、絶縁層 722 および導電層 656 が重なっている領域が容量素子 C S 1 として機能する。

【0204】

絶縁層 723、724 はトランジスタ M1 - M4 のパッシベーション膜として機能する。絶縁層 723 上に導電層 673、674 が設けられている。導電層 673 はトランジスタ M3 のバックゲート電極であり、導電層 655 に電気的に接続されている。つまり導電層 655 によって、トランジスタ M3 のバックゲート電極とゲート電極が電気的に接続される。導電層 674 はトランジスタ M4 のバックゲート電極である。トランジスタ M3 と同様に、導電層 655 と同じ層の導電層によって、トランジスタ M4 のゲート電極とバックゲート電極とが電気的に接続されている。

10

【0205】

絶縁層 723 を覆ってカラーフィルタ層 C F R 2 が設けられている。カラーフィルタ層 C F R 2 は、E L 素子 D E 2 用のカラーフィルタ層である。E L 素子 D E 2 用のカラーフィルタ層は適宜設ければよい。カラーフィルタ層 C F R 2 はサブ画素 10R の色に応じた赤色のカラーフィルタ層である。サブ画素 10G、10B にも、それぞれ、緑色、青色のカラーフィルタ層が設けられる。カラーフィルタ層を覆って、絶縁層 725 が設けられている。絶縁層 725 は平坦化膜として機能する。そのため、絶縁層 725 は、ポリイミド樹脂、アクリル樹脂などの樹脂で形成することが好ましい。

20

【0206】

絶縁層 725 上に導電層 680 が設けられている。導電層 680 は E L 素子 D E 2 の画素電極である。導電層 680 は導電層 653 と電気的に接続されている。導電層 680 を覆って絶縁層 726 が設けられている。絶縁層 726 上に絶縁層 727 が設けられている。絶縁層 727 は、基板 521 と E L 素子層 582 との間の空間を維持するためのスペーサとして機能する。絶縁層 726、727 上に E L 層 681、導電層 682 が積層されている。導電層 682 は E L 素子 D E 2 のコモン電極である。絶縁層 726 は、導電層 620 の開口 620a と重なる領域に開口 726a を有する。開口 726a において、導電層 680 が露出される。開口 726a に形成される導電層 680、E L 層 681、導電層 682 の積層が、奇数列の E L 素子 D E 2 の発光領域を構成する。

30

【0207】

また、導電層 680 と同様に、導電層 683 が絶縁層 725 上に設けられている。開口 726b に形成される導電層 683、E L 層 681、導電層 682 の積層が、偶数列の E L 素子 D E 2 の発光領域を構成する。

【0208】

E L 層 681 は、正孔と電子とが再結合することで発光することが可能な発光材料を少なくとも有する。E L 層 681 には、正孔注入層、正孔輸送層、電子輸送層、電子注入層などの機能層を有してもよい。ここでは、E L 層 681 はサブ画素 10 の色で発光する。あるいは、全てのサブ画素 10 に白色で発光する E L 層 681 を設けてもよい。サブ画素 10 の色で発光する E L 層 681 を設けることで、E L 素子 D E 2 の光 762 を効率よく基板 522 から取り出すことができるため、省電力化につながる。また、表示パネル 510 の表示品位（コントラスト、色再現性）を高めることができる。

40

【0209】

<基板 522（対向基板）>

基板 522 は L C 表示パネルの対向基板に対応する。基板 522 には、絶縁層 728、導電層 740、配向膜 742、オーバーコート層 743、カラーフィルタ層 C F R 1、遮光層 B M F 1 が設けられている。

【0210】

50

絶縁層 728 は、基板 522 と基板 521 (トランジスタ層 581)との間の空間を維持するためのスペーサとして機能する。導電層 740 は LC 素子 DE1 のコモン電極である。カラーフィルタ層 CFR1 は LC 素子 DE1 用のカラーフィルタ層であり、赤色のカラーフィルタである。基板 522 には、サブ画素 10 の色に応じたカラーフィルタ層が設けられる。ここでは、赤、緑、青のカラーフィルタ層がストライプ状に配列される。遮光層 BMF1 は、表示に寄与しない領域を遮光する。GD531、532 は遮光層 BMF1 で覆われている。遮光層 BMF1 は、画素部 530 では、隣接する画素電極 (導電層 620、623) の間を遮光する。つまり、画素部 530 において、遮光層 BMF1 の平面形状は、配線 SL1、SL2、GL1 と重なる格子状である。

## 【0211】

10

&lt;コモンコンタクト部 536、端子部 534&gt;

端子 TP1 は、導電層 611、621、638 を有する。導電層 621 によって導電層 637 と導電層 611 とが電気的に接続されている。端子 TP2 は、導電層 612、622、638 を有する。導電層 622 によって導電層 638 と導電層 612 とが電気的に接続されている。導電層 657 は引き回し配線を構成する。図 25 の例では、導電層 657 によって、端子 TP1 と端子 TP2 とが電気的に接続される。

## 【0212】

なお、導電層 638、639 は適宜設ければよい。導電層 638、639 を設けない場合は、導電層 621、622 が導電層 657 と直接的に電気的に接続される。また、引き回し配線を、導電層 657 に代えて、導電層 637 で構成してもよい。この場合、端子 TP2 に導電層 638 を設けず、導電層 637 と導電層 622 とを直接的に電気的に接続すればよい。

20

## 【0213】

封止材 523 は、導電性粒子 793 を有する。導電性粒子 793 を含む封止材 523 を形成して液晶層 580 を封止することで、コモンコンタクト部 536 において、導電層 740 を端子 TP1 に電気的に接続することができる。なお、封止材 523 中のコモンコンタクト部 536 とその近傍のみに導電性粒子 793 を分布するようにしてもよい。導電性粒子 794 を含む ACF (異方性導電フィルム) 564 によって、FPC544 が端子 TP2 と電気的に接続される。つまり、基板 522 に設けられたコモン電極 (導電層 740) は、端子 TP1、引き回し配線 (導電層 754)、端子 TP2 を介して、FPC544 に電気的に接続される。

30

## 【0214】

表示モジュール 500 の表示原理は、表示モジュール 150 (図 3) と同様である。図 24 に示すように、基板 522 から入射した外光 760 は、カラーフィルタ層 CFR1、導電層 740、液晶層 580 等を通り導電層 620 で反射される。導電層 620 で反射された光 761 は、再び液晶層 580、導電層 740、カラーフィルタ層 CFR1 等を通過し、基板 522 から射出する。EL 素子 DE2 の光 762 は、導電層 682 で反射され、導電層 680、カラーフィルタ層 CFR2、導電層 620 の開口 620a、カラーフィルタ層 CFR1 等を通り、基板 522 から射出する。

40

## 【0215】

表示パネル 510 を構成する各種の層は、単層構造でも積層構造でもよい。例えば、導電層に用いられる導電材料には、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タンクステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニア、ベリリウム等の金属、これら金属の合金および化合物がある。また、リン等の不純物元素を含有させた多結晶シリコン、金属酸化物を有する透光性導電体などがある。透光性導電体としては、例えば酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物 (ITO と呼ばれる)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物等の金属酸化物を挙げることができる。

50

**【0216】**

また、表示パネル510の絶縁層に用いられる絶縁材料には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタル等があげられる。また、樹脂材料でもよく、アクリル樹脂、ポリイミド樹脂、ベンゾシクロブテン系樹脂、シロキサン系樹脂、ポリアミド樹脂、エポキシ樹脂等を用いることができる。なお、本明細書において、酸化窒化物とは、窒素よりも酸素の含有量が多い化合物をいい、窒化酸化物とは、酸素よりも窒素の含有量が多い化合物をいう。

**【0217】**

上述したようにトランジスタ層581には様々な構造のトランジスタを適用することができる。以下に、トランジスタ層581のトランジスタの他の構成例を示す。

**【0218】**

<<トランジスタM21、M22>>

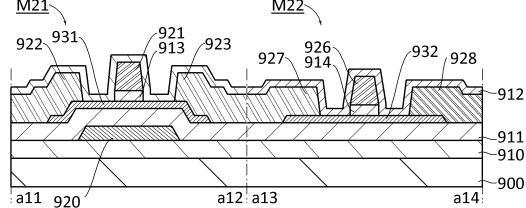

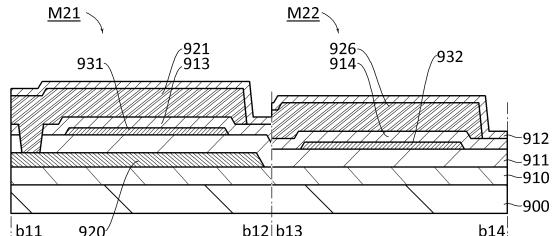

図26に、トップゲート構造のOSトランジスタの構成の一例を示す。図26A、図26BはトランジスタM21、M22の上面図である。図26CはトランジスタM21、M22のチャネル長方向の断面図であり、図26DはトランジスタM21、M22のチャネル幅方向の断面図である。図26Cには、トランジスタM21のa11-a12線による断面図、およびトランジスタM22のa13-a14線による断面図を示し、図26Dには、トランジスタM21のb11-b12線による断面図、およびトランジスタM22のb13-b14線による断面図を示す。

10

**【0219】**

トランジスタM21、M22は、絶縁層910を介して基板900上に形成されている。トランジスタM21、M22は絶縁層912で覆われている。トランジスタM21は、ゲート絶縁層913、半導体層931、バックゲート電極920、ゲート電極921、ソース電極922、ドレイン電極923を有する。トランジスタM22は、ゲート絶縁層914、半導体層932、ゲート電極926、ソース電極927、ドレイン電極928を有する。バックゲート電極920を覆って絶縁層911が設けられ、絶縁層911上に半導体層931、932が設けられている。半導体層931、932は、単層の酸化物半導体膜、または酸化物半導体膜の積層膜で形成されている。バックゲート電極920はゲート電極921と電気的に接続されている。

20

**【0220】**

トランジスタM21において、ゲート電極921は、ソース電極922およびドレイン電極923と重なる領域を有していない。そのため、トランジスタM21のゲート電極921の寄生容量を小さくすることができる。トランジスタM22もトランジスタM21と同様の積層構造をもつため、トランジスタM22のゲート電極926の寄生容量を小さくすることができる。トランジスタのゲート電極の寄生容量は信号遅延の原因である。そのため、トランジスタM21、M22は、大面積な表示パネルの画素部、ゲートドライバに好適である。

30

**【0221】**

<<トランジスタM23、M24>>

ここでは、シリコンで半導体層が形成されているトランジスタ(Siトランジスタ)の構成例を示す。SiトランジスタでGD531、532を構成する場合、nチャネル型トランジスタとpチャネル型トランジスタとでこれらを構成してもよい。あるいは、画素部530、GD531、532のトランジスタを全てpチャネル型トランジスタとしてもよい。

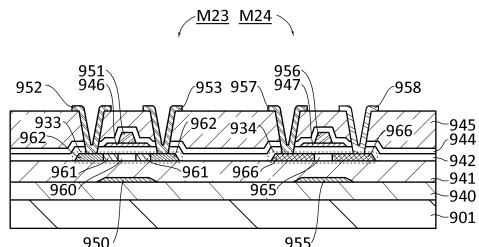

40

**【0222】**

図27に示すトランジスタM23、M24はトップゲート構造のトランジスタである。トランジスタM23はnチャネル型トランジスタであり、トランジスタM24はpチャネル型のトランジスタである。940-947で示される層は絶縁層である。トランジスタM23、M24は、絶縁層940を介して基板900上に形成されている。絶縁層946が

50

トランジスタM 2 3 のゲート絶縁層であり、絶縁層9 4 7 はトランジスタM 2 4 のゲート絶縁層である。トランジスタM 2 3 は、半導体層9 3 3 、バックゲート電極9 5 0 、ゲート電極9 5 1 、ソース電極9 5 2 、ドレイン電極9 5 3 を有する。トランジスタM 2 4 は、半導体層9 3 4 、バックゲート電極9 5 5 、ゲート電極9 5 6 、ソース電極9 5 7 、ドレイン電極9 5 8 を有する。

#### 【0 2 2 3】

基板9 0 1 には、n チャネル型トランジスタとして、バックゲート電極9 5 0 を有さないトランジスタM 2 3 を設けることができる。また、p チャネル型トランジスタとして、バックゲート電極9 5 5 を有さないトランジスタM 2 4 を設けることができる。

#### 【0 2 2 4】

半導体層9 3 3 、9 3 4 はシリコン膜で形成される。例えば、半導体層9 3 3 、9 3 4 はプラズマC V D法などの気相成長法若しくはスパッタリング法で成膜される非晶質シリコンで形成することができる。また、このような非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコンで形成することができる。また、単結晶シリコンウェハに水素イオン等を注入して表層部を剥離した単結晶シリコン層で形成することができる。

10

#### 【0 2 2 5】

シリコン膜の結晶化方法として、例えば、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、基板9 0 1 として石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法、9 5 0 度の高温アニールを組み合わせた結晶法を用いてもよい。

20

#### 【0 2 2 6】

半導体層9 3 3 は、チャネル形成領域9 6 0 、一対のL D D ( L i g h t D o p e d D r a i n ) 領域9 6 1 、並びに一対の不純物領域9 6 2 を有する。チャネル形成領域9 6 0 は、半導体層9 3 3 がゲート電極9 5 1 と重畳する領域である。一対の不純物領域9 6 2 はソース領域またはドレイン領域として機能する。n 型の導電型を付与するために、L D D 領域9 6 1 および不純物領域9 6 2 にはボロン( B )、アルミニウム( A l )、ガリウム( G a )等の不純物元素が添加されている。半導体層9 3 4 はチャネル形成領域9 6 5 、および一対の不純物領域9 6 6 を有する。チャネル形成領域9 6 5 は、半導体層9 3 4 がゲート電極9 5 6 と重畳する領域である。一対の不純物領域9 6 6 はソース領域またはドレイン領域として機能する。p 型の導電型を付与するため、不純物領域9 6 6 にはリン( P )、ヒ素( A s )等不純物元素が添加されている。

30

#### 【符号の説明】

#### 【0 2 2 7】

|       |                 |      |

|-------|-----------------|------|

| 1 0   | 1 2 、 1 5 、 1 7 | サブ画素 |

| 4 0   | 4 3 、 4 5       | ピン   |

| 1 0 0 | 表示装置            |      |

| 1 1 0 | 画素部             |      |

| 1 1 2 | 周辺回路            |      |

| 1 1 4 | 画素部             |      |

| 1 1 5 | 周辺回路            |      |

| 1 2 1 | ゲートドライバ         |      |

| 1 2 2 | ゲートドライバ         |      |

| 1 2 3 | ソースドライバ         |      |

| 1 2 4 | 信号処理回路          |      |

| 1 2 5 | 出力回路            |      |

| 1 3 0 | プロセッサ           |      |

| 1 3 1 | 制御回路            |      |

40

50

|         |                          |    |

|---------|--------------------------|----|

| 1 3 2   | 画像プロセッサ                  |    |

| 1 3 3   | 記憶装置                     |    |

| 1 3 5   | センサ                      |    |

| 1 4 0   | 外光                       |    |

| 1 4 1   | 光                        |    |

| 1 4 2   | 光                        |    |

| 1 5 0   | 1 5 3 表示モジュール            |    |

| 1 5 3、  | 1 5 4 F P C              |    |

| 1 6 0   | 表示パネル                    |    |

| 1 6 1、  | 1 6 2 基板                 | 10 |

| 1 6 3   | トランジスタ層                  |    |

| 1 6 4   | L C 層                    |    |

| 1 6 5   | E L 素子層                  |    |

| 1 6 6   | タッチセンサ                   |    |

| 1 6 7   | F P C                    |    |

| 1 6 8   | タッチセンサドライバ I C           |    |

| 1 7 0   | 封止材                      |    |

| 1 7 1   | 画素電極                     |    |

| 1 7 1 a | 開口                       |    |

| 1 7 2   | 画素電極                     | 20 |

| 1 7 3、  | 1 7 4、 1 7 7 端子部         |    |

| 1 7 5、  | 1 7 6 コモン電極              |    |

| 1 7 8   | カラーフィルタ                  |    |

| 2 0 0   | ソースドライバ I C              |    |

| 2 1 0   | L V D S レシーバ             |    |

| 2 1 1   | ロジック回路                   |    |

| 2 1 2   | シフトレジスタ ( S R )          |    |

| 2 1 3   | ラッチ回路 ( D - L A T )      |    |

| 2 1 4   | レベルシフタ ( L S )           |    |

| 2 1 5   | パストランジスタロジック回路 ( P T L ) | 30 |

| 2 1 6   | マルチプレクサ ( M U X )        |    |

| 2 1 7   | 增幅回路 ( A M P )           |    |

| 2 2 0   | 回路                       |    |

| 2 3 1   | 電圧生成回路 ( V G E N )       |    |

| 2 3 2   | バッファ回路 ( B U F )         |    |

## 【図面】

## 【図 1】

FIG. 1

## 【図 2】

FIG. 2

10

20

30

40

## 【図 3】

FIG. 3

## 【図 4】

FIG. 4A

FIG. 4B

50

【図 5】

【図 6】

【図 7】

【図 8】

10

20

30

40

50

【図 9】

FIG. 9

【図 10】

10

20

30

40

【図 11】

FIG. 11A

FIG. 11B

【図 12】

FIG. 12A

FIG. 12B

50

【図 1 3】

FIG. 13

【図 1 4】

FIG. 14

【図 1 5】

FIG. 15

【図 1 6】

FIG. 16

10

20

30

40

50

【図 17】

FIG. 17A

FIG. 17B

FIG. 17C

【図 18】

FIG. 18A

10

FIG. 18B

20

【図 19】

【図 20】

FIG. 20A

30

FIG. 20B

40

FIG. 20C

FIG. 20D

50

【図21】

FIG. 21A

FIG. 21B

【図22】

FIG. 22A

FIG. 22B

【図23】

【図24】

【図25】

【図26】

FIG. 26C

FIG. 26D

【図27】

FIG. 27

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

|         | F I             |         |              |

|---------|-----------------|---------|--------------|

| G 0 9 G | 3/32 (2016.01)  | G 0 9 G | 3/20 6 2 3 R |

| G 0 9 G | 3/3225(2016.01) | G 0 9 G | 3/20 6 1 1 F |

| G 0 9 G | 3/3233(2016.01) | G 0 9 G | 3/20 6 1 2 L |

| G 0 9 G | 3/3291(2016.01) | G 0 9 G | 3/20 6 2 1 B |

| G 0 9 G | 3/36 (2006.01)  | G 0 9 G | 3/20 6 2 1 K |

| H 0 1 L | 51/50 (2006.01) | G 0 9 G | 3/20 6 2 1 M |

| H 0 5 B | 33/14 (2006.01) | G 0 9 G | 3/20 6 2 4 B |

|         |                 | G 0 9 G | 3/20 6 3 3 D |

|         |                 | G 0 9 G | 3/20 6 3 3 R |

|         |                 | G 0 9 G | 3/20 6 4 1 C |

|         |                 | G 0 9 G | 3/20 6 4 1 P |

|         |                 | G 0 9 G | 3/20 6 4 2 F |

|         |                 | G 0 9 G | 3/20 6 5 0 M |

|         |                 | G 0 9 G | 3/20 6 8 0 D |

|         |                 | G 0 9 G | 3/20 6 8 0 H |

|         |                 | G 0 2 F | 1/133 5 5 0  |

|         |                 | G 0 9 F | 9/30 3 6 5   |

|         |                 | G 0 9 F | 9/46 Z       |

|         |                 | G 0 9 G | 3/30 J       |

|         |                 | G 0 9 G | 3/32 A       |

|         |                 | G 0 9 G | 3/3225       |

|         |                 | G 0 9 G | 3/3233       |

|         |                 | G 0 9 G | 3/3291       |

|         |                 | G 0 9 G | 3/36         |

|         |                 | H 0 5 B | 33/14 A      |

|         |                 | H 0 5 B | 33/14 Z      |

## (56)参考文献

- 特許第4185556 (JP, B2)

特開2008-225381 (JP, A)

特開2000-250526 (JP, A)

特開2002-62856 (JP, A)

特開2008-90276 (JP, A)

特開2011-107679 (JP, A)

特開2006-163246 (JP, A)

特開2012-34066 (JP, A)

特開2003-233357 (JP, A)

特開2015-161752 (JP, A)

特開2007-256913 (JP, A)

特開2008-152179 (JP, A)

特開2003-157026 (JP, A)

中国特許出願公開第102301409 (CN, A)

特開2003-322850 (JP, A)

特表2009-510527 (JP, A)

特開平8-211832 (JP, A)

特開2004-45769 (JP, A)

特開2003-76302 (JP, A)

特開2002-258789 (JP, A)

特開2008-20712 (JP, A)

特開2002-296375 (JP, A)

特開2005-31294 (JP, A)

特開2001-222249 (JP, A)

特開2008-129426 (JP, A)

特開2002-140022 (JP, A)

特開2004-327431(JP,A)

(58)調査した分野 (Int.Cl., DB名)

G09G 3/20,3/30,3/32,3/36