(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5400131号

(P5400131)

(45) 発行日 平成26年1月29日(2014.1.29)

(24) 登録日 平成25年11月1日(2013.11.1)

(51) Int.Cl.

HO2M 3/28 (2006.01)

F 1

HO2M 3/28

HO2M 3/28E

Q

請求項の数 12 (全 8 頁)

(21) 出願番号 特願2011-501304 (P2011-501304)

(86) (22) 出願日 平成20年3月25日 (2008.3.25)

(65) 公表番号 特表2011-516020 (P2011-516020A)

(43) 公表日 平成23年5月19日 (2011.5.19)

(86) 国際出願番号 PCT/IB2008/000693

(87) 国際公開番号 WO2009/118576

(87) 国際公開日 平成21年10月1日 (2009.10.1)

審査請求日 平成23年3月25日 (2011.3.25)

(73) 特許権者 501263810

トムソン ライセンシング

Thomson Licensing

フランス国, 92130 イッサー レ

ムーリノー, ル ジヤンヌ ダルク,

1-5

1-5, rue Jeanne d' Arc, 92130 ISSY LES

MOULINEAUX, France

(74) 代理人 110001243

特許業務法人 谷・阿部特許事務所

(72) 発明者 アントン ワーナー ケラー

スイス シーエイチ-8905 アーニ

チェルマットシュトラッセ 47

最終頁に続く

(54) 【発明の名称】補助電源電圧を発生させるスナバキャパシタ

## (57) 【特許請求の範囲】

## 【請求項 1】

電源装置であって、

変圧器の第一の巻線に結合される入力供給電圧源と、

前記変圧器の第二の巻線にトランス結合された前記第一の巻線において電流を発生し、第一の負荷回路に電圧を加える第一の出力供給電圧を発生するため、第一のスイッチング制御信号に応答し、前記第一の巻線に結合される出力スイッチングトランジスタであつて、前記出力スイッチングトランジスタは、前記第一のスイッチング制御信号のサイクルの第一の部分の間に、前記第一の巻線の電流を遮断し、前記第一の巻線にフライバック電圧を発生する、出力スイッチングトランジスタと、

前記第一の巻線に結合されかつ第二のキャパシタに直列に結合されて、前記フライバック電圧の変化率を低減し、前記第一および第二のキャパシタのそれぞれに容量性電流を発生する容量性分圧器スナバネットワークを形成する第一のキャパシタであって、前記容量性電流は、対応する電荷を、前記第二のキャパシタにおいて第二の供給電圧の第一の部分を発生する前記第一および第二のキャパシタのそれぞれに蓄積し、前記第二の供給電圧は、第二の負荷回路に結合される、第一のキャパシタと、

前記サイクルの第二の部分の間に前記第一のキャパシタに結合されるインダクタであつて、前記出力スイッチングトランジスタが導通した状態で前記第一のキャパシタに蓄積された電荷から前記第二のキャパシタに結合される共振電流を発生するための前記インダクタの共振回路を前記第一のキャパシタを用いて形成するとき、前記共振電流は、前記第二

の供給電圧の第二の部分を発生するために、電荷を前記第二のキャパシタに蓄積する、インダクタと

を備える、電源装置。

**【請求項 2】**

前記第二の供給電圧を調整するように、前記対応する電荷を前記第二のキャパシタに蓄積する電流のうちの少なくとも一つを選択的に遮断するための、制御可能な第二のスイッチングトランジスタをさらに備える、請求項 1に記載の電源装置。

**【請求項 3】**

前記第二の供給電圧に応答し、かつ、前記第二の供給電圧が値の範囲を外れるとき、前記制御可能な第二のスイッチングトランジスタの導通状態を変更するために、前記制御可能な第二のスイッチングトランジスタの制御端子に結合される比較器をさらに備える、請求項 2に記載の電源装置。

10

**【請求項 4】**

前記第二のスイッチングトランジスタは、前記インダクタと並列で結合される、請求項 2に記載の電源装置。

**【請求項 5】**

前記第二のスイッチングトランジスタは、前記インダクタおよび前記第一のキャパシタのそれぞれの間の接合端子に結合される、請求項 2に記載の電源装置。

**【請求項 6】**

前記第二のキャパシタを充電する対応する電流が第一の方向で流れることができるようにするために、および、前記第二のキャパシタにおいて電流が反対方向で流れることを防ぐために、前記第一および第二のキャパシタの間に結合される整流器をさらに備える、請求項 1に記載の電源装置。

20

**【請求項 7】**

前記第一の出力電圧は、前記第一の出力供給電圧を前記第二の出力供給電圧から絶縁する前記変圧器の第二の巻線に発生する、請求項 1に記載の電源装置。

**【請求項 8】**

前記第一および第二のキャパシタは、直列で結合される、請求項 1に記載の電源装置。

**【請求項 9】**

前記第二のキャパシタは、前記第一のキャパシタより大きい、請求項 1に記載の電源装置。

30

**【請求項 10】**

前記出力スイッチングトランジスタは、前記インダクタを前記第二のキャパシタと並列で結合させて、前記共振回路を形成する、請求項 1に記載の電源装置。

**【請求項 11】**

前記第一のスイッチング制御信号を発生するためのデューティサイクル変調器であって、前記第二の供給電圧は、前記デューティサイクル変調器に電圧を加えるために、前記デューティサイクル変調器に結合される、デューティサイクル変調器をさらに備える、請求項 1に記載の電源装置。

**【請求項 12】**

電源装置であって、

変圧器の第一の巻線に結合される入力供給電圧源と、

前記変圧器の第二の巻線にトランス結合された前記第一の巻線において電流を発生し、第一の負荷回路に電圧を加える第一の出力供給電圧を発生するために、第一のスイッチング制御信号に応答し、前記第一の巻線に結合される出力スイッチングトランジスタであって、前記出力スイッチングトランジスタは、前記第一のスイッチング制御信号のサイクルの第一の部分の間に、前記第一の巻線の電流を遮断し、前記第一の巻線にフライバック電圧を発生する、出力スイッチングトランジスタと、

前記第一の巻線に結合されて、かつ、ダイオードを介して第二のキャパシタに直接結合されて、前記フライバック電圧の変化率を低減し、前記第一および第二のキャパシタのそ

40

10

20

30

40

50

れぞれに容量性電流を発生するスナバ容量ネットワークを形成する、第一のキャパシタであって、前記容量性電流は、対応する電荷を、前記第二のキャパシタにおいて第二の供給電圧の第一の部分を発生する前記第一および第二のキャパシタのそれぞれに蓄積し、前記第二の供給電圧は、第二の負荷回路に結合される、第一のキャパシタと、

前記出力スイッチングトランジスタの動作により、前記サイクルの第二の部分の間に前記第一のキャパシタに結合されるインダクタであって、前記第一のキャパシタに蓄積された電荷から前記第二のキャパシタに結合される共振電流を発生するための前記インダクタの共振回路を前記第一のキャパシタを用いて形成し、前記共振電流は、前記第二の供給電圧の第二の部分を発生するために、電荷を前記第二のキャパシタに蓄積する、インダクタと

10

を備える、電源装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子回路に電圧を加えるための低電力電源装置に関する。

【背景技術】

【0002】

スイッチング電源装置、例えば、パルス幅変調電源装置は、絶縁変圧器の一次巻線を有する出力部を含むことができる。変圧器の一次巻線は、非絶縁で主電源供給電圧に結合される。絶縁電源電圧は、絶縁変圧器の二次巻線に生じた電圧から発生する。典型的には、スナバキャパシタが一次巻線に結合され、一次巻線で生じた電圧におけるフライバック電圧部分の変化率を低減する。

20

【0003】

パルス幅変調器を形成した集積回路（IC）は、出力部のスイッチング動作を制御する。動作のため、このICは、補助的な非絶縁電源電圧によって電力供給されることを必要とする。非絶縁電源電圧は、相対的低電力を供給すべきである電源で発生することができる。非絶縁電源電圧を、変圧器の一次巻線に既に発生した非絶縁電圧から発生させることができ、望ましいかもしれない。

【0004】

本発明の一態様を実施する際、一次巻線に結合されるスナバキャパシタは、容量結合型充電電流を発生させるために使用される。容量結合型充電電流は、フィルタまたは電荷蓄積用の第二のキャパシタに結合され、第二のキャパシタに、ICに電圧を加えるための非絶縁電源電圧の第一の部分を発生させる。

30

【0005】

本発明の他の態様を実施する際、出力部のスイッチングサイクルの一部の間に、スナバキャパシタがインダクタに結合されて、共振回路を形成する。共振回路は、第二のキャパシタに、ICに電圧を加えるための非絶縁電源電圧の第二の部分を発生させる。

【0006】

更なる発明の特徴を実施する際、スイッチング型分流トランジスタは、遮断されない場合に第二のキャパシタを充電する電流を選択的に遮断することにより、低電圧電源電圧を調整する。

40

【発明の概要】

【0007】

発明の特徴を実施する電源装置は、変圧器の第一の巻線に結合される入力供給電圧源を含む。出力スイッチングトランジスタは、第一のスイッチング制御信号に応答し、第一の巻線に結合される。第一の巻線は、変圧器の第二の巻線にトランス結合（Transformer-coupled）されて、第一の負荷回路に電圧を加える第一の出力供給電圧を発生させる。出力スイッチングトランジスタは、第一のスイッチング制御信号のサイクルの第一の部分の間に第一の巻線電流を遮断して、フライバック電圧を第一の巻線に発生させる。第一のキャパシタは、第一の巻線にかつ第二のキャパシタに結合されて、スナバ

50

容量ネットワークを形成し、スナバ容量ネットワークは、フライバック電圧の変化率を低減して、かつ、第一および第二のキャパシタのそれぞれに容量性電流を発生させる。容量性電流は、対応する電荷を第一および第二のキャパシタのそれぞれに蓄積し、該電荷が第二のキャパシタに第二の供給電圧の第一の部分を生じさせる。第二の供給電圧が第二の負荷回路に結合される。インダクタは、出力スイッチングトランジスタの動作により、第一のキャパシタに結合されて、スイッチングサイクルの第二の部分の間に、第一のキャパシタと共に、第一のキャパシタに蓄積された電荷から共振電流を発生させるための共振回路を形成する。共振電流が第二のキャパシタに結合される。共振電流は、第二の供給電圧の第二の部分を生じさせるための電荷を第二のキャパシタに蓄積する。

## 【図面の簡単な説明】

10

## 【0008】

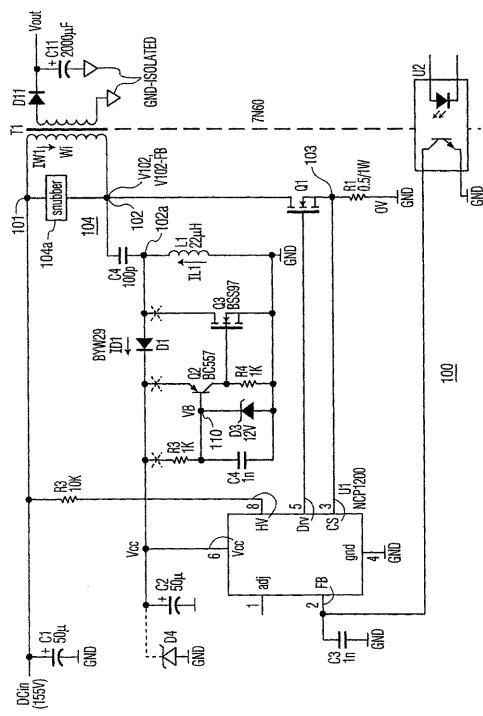

【図1】本発明の一形態による電源装置100を示す図である。

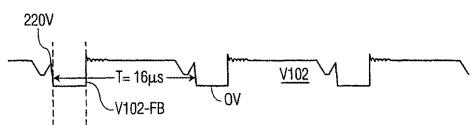

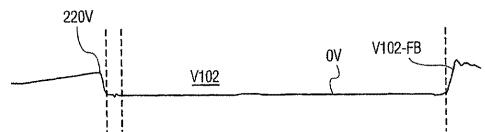

【図2a】図1における回路100の動作に関連する波形を示す図である。

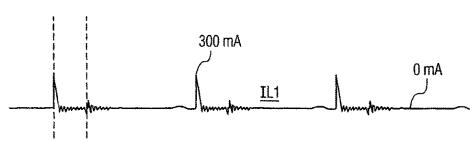

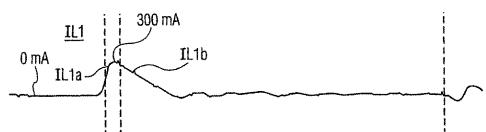

【図2b】図1における回路100の動作に関連する波形を示す図である。

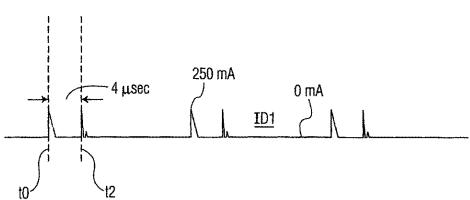

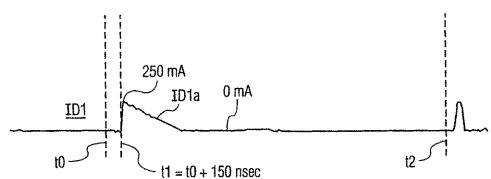

【図2c】図1における回路100の動作に関連する波形を示す図である。

【図3a】図2aにおける波形を拡大された時間スケールで示す図である。

【図3b】図2bにおける波形を拡大された時間スケールで示す図である。

【図3c】図2cにおける波形を拡大された時間スケールで示す図である。

## 【発明を実施するための形態】

## 【0009】

20

図1は、本発明の一形態を実施する電源装置100を示す。主電源供給電圧(図示せず)から発生したDC(直流)入力供給電圧DCinは、主電源フィルタキャパシタC1に生じ、絶縁変圧器T1の一次巻線W1の入力端子101と一次側の非絶縁基準電位GNDとの間に供給される。巻線W1の第二の端子102は、スイッチング出力トランジスタQ1のドレーン端子に結合される。トランジスタQ1のソース端子103は、電流サンプリング抵抗R1に結合されて、トランジスタQ1に流れる電流を示す電流サンプリング信号CSを発生させる。抵抗R1は、端子103と一次側の基準電位GNDとの間に結合される。

## 【0010】

30

信号CSが従来のデューティサイクル変調器(Duty Cycle Modulator)集積回路(IC)U1に結合される。ICU1は、従来の方式で電流モード制御において動作する。ICU1が、トランジスタQ1のゲート端子に結合されるデューティサイクル変調制御信号(Duty Cycle Modulated Control Signal)Drvを発生させる。トランジスタQ1と変圧器T1が、従来の方式で、巻線W1よりトランス結合される電圧から、第一の出力供給電圧を発生させる。電圧Voutは、一次側の基準電位GNDから絶縁され、絶縁の二次側の基準電位GND-ISOLATEDを基準とする。出力供給電圧Voutが、従来の方式でデューティサイクル変調制御信号Drvにより制御される。

## 【0011】

40

キャパシタC3に生じたフィードバック信号FBは、一次側の基準電位GNDを基準とする。信号FBが、従来の方式により光カプラU2で発生する。信号FBが、第一の出力供給電圧Voutの振幅を示す。フィードバック信号FBが、従来の負帰還の方式でデューティサイクル変調制御信号Drvのデューティサイクルの変動を発生させる。供給電圧DCinは、またスタートアップ抵抗R3を介してICU1に結合されて、従来の方式でスタートアップ動作を開始するためのスタートアップ電圧HVを発生させる。

## 【0012】

50

図2a、2bおよび2cは、図1における回路100の動作に関連する電流または電圧波形を示す。図3a、3bおよび3cは、それぞれに図2a、2bおよび2cにおける電流または電圧波形を拡大された時間スケールで示す。図2a、2bおよび2c、図3a、3bおよび3c、ならびに図1における同じ符号および同じ数字は、同じアイテムまたは

同じ機能を示す。

#### 【0013】

一つの発明の特徴を実施する際、図1におけるスナバキャパシタC4は、ダイオードD1を介して、よりはるかに大きいフィルタ供給キャパシタC2に結合される。トランジスタQ1がオフにされると、図3aまたは3bの時刻t2で、図1の巻線W1における電流IW1の流れが遮断される。結果的に、図2aにおける周期Tを有する、図1、3aおよび2aにおけるドレーン電圧V102の周期的なフライバック部分V102-FBは、図1における端子102で発生し、それにより、図1、3cおよび2cにおける電流ID1が図1におけるキャパシタC4(複数)、ダイオードD1およびキャパシタC2に流れる。従って、キャパシタC2およびC4は、ドレーン電圧V102に関する容量性分圧器を形成する。電流ID1はキャパシタC2およびC4のそれぞれを充電する。従って、有利なこととしては、供給電圧Vccの第一の部分がキャパシタC2に生じる。

10

#### 【0014】

もう一つの発明の特徴を実施する際、キャパシタC2およびC4は、スナバネットワーク104に含まれる。直列結合されるキャパシタC2およびC4の容量は、キャパシタC2の容量値より、キャパシタC4の容量値によって決定される。トランジスタQ1がオフになると、スナバネットワーク104が、従来の方式で図3aにおける上昇ランプ(up-ramping)のフライバック部分V102-FBの変化率を低減する。図1におけるスナバネットワーク104は、従来の方式でエレメント104aにより集合的に特定される他の構成要素を含むことができる。インダクタL1がスナバキャパシタC4と一次側の基準電位GNDとの間に結合される。

20

#### 【0015】

図2aおよび3aの時刻t0で、図1のトランジスタQ1がオンにされ、上昇ランプ電流IW1を巻線W1に発生させる。電流IW1は、線形に増加し、磁気エネルギーを巻線W1のインダクタンスに蓄積する。同時に、インダクタL1がキャパシタC4と並列で結合されて、共振回路を形成する。インダクタL1における共振電流IL1は、キャパシタC4の端子102aで電圧を発生させ、該電圧は、図3bおよび3aの時刻t1で図1の出力電圧Vccを超える。それにより、ダイオードD1が導通になる。導通になってから、ダイオードD1は、図3cにおける電流ID1の下降ランプ(down-ramping)の部分ID1aを図1のキャパシタC2に発生させる。有利なこととしては、下降ランプ部分ID1aは、電圧Vccの第二の部分をキャパシタC2に生じさせる。ダイオードD1は、導通する時、巻線L1の両端の間に電圧Vccを印加して、図3bにおける電流IL1の対応する下降ランプ部分IL1aを発生させる。

30

#### 【0016】

有利なこととしては、スナバキャパシタC4に蓄積された電荷またはエネルギーは、無駄にされず、かわりに、使用されて電圧Vccの第二の部分を発生させる。また、有利なこととしては、変圧器T1に追加の巻線を必要とせずに、電圧Vccが発生する。

#### 【0017】

更なる発明の特徴を実施する際、スイッチングトランジスタQ3の主電流導通端子対は、インダクタL1の両端で、それぞれに端子102aおよび基準電位GNDに結合される。電圧Vccは、抵抗R3を介してツェナーダイオードの陰極端子110に結合されて、電圧比較器トランジスタQ2の基準ベース電圧VBを生成する。ツェナーダイオードD3のもう一方の端子は、一次側の基準電位GNDに結合される。トランジスタQ2のエミッタ端子は、電圧Vccが生じるキャパシタC2に結合される。トランジスタQ2のコレクターは、トランジスタQ3のゲート端子にも、そして負荷抵抗R4にも、結合される。

40

#### 【0018】

電圧Vccが過大になる時、電圧Vccと端子110で生じたツェナー電圧との間の差は、トランジスタQ2のベースとエミッタ間の閾値順電圧を超える。結果的に、トランジスタQ2が導通になって、それにより、トランジスタQ3がオンになる。このように、トランジスタQ2は、選択的に充電電流ID1をゼロにするまたは大幅に低減する。また、

50

電流  $I_{L1}$ 、インダクタ  $L_1$  は、トランジスタ  $Q_3$  を介して短絡される。結果としては、有利になるように、電圧  $V_{CC}$  が調整される。電圧調整についての代替形態は、破線で示される導体を介してキャパシタ  $C_2$  と並列で結合される短絡レギュレータダイオード  $D_4$  を使用することにより、得ることができる。

【図 1】

【図 2 a】

【図 2 b】

【図 2 c】

【図 3 a】

【図 3 b】

【図 3 c】

---

フロントページの続き

審査官 安食 泰秀

(56)参考文献 米国特許出願公開第2005/0207185(US,A1)

米国特許出願公開第2004/0085050(US,A1)

米国特許第04912620(US,A)

(58)調査した分野(Int.Cl., DB名)

H 02 M 3 / 28